画像表示装置

【課題】画素内の配線を減らし、量産上の歩留りを上げると共に、低コスト化を図ることのできる画像表示装置を提供する。

【解決手段】画像表示装置は、マトリクス状に配列された画素において、画素毎に設けられ、透明基板(36)上で透明基板に平行に移動し、光の透過及び遮断を行う機械的シャッタ部(26)と、透明基板上で機械的シャッタ部を挟むように配置される一対の制御電極(25,27)と、この一対の制御電極に、予め定められたタイミングで、制御電極のための高電圧及び低電圧をそれぞれに交互に印加する制御電極駆動回路と、画素毎に設けられ、画素毎の階調値に応じたタイミングで、信号線を介して設定される高電圧及び低電圧のいずれかを印加することにより、機械的シャッタ部の動作を静電的に制御するシャッタ制御回路を備える。

【解決手段】画像表示装置は、マトリクス状に配列された画素において、画素毎に設けられ、透明基板(36)上で透明基板に平行に移動し、光の透過及び遮断を行う機械的シャッタ部(26)と、透明基板上で機械的シャッタ部を挟むように配置される一対の制御電極(25,27)と、この一対の制御電極に、予め定められたタイミングで、制御電極のための高電圧及び低電圧をそれぞれに交互に印加する制御電極駆動回路と、画素毎に設けられ、画素毎の階調値に応じたタイミングで、信号線を介して設定される高電圧及び低電圧のいずれかを印加することにより、機械的シャッタ部の動作を静電的に制御するシャッタ制御回路を備える。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、画像表示装置に関し、より詳しくは、機械的シャッタを用いた画像表示装置に関する。

【背景技術】

【0002】

図20は従来の技術による、機械的シャッタを用いた画像表示装置のシャッタ制御回路を示す図である。各画素213には信号線206が設けられており、信号線206と信号蓄積容量204の一端とは走査スイッチ205で接続されている。信号蓄積容量204の一端は更にシャッタ負電圧書込み用nMOSトランジスタ203のゲートに接続されており、シャッタ負電圧書込み用nMOSトランジスタ203のドレインはシャッタ正電圧書込み用pMOSトランジスタ202のドレインに接続されている。各画素にはシャッタ電圧線211に接続された双極性シャッタ(Dual Actuator Shutter Assembly)201を有しているが、二つある双極性シャッタ201の制御電極の内の一方はシャッタ負電圧書込み用nMOSトランジスタ203のドレインに接続されており、制御電極の他方は制御電極電圧線209に接続されている。なお信号蓄積容量204の他端はシャッタ電圧線211に接続されており、シャッタ負電圧書込み用nMOSトランジスタ203のソースはシャッタ負電圧書込み用nMOSソース電圧線212に、シャッタ正電圧書込み用pMOSトランジスタ202のゲートとドレインはそれぞれシャッタ正電圧書込み用pMOSゲート電圧線207と正電圧線208に、走査スイッチ205のゲートは走査線210に接続されている。なお上記の双極性シャッタ201は、遮光面上に設けられた開口に対向して設けられており、当該画像表示装置にはこのような画素がマトリクス状に配列されている。

【0003】

次に、上記の画像表示装置の動作について説明する。信号線206に書込まれた画像信号電圧は、走査線210を順次走査することによって走査スイッチ205を介して信号蓄積容量204に記憶される。次に、全画素の信号蓄積容量204に対する画像信号電圧の書込み走査が終了した後に、各画素において、書込まれた画像信号電圧を元に双極性シャッタ201の制御電極の内の一方に対して画像信号の増幅書込みを行う。即ちまず全画素において、シャッタ正電圧書込み用pMOSゲート電圧線207を所定の期間だけ低電圧にすることによって、シャッタ正電圧書込み用pMOSトランジスタ202をこの期間のみオン状態にして、双極性シャッタ201の制御電極の内の一方の電極に、正電圧線208に印加されていた所定の正電圧をプリチャージする。この次にシャッタ負電圧書込み用nMOSソース電圧線212を、所定の期間だけ所定の低電圧にする。このとき信号蓄積容量204に画像信号電圧として高電圧が書込まれていた場合には、この期間のみシャッタ負電圧書込み用nMOSトランジスタ203がオン状態となることによって、双極性シャッタ201の制御電極の内の一方の電圧はシャッタ負電圧書込み用nMOSソース電圧線212に印加されている所定の低電圧に書き換えられる。また信号蓄積容量204に画像信号電圧として低電圧が書込まれていた場合には、この期間もシャッタ負電圧書込み用nMOSトランジスタ203はオフ状態を維持するため、双極性シャッタ201の制御電極の内の一方の電圧は、既にプリチャージされた所定の正電圧を維持する。

【0004】

このようにして双極性シャッタ201の制御電極の内の一方の電極に画像信号の増幅書込みを行うが、これと並行して制御電極電圧線209への印加電圧を制御することによって、双極性シャッタ201を静電的に開閉操作することができる。このように双極性シャッタ201で遮光面上に設けられた開口を開閉することで光の透過量を制御して、当該画像表示装置は書込まれた画像信号電圧に対応した画像を画素マトリクス上に表示することができる。なお、このような従来例に関しては、例えば特許文献1などに詳しく記載されている。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】米国特許出願公開第2008/174532号明細書

【特許文献2】米国特許出願公開第2008/145527号明細書

【特許文献3】米国特許出願公開第2008/062500号明細書

【特許文献4】米国特許出願公開第2007/159679号明細書

【特許文献5】米国特許出願公開第2007/091038号明細書

【特許文献6】米国特許出願公開第2007/030555号明細書

【特許文献7】米国特許出願公開第2006/187528号明細書

【特許文献8】米国特許出願公開第2009/034052号明細書

【特許文献9】米国特許出願公開第2008/158635号明細書

【特許文献10】米国特許出願公開第2007/223080号明細書

【特許文献11】米国特許出願公開第2007/216987号明細書

【特許文献12】米国特許出願公開第2006/187530号明細書

【特許文献13】米国特許出願公開第2008/030827号明細書

【特許文献14】米国特許出願公開第2006/187529号明細書

【特許文献15】米国特許出願公開第2006/250676号明細書

【特許文献16】米国特許出願公開第2008/123175号明細書

【特許文献17】米国特許出願公開第2006/187531号明細書

【特許文献18】米国特許出願公開第2008/151357号明細書

【特許文献19】米国特許出願公開第2007/002156号明細書

【特許文献20】米国特許出願公開第2010/110518号明細書

【特許文献21】米国特許出願公開第2010/027100号明細書

【特許文献22】米国特許出願公開第2009/257245号明細書

【特許文献23】米国特許出願公開第2009/244678号明細書

【特許文献24】米国特許出願公開第2009/195855号明細書

【特許文献25】米国特許出願公開第2009/103164号明細書

【特許文献26】米国特許出願公開第2008/283175号明細書

【特許文献27】米国特許出願公開第2008/278798号明細書

【特許文献28】米国特許出願公開第2008/158636号明細書

【特許文献29】米国特許出願公開第2008/129681号明細書

【特許文献30】米国特許出願公開第2008/094853号明細書

【特許文献31】米国特許出願公開第2008/037104号明細書

【特許文献32】米国特許出願公開第2007/279727号明細書

【特許文献33】米国特許出願公開第2007/205969号明細書

【特許文献34】米国特許出願公開第2007/195026号明細書

【特許文献35】米国特許出願公開第2006/250325号明細書

【特許文献36】米国特許出願公開第2007/086078号明細書

【特許文献37】米国特許出願公開第2006/256039号明細書

【特許文献38】米国特許出願公開第2006/209012号明細書

【特許文献39】米国特許出願公開第2006/187191号明細書

【特許文献40】米国特許出願公開第2006/187190号明細書

【特許文献41】米国特許出願公開第2010/188443号明細書

【発明の概要】

【発明が解決しようとする課題】

【0006】

従来の技術は、各画素の双極性シャッタ201を制御するために各画素に多くの配線を設ける必要があることから、画素内に設ける回路が密になり、量産上の歩留りを上げ難いという課題があった。例えば図20の例では、各画素には信号線206、シャッタ正電圧書込み用pMOSゲート電圧線207、正電圧線208、制御電極電圧線209、走査線210、シャッタ電圧線211、シャッタ負電圧書込み用nMOSソース電圧線212の計7本の配線が必要であった。

【0007】

本発明は、上述の事情を鑑みてしたものであり、低消費電力でありながら高コントラストで色再現性が良いといった、機械的シャッタを用いた従来技術の利点である高画質性能を維持しながら、画素内の配線を減らし、量産上の歩留りを上げると共に、低コスト化を図ることのできる表示装置を提供することを目的とする。

【課題を解決するための手段】

【0008】

上記の課題は、マトリクス状に配列された画素において前記画素毎に設けられ、透明基板上で前記透明基板の面に平行に移動し、光の透過及び遮断を行う機械的シャッタ部と、前記透明基板上で前記機械的シャッタ部を挟むように配置される一対の制御電極と、前記透明基板に向けて光を発し、前記透明基板と平行に配置される面状の光源と、前記面状の光源上の前記透明基板側に成膜され、前記機械的シャッタ部が光の透過及び遮断を行う領域に対応して前記画素毎に開けられた光学的開口を有し、前記面状の光源から出射された光に対して、前記光学的開口以外の領域を遮光する遮光膜と、前記一対の制御電極に、前記制御電極のための高電圧及び低電圧をそれぞれに印加する制御電極駆動回路と、前記画素毎に設けられ、前記画素毎の階調値に応じたタイミングで、信号線を介して設定される高電圧及び低電圧のいずれかを印加することにより、前記機械的シャッタ部の動作を静電的に制御するシャッタ制御回路とを備え、前記遮光膜は、誘電体で形成されている、ことを特徴とする画像表示装置によって解決される。

【0009】

ここで、「面状の光源」とは、点光源等の光源から発せられた光を導光板等を介して出射するように構成されたバックライト等を含む意味である。

【発明の効果】

【0010】

本発明によれば、低消費電力でありながら高コントラストで色再現性が良いといった、機械的シャッタを用いた従来技術の利点である高画質性能を維持しながら、更に画素内の配線を少なくすることが可能であるため、量産上の歩留りを上げて低コスト化を実現することができる。

【図面の簡単な説明】

【0011】

【図1】第1実施形態に係る画像表示装置について示す図である。

【図2】第1実施形態に係る画像表示装置のTFT基板の画素周辺回路図である。

【図3】第1実施形態に係る画像表示装置のシャッタ制御回路について示す図である。

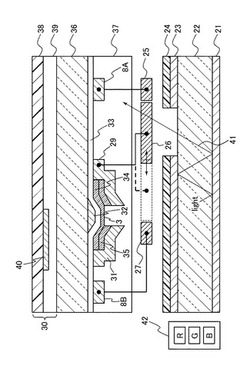

【図4】第1実施形態に係る画像表示装置における、画素の断面構造を示す図である。

【図5】図3のシャッタ制御回路の動作タイミングチャートである。

【図6A】画像信号電圧が0(V)の時のシャッタ電極への信号電圧書込みを説明するための図である。

【図6B】画像信号電圧が0(V)の時のシャッタ電極への信号電圧書込みを説明するための図である。

【図6C】画像信号電圧が0(V)の時のシャッタ電極への信号電圧書込みを説明するための図である。

【図7A】画像信号電圧がVsigHの時のシャッタ電極への信号電圧書込みを説明するための図である。

【図7B】画像信号電圧がVsigHの時のシャッタ電極への信号電圧書込みを説明するための図である。

【図7C】画像信号電圧がVsigHの時のシャッタ電極への信号電圧書込みを説明するための図である。

【図8】第2実施形態に係る画像表示装置の表示領域内の画素配列構成図である。

【図9】第2実施形態に係る画像表示装置における、画素の断面構造を示す図である。

【図10】第3実施形態に係る画像表示装置における、画素断面構造を示す図である。

【図11】第4実施形態に係る画像表示装置のシャッタ制御回路を示す図である。

【図12】第5実施形態に係る画像表示装置の画素周辺回路図である。

【図13】第5実施形態に係る画像表示装置のシャッタ制御回路を示す図である。

【図14】第5実施形態に係る画像表示装置における、画素断面構造を示す図である。

【図15】図13のシャッタ制御回路の動作タイミングチャートである。

【図16】第6実施形態に係る画像表示装置の画素周辺回路図である。

【図17】第6実施形態に係る画像表示装置のシャッタ制御回路を示す図である。

【図18】図13のシャッタ制御回路の動作タイミングチャートである。

【図19】第7実施形態に係るインターネット画像表示装置の構成図である。

【図20】従来の技術によるシャッタ制御回路を示す図である。

【発明を実施するための形態】

【0012】

以下、本発明の実施形態について、図面を参照しつつ説明する。なお、図面において、同一又は同等の要素には同一の符号を付し、重複する説明を省略する。

【0013】

[第1実施形態]

以下、図1〜図7を用いて、本発明の第1実施形態に係る画像表示装置について、その構成および動作を順次説明する。

【0014】

図1は、各画素のシャッター機構により表示画像の制御を行う、本発明の第1実施形態に係る画像表示装置300について示す図である。この図1に示されるように、画像表示装置300は、各画素毎に、光を透過する開口部を有する遮光膜(後述)を備えるバックライト光源320と、バックライト光源320からの光の透過をシャッター機構部(後述)により制御すると共に、タッチパネルを有するTFT(Thin Film Transistor)基板330と、バックライト光源320のR(赤)G(緑)B(青)の3色の光を時間をずらして発光させるための制御を行う発光制御回路302と、TFT基板330のシャッター機構部の動作を、パネル制御線308を介して制御する表示制御回路306と、発光制御回路302及び表示制御回路306の統括的な制御を行うシステム制御回路304とを有している。

【0015】

図2は、図1のTFT基板330の画素周辺回路図である。マトリクス状に配列された画素13が表示領域を構成しており、画素13には列方向に信号線6A及び6Bと、制御電極線8A及び8Bが、行方向に走査線10、容量線11、シャッタ電圧書込み用ソース電圧線12が設けられている。表示領域の周辺で、信号線6A及び6Bの一端は画像信号電圧書込み回路14に接続されており、制御電極線8A及び8Bの一端はそれぞれ制御電極駆動回路17に接続されている。また走査線10の一端は走査回路15に接続されており、容量線11、シャッタ電圧書込み用ソース電圧線12の一端は、それぞれ書込み駆動回路16に接続されている。なお、図2は簡単のために表示領域を画素数が4×3画素のマトリクスで記載しているが、本発明の開示する技術思想が特に画素数を制限するものではない。

【0016】

図3には、図2の各画素13におけるシャッタ制御回路18が示されている。各画素13には信号線6Aが設けられており、信号線6Aと信号蓄積容量4とは走査スイッチ5で接続されている。信号蓄積容量4は更にシャッタ電圧書込み用トランジスタ3のゲートに接続されており、シャッタ電圧書込み用トランジスタ3のドレインは双極性シャッタ1のシャッタ電極に接続されている。二つある双極性シャッタ1の制御電極の内の一方は画素内の制御電極線8Aに接続されているが、制御電極の他方は隣接する画素の制御電極線8Bに接続されている。なお信号蓄積容量4の他端は容量線11に接続されており、シャッタ電圧書込み用トランジスタ3のソースはシャッタ電圧書込み用ソース電圧線12に、走査スイッチ5のゲートは走査線10に接続されている。なお上記の双極性シャッタ1は、後に図4を用いて説明するように、遮光面上に設けられた開口に対向して設けられている。

【0017】

なお、図3には信号線6Aと制御電極線8Aを有する画素と、信号線6Bと制御電極線8Bを有する画素の、2画素分が記載されている。両画素は後述のように駆動条件は異なるものの、基本的なシャッタ制御回路は同一である。

【0018】

図4は、画素13の画素部断面構造図である。ガラス基板36上には、高融点金属で形成されたゲート電極32、ゲート絶縁膜33、ノンドープのアモルファスシリコン薄膜34、高濃度n型不純物をドープしたアモルファスシリコン薄膜35、ソース電極31、ドレイン電極29とから構成されるアモルファスシリコン薄膜トランジスタが設けられており、これはシャッタ電圧書込み用トランジスタ3に対応するものである。更にガラス基板36上には、ソース電極31、ドレイン電極29と同じAl配線層で制御電極線8A、8Bが形成されており、これらはシリコンナイトライドと有機材料の多層膜からなる保護膜37によって覆われている。

【0019】

保護膜37上には、シャッタ電極26と、二つの制御電極25、27を有する双極性シャッタ1が設けられており、ドレイン電極29はシャッタ電極26に、制御電極線8Aは制御電極25に、制御電極線8Bは制御電極27に、それぞれコンタクトホールを介して接続されている。またこれらシャッタ電極26と、二つの制御電極25、27には互いに接触した際の短絡防止のために、表面には絶縁膜が形成されている。なおここでシャッタ電極26は、シャッタ電極26に入力される電圧と、二つの制御電極25、27に入力される電圧との相対関係による電界でその位置が制御されるため、図4には破線を用いてその可動範囲も開示している。なお図4には記載されていないが、画素13内に設けられたその他のトランジスタも、同様にアモルファスシリコン薄膜トランジスタで構成されている。

【0020】

シャッタ電極26に対してガラス基板36と反対側には、R(赤)G(緑)B(青)の3色の独立LED光源からなる光源42を有する導光板22が設けられている。導光板22の両面には反射膜21、23が設けられているが、ここで特にシャッタ電極26側の反射膜23は多層誘電膜より構成されている。反射膜23を構成する多層誘電膜はTiO2、Ta2O3等の高屈折率材料とSiO2、MgF2等の低屈折材料の積層構造からなっており、これらの積層構造の各膜厚を適切な値に設計することによって、光源42が有するR(赤)G(緑)B(青)の3色の独立LED光源の射出光に対して実用上十分な全反射特性を得ることができる。ところで多層誘電膜を全反射膜として用いた場合の課題は、垂直方向に入射する光に対して最適設計した場合に、水平に近い角度で入射した光に対しては反射特性が悪化することである。反射膜23が光を透過した場合には表示装置の光漏れとなってしまい、コントラストの著しい低下を招いてしまう。そこでこのような光漏れを防止するために、更に反射膜23の上には有機材料で作成された黒色樹脂膜24を形成した。この黒色樹脂膜は、ポリイミド樹脂等にカーボンブラック、チタンブラック等の顔料粒子を適切に分散させることで形成することができる。ここで反射膜23及び黒色樹脂膜24には図4に示すように、シャッタ電極26に対応する位置に開口が設けられており、光源42から射出されて導光板22を伝播した光41の一部が、この開口から射出されるように構成されている。開口は例えば、黒色樹脂膜24をマスクとしたフォトリソグラフィーによって一括加工形成することができる。

【0021】

ガラス基板36に対して導光板22と反対側には、フィルムシート38、センス電極40、保護膜39からなるタッチパネル30が設けられている。タッチパネル30のセンス電極40は表示領域の周辺でタッチ検出用回路に接続されているが、この部分の構成は既に一般に知られている技術であるため、ここではその詳細な説明は省略する。

【0022】

次に、図3で述べた第1実施形態のシャッタ制御回路18の動作について説明する。図5は第1実施形態のシャッタ制御回路18の動作タイミングチャートであり、横軸に時間を取って、縦軸に各部分の電圧を示したものである。また特に最下段に記載した双極性シャッタ1のシャッタ電極26の電圧値に関しては、画像信号によって約0(V)と約Vhの二値を取るため、図面を判り易くするために前者を実線、後者を破線で示している。

【0023】

[タイミングt1まで]

この期間には、画素に対する画像信号電圧の書込みが行われている。この期間は制御電極線8A、8Bにはそれぞれ高電圧Vh、低電圧0(V)が印加されているが、後述するようにシャッタ電極26の極性反転駆動を目的として、奇数画素列と偶数画素列に相当する制御電極線8A、8Bの印加電圧は毎フレーム毎にその値が入れ替わる。各画素の走査スイッチ5は走査線10によって順次走査されており、走査スイッチ5が走査された画素の信号蓄積容量4には、信号線6A、6Bから所定の画像信号電圧が書込まれる。ここで信号線6A、6Bに印加される画像信号電圧は例えば7(V)と0(V)の二値をとるが、白表示時と黒表示時にそれぞれ7(V)と0(V)のいずれに該当するかは、シャッタ電極26の極性反転駆動を目的とした制御電極線8A、8Bの印加電圧の毎フレーム毎の値によって、信号線6A及び6Bの列毎に入れ替わる。なお容量線11には0(V)、シャッタ電圧書込み用ソース電圧線12にはVmが印加されており、双極性シャッタ1のシャッタ電極26には約0(V)ないし約Vhが印加されている。なおここでVhの値は双極性シャッタ1の静電的な機械駆動が可能な最小の電圧に設計されるが、例えばこの値は20(V)である。またVmの値は信号電圧が信号蓄積容量4に書込まれてもシャッタ電圧書込み用トランジスタ3がオンすることのない値であり、例えば7(V)である。

【0024】

[タイミングt1からt2まで]

この期間にはシャッタ電極26の極性反転駆動を目的として、毎フレーム毎に奇数画素列と偶数画素列に相当する制御電極線8A、8Bの印加電圧の入れ替わりが行われる。本実施形態は後述するように光源42の発光にサブフィールド毎に時間重みを持たせて、シャッタ電極26の開閉で外部への発光を制御するPWM(Pulse Width Modulation)駆動を行うが、制御電極線8A、8Bの印加電圧の入れ替えはフレーム毎に替えて、サブフィールド毎や、複数サブフィールド毎に行っても良い。制御電極線8A、8Bの印加電圧の入れ替えを行わないサブフィールドでは、この[タイミングt1からt2まで]の期間は設ける必要はない。なお、制御電極線8A、8Bの印加電圧の入れ替えを頻繁に行う場合には、これに伴うタイミングt1からt2までの遷移期間を頻繁に設ける必要があることと、消費電力が増加することには留意する必要がある。

【0025】

[タイミングt2からt3まで]

この期間には信号蓄積容量4に書込まれた画像信号電圧に基づいて、全画素において一斉にシャッタ電極26への信号電圧書込みが行われる。容量線11とシャッタ電圧書込み用ソース電圧線12に同時にVhが書込まれ、この後に両者の電圧は揃って0(V)に立ち下げられる。この動作によってシャッタ電圧書込み用トランジスタ3が制御され、信号蓄積容量4に書込まれていた画像信号電圧が0(V)の場合にはシャッタ電極26には信号電圧として(Vh−Vth)が書込まれ、画像信号電圧が7(V)だった場合にはシャッタ電極26には信号電圧として0(V)が書込まれる。なおここでVthは、シャッタ電圧書込み用トランジスタ3のしきい値電圧である。

【0026】

以下に図6、図7を用いて、上記のシャッタ電極26への信号電圧書込みについて詳細に説明する。

【0027】

図6A〜6Cは信号蓄積容量4に書込まれていた画像信号電圧が0(V)の場合の、シャッタ電極26への信号電圧書込み説明図である。図6Aはこの期間の最初に信号蓄積容量4に0(V)が書込まれている場合の画素等価回路を示しており、ここではシャッタ電極26に替えて、シャッタ電極26の等価入力容量45を記載してある。次にこの期間に、容量線11とシャッタ電圧書込み用ソース電圧線12が同時に操作される状態を考えると、これは図6Bの等価回路に示すように、0(V)が書込まれている信号蓄積容量4は短絡と等価であり、容量線11とシャッタ電圧書込み用ソース電圧線12はまとめて一本の等価配線46とみなす事ができる。すると更にシャッタ電圧書込み用トランジスタ3はダイオード接続されたトランジスタであるから、図6Cの等価回路に示すように、全体はシャッタ電極26の等価入力容量45がシャッタ電圧書込み用トランジスタ3の等価ダイオード47を介して等価配線46と接続された構成とみなすことができる。この図6Cの等価回路を用いると、容量線11とシャッタ電圧書込み用ソース電圧線12に同時にVhが書込まれた際には、等価ダイオード47がオンしてシャッタ電極26の等価入力容量45に信号電圧として(Vh−Vth)が書込まれ、この後に容量線11とシャッタ電圧書込み用ソース電圧線12に同時に0(V)が書込まれてもシャッタ電極26が(Vh−Vth)を信号電圧として保持することが容易に説明できる。

【0028】

次に、図7A〜7Cは信号蓄積容量4に書込まれていた画像信号電圧が7(V)であった場合の、シャッタ電極26への信号電圧書込み説明図である。図7Aはこの期間の最初に信号蓄積容量4に7(V)(図7A〜7Cでは一般化のためにVsigHと記載)が書込まれている場合の画素等価回路を示しており、ここでもシャッタ電極26に替えて、シャッタ電極26の等価入力容量45を記載してある。次にこの期間に、容量線11とシャッタ電圧書込み用ソース電圧線12が同時に操作される状態を考えると、これは図7Bの等価回路に示すように、7(V)が書込まれている信号蓄積容量4は7(V)の直流電源48と等価であり、容量線11とシャッタ電圧書込み用ソース電圧線12はまとめて一本の等価配線46とみなす事ができる。するとゲートに7(V)の直流電源48が接続されたシャッタ電圧書込み用トランジスタ3は常時オンであるために等価抵抗49とみなす事ができるから、図7Cの等価回路に示すように、全体はシャッタ電極26の等価入力容量45がシャッタ電圧書込み用トランジスタ3の等価抵抗49を介して等価配線46と接続された構成とみなすことができる。この図7Cの等価回路を用いると、容量線11とシャッタ電圧書込み用ソース電圧線12に同時にVhが書込まれた際には、等価抵抗49を経由してシャッタ電極26の等価入力容量45には信号電圧として一旦はVthが書込まれ、その後に容量線11とシャッタ電圧書込み用ソース電圧線12に同時に0(V)が書込まれた際には、等価抵抗49を経由してシャッタ電極26の等価入力容量45には再び0(V)が書込まれることが容易に説明できる。

【0029】

このようなシャッタ電圧書込み用トランジスタ3と信号蓄積容量4を用いた信号書込み回路を、ここでは擬似ダイオード回路と称することにする。

【0030】

[タイミングt3からt4まで]

この期間には容量線11とシャッタ電圧書込み用ソース電圧線12は0(V)に立ち下げられた電圧値を維持しており、シャッタ電極26に0(V)が書込まれる場合には、この期間に電圧は約0(V)に収束する。

【0031】

[タイミングt4以降]

この期間は再びタイミングt1までの動作と同様に、画素に対する画像信号電圧の書込みが行われる。各画素の走査スイッチ5は走査線10によって順次走査され、走査スイッチ5が走査された画素の信号蓄積容量4には、信号線6A、6Bから所定の画像信号電圧が書込まれる。シャッタ電圧書込み用ソース電圧線12にはVmが印加されており、信号電圧が信号蓄積容量4に書込まれても基本的にはシャッタ電圧書込み用トランジスタ3がオンすることはない。

【0032】

但しシャッタ電極26に0(V)が書込まれており、信号蓄積容量4に7(V)(VsigH)が書込まれている場合には、シャッタ電極26の電圧はシャッタ電圧書込み用トランジスタ3のオフする電圧である7(V)−Vth(VsigH−Vth)まで、この期間に再度上昇する点には注意が必要である。基本的にシャッタ電極26は二値駆動であるため、0(V)が7(V)−Vth(VsigH−Vth)に上昇しても動作そのものに大きな支障はないが、これによって動作マージンが減る方向にはなる。ここでVsigHは高い電圧である方がシャッタ電圧書込み用トランジスタ3によるシャッタ電極26の等価入力容量45への書込み動作はより高速化できるという長所がある。しかしその一方で、画像信号電圧書込み回路14から信号線6A及び6BにVsigHを書込む際の消費電力が上昇する点や、上記のようにシャッタ電極26に0(V)が書込まれている場合には、シャッタ電極26の電圧はシャッタ電圧書込み用トランジスタ3のオフする電圧である7(V)−Vth(VsigH−Vth)までは再度上昇するといった副作用も有しているため、本実施形態では7(V)としたVsigHの電圧値は、これらを勘案した上で最適に設定する必要がある。

【0033】

次に図2で述べた第1実施形態の画素周辺回路の動作について説明する。前述の[タイミングt1まで]に相当する画素に対する画像信号電圧の書込み期間においては、走査線10は走査回路15によって順次走査され、これと同期して信号線6A及び6Bには画像信号電圧書込み回路14から画像信号電圧が書込まれる。ここで前述のように本実施形態は光源42の発光にサブフィールド毎に時間重みを持たせて、シャッタ電極26の開閉で外部への発光を制御するPWM駆動を行う。このため画像信号電圧書込み回路14から信号線6A及び6Bに書込まれる画像信号電圧は、例えば0(V)と7(V)の二値の電圧であり、これによって各画素に設けられたシャッタ電極26に印加される信号電圧を制御する。なお白表示時と黒表示時にそれぞれ7(V)と0(V)のいずれに該当するかは、シャッタ電極26の極性反転駆動を目的とした制御電極線8A、8Bの印加電圧の毎フレーム毎の値によって、信号線6A及び6Bの列毎に入れ替わることは既に述べたとおりである。次に全画素に対する画像信号電圧の書込みが終了した後、前述の[タイミングt1からt2まで]の期間において、シャッタ電極26の極性反転駆動を目的として、フレーム毎に奇数画素列と偶数画素列に相当する制御電極線8A、8Bの印加電圧が制御電極駆動回路17によって相補的に駆動されることは既に述べたとおりである。また引続き行われる[タイミングt2からt3まで]における、信号蓄積容量4に書込まれた画像信号電圧に基づいた、全画素におけるシャッタ電極26への信号電圧書込みは、書込み駆動回路16が容量線11、シャッタ電圧書込み用ソース電圧線12を一斉に駆動することによって行われる。その後の[タイミングt4以降]において、シャッタ電圧書込み用ソース電圧線12へのVm印加を行うのも書込み駆動回路16である。

【0034】

最後に図4で述べた第1実施形態のシャッタ電極26近傍構造の動作について説明する。前述の[タイミングt1まで]に相当する、画素に対する画像信号電圧の書込み終了後、[タイミングt1からt2まで]の期間においてフレーム期間毎に奇数画素列と偶数画素列に相当する制御電極線8A、8Bの印加電圧が制御され、これらの電圧はそれぞれ双極性シャッタ1の制御電極25、27に印加される。例えばあるフレームにおいて、制御電極25には0(V)、制御電極27にはVh(例えば20(V))が印加される。次いで[タイミングt2からt3まで]の期間におけるシャッタ電極26への信号電圧書込み動作によって、シャッタ電極26には約Vh(例えば20(V))或いは約0(V)が書込まれる。ここで制御電極25には0(V)、制御電極27にはVh(例えば20(V))が印加されているため、シャッタ電極26と制御電極25、27が生じる電界の効果によって、シャッタ電極26に約Vh(例えば20(V))が書込まれた場合にはシャッタ電極26は反射膜23及び黒色樹脂膜24の開口上でその位置が安定し、シャッタ電極26に約0(V)が書込まれた場合にはシャッタ電極26は反射膜23及び黒色樹脂膜24の遮光上でその位置が安定する。これによりシャッタ電極26に約Vh(例えば20(V))が書込まれた場合には、光源42から射出されて導光板22を伝播した光41は開口から射出されてもシャッタ電極26で反射されることで再び導光板22に戻されてしまうため、画素は非発光状態として観測される。またシャッタ電極26に約0(V)が書込まれた場合には光源42から射出されて導光板22を伝播した光41はこの開口から射出されるため、画素は発光状態として観測される。

【0035】

なお、ここで次のフレームにおいては制御電極25、27と画像信号電圧の極性は逆になる。即ち制御電極25にはVh(例えば20(V))、制御電極27には0(V)が印加されるため、シャッタ電極26に約0(V)が書込まれた場合には、光源42から射出されて導光板22を伝播した光41は開口から射出されてもシャッタ電極26で反射されることで再び導光板22に戻されてしまうため、画素は非発光状態として観測される。またシャッタ電極26に約Vh(例えば20(V))が書込まれた場合には光源42から射出されて導光板22を伝播した光41はこの開口から射出されるため、画素は発光状態として観測される。このようにシャッタ電極26の極性反転駆動を行うことによって、シャッタ電極26、制御電極25、27の表面の絶縁膜に印加される電界を交流化することができ、これらの電極の電気的安定性をより増加させることができる。

【0036】

前述のように本実施形態では光源42の発光にサブフィールド毎に時間重みを持たせて、シャッタ電極26の開閉で外部への発光を制御するPWM駆動を行う。即ち光源42が有するR(赤)G(緑)B(青)の3色の独立LED光源の発光期間に2のn乗の時間重みを持たせ、画素毎のシャッタ電極26の開閉制御と組合されることで、画素毎にPWM方式による階調発光を実現すると同時に、FSC方式によるカラー表示を実現している。このような光源42の点灯は、[タイミングt1まで]及び[タイミングt4以降]の、画素に対する画像信号電圧の書込み期間内に行われる。

【0037】

上述したように、シャッタ電極26への信号電圧の書込みを行う構成としたことにより、画素内の配線を減少させることができる。また、これにより、量産上の歩留りを上げると共に、低コスト化を図ることができる。

【0038】

また、画像信号に応じて機械的シャッタに所定の高電圧、或いは所定の低電圧を選択的に印加した場合に、機械的シャッタと遮光膜との間に電界が生じると、この電界は画像信号に応じて変調されてしまうために機械的シャッタの動作マージンを著しく損なってしまう恐れがあるが、本実施形態においては、更に遮光膜を誘電体で形成しているため、機械的シャッタと遮光膜との間に電界が生じることを回避して、機械的シャッタの動作マージンを損なうことなく高コントラストを実現し得る理想的な遮光膜を実現できる。

【0039】

本実施形態では極性反転駆動に伴う制御電極25、27の駆動が、前述のように交流化され、互いに打ち消しあっているため、特にEMI(Electro−Magnetic Interference)が少ないという特徴を有する。この特徴によって、ガラス基板36に設けられているタッチパネル30のセンス電極40に対する飛込みノイズを抑制することができ、特に感度の良いタッチパネル特性を実現することができる。本実施形態においても容量線11とシャッタ電圧書込み用ソース電圧線12は交流化できていないが、これらの波形が制御するシャッタ電圧書込み用トランジスタ3を介したシャッタ電極26への書込み駆動は元々時定数が大きい。従って書込み駆動回路16による容量線11とシャッタ電圧書込み用ソース電圧線12の駆動時定数を十分に大きく設定することで、容量線11とシャッタ電圧書込み用ソース電圧線12に起因するEMIの抑制は可能である。

【0040】

また、本実施形態においては制御電極線8A、8Bの印加電圧の入れ替わりによって極性反転駆動を実現しているが、一般に制御電極線8A、8Bに接続される制御電極25、27は、シャッタ電極26と比較して寄生容量が小さくなる。本実施形態においては極性反転駆動を行う際にシャッタ電極26を制御する必要がないため、この観点からも本実施形態には極性反転駆動時の消費電力やEMIを抑制できるという長所があることが判る。

【0041】

また、本実施形態においては、走査スイッチ5及びシャッタ電圧書込み用トランジスタ3のオンする期間は、それぞれ当該画素が走査線10によって選択された期間及びシャッタ電極26への信号電圧書込み期間である[タイミングt2からt4まで]の期間に限定される。これによって、これらのアモルファスシリコン薄膜トランジスタのオン期間が長時間継続することに起因するしきい値電圧のシフトを、十分に回避することが可能であるという特長を有する。

【0042】

なお、本実施形態に開示した技術は、本発明の趣旨を損なわない範囲で、様々な変更が可能である。本実施形態ではガラス基板36上に走査スイッチ5とシャッタ電圧書込み用トランジスタ3をn型のアモルファスシリコン薄膜トランジスタで設けているが、ガラス基板36に変えて耐熱プラスチック基板等を用いることで基板に曲げに対するフレキシビリティを持たせることが可能である。またn型のアモルファスシリコン薄膜トランジスタに変えて、より低電圧で動作が可能なn型やp型の多結晶シリコン薄膜トランジスタを用いることで、画像信号電圧書込み回路14から信号線6A及び6Bに出力する画像信号電圧の振幅を5V以下に下げて低消費電力化を図ることができる。なおp型薄膜トランジスタを用いた際には、これらに印加する電圧関係の正負を逆にする必要があることは言うまでも無い。或いはまたn型のアモルファスシリコン薄膜トランジスタに変えて、InGaZnOに代表されるアモルファス酸化物薄膜トランジスタを用いることでも、同様に画像信号電圧の振幅を5V以下に下げて低消費電力化を図ることができ、かつ多結晶シリコン薄膜トランジスタと比較してプロセス装置コストを低減することができる。なお、n型薄膜トランジスタをp型薄膜トランジスタに変更した場合には、接続されるソースとドレインが入れ替わるのは勿論である。

【0043】

また、本実施形態では黒色樹脂膜24として、ポリイミド樹脂等にカーボンブラック、チタンブラック等の顔料粒子を適切に分散させたものを用いたが、黒色樹脂膜としてはこれに限るものではない。シャッタ電極26への電界の影響を回避するために誘電体であれば良く、更に反射膜23を透過する光の波長特性によっては黒色である必要もない。例えば反射膜23を透過する光に含まれている青色が実質的に無視できる量であれば、黒色樹脂膜24に替えて青色樹脂層で良いし、反射膜23を透過する光が実質的に赤以外は無視できる量であれば、黒色樹脂膜24に替えてシアン色樹脂層でも良い。また反射膜23への入射光の角度が適切な範囲を超えないように導光板22全体を光学設計できた場合、或いは必要な入射角度全域で反射膜の全反射特性を十分に確保できた場合には、黒色樹脂膜24そのものが不要になる。

【0044】

また、本実施形態ではシャッタ電極26側の反射膜23は多層誘電膜を用いて構成したが、反射膜23に必要な特性は、シャッタ電極26への電界の影響を回避するために誘電体であって、かつ光源42から発生し、導光板22側から照射されたR(赤)G(緑)B(青)の3色の光からなる光を高効率で反射することであるため、このような特性を満足すれば必ずしも多層誘電膜に限るものではない。また反射膜23における反射は鏡面反射に限られるものではなく、反射膜23は拡散反射特性を有する膜でも良いことから、白色樹脂材料等を用いて作成することも可能である。

【0045】

なお、本実施形態ではシャッタ電極26の極性反転駆動を列毎に行ったが、制御電極線8A、8Bを適切に各画素内に配置すれば、極性反転駆動は必ずしも列毎に行わなくとも、例えば行毎、或いは格子ドット毎等で行うことも可能である。またシャッタ電極26、制御電極25、27の電極表面の絶縁膜が十分な電気的安定性を有していれば、極性反転駆動自体を行わなくとも良い。

【0046】

[第2実施形態]

以下、図8、9を用いて、本発明の第2実施形態について順次説明する。第2実施形態に係る画像表示装置のシステム構成と動作、表示パネルの構成と動作、画素の構成及び動作等は既に説明した第1実施形態のそれらと同様であるため、ここではその説明は省略し、特に両者で異なる内容に関して述べることにする。

【0047】

図8は第2実施形態に係る画像表示装置における、表示領域内の画素配列構成図である。表示領域内には画素13R、13G、13Bがマトリクス状に設けられており、列方向に配列された画素13R、13G、13Bはそれぞれ、R(赤)G(緑)B(青)の各色に発光する。

【0048】

次に第2実施形態の画素部断面構造について説明する。図9は第2実施形態の画素13Rに関する画素断面構造図である。本画素断面構造図の構成及び動作は基本的には図4で説明した第1実施形態と同様であるが、第2実施形態の画素13Rでは、反射膜50はR(赤)を全反射する多層誘電膜50R、G(緑)を全反射する多層誘電膜50G、B(青)を全反射する多層誘電膜50Bの積層で構成されている。またR(赤)G(緑)B(青)の3色の独立LED光源からなる光源42に替えて、W(白)色のLED光源を有する光源52が設けられている。

【0049】

更に反射膜50の開口部にはR(赤)を全反射する多層誘電膜50Rは設けられておらず、G(緑)を全反射する多層誘電膜50G、及びB(青)を全反射する多層誘電膜50Bの積層構造からなるR(赤)色カラーフィルタ51が設けられている。これによって本第2実施形態の画素13RではR(赤)の発光を行うが、G(緑)とB(青)の光はR(赤)色カラーフィルタ51によって再度導光板22方向に反射、リサイクルされるという特徴を有している。

【0050】

また、同様に画素13Gでは、反射膜50の開口部にはG(緑)を全反射する多層誘電膜50Gは設けられておらず、B(青)を全反射する多層誘電膜50B、及びR(赤)を全反射する多層誘電膜50Rの積層構造からなるG(緑)色カラーフィルタが設けられている。これによって画素13GではG(緑)の発光を行うが、B(青)とR(赤)の光はG(緑)色カラーフィルタによって再度導光板22方向に反射、リサイクルされる。

【0051】

同様に画素13Bでは、反射膜50の開口部にはB(青)を全反射する多層誘電膜50Bは設けられておらず、R(赤)を全反射する多層誘電膜50R、及びG(緑)を全反射する多層誘電膜50Gの積層構造からなるB(青)色カラーフィルタが設けられている。これによって画素13BではB(青)の発光を行うが、R(赤)とG(緑)の光はB(青)色カラーフィルタによって再度導光板22方向に反射、リサイクルされる。

【0052】

本第2実施形態では、上記のようにW(白)色のLED光源を有する光源52が設けられ、また各画素が画素13R、13G、13Bの3色に分かれているため、カラー表示にFSC方式ではなく、白色発光+カラーフィルタ方式を用いることができる。第2実施形態ではこれによって、FSC方式で問題となる色分解(Color break-up)を完全に回避することができる。なおこのとき各画素に設けられたダイクロイックカラーフィルタは選択透過波長以外の波長の光を導光板22方向に反射、リサイクルするため、一般のカラーフィルタを用いた場合のような光吸収による光の損失が無く、低消費電力化を図ることができる。またR(赤)G(緑)B(青)の3色の独立LED光源からなる光源42に変えて、一般のTV等にも通常用いられているW(白)色のLED光源を有する光源52を使用するため、LED光源部品の低コスト化を図ることができる。W(白)色のLED光源は青色LEDと黄色蛍光体で構成できるために材料費が安く、更に大量生産による量産効果も期待できるからである。

【0053】

また、本実施形態においても、第1実施形態と同様に、画素内の配線を減少させることができ、量産上の歩留りを上げると共に、低コスト化を図ることができる。また、遮光膜を誘電体で形成しているため、機械的シャッタと遮光膜との間に電界が生じることを回避して、機械的シャッタの動作マージンを損なうことなく高コントラストを実現できる。

【0054】

[第3実施形態]

以下、図10を用いて、本発明の第3実施形態について順次説明する。本第3実施形態に係る画像表示装置のシステム構成と動作、表示パネルの構成と動作、画素の構成及び動作等は既に説明した第1実施形態のそれらと同様であるため、ここではその説明は省略し、特に両者で異なる内容に関して述べることにする。

【0055】

図10は、第3実施形態の画素13に関する画素断面構造図である。本画素断面構造図の構成及び動作は基本的には図4で説明した第1実施形態と同様であるが、第3実施形態の画素13では、反射膜23と黒色樹脂膜24は透明保護膜60で覆われている点が異なっている。この透明保護膜60としては、有機ないし無機の保護膜を用いることができる。

【0056】

本第3実施形態ではこの透明保護膜60を用いることによって、可動するシャッタ電極26が透明保護膜60に接触しても異物が生成することを防止することができ、結果的にシャッタ電極26と反射膜23及び黒色樹脂膜24との距離を短く設計することができる。シャッタ電極26が閉状態の際には、反射膜23及び黒色樹脂膜24の開口はシャッタ電極26で十分に遮光しないと光漏れによってコントラストが低下するため、このようにシャッタ電極26と反射膜23及び黒色樹脂膜24との距離を短く設計することで、第3実施形態では実質的にコントラストの向上を図ることができる。

【0057】

本実施形態においても、第1実施形態と同様に、画素内の配線を減少させることができ、量産上の歩留りを上げると共に、低コスト化を図ることができる。また、遮光膜を誘電体で形成しているため、機械的シャッタと遮光膜との間に電界が生じることを回避して、機械的シャッタの動作マージンを損なうことなく高コントラストを実現できる。

【0058】

[第4実施形態]

以下、図11を用いて、本発明の第4実施形態について順次説明する。第4実施形態に係る画像表示装置のシステム構成と動作、表示パネルの構成と動作、画素の構成及び動作等は既に説明した第1実施形態のそれらと同様であるため、ここではその説明は省略し、特に両者で異なる内容に関して述べることにする。

【0059】

図11は、第4実施形態である、機械的シャッタを用いた画像表示装置のシャッタ制御回路を示す図である。第1実施形態における画素13と、第4実施形態における画素73との差異は、シャッタ電圧書込み用トランジスタ3のドレインが双極性シャッタ1のシャッタ電極26に接続されているのに加えて、新たに双極性シャッタ1の制御電極25、27との間にそれぞれ補助容量70、71が設けられていることである。

【0060】

第1実施形態で述べたようにシャッタ電極26は、シャッタ電極26と制御電極25、27が生じる電界の効果によってその位置が制御されるが、シャッタ電極26の位置が制御電極25、27のいずれかの側で安定するまでは、シャッタ電極26に必要な電荷を供給し続けることが望ましい。シャッタ電極26と制御電極25、27の間には必ず寄生容量が形成されるが、この寄生容量の値はシャッタ電極26が移動し、シャッタ電極26と制御電極25或いは制御電極27との間隔が狭まることによって増加する。ここでシャッタ電極26と制御電極25或いは制御電極27との間のある距離での寄生容量をC、その後のシャッタ電極26の位置変動に起因する寄生容量の増分をΔC、電圧をV、この距離でこの寄生容量に蓄えられる電荷をQ、その後のシャッタ電極26の位置変動に起因する電荷の増分をΔQとすると、下記の式(1)が成立する。

(Q+ΔQ)=(C+ΔC)×V ・・・・・・・・ (1)

【0061】

従って、シャッタ電極26と制御電極25或いは制御電極27との間の電圧Vを一定に保つためには、寄生容量Cの値の増加分ΔCに相当する電荷ΔQの供給が必要になる。

【0062】

このことはシャッタ電極26の位置が安定点に落ち着くまでは、シャッタ電圧書込み用トランジスタ3はオンし続ける必要のあることを意味する。しかしながらこの場合には図5に記載した[タイミングt2からt3まで]及び[タイミングt3からt4まで]の期間を十分に長く確保することになり、[タイミングt1まで]及び[タイミングt4以降]である画素に対する画像信号電圧の書込み期間が短くなることになってしまう。特に列方向に画素数の大きいディスプレイを設計する必要のある場合には、この制約は非常に厳しいものとなる。

【0063】

これに対して第4実施形態は、新たに双極性シャッタ1のシャッタ電極26と制御電極25、27との間にそれぞれ補助容量70、71を設けることで、補助容量70、71から上記寄生容量に電荷を供給できるようにして、シャッタ電極26における上記寄生容量の影響を緩和したものである。

【0064】

これによって第4実施形態は、シャッタ電極26の位置が安定点に完全に落ち着く前にシャッタ電圧書込み用トランジスタ3をオフしても、上記寄生容量の増加に起因するシャッタ電極26と制御電極25、27との間の電圧変動を十分に抑制することが可能である。これによって図5に記載した[タイミングt2からt3まで]及び[タイミングt3からt4まで]の期間を十分に長く確保しなくとも良く、[タイミングt1まで]及び[タイミングt4以降]である画素に対する画像信号電圧の書込み期間を十分に確保することができる。これにより特に列方向に画素数の大きいディスプレイを設計する場合には走査回路15の駆動クロックを低減することができ、回路設計マージンの確保による歩留りの向上や、消費電力の削減を図る上で大きな利点となる。

【0065】

なお、第4実施形態では補助容量70、71の値はそれぞれ200fFに設計したが、前述した効果からは例えば10fF以上が望ましい。またここでは補助容量70、71は等しい値に設けているが、これは図5の[タイミングt1からt2まで]の期間に、シャッタ電極26の極性反転駆動を目的として毎フレーム毎に奇数画素列と偶数画素列に相当する制御電極線8A、8Bの印加電圧の入れ替わりが行われる際の制御電極線8A、8Bの電圧変動が、補助容量70、71のカップリングを通じてシャッタ電極26へ影響することを互いにキャンセルするためである。しかしながらこのカップリング効果が問題とならないような場合には、補助容量70、71の値を非対称にしても、或いはいずれか一方のみを設けても、第4実施形態に準じた効果が得られることは明らかである。

【0066】

本実施形態においても、第1実施形態と同様に、画素内の配線を減少させることができ、量産上の歩留りを上げると共に、低コスト化を図ることができる。また、遮光膜を誘電体で形成しているため、機械的シャッタと遮光膜との間に電界が生じることを回避して、機械的シャッタの動作マージンを損なうことなく高コントラストを実現できる。

【0067】

[第5実施形態]

以下、図12〜図15を用いて、本発明の第5実施形態について、その構成および動作を順次説明する。

【0068】

図12は、第5実施形態に係る画像表示装置の画素周辺回路図である。マトリクス状に配列された画素85が表示領域を構成しており、画素85には列方向に信号線6A及び6Bと、制御電極線8A及び8Bが、行方向に走査線10、容量線11、シャッタ電圧書込み用ソース電圧線12、及びCMOSシャッタ電圧書込み用pMOSソース電圧線84が設けられている。表示領域の周辺で、信号線6A及び6Bの一端は画像信号電圧書込み回路14に接続されており、制御電極線8A及び8Bの一端はそれぞれ制御電極駆動回路17に接続されている。また走査線10の一端は走査回路15に接続されており、容量線11、シャッタ電圧書込み用ソース電圧線12及びCMOSシャッタ電圧書込み用pMOSソース電圧線84の一端は、それぞれ書込み駆動回路86に接続されている。

【0069】

ここでCMOSシャッタ電圧書込み用pMOSソース電圧線84には、書込み駆動回路86から常時Vh(後述のように例えば15(V))が入力される。なお、図12は簡単のために表示領域を画素数が4×3画素のマトリクスで記載しているが、本発明の開示する技術思想が特に画素数を制限するものではない。

【0070】

図13には、図12の各画素85におけるシャッタ制御回路87が示されている。各画素85には信号線6Aが設けられており、信号線6Aと信号蓄積容量4とは走査スイッチ5で接続されている。信号蓄積容量4は更にCMOS書込み用トランジスタ80のゲートに接続されており、CMOS書込み用トランジスタ80のドレインはCMOS信号蓄積容量81の一端に接続されている。また更にCMOS書込み用トランジスタ80のドレインは、CMOSシャッタ電圧書込み用nMOSトランジスタ83及びCMOSシャッタ電圧書込み用pMOSトランジスタ82のゲートにも接続される。更にCMOSシャッタ電圧書込み用nMOSトランジスタ83及びCMOSシャッタ電圧書込み用pMOSトランジスタ82のドレインは双極性シャッタ1のシャッタ電極26に接続されている。即ちこれによって、CMOSシャッタ電圧書込み用nMOSトランジスタ83及びCMOSシャッタ電圧書込み用pMOSトランジスタ82は画素内にCMOSインバータ回路を構成している。二つある双極性シャッタ1の制御電極の内の一方は画素内の制御電極線8Aに接続されているが、制御電極の他方は隣接する画素の制御電極線8Bに接続されている。なお信号蓄積容量4の他端は容量線11に接続されており、CMOS信号蓄積容量81の他端は制御電極線8Bに、CMOS書込み用トランジスタ80のソースはシャッタ電圧書込み用ソース電圧線12に、CMOSシャッタ電圧書込み用nMOSトランジスタ83及びCMOSシャッタ電圧書込み用pMOSトランジスタ82のソースはそれぞれ容量線11及びCMOSシャッタ電圧書込み用pMOSソース電圧線84に、走査スイッチ5のゲートは走査線10に接続されている。なお上記の双極性シャッタ1が遮光面上に設けられた開口に対向して設けられていること等の立体的な画素構造は、基本的に第1実施形態と同様である。なお図13には信号線6Aと制御電極線8Aを有する画素と、信号線6Bと制御電極線8Bを有する画素の、2画素分が記載されている。両画素は後述のように駆動条件は異なるものの、基本的なシャッタ制御回路は同一である。

【0071】

図14は、第5実施形態の画素部断面構造図である。ガラス基板36上には、低不純物濃度低温多結晶シリコン薄膜91、高濃度n型不純物をドープした低温多結晶シリコン薄膜92、90、ゲート絶縁膜93、ゲート電極95、層間絶縁膜94、ソース電極96、ドレイン電極97とから構成される低温多結晶シリコン薄膜トランジスタが設けられており、これはCMOSシャッタ電圧書込み用nMOSトランジスタ83に対応している。更にガラス基板36上には、ソース電極96、ドレイン電極97と同じAl配線層で制御電極線8A、8Bが形成されており、これらはシリコンナイトライドと有機材料の多層膜からなる保護膜37によって覆われている。

【0072】

保護膜37上には、シャッタ電極26と、二つの制御電極25、27を有する双極性シャッタ1が設けられており、ドレイン電極97はシャッタ電極26に、制御電極線8Aは制御電極25に、制御電極線8Bは制御電極27に、それぞれコンタクトホールを介して接続されている。またこれらシャッタ電極26と、二つの制御電極25、27には互いに接触した際の短絡防止のために、表面には絶縁膜が形成されている。なおここでシャッタ電極26は、シャッタ電極26に入力される電圧と、二つの制御電極25、27に入力される電圧との相対関係による電界でその位置が制御されるため、図14には破線を用いてその可動範囲も開示している。なお図14には記載されていないが、画素85内に設けられたその他のトランジスタも、同様に低温多結晶シリコン薄膜トランジスタで構成されている。

【0073】

シャッタ電極26に対してガラス基板36と反対側には、R(赤)G(緑)B(青)の3色の独立LED光源からなる光源42を有する導光板22が設けられている。導光板22の両面には反射膜21、23が設けられているが、ここで特にシャッタ電極26側の反射膜23は多層誘電膜より構成されている。反射膜23を構成する多層誘電膜はTiO2、Ta2O3等の高屈折率材料とSiO2、MgF2等の低屈折材料の積層構造からなっており、これらの積層構造の各膜厚を適切な値に設計することによって、光源42が有するR(赤)G(緑)B(青)の3色の独立LED光源の射出光に対して実用上十分な全反射特性を得ることができる。ところで多層誘電膜を全反射膜として用いた場合の課題は、垂直方向に入射する光に対して最適設計した場合に、水平に近い角度で入射した光に対しては反射特性が悪化することである。反射膜23が光を透過した場合には表示装置の光漏れとなってしまい、コントラストの著しい低下を招いてしまう。そこでこのような光漏れを防止するために、更に反射膜23の上には有機材料で作成された黒色樹脂膜24を形成した。この黒色樹脂膜は、ポリイミド樹脂等にカーボンブラック、チタンブラック等の顔料粒子を適切に分散させることで形成することができる。ここで反射膜23及び黒色樹脂膜24には図14に示すように、シャッタ電極26に対応する位置に開口が設けられており、光源42から射出されて導光板22を伝播した光41の一部が、この開口から射出されるように構成されている。開口は例えば、黒色樹脂膜24をマスクとしたフォトリソグラフィーによって一括加工形成することができる。

【0074】

ガラス基板36に対して導光板22と反対側には、フィルムシート38、センス電極40、保護膜39からなるタッチパネル30が設けられている。タッチパネル30のセンス電極40は表示領域の周辺でタッチ検出用回路に接続されているが、この部分の構成は既に一般に知られている技術であるため、ここではその詳細な説明は省略する。

【0075】

次に、図15を用いて、本発明の第5実施形態の動作を説明する。まず、図13で述べた第5実施形態のシャッタ制御回路87の動作について説明する。

【0076】

図15は、第5実施形態のシャッタ制御回路87の動作タイミングチャートであり、横軸に時間を取って、縦軸に各部分の電圧を示したものである。また特に下2段に記載したCMOS信号蓄積容量81の蓄積信号電圧(=CMOSインバータ回路入力電圧)及び双極性シャッタ1のシャッタ電極26の電圧値に関しては、画像信号によって約0(V)と約Vhの二値を取るため、図面を判り易くするために基本的に約0(V)を実線、約Vhを破線で示している。

【0077】

[タイミングt1まで]

この期間には、画素に対する画像信号電圧の書込みが行われている。この期間は制御電極線8A、8Bにはそれぞれ高電圧Vh、低電圧0(V)が印加されているが、後述するようにシャッタ電極26の極性反転駆動を目的として、奇数画素列と偶数画素列に相当する制御電極線8A、8Bの印加電圧は毎フレーム毎にその値が入れ替わる。各画素の走査スイッチ5は走査線10によって順次走査されており、走査スイッチ5が走査された画素の信号蓄積容量4には、信号線6A、6Bから所定の画像信号電圧が書込まれる。ここで信号線6A、6Bに印加される画像信号電圧は例えば4(V)と0(V)の二値をとるが、白表示時と黒表示時にそれぞれ4(V)と0(V)のいずれに該当するかは、シャッタ電極26の極性反転駆動を目的とした制御電極線8A、8Bの印加電圧の毎フレーム毎の値によって、信号線6A及び6Bの列毎に入れ替わる。なお容量線11には0(V)、シャッタ電圧書込み用ソース電圧線12にはVmが印加されており、双極性シャッタ1のシャッタ電極26には約0(V)ないし約Vhが印加されている。なおここでVhの値は双極性シャッタ1の静電的な機械駆動が可能な最小の電圧に設計されるが、例えばこの値は15(V)である。またVmの値は信号電圧が信号蓄積容量4に書込まれてもCMOS書込み用トランジスタ80がオンすることのない値であり、例えば4(V)である。なお第1実施形態と比較して、第5実施形態の画像信号電圧は4(V)と低い値をとるが、これはCMOS書込み用トランジスタ80が書込む容量がCMOS信号蓄積容量81の約20fFとCMOSシャッタ電圧書込み用nMOSトランジスタ83及びCMOSシャッタ電圧書込み用pMOSトランジスタ82のゲート容量の和であって、比較的小さい値であることと、走査スイッチ5とCMOS書込み用トランジスタ80が電流駆動力の大きい低温多結晶シリコン薄膜トランジスタで構成されていることに起因する。

【0078】

[タイミングt1からt2まで]

この期間にはシャッタ電極26の極性反転駆動を目的として、毎フレーム毎に奇数画素列と偶数画素列に相当する制御電極線8A、8Bの印加電圧の入れ替わりが行われる。本実施形態は後述するように光源42の発光にサブフィールド毎に時間重みを持たせて、シャッタ電極26の開閉で外部への発光を制御するPWM駆動を行うが、制御電極線8A、8Bの印加電圧の入れ替えはフレーム毎に替えて、サブフィールド毎や、複数サブフィールド毎に行っても良い。制御電極線8A、8Bの印加電圧の入れ替えを行わないサブフィールドでは、この[タイミングt1からt2まで]の期間は設ける必要はない。制御電極線8A、8Bの印加電圧の入れ替えを頻繁に行うと、これに伴うタイミングt1からt2までの遷移期間を頻繁に設ける必要があることと、消費電力が増加することには留意する必要がある。

【0079】

[タイミングt2からt13まで]

この期間には信号蓄積容量4に書込まれた画像信号電圧に基づいて、全画素において一斉にCMOS信号蓄積容量81への信号電圧書込みが行われる。

【0080】

容量線11とシャッタ電圧書込み用ソース電圧線12に同時にVhが書込まれ、この後に両者の電圧は揃って0(V)に立ち下げられる。この動作によってCMOS書込み用トランジスタ80が制御され、信号蓄積容量4に書込まれていた画像信号電圧が0(V)の場合にはCMOS信号蓄積容量81には信号電圧として(Vh−Vth)が書込まれ、画像信号電圧が4(V)だった場合にはCMOS信号蓄積容量81には信号電圧として0(V)が書込まれる。なおここでVthは、CMOS書込み用トランジスタ80のしきい値電圧である。

【0081】

上記のCMOS信号蓄積容量81への信号電圧書込みについては、既に第1実施形態で図6A〜図7Cを用いて詳細に説明した擬似ダイオード回路の動作であるので、ここではその説明は省略する。

【0082】

[タイミングt13からt14まで]

この期間には容量線11とシャッタ電圧書込み用ソース電圧線12は0(V)に立ち下げられた電圧値を維持し、CMOS信号蓄積容量81へ書込まれた信号電圧は、そのままCMOSシャッタ電圧書込み用nMOSトランジスタ83及びCMOSシャッタ電圧書込み用pMOSトランジスタ82のゲートに入力される。前述のようにCMOSシャッタ電圧書込み用pMOSソース電圧線84には、書込み駆動回路86から常時Vh(例えば15(V))が入力されるため、このときCMOSシャッタ電圧書込み用nMOSトランジスタ83及びCMOSシャッタ電圧書込み用pMOSトランジスタ82はCMOSインバータ回路として機能する。従ってCMOS信号蓄積容量81には信号電圧として(Vh−Vth)が書込まれている場合には、CMOSインバータ回路はシャッタ電極26に0(V)を出力し、CMOS信号蓄積容量81に信号電圧として0(V)が書込まれている場合には、CMOSインバータ回路はシャッタ電極26にVh(例えば15(V))を出力する。

【0083】

[タイミングt14以降]

この期間は再びタイミングt1までの動作と同様に、画素に対する画像信号電圧の書込みが行われる。各画素の走査スイッチ5は走査線10によって順次走査され、走査スイッチ5が走査された画素の信号蓄積容量4には、信号線6A、6Bから所定の画像信号電圧が書込まれる。シャッタ電圧書込み用ソース電圧線12にはVm(例えば4(V))が印加されており、信号電圧が信号蓄積容量4に書込まれても基本的にはCMOS書込み用トランジスタ80がオンすることはない。ここで本実施形態においては、[タイミングt13からt14まで]と同様にCMOSシャッタ電圧書込み用nMOSトランジスタ83及びCMOSシャッタ電圧書込み用pMOSトランジスタ82がCMOSインバータ回路として機能し続けるため、シャッタ電極26への信号電圧の書込みと、画素に対する画像信号電圧の書込み走査を並行して行えるという利点がある。

【0084】

なおここでも第1実施形態と同様に、CMOS信号蓄積容量81に0(V)が書込まれており、信号蓄積容量4に4(V)(VsigH)が書込まれている場合には、CMOS信号蓄積容量81の電圧はCMOS書込み用トランジスタ80のオフする電圧である4(V)−Vth(VsigH−Vth)まで、この期間に再度上昇する。基本的にCMOSシャッタ電圧書込み用nMOSトランジスタ83及びCMOSシャッタ電圧書込み用pMOSトランジスタ82で構成されるCMOSインバータ回路は二値駆動であるため、0(V)が4(V)−Vth(VsigH−Vth)に上昇しても動作そのものには支障はないが、これによってCMOSインバータを流れる貫通電流が増えて消費電力が増加する点には留意する必要がある。ここでVsigHは高い電圧である方がCMOS書込み用トランジスタ80によるCMOS信号蓄積容量81への書込み動作はより高速化できるという長所がある。しかしその一方で、画像信号電圧書込み回路14から信号線6A及び6BにVsigHを書込む際の消費電力が上昇する点や、上記のような副作用も有しているため、本実施形態では4(V)としたVsigHの電圧値は、これらを勘案した上で最適に設定する必要がある。

【0085】

次に図13で述べた本第5実施形態の画素周辺回路の動作について説明する。

【0086】

前述の[タイミングt1まで]に相当する画素に対する画像信号電圧の書込み期間においては、走査線10は走査回路15によって順次走査され、これと同期して信号線6A及び6Bには画像信号電圧書込み回路14から画像信号電圧が書込まれる。ここで前述のように本実施形態は光源42の発光にサブフィールド毎に時間重みを持たせて、シャッタ電極26の開閉で外部への発光を制御するPWM駆動を行う。このため画像信号電圧書込み回路14から信号線6A及び6Bに書込まれる画像信号電圧は、例えば0(V)と4(V)の二値の電圧であり、これによって各画素に設けられたシャッタ電極26に印加される信号電圧を制御する。なお白表示時と黒表示時にそれぞれ4(V)と0(V)のいずれに該当するかは、シャッタ電極26の極性反転駆動を目的とした制御電極線8A、8Bの印加電圧の毎フレーム毎の値によって、信号線6A及び6Bの列毎に入れ替わることは既に述べたとおりである。次に全画素に対する画像信号電圧の書込みが終了した後、前述の[タイミングt1からt2まで]の期間において、シャッタ電極26の極性反転駆動を目的として、フレーム毎に奇数画素列と偶数画素列に相当する制御電極線8A、8Bの印加電圧が制御電極駆動回路17によって相補的に駆動されることは既に述べたとおりである。また引続き行われる[タイミングt2からt3まで]における、信号蓄積容量4に書込まれた画像信号電圧に基づいた、全画素におけるCMOS信号蓄積容量81への信号電圧書込みは、書込み駆動回路86が容量線11、シャッタ電圧書込み用ソース電圧線12を一斉に駆動することによって行われる。その後の[タイミングt4以降]において、シャッタ電圧書込み用ソース電圧線12へのVm印加を行うのも書込み駆動回路86である。なおCMOSシャッタ電圧書込み用pMOSソース電圧線84に常時Vh(例えば15(V))を入力するのも書込み駆動回路86である。

【0087】

最後に図14で述べた第5実施形態のシャッタ電極26近傍構造の動作については、トランジスタの構造とVhの電圧値に関しては異なるものの、基本的な動作に関しては既に第1実施形態で述べたものと同じであるため、ここではこれ以上の説明は省略する。

【0088】

既に述べたように第5実施形態においては、[タイミングt13からt14まで]と同様に[タイミングt14以降]においても、CMOSシャッタ電圧書込み用nMOSトランジスタ83及びCMOSシャッタ電圧書込み用pMOSトランジスタ82がCMOSインバータ回路として機能し続けるため、シャッタ電極26への信号電圧の書込みと、画素に対する画像信号電圧の書込み走査を並行して行えるという利点がある。これによって本実施形態は、特に列方向に画素数の大きいディスプレイを設計する場合には走査回路15の駆動クロックを低減することができ、回路設計マージンの確保による歩留りの向上や、消費電力の削減を図る上で大きな利点となる。

【0089】

本実施形態においても、第1実施形態と同様に、画素内の配線を減少させることができ、量産上の歩留りを上げると共に、低コスト化を図ることができる。また、遮光膜を誘電体で形成しているため、機械的シャッタと遮光膜との間に電界が生じることを回避して、機械的シャッタの動作マージンを損なうことなく高コントラストを実現できる。

【0090】

[第6実施形態]

以下図16〜図18を用いて、本発明の第6実施形態について、その構成および動作を順次説明する。第6実施形態に係る画像表示装置のシステム構成と動作、表示パネルの構成と動作、画素の構成及び動作等は既に説明した第1実施形態のそれらと同様であるため、ここではその説明は省略し、特に両者で異なる内容に関して述べることにする。

【0091】

図16は第6実施形態の画素周辺回路図である。マトリクス状に配列された画素105が表示領域を構成しており、画素105には列方向に信号線6A及び6Bと、制御電極線8A及び8Bが、行方向に走査線10、容量線11、シャッタ電圧書込み用ソース電圧線12、次段シャッタ電圧書込み用ソース電圧線104が設けられている。表示領域の周辺で、信号線6A及び6Bの一端は画像信号電圧書込み回路14に接続されており、制御電極線8A及び8Bの一端はそれぞれ制御電極駆動回路17に接続されている。また走査線10の一端は走査回路15に接続されており、容量線11、シャッタ電圧書込み用ソース電圧線12、次段シャッタ電圧書込み用ソース電圧線104の一端は、それぞれ書込み駆動回路106に接続されている。なお図16は簡単のために表示領域を画素数が4×3画素のマトリクスで記載しているが、本発明の開示する技術思想が特に画素数を制限するものではない。

【0092】

図17は、第6実施形態のシャッタ制御回路107を示す図である。各画素105には信号線6Aが設けられており、信号線6Aと信号蓄積容量4とは走査スイッチ5で接続されている。信号蓄積容量4は更に次段書込み用トランジスタ100のゲートに接続されており、次段書込み用トランジスタ100のドレインは次段信号蓄積容量101の一端に接続されている。また更に次段書込み用トランジスタ100のドレインは、次段シャッタ電圧書込み用トランジスタ102のゲートにも接続される。更に次段シャッタ電圧書込み用トランジスタ102のドレインは双極性シャッタ1のシャッタ電極26に接続されている。即ちこれによって、信号蓄積容量4と次段書込み用トランジスタ100同様に、次段信号蓄積容量101と次段シャッタ電圧書込み用トランジスタ102は、画素内に2個目の擬似ダイオード回路を構成している。二つある双極性シャッタ1の制御電極の内の一方は画素内の制御電極線8Aに接続されているが、制御電極の他方は隣接する画素の制御電極線8Bに接続されている。なお信号蓄積容量4の他端は容量線11に接続されており、次段書込み用トランジスタ100のソースはシャッタ電圧書込み用ソース電圧線12に、次段信号蓄積容量101の他端と次段シャッタ電圧書込み用トランジスタ102のソースは次段シャッタ電圧書込み用ソース電圧線104に、走査スイッチ5のゲートは走査線10に接続されている。なお上記の双極性シャッタ1が遮光面上に設けられた開口に対向して設けられていること等の立体的な画素構造は、基本的に第1実施形態と同様である。なお図17には信号線6Aと制御電極線8Aを有する画素と、信号線6Bと制御電極線8Bを有する画素の、2画素分が記載されている。両画素は後述のように駆動条件は異なるものの、基本的なシャッタ制御回路は同一である。

【0093】

次に第6実施形態の画素部断面構造は、既に述べた第1実施形態の画素部断面構造と同様であるので、ここではその説明は省略する。

【0094】

次に図18を用いて、第6実施形態のシャッタ制御回路107の動作について説明する。図18は第6実施形態のシャッタ制御回路107の動作タイミングチャートであり、横軸に時間を取って、縦軸に各部分の電圧を示したものである。また特に次段シャッタ電圧書込み用トランジスタ102のゲート入力電圧と、最下段に記載した双極性シャッタ1のシャッタ電極26の電圧値に関しては、画像信号によって約Vm2と約Vhの二値を取るため、図面を判り易くするために前者を実線、後者を破線で示している。

【0095】

[タイミングt1まで]

この期間には、画素に対する画像信号電圧の書込みが行われている。この期間は制御電極線8A、8Bにはそれぞれ高電圧Vh、低電圧Vm2(例えば7(V))が印加されているが、後述するようにシャッタ電極26の極性反転駆動を目的として、奇数画素列と偶数画素列に相当する制御電極線8A、8Bの印加電圧は毎フレーム毎にその値が入れ替わる。各画素の走査スイッチ5は走査線10によって順次走査されており、走査スイッチ5が走査された画素の信号蓄積容量4には、信号線6A、6Bから所定の画像信号電圧が書込まれる。ここで信号線6A、6Bに印加される画像信号電圧は例えば7(V)と0(V)の二値をとるが、白表示時と黒表示時にそれぞれ7(V)と0(V)のいずれに該当するかは、シャッタ電極26の極性反転駆動を目的とした制御電極線8A、8Bの印加電圧の毎フレーム毎の値によって、信号線6A及び6Bの列毎に入れ替わる。なお容量線11には0(V)、シャッタ電圧書込み用ソース電圧線12にはVmが印加されており、次段シャッタ電圧書込み用ソース電圧線104にはVm2、次段シャッタ電圧書込み用トランジスタ102のゲートには約0(V)ないし約Vh、双極性シャッタ1のシャッタ電極26には約Vm2ないし約Vhが印加されている。なおここでVhの値は双極性シャッタ1の静電的な機械駆動が可能な最小の電圧に設計されるが、例えばこの値は20(V)である。

【0096】

なお、Vmの値は信号電圧が信号蓄積容量4に書込まれても次段書込み用トランジスタ100がオンすることのない値であり、例えば7(V)である。またVm2の値は、後述するように信号蓄積容量4にVsigH(7(V))が入力することによって、次段書込み用トランジスタ100を介して次段信号蓄積容量101の電圧値が0(V)から(VsigH−Vth)(Vthは次段書込み用トランジスタ100のしきい値電圧である)に上昇したとしても、次段シャッタ電圧書込み用トランジスタ102がオンしてシャッタ電極26に蓄えられたVhの電圧がリークしないように設定された電圧であり、基本的には以下の式(2)を満足する。

(VsigH−Vth)−Vth2 < Vm2 ・・・・・・・・ (2)

なおここでVth2は、次段シャッタ電圧書込み用トランジスタ102のしきい値電圧である。

【0097】

[タイミングt1からt2まで]

この期間にはシャッタ電極26の極性反転駆動を目的として、毎フレーム毎に奇数画素列と偶数画素列に相当する制御電極線8A、8Bの印加電圧の入れ替わりが行われる。本実施形態は後述するように光源42の発光にサブフィールド毎に時間重みを持たせて、シャッタ電極26の開閉で外部への発光を制御するPWM駆動を行うが、制御電極線8A、8Bの印加電圧の入れ替えはフレーム毎に替えて、サブフィールド毎や、複数サブフィールド毎に行っても良い。制御電極線8A、8Bの印加電圧の入れ替えを行わないサブフィールドでは、この[タイミングt1からt2まで]の期間は設ける必要はない。

制御電極線8A、8Bの印加電圧の入れ替えを頻繁に行うと、これに伴うタイミングt1からt2までの遷移期間を頻繁に設ける必要があることと、消費電力が増加することには留意する必要がある。

【0098】

[タイミングt2からt23まで]

この期間には信号蓄積容量4に書込まれた画像信号電圧に基づいて、全画素において一斉に次段信号蓄積容量101への信号電圧書込みが行われる。次段信号蓄積容量101へ書込まれる信号電圧は、次段シャッタ電圧書込み用トランジスタ102のゲート入力電圧と同じである。

【0099】

容量線11とシャッタ電圧書込み用ソース電圧線12に同時にVhが書込まれ、この後に両者の電圧は揃って0(V)に立ち下げられる。この動作によって次段書込み用トランジスタ100が制御され、信号蓄積容量4に書込まれていた画像信号電圧が0(V)の場合には次段信号蓄積容量101には信号電圧として(Vh−Vth)が書込まれ、画像信号電圧が7(V)だった場合には次段信号蓄積容量101には信号電圧として0(V)が書込まれる。ここでVthは、次段書込み用トランジスタ100のしきい値電圧である。

【0100】

上記の次段信号蓄積容量101への信号電圧書込みについては、既に第1実施形態で図6、図7を用いて詳細に説明した擬似ダイオード回路の動作であるので、ここではその説明は省略する。

【0101】

[タイミングt23からt24まで]

この期間には容量線11とシャッタ電圧書込み用ソース電圧線12は0(V)に立ち下げられた電圧値を維持しており、次段信号蓄積容量101に0(V)が書込まれる場合には、この期間にこの電圧は約0(V)に収束する。

【0102】

[タイミングt24からt25まで]

この期間には次段信号蓄積容量101に書込まれた画像信号電圧に基づいて、全画素において一斉にシャッタ電極26への信号電圧書込みが行われる。

【0103】

次段シャッタ電圧書込み用ソース電圧線104にVhが書込まれ、この後にこの電圧は再びVm2に立ち下げられる。この動作によって次段シャッタ電圧書込み用トランジスタ102が制御され、次段信号蓄積容量101に書込まれていた画像信号電圧が0(V)の場合にはシャッタ電極26には信号電圧として(Vh−Vth2)が書込まれ、画像信号電圧が7(V)だった場合にはシャッタ電極26には信号電圧としてVm2が書込まれる。ここでVth2は、次段シャッタ電圧書込み用トランジスタ102のしきい値電圧である。

【0104】

上記のシャッタ電極26への信号電圧書込みについては、既に述べた擬似ダイオード回路の動作であるので、ここではその説明は省略する。

【0105】

なおこれと並行してこの期間には、再びタイミングt1までの動作と同様に、画素に対する画像信号電圧の書込みが行われる。各画素の走査スイッチ5は走査線10によって順次走査され、走査スイッチ5が走査された画素の信号蓄積容量4には、信号線6A、6Bから所定の画像信号電圧が書込まれる。シャッタ電圧書込み用ソース電圧線12にはVmが印加されており、信号電圧が信号蓄積容量4に書込まれても基本的には次段書込み用トランジスタ100がオンすることはない。

【0106】

[タイミングt25以降]

この期間も継続して、引続き画素に対する画像信号電圧の書込みが行われる。また擬似ダイオード回路の動作によって、シャッタ電極26にVm2の信号電圧が書込まれる場合には、図18に示したようにこの期間の初期に行われる。

【0107】

なお次段信号蓄積容量101に0(V)が書込まれており、信号蓄積容量4に7(V)(VsigH)が書込まれている場合には、次段信号蓄積容量101の電圧が次段書込み用トランジスタ100のオフする電圧である7(V)−Vth(VsigH−Vth)まで、この期間に再度上昇する点は第1実施形態と同様である。このとき次段シャッタ電圧書込み用トランジスタ102がオンしてシャッタ電極26に蓄えられたVhの電圧がリークしないように、次段シャッタ電圧書込み用ソース電圧線104はVm2に設定されており、Vm2の値が式(2)を満足することは、前述したとおりである。

【0108】

次に図16で述べた第6実施形態の画素周辺回路の動作について説明する。

【0109】

前述の[タイミングt1まで]に相当する画素に対する画像信号電圧の書込み期間においては、走査線10は走査回路15によって順次走査され、これと同期して信号線6A及び6Bには画像信号電圧書込み回路14から画像信号電圧が書込まれる。ここで前述のように本実施形態は光源42の発光にサブフィールド毎に時間重みを持たせて、シャッタ電極26の開閉で外部への発光を制御するPWM駆動を行う。このため画像信号電圧書込み回路14から信号線6A及び6Bに書込まれる画像信号電圧は、例えば0(V)と7(V)の二値の電圧であり、これによって各画素に設けられたシャッタ電極26に印加される信号電圧を制御する。なお白表示時と黒表示時にそれぞれ7(V)と0(V)のいずれに該当するかは、シャッタ電極26の極性反転駆動を目的とした制御電極線8A、8Bの印加電圧の毎フレーム毎の値によって、信号線6A及び6Bの列毎に入れ替わることは既に述べたとおりである。次に全画素に対する画像信号電圧の書込みが終了した後、前述の[タイミングt1からt2まで]の期間において、シャッタ電極26の極性反転駆動を目的として、フレーム毎に奇数画素列と偶数画素列に相当する制御電極線8A、8Bの印加電圧が制御電極駆動回路17によって相補的に駆動されることは既に述べたとおりである。また引続き行われる[タイミングt2からt23まで]における、信号蓄積容量4に書込まれた画像信号電圧に基づいた、全画素における次段信号蓄積容量101への信号電圧書込みは、書込み駆動回路106が容量線11、シャッタ電圧書込み用ソース電圧線12を一斉に駆動することによって行われる。その後[タイミングt24からt25まで]において、書込み駆動回路106から次段シャッタ電圧書込み用ソース電圧線104を一斉に駆動してシャッタ電極26への信号電圧書込みが行われると共に、シャッタ電圧書込み用ソース電圧線12へのVm印加が行われる。

【0110】

なお既に述べたように、第6実施形態の画素部断面構造は第1実施形態の画素部断面構造と同様であると同時に、基本的な動作に関しても既に第1実施形態で述べたものと同じであるため、ここではこれ以上の説明は省略する。

【0111】

既に述べたように第6実施形態においては、次段信号蓄積容量101及び次段シャッタ電圧書込み用トランジスタ102が擬似ダイオード回路としてシャッタ電極26への書込みを行うため、[タイミングt24からt25まで]及び[タイミングt25以降]において、シャッタ電極26への信号電圧の書込みと、画素に対する画像信号電圧の書込み走査を並行して行えるという利点がある。次段信号蓄積容量101の容量値はシャッタ電極26の入力容量値と異なってシャッタ電極26の位置にかかわらず一定値をとるため、次段信号蓄積容量101への書込みは、比較的短時間で完了することができる。これによって本実施形態は、特に列方向に画素数の大きいディスプレイを設計する場合には走査回路15の駆動クロックを低減することができ、回路設計マージンの確保による歩留りの向上や、消費電力の削減を図る上で大きな利点となる。

【0112】

本実施形態においても、第1実施形態と同様に、画素内の配線を減少させることができ、量産上の歩留りを上げると共に、低コスト化を図ることができる。また、遮光膜を誘電体で形成しているため、機械的シャッタと遮光膜との間に電界が生じることを回避して、機械的シャッタの動作マージンを損なうことなく高コントラストを実現できる。

【0113】

[第7実施形態]

以下、図19を用いて、本発明における第7実施形態に関して説明する。

【0114】

図19は第7実施形態であるインターネット画像表示装置150の構成図である。無線インターフェース(I/F)回路152には、圧縮された画像データ等が外部から無線データとして入力し、無線I/F回路152の出力はI/O(Input/Output)回路153を介してデータバス158に接続される。データバス158にはこの他にマイクロプロセッサ(MPU)154、表示パネルコントローラ156、フレームメモリ157等が接続されている。更に表示パネルコントローラ156の出力は機械的シャッタを用いた表示装置151に入力している。なおインターネット画像表示装置150には更に、電源159が設けられている。なおここで機械的シャッタを用いた表示装置151は、先に延べた第1実施形態と同一の構成および動作を有しているので、その内部の構成及び動作の記載はここでは省略する。

【0115】

以下に、第7実施形態の動作を説明する。始めに無線I/F回路152は命令に応じて圧縮された画像データを外部から取り込み、この画像データをI/O回路153を介してマイクロプロセッサ154及びフレームメモリ157に転送する。マイクロプロセッサ154はユーザからの命令操作を受けて、必要に応じてインターネット画像表示装置150全体を駆動し、圧縮された画像データのデコードや信号処理、情報表示を行う。ここで信号処理された画像データは、フレームメモリ157に一時的に蓄積が可能である。

【0116】

ここでマイクロプロセッサ154が表示命令を出した場合には、その指示に従ってフレームメモリ157から表示パネルコントローラ156を介して表示装置151に画像データが入力され、表示装置151は入力された画像データをリアルタイムで表示する。このとき表示パネルコントローラ156は、同時に画像を表示するために必要な所定のタイミングパルスを出力制御する。なお表示装置151がこれらの信号を用いて、入力された画像データをリアルタイムで表示することに関しては、第1実施形態の説明で述べたとおりである。なおここで電源159には二次電池が含まれており、インターネット画像表示装置150全体を駆動する電力を供給する。

【0117】

本実施形態によれば、高画質表示が可能であり、かつ消費電力の少ないインターネット画像表示装置150を低コストで提供することができる。

【0118】

なお、本実施形態では画像表示デバイスとして、第1実施形態で説明した表示装置151を用いたが、これ以外にその他の本発明の実施形態に記載されたような種々の表示装置を用いることが可能である。但しこの場合は表示パネルコントローラ156の出力するタイミングパルスには、必要に応じて若干の変更が必要になることは言うまでもない。

【0119】

本実施形態のインターネット画像表示装置150においても、第1実施形態と同様に、画素内の配線を減少させることができ、量産上の歩留りを上げると共に、低コスト化を図ることができる。また、遮光膜を誘電体で形成しているため、機械的シャッタと遮光膜との間に電界が生じることを回避して、機械的シャッタの動作マージンを損なうことなく高コントラストを実現できる。

【符号の説明】

【0120】

1 双極性シャッタ、3 シャッタ電圧書込み用トランジスタ、4 信号蓄積容量、5 走査スイッチ、6A 信号線、6B 信号線、8A 制御電極線、8B 制御電極線、10 走査線、11 容量線、12 シャッタ電圧書込み用ソース電圧線、13 画素、13B 画素、13G 画素、13R 画素、14 画像信号電圧書込み回路、15 走査回路、16 駆動回路、17 制御電極駆動回路、18 シャッタ制御回路、21 反射膜、22 導光板、23 反射膜、24 黒色樹脂膜、25 制御電極、26 シャッタ電極、27 制御電極、29 ドレイン電極、30 タッチパネル、31 ソース電極、32 ゲート電極、33 ゲート絶縁膜、34 アモルファスシリコン薄膜、35 アモルファスシリコン薄膜、36 ガラス基板、37 保護膜、38 フィルムシート、39 保護膜、40 センス電極、41 光、42 光源、45 等価入力容量、46 等価配線、47 等価ダイオード、48 直流電源、49 等価抵抗、50 反射膜、50B 多層誘電膜、50G 多層誘電膜、50R 多層誘電膜、51 色カラーフィルタ、52 光源、60 透明保護膜、70 補助容量、73 画素、80 CMOS書込み用トランジスタ、81 信号蓄積容量、82 CMOSシャッタ電圧書込み用pMOSトランジスタ、83 CMOSシャッタ電圧書込み用nMOSトランジスタ、84 CMOSシャッタ電圧書込み用pMOSソース電圧線、85 画素、86 駆動回路、87 シャッタ制御回路、91 低不純物濃度低温多結晶シリコン薄膜、92 低温多結晶シリコン薄膜、93 ゲート絶縁膜、94 層間絶縁膜、95 ゲート電極、96 ソース電極、97 ドレイン電極、100 次段書込み用トランジスタ、101 次段信号蓄積容量、102 シャッタ電圧書込み用トランジスタ、104 シャッタ電圧書込み用ソース電圧線、105 画素、106 駆動回路、107 シャッタ制御回路、150 インターネット画像表示装置、151 表示装置、152 無線I/F回路、153 I/O回路、154 マイクロプロセッサ、156 表示パネルコントローラ、157 フレームメモリ、158 データバス、159 電源、201 双極性シャッタ、202 シャッタ正電圧書込み用pMOSトランジスタ、203 シャッタ負電圧書込み用nMOSトランジスタ、204 信号蓄積容量、205 走査スイッチ、206 信号線、207 ゲート電圧線、208 正電圧線、209 制御電極電圧線、210 走査線、211 シャッタ電圧線、212 ソース電圧線、213 画素、300 画像表示装置、302 発光制御回路、304 システム制御回路、306 表示制御回路、308 パネル制御線、320 バックライト光源、330 TFT基板。

【技術分野】

【0001】

本発明は、画像表示装置に関し、より詳しくは、機械的シャッタを用いた画像表示装置に関する。

【背景技術】

【0002】

図20は従来の技術による、機械的シャッタを用いた画像表示装置のシャッタ制御回路を示す図である。各画素213には信号線206が設けられており、信号線206と信号蓄積容量204の一端とは走査スイッチ205で接続されている。信号蓄積容量204の一端は更にシャッタ負電圧書込み用nMOSトランジスタ203のゲートに接続されており、シャッタ負電圧書込み用nMOSトランジスタ203のドレインはシャッタ正電圧書込み用pMOSトランジスタ202のドレインに接続されている。各画素にはシャッタ電圧線211に接続された双極性シャッタ(Dual Actuator Shutter Assembly)201を有しているが、二つある双極性シャッタ201の制御電極の内の一方はシャッタ負電圧書込み用nMOSトランジスタ203のドレインに接続されており、制御電極の他方は制御電極電圧線209に接続されている。なお信号蓄積容量204の他端はシャッタ電圧線211に接続されており、シャッタ負電圧書込み用nMOSトランジスタ203のソースはシャッタ負電圧書込み用nMOSソース電圧線212に、シャッタ正電圧書込み用pMOSトランジスタ202のゲートとドレインはそれぞれシャッタ正電圧書込み用pMOSゲート電圧線207と正電圧線208に、走査スイッチ205のゲートは走査線210に接続されている。なお上記の双極性シャッタ201は、遮光面上に設けられた開口に対向して設けられており、当該画像表示装置にはこのような画素がマトリクス状に配列されている。

【0003】

次に、上記の画像表示装置の動作について説明する。信号線206に書込まれた画像信号電圧は、走査線210を順次走査することによって走査スイッチ205を介して信号蓄積容量204に記憶される。次に、全画素の信号蓄積容量204に対する画像信号電圧の書込み走査が終了した後に、各画素において、書込まれた画像信号電圧を元に双極性シャッタ201の制御電極の内の一方に対して画像信号の増幅書込みを行う。即ちまず全画素において、シャッタ正電圧書込み用pMOSゲート電圧線207を所定の期間だけ低電圧にすることによって、シャッタ正電圧書込み用pMOSトランジスタ202をこの期間のみオン状態にして、双極性シャッタ201の制御電極の内の一方の電極に、正電圧線208に印加されていた所定の正電圧をプリチャージする。この次にシャッタ負電圧書込み用nMOSソース電圧線212を、所定の期間だけ所定の低電圧にする。このとき信号蓄積容量204に画像信号電圧として高電圧が書込まれていた場合には、この期間のみシャッタ負電圧書込み用nMOSトランジスタ203がオン状態となることによって、双極性シャッタ201の制御電極の内の一方の電圧はシャッタ負電圧書込み用nMOSソース電圧線212に印加されている所定の低電圧に書き換えられる。また信号蓄積容量204に画像信号電圧として低電圧が書込まれていた場合には、この期間もシャッタ負電圧書込み用nMOSトランジスタ203はオフ状態を維持するため、双極性シャッタ201の制御電極の内の一方の電圧は、既にプリチャージされた所定の正電圧を維持する。

【0004】

このようにして双極性シャッタ201の制御電極の内の一方の電極に画像信号の増幅書込みを行うが、これと並行して制御電極電圧線209への印加電圧を制御することによって、双極性シャッタ201を静電的に開閉操作することができる。このように双極性シャッタ201で遮光面上に設けられた開口を開閉することで光の透過量を制御して、当該画像表示装置は書込まれた画像信号電圧に対応した画像を画素マトリクス上に表示することができる。なお、このような従来例に関しては、例えば特許文献1などに詳しく記載されている。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】米国特許出願公開第2008/174532号明細書

【特許文献2】米国特許出願公開第2008/145527号明細書

【特許文献3】米国特許出願公開第2008/062500号明細書

【特許文献4】米国特許出願公開第2007/159679号明細書

【特許文献5】米国特許出願公開第2007/091038号明細書

【特許文献6】米国特許出願公開第2007/030555号明細書

【特許文献7】米国特許出願公開第2006/187528号明細書

【特許文献8】米国特許出願公開第2009/034052号明細書

【特許文献9】米国特許出願公開第2008/158635号明細書

【特許文献10】米国特許出願公開第2007/223080号明細書

【特許文献11】米国特許出願公開第2007/216987号明細書

【特許文献12】米国特許出願公開第2006/187530号明細書

【特許文献13】米国特許出願公開第2008/030827号明細書

【特許文献14】米国特許出願公開第2006/187529号明細書

【特許文献15】米国特許出願公開第2006/250676号明細書

【特許文献16】米国特許出願公開第2008/123175号明細書

【特許文献17】米国特許出願公開第2006/187531号明細書

【特許文献18】米国特許出願公開第2008/151357号明細書

【特許文献19】米国特許出願公開第2007/002156号明細書

【特許文献20】米国特許出願公開第2010/110518号明細書

【特許文献21】米国特許出願公開第2010/027100号明細書

【特許文献22】米国特許出願公開第2009/257245号明細書

【特許文献23】米国特許出願公開第2009/244678号明細書

【特許文献24】米国特許出願公開第2009/195855号明細書

【特許文献25】米国特許出願公開第2009/103164号明細書

【特許文献26】米国特許出願公開第2008/283175号明細書

【特許文献27】米国特許出願公開第2008/278798号明細書

【特許文献28】米国特許出願公開第2008/158636号明細書

【特許文献29】米国特許出願公開第2008/129681号明細書

【特許文献30】米国特許出願公開第2008/094853号明細書

【特許文献31】米国特許出願公開第2008/037104号明細書

【特許文献32】米国特許出願公開第2007/279727号明細書

【特許文献33】米国特許出願公開第2007/205969号明細書

【特許文献34】米国特許出願公開第2007/195026号明細書

【特許文献35】米国特許出願公開第2006/250325号明細書

【特許文献36】米国特許出願公開第2007/086078号明細書

【特許文献37】米国特許出願公開第2006/256039号明細書

【特許文献38】米国特許出願公開第2006/209012号明細書

【特許文献39】米国特許出願公開第2006/187191号明細書

【特許文献40】米国特許出願公開第2006/187190号明細書

【特許文献41】米国特許出願公開第2010/188443号明細書

【発明の概要】

【発明が解決しようとする課題】

【0006】

従来の技術は、各画素の双極性シャッタ201を制御するために各画素に多くの配線を設ける必要があることから、画素内に設ける回路が密になり、量産上の歩留りを上げ難いという課題があった。例えば図20の例では、各画素には信号線206、シャッタ正電圧書込み用pMOSゲート電圧線207、正電圧線208、制御電極電圧線209、走査線210、シャッタ電圧線211、シャッタ負電圧書込み用nMOSソース電圧線212の計7本の配線が必要であった。

【0007】

本発明は、上述の事情を鑑みてしたものであり、低消費電力でありながら高コントラストで色再現性が良いといった、機械的シャッタを用いた従来技術の利点である高画質性能を維持しながら、画素内の配線を減らし、量産上の歩留りを上げると共に、低コスト化を図ることのできる表示装置を提供することを目的とする。

【課題を解決するための手段】

【0008】

上記の課題は、マトリクス状に配列された画素において前記画素毎に設けられ、透明基板上で前記透明基板の面に平行に移動し、光の透過及び遮断を行う機械的シャッタ部と、前記透明基板上で前記機械的シャッタ部を挟むように配置される一対の制御電極と、前記透明基板に向けて光を発し、前記透明基板と平行に配置される面状の光源と、前記面状の光源上の前記透明基板側に成膜され、前記機械的シャッタ部が光の透過及び遮断を行う領域に対応して前記画素毎に開けられた光学的開口を有し、前記面状の光源から出射された光に対して、前記光学的開口以外の領域を遮光する遮光膜と、前記一対の制御電極に、前記制御電極のための高電圧及び低電圧をそれぞれに印加する制御電極駆動回路と、前記画素毎に設けられ、前記画素毎の階調値に応じたタイミングで、信号線を介して設定される高電圧及び低電圧のいずれかを印加することにより、前記機械的シャッタ部の動作を静電的に制御するシャッタ制御回路とを備え、前記遮光膜は、誘電体で形成されている、ことを特徴とする画像表示装置によって解決される。

【0009】

ここで、「面状の光源」とは、点光源等の光源から発せられた光を導光板等を介して出射するように構成されたバックライト等を含む意味である。

【発明の効果】

【0010】

本発明によれば、低消費電力でありながら高コントラストで色再現性が良いといった、機械的シャッタを用いた従来技術の利点である高画質性能を維持しながら、更に画素内の配線を少なくすることが可能であるため、量産上の歩留りを上げて低コスト化を実現することができる。

【図面の簡単な説明】

【0011】

【図1】第1実施形態に係る画像表示装置について示す図である。

【図2】第1実施形態に係る画像表示装置のTFT基板の画素周辺回路図である。

【図3】第1実施形態に係る画像表示装置のシャッタ制御回路について示す図である。

【図4】第1実施形態に係る画像表示装置における、画素の断面構造を示す図である。

【図5】図3のシャッタ制御回路の動作タイミングチャートである。

【図6A】画像信号電圧が0(V)の時のシャッタ電極への信号電圧書込みを説明するための図である。

【図6B】画像信号電圧が0(V)の時のシャッタ電極への信号電圧書込みを説明するための図である。

【図6C】画像信号電圧が0(V)の時のシャッタ電極への信号電圧書込みを説明するための図である。

【図7A】画像信号電圧がVsigHの時のシャッタ電極への信号電圧書込みを説明するための図である。

【図7B】画像信号電圧がVsigHの時のシャッタ電極への信号電圧書込みを説明するための図である。

【図7C】画像信号電圧がVsigHの時のシャッタ電極への信号電圧書込みを説明するための図である。

【図8】第2実施形態に係る画像表示装置の表示領域内の画素配列構成図である。

【図9】第2実施形態に係る画像表示装置における、画素の断面構造を示す図である。

【図10】第3実施形態に係る画像表示装置における、画素断面構造を示す図である。

【図11】第4実施形態に係る画像表示装置のシャッタ制御回路を示す図である。

【図12】第5実施形態に係る画像表示装置の画素周辺回路図である。

【図13】第5実施形態に係る画像表示装置のシャッタ制御回路を示す図である。

【図14】第5実施形態に係る画像表示装置における、画素断面構造を示す図である。

【図15】図13のシャッタ制御回路の動作タイミングチャートである。

【図16】第6実施形態に係る画像表示装置の画素周辺回路図である。

【図17】第6実施形態に係る画像表示装置のシャッタ制御回路を示す図である。

【図18】図13のシャッタ制御回路の動作タイミングチャートである。

【図19】第7実施形態に係るインターネット画像表示装置の構成図である。

【図20】従来の技術によるシャッタ制御回路を示す図である。

【発明を実施するための形態】

【0012】

以下、本発明の実施形態について、図面を参照しつつ説明する。なお、図面において、同一又は同等の要素には同一の符号を付し、重複する説明を省略する。

【0013】

[第1実施形態]

以下、図1〜図7を用いて、本発明の第1実施形態に係る画像表示装置について、その構成および動作を順次説明する。

【0014】

図1は、各画素のシャッター機構により表示画像の制御を行う、本発明の第1実施形態に係る画像表示装置300について示す図である。この図1に示されるように、画像表示装置300は、各画素毎に、光を透過する開口部を有する遮光膜(後述)を備えるバックライト光源320と、バックライト光源320からの光の透過をシャッター機構部(後述)により制御すると共に、タッチパネルを有するTFT(Thin Film Transistor)基板330と、バックライト光源320のR(赤)G(緑)B(青)の3色の光を時間をずらして発光させるための制御を行う発光制御回路302と、TFT基板330のシャッター機構部の動作を、パネル制御線308を介して制御する表示制御回路306と、発光制御回路302及び表示制御回路306の統括的な制御を行うシステム制御回路304とを有している。

【0015】

図2は、図1のTFT基板330の画素周辺回路図である。マトリクス状に配列された画素13が表示領域を構成しており、画素13には列方向に信号線6A及び6Bと、制御電極線8A及び8Bが、行方向に走査線10、容量線11、シャッタ電圧書込み用ソース電圧線12が設けられている。表示領域の周辺で、信号線6A及び6Bの一端は画像信号電圧書込み回路14に接続されており、制御電極線8A及び8Bの一端はそれぞれ制御電極駆動回路17に接続されている。また走査線10の一端は走査回路15に接続されており、容量線11、シャッタ電圧書込み用ソース電圧線12の一端は、それぞれ書込み駆動回路16に接続されている。なお、図2は簡単のために表示領域を画素数が4×3画素のマトリクスで記載しているが、本発明の開示する技術思想が特に画素数を制限するものではない。

【0016】

図3には、図2の各画素13におけるシャッタ制御回路18が示されている。各画素13には信号線6Aが設けられており、信号線6Aと信号蓄積容量4とは走査スイッチ5で接続されている。信号蓄積容量4は更にシャッタ電圧書込み用トランジスタ3のゲートに接続されており、シャッタ電圧書込み用トランジスタ3のドレインは双極性シャッタ1のシャッタ電極に接続されている。二つある双極性シャッタ1の制御電極の内の一方は画素内の制御電極線8Aに接続されているが、制御電極の他方は隣接する画素の制御電極線8Bに接続されている。なお信号蓄積容量4の他端は容量線11に接続されており、シャッタ電圧書込み用トランジスタ3のソースはシャッタ電圧書込み用ソース電圧線12に、走査スイッチ5のゲートは走査線10に接続されている。なお上記の双極性シャッタ1は、後に図4を用いて説明するように、遮光面上に設けられた開口に対向して設けられている。

【0017】

なお、図3には信号線6Aと制御電極線8Aを有する画素と、信号線6Bと制御電極線8Bを有する画素の、2画素分が記載されている。両画素は後述のように駆動条件は異なるものの、基本的なシャッタ制御回路は同一である。

【0018】

図4は、画素13の画素部断面構造図である。ガラス基板36上には、高融点金属で形成されたゲート電極32、ゲート絶縁膜33、ノンドープのアモルファスシリコン薄膜34、高濃度n型不純物をドープしたアモルファスシリコン薄膜35、ソース電極31、ドレイン電極29とから構成されるアモルファスシリコン薄膜トランジスタが設けられており、これはシャッタ電圧書込み用トランジスタ3に対応するものである。更にガラス基板36上には、ソース電極31、ドレイン電極29と同じAl配線層で制御電極線8A、8Bが形成されており、これらはシリコンナイトライドと有機材料の多層膜からなる保護膜37によって覆われている。

【0019】

保護膜37上には、シャッタ電極26と、二つの制御電極25、27を有する双極性シャッタ1が設けられており、ドレイン電極29はシャッタ電極26に、制御電極線8Aは制御電極25に、制御電極線8Bは制御電極27に、それぞれコンタクトホールを介して接続されている。またこれらシャッタ電極26と、二つの制御電極25、27には互いに接触した際の短絡防止のために、表面には絶縁膜が形成されている。なおここでシャッタ電極26は、シャッタ電極26に入力される電圧と、二つの制御電極25、27に入力される電圧との相対関係による電界でその位置が制御されるため、図4には破線を用いてその可動範囲も開示している。なお図4には記載されていないが、画素13内に設けられたその他のトランジスタも、同様にアモルファスシリコン薄膜トランジスタで構成されている。

【0020】

シャッタ電極26に対してガラス基板36と反対側には、R(赤)G(緑)B(青)の3色の独立LED光源からなる光源42を有する導光板22が設けられている。導光板22の両面には反射膜21、23が設けられているが、ここで特にシャッタ電極26側の反射膜23は多層誘電膜より構成されている。反射膜23を構成する多層誘電膜はTiO2、Ta2O3等の高屈折率材料とSiO2、MgF2等の低屈折材料の積層構造からなっており、これらの積層構造の各膜厚を適切な値に設計することによって、光源42が有するR(赤)G(緑)B(青)の3色の独立LED光源の射出光に対して実用上十分な全反射特性を得ることができる。ところで多層誘電膜を全反射膜として用いた場合の課題は、垂直方向に入射する光に対して最適設計した場合に、水平に近い角度で入射した光に対しては反射特性が悪化することである。反射膜23が光を透過した場合には表示装置の光漏れとなってしまい、コントラストの著しい低下を招いてしまう。そこでこのような光漏れを防止するために、更に反射膜23の上には有機材料で作成された黒色樹脂膜24を形成した。この黒色樹脂膜は、ポリイミド樹脂等にカーボンブラック、チタンブラック等の顔料粒子を適切に分散させることで形成することができる。ここで反射膜23及び黒色樹脂膜24には図4に示すように、シャッタ電極26に対応する位置に開口が設けられており、光源42から射出されて導光板22を伝播した光41の一部が、この開口から射出されるように構成されている。開口は例えば、黒色樹脂膜24をマスクとしたフォトリソグラフィーによって一括加工形成することができる。

【0021】

ガラス基板36に対して導光板22と反対側には、フィルムシート38、センス電極40、保護膜39からなるタッチパネル30が設けられている。タッチパネル30のセンス電極40は表示領域の周辺でタッチ検出用回路に接続されているが、この部分の構成は既に一般に知られている技術であるため、ここではその詳細な説明は省略する。

【0022】

次に、図3で述べた第1実施形態のシャッタ制御回路18の動作について説明する。図5は第1実施形態のシャッタ制御回路18の動作タイミングチャートであり、横軸に時間を取って、縦軸に各部分の電圧を示したものである。また特に最下段に記載した双極性シャッタ1のシャッタ電極26の電圧値に関しては、画像信号によって約0(V)と約Vhの二値を取るため、図面を判り易くするために前者を実線、後者を破線で示している。

【0023】

[タイミングt1まで]

この期間には、画素に対する画像信号電圧の書込みが行われている。この期間は制御電極線8A、8Bにはそれぞれ高電圧Vh、低電圧0(V)が印加されているが、後述するようにシャッタ電極26の極性反転駆動を目的として、奇数画素列と偶数画素列に相当する制御電極線8A、8Bの印加電圧は毎フレーム毎にその値が入れ替わる。各画素の走査スイッチ5は走査線10によって順次走査されており、走査スイッチ5が走査された画素の信号蓄積容量4には、信号線6A、6Bから所定の画像信号電圧が書込まれる。ここで信号線6A、6Bに印加される画像信号電圧は例えば7(V)と0(V)の二値をとるが、白表示時と黒表示時にそれぞれ7(V)と0(V)のいずれに該当するかは、シャッタ電極26の極性反転駆動を目的とした制御電極線8A、8Bの印加電圧の毎フレーム毎の値によって、信号線6A及び6Bの列毎に入れ替わる。なお容量線11には0(V)、シャッタ電圧書込み用ソース電圧線12にはVmが印加されており、双極性シャッタ1のシャッタ電極26には約0(V)ないし約Vhが印加されている。なおここでVhの値は双極性シャッタ1の静電的な機械駆動が可能な最小の電圧に設計されるが、例えばこの値は20(V)である。またVmの値は信号電圧が信号蓄積容量4に書込まれてもシャッタ電圧書込み用トランジスタ3がオンすることのない値であり、例えば7(V)である。

【0024】

[タイミングt1からt2まで]

この期間にはシャッタ電極26の極性反転駆動を目的として、毎フレーム毎に奇数画素列と偶数画素列に相当する制御電極線8A、8Bの印加電圧の入れ替わりが行われる。本実施形態は後述するように光源42の発光にサブフィールド毎に時間重みを持たせて、シャッタ電極26の開閉で外部への発光を制御するPWM(Pulse Width Modulation)駆動を行うが、制御電極線8A、8Bの印加電圧の入れ替えはフレーム毎に替えて、サブフィールド毎や、複数サブフィールド毎に行っても良い。制御電極線8A、8Bの印加電圧の入れ替えを行わないサブフィールドでは、この[タイミングt1からt2まで]の期間は設ける必要はない。なお、制御電極線8A、8Bの印加電圧の入れ替えを頻繁に行う場合には、これに伴うタイミングt1からt2までの遷移期間を頻繁に設ける必要があることと、消費電力が増加することには留意する必要がある。

【0025】

[タイミングt2からt3まで]

この期間には信号蓄積容量4に書込まれた画像信号電圧に基づいて、全画素において一斉にシャッタ電極26への信号電圧書込みが行われる。容量線11とシャッタ電圧書込み用ソース電圧線12に同時にVhが書込まれ、この後に両者の電圧は揃って0(V)に立ち下げられる。この動作によってシャッタ電圧書込み用トランジスタ3が制御され、信号蓄積容量4に書込まれていた画像信号電圧が0(V)の場合にはシャッタ電極26には信号電圧として(Vh−Vth)が書込まれ、画像信号電圧が7(V)だった場合にはシャッタ電極26には信号電圧として0(V)が書込まれる。なおここでVthは、シャッタ電圧書込み用トランジスタ3のしきい値電圧である。

【0026】

以下に図6、図7を用いて、上記のシャッタ電極26への信号電圧書込みについて詳細に説明する。

【0027】

図6A〜6Cは信号蓄積容量4に書込まれていた画像信号電圧が0(V)の場合の、シャッタ電極26への信号電圧書込み説明図である。図6Aはこの期間の最初に信号蓄積容量4に0(V)が書込まれている場合の画素等価回路を示しており、ここではシャッタ電極26に替えて、シャッタ電極26の等価入力容量45を記載してある。次にこの期間に、容量線11とシャッタ電圧書込み用ソース電圧線12が同時に操作される状態を考えると、これは図6Bの等価回路に示すように、0(V)が書込まれている信号蓄積容量4は短絡と等価であり、容量線11とシャッタ電圧書込み用ソース電圧線12はまとめて一本の等価配線46とみなす事ができる。すると更にシャッタ電圧書込み用トランジスタ3はダイオード接続されたトランジスタであるから、図6Cの等価回路に示すように、全体はシャッタ電極26の等価入力容量45がシャッタ電圧書込み用トランジスタ3の等価ダイオード47を介して等価配線46と接続された構成とみなすことができる。この図6Cの等価回路を用いると、容量線11とシャッタ電圧書込み用ソース電圧線12に同時にVhが書込まれた際には、等価ダイオード47がオンしてシャッタ電極26の等価入力容量45に信号電圧として(Vh−Vth)が書込まれ、この後に容量線11とシャッタ電圧書込み用ソース電圧線12に同時に0(V)が書込まれてもシャッタ電極26が(Vh−Vth)を信号電圧として保持することが容易に説明できる。

【0028】

次に、図7A〜7Cは信号蓄積容量4に書込まれていた画像信号電圧が7(V)であった場合の、シャッタ電極26への信号電圧書込み説明図である。図7Aはこの期間の最初に信号蓄積容量4に7(V)(図7A〜7Cでは一般化のためにVsigHと記載)が書込まれている場合の画素等価回路を示しており、ここでもシャッタ電極26に替えて、シャッタ電極26の等価入力容量45を記載してある。次にこの期間に、容量線11とシャッタ電圧書込み用ソース電圧線12が同時に操作される状態を考えると、これは図7Bの等価回路に示すように、7(V)が書込まれている信号蓄積容量4は7(V)の直流電源48と等価であり、容量線11とシャッタ電圧書込み用ソース電圧線12はまとめて一本の等価配線46とみなす事ができる。するとゲートに7(V)の直流電源48が接続されたシャッタ電圧書込み用トランジスタ3は常時オンであるために等価抵抗49とみなす事ができるから、図7Cの等価回路に示すように、全体はシャッタ電極26の等価入力容量45がシャッタ電圧書込み用トランジスタ3の等価抵抗49を介して等価配線46と接続された構成とみなすことができる。この図7Cの等価回路を用いると、容量線11とシャッタ電圧書込み用ソース電圧線12に同時にVhが書込まれた際には、等価抵抗49を経由してシャッタ電極26の等価入力容量45には信号電圧として一旦はVthが書込まれ、その後に容量線11とシャッタ電圧書込み用ソース電圧線12に同時に0(V)が書込まれた際には、等価抵抗49を経由してシャッタ電極26の等価入力容量45には再び0(V)が書込まれることが容易に説明できる。

【0029】

このようなシャッタ電圧書込み用トランジスタ3と信号蓄積容量4を用いた信号書込み回路を、ここでは擬似ダイオード回路と称することにする。

【0030】

[タイミングt3からt4まで]

この期間には容量線11とシャッタ電圧書込み用ソース電圧線12は0(V)に立ち下げられた電圧値を維持しており、シャッタ電極26に0(V)が書込まれる場合には、この期間に電圧は約0(V)に収束する。

【0031】

[タイミングt4以降]

この期間は再びタイミングt1までの動作と同様に、画素に対する画像信号電圧の書込みが行われる。各画素の走査スイッチ5は走査線10によって順次走査され、走査スイッチ5が走査された画素の信号蓄積容量4には、信号線6A、6Bから所定の画像信号電圧が書込まれる。シャッタ電圧書込み用ソース電圧線12にはVmが印加されており、信号電圧が信号蓄積容量4に書込まれても基本的にはシャッタ電圧書込み用トランジスタ3がオンすることはない。

【0032】

但しシャッタ電極26に0(V)が書込まれており、信号蓄積容量4に7(V)(VsigH)が書込まれている場合には、シャッタ電極26の電圧はシャッタ電圧書込み用トランジスタ3のオフする電圧である7(V)−Vth(VsigH−Vth)まで、この期間に再度上昇する点には注意が必要である。基本的にシャッタ電極26は二値駆動であるため、0(V)が7(V)−Vth(VsigH−Vth)に上昇しても動作そのものに大きな支障はないが、これによって動作マージンが減る方向にはなる。ここでVsigHは高い電圧である方がシャッタ電圧書込み用トランジスタ3によるシャッタ電極26の等価入力容量45への書込み動作はより高速化できるという長所がある。しかしその一方で、画像信号電圧書込み回路14から信号線6A及び6BにVsigHを書込む際の消費電力が上昇する点や、上記のようにシャッタ電極26に0(V)が書込まれている場合には、シャッタ電極26の電圧はシャッタ電圧書込み用トランジスタ3のオフする電圧である7(V)−Vth(VsigH−Vth)までは再度上昇するといった副作用も有しているため、本実施形態では7(V)としたVsigHの電圧値は、これらを勘案した上で最適に設定する必要がある。

【0033】

次に図2で述べた第1実施形態の画素周辺回路の動作について説明する。前述の[タイミングt1まで]に相当する画素に対する画像信号電圧の書込み期間においては、走査線10は走査回路15によって順次走査され、これと同期して信号線6A及び6Bには画像信号電圧書込み回路14から画像信号電圧が書込まれる。ここで前述のように本実施形態は光源42の発光にサブフィールド毎に時間重みを持たせて、シャッタ電極26の開閉で外部への発光を制御するPWM駆動を行う。このため画像信号電圧書込み回路14から信号線6A及び6Bに書込まれる画像信号電圧は、例えば0(V)と7(V)の二値の電圧であり、これによって各画素に設けられたシャッタ電極26に印加される信号電圧を制御する。なお白表示時と黒表示時にそれぞれ7(V)と0(V)のいずれに該当するかは、シャッタ電極26の極性反転駆動を目的とした制御電極線8A、8Bの印加電圧の毎フレーム毎の値によって、信号線6A及び6Bの列毎に入れ替わることは既に述べたとおりである。次に全画素に対する画像信号電圧の書込みが終了した後、前述の[タイミングt1からt2まで]の期間において、シャッタ電極26の極性反転駆動を目的として、フレーム毎に奇数画素列と偶数画素列に相当する制御電極線8A、8Bの印加電圧が制御電極駆動回路17によって相補的に駆動されることは既に述べたとおりである。また引続き行われる[タイミングt2からt3まで]における、信号蓄積容量4に書込まれた画像信号電圧に基づいた、全画素におけるシャッタ電極26への信号電圧書込みは、書込み駆動回路16が容量線11、シャッタ電圧書込み用ソース電圧線12を一斉に駆動することによって行われる。その後の[タイミングt4以降]において、シャッタ電圧書込み用ソース電圧線12へのVm印加を行うのも書込み駆動回路16である。

【0034】

最後に図4で述べた第1実施形態のシャッタ電極26近傍構造の動作について説明する。前述の[タイミングt1まで]に相当する、画素に対する画像信号電圧の書込み終了後、[タイミングt1からt2まで]の期間においてフレーム期間毎に奇数画素列と偶数画素列に相当する制御電極線8A、8Bの印加電圧が制御され、これらの電圧はそれぞれ双極性シャッタ1の制御電極25、27に印加される。例えばあるフレームにおいて、制御電極25には0(V)、制御電極27にはVh(例えば20(V))が印加される。次いで[タイミングt2からt3まで]の期間におけるシャッタ電極26への信号電圧書込み動作によって、シャッタ電極26には約Vh(例えば20(V))或いは約0(V)が書込まれる。ここで制御電極25には0(V)、制御電極27にはVh(例えば20(V))が印加されているため、シャッタ電極26と制御電極25、27が生じる電界の効果によって、シャッタ電極26に約Vh(例えば20(V))が書込まれた場合にはシャッタ電極26は反射膜23及び黒色樹脂膜24の開口上でその位置が安定し、シャッタ電極26に約0(V)が書込まれた場合にはシャッタ電極26は反射膜23及び黒色樹脂膜24の遮光上でその位置が安定する。これによりシャッタ電極26に約Vh(例えば20(V))が書込まれた場合には、光源42から射出されて導光板22を伝播した光41は開口から射出されてもシャッタ電極26で反射されることで再び導光板22に戻されてしまうため、画素は非発光状態として観測される。またシャッタ電極26に約0(V)が書込まれた場合には光源42から射出されて導光板22を伝播した光41はこの開口から射出されるため、画素は発光状態として観測される。

【0035】

なお、ここで次のフレームにおいては制御電極25、27と画像信号電圧の極性は逆になる。即ち制御電極25にはVh(例えば20(V))、制御電極27には0(V)が印加されるため、シャッタ電極26に約0(V)が書込まれた場合には、光源42から射出されて導光板22を伝播した光41は開口から射出されてもシャッタ電極26で反射されることで再び導光板22に戻されてしまうため、画素は非発光状態として観測される。またシャッタ電極26に約Vh(例えば20(V))が書込まれた場合には光源42から射出されて導光板22を伝播した光41はこの開口から射出されるため、画素は発光状態として観測される。このようにシャッタ電極26の極性反転駆動を行うことによって、シャッタ電極26、制御電極25、27の表面の絶縁膜に印加される電界を交流化することができ、これらの電極の電気的安定性をより増加させることができる。

【0036】

前述のように本実施形態では光源42の発光にサブフィールド毎に時間重みを持たせて、シャッタ電極26の開閉で外部への発光を制御するPWM駆動を行う。即ち光源42が有するR(赤)G(緑)B(青)の3色の独立LED光源の発光期間に2のn乗の時間重みを持たせ、画素毎のシャッタ電極26の開閉制御と組合されることで、画素毎にPWM方式による階調発光を実現すると同時に、FSC方式によるカラー表示を実現している。このような光源42の点灯は、[タイミングt1まで]及び[タイミングt4以降]の、画素に対する画像信号電圧の書込み期間内に行われる。

【0037】

上述したように、シャッタ電極26への信号電圧の書込みを行う構成としたことにより、画素内の配線を減少させることができる。また、これにより、量産上の歩留りを上げると共に、低コスト化を図ることができる。

【0038】

また、画像信号に応じて機械的シャッタに所定の高電圧、或いは所定の低電圧を選択的に印加した場合に、機械的シャッタと遮光膜との間に電界が生じると、この電界は画像信号に応じて変調されてしまうために機械的シャッタの動作マージンを著しく損なってしまう恐れがあるが、本実施形態においては、更に遮光膜を誘電体で形成しているため、機械的シャッタと遮光膜との間に電界が生じることを回避して、機械的シャッタの動作マージンを損なうことなく高コントラストを実現し得る理想的な遮光膜を実現できる。

【0039】

本実施形態では極性反転駆動に伴う制御電極25、27の駆動が、前述のように交流化され、互いに打ち消しあっているため、特にEMI(Electro−Magnetic Interference)が少ないという特徴を有する。この特徴によって、ガラス基板36に設けられているタッチパネル30のセンス電極40に対する飛込みノイズを抑制することができ、特に感度の良いタッチパネル特性を実現することができる。本実施形態においても容量線11とシャッタ電圧書込み用ソース電圧線12は交流化できていないが、これらの波形が制御するシャッタ電圧書込み用トランジスタ3を介したシャッタ電極26への書込み駆動は元々時定数が大きい。従って書込み駆動回路16による容量線11とシャッタ電圧書込み用ソース電圧線12の駆動時定数を十分に大きく設定することで、容量線11とシャッタ電圧書込み用ソース電圧線12に起因するEMIの抑制は可能である。

【0040】

また、本実施形態においては制御電極線8A、8Bの印加電圧の入れ替わりによって極性反転駆動を実現しているが、一般に制御電極線8A、8Bに接続される制御電極25、27は、シャッタ電極26と比較して寄生容量が小さくなる。本実施形態においては極性反転駆動を行う際にシャッタ電極26を制御する必要がないため、この観点からも本実施形態には極性反転駆動時の消費電力やEMIを抑制できるという長所があることが判る。

【0041】

また、本実施形態においては、走査スイッチ5及びシャッタ電圧書込み用トランジスタ3のオンする期間は、それぞれ当該画素が走査線10によって選択された期間及びシャッタ電極26への信号電圧書込み期間である[タイミングt2からt4まで]の期間に限定される。これによって、これらのアモルファスシリコン薄膜トランジスタのオン期間が長時間継続することに起因するしきい値電圧のシフトを、十分に回避することが可能であるという特長を有する。

【0042】

なお、本実施形態に開示した技術は、本発明の趣旨を損なわない範囲で、様々な変更が可能である。本実施形態ではガラス基板36上に走査スイッチ5とシャッタ電圧書込み用トランジスタ3をn型のアモルファスシリコン薄膜トランジスタで設けているが、ガラス基板36に変えて耐熱プラスチック基板等を用いることで基板に曲げに対するフレキシビリティを持たせることが可能である。またn型のアモルファスシリコン薄膜トランジスタに変えて、より低電圧で動作が可能なn型やp型の多結晶シリコン薄膜トランジスタを用いることで、画像信号電圧書込み回路14から信号線6A及び6Bに出力する画像信号電圧の振幅を5V以下に下げて低消費電力化を図ることができる。なおp型薄膜トランジスタを用いた際には、これらに印加する電圧関係の正負を逆にする必要があることは言うまでも無い。或いはまたn型のアモルファスシリコン薄膜トランジスタに変えて、InGaZnOに代表されるアモルファス酸化物薄膜トランジスタを用いることでも、同様に画像信号電圧の振幅を5V以下に下げて低消費電力化を図ることができ、かつ多結晶シリコン薄膜トランジスタと比較してプロセス装置コストを低減することができる。なお、n型薄膜トランジスタをp型薄膜トランジスタに変更した場合には、接続されるソースとドレインが入れ替わるのは勿論である。

【0043】

また、本実施形態では黒色樹脂膜24として、ポリイミド樹脂等にカーボンブラック、チタンブラック等の顔料粒子を適切に分散させたものを用いたが、黒色樹脂膜としてはこれに限るものではない。シャッタ電極26への電界の影響を回避するために誘電体であれば良く、更に反射膜23を透過する光の波長特性によっては黒色である必要もない。例えば反射膜23を透過する光に含まれている青色が実質的に無視できる量であれば、黒色樹脂膜24に替えて青色樹脂層で良いし、反射膜23を透過する光が実質的に赤以外は無視できる量であれば、黒色樹脂膜24に替えてシアン色樹脂層でも良い。また反射膜23への入射光の角度が適切な範囲を超えないように導光板22全体を光学設計できた場合、或いは必要な入射角度全域で反射膜の全反射特性を十分に確保できた場合には、黒色樹脂膜24そのものが不要になる。

【0044】

また、本実施形態ではシャッタ電極26側の反射膜23は多層誘電膜を用いて構成したが、反射膜23に必要な特性は、シャッタ電極26への電界の影響を回避するために誘電体であって、かつ光源42から発生し、導光板22側から照射されたR(赤)G(緑)B(青)の3色の光からなる光を高効率で反射することであるため、このような特性を満足すれば必ずしも多層誘電膜に限るものではない。また反射膜23における反射は鏡面反射に限られるものではなく、反射膜23は拡散反射特性を有する膜でも良いことから、白色樹脂材料等を用いて作成することも可能である。

【0045】

なお、本実施形態ではシャッタ電極26の極性反転駆動を列毎に行ったが、制御電極線8A、8Bを適切に各画素内に配置すれば、極性反転駆動は必ずしも列毎に行わなくとも、例えば行毎、或いは格子ドット毎等で行うことも可能である。またシャッタ電極26、制御電極25、27の電極表面の絶縁膜が十分な電気的安定性を有していれば、極性反転駆動自体を行わなくとも良い。

【0046】

[第2実施形態]

以下、図8、9を用いて、本発明の第2実施形態について順次説明する。第2実施形態に係る画像表示装置のシステム構成と動作、表示パネルの構成と動作、画素の構成及び動作等は既に説明した第1実施形態のそれらと同様であるため、ここではその説明は省略し、特に両者で異なる内容に関して述べることにする。

【0047】

図8は第2実施形態に係る画像表示装置における、表示領域内の画素配列構成図である。表示領域内には画素13R、13G、13Bがマトリクス状に設けられており、列方向に配列された画素13R、13G、13Bはそれぞれ、R(赤)G(緑)B(青)の各色に発光する。

【0048】

次に第2実施形態の画素部断面構造について説明する。図9は第2実施形態の画素13Rに関する画素断面構造図である。本画素断面構造図の構成及び動作は基本的には図4で説明した第1実施形態と同様であるが、第2実施形態の画素13Rでは、反射膜50はR(赤)を全反射する多層誘電膜50R、G(緑)を全反射する多層誘電膜50G、B(青)を全反射する多層誘電膜50Bの積層で構成されている。またR(赤)G(緑)B(青)の3色の独立LED光源からなる光源42に替えて、W(白)色のLED光源を有する光源52が設けられている。

【0049】

更に反射膜50の開口部にはR(赤)を全反射する多層誘電膜50Rは設けられておらず、G(緑)を全反射する多層誘電膜50G、及びB(青)を全反射する多層誘電膜50Bの積層構造からなるR(赤)色カラーフィルタ51が設けられている。これによって本第2実施形態の画素13RではR(赤)の発光を行うが、G(緑)とB(青)の光はR(赤)色カラーフィルタ51によって再度導光板22方向に反射、リサイクルされるという特徴を有している。

【0050】

また、同様に画素13Gでは、反射膜50の開口部にはG(緑)を全反射する多層誘電膜50Gは設けられておらず、B(青)を全反射する多層誘電膜50B、及びR(赤)を全反射する多層誘電膜50Rの積層構造からなるG(緑)色カラーフィルタが設けられている。これによって画素13GではG(緑)の発光を行うが、B(青)とR(赤)の光はG(緑)色カラーフィルタによって再度導光板22方向に反射、リサイクルされる。

【0051】

同様に画素13Bでは、反射膜50の開口部にはB(青)を全反射する多層誘電膜50Bは設けられておらず、R(赤)を全反射する多層誘電膜50R、及びG(緑)を全反射する多層誘電膜50Gの積層構造からなるB(青)色カラーフィルタが設けられている。これによって画素13BではB(青)の発光を行うが、R(赤)とG(緑)の光はB(青)色カラーフィルタによって再度導光板22方向に反射、リサイクルされる。

【0052】

本第2実施形態では、上記のようにW(白)色のLED光源を有する光源52が設けられ、また各画素が画素13R、13G、13Bの3色に分かれているため、カラー表示にFSC方式ではなく、白色発光+カラーフィルタ方式を用いることができる。第2実施形態ではこれによって、FSC方式で問題となる色分解(Color break-up)を完全に回避することができる。なおこのとき各画素に設けられたダイクロイックカラーフィルタは選択透過波長以外の波長の光を導光板22方向に反射、リサイクルするため、一般のカラーフィルタを用いた場合のような光吸収による光の損失が無く、低消費電力化を図ることができる。またR(赤)G(緑)B(青)の3色の独立LED光源からなる光源42に変えて、一般のTV等にも通常用いられているW(白)色のLED光源を有する光源52を使用するため、LED光源部品の低コスト化を図ることができる。W(白)色のLED光源は青色LEDと黄色蛍光体で構成できるために材料費が安く、更に大量生産による量産効果も期待できるからである。

【0053】

また、本実施形態においても、第1実施形態と同様に、画素内の配線を減少させることができ、量産上の歩留りを上げると共に、低コスト化を図ることができる。また、遮光膜を誘電体で形成しているため、機械的シャッタと遮光膜との間に電界が生じることを回避して、機械的シャッタの動作マージンを損なうことなく高コントラストを実現できる。

【0054】

[第3実施形態]

以下、図10を用いて、本発明の第3実施形態について順次説明する。本第3実施形態に係る画像表示装置のシステム構成と動作、表示パネルの構成と動作、画素の構成及び動作等は既に説明した第1実施形態のそれらと同様であるため、ここではその説明は省略し、特に両者で異なる内容に関して述べることにする。

【0055】

図10は、第3実施形態の画素13に関する画素断面構造図である。本画素断面構造図の構成及び動作は基本的には図4で説明した第1実施形態と同様であるが、第3実施形態の画素13では、反射膜23と黒色樹脂膜24は透明保護膜60で覆われている点が異なっている。この透明保護膜60としては、有機ないし無機の保護膜を用いることができる。

【0056】

本第3実施形態ではこの透明保護膜60を用いることによって、可動するシャッタ電極26が透明保護膜60に接触しても異物が生成することを防止することができ、結果的にシャッタ電極26と反射膜23及び黒色樹脂膜24との距離を短く設計することができる。シャッタ電極26が閉状態の際には、反射膜23及び黒色樹脂膜24の開口はシャッタ電極26で十分に遮光しないと光漏れによってコントラストが低下するため、このようにシャッタ電極26と反射膜23及び黒色樹脂膜24との距離を短く設計することで、第3実施形態では実質的にコントラストの向上を図ることができる。

【0057】

本実施形態においても、第1実施形態と同様に、画素内の配線を減少させることができ、量産上の歩留りを上げると共に、低コスト化を図ることができる。また、遮光膜を誘電体で形成しているため、機械的シャッタと遮光膜との間に電界が生じることを回避して、機械的シャッタの動作マージンを損なうことなく高コントラストを実現できる。

【0058】

[第4実施形態]

以下、図11を用いて、本発明の第4実施形態について順次説明する。第4実施形態に係る画像表示装置のシステム構成と動作、表示パネルの構成と動作、画素の構成及び動作等は既に説明した第1実施形態のそれらと同様であるため、ここではその説明は省略し、特に両者で異なる内容に関して述べることにする。

【0059】

図11は、第4実施形態である、機械的シャッタを用いた画像表示装置のシャッタ制御回路を示す図である。第1実施形態における画素13と、第4実施形態における画素73との差異は、シャッタ電圧書込み用トランジスタ3のドレインが双極性シャッタ1のシャッタ電極26に接続されているのに加えて、新たに双極性シャッタ1の制御電極25、27との間にそれぞれ補助容量70、71が設けられていることである。

【0060】

第1実施形態で述べたようにシャッタ電極26は、シャッタ電極26と制御電極25、27が生じる電界の効果によってその位置が制御されるが、シャッタ電極26の位置が制御電極25、27のいずれかの側で安定するまでは、シャッタ電極26に必要な電荷を供給し続けることが望ましい。シャッタ電極26と制御電極25、27の間には必ず寄生容量が形成されるが、この寄生容量の値はシャッタ電極26が移動し、シャッタ電極26と制御電極25或いは制御電極27との間隔が狭まることによって増加する。ここでシャッタ電極26と制御電極25或いは制御電極27との間のある距離での寄生容量をC、その後のシャッタ電極26の位置変動に起因する寄生容量の増分をΔC、電圧をV、この距離でこの寄生容量に蓄えられる電荷をQ、その後のシャッタ電極26の位置変動に起因する電荷の増分をΔQとすると、下記の式(1)が成立する。

(Q+ΔQ)=(C+ΔC)×V ・・・・・・・・ (1)

【0061】

従って、シャッタ電極26と制御電極25或いは制御電極27との間の電圧Vを一定に保つためには、寄生容量Cの値の増加分ΔCに相当する電荷ΔQの供給が必要になる。

【0062】

このことはシャッタ電極26の位置が安定点に落ち着くまでは、シャッタ電圧書込み用トランジスタ3はオンし続ける必要のあることを意味する。しかしながらこの場合には図5に記載した[タイミングt2からt3まで]及び[タイミングt3からt4まで]の期間を十分に長く確保することになり、[タイミングt1まで]及び[タイミングt4以降]である画素に対する画像信号電圧の書込み期間が短くなることになってしまう。特に列方向に画素数の大きいディスプレイを設計する必要のある場合には、この制約は非常に厳しいものとなる。

【0063】

これに対して第4実施形態は、新たに双極性シャッタ1のシャッタ電極26と制御電極25、27との間にそれぞれ補助容量70、71を設けることで、補助容量70、71から上記寄生容量に電荷を供給できるようにして、シャッタ電極26における上記寄生容量の影響を緩和したものである。

【0064】

これによって第4実施形態は、シャッタ電極26の位置が安定点に完全に落ち着く前にシャッタ電圧書込み用トランジスタ3をオフしても、上記寄生容量の増加に起因するシャッタ電極26と制御電極25、27との間の電圧変動を十分に抑制することが可能である。これによって図5に記載した[タイミングt2からt3まで]及び[タイミングt3からt4まで]の期間を十分に長く確保しなくとも良く、[タイミングt1まで]及び[タイミングt4以降]である画素に対する画像信号電圧の書込み期間を十分に確保することができる。これにより特に列方向に画素数の大きいディスプレイを設計する場合には走査回路15の駆動クロックを低減することができ、回路設計マージンの確保による歩留りの向上や、消費電力の削減を図る上で大きな利点となる。

【0065】

なお、第4実施形態では補助容量70、71の値はそれぞれ200fFに設計したが、前述した効果からは例えば10fF以上が望ましい。またここでは補助容量70、71は等しい値に設けているが、これは図5の[タイミングt1からt2まで]の期間に、シャッタ電極26の極性反転駆動を目的として毎フレーム毎に奇数画素列と偶数画素列に相当する制御電極線8A、8Bの印加電圧の入れ替わりが行われる際の制御電極線8A、8Bの電圧変動が、補助容量70、71のカップリングを通じてシャッタ電極26へ影響することを互いにキャンセルするためである。しかしながらこのカップリング効果が問題とならないような場合には、補助容量70、71の値を非対称にしても、或いはいずれか一方のみを設けても、第4実施形態に準じた効果が得られることは明らかである。

【0066】

本実施形態においても、第1実施形態と同様に、画素内の配線を減少させることができ、量産上の歩留りを上げると共に、低コスト化を図ることができる。また、遮光膜を誘電体で形成しているため、機械的シャッタと遮光膜との間に電界が生じることを回避して、機械的シャッタの動作マージンを損なうことなく高コントラストを実現できる。

【0067】

[第5実施形態]

以下、図12〜図15を用いて、本発明の第5実施形態について、その構成および動作を順次説明する。

【0068】

図12は、第5実施形態に係る画像表示装置の画素周辺回路図である。マトリクス状に配列された画素85が表示領域を構成しており、画素85には列方向に信号線6A及び6Bと、制御電極線8A及び8Bが、行方向に走査線10、容量線11、シャッタ電圧書込み用ソース電圧線12、及びCMOSシャッタ電圧書込み用pMOSソース電圧線84が設けられている。表示領域の周辺で、信号線6A及び6Bの一端は画像信号電圧書込み回路14に接続されており、制御電極線8A及び8Bの一端はそれぞれ制御電極駆動回路17に接続されている。また走査線10の一端は走査回路15に接続されており、容量線11、シャッタ電圧書込み用ソース電圧線12及びCMOSシャッタ電圧書込み用pMOSソース電圧線84の一端は、それぞれ書込み駆動回路86に接続されている。

【0069】

ここでCMOSシャッタ電圧書込み用pMOSソース電圧線84には、書込み駆動回路86から常時Vh(後述のように例えば15(V))が入力される。なお、図12は簡単のために表示領域を画素数が4×3画素のマトリクスで記載しているが、本発明の開示する技術思想が特に画素数を制限するものではない。

【0070】

図13には、図12の各画素85におけるシャッタ制御回路87が示されている。各画素85には信号線6Aが設けられており、信号線6Aと信号蓄積容量4とは走査スイッチ5で接続されている。信号蓄積容量4は更にCMOS書込み用トランジスタ80のゲートに接続されており、CMOS書込み用トランジスタ80のドレインはCMOS信号蓄積容量81の一端に接続されている。また更にCMOS書込み用トランジスタ80のドレインは、CMOSシャッタ電圧書込み用nMOSトランジスタ83及びCMOSシャッタ電圧書込み用pMOSトランジスタ82のゲートにも接続される。更にCMOSシャッタ電圧書込み用nMOSトランジスタ83及びCMOSシャッタ電圧書込み用pMOSトランジスタ82のドレインは双極性シャッタ1のシャッタ電極26に接続されている。即ちこれによって、CMOSシャッタ電圧書込み用nMOSトランジスタ83及びCMOSシャッタ電圧書込み用pMOSトランジスタ82は画素内にCMOSインバータ回路を構成している。二つある双極性シャッタ1の制御電極の内の一方は画素内の制御電極線8Aに接続されているが、制御電極の他方は隣接する画素の制御電極線8Bに接続されている。なお信号蓄積容量4の他端は容量線11に接続されており、CMOS信号蓄積容量81の他端は制御電極線8Bに、CMOS書込み用トランジスタ80のソースはシャッタ電圧書込み用ソース電圧線12に、CMOSシャッタ電圧書込み用nMOSトランジスタ83及びCMOSシャッタ電圧書込み用pMOSトランジスタ82のソースはそれぞれ容量線11及びCMOSシャッタ電圧書込み用pMOSソース電圧線84に、走査スイッチ5のゲートは走査線10に接続されている。なお上記の双極性シャッタ1が遮光面上に設けられた開口に対向して設けられていること等の立体的な画素構造は、基本的に第1実施形態と同様である。なお図13には信号線6Aと制御電極線8Aを有する画素と、信号線6Bと制御電極線8Bを有する画素の、2画素分が記載されている。両画素は後述のように駆動条件は異なるものの、基本的なシャッタ制御回路は同一である。

【0071】

図14は、第5実施形態の画素部断面構造図である。ガラス基板36上には、低不純物濃度低温多結晶シリコン薄膜91、高濃度n型不純物をドープした低温多結晶シリコン薄膜92、90、ゲート絶縁膜93、ゲート電極95、層間絶縁膜94、ソース電極96、ドレイン電極97とから構成される低温多結晶シリコン薄膜トランジスタが設けられており、これはCMOSシャッタ電圧書込み用nMOSトランジスタ83に対応している。更にガラス基板36上には、ソース電極96、ドレイン電極97と同じAl配線層で制御電極線8A、8Bが形成されており、これらはシリコンナイトライドと有機材料の多層膜からなる保護膜37によって覆われている。

【0072】

保護膜37上には、シャッタ電極26と、二つの制御電極25、27を有する双極性シャッタ1が設けられており、ドレイン電極97はシャッタ電極26に、制御電極線8Aは制御電極25に、制御電極線8Bは制御電極27に、それぞれコンタクトホールを介して接続されている。またこれらシャッタ電極26と、二つの制御電極25、27には互いに接触した際の短絡防止のために、表面には絶縁膜が形成されている。なおここでシャッタ電極26は、シャッタ電極26に入力される電圧と、二つの制御電極25、27に入力される電圧との相対関係による電界でその位置が制御されるため、図14には破線を用いてその可動範囲も開示している。なお図14には記載されていないが、画素85内に設けられたその他のトランジスタも、同様に低温多結晶シリコン薄膜トランジスタで構成されている。

【0073】

シャッタ電極26に対してガラス基板36と反対側には、R(赤)G(緑)B(青)の3色の独立LED光源からなる光源42を有する導光板22が設けられている。導光板22の両面には反射膜21、23が設けられているが、ここで特にシャッタ電極26側の反射膜23は多層誘電膜より構成されている。反射膜23を構成する多層誘電膜はTiO2、Ta2O3等の高屈折率材料とSiO2、MgF2等の低屈折材料の積層構造からなっており、これらの積層構造の各膜厚を適切な値に設計することによって、光源42が有するR(赤)G(緑)B(青)の3色の独立LED光源の射出光に対して実用上十分な全反射特性を得ることができる。ところで多層誘電膜を全反射膜として用いた場合の課題は、垂直方向に入射する光に対して最適設計した場合に、水平に近い角度で入射した光に対しては反射特性が悪化することである。反射膜23が光を透過した場合には表示装置の光漏れとなってしまい、コントラストの著しい低下を招いてしまう。そこでこのような光漏れを防止するために、更に反射膜23の上には有機材料で作成された黒色樹脂膜24を形成した。この黒色樹脂膜は、ポリイミド樹脂等にカーボンブラック、チタンブラック等の顔料粒子を適切に分散させることで形成することができる。ここで反射膜23及び黒色樹脂膜24には図14に示すように、シャッタ電極26に対応する位置に開口が設けられており、光源42から射出されて導光板22を伝播した光41の一部が、この開口から射出されるように構成されている。開口は例えば、黒色樹脂膜24をマスクとしたフォトリソグラフィーによって一括加工形成することができる。

【0074】

ガラス基板36に対して導光板22と反対側には、フィルムシート38、センス電極40、保護膜39からなるタッチパネル30が設けられている。タッチパネル30のセンス電極40は表示領域の周辺でタッチ検出用回路に接続されているが、この部分の構成は既に一般に知られている技術であるため、ここではその詳細な説明は省略する。

【0075】

次に、図15を用いて、本発明の第5実施形態の動作を説明する。まず、図13で述べた第5実施形態のシャッタ制御回路87の動作について説明する。

【0076】

図15は、第5実施形態のシャッタ制御回路87の動作タイミングチャートであり、横軸に時間を取って、縦軸に各部分の電圧を示したものである。また特に下2段に記載したCMOS信号蓄積容量81の蓄積信号電圧(=CMOSインバータ回路入力電圧)及び双極性シャッタ1のシャッタ電極26の電圧値に関しては、画像信号によって約0(V)と約Vhの二値を取るため、図面を判り易くするために基本的に約0(V)を実線、約Vhを破線で示している。

【0077】

[タイミングt1まで]

この期間には、画素に対する画像信号電圧の書込みが行われている。この期間は制御電極線8A、8Bにはそれぞれ高電圧Vh、低電圧0(V)が印加されているが、後述するようにシャッタ電極26の極性反転駆動を目的として、奇数画素列と偶数画素列に相当する制御電極線8A、8Bの印加電圧は毎フレーム毎にその値が入れ替わる。各画素の走査スイッチ5は走査線10によって順次走査されており、走査スイッチ5が走査された画素の信号蓄積容量4には、信号線6A、6Bから所定の画像信号電圧が書込まれる。ここで信号線6A、6Bに印加される画像信号電圧は例えば4(V)と0(V)の二値をとるが、白表示時と黒表示時にそれぞれ4(V)と0(V)のいずれに該当するかは、シャッタ電極26の極性反転駆動を目的とした制御電極線8A、8Bの印加電圧の毎フレーム毎の値によって、信号線6A及び6Bの列毎に入れ替わる。なお容量線11には0(V)、シャッタ電圧書込み用ソース電圧線12にはVmが印加されており、双極性シャッタ1のシャッタ電極26には約0(V)ないし約Vhが印加されている。なおここでVhの値は双極性シャッタ1の静電的な機械駆動が可能な最小の電圧に設計されるが、例えばこの値は15(V)である。またVmの値は信号電圧が信号蓄積容量4に書込まれてもCMOS書込み用トランジスタ80がオンすることのない値であり、例えば4(V)である。なお第1実施形態と比較して、第5実施形態の画像信号電圧は4(V)と低い値をとるが、これはCMOS書込み用トランジスタ80が書込む容量がCMOS信号蓄積容量81の約20fFとCMOSシャッタ電圧書込み用nMOSトランジスタ83及びCMOSシャッタ電圧書込み用pMOSトランジスタ82のゲート容量の和であって、比較的小さい値であることと、走査スイッチ5とCMOS書込み用トランジスタ80が電流駆動力の大きい低温多結晶シリコン薄膜トランジスタで構成されていることに起因する。

【0078】

[タイミングt1からt2まで]

この期間にはシャッタ電極26の極性反転駆動を目的として、毎フレーム毎に奇数画素列と偶数画素列に相当する制御電極線8A、8Bの印加電圧の入れ替わりが行われる。本実施形態は後述するように光源42の発光にサブフィールド毎に時間重みを持たせて、シャッタ電極26の開閉で外部への発光を制御するPWM駆動を行うが、制御電極線8A、8Bの印加電圧の入れ替えはフレーム毎に替えて、サブフィールド毎や、複数サブフィールド毎に行っても良い。制御電極線8A、8Bの印加電圧の入れ替えを行わないサブフィールドでは、この[タイミングt1からt2まで]の期間は設ける必要はない。制御電極線8A、8Bの印加電圧の入れ替えを頻繁に行うと、これに伴うタイミングt1からt2までの遷移期間を頻繁に設ける必要があることと、消費電力が増加することには留意する必要がある。

【0079】

[タイミングt2からt13まで]

この期間には信号蓄積容量4に書込まれた画像信号電圧に基づいて、全画素において一斉にCMOS信号蓄積容量81への信号電圧書込みが行われる。

【0080】

容量線11とシャッタ電圧書込み用ソース電圧線12に同時にVhが書込まれ、この後に両者の電圧は揃って0(V)に立ち下げられる。この動作によってCMOS書込み用トランジスタ80が制御され、信号蓄積容量4に書込まれていた画像信号電圧が0(V)の場合にはCMOS信号蓄積容量81には信号電圧として(Vh−Vth)が書込まれ、画像信号電圧が4(V)だった場合にはCMOS信号蓄積容量81には信号電圧として0(V)が書込まれる。なおここでVthは、CMOS書込み用トランジスタ80のしきい値電圧である。

【0081】

上記のCMOS信号蓄積容量81への信号電圧書込みについては、既に第1実施形態で図6A〜図7Cを用いて詳細に説明した擬似ダイオード回路の動作であるので、ここではその説明は省略する。

【0082】

[タイミングt13からt14まで]

この期間には容量線11とシャッタ電圧書込み用ソース電圧線12は0(V)に立ち下げられた電圧値を維持し、CMOS信号蓄積容量81へ書込まれた信号電圧は、そのままCMOSシャッタ電圧書込み用nMOSトランジスタ83及びCMOSシャッタ電圧書込み用pMOSトランジスタ82のゲートに入力される。前述のようにCMOSシャッタ電圧書込み用pMOSソース電圧線84には、書込み駆動回路86から常時Vh(例えば15(V))が入力されるため、このときCMOSシャッタ電圧書込み用nMOSトランジスタ83及びCMOSシャッタ電圧書込み用pMOSトランジスタ82はCMOSインバータ回路として機能する。従ってCMOS信号蓄積容量81には信号電圧として(Vh−Vth)が書込まれている場合には、CMOSインバータ回路はシャッタ電極26に0(V)を出力し、CMOS信号蓄積容量81に信号電圧として0(V)が書込まれている場合には、CMOSインバータ回路はシャッタ電極26にVh(例えば15(V))を出力する。

【0083】

[タイミングt14以降]

この期間は再びタイミングt1までの動作と同様に、画素に対する画像信号電圧の書込みが行われる。各画素の走査スイッチ5は走査線10によって順次走査され、走査スイッチ5が走査された画素の信号蓄積容量4には、信号線6A、6Bから所定の画像信号電圧が書込まれる。シャッタ電圧書込み用ソース電圧線12にはVm(例えば4(V))が印加されており、信号電圧が信号蓄積容量4に書込まれても基本的にはCMOS書込み用トランジスタ80がオンすることはない。ここで本実施形態においては、[タイミングt13からt14まで]と同様にCMOSシャッタ電圧書込み用nMOSトランジスタ83及びCMOSシャッタ電圧書込み用pMOSトランジスタ82がCMOSインバータ回路として機能し続けるため、シャッタ電極26への信号電圧の書込みと、画素に対する画像信号電圧の書込み走査を並行して行えるという利点がある。

【0084】

なおここでも第1実施形態と同様に、CMOS信号蓄積容量81に0(V)が書込まれており、信号蓄積容量4に4(V)(VsigH)が書込まれている場合には、CMOS信号蓄積容量81の電圧はCMOS書込み用トランジスタ80のオフする電圧である4(V)−Vth(VsigH−Vth)まで、この期間に再度上昇する。基本的にCMOSシャッタ電圧書込み用nMOSトランジスタ83及びCMOSシャッタ電圧書込み用pMOSトランジスタ82で構成されるCMOSインバータ回路は二値駆動であるため、0(V)が4(V)−Vth(VsigH−Vth)に上昇しても動作そのものには支障はないが、これによってCMOSインバータを流れる貫通電流が増えて消費電力が増加する点には留意する必要がある。ここでVsigHは高い電圧である方がCMOS書込み用トランジスタ80によるCMOS信号蓄積容量81への書込み動作はより高速化できるという長所がある。しかしその一方で、画像信号電圧書込み回路14から信号線6A及び6BにVsigHを書込む際の消費電力が上昇する点や、上記のような副作用も有しているため、本実施形態では4(V)としたVsigHの電圧値は、これらを勘案した上で最適に設定する必要がある。

【0085】

次に図13で述べた本第5実施形態の画素周辺回路の動作について説明する。

【0086】

前述の[タイミングt1まで]に相当する画素に対する画像信号電圧の書込み期間においては、走査線10は走査回路15によって順次走査され、これと同期して信号線6A及び6Bには画像信号電圧書込み回路14から画像信号電圧が書込まれる。ここで前述のように本実施形態は光源42の発光にサブフィールド毎に時間重みを持たせて、シャッタ電極26の開閉で外部への発光を制御するPWM駆動を行う。このため画像信号電圧書込み回路14から信号線6A及び6Bに書込まれる画像信号電圧は、例えば0(V)と4(V)の二値の電圧であり、これによって各画素に設けられたシャッタ電極26に印加される信号電圧を制御する。なお白表示時と黒表示時にそれぞれ4(V)と0(V)のいずれに該当するかは、シャッタ電極26の極性反転駆動を目的とした制御電極線8A、8Bの印加電圧の毎フレーム毎の値によって、信号線6A及び6Bの列毎に入れ替わることは既に述べたとおりである。次に全画素に対する画像信号電圧の書込みが終了した後、前述の[タイミングt1からt2まで]の期間において、シャッタ電極26の極性反転駆動を目的として、フレーム毎に奇数画素列と偶数画素列に相当する制御電極線8A、8Bの印加電圧が制御電極駆動回路17によって相補的に駆動されることは既に述べたとおりである。また引続き行われる[タイミングt2からt3まで]における、信号蓄積容量4に書込まれた画像信号電圧に基づいた、全画素におけるCMOS信号蓄積容量81への信号電圧書込みは、書込み駆動回路86が容量線11、シャッタ電圧書込み用ソース電圧線12を一斉に駆動することによって行われる。その後の[タイミングt4以降]において、シャッタ電圧書込み用ソース電圧線12へのVm印加を行うのも書込み駆動回路86である。なおCMOSシャッタ電圧書込み用pMOSソース電圧線84に常時Vh(例えば15(V))を入力するのも書込み駆動回路86である。

【0087】

最後に図14で述べた第5実施形態のシャッタ電極26近傍構造の動作については、トランジスタの構造とVhの電圧値に関しては異なるものの、基本的な動作に関しては既に第1実施形態で述べたものと同じであるため、ここではこれ以上の説明は省略する。

【0088】

既に述べたように第5実施形態においては、[タイミングt13からt14まで]と同様に[タイミングt14以降]においても、CMOSシャッタ電圧書込み用nMOSトランジスタ83及びCMOSシャッタ電圧書込み用pMOSトランジスタ82がCMOSインバータ回路として機能し続けるため、シャッタ電極26への信号電圧の書込みと、画素に対する画像信号電圧の書込み走査を並行して行えるという利点がある。これによって本実施形態は、特に列方向に画素数の大きいディスプレイを設計する場合には走査回路15の駆動クロックを低減することができ、回路設計マージンの確保による歩留りの向上や、消費電力の削減を図る上で大きな利点となる。

【0089】

本実施形態においても、第1実施形態と同様に、画素内の配線を減少させることができ、量産上の歩留りを上げると共に、低コスト化を図ることができる。また、遮光膜を誘電体で形成しているため、機械的シャッタと遮光膜との間に電界が生じることを回避して、機械的シャッタの動作マージンを損なうことなく高コントラストを実現できる。

【0090】

[第6実施形態]

以下図16〜図18を用いて、本発明の第6実施形態について、その構成および動作を順次説明する。第6実施形態に係る画像表示装置のシステム構成と動作、表示パネルの構成と動作、画素の構成及び動作等は既に説明した第1実施形態のそれらと同様であるため、ここではその説明は省略し、特に両者で異なる内容に関して述べることにする。

【0091】

図16は第6実施形態の画素周辺回路図である。マトリクス状に配列された画素105が表示領域を構成しており、画素105には列方向に信号線6A及び6Bと、制御電極線8A及び8Bが、行方向に走査線10、容量線11、シャッタ電圧書込み用ソース電圧線12、次段シャッタ電圧書込み用ソース電圧線104が設けられている。表示領域の周辺で、信号線6A及び6Bの一端は画像信号電圧書込み回路14に接続されており、制御電極線8A及び8Bの一端はそれぞれ制御電極駆動回路17に接続されている。また走査線10の一端は走査回路15に接続されており、容量線11、シャッタ電圧書込み用ソース電圧線12、次段シャッタ電圧書込み用ソース電圧線104の一端は、それぞれ書込み駆動回路106に接続されている。なお図16は簡単のために表示領域を画素数が4×3画素のマトリクスで記載しているが、本発明の開示する技術思想が特に画素数を制限するものではない。

【0092】

図17は、第6実施形態のシャッタ制御回路107を示す図である。各画素105には信号線6Aが設けられており、信号線6Aと信号蓄積容量4とは走査スイッチ5で接続されている。信号蓄積容量4は更に次段書込み用トランジスタ100のゲートに接続されており、次段書込み用トランジスタ100のドレインは次段信号蓄積容量101の一端に接続されている。また更に次段書込み用トランジスタ100のドレインは、次段シャッタ電圧書込み用トランジスタ102のゲートにも接続される。更に次段シャッタ電圧書込み用トランジスタ102のドレインは双極性シャッタ1のシャッタ電極26に接続されている。即ちこれによって、信号蓄積容量4と次段書込み用トランジスタ100同様に、次段信号蓄積容量101と次段シャッタ電圧書込み用トランジスタ102は、画素内に2個目の擬似ダイオード回路を構成している。二つある双極性シャッタ1の制御電極の内の一方は画素内の制御電極線8Aに接続されているが、制御電極の他方は隣接する画素の制御電極線8Bに接続されている。なお信号蓄積容量4の他端は容量線11に接続されており、次段書込み用トランジスタ100のソースはシャッタ電圧書込み用ソース電圧線12に、次段信号蓄積容量101の他端と次段シャッタ電圧書込み用トランジスタ102のソースは次段シャッタ電圧書込み用ソース電圧線104に、走査スイッチ5のゲートは走査線10に接続されている。なお上記の双極性シャッタ1が遮光面上に設けられた開口に対向して設けられていること等の立体的な画素構造は、基本的に第1実施形態と同様である。なお図17には信号線6Aと制御電極線8Aを有する画素と、信号線6Bと制御電極線8Bを有する画素の、2画素分が記載されている。両画素は後述のように駆動条件は異なるものの、基本的なシャッタ制御回路は同一である。

【0093】

次に第6実施形態の画素部断面構造は、既に述べた第1実施形態の画素部断面構造と同様であるので、ここではその説明は省略する。

【0094】

次に図18を用いて、第6実施形態のシャッタ制御回路107の動作について説明する。図18は第6実施形態のシャッタ制御回路107の動作タイミングチャートであり、横軸に時間を取って、縦軸に各部分の電圧を示したものである。また特に次段シャッタ電圧書込み用トランジスタ102のゲート入力電圧と、最下段に記載した双極性シャッタ1のシャッタ電極26の電圧値に関しては、画像信号によって約Vm2と約Vhの二値を取るため、図面を判り易くするために前者を実線、後者を破線で示している。

【0095】

[タイミングt1まで]

この期間には、画素に対する画像信号電圧の書込みが行われている。この期間は制御電極線8A、8Bにはそれぞれ高電圧Vh、低電圧Vm2(例えば7(V))が印加されているが、後述するようにシャッタ電極26の極性反転駆動を目的として、奇数画素列と偶数画素列に相当する制御電極線8A、8Bの印加電圧は毎フレーム毎にその値が入れ替わる。各画素の走査スイッチ5は走査線10によって順次走査されており、走査スイッチ5が走査された画素の信号蓄積容量4には、信号線6A、6Bから所定の画像信号電圧が書込まれる。ここで信号線6A、6Bに印加される画像信号電圧は例えば7(V)と0(V)の二値をとるが、白表示時と黒表示時にそれぞれ7(V)と0(V)のいずれに該当するかは、シャッタ電極26の極性反転駆動を目的とした制御電極線8A、8Bの印加電圧の毎フレーム毎の値によって、信号線6A及び6Bの列毎に入れ替わる。なお容量線11には0(V)、シャッタ電圧書込み用ソース電圧線12にはVmが印加されており、次段シャッタ電圧書込み用ソース電圧線104にはVm2、次段シャッタ電圧書込み用トランジスタ102のゲートには約0(V)ないし約Vh、双極性シャッタ1のシャッタ電極26には約Vm2ないし約Vhが印加されている。なおここでVhの値は双極性シャッタ1の静電的な機械駆動が可能な最小の電圧に設計されるが、例えばこの値は20(V)である。

【0096】

なお、Vmの値は信号電圧が信号蓄積容量4に書込まれても次段書込み用トランジスタ100がオンすることのない値であり、例えば7(V)である。またVm2の値は、後述するように信号蓄積容量4にVsigH(7(V))が入力することによって、次段書込み用トランジスタ100を介して次段信号蓄積容量101の電圧値が0(V)から(VsigH−Vth)(Vthは次段書込み用トランジスタ100のしきい値電圧である)に上昇したとしても、次段シャッタ電圧書込み用トランジスタ102がオンしてシャッタ電極26に蓄えられたVhの電圧がリークしないように設定された電圧であり、基本的には以下の式(2)を満足する。

(VsigH−Vth)−Vth2 < Vm2 ・・・・・・・・ (2)

なおここでVth2は、次段シャッタ電圧書込み用トランジスタ102のしきい値電圧である。

【0097】

[タイミングt1からt2まで]

この期間にはシャッタ電極26の極性反転駆動を目的として、毎フレーム毎に奇数画素列と偶数画素列に相当する制御電極線8A、8Bの印加電圧の入れ替わりが行われる。本実施形態は後述するように光源42の発光にサブフィールド毎に時間重みを持たせて、シャッタ電極26の開閉で外部への発光を制御するPWM駆動を行うが、制御電極線8A、8Bの印加電圧の入れ替えはフレーム毎に替えて、サブフィールド毎や、複数サブフィールド毎に行っても良い。制御電極線8A、8Bの印加電圧の入れ替えを行わないサブフィールドでは、この[タイミングt1からt2まで]の期間は設ける必要はない。

制御電極線8A、8Bの印加電圧の入れ替えを頻繁に行うと、これに伴うタイミングt1からt2までの遷移期間を頻繁に設ける必要があることと、消費電力が増加することには留意する必要がある。

【0098】

[タイミングt2からt23まで]

この期間には信号蓄積容量4に書込まれた画像信号電圧に基づいて、全画素において一斉に次段信号蓄積容量101への信号電圧書込みが行われる。次段信号蓄積容量101へ書込まれる信号電圧は、次段シャッタ電圧書込み用トランジスタ102のゲート入力電圧と同じである。

【0099】

容量線11とシャッタ電圧書込み用ソース電圧線12に同時にVhが書込まれ、この後に両者の電圧は揃って0(V)に立ち下げられる。この動作によって次段書込み用トランジスタ100が制御され、信号蓄積容量4に書込まれていた画像信号電圧が0(V)の場合には次段信号蓄積容量101には信号電圧として(Vh−Vth)が書込まれ、画像信号電圧が7(V)だった場合には次段信号蓄積容量101には信号電圧として0(V)が書込まれる。ここでVthは、次段書込み用トランジスタ100のしきい値電圧である。

【0100】

上記の次段信号蓄積容量101への信号電圧書込みについては、既に第1実施形態で図6、図7を用いて詳細に説明した擬似ダイオード回路の動作であるので、ここではその説明は省略する。

【0101】

[タイミングt23からt24まで]

この期間には容量線11とシャッタ電圧書込み用ソース電圧線12は0(V)に立ち下げられた電圧値を維持しており、次段信号蓄積容量101に0(V)が書込まれる場合には、この期間にこの電圧は約0(V)に収束する。

【0102】

[タイミングt24からt25まで]

この期間には次段信号蓄積容量101に書込まれた画像信号電圧に基づいて、全画素において一斉にシャッタ電極26への信号電圧書込みが行われる。

【0103】

次段シャッタ電圧書込み用ソース電圧線104にVhが書込まれ、この後にこの電圧は再びVm2に立ち下げられる。この動作によって次段シャッタ電圧書込み用トランジスタ102が制御され、次段信号蓄積容量101に書込まれていた画像信号電圧が0(V)の場合にはシャッタ電極26には信号電圧として(Vh−Vth2)が書込まれ、画像信号電圧が7(V)だった場合にはシャッタ電極26には信号電圧としてVm2が書込まれる。ここでVth2は、次段シャッタ電圧書込み用トランジスタ102のしきい値電圧である。

【0104】

上記のシャッタ電極26への信号電圧書込みについては、既に述べた擬似ダイオード回路の動作であるので、ここではその説明は省略する。

【0105】

なおこれと並行してこの期間には、再びタイミングt1までの動作と同様に、画素に対する画像信号電圧の書込みが行われる。各画素の走査スイッチ5は走査線10によって順次走査され、走査スイッチ5が走査された画素の信号蓄積容量4には、信号線6A、6Bから所定の画像信号電圧が書込まれる。シャッタ電圧書込み用ソース電圧線12にはVmが印加されており、信号電圧が信号蓄積容量4に書込まれても基本的には次段書込み用トランジスタ100がオンすることはない。

【0106】

[タイミングt25以降]

この期間も継続して、引続き画素に対する画像信号電圧の書込みが行われる。また擬似ダイオード回路の動作によって、シャッタ電極26にVm2の信号電圧が書込まれる場合には、図18に示したようにこの期間の初期に行われる。

【0107】

なお次段信号蓄積容量101に0(V)が書込まれており、信号蓄積容量4に7(V)(VsigH)が書込まれている場合には、次段信号蓄積容量101の電圧が次段書込み用トランジスタ100のオフする電圧である7(V)−Vth(VsigH−Vth)まで、この期間に再度上昇する点は第1実施形態と同様である。このとき次段シャッタ電圧書込み用トランジスタ102がオンしてシャッタ電極26に蓄えられたVhの電圧がリークしないように、次段シャッタ電圧書込み用ソース電圧線104はVm2に設定されており、Vm2の値が式(2)を満足することは、前述したとおりである。

【0108】

次に図16で述べた第6実施形態の画素周辺回路の動作について説明する。

【0109】

前述の[タイミングt1まで]に相当する画素に対する画像信号電圧の書込み期間においては、走査線10は走査回路15によって順次走査され、これと同期して信号線6A及び6Bには画像信号電圧書込み回路14から画像信号電圧が書込まれる。ここで前述のように本実施形態は光源42の発光にサブフィールド毎に時間重みを持たせて、シャッタ電極26の開閉で外部への発光を制御するPWM駆動を行う。このため画像信号電圧書込み回路14から信号線6A及び6Bに書込まれる画像信号電圧は、例えば0(V)と7(V)の二値の電圧であり、これによって各画素に設けられたシャッタ電極26に印加される信号電圧を制御する。なお白表示時と黒表示時にそれぞれ7(V)と0(V)のいずれに該当するかは、シャッタ電極26の極性反転駆動を目的とした制御電極線8A、8Bの印加電圧の毎フレーム毎の値によって、信号線6A及び6Bの列毎に入れ替わることは既に述べたとおりである。次に全画素に対する画像信号電圧の書込みが終了した後、前述の[タイミングt1からt2まで]の期間において、シャッタ電極26の極性反転駆動を目的として、フレーム毎に奇数画素列と偶数画素列に相当する制御電極線8A、8Bの印加電圧が制御電極駆動回路17によって相補的に駆動されることは既に述べたとおりである。また引続き行われる[タイミングt2からt23まで]における、信号蓄積容量4に書込まれた画像信号電圧に基づいた、全画素における次段信号蓄積容量101への信号電圧書込みは、書込み駆動回路106が容量線11、シャッタ電圧書込み用ソース電圧線12を一斉に駆動することによって行われる。その後[タイミングt24からt25まで]において、書込み駆動回路106から次段シャッタ電圧書込み用ソース電圧線104を一斉に駆動してシャッタ電極26への信号電圧書込みが行われると共に、シャッタ電圧書込み用ソース電圧線12へのVm印加が行われる。

【0110】

なお既に述べたように、第6実施形態の画素部断面構造は第1実施形態の画素部断面構造と同様であると同時に、基本的な動作に関しても既に第1実施形態で述べたものと同じであるため、ここではこれ以上の説明は省略する。

【0111】

既に述べたように第6実施形態においては、次段信号蓄積容量101及び次段シャッタ電圧書込み用トランジスタ102が擬似ダイオード回路としてシャッタ電極26への書込みを行うため、[タイミングt24からt25まで]及び[タイミングt25以降]において、シャッタ電極26への信号電圧の書込みと、画素に対する画像信号電圧の書込み走査を並行して行えるという利点がある。次段信号蓄積容量101の容量値はシャッタ電極26の入力容量値と異なってシャッタ電極26の位置にかかわらず一定値をとるため、次段信号蓄積容量101への書込みは、比較的短時間で完了することができる。これによって本実施形態は、特に列方向に画素数の大きいディスプレイを設計する場合には走査回路15の駆動クロックを低減することができ、回路設計マージンの確保による歩留りの向上や、消費電力の削減を図る上で大きな利点となる。

【0112】

本実施形態においても、第1実施形態と同様に、画素内の配線を減少させることができ、量産上の歩留りを上げると共に、低コスト化を図ることができる。また、遮光膜を誘電体で形成しているため、機械的シャッタと遮光膜との間に電界が生じることを回避して、機械的シャッタの動作マージンを損なうことなく高コントラストを実現できる。

【0113】

[第7実施形態]

以下、図19を用いて、本発明における第7実施形態に関して説明する。

【0114】

図19は第7実施形態であるインターネット画像表示装置150の構成図である。無線インターフェース(I/F)回路152には、圧縮された画像データ等が外部から無線データとして入力し、無線I/F回路152の出力はI/O(Input/Output)回路153を介してデータバス158に接続される。データバス158にはこの他にマイクロプロセッサ(MPU)154、表示パネルコントローラ156、フレームメモリ157等が接続されている。更に表示パネルコントローラ156の出力は機械的シャッタを用いた表示装置151に入力している。なおインターネット画像表示装置150には更に、電源159が設けられている。なおここで機械的シャッタを用いた表示装置151は、先に延べた第1実施形態と同一の構成および動作を有しているので、その内部の構成及び動作の記載はここでは省略する。

【0115】

以下に、第7実施形態の動作を説明する。始めに無線I/F回路152は命令に応じて圧縮された画像データを外部から取り込み、この画像データをI/O回路153を介してマイクロプロセッサ154及びフレームメモリ157に転送する。マイクロプロセッサ154はユーザからの命令操作を受けて、必要に応じてインターネット画像表示装置150全体を駆動し、圧縮された画像データのデコードや信号処理、情報表示を行う。ここで信号処理された画像データは、フレームメモリ157に一時的に蓄積が可能である。

【0116】

ここでマイクロプロセッサ154が表示命令を出した場合には、その指示に従ってフレームメモリ157から表示パネルコントローラ156を介して表示装置151に画像データが入力され、表示装置151は入力された画像データをリアルタイムで表示する。このとき表示パネルコントローラ156は、同時に画像を表示するために必要な所定のタイミングパルスを出力制御する。なお表示装置151がこれらの信号を用いて、入力された画像データをリアルタイムで表示することに関しては、第1実施形態の説明で述べたとおりである。なおここで電源159には二次電池が含まれており、インターネット画像表示装置150全体を駆動する電力を供給する。

【0117】

本実施形態によれば、高画質表示が可能であり、かつ消費電力の少ないインターネット画像表示装置150を低コストで提供することができる。

【0118】

なお、本実施形態では画像表示デバイスとして、第1実施形態で説明した表示装置151を用いたが、これ以外にその他の本発明の実施形態に記載されたような種々の表示装置を用いることが可能である。但しこの場合は表示パネルコントローラ156の出力するタイミングパルスには、必要に応じて若干の変更が必要になることは言うまでもない。

【0119】

本実施形態のインターネット画像表示装置150においても、第1実施形態と同様に、画素内の配線を減少させることができ、量産上の歩留りを上げると共に、低コスト化を図ることができる。また、遮光膜を誘電体で形成しているため、機械的シャッタと遮光膜との間に電界が生じることを回避して、機械的シャッタの動作マージンを損なうことなく高コントラストを実現できる。