画像音声信号処理装置及びそれを用いた電子機器

【課題】 MPEG−4 AVCの符号化/復号処理のような、大量のデータ処理量が要求される画像処理に対して、高性能で、高効率な画像処理が行える信号処理装置及びそれを用いた電子機器を提供する。

【解決手段】 信号処理装置は、命令並列プロセッサ100、第1データ並列プロセッサ101、第2データ並列プロセッサ102、及び、専用ハードウェアである動き検出ユニット103とデブロックフィルタ処理ユニット104と可変長符号化/復号処理ユニット105とを備える。この構成により、処理量の多い画像圧縮伸張アルゴリズムの信号処理において、ソフトウェアとハードウェアで負荷が分散され高い処理能力と柔軟性を実現した信号処理装置、及びそれを用いた電子機器を提供出来る。

【解決手段】 信号処理装置は、命令並列プロセッサ100、第1データ並列プロセッサ101、第2データ並列プロセッサ102、及び、専用ハードウェアである動き検出ユニット103とデブロックフィルタ処理ユニット104と可変長符号化/復号処理ユニット105とを備える。この構成により、処理量の多い画像圧縮伸張アルゴリズムの信号処理において、ソフトウェアとハードウェアで負荷が分散され高い処理能力と柔軟性を実現した信号処理装置、及びそれを用いた電子機器を提供出来る。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、オーディオ及び画像の圧縮伸張処理を、並列プロセッサと専用ハードウェアを用いて高速に行う、画像音声信号処理装置及びそれを用いた電子機器に関するものである。

【背景技術】

【0002】

近年の動画像を扱う画像処理装置及び画像表示装置の高性能化、小型化の動きに呼応して、ISO(International Standard Organization)とITU−T(International Telecommunication

Union−Telecommunication Standardization

Sector)は、共同で次世代の圧縮伸張技術として、MPEG−4 AVC(Advanced Video Coding)を規格化策定中である。MPEG−4 AVCは、4×4画素の整数変換、最大9方向のイントラ予測、7種類のサブマクロブロックタイプ、マクロブロックあたり最大16本の動きベクトル、マルチフレーム参照、ループ内のデブロックフィルタ、算術符号などの新しい技術を導入することによって、画像の高圧縮率を実現し、既に実用化されているMPEG−2方式の50%に圧縮された符号量を目指している。

【0003】

しかし、新たに導入された符号化ツールは、符号化効率を重視したアルゴリズムを採用しているために、その処理量が多く、組み込みシステムへの実装が困難になっている。

【0004】

これまでの符号化方式の圧縮伸張を行う画像音声信号処理装置には、プロセッサによる並列処理と専用ハードウェアによる構成とが用いられてきた。

【0005】

プロセッサによる並列処理手法を使った高速化信号処理の例として、特許文献1がある。この特許文献1に示される例は、制御の流れが1つで、処理されるデータの流れが複数である、SIMD(Single Instruction stream Multiple Data stream)型の並列データ処理装置と、制御の流れもデータの流れも複数である、MIMD(Multiple Instruction stream

Multiple Data stream)型の並列データ処理装置とを組み合わせた、並列処理装置である。

【0006】

図16は、特許文献1の図1から引用した、従来のSIMD型並列データ処理装置902とMIMD型並列データ処理装置903とを組み合わせた信号処理装置のブロック図である。

【0007】

この信号処理装置は、装置全体を制御するシステム制御部901、SIMD型並列データ処理装置902、MIMD型並列データ処理装置903、共有メモリバス904、及び共有メモリ905を備える。

【0008】

システム制御部901は、アプリケーションプログラムの実行制御を行う。

【0009】

SIMD型並列データ処理装置902は、全体制御部910と、演算器911〜914とそれぞれのローカルメモリ915〜918とを有している。一つの演算器と一つのローカルメモリは、一つのプロセッサを構成している。全体制御部910は、プログラムを実行し、演算器911〜914のすべてに同一の命令を発行する。演算器911〜914は、発行された同一の命令の下で、各々のローカルメモリ915〜918に格納されている

データを処理する。

【0010】

MIMD型並列データ処理装置903は、全体制御部920と、制御部921〜924と、演算器925〜928と、ローカルメモリ929〜932とを有している。一つの制御部と一つの演算器と一つのローカルメモリは、一つのプロセッサを構成している。制御部921〜924の各々において別々のプログラムが実行され、演算器925〜928の各々に別々の命令が発効され、ローカルメモリ929〜932の各々に格納されているデータを処理する。全体制御部920は、MIMD型並列データ処理装置903の全体の同期や監視のための制御を行う。

【0011】

以上のような並列データ処理装置においては、対象となる処理が単純で、かつ、データ処理が大量なものをSIMD型並列データ処理装置902で処理し、対象となる処理が複雑で、かつ、データ処理が少量なものをMIMD型並列データ処理装置903で処理していた。

【0012】

一方、対象となる処理に対して最適な演算器を専用ハードウェアで構成することによって、演算性能を改善した高速化手法も用いられている。その例として、特許文献2は、画像処理の可変長符号/復号処理を専用ハードウェア化することにより、処理の高速化を実現した技術を開示している。

【0013】

図17は、特許文献2の図1から引用した、従来のSIMD型並列データ処理装置と専用ハードウェアとを組み合わせた画像処理装置1001のブロック図である。

【0014】

この画像処理装置1001は、外部のビデオデータバス1008を介して、外部のビデオ入力装置1009と、ビデオ出力装置1010と、外部メモリ1011とに接続されている。画像処理装置1001は、命令メモリ1002、プロセッサ1003、SIMD型演算手段1004、VLC(可変長符号化)処理手段1005、外部データインターフェース1006、及び、内部データバス1007を備える。VLC処理手段1005は、専用ハードウェアにより構成されている。

【0015】

プロセッサ1003は、スカラー演算やビット操作演算、比較分岐命令を行うと共に、命令メモリ1002に保持されている命令をデコードし、SIMD型演算手段1004と、VLC処理手段1005と、外部データインターフェース1006と、ビデオ入力装置1009と、ビデオ出力装置1010とを制御する。

【0016】

ビデオ入力装置1009は、外部からのビデオ信号を入力し、ビデオ出力装置1010は外部にビデオデータを出力する。

【0017】

ビデオ入力装置1009から入力された画像データは、外部メモリ1011に転送され、次のステップで、SIMD演算手段1004で行う処理に応じて、外部データインターフェース1006に転送される。SIMD演算手段1004では、動き補償、DCT、量子化の各処理が行われ、変換係数データを得る。次のステップで、VLC変換手段1005において、変換係数データは、可変長符号化され、ビットストリームデータが生成される。

【0018】

SIMD演算手段1004は、8並列のパイプライン演算器で構成されているため、DCTなどの定型処理を効率よく処理することができる。

【0019】

上述した特許文献1に代表される、SIMD型データ並列処理装置とMIMD型並列データ処理装置を組み合わせた信号処理装置は、様々な符号化アルゴリズムに対する柔軟性

を持っている。したがって、並列度を増すことによって、画像処理に十分対応できていた。これは、従来の動き検出処理が、最大16×16ペルで最小8×8ペルのマクロブロックサイズに対するものであったことによる。

【0020】

しかし、MPEG−4 AVCでは、最小のサブマクロブロックサイズが4×4ペルになっているため、従来の信号処理装置では、16並列以上の演算器を用意しても、演算器の処理効率が向上しない。

【0021】

また、MPEG−4 AVCの算術符号化/復号処理では、周辺のマクロブロックのコンテキストによって発生確率を変更しながら処理するために、1ビットづつ符号化しなければならず、並列処理ができない。つまり、従来の信号処理装置では、MIMD型並列データ処理装置の並列度を増加させても、MPEG−4 AVCでの処理性能は改善されない。

【0022】

MPEG−4 AVCのデブロックフィルタにおいても、4×4ペルのサブマクロブロック単位でフィルタパラメータを計算し、その結果に基づいてフィルタ処理を行う。SIMD型演算装置を使えば、フィルタ処理を並列処理することが可能であるが、判定処理の際に演算器を有効に活用できない。

【0023】

また、上述した特許文献2に代表される、SIMD型データ並列処理装置と専用ハードウェアとを組み合わせた信号処理装置では、高い処理性能を要求する算術符号化/復号処理に対しては、専用ハードウェアを採用することによって処理性能が改善されるが、最も処理量の多い動き検出をSIMD型並列データ処理装置で処理するには、以下の問題がある。

【0024】

MPEG−4 AVCでは、1/4画素精度の動き補償が導入され、ハーフペルの画素生成に6タップフィルタ処理を行わなければならない。更に、4×4ペルのサブマクロブロックブロックサイズが導入されたために、1マクロブロックあたり最大16本の動きベクトルの設定が可能である。小さなサブマクロブロックサイズで、1/4画素精度の探索を行い、マクロブロック当たり最大16本の動きベクトルを計算する動き検出の処理は、その処理量が飛躍的に増加している。

【0025】

このような動き検出処理をSIMD型データ並列処理装置で処理させようとすると、演算器の並列度を高め、動作周波数を高く設定しなければならない。そのような能力を持ったSIMD型並列データ装置は、デコード処理においては、その能力に余剰が発生してしまい、装置全体を効率的に利用できない。

【0026】

さらに、SIMD型並列データ処理装置の並列度を高めて処理性能を改善しようとしても、ブロックサイズが4×4ペルであるために、16並列以上にはできない。

【先行技術文献】

【特許文献】

【0027】

【特許文献1】国際公開第91/17507号

【特許文献2】特開2001−309386号公報

【発明の概要】

【発明が解決しようとする課題】

【0028】

そこで本発明は、MPEG−4 AVCの符号化/復号処理のような、大量のデータ処理量が要求される画像処理に対して、高性能で、高効率な画像処理が行える信号処理装置及びそれを用いた電子機器を提供することを目的とする。

【課題を解決するための手段】

【0029】

第1の発明に係る画像音声信号処理装置は、第1データバスと、前記第1データバスに接続され、前記第1データバスを介して共有される第1共有メモリと、前記第1データバスとは独立分離した状態に設けられる第2データバスと、前記第2データバスに接続され、前記第2データバスを介して共有される第2共有メモリと、前記第1データバスと前記第2データバスとを仲介し、前記第1データバスと前記第2データバスとを間接的に接続するブリッジユニットと、音声オーディオの圧縮処理を行い、前記第2データバスに接続される命令並列プロセッサと、前記第1データバスに接続されるが前記第2データバスには直接接続されず、かつ前記命令並列プロセッサとともに同時並行して画像圧縮処理を行うデータ並列プロセッサ及び専用ハードウェアとを備え、命令並列プロセッサ、データ並列プロセッサ及び前記専用ハードウェアのそれぞれは、同時並行して圧縮処理を実行する。

【0030】

第2の発明に係る画像音声信号処理装置は、第1データバスと、前記第1データバスに接続され、前記第1データバスを介して共有される第1共有メモリと、前記第1データバスとは独立分離した状態に設けられる第2データバスと、前記第2データバスに接続され、前記第2データバスを介して共有される第2共有メモリと、前記第1データバスと前記第2データバスとを仲介し、前記第1データバスと前記第2データバスとを間接的に接続するブリッジユニットと、音声オーディオの伸長処理を行い、前記第2データバスに接続される命令並列プロセッサと、前記第1データバスに接続されるが前記第2データバスには直接接続されず、かつ前記命令並列プロセッサとともに同時並行して画像伸長処理を行うデータ並列プロセッサ及び専用ハードウェアとを備え、命令並列プロセッサ、データ並列プロセッサ及び前記専用ハードウェアのそれぞれは、同時並行して伸長処理を実行する。

【0031】

第3の発明に係る画像音声信号処理装置は、命令並列プロセッサと、データ並列プロセッサと、専用ハードウェアとは、それぞれのローカルメモリを有し、データ並列プロセッサのローカルメモリと専用ハードウェアのそれぞれのローカルメモリは第1データバスに接続され、命令並列プロセッサのローカルメモリは第2データバスに接続され、ブリッジユニットは、第1データバスと第2データバスとに互いに独立した状態で接続される各メモリ間のデータ転送を仲介する。

【0032】

第4の発明に係る画像音声信号処理装置は、ローカルメモリを有する入出力インターフェイスをさらに備え、入出力インターフェイスのローカルメモリは第1のデータバスに接続される。

【0033】

第5の発明に係る画像音声信号処理装置は、命令並列プロセッサは、入出力インターフェイスによる入出力処理を制御する。

【発明の効果】

【0034】

本発明によれば、MPEG−4 AVCの符号化/復号処理のような、大量のデータ処理量が要求される画像処理に対して、高性能で、高効率な画像処理が行える信号処理装置及びそれを用いた電子機器を提供すること出来る。

【図面の簡単な説明】

【0035】

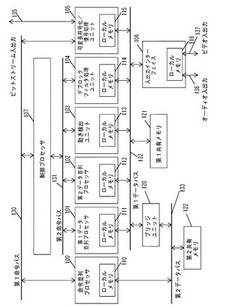

【図1】本発明の第1の実施の形態における信号処理装置のブロック図

【図2】本発明の第2の実施の形態における信号処理装置のブロック図

【図3】本発明の第3の実施の形態におけるビデオエンコーダのブロック図

【図4】CABAC算術符号化処理ユニットのブロック図

【図5】符号化対象ブロックと隣接ブロックの配置図

【図6】1/4画素精度の動き補償を説明する図

【図7】本発明の第3の実施の形態におけるデブロックフィルタのブロック図

【図8】デブロックフィルタの処理順序を説明する図

【図9】本発明の第3の実施の形態と他の方式におけるエンコード処理量の比較を説明する図

【図10】本発明の第4の実施の形態におけるビデオエデコーダのブロック図

【図11】本発明の第5の実施の形態におけるオーディオエンコーダのブロック図

【図12】本発明の第5の実施の形態におけるオーディオデコーダのブロック図

【図13】本発明の第6の実施の形態におけるAV再生システムのブロック図

【図14】本発明の第7の実施の形態におけるAV記録システムのブロック図

【図15】本発明の第8の実施の形態におけるAV記録/再生システムのブロック図

【図16】従来のSIMD型並列データ処理装置とMIMD型並列データ処理装置とを組み合わせた信号処理装置のブロック図

【図17】従来のSIMD型並列データ処理装置と専用ハードウェアとを組み合わせた画像処理装置のブロック図

【発明を実施するための形態】

【0036】

第1の構成による信号処理装置は、命令並列プロセッサと、データ並列プロセッサと、複数の専用ハードウェアとを備え、命令並列プロセッサは、音声オーディオの圧縮伸長処理、及び、画像の圧縮伸長処理のうちの非定型でかつ比較的軽い処理を行い、データ並列プロセッサは、画像の圧縮伸張処理のうちの定型でかつ比較的重い処理を行い、複数の専用ハードウェアは、画像の圧縮伸張処理のうちの比較的重い処理を行う。

【0037】

この構成によれば、命令並列のプロセッサとデータ並列のプロセッサと専用ハードウェアとからなる構成で信号処理装置を形成し、命令並列プロセッサで、音声・オーディオの圧縮伸張処理と画像処理のうち非定型処理を行い、データ並列プロセッサで画像処理のうち定型処理を行い、専用ハードウェアで動き検出、可変長符合化、デブロックフィルタ処理などの処理を行うことが出来る。したがって、処理量の多い画像圧縮伸張アルゴリズムの信号処理に対して、ソフトウェアとハードウェアで負荷が分散され、高い処理能力と柔軟性を持った信号処理装置を実現することが出来る。

【0038】

第2の構成による信号処理装置は、請求項1記載の信号処理装置であって、第1命令バスと、第1データバスと、第1共有メモリと、入出力インターフェースとを、さらに備え、命令並列プロセッサと、データ並列プロセッサと、複数の専用ハードウェアと、入出力インターフェースとは、それぞれのローカルメモリを有し、第1命令バスには、命令並列プロセッサと、データ並列プロセッサと、複数の専用ハードウェアとが接続され、第1命令バスを介して、命令並列プロセッサが、データ並列プロセッサ、及び、複数の専用ハードウェアを制御するための命令が通信され、第1データバスには、命令並列プロセッサのローカルメモリと、データ並列プロセッサのそれぞれのローカルメモリと、複数の専用ハードウェアのそれぞれのローカルメモリと、第1共有メモリと、入出力インターフェースのローカルメモリとが接続され、これらのメモリの間でのデータ転送が行われる。

【0039】

この構成によれば、第1の構成による信号処理装置が有する特徴に加えて、さらに、命令バスとデータバスを分離することによって、バスのトラフィックを分散し、処理性能を向上させることが出来る。

【0040】

第3の構成による信号処理装置は、第1、第2の構成による信号処理装置であって、第2データバスと、第2共有メモリと、第1データバスと第2データバスとを接続するブリッジユニットとを、さらに備え、第1データバスには、データ並列プロセッサのそれぞれ

のローカルメモリと、複数の専用ハードウェアのそれぞれのローカルメモリと、第1共有メモリと、入出力インターフェースのローカルメモリとが接続され、これらのメモリの間でのデータ転送が行われ、第2データバスには、命令並列プロセッサのローカルメモリと、第2共有メモリとが接続され、これらのメモリの間でのデータ転送が行われ、ブリッジユニットを介して、第1データバスに接続された各メモリと、第2データバスに接続された各メモリとの間のデータ転送が行われる。

【0041】

この構成によれば、データ処理プロセッサのローカルメモリと、専用ハードウェアの専用メモリと、共有メモリとを第1データバスで接続し、命令並列プロセッサのローカルメモリと共有メモリとを第2データバスで接続する。これにより、大容量のデータを扱う画像処理のデータ転送が第1データバス中心に行われ、オーディオ処理を行う命令並列プロセッサが接続される第2データバスとの負荷分散が実現出来る。

【0042】

第4の構成による信号処理装置は、第1から第3の構成による信号処理装置であって、制御プロセッサをさらに備え、命令並列プロセッサは、制御プロセッサを経由して、データ並列プロセッサと、複数の専用ハードウェアとを制御する。

【0043】

この構成によれば、命令並列プロセッサは、制御プロセッサを経由してデータ並列プロセッサ及び専用ハードウェアを制御することが出来るので、命令並列プロセッサと制御プロセッサの負荷が分散され、より高い処理性能を実現することが出来る。

【0044】

第5の構成による信号処理装置は、第1から第4の構成による信号処理装置であって、第2命令バスをさらに備え、第1命令バスには、命令並列プロセッサと、制御プロセッサと、複数の専用ハードウェアのうちの一部のハードウェアが接続され、第2命令バスには、制御プロセッサと、データ並列プロセッサと、複数の専用ハードウェアのうちの第1命令バスに接続されていない、他の専用ハードウェアが接続され、命令並列プロセッサは、複数の専用ハードウェアのうちの、第1命令バスに接続されている一部のハードウェアを制御し、また、制御プロセッサを経由して、データ並列プロセッサと、複数の専用ハードウェアのうちの第1命令バスに接続されていない、他の専用ハードウェアとを制御する。

【0045】

この構成によれば、命令並列プロセッサは、第1命令バスを介して、制御プロセッサと、一部の専用ハードウェアのみを制御すればよく、定型的な処理を行うデータ並列プロセッサと専用ハードウェアは、第2命令バスを介して、制御プロセッサによって制御されるため、命令バスにおける命令の輻輳を回避でき、効率良く信号処理を行うことが出来る。

【0046】

第6の構成による信号処理装置では、データ並列プロセッサの並列度は、圧縮伸長処理する画像サイズによって定められる。

【0047】

この構成によれば、圧縮伸張の対象となる画像のサイズによって、データ並列プロセッサの並列度を変更するので、同一のプロセッサアーキテクチャでありながら、多様な画像サイズに対応出来る信号処理装置を提供出来る。

【0048】

第7の構成による信号処理装置では、データ並列プロセッサの並列度は、信号処理装置に供給される電源電圧や、動作周波数によって定められる。

【0049】

この構成によれば、LSIに共有される電源電圧や動作周波数によって、データ並列プロセッサの並列度を変更出来る。データ並列プロセッサの並列度を増大させることによって、動作周波数を下げ、信号処理装置の消費電力を低減することが出来るので、モバイル端末などの電子機器への応用が特に有効となる。

【0050】

第8の構成による信号処理装置では、専用ハードウェアが行う処理は、可変長符号化処理、可変長復号処理、ビデオ入出力処理、動き検出処理、動き補償処理、DCT(離散コサイン変換)処理、逆DCT処理、量子化処理、逆量子化処理、及び、デブロックフィルタ処理の少なくとも一つを含む。

【0051】

この構成によれば、圧縮伸張処理の中で、動き検出、可変長符号/復号、デブロックフィルタなどの処理量の多いモジュールを専用ハードウェアで処理することにより、命令並列プロセッサ及びデータ並列プロセッサの動作周波数の増大を抑制することが出来る。

【0052】

第9の構成による信号処理装置では、複数の専用ハードウェアのうちの、第1命令バスに接続される一部のハードウェアが行う処理は、可変長符号化処理、及び/又は、可変長復号処理である。

【0053】

この構成によれば、可変長符号化処理、及び/又は、可変長復号処理を行う専用ハードウェアを、命令並列プロセッサによって、直接、かつ、頻繁に制御出来る。したがって、可変長符号化処理、及び/又は、可変長復号処理を繊細に、かつ多様に制御出来る。

【0054】

第10の構成による電子機器は、第1から第9の構成による信号処理装置を用いた電子機器であって、信号処理装置は、音声オーディオの圧縮処理、音声オーディオの伸長処理、画像圧縮処理、及び、画像伸長処理の、少なくとも一つの処理を行う。

【0055】

この構成によれば、請求項1から9記載の信号処理装置が有する特徴を生かした、電子機器を提供出来る。

【0056】

第11の構成による電子機器は、第1から第9の構成による信号処理装置と、再生機構を有する再生装置と、復調・エラー訂正部と、メモリと、複数のD/A変換器とを備え、再生装置は、変調された符号化信号を記録媒体から再生し、復調・エラー訂正部は、再生装置が再生した変調された符号化信号を復調して、エラー訂正を行い、符号化データとして出力し、信号処理装置は、復調・エラー訂正部が出力した符号化データをデコードして、ビデオデータ及びオーディオデータとして出力し、メモリは、デコード処理前、処理中、及び/又は、処理後のデータを格納し、複数のD/A変換器は、信号処理装置が出力したビデオデータ及びオーディオデータをD/A変換して、アナログのビデオ出力及びアナログのオーディオ出力を出力する。

【0057】

この構成によれば、符号化データを高速に、効率よくデコードでき、消費電力が小さい再生電子機器を実現出来る。

【0058】

第12の構成による電子機器は、第1から第9の構成による信号処理装置と、複数のA/D変換器と、メモリと、エラー訂正・変調部と、記録機構を有する記録装置とを備え、複数のA/D変換器は、入力されたアナログのビデオ入力及びアナログのオーディオ入力をA/D変換して、ビデオデータ及びオーディオデータを出力し、信号処理装置は、複数のA/D変換器が出力したビデオデータ及びオーディオデータをエンコードして、符号化データを出力し、メモリは、エンコード処理前、処理中、及び/又は、処理後のデータを格納し、エラー訂正・変調部は、信号処理装置がエンコードした符号化データに、エラー訂正符号を付加して、変調し、符号化信号として出力し、記録装置は、エラー訂正・変調部が出力した符号化信号を、記録媒体に記録する。

【0059】

この構成によれば、AV信号を、高速に効率よくエンコードでき、消費電力が小さい記録電子機器を実現出来る。

【0060】

第13の構成による電子機器は、第11の構成による電子機器と第12の構成による電子機器とを一体的に構成される。

【0061】

この構成によれば、AV信号を、高速に効率よくエンコード/デコードでき、消費電力が小さい、記録機能と再生機能とを一体化した電子機器を実現出来る。

【0062】

次に、図面を参照しながら、本発明の実施の形態を説明する。

【0063】

(第1の実施の形態)

図1は、本発明の第1の実施の形態における信号処理装置のブロック図である。本形態の信号処理装置は、ローカルメモリ110を有する命令並列プロセッサ100、ローカルメモリ111を有する第1データ並列プロセッサ101、ローカルメモリ112を有する第2データ並列プロセッサ102、ローカルメモリ113を有する動き検出ユニット103、ローカルメモリ114を有するデブロックフィルタ処理ユニット104、ローカルメモリ115を有する可変長符号化/復号処理ユニット105、ローカルメモリ116を有する入出力インターフェース106、第1共有メモリ121、第1命令バス130、及び、第1データバス132を備え、第1命令バス130には、各プロセッサ100〜102と各ユニット112〜116とが接続され、第1データバス132には、ローカルメモリ110〜116と、第1共有メモリ121と、入出力インターフェース106とが接続されている。可変長符号化/復号処理ユニット105は、さらに、外部装置に対してビットストリーム入出力135を有しており、入出力インターフェース106は、外部装置に対してオーディオ入出力136とビデオ入出力137を有している。

【0064】

第1データ並列プロセッサ101と第2データ並列プロセッサ102とに採用されているSIMD型プロセッサには、8個の処理要素が含まれており、1個の命令で8個のデータ流を並列に処理することが出来る。

【0065】

動き検出ユニット103と、デブロックフィルタ処理ユニット104と、可変長符号化/復号処理ユニット105と、入出力インターフェース106とは、それぞれ専用のハードウェアである。

【0066】

次に、本形態の動作の概略を、画像の符号化処理を例として、説明する。

【0067】

外部から入力されたビデオ信号は、A/D変換された後、入出力インターフェース106より、第1データバス132を経由して、第1共有メモリ121に格納される。

【0068】

動き検出ユニット103は、第1共有メモリ121に格納されている前フレームの画像データと、現フレームの画像データを基に、動きベクトルを算出する。

【0069】

第1データ並列プロセッサ101は、第1共有メモリ121に格納されている前フレームの画像データと、動き検出ユニット103が算出した動きベクトルを基に、動き補償処理を行って、予測画像データを算出する。また、この予測画像データに対する現フレームの画像データの差分画像データを算出する。

【0070】

第2データ並列プロセッサ102は、差分画像データをDCT変換処理し、さらに、得られたDCT係数を量子化処理する。また、第2データ並列プロセッサ102は、量子化DCT係数を逆量子化し、さらに、逆DCT変換処理して、差分画像データを算出し、第1データ並列プロセッサ101が処理した予測画像データとから、再構築画像データを算出する。

【0071】

本形態の信号処理装置では、第1データ並列プロセッサ101が、動き補償処理の画素値計算を行っている間に、第2データ並列プロセッサ102が、DCT変換処理を行う。このように、2つのデータ並列プロセッサの稼働率を維持して、それぞれに別々の処理をさせることができ、演算性能の改善を図っている。

【0072】

デブロックフィルタ処理ユニット104は、再構築画像データに対して、デブロックフィルタ処理をして、ブロックノイズを除去し、第1共有メモリ121に格納する。

【0073】

可変長符号化/復号処理ユニット105は、量子化DCT係数と動きベクトルとを、算術符号を用いた可変長符号化処理し、ビットストリームとして出力する。

【0074】

命令並列プロセッサ100は、上述した各種の処理の全体的な制御を、第1命令バス130を介して行う。また、命令並列プロセッサ100は、予測画像の生成を、イントラ予測符号化で行うか、あるいは、インター予測符号化で行うかの符号化モードの判定を行う。

【0075】

各プロセッサと各ユニットと間のデータ転送は、第1データバス132を介して行われる。

【0076】

このように、画像圧縮・伸長処理のうち逐次的な処理を命令並列プロセッサ100が行い、画像圧縮・伸長処理のうち定型的な処理を第1データ並列プロセッサ101と第2データ並列プロセッサ102とが行い、さらに、動き検出処理、デブロックフィルタ処理、及び、可変長符号化処理といった重い処理を専用ハードウェアで行うことにより、高効率な画像処理を実現出来る。

【0077】

本形態における、第1データ並列プロセッサ101と第2データ並列プロセッサ102との処理対象の分担区分は、一例であって、その他の区分でも良い。あるいは、プロセッサの性能によっては、第1データ並列プロセッサ101と第2データ並列プロセッサ102の処理を一つのデータ並列プロセッサで行っても良い。

【0078】

さらに、第1データ並列プロセッサ101が行っている動き補償処理は、動き検出ユニット103が行っても良い。

【0079】

(第2の実施の形態)

図2は、本発明の第2の実施の形態における信号処理装置のブロック図である。図2において、図1と同様の構成要素については、同一の符号を付すことにより、説明を省略する。

【0080】

本形態の信号処理装置は、第1の実施の形態の信号処理装置に比べ、制御プロセッサ107、第2共有メモリ122、第2命令バス131、第2データバス133、及び、第1データバス132と第2データバス133とを接続するブリッジユニット120とを、さらに備える。

【0081】

第1命令バス130には、命令並列プロセッサ100と、制御プロセッサ107と、可変長符号化/復号処理ユニット105とが接続されている。第2命令バスには、制御プロセッサ107、第1データ並列プロセッサ101、第2データ並列プロセッサ102、動き検出ユニット103、及び、デブロックフィルタ処理ユニット104とが接続されている。

【0082】

第1データバスには、ローカルメモリ111〜115、第1共有メモリ121、入出力

インターフェース106、及び、ブリッジユニット120とが接続されている。第2データバスには、ローカルメモリ110と第2共有メモリ122とブリッジユニット120とが接続されている。

【0083】

本形態の信号処理装置は、第1の実施の形態に比べ、データの並列処理をさらに強固にしたものである。すなわち、本形態において導入された制御プロセッサ107は、命令並列プロセッサ100からの命令を受けて、第1データ並列プロセッサ101、第2データ並列プロセッサ102、動き検出ユニット103、及び、デブロックフィルタ処理ユニット104とを、第2命令バス131を介して制御する。その結果、本形態の信号処理装置は、各データ並列プロセッサ及び専用ハードウェアでの並列処理がより迅速に行えるように構成されている。

【0084】

さらに、本形態の第2共有メモリ122は、命令並列プロセッサ100に関係するデータと、第1データバス132に接続されている各構成要素が扱うデータのうち、比較的アクセス頻度が低いデータとを格納する。この構成により、第1共有メモリ121の負荷が軽減され、信号処理装置全体の処理効率が改善される。

【0085】

本形態の動作は、以下に述べる第3の実施の形態において、詳述する。

【0086】

(第3の実施の形態)

図3は、本発明の第3の実施の形態におけるビデオエンコーダのブロック図である。

【0087】

本形態のビデオエンコーダは、MPEG−4 AVCに対応出来るエンコーダであり、各構成要素には、MPEG−4 AVCに対応するビデオエンコーダの各機能を的確に表現した名前が付されている。

【0088】

図3に示した本形態のビデオエンコーダは、第2の実施の形態の信号処理装置によって構成されている。そこで、まず、図3の構成要素と、図2の構成要素との対応関係を示す。

【0089】

符号化制御部301とモード切替部303の処理は、図2の命令並列プロセッサ100が行う。

【0090】

動き補償部312と差分検出部302の処理は、図2の第1データ並列プロセッサ101が行う。

【0091】

4×4DCT変換部304、量子化部305、逆量子化部306、逆4×4DCT変換部307、及び、再構築部309の処理は、図2の第2データ並列プロセッサ102が行う。

【0092】

可変長符号化部308は、図2の可変長符号化/復号処理ユニット105に相当し、デブロックフィルタ310は、図2のデブロックフィルタ処理ユニット104に相当し、フレームメモリ311は、図2の第1共有メモリ121に相当し、動き検出部313は、図2の動き検出ユニット103に相当する。

【0093】

次に、MPEG−4 AVCの主要な信号処理を、本形態の各部の動作を参照して、説明する。

【0094】

まず、図3を参照して、エンコード処理を説明する。ビデオ入力314は、イントラ符号化の場合、4×4DCT変換部304において離散コサイン変換(直交変換)されDC

T係数が求められる。次に、量子化部305においてDCT係数が量子化される。

【0095】

MPEG−2やH.263などの既存の符号化規格では、8×8ブロックサイズに対して、実数精度のDCTが採用されており、DCT精度を規定しなければミスマッチが発生した。しかし、MPEG−4 AVCでは、4×4ブロックサイズに対して、整数精度のDCT変換が適用されており、この結果、DCT精度に起因するミスマッチが発生しなくなった。

【0096】

量子化されたDCT係数は、可変長符号部308において、算術符号化器を使ってエントロピー符号化される。その詳細は、後述する。

【0097】

次に、可変長符号化/復号処理について説明する。

【0098】

MPEG−4 AVCの概要は、非特許文献1「MPEG−4 AVC|H.264の概要と標準化動向」(鈴木輝明;情報処理学会、オーディオビジュアル複合情報処理38―13、69〜73頁、2002年11月)で説明されている。以下では、非特許文献1に基づいて説明する。

【0099】

マクロブロックの個数、動きベクトルの差分、変換係数などのシンタックス要素の可変長符号化では、CAVLC(Context Adaptive Variable Length Coding;コンテキスト適応可変長符号化)と、CABAC(Context Adaptive Binary Arithmetic Coding;コンテキスト適応2進算術符号化)という2種類のエントロピー符号化方式が使い分けられる。

【0100】

ここでは、メインプロファイルで用いられるCABACという算術符号化方式について説明する。算術符号は、長さ「1」の線分を、符号化しようとするシンボルの出現確率に従って分割し、その分割された線分と符号化しようとするシンボルとが1対1に対応することから、その線分について符号化するものである。その線分を代表する2進数が符号となるため、線分の区間が広い、すなわち符号化しようとするシンボルの出現確率が高いほど、そのシンボルは短い2進数で表現でき、その結果圧縮率が高くなる。そこで、対象ブロックの符号化を行う場合に、周辺ブロックのコンテキストに応じて出現確率を操作して、圧縮率が高くなるように制御される。

【0101】

図4は、CABAC算術符号化処理ユニットのブロック図である。これは、非特許文献1の図7から引用したものである。図4に示すCABAC算術符号化処理ユニットは、コンテキストモデリング部401と、バイナリ化部402と、適応2進算術符号化処理部405とを備え、適応2進算術符号化処理部405は、出現確立予測部403、及び、符号化部404とを有する。

【0102】

コンテキスト・モデリングは、各シンボルを符号化する際の確率モデルである。各シンタックス要素には、コンテキストが定義されており、このコンテキストに応じて確率テーブルを切り替えて算術符号を行う。

【0103】

図5は、符号化対象ブロックと隣接ブロックの配置図である。図5において、符号化対象ブロックC408を符号化する際、隣接ブロックA406と隣接ブロックB407の状態に応じて、符号化対象ブロックC408のコンテキストが決定される。

【0104】

以上のような算術符号処理において、可変長符号化された符号のデコード処理は、出現確率情報をデコーダで解釈し、その情報に基づいて再構成するという逐次処理である。ま

た、出現確率の操作は、テーブルによって行われることから、これらの符号化処理と復号処理を、VLIW(極長命令語)対応の命令並列プロセッサ(上述した第2の実施の形態では、図2に示す命令並列プロセッサ100に相当)や、SIMD型のデータ並列プロセッサ(同じく、第1データ並列プロセッサ101、あるいは、第2データ並列プロセッサ102に相当)で行ったのでは、処理性能は、改善されない。むしろ、これらの処理は、専用ハードウェア(同じく、可変長符号化/復号処理ユニット105に相当)を用いて処理することによって、命令並列プロセッサとデータ並列プロセッサの負荷分散ができ、その結果、動作周波数が低減され、処理装置の周波数バランスを良好にすることが出来る。これが、本実施の形態において、図3に示す可変長符号化部308を、図2に示す専用ハードウェアである可変長符号化/復号処理ユニット105によって、処理している理由である。

【0105】

図3において、量子化部305によって量子化されたDCT係数は、逆量子化部306において逆量子化された後、逆4×4DCT変換部307において、逆DCT変換され、再構築部309において、画像が再構築される。再構築された画像は、デブロックフィルタ310によって、デブロックフィルタ処理が施され、4×4画素境界で画素値が書き換えられる。デブロックフィルタ処理については、後述する。

【0106】

次に、図3の動き補償部312において行う1/4画素精度の動き補償処理について、図6を参照して、説明する。図6は、1/4画素精度の動き補償を説明する図である。

【0107】

動き補償とは、参照する画像から予測画像を構成する場合に、動きベクトルの情報を用いて、符号化しようとする画像により近い予測画像を構成しようとするものである。予測誤差が少ないほど、符号量が小さくなるため、MPEG−4 AVCでは1/4画素精度の動き補償が採用されている。動きベクトルは、ブロック単位での平行移動を表す2つのパラメータ(水平方向の移動距離と垂直方向の移動距離)から構成される。

【0108】

動きベクトルが指し示した参照画像の予測画像は、下記の方法によって求められる。

【0109】

図6において、画素A、B、C、D、E、F、G、H、I、J、K、L、M、N、P、Q、R、S、T、Uは、それぞれ整数位置の画素であり、画素aa、bb、cc、dd、ee、ff、gg、hh、及び、画素b、h、j、m、sは、それぞれ1/2精度の画素であり、画素a、c、d、e、f、g、i、k、n、p、q、rは、それぞれ1/4精度の画素である。

【0110】

これらの画素の画素値を求める手順について説明する。まず、1/2精度の画素bは、以下のように求められる。画素bの水平方向の近傍の画素E、F、G、H、I、Jを変数として、(数1)で定義される6タップフィルタを用いて、中間データb1が生成される。

【0111】

【数1】

【0112】

次に、この中間データb1を、(数2)によって、丸め処理と正規化の後、0〜255にクリップ処理して、画素bが求まる。

【0113】

【数2】

【0114】

ここに、Clip(X)は、カッコ内の変数Xを0から255の範囲にクリップする関数である。すなわち、変数Xが0未満であれば、b=0とし、変数Xが0から255の範囲であれば、b=Xとし、変数Xが256以上であれば、b=255とする。

【0115】

同様に、1/2精度の画素hは、次のように求められる。画素hの垂直方向の近傍の画素A、C、G、M、R、Tを変数として、(数3)で定義される6タップフィルタを用いて、中間データh1が生成される。

【0116】

【数3】

【0117】

この中間データh1を、(数4)によって、丸め処理と正規化の後、0〜255にクリップ処理して、画素hが求まる。

【0118】

【数4】

【0119】

1/4精度の画素a、c、d、f、i、k、n、q、は、(数5)に示すように、それぞれの近傍の2画素を用いて、丸め付き平均により求められる。

【0120】

【数5】

【0121】

1/4精度の画素e、g、p、rは、同様に、(数6)に示すように、それぞれの近傍の2画素を用いて、丸め付き平均により求められる。

【0122】

【数6】

【0123】

以上のような予測画像の生成において、動きベクトルはサブマクロブロック毎に設定することが可能である。最も小さなサブマクロブロックである4×4の場合においては、整数位置の画素から実数位置の16箇所の画素を6タップフィルタを使って内挿しなければならない。画素の内挿では画素間にデータの依存関係がないため並列に処理が可能である。従って、本実施の形態に示すように、SIMD型データ並列プロセッサを使うと、効率よくフィルタ処理が出来る。

【0124】

次に、デブロックフィルタ処理について説明する。

【0125】

MPEG−4 AVCでは、4×4画素単位でDCT処理を行うために、ブロックの境界にブロック歪みが発生する。デブロックフィルタ処理は、ブロックの境界にフィルタをかけて歪みを平滑化するものである。画像の4×4境界に施すフィルタ処理は、Boundary Strength(BS)という境界の強度の値に応じて、フィルタの強度がブロック境界毎に最も適した値に調整される、適応的なフィルタ処理である。すなわち、境界の強度BSは、その境界にフィルタをかけるかどうかの判定と、フィルタをかける際の画素値変動の最大値を定義するために用いられる。

【0126】

図7は、本発明の第3の実施の形態におけるデブロックフィルタ310のブロック図である。本形態のデブロックフィルタ310は、BS条件判定処理部602、メモリ603、制御部604、及び、フィルタ処理部605を備え、フィルタ処理部605は、メモリ606とフィルタ607〜609を有する。

【0127】

図7に示すデブロックフィルタ310において、BS条件判定処理部602は、境界の強度BSを計算し、その結果を判定して、制御パラメータ613をフィルタ処理部605に渡す。フィルタ処理部605は、制御パラメータ613に応じてフィルタ処理を行う。

【0128】

デブロックフィルタ310の処理を、図8を参照して、説明する。

【0129】

図8は、本発明の第3の実施の形態におけるデブロックフィルタ310の処理順序を示す。フィルタ処理は、図8に示すように、境界[1]〜[4]に対する水平フィルタ処理が行われ、続いて、境界[5]〜[8]に対する垂直フィルタ処理が行われる。

【0130】

境界の強度 BS=4 の時のフィルタ処理について説明する。4×4のサブマクロブロックの境界[1]における最初のフィルタ処理では、境界[1]を挟んだ画素p3、p2、p1、p0、q0、q1、q2、q3の8画素を入力として、画素p2、p1、p0、q0、q1、q2の6画素を、画素P2、P1、P0、Q0、Q1、Q2に書き換える。

【0131】

画素P2、P1、P0は、(数7)の条件式によってフィルタ処理の式を切り換え、(数8)と(数9)とによって求められる。

【0132】

【数7】

【0133】

(数7)の条件が満たされる場合は、画素P0、P1、P2を(数8)から求める。

【0134】

【数8】

【0135】

(数7)の条件が満たされない場合は、画素P0、P1、P2を(数9)から求める。

【0136】

【数9】

【0137】

また、画素Q0、Q1、Q2は、(数10)の条件式によってフィルタ処理の式を切り換え、(数11)と(数12)とによって求められる。

【0138】

【数10】

【0139】

(数10)の条件が満たされる場合は、画素Q0、Q1、Q2を(数11)から求める。

【0140】

【数11】

【0141】

(数10)の条件が満たされない場合は、画素Q0、Q1、Q2を(数12)から求める。

【0142】

【数12】

【0143】

以上のように、量子化パラメータと画素値によって適応的にフィルタ処理を切り換える場合、SIMD型データ並列プロセッサによるデータ処理装置では、BS条件判定を並列

に処理できないために、並列設置された演算器が有効に活用できない。それに代わって、図7に示したように、デブロックフィルタ処理を、BS条件判定処理部602とフィルタ処理部605とからなる専用ハードウェアで実行すれば、BS計算処理とフィルタ処理を別々に演算することができ、BS条件の判定処理が高速化され、フィルタ処理が並列処理出来る。その結果、デブロックフィルタ処理を、効率よく行うことが出来る。さらに、フィルタ処理部は、輝度Yと色差UVにデータの依存がないため、並列動作が可能であり、演算器を導入すると更に処理サイクル数の削減が可能である。これが、本実施の形態において、図3に示すデブロックフィルタ310を、図2に示す専用ハードウェアであるデブロックフィルタ処理ユニット104によって、処理している理由である。

【0144】

図3に示す本形態のビデオエンコーダにおいて、デブロックフィルタ310によりデブロックフィルタ処理された画像は、出力画像として用いられるだけでなく、そのフレーム以降の参照画像として参照されるため、フレームメモリ311に保存しておく。

【0145】

次に、図3に示すビデオエンコーダを、本形態の信号処理装置で実現した場合の所要処理量と、他の方式によって構成した場合の所要処理量とを比較する。

【0146】

図9は、本発明の第3の実施の形態と他の方式におけるエンコード処理量の比較を示す図である。

【0147】

図9において、方式1は、1クロックサイクルあたり1命令を発行出来るプロセッサを用いて、図3に示すビデオエンコーダを構成し、全てソフト処理した場合である。方式2は、MIMD型並列データ処理装置とSIMD型並列データ処理装置を組み合わせて、図3に示すビデオエンコーダを構成し、全てソフト処理した場合である。方式3は、SIMD型並列データ処理装置とVLCの専用ハードウェアを用いて、図3に示すビデオエンコーダを構成した場合である。方式4は、VLIW型並列データ処理装置とSIMD型並列データ処理装置と専用ハードウェアを用いて、図3に示すビデオエンコーダを構成した場合であり、本実施の形態に相当する。すなわち、方式4のVLIW型並列データ処理装置は、本形態の図2に示す、命令並列プロセッサ100に相当し、SIMD型並列データ処理装置は、同じく、第1データ並列プロセッサ101と第2データ並列プロセッサ102に相当し、専用ハードウェアは、同じく、動き検出ユニット103と、デブロックフィルタ処理ユニット104と、可変長符号化/復号処理ユニット105に、相当する。

【0148】

エンコード処理において、処理量が多いのは、動き検出と動き補償と可変長符号化とデブロックフィルタである。これらの処理量の具体的な数値を各方式について比較すると、以下のようになる。

【0149】

方式1においては、動き検出処理が「3048」メガサイクル、可変長符号化処理が「1000」メガサイクル、デブロックフィルタ処理が「321」メガサイクル、動き補償処理が「314」メガサイクル、その他の処理が「217」メガサイクルである。全処理量は、「4900」メガサイクルである。

【0150】

方式2においては、動き検出処理が「381」メガサイクル、可変長符号化処理が「333」メガサイクル、デブロックフィルタ処理が「107」メガサイクル、動き補償処理が「39」メガサイクル、その他の処理が「52」メガサイクルである。全処理量は、「900」メガサイクルである。

【0151】

方式3においては、動き検出処理が「381」メガサイクル、可変長符号化処理が「67」メガサイクル、デブロックフィルタ処理が「80」メガサイクル、動き補償処理が「39」メガサイクル、その他の処理が「30」メガサイクルである。全処理量は、「60

7」メガサイクルである。

【0152】

方式4においては、動き検出処理が「203」メガサイクル、可変長符号化処理が「67」メガサイクル、デブロックフィルタ処理が「21」メガサイクル、動き補償処理が「21」メガサイクル、その他の処理が「29」メガサイクルである。全処理量は、「352」メガサイクルである。

【0153】

動き検出処理は、対象マクロブロックと参照マクロブロックの画素値の差分絶対値和が最も少ないポジション(動きベクトル)を選択する処理である。MPEG−4 AVCの場合、4×4のサブマクロブロック単位で動きベクトルを設定することが可能である。従って、16画素の差分絶対値和の計算が並列に処理出来る。方式2及び方式3では、この動き検出の処理を、8並列のSIMD型並列データ処理装置で処理させたものであり、方式1に比べ大幅な高速化が実現している。方式4は、16並列で差分絶対値和の計算が可能な専用ハードウェアで、動き検出を処理しているため、SIMD型並列データ処理装置よりも更に高速な処理が実現している。

【0154】

動き補償処理は、動きベクトルが指し示した参照画像を、1/4画素精度で求める処理である。この処理においても、4×4サブマクロブロック単位で処理が行われるため、並列処理が可能である。動き検出処理と同様に、方式2と方式3は、8並列のSIMD型並列データ処理装置で、方式4は、専用ハードウェアで動き補償処理を行っており、大幅な高速化を達成している。

【0155】

可変長符号化処理は、CABACと呼ばれる算術符号処理で、周辺ブロックのコンテキストに応じて対象ブロックの発生確率を変化させて復号を行う逐次処理である。方式2では、可変長符号化の処理を、4命令発行可能なMIMD型並列データ処理装置を用いて行うことを想定しているが、方式1の1命令発行のプロセッサに比べて、最大でも1/3の処理量である。方式3と方式4は、専用ハードウェアでVLC処理を行うもので、判定処理やテーブル検索が高速に行われるため、方式1に比べて、1/15に高速化が可能である。

【0156】

デブロックフィルタ処理は、方式2がMIMD型並列データ処理装置による並列処理で、方式3がSIMD型並列データ処理装置による並列処理である。MIMD型では、フィルタ処理の性能が、SIMD型では、BS判定処理の性能が改善されないため、1/3〜1/4の高速化しか得られない。一方、方式4は、デブロックフィルタ処理を専用ハードウェアで実行するもので、BS判定処理とフィルタ処理を分割し、パイプライン動作させることによって、方式1に比べ、1/15の高速化が可能である。

【0157】

以上、明らかなように、本形態のように、動き検出処理と動き補償処理と可変長符号化処理とデブロックフィルタ処理とを、専用ハードウェアで構成することによって、大幅な高速化が可能である。

【0158】

(第4の実施の形態)

図10は、本発明の第4の実施の形態におけるビデオデコーダのブロック図である。

【0159】

本形態のビデオデコーダは、MPEG−4 AVCに対応出来るデコーダであり、各構成要素には、MPEG−4 AVCに対応するビデオデコーダの各機能を的確に表現した名前が付されている。

【0160】

図10に示した本形態のビデオデコーダは、第2の実施の形態の信号処理装置によって構成されている。そこで、まず、図10の構成要素と、図2の構成要素との対応関係を示

す。

【0161】

復号制御部331の処理は、図2の命令並列プロセッサ100が行う。

【0162】

動きベクトル復号部336と動き補償部337の処理は、図2の第1データ並列プロセッサ101が行う。

【0163】

逆量子化部333、逆4×4DCT変換部334、及び、再構築部335の処理は、図2の第2データ並列プロセッサ102が行う。

【0164】

可変長復号部332は、図2の可変長符号化/復号処理ユニット105に相当し、デブロックフィルタ338は、図2のデブロックフィルタ処理ユニット104に相当し、フレームメモリ339は、図2の第1共有メモリ121に相当する。

【0165】

本形態のビデオデコーダの動作の概略を説明する。

【0166】

可変長復号部332に、算術符号で符号化された符号化ビデオ入力341が入力され、復号されて、量子化DCT係数と動きベクトルの差分が求められる。得られた量子化DCT係数は、逆量子化部333において逆量子化され、さらに、逆4×4DCT変換部334において逆DCT変換されて、差分画像データが得られる。

【0167】

一方、可変長復号部332で得られた動きベクトルの差分から、動きベクトル復号部336において、動きベクトルが求められ、動き補償部337において、フレームメモリ339に格納されている参照画像と動きベクトルとから、予測画像が求められる。

【0168】

再構築部335において、前述の差分画像データと予測画像から、新しい画像が再構築されて、ビデオ出力342として出力される。出力されたビデオ出力342は、同時に、デブロックフィルタ338においてデブロックフィルタ処理された後、フレームメモリ339に格納される。

【0169】

逆量子化部333や逆4×4DCT変換部334の制御は、復号制御部331が行う。

【0170】

デブロックフィルタ処理をはじめ、逆量子化処理、逆DCT変換処理は、上述した第3の実施の形態の場合と同様であり、ここでは説明を省略する。

【0171】

本形態においても、可変長復号処理とデブロックフィルタ処理とを、専用ハードウェアで処理することによって、大幅な高速化が実現出来ている。

【0172】

また、上述した説明は、本形態のビデオエデコーダを、図2に示す本発明の第2の実施の形態の信号処理装置で実現する例を取り上げたが、本形態のビデオエデコーダは、本発明の第1の実施の形態の信号処理装置を用いて実現することも出来る。また、各プロセッサが分担する処理対象は、適宜変更することも出来る。

【0173】

(第5の実施の形態)

図11は、本発明の第5の実施の形態におけるオーディオエンコーダのブロック図であり、図12は、同じく、本発明の第5の実施の形態におけるオーディオデコーダのブロック図である。

【0174】

図11に示すオーディオエンコーダにおいては、オーディオ入力353は、圧縮部351において、サンプリング及び量子化を含む圧縮処理が行われ、符号化部352において

、符号化が行われ、符号化オーディオ出力354として、出力される。

【0175】

図12に示すオーディオデコーダにおいては、符号化オーディオ入力363は、復号部361において、復号が行われ、伸長部362において、逆量子化され伸長処理が行われる。

【0176】

オーディオのエンコーディング及びデコーディングは、MPEG−4 AVCのビデオのエンコーディングやデコーディングに比べて、必要な処理量が少ないために、いずれのプロセッサを用いても処理出来る。

【0177】

本形態のオーディオエンコーダとオーディオデコーダとを、第1の実施の形態の信号処理装置で実現する場合には、図11に示す圧縮部351と符号化部352の処理と、図12に示す復号部361と伸長部362の処理とは、図1に示す命令並列プロセッサ100によってお行う。これらの処理は、十分な余裕を持って実行出来る。

【0178】

(第6の実施の形態)

図13は、本発明の第6の実施の形態におけるAV再生システムのブロック図である。

【0179】

本形態のAV再生システムは、再生装置801、復調/エラー訂正部802、AVデコーダ部803、メモリ804、D/A変換器805、807を備え、AVデコーダ部803は、ビデオデコーダ803Aとオーディオデコーダ803Bを有する。

【0180】

ビデオデコーダ803Aは、図10に示した、本発明の第4の実施の形態のビデオデコーダであり、本発明の第1の実施の形態の信号処理装置、あるいは、第2の実施の形態の信号処理装置を用いて実現出来る。

【0181】

オーディオデコーダ803Bは、図12に示した、本発明の第5の実施の形態のオーディオデコーダである。第5の実施の形態において述べたように、第5の実施の形態のオーディオデコーダの処理は、画像データの処理に比べれば、必要な処理量が少ないために、ビデオデコーダ803Aに適用される第1の実施の形態の信号処理装置、あるいは、第2の実施の形態の信号処理装置の命令並列プロセッサ100(図1、あるいは、図2)によって、並列に処理することが可能であり、別のプロセッサを用意する必要はない。従って、AVデコーダ部803は、第1の実施の形態における一つの信号処理装置、あるいは、第2の実施の形態における一つの信号処理装置によって構成することが出来る。

【0182】

再生装置801は、符号化AV信号を記録したメディアを再生して、再生信号を出力する。この再生装置801は、MPEG−4 AVC規格の符号化AV信号を記録したメディアを再生出来るものであれば、DVDビデオ再生機、HD(ハードディスク)ビデオ再生機、など、いずれの再生機でも良い。

【0183】

復調/エラー訂正部802は、再生装置801が再生した信号を復調し、エラー訂正を行って、AVデコーダ部803に出力する。

【0184】

AVデコーダ部803のビデオデコーダ803Aは、符号化ビデオ信号をデコードして、出力し、D/A変換器805において、アナログ信号に変換して、ビデオ出力806として出力する。

【0185】

AVデコーダ部803のオーディオデコーダ803Bは、符号化オーディオ信号をデコードして、出力し、D/A変換器807において、アナログ信号に変換して、オーディオ出力808として出力する。

【0186】

メモリ804は、デコード前、デコード中、及び/又は、デコード後のAV信号とその他のデータとを保存する。

【0187】

なお、本形態のAV再生システムにおいて、復調/エラー訂正部802の機能の一部、または全部を、再生装置801に持たせてもよい。

【0188】

本形態のAV再生システムは、CATV、インターネット、あるいは、衛星通信などから、送られてくる、MEPG−4 AVC仕様のAV信号を受信して、復調、デコードすることにも利用出来る。この場合には、受信した信号を復調/エラー訂正部802に入力して、上述したプロセスでデコードすることが出来る。さらに、ビデオ出力をディスプレイに表示すれば、ディジタルテレビとしても応用出来る。

【0189】

(第7の実施の形態)

図14は、本発明の第7の実施の形態におけるAV記録システムのブロック図である。

【0190】

本形態のAV記録システムは、AVエンコーダ部825、エラー訂正符号付与/変調部827、記録装置828、メモリ826、及び、A/D変換器822、824を備え、AVエンコーダ部825は、ビデオエンコーダ825Aとオーディオエンコーダ825Bを有する。

【0191】

ビデオエンコーダ825Aは、図3に示した、本発明の第3の実施の形態のビデオエンコーダであり、本発明の第1の実施の形態の信号処理装置、あるいは、第2の実施の形態の信号処理装置でを用いて実現出来る。

【0192】

オーディオエンコーダ825Bは、図11に示した、本発明の第5の実施の形態のオーディオエンコーダである。第5の実施の形態において述べたように、第5の実施の形態のオーディオエンコーダの処理は、画像データの処理に比べれば、必要な処理量が少ないために、ビデオエンコーダ825Aに適用される第1の実施の形態の信号処理装置、あるいは、第2の実施の形態の信号処理装置の命令並列プロセッサ100(図1、あるいは、図2)によって、並列に処理することが可能であり、別のプロセッサを用意する必要はない。従って、AVエンコーダ部825は、第1の実施の形態における一つの信号処理装置、あるいは、第2の実施の形態における一つの信号処理装置によって構成することが出来る。

【0193】

本形態のAV記録システムの動作の概略を説明する。

【0194】

ビデオ入力821は、A/D変換器822でA/D変換され、オーディオ入力823は、A/D変換器824でA/D変換され、それぞれ、AVエンコーダ部825に出力される。

【0195】

AVエンコーダ部825のビデオエンコーダ825Aは、入力されたビデオ信号を、MPEG−4 AVCの仕様に従って、エンコードして、符号化ビデオビットストリームとして出力する。同様に、オーディオエンコーダ825Bは、入力されたオーディオ信号を、MPEG−4 AVCの仕様に従って、エンコードして、符号化オーディオビットストリームとして出力する。

【0196】

エラー訂正/変調部827は、AVエンコーダ部825が出力した符号化ビデオビットストリームと符号化オーディオビットストリームとに、エラー訂正符号を付与した後、変調し記録装置に出力する。

【0197】

記録装置828は、変調されたAV信号を記録媒体に記録する。記録媒体は、DVDなどの光メディア、HD(ハードディスク)などの磁気記録媒体、半導体メモリなどである。

【0198】

メモリ826は、AVエンコーダ部825でのエンコード前、エンコード中、及び/又は、エンコード後のAV信号とその他のデータとを保存する。

【0199】

なお、本形態のAV記録システムにおいて、エラー訂正/変調部827の機能の一部、または全部を、記録装置828に含めることも出来る。

【0200】

本形態のAV記録システムは、入力にビデオカメラを接続して、その信号をMPEG−4 AVC仕様でエンコードして記録する、ビデオカメラシステムとして利用することも出来る。

【0201】

(第8の実施の形態)

図15は、本発明の第8の実施の形態におけるAV記録/再生システムのブロック図である。本形態のAV記録/再生システムは、制御部840、記録/再生装置841、変復調/エラー処理部842、AVエンコーダ/デコーダ部843、AVインターフェース845、及び、メモリ844を備え、AVエンコーダ/デコーダ部843は、ビデオエンコーダ/デコーダ843Aとオーディオエンコーダ/デコーダ843Bを有し、AVインターフェース845は、ビデオの入出力とオーディオの入出力を行う。

【0202】

AVエンコーダ/デコーダ部843は、機能的には、本発明の第3の実施の形態のビデオエンコーダと、第4の実施の形態のビデオデコーダと、第5の実施の形態のオーディオエンコーダとオーディオデコーダの、それぞれの機能と同等の機能を有しており、第1の実施の形態における一つの信号処理装置、又は、第2の実施の形態における一つの信号処理装置によって構築されている。それぞれの動作については、すでに述べたので、ここでは説明を省略する。

【0203】

記録再生装置841は、変調されたMPEG−4 AVC規格のAV信号を、記録/再生するもので、記録媒体は、DVDなどの光メディア、HD(ハードディスク)などの磁気記録媒体、半導体メモリなどである。使用する記録媒体によって、異なる記録/再生機構を有している。

【0204】

変復調/エラー処理部842は、記録時には、AVエンコーダ/デコーダ部843のエンコードしたビデオビットストリームとオーディオビットストリームとに、エラー訂正符号を付与して変調し、記録/再生装置841に送出する。変復調/エラー処理部842は、再生時には、記録/再生装置841が再生したAV信号を復調して、エラー訂正を施した後、ビデオビットストリームとオーディオビットストリームとを、AVエンコーダ/デコーダ部843に、送出する。

【0205】

AVインターフェース845は、再生時には、AVエンコーダ/デコーダ部843がデコードしたビデオ信号とオーディオ信号とを, それぞれD/A変換して、ビデオ出力846とオーディオ出力848を出力する。AVインターフェース845は、記録時には、ビデオ入力847とオーディオ入力849とを、それぞれA/D変換して、AVエンコーダ/デコーダ部843に送出する。

【0206】

メモリ844は、AVエンコーダ/デコーダ部843でのエンコード前、エンコード中、及び/又は、エンコード後のAV信号、並びに、デコード前、デコード中、及び/又は

、デコード後のAV信号と、その他のデータとを保存する。

【0207】

制御部840は、記録/再生装置841、変復調/エラー処理部842、AVエンコーダ/でコーダ部843、及び、AVインターフェース845を制御して、それぞれの記録時と、再生時の機能の切り替えと、データ転送の制御を行う。

【0208】

なお、本形態のAV記録/再生システムにおいて、変復調/エラー処理部842の機能の一部、または全部を、記録/再生装置841に含めることも出来る。

【0209】

以上、詳細に述べたように、本発明の信号処理装置及びそれを用いた電子機器は、今後、MPEG−4 AVCの符号化規格が適用される様々な電子機器への応用が期待される。このような電子機器への応用は、現在MPEG−2で行われているDVDシステムや、ビデオカメラのシステム、携帯電話におけるテレビ電話システムなど家庭内の据え置き端末から電池駆動のモバイル端末までの広い範囲に渡る。

【0210】

それらのシステムでは、MPEG−4 AVC規格を実現するLSIに対して要求される性能が、システムの応用の仕方によって異なる。据え置きのシステムでは、大きな画像サイズを扱うために処理性能が重要であり、一方、携帯端末ではバッテリ寿命を長くするために低消費電力が重要となる。本発明の信号処理装置及びそれを用いた電子機器は、そのいずれにも応用可能である。すなわち、命令並列プロセッサとデータ並列プロセッサと専用ハードウェアを組み合わせることにより、処理性能の向上と消費電力の低減を可能としている。

【0211】

本発明の信号処理装置は、複数のSIMD型プロセッサ(図1の例では、第1データ並列プロセッサ101と第2のデータ並列プロセッサ102)で構成されている。1個のSIMD型プロセッサには、8個の処理要素が含まれており、一つの命令で8種類のデータ流を並列に処理することが出来る。これらのSIMD型プロセッサの搭載数を信号処理装置の利用目的に応じて変更することにより、LSIのアーキテクチャ変更することなしに様々な要求性能に対応することが出来る。

【0212】

例えば、低消費電力が求められる携帯端末向けの信号処理装置では、SIMD型プロセッサを2つ搭載することにより、並列度を16にすることができ、低電圧動作及び動作周波数低減が可能である。

【0213】

また、16並列で使用するのではなく、8個の処理要素からなるSIMD型プロセッサを2組使い別の処理をさせることも可能である。

【0214】

第一のSIMD型プロセッサが動き補償の画素値計算をしている間に、第二のSIMD型プロセッサがDCT処理を行うといったように、全体の処理を分担して、並列処理することによって、処理要素の稼働率を維持したまま、複数の処理が出来る。この結果、演算性能の大幅な改善が可能となる。

【0215】

上記の実施の形態では、MPEG−4 AVC規格に則った応用について述べたが、本発明は、この応用のみに限定されるものではない。本発明の趣旨は、命令並列プロセッサとデータ並列プロセッサと専用ハードウェアを組み合わせることにより、処理性能の向上と消費電力の低減を実現することにあるのであって、本発明の趣旨を逸脱しない限り、種々の適用が可能である。

【産業上の利用可能性】

【0216】

本発明に係る信号処理装置は、例えば、オーディオ及び画像の圧縮伸張処理を、並列プ

ロセッサと専用ハードウェアを用いて高速に行う分野あるいはその関連分野等において利用できる。

【符号の説明】

【0217】

100 命令並列プロセッサ

101 第1データ並列プロセッサ

102 第2データ並列プロセッサ

103 動き検出ユニット

104 デブロックフィルタ処理ユニット

105 可変長符号化/復号処理ユニット

106 入出力インターフェース

110〜116 ローカルメモリ

120 ブリッジユニット

121 第1共有メモリ

122 第2共有メモリ

130 第1命令バス

131 第2命令バス

132 第1データバス

133 第2データバス

301 符号化制御部

302 差分検出部

303 モード切替部

304 4×4DCT変換部

305 量子化部

306 逆量子化部

307 逆4×4DCT変換部

308 可変長符号部

309 再構築部

310、338 デブロックフィルタ

311、339 フレームメモリ

312 動き補償部

313 動き検出部

316 動きベクトル

317 予測画像

318 イントラモード

319 インターモード

331 復号制御部

332 可変長復号部

333 逆量子化部

334 逆4×4DCT変換部

335 再構築部

336 動きベクトル復号部

337 動き補償部

351 圧縮部

352 符号化部

361 復号部

362 伸長部

401 コンテキストモデリング部

402 バイナリ化部

403 出現確立予測部

404 符号化部

405 適応2進算術符号化処理部

406 隣接ブロックA

407 隣接ブロックB

408 符号化対象ブロックC

602 BS条件判定処理部

603、606、804、826、844 メモリ

604 制御部

605 フィルタ処理部

607〜609 フィルタ

801 再生装置

802 復調/エラー訂正部

803 AVデコーダ部

803A ビデオデコーダ

803B オーディオデコーダ

805、807 D/A変換器

822、824 A/D変換器

825 AVエンコーダ部

825A ビデオエンコーダ

825B オーディオエンコーダ

827 エラー訂正符号付与/変調部

828 記録装置

840 制御部

841 記録/再生装置

842 変復調/エラー処理部

843 AVエンコーダ/でコーダ部

843A ビデオエンコーダ/デコーダ

843B オーディオエンコーダ/デコーダ

845 AVインターフェース

901 システム制御部

902 SIMD型並列データ処理装置

903 MIMD型並列データ処理装置

904 共有メモリバス

905 共有メモリ

910、920 全体制御部

911〜914、925〜928 演算器

915〜918、929〜932 ローカルメモリ

921〜924 制御部

1001 画像処理装置

1002 命令メモリ

1003 プロセッサ

1004 SIMD型演算手段

1005 VLC(可変長符号化)処理手段

1006 外部データインターフェース

1007 内部データバス

1008 ビデオデータバス

1009 ビデオ入力装置

1010 ビデオ出力装置

1011 外部メモリ

【技術分野】

【0001】

本発明は、オーディオ及び画像の圧縮伸張処理を、並列プロセッサと専用ハードウェアを用いて高速に行う、画像音声信号処理装置及びそれを用いた電子機器に関するものである。

【背景技術】

【0002】

近年の動画像を扱う画像処理装置及び画像表示装置の高性能化、小型化の動きに呼応して、ISO(International Standard Organization)とITU−T(International Telecommunication

Union−Telecommunication Standardization

Sector)は、共同で次世代の圧縮伸張技術として、MPEG−4 AVC(Advanced Video Coding)を規格化策定中である。MPEG−4 AVCは、4×4画素の整数変換、最大9方向のイントラ予測、7種類のサブマクロブロックタイプ、マクロブロックあたり最大16本の動きベクトル、マルチフレーム参照、ループ内のデブロックフィルタ、算術符号などの新しい技術を導入することによって、画像の高圧縮率を実現し、既に実用化されているMPEG−2方式の50%に圧縮された符号量を目指している。

【0003】

しかし、新たに導入された符号化ツールは、符号化効率を重視したアルゴリズムを採用しているために、その処理量が多く、組み込みシステムへの実装が困難になっている。

【0004】

これまでの符号化方式の圧縮伸張を行う画像音声信号処理装置には、プロセッサによる並列処理と専用ハードウェアによる構成とが用いられてきた。

【0005】

プロセッサによる並列処理手法を使った高速化信号処理の例として、特許文献1がある。この特許文献1に示される例は、制御の流れが1つで、処理されるデータの流れが複数である、SIMD(Single Instruction stream Multiple Data stream)型の並列データ処理装置と、制御の流れもデータの流れも複数である、MIMD(Multiple Instruction stream

Multiple Data stream)型の並列データ処理装置とを組み合わせた、並列処理装置である。

【0006】

図16は、特許文献1の図1から引用した、従来のSIMD型並列データ処理装置902とMIMD型並列データ処理装置903とを組み合わせた信号処理装置のブロック図である。

【0007】

この信号処理装置は、装置全体を制御するシステム制御部901、SIMD型並列データ処理装置902、MIMD型並列データ処理装置903、共有メモリバス904、及び共有メモリ905を備える。

【0008】

システム制御部901は、アプリケーションプログラムの実行制御を行う。

【0009】

SIMD型並列データ処理装置902は、全体制御部910と、演算器911〜914とそれぞれのローカルメモリ915〜918とを有している。一つの演算器と一つのローカルメモリは、一つのプロセッサを構成している。全体制御部910は、プログラムを実行し、演算器911〜914のすべてに同一の命令を発行する。演算器911〜914は、発行された同一の命令の下で、各々のローカルメモリ915〜918に格納されている

データを処理する。

【0010】

MIMD型並列データ処理装置903は、全体制御部920と、制御部921〜924と、演算器925〜928と、ローカルメモリ929〜932とを有している。一つの制御部と一つの演算器と一つのローカルメモリは、一つのプロセッサを構成している。制御部921〜924の各々において別々のプログラムが実行され、演算器925〜928の各々に別々の命令が発効され、ローカルメモリ929〜932の各々に格納されているデータを処理する。全体制御部920は、MIMD型並列データ処理装置903の全体の同期や監視のための制御を行う。

【0011】

以上のような並列データ処理装置においては、対象となる処理が単純で、かつ、データ処理が大量なものをSIMD型並列データ処理装置902で処理し、対象となる処理が複雑で、かつ、データ処理が少量なものをMIMD型並列データ処理装置903で処理していた。

【0012】

一方、対象となる処理に対して最適な演算器を専用ハードウェアで構成することによって、演算性能を改善した高速化手法も用いられている。その例として、特許文献2は、画像処理の可変長符号/復号処理を専用ハードウェア化することにより、処理の高速化を実現した技術を開示している。

【0013】

図17は、特許文献2の図1から引用した、従来のSIMD型並列データ処理装置と専用ハードウェアとを組み合わせた画像処理装置1001のブロック図である。

【0014】

この画像処理装置1001は、外部のビデオデータバス1008を介して、外部のビデオ入力装置1009と、ビデオ出力装置1010と、外部メモリ1011とに接続されている。画像処理装置1001は、命令メモリ1002、プロセッサ1003、SIMD型演算手段1004、VLC(可変長符号化)処理手段1005、外部データインターフェース1006、及び、内部データバス1007を備える。VLC処理手段1005は、専用ハードウェアにより構成されている。

【0015】

プロセッサ1003は、スカラー演算やビット操作演算、比較分岐命令を行うと共に、命令メモリ1002に保持されている命令をデコードし、SIMD型演算手段1004と、VLC処理手段1005と、外部データインターフェース1006と、ビデオ入力装置1009と、ビデオ出力装置1010とを制御する。

【0016】

ビデオ入力装置1009は、外部からのビデオ信号を入力し、ビデオ出力装置1010は外部にビデオデータを出力する。

【0017】

ビデオ入力装置1009から入力された画像データは、外部メモリ1011に転送され、次のステップで、SIMD演算手段1004で行う処理に応じて、外部データインターフェース1006に転送される。SIMD演算手段1004では、動き補償、DCT、量子化の各処理が行われ、変換係数データを得る。次のステップで、VLC変換手段1005において、変換係数データは、可変長符号化され、ビットストリームデータが生成される。

【0018】

SIMD演算手段1004は、8並列のパイプライン演算器で構成されているため、DCTなどの定型処理を効率よく処理することができる。

【0019】

上述した特許文献1に代表される、SIMD型データ並列処理装置とMIMD型並列データ処理装置を組み合わせた信号処理装置は、様々な符号化アルゴリズムに対する柔軟性

を持っている。したがって、並列度を増すことによって、画像処理に十分対応できていた。これは、従来の動き検出処理が、最大16×16ペルで最小8×8ペルのマクロブロックサイズに対するものであったことによる。

【0020】

しかし、MPEG−4 AVCでは、最小のサブマクロブロックサイズが4×4ペルになっているため、従来の信号処理装置では、16並列以上の演算器を用意しても、演算器の処理効率が向上しない。

【0021】

また、MPEG−4 AVCの算術符号化/復号処理では、周辺のマクロブロックのコンテキストによって発生確率を変更しながら処理するために、1ビットづつ符号化しなければならず、並列処理ができない。つまり、従来の信号処理装置では、MIMD型並列データ処理装置の並列度を増加させても、MPEG−4 AVCでの処理性能は改善されない。

【0022】

MPEG−4 AVCのデブロックフィルタにおいても、4×4ペルのサブマクロブロック単位でフィルタパラメータを計算し、その結果に基づいてフィルタ処理を行う。SIMD型演算装置を使えば、フィルタ処理を並列処理することが可能であるが、判定処理の際に演算器を有効に活用できない。

【0023】

また、上述した特許文献2に代表される、SIMD型データ並列処理装置と専用ハードウェアとを組み合わせた信号処理装置では、高い処理性能を要求する算術符号化/復号処理に対しては、専用ハードウェアを採用することによって処理性能が改善されるが、最も処理量の多い動き検出をSIMD型並列データ処理装置で処理するには、以下の問題がある。

【0024】

MPEG−4 AVCでは、1/4画素精度の動き補償が導入され、ハーフペルの画素生成に6タップフィルタ処理を行わなければならない。更に、4×4ペルのサブマクロブロックブロックサイズが導入されたために、1マクロブロックあたり最大16本の動きベクトルの設定が可能である。小さなサブマクロブロックサイズで、1/4画素精度の探索を行い、マクロブロック当たり最大16本の動きベクトルを計算する動き検出の処理は、その処理量が飛躍的に増加している。

【0025】

このような動き検出処理をSIMD型データ並列処理装置で処理させようとすると、演算器の並列度を高め、動作周波数を高く設定しなければならない。そのような能力を持ったSIMD型並列データ装置は、デコード処理においては、その能力に余剰が発生してしまい、装置全体を効率的に利用できない。

【0026】

さらに、SIMD型並列データ処理装置の並列度を高めて処理性能を改善しようとしても、ブロックサイズが4×4ペルであるために、16並列以上にはできない。

【先行技術文献】

【特許文献】

【0027】

【特許文献1】国際公開第91/17507号

【特許文献2】特開2001−309386号公報

【発明の概要】

【発明が解決しようとする課題】

【0028】

そこで本発明は、MPEG−4 AVCの符号化/復号処理のような、大量のデータ処理量が要求される画像処理に対して、高性能で、高効率な画像処理が行える信号処理装置及びそれを用いた電子機器を提供することを目的とする。

【課題を解決するための手段】

【0029】

第1の発明に係る画像音声信号処理装置は、第1データバスと、前記第1データバスに接続され、前記第1データバスを介して共有される第1共有メモリと、前記第1データバスとは独立分離した状態に設けられる第2データバスと、前記第2データバスに接続され、前記第2データバスを介して共有される第2共有メモリと、前記第1データバスと前記第2データバスとを仲介し、前記第1データバスと前記第2データバスとを間接的に接続するブリッジユニットと、音声オーディオの圧縮処理を行い、前記第2データバスに接続される命令並列プロセッサと、前記第1データバスに接続されるが前記第2データバスには直接接続されず、かつ前記命令並列プロセッサとともに同時並行して画像圧縮処理を行うデータ並列プロセッサ及び専用ハードウェアとを備え、命令並列プロセッサ、データ並列プロセッサ及び前記専用ハードウェアのそれぞれは、同時並行して圧縮処理を実行する。

【0030】

第2の発明に係る画像音声信号処理装置は、第1データバスと、前記第1データバスに接続され、前記第1データバスを介して共有される第1共有メモリと、前記第1データバスとは独立分離した状態に設けられる第2データバスと、前記第2データバスに接続され、前記第2データバスを介して共有される第2共有メモリと、前記第1データバスと前記第2データバスとを仲介し、前記第1データバスと前記第2データバスとを間接的に接続するブリッジユニットと、音声オーディオの伸長処理を行い、前記第2データバスに接続される命令並列プロセッサと、前記第1データバスに接続されるが前記第2データバスには直接接続されず、かつ前記命令並列プロセッサとともに同時並行して画像伸長処理を行うデータ並列プロセッサ及び専用ハードウェアとを備え、命令並列プロセッサ、データ並列プロセッサ及び前記専用ハードウェアのそれぞれは、同時並行して伸長処理を実行する。

【0031】

第3の発明に係る画像音声信号処理装置は、命令並列プロセッサと、データ並列プロセッサと、専用ハードウェアとは、それぞれのローカルメモリを有し、データ並列プロセッサのローカルメモリと専用ハードウェアのそれぞれのローカルメモリは第1データバスに接続され、命令並列プロセッサのローカルメモリは第2データバスに接続され、ブリッジユニットは、第1データバスと第2データバスとに互いに独立した状態で接続される各メモリ間のデータ転送を仲介する。

【0032】

第4の発明に係る画像音声信号処理装置は、ローカルメモリを有する入出力インターフェイスをさらに備え、入出力インターフェイスのローカルメモリは第1のデータバスに接続される。

【0033】

第5の発明に係る画像音声信号処理装置は、命令並列プロセッサは、入出力インターフェイスによる入出力処理を制御する。

【発明の効果】

【0034】

本発明によれば、MPEG−4 AVCの符号化/復号処理のような、大量のデータ処理量が要求される画像処理に対して、高性能で、高効率な画像処理が行える信号処理装置及びそれを用いた電子機器を提供すること出来る。

【図面の簡単な説明】

【0035】

【図1】本発明の第1の実施の形態における信号処理装置のブロック図

【図2】本発明の第2の実施の形態における信号処理装置のブロック図

【図3】本発明の第3の実施の形態におけるビデオエンコーダのブロック図

【図4】CABAC算術符号化処理ユニットのブロック図

【図5】符号化対象ブロックと隣接ブロックの配置図

【図6】1/4画素精度の動き補償を説明する図

【図7】本発明の第3の実施の形態におけるデブロックフィルタのブロック図

【図8】デブロックフィルタの処理順序を説明する図

【図9】本発明の第3の実施の形態と他の方式におけるエンコード処理量の比較を説明する図

【図10】本発明の第4の実施の形態におけるビデオエデコーダのブロック図

【図11】本発明の第5の実施の形態におけるオーディオエンコーダのブロック図

【図12】本発明の第5の実施の形態におけるオーディオデコーダのブロック図

【図13】本発明の第6の実施の形態におけるAV再生システムのブロック図

【図14】本発明の第7の実施の形態におけるAV記録システムのブロック図

【図15】本発明の第8の実施の形態におけるAV記録/再生システムのブロック図

【図16】従来のSIMD型並列データ処理装置とMIMD型並列データ処理装置とを組み合わせた信号処理装置のブロック図

【図17】従来のSIMD型並列データ処理装置と専用ハードウェアとを組み合わせた画像処理装置のブロック図

【発明を実施するための形態】

【0036】

第1の構成による信号処理装置は、命令並列プロセッサと、データ並列プロセッサと、複数の専用ハードウェアとを備え、命令並列プロセッサは、音声オーディオの圧縮伸長処理、及び、画像の圧縮伸長処理のうちの非定型でかつ比較的軽い処理を行い、データ並列プロセッサは、画像の圧縮伸張処理のうちの定型でかつ比較的重い処理を行い、複数の専用ハードウェアは、画像の圧縮伸張処理のうちの比較的重い処理を行う。

【0037】

この構成によれば、命令並列のプロセッサとデータ並列のプロセッサと専用ハードウェアとからなる構成で信号処理装置を形成し、命令並列プロセッサで、音声・オーディオの圧縮伸張処理と画像処理のうち非定型処理を行い、データ並列プロセッサで画像処理のうち定型処理を行い、専用ハードウェアで動き検出、可変長符合化、デブロックフィルタ処理などの処理を行うことが出来る。したがって、処理量の多い画像圧縮伸張アルゴリズムの信号処理に対して、ソフトウェアとハードウェアで負荷が分散され、高い処理能力と柔軟性を持った信号処理装置を実現することが出来る。

【0038】

第2の構成による信号処理装置は、請求項1記載の信号処理装置であって、第1命令バスと、第1データバスと、第1共有メモリと、入出力インターフェースとを、さらに備え、命令並列プロセッサと、データ並列プロセッサと、複数の専用ハードウェアと、入出力インターフェースとは、それぞれのローカルメモリを有し、第1命令バスには、命令並列プロセッサと、データ並列プロセッサと、複数の専用ハードウェアとが接続され、第1命令バスを介して、命令並列プロセッサが、データ並列プロセッサ、及び、複数の専用ハードウェアを制御するための命令が通信され、第1データバスには、命令並列プロセッサのローカルメモリと、データ並列プロセッサのそれぞれのローカルメモリと、複数の専用ハードウェアのそれぞれのローカルメモリと、第1共有メモリと、入出力インターフェースのローカルメモリとが接続され、これらのメモリの間でのデータ転送が行われる。

【0039】

この構成によれば、第1の構成による信号処理装置が有する特徴に加えて、さらに、命令バスとデータバスを分離することによって、バスのトラフィックを分散し、処理性能を向上させることが出来る。

【0040】

第3の構成による信号処理装置は、第1、第2の構成による信号処理装置であって、第2データバスと、第2共有メモリと、第1データバスと第2データバスとを接続するブリッジユニットとを、さらに備え、第1データバスには、データ並列プロセッサのそれぞれ

のローカルメモリと、複数の専用ハードウェアのそれぞれのローカルメモリと、第1共有メモリと、入出力インターフェースのローカルメモリとが接続され、これらのメモリの間でのデータ転送が行われ、第2データバスには、命令並列プロセッサのローカルメモリと、第2共有メモリとが接続され、これらのメモリの間でのデータ転送が行われ、ブリッジユニットを介して、第1データバスに接続された各メモリと、第2データバスに接続された各メモリとの間のデータ転送が行われる。

【0041】

この構成によれば、データ処理プロセッサのローカルメモリと、専用ハードウェアの専用メモリと、共有メモリとを第1データバスで接続し、命令並列プロセッサのローカルメモリと共有メモリとを第2データバスで接続する。これにより、大容量のデータを扱う画像処理のデータ転送が第1データバス中心に行われ、オーディオ処理を行う命令並列プロセッサが接続される第2データバスとの負荷分散が実現出来る。

【0042】

第4の構成による信号処理装置は、第1から第3の構成による信号処理装置であって、制御プロセッサをさらに備え、命令並列プロセッサは、制御プロセッサを経由して、データ並列プロセッサと、複数の専用ハードウェアとを制御する。

【0043】

この構成によれば、命令並列プロセッサは、制御プロセッサを経由してデータ並列プロセッサ及び専用ハードウェアを制御することが出来るので、命令並列プロセッサと制御プロセッサの負荷が分散され、より高い処理性能を実現することが出来る。

【0044】

第5の構成による信号処理装置は、第1から第4の構成による信号処理装置であって、第2命令バスをさらに備え、第1命令バスには、命令並列プロセッサと、制御プロセッサと、複数の専用ハードウェアのうちの一部のハードウェアが接続され、第2命令バスには、制御プロセッサと、データ並列プロセッサと、複数の専用ハードウェアのうちの第1命令バスに接続されていない、他の専用ハードウェアが接続され、命令並列プロセッサは、複数の専用ハードウェアのうちの、第1命令バスに接続されている一部のハードウェアを制御し、また、制御プロセッサを経由して、データ並列プロセッサと、複数の専用ハードウェアのうちの第1命令バスに接続されていない、他の専用ハードウェアとを制御する。

【0045】

この構成によれば、命令並列プロセッサは、第1命令バスを介して、制御プロセッサと、一部の専用ハードウェアのみを制御すればよく、定型的な処理を行うデータ並列プロセッサと専用ハードウェアは、第2命令バスを介して、制御プロセッサによって制御されるため、命令バスにおける命令の輻輳を回避でき、効率良く信号処理を行うことが出来る。

【0046】

第6の構成による信号処理装置では、データ並列プロセッサの並列度は、圧縮伸長処理する画像サイズによって定められる。

【0047】

この構成によれば、圧縮伸張の対象となる画像のサイズによって、データ並列プロセッサの並列度を変更するので、同一のプロセッサアーキテクチャでありながら、多様な画像サイズに対応出来る信号処理装置を提供出来る。

【0048】

第7の構成による信号処理装置では、データ並列プロセッサの並列度は、信号処理装置に供給される電源電圧や、動作周波数によって定められる。

【0049】

この構成によれば、LSIに共有される電源電圧や動作周波数によって、データ並列プロセッサの並列度を変更出来る。データ並列プロセッサの並列度を増大させることによって、動作周波数を下げ、信号処理装置の消費電力を低減することが出来るので、モバイル端末などの電子機器への応用が特に有効となる。

【0050】

第8の構成による信号処理装置では、専用ハードウェアが行う処理は、可変長符号化処理、可変長復号処理、ビデオ入出力処理、動き検出処理、動き補償処理、DCT(離散コサイン変換)処理、逆DCT処理、量子化処理、逆量子化処理、及び、デブロックフィルタ処理の少なくとも一つを含む。

【0051】

この構成によれば、圧縮伸張処理の中で、動き検出、可変長符号/復号、デブロックフィルタなどの処理量の多いモジュールを専用ハードウェアで処理することにより、命令並列プロセッサ及びデータ並列プロセッサの動作周波数の増大を抑制することが出来る。

【0052】

第9の構成による信号処理装置では、複数の専用ハードウェアのうちの、第1命令バスに接続される一部のハードウェアが行う処理は、可変長符号化処理、及び/又は、可変長復号処理である。

【0053】

この構成によれば、可変長符号化処理、及び/又は、可変長復号処理を行う専用ハードウェアを、命令並列プロセッサによって、直接、かつ、頻繁に制御出来る。したがって、可変長符号化処理、及び/又は、可変長復号処理を繊細に、かつ多様に制御出来る。

【0054】

第10の構成による電子機器は、第1から第9の構成による信号処理装置を用いた電子機器であって、信号処理装置は、音声オーディオの圧縮処理、音声オーディオの伸長処理、画像圧縮処理、及び、画像伸長処理の、少なくとも一つの処理を行う。

【0055】

この構成によれば、請求項1から9記載の信号処理装置が有する特徴を生かした、電子機器を提供出来る。

【0056】

第11の構成による電子機器は、第1から第9の構成による信号処理装置と、再生機構を有する再生装置と、復調・エラー訂正部と、メモリと、複数のD/A変換器とを備え、再生装置は、変調された符号化信号を記録媒体から再生し、復調・エラー訂正部は、再生装置が再生した変調された符号化信号を復調して、エラー訂正を行い、符号化データとして出力し、信号処理装置は、復調・エラー訂正部が出力した符号化データをデコードして、ビデオデータ及びオーディオデータとして出力し、メモリは、デコード処理前、処理中、及び/又は、処理後のデータを格納し、複数のD/A変換器は、信号処理装置が出力したビデオデータ及びオーディオデータをD/A変換して、アナログのビデオ出力及びアナログのオーディオ出力を出力する。

【0057】

この構成によれば、符号化データを高速に、効率よくデコードでき、消費電力が小さい再生電子機器を実現出来る。

【0058】

第12の構成による電子機器は、第1から第9の構成による信号処理装置と、複数のA/D変換器と、メモリと、エラー訂正・変調部と、記録機構を有する記録装置とを備え、複数のA/D変換器は、入力されたアナログのビデオ入力及びアナログのオーディオ入力をA/D変換して、ビデオデータ及びオーディオデータを出力し、信号処理装置は、複数のA/D変換器が出力したビデオデータ及びオーディオデータをエンコードして、符号化データを出力し、メモリは、エンコード処理前、処理中、及び/又は、処理後のデータを格納し、エラー訂正・変調部は、信号処理装置がエンコードした符号化データに、エラー訂正符号を付加して、変調し、符号化信号として出力し、記録装置は、エラー訂正・変調部が出力した符号化信号を、記録媒体に記録する。

【0059】

この構成によれば、AV信号を、高速に効率よくエンコードでき、消費電力が小さい記録電子機器を実現出来る。

【0060】

第13の構成による電子機器は、第11の構成による電子機器と第12の構成による電子機器とを一体的に構成される。

【0061】

この構成によれば、AV信号を、高速に効率よくエンコード/デコードでき、消費電力が小さい、記録機能と再生機能とを一体化した電子機器を実現出来る。

【0062】

次に、図面を参照しながら、本発明の実施の形態を説明する。

【0063】

(第1の実施の形態)

図1は、本発明の第1の実施の形態における信号処理装置のブロック図である。本形態の信号処理装置は、ローカルメモリ110を有する命令並列プロセッサ100、ローカルメモリ111を有する第1データ並列プロセッサ101、ローカルメモリ112を有する第2データ並列プロセッサ102、ローカルメモリ113を有する動き検出ユニット103、ローカルメモリ114を有するデブロックフィルタ処理ユニット104、ローカルメモリ115を有する可変長符号化/復号処理ユニット105、ローカルメモリ116を有する入出力インターフェース106、第1共有メモリ121、第1命令バス130、及び、第1データバス132を備え、第1命令バス130には、各プロセッサ100〜102と各ユニット112〜116とが接続され、第1データバス132には、ローカルメモリ110〜116と、第1共有メモリ121と、入出力インターフェース106とが接続されている。可変長符号化/復号処理ユニット105は、さらに、外部装置に対してビットストリーム入出力135を有しており、入出力インターフェース106は、外部装置に対してオーディオ入出力136とビデオ入出力137を有している。

【0064】

第1データ並列プロセッサ101と第2データ並列プロセッサ102とに採用されているSIMD型プロセッサには、8個の処理要素が含まれており、1個の命令で8個のデータ流を並列に処理することが出来る。

【0065】

動き検出ユニット103と、デブロックフィルタ処理ユニット104と、可変長符号化/復号処理ユニット105と、入出力インターフェース106とは、それぞれ専用のハードウェアである。

【0066】

次に、本形態の動作の概略を、画像の符号化処理を例として、説明する。

【0067】

外部から入力されたビデオ信号は、A/D変換された後、入出力インターフェース106より、第1データバス132を経由して、第1共有メモリ121に格納される。

【0068】

動き検出ユニット103は、第1共有メモリ121に格納されている前フレームの画像データと、現フレームの画像データを基に、動きベクトルを算出する。

【0069】

第1データ並列プロセッサ101は、第1共有メモリ121に格納されている前フレームの画像データと、動き検出ユニット103が算出した動きベクトルを基に、動き補償処理を行って、予測画像データを算出する。また、この予測画像データに対する現フレームの画像データの差分画像データを算出する。

【0070】

第2データ並列プロセッサ102は、差分画像データをDCT変換処理し、さらに、得られたDCT係数を量子化処理する。また、第2データ並列プロセッサ102は、量子化DCT係数を逆量子化し、さらに、逆DCT変換処理して、差分画像データを算出し、第1データ並列プロセッサ101が処理した予測画像データとから、再構築画像データを算出する。

【0071】

本形態の信号処理装置では、第1データ並列プロセッサ101が、動き補償処理の画素値計算を行っている間に、第2データ並列プロセッサ102が、DCT変換処理を行う。このように、2つのデータ並列プロセッサの稼働率を維持して、それぞれに別々の処理をさせることができ、演算性能の改善を図っている。

【0072】

デブロックフィルタ処理ユニット104は、再構築画像データに対して、デブロックフィルタ処理をして、ブロックノイズを除去し、第1共有メモリ121に格納する。

【0073】

可変長符号化/復号処理ユニット105は、量子化DCT係数と動きベクトルとを、算術符号を用いた可変長符号化処理し、ビットストリームとして出力する。

【0074】

命令並列プロセッサ100は、上述した各種の処理の全体的な制御を、第1命令バス130を介して行う。また、命令並列プロセッサ100は、予測画像の生成を、イントラ予測符号化で行うか、あるいは、インター予測符号化で行うかの符号化モードの判定を行う。

【0075】

各プロセッサと各ユニットと間のデータ転送は、第1データバス132を介して行われる。

【0076】

このように、画像圧縮・伸長処理のうち逐次的な処理を命令並列プロセッサ100が行い、画像圧縮・伸長処理のうち定型的な処理を第1データ並列プロセッサ101と第2データ並列プロセッサ102とが行い、さらに、動き検出処理、デブロックフィルタ処理、及び、可変長符号化処理といった重い処理を専用ハードウェアで行うことにより、高効率な画像処理を実現出来る。

【0077】

本形態における、第1データ並列プロセッサ101と第2データ並列プロセッサ102との処理対象の分担区分は、一例であって、その他の区分でも良い。あるいは、プロセッサの性能によっては、第1データ並列プロセッサ101と第2データ並列プロセッサ102の処理を一つのデータ並列プロセッサで行っても良い。

【0078】

さらに、第1データ並列プロセッサ101が行っている動き補償処理は、動き検出ユニット103が行っても良い。

【0079】

(第2の実施の形態)

図2は、本発明の第2の実施の形態における信号処理装置のブロック図である。図2において、図1と同様の構成要素については、同一の符号を付すことにより、説明を省略する。

【0080】

本形態の信号処理装置は、第1の実施の形態の信号処理装置に比べ、制御プロセッサ107、第2共有メモリ122、第2命令バス131、第2データバス133、及び、第1データバス132と第2データバス133とを接続するブリッジユニット120とを、さらに備える。

【0081】

第1命令バス130には、命令並列プロセッサ100と、制御プロセッサ107と、可変長符号化/復号処理ユニット105とが接続されている。第2命令バスには、制御プロセッサ107、第1データ並列プロセッサ101、第2データ並列プロセッサ102、動き検出ユニット103、及び、デブロックフィルタ処理ユニット104とが接続されている。

【0082】

第1データバスには、ローカルメモリ111〜115、第1共有メモリ121、入出力

インターフェース106、及び、ブリッジユニット120とが接続されている。第2データバスには、ローカルメモリ110と第2共有メモリ122とブリッジユニット120とが接続されている。

【0083】

本形態の信号処理装置は、第1の実施の形態に比べ、データの並列処理をさらに強固にしたものである。すなわち、本形態において導入された制御プロセッサ107は、命令並列プロセッサ100からの命令を受けて、第1データ並列プロセッサ101、第2データ並列プロセッサ102、動き検出ユニット103、及び、デブロックフィルタ処理ユニット104とを、第2命令バス131を介して制御する。その結果、本形態の信号処理装置は、各データ並列プロセッサ及び専用ハードウェアでの並列処理がより迅速に行えるように構成されている。

【0084】

さらに、本形態の第2共有メモリ122は、命令並列プロセッサ100に関係するデータと、第1データバス132に接続されている各構成要素が扱うデータのうち、比較的アクセス頻度が低いデータとを格納する。この構成により、第1共有メモリ121の負荷が軽減され、信号処理装置全体の処理効率が改善される。

【0085】

本形態の動作は、以下に述べる第3の実施の形態において、詳述する。

【0086】

(第3の実施の形態)

図3は、本発明の第3の実施の形態におけるビデオエンコーダのブロック図である。

【0087】

本形態のビデオエンコーダは、MPEG−4 AVCに対応出来るエンコーダであり、各構成要素には、MPEG−4 AVCに対応するビデオエンコーダの各機能を的確に表現した名前が付されている。

【0088】

図3に示した本形態のビデオエンコーダは、第2の実施の形態の信号処理装置によって構成されている。そこで、まず、図3の構成要素と、図2の構成要素との対応関係を示す。

【0089】

符号化制御部301とモード切替部303の処理は、図2の命令並列プロセッサ100が行う。

【0090】

動き補償部312と差分検出部302の処理は、図2の第1データ並列プロセッサ101が行う。

【0091】

4×4DCT変換部304、量子化部305、逆量子化部306、逆4×4DCT変換部307、及び、再構築部309の処理は、図2の第2データ並列プロセッサ102が行う。

【0092】

可変長符号化部308は、図2の可変長符号化/復号処理ユニット105に相当し、デブロックフィルタ310は、図2のデブロックフィルタ処理ユニット104に相当し、フレームメモリ311は、図2の第1共有メモリ121に相当し、動き検出部313は、図2の動き検出ユニット103に相当する。

【0093】

次に、MPEG−4 AVCの主要な信号処理を、本形態の各部の動作を参照して、説明する。

【0094】

まず、図3を参照して、エンコード処理を説明する。ビデオ入力314は、イントラ符号化の場合、4×4DCT変換部304において離散コサイン変換(直交変換)されDC

T係数が求められる。次に、量子化部305においてDCT係数が量子化される。

【0095】

MPEG−2やH.263などの既存の符号化規格では、8×8ブロックサイズに対して、実数精度のDCTが採用されており、DCT精度を規定しなければミスマッチが発生した。しかし、MPEG−4 AVCでは、4×4ブロックサイズに対して、整数精度のDCT変換が適用されており、この結果、DCT精度に起因するミスマッチが発生しなくなった。

【0096】

量子化されたDCT係数は、可変長符号部308において、算術符号化器を使ってエントロピー符号化される。その詳細は、後述する。

【0097】

次に、可変長符号化/復号処理について説明する。

【0098】

MPEG−4 AVCの概要は、非特許文献1「MPEG−4 AVC|H.264の概要と標準化動向」(鈴木輝明;情報処理学会、オーディオビジュアル複合情報処理38―13、69〜73頁、2002年11月)で説明されている。以下では、非特許文献1に基づいて説明する。

【0099】

マクロブロックの個数、動きベクトルの差分、変換係数などのシンタックス要素の可変長符号化では、CAVLC(Context Adaptive Variable Length Coding;コンテキスト適応可変長符号化)と、CABAC(Context Adaptive Binary Arithmetic Coding;コンテキスト適応2進算術符号化)という2種類のエントロピー符号化方式が使い分けられる。

【0100】

ここでは、メインプロファイルで用いられるCABACという算術符号化方式について説明する。算術符号は、長さ「1」の線分を、符号化しようとするシンボルの出現確率に従って分割し、その分割された線分と符号化しようとするシンボルとが1対1に対応することから、その線分について符号化するものである。その線分を代表する2進数が符号となるため、線分の区間が広い、すなわち符号化しようとするシンボルの出現確率が高いほど、そのシンボルは短い2進数で表現でき、その結果圧縮率が高くなる。そこで、対象ブロックの符号化を行う場合に、周辺ブロックのコンテキストに応じて出現確率を操作して、圧縮率が高くなるように制御される。

【0101】

図4は、CABAC算術符号化処理ユニットのブロック図である。これは、非特許文献1の図7から引用したものである。図4に示すCABAC算術符号化処理ユニットは、コンテキストモデリング部401と、バイナリ化部402と、適応2進算術符号化処理部405とを備え、適応2進算術符号化処理部405は、出現確立予測部403、及び、符号化部404とを有する。

【0102】

コンテキスト・モデリングは、各シンボルを符号化する際の確率モデルである。各シンタックス要素には、コンテキストが定義されており、このコンテキストに応じて確率テーブルを切り替えて算術符号を行う。

【0103】

図5は、符号化対象ブロックと隣接ブロックの配置図である。図5において、符号化対象ブロックC408を符号化する際、隣接ブロックA406と隣接ブロックB407の状態に応じて、符号化対象ブロックC408のコンテキストが決定される。

【0104】

以上のような算術符号処理において、可変長符号化された符号のデコード処理は、出現確率情報をデコーダで解釈し、その情報に基づいて再構成するという逐次処理である。ま

た、出現確率の操作は、テーブルによって行われることから、これらの符号化処理と復号処理を、VLIW(極長命令語)対応の命令並列プロセッサ(上述した第2の実施の形態では、図2に示す命令並列プロセッサ100に相当)や、SIMD型のデータ並列プロセッサ(同じく、第1データ並列プロセッサ101、あるいは、第2データ並列プロセッサ102に相当)で行ったのでは、処理性能は、改善されない。むしろ、これらの処理は、専用ハードウェア(同じく、可変長符号化/復号処理ユニット105に相当)を用いて処理することによって、命令並列プロセッサとデータ並列プロセッサの負荷分散ができ、その結果、動作周波数が低減され、処理装置の周波数バランスを良好にすることが出来る。これが、本実施の形態において、図3に示す可変長符号化部308を、図2に示す専用ハードウェアである可変長符号化/復号処理ユニット105によって、処理している理由である。

【0105】

図3において、量子化部305によって量子化されたDCT係数は、逆量子化部306において逆量子化された後、逆4×4DCT変換部307において、逆DCT変換され、再構築部309において、画像が再構築される。再構築された画像は、デブロックフィルタ310によって、デブロックフィルタ処理が施され、4×4画素境界で画素値が書き換えられる。デブロックフィルタ処理については、後述する。

【0106】

次に、図3の動き補償部312において行う1/4画素精度の動き補償処理について、図6を参照して、説明する。図6は、1/4画素精度の動き補償を説明する図である。

【0107】

動き補償とは、参照する画像から予測画像を構成する場合に、動きベクトルの情報を用いて、符号化しようとする画像により近い予測画像を構成しようとするものである。予測誤差が少ないほど、符号量が小さくなるため、MPEG−4 AVCでは1/4画素精度の動き補償が採用されている。動きベクトルは、ブロック単位での平行移動を表す2つのパラメータ(水平方向の移動距離と垂直方向の移動距離)から構成される。

【0108】

動きベクトルが指し示した参照画像の予測画像は、下記の方法によって求められる。

【0109】

図6において、画素A、B、C、D、E、F、G、H、I、J、K、L、M、N、P、Q、R、S、T、Uは、それぞれ整数位置の画素であり、画素aa、bb、cc、dd、ee、ff、gg、hh、及び、画素b、h、j、m、sは、それぞれ1/2精度の画素であり、画素a、c、d、e、f、g、i、k、n、p、q、rは、それぞれ1/4精度の画素である。

【0110】

これらの画素の画素値を求める手順について説明する。まず、1/2精度の画素bは、以下のように求められる。画素bの水平方向の近傍の画素E、F、G、H、I、Jを変数として、(数1)で定義される6タップフィルタを用いて、中間データb1が生成される。

【0111】

【数1】

【0112】

次に、この中間データb1を、(数2)によって、丸め処理と正規化の後、0〜255にクリップ処理して、画素bが求まる。

【0113】

【数2】

【0114】

ここに、Clip(X)は、カッコ内の変数Xを0から255の範囲にクリップする関数である。すなわち、変数Xが0未満であれば、b=0とし、変数Xが0から255の範囲であれば、b=Xとし、変数Xが256以上であれば、b=255とする。

【0115】

同様に、1/2精度の画素hは、次のように求められる。画素hの垂直方向の近傍の画素A、C、G、M、R、Tを変数として、(数3)で定義される6タップフィルタを用いて、中間データh1が生成される。

【0116】

【数3】

【0117】

この中間データh1を、(数4)によって、丸め処理と正規化の後、0〜255にクリップ処理して、画素hが求まる。

【0118】

【数4】

【0119】

1/4精度の画素a、c、d、f、i、k、n、q、は、(数5)に示すように、それぞれの近傍の2画素を用いて、丸め付き平均により求められる。

【0120】

【数5】

【0121】

1/4精度の画素e、g、p、rは、同様に、(数6)に示すように、それぞれの近傍の2画素を用いて、丸め付き平均により求められる。

【0122】

【数6】

【0123】

以上のような予測画像の生成において、動きベクトルはサブマクロブロック毎に設定することが可能である。最も小さなサブマクロブロックである4×4の場合においては、整数位置の画素から実数位置の16箇所の画素を6タップフィルタを使って内挿しなければならない。画素の内挿では画素間にデータの依存関係がないため並列に処理が可能である。従って、本実施の形態に示すように、SIMD型データ並列プロセッサを使うと、効率よくフィルタ処理が出来る。

【0124】

次に、デブロックフィルタ処理について説明する。

【0125】

MPEG−4 AVCでは、4×4画素単位でDCT処理を行うために、ブロックの境界にブロック歪みが発生する。デブロックフィルタ処理は、ブロックの境界にフィルタをかけて歪みを平滑化するものである。画像の4×4境界に施すフィルタ処理は、Boundary Strength(BS)という境界の強度の値に応じて、フィルタの強度がブロック境界毎に最も適した値に調整される、適応的なフィルタ処理である。すなわち、境界の強度BSは、その境界にフィルタをかけるかどうかの判定と、フィルタをかける際の画素値変動の最大値を定義するために用いられる。

【0126】

図7は、本発明の第3の実施の形態におけるデブロックフィルタ310のブロック図である。本形態のデブロックフィルタ310は、BS条件判定処理部602、メモリ603、制御部604、及び、フィルタ処理部605を備え、フィルタ処理部605は、メモリ606とフィルタ607〜609を有する。

【0127】

図7に示すデブロックフィルタ310において、BS条件判定処理部602は、境界の強度BSを計算し、その結果を判定して、制御パラメータ613をフィルタ処理部605に渡す。フィルタ処理部605は、制御パラメータ613に応じてフィルタ処理を行う。

【0128】

デブロックフィルタ310の処理を、図8を参照して、説明する。

【0129】

図8は、本発明の第3の実施の形態におけるデブロックフィルタ310の処理順序を示す。フィルタ処理は、図8に示すように、境界[1]〜[4]に対する水平フィルタ処理が行われ、続いて、境界[5]〜[8]に対する垂直フィルタ処理が行われる。

【0130】

境界の強度 BS=4 の時のフィルタ処理について説明する。4×4のサブマクロブロックの境界[1]における最初のフィルタ処理では、境界[1]を挟んだ画素p3、p2、p1、p0、q0、q1、q2、q3の8画素を入力として、画素p2、p1、p0、q0、q1、q2の6画素を、画素P2、P1、P0、Q0、Q1、Q2に書き換える。

【0131】

画素P2、P1、P0は、(数7)の条件式によってフィルタ処理の式を切り換え、(数8)と(数9)とによって求められる。

【0132】

【数7】

【0133】

(数7)の条件が満たされる場合は、画素P0、P1、P2を(数8)から求める。

【0134】

【数8】

【0135】

(数7)の条件が満たされない場合は、画素P0、P1、P2を(数9)から求める。

【0136】

【数9】

【0137】

また、画素Q0、Q1、Q2は、(数10)の条件式によってフィルタ処理の式を切り換え、(数11)と(数12)とによって求められる。

【0138】

【数10】

【0139】

(数10)の条件が満たされる場合は、画素Q0、Q1、Q2を(数11)から求める。

【0140】

【数11】

【0141】

(数10)の条件が満たされない場合は、画素Q0、Q1、Q2を(数12)から求める。

【0142】

【数12】

【0143】

以上のように、量子化パラメータと画素値によって適応的にフィルタ処理を切り換える場合、SIMD型データ並列プロセッサによるデータ処理装置では、BS条件判定を並列

に処理できないために、並列設置された演算器が有効に活用できない。それに代わって、図7に示したように、デブロックフィルタ処理を、BS条件判定処理部602とフィルタ処理部605とからなる専用ハードウェアで実行すれば、BS計算処理とフィルタ処理を別々に演算することができ、BS条件の判定処理が高速化され、フィルタ処理が並列処理出来る。その結果、デブロックフィルタ処理を、効率よく行うことが出来る。さらに、フィルタ処理部は、輝度Yと色差UVにデータの依存がないため、並列動作が可能であり、演算器を導入すると更に処理サイクル数の削減が可能である。これが、本実施の形態において、図3に示すデブロックフィルタ310を、図2に示す専用ハードウェアであるデブロックフィルタ処理ユニット104によって、処理している理由である。

【0144】

図3に示す本形態のビデオエンコーダにおいて、デブロックフィルタ310によりデブロックフィルタ処理された画像は、出力画像として用いられるだけでなく、そのフレーム以降の参照画像として参照されるため、フレームメモリ311に保存しておく。

【0145】

次に、図3に示すビデオエンコーダを、本形態の信号処理装置で実現した場合の所要処理量と、他の方式によって構成した場合の所要処理量とを比較する。

【0146】

図9は、本発明の第3の実施の形態と他の方式におけるエンコード処理量の比較を示す図である。

【0147】

図9において、方式1は、1クロックサイクルあたり1命令を発行出来るプロセッサを用いて、図3に示すビデオエンコーダを構成し、全てソフト処理した場合である。方式2は、MIMD型並列データ処理装置とSIMD型並列データ処理装置を組み合わせて、図3に示すビデオエンコーダを構成し、全てソフト処理した場合である。方式3は、SIMD型並列データ処理装置とVLCの専用ハードウェアを用いて、図3に示すビデオエンコーダを構成した場合である。方式4は、VLIW型並列データ処理装置とSIMD型並列データ処理装置と専用ハードウェアを用いて、図3に示すビデオエンコーダを構成した場合であり、本実施の形態に相当する。すなわち、方式4のVLIW型並列データ処理装置は、本形態の図2に示す、命令並列プロセッサ100に相当し、SIMD型並列データ処理装置は、同じく、第1データ並列プロセッサ101と第2データ並列プロセッサ102に相当し、専用ハードウェアは、同じく、動き検出ユニット103と、デブロックフィルタ処理ユニット104と、可変長符号化/復号処理ユニット105に、相当する。

【0148】

エンコード処理において、処理量が多いのは、動き検出と動き補償と可変長符号化とデブロックフィルタである。これらの処理量の具体的な数値を各方式について比較すると、以下のようになる。

【0149】

方式1においては、動き検出処理が「3048」メガサイクル、可変長符号化処理が「1000」メガサイクル、デブロックフィルタ処理が「321」メガサイクル、動き補償処理が「314」メガサイクル、その他の処理が「217」メガサイクルである。全処理量は、「4900」メガサイクルである。

【0150】

方式2においては、動き検出処理が「381」メガサイクル、可変長符号化処理が「333」メガサイクル、デブロックフィルタ処理が「107」メガサイクル、動き補償処理が「39」メガサイクル、その他の処理が「52」メガサイクルである。全処理量は、「900」メガサイクルである。

【0151】

方式3においては、動き検出処理が「381」メガサイクル、可変長符号化処理が「67」メガサイクル、デブロックフィルタ処理が「80」メガサイクル、動き補償処理が「39」メガサイクル、その他の処理が「30」メガサイクルである。全処理量は、「60

7」メガサイクルである。

【0152】

方式4においては、動き検出処理が「203」メガサイクル、可変長符号化処理が「67」メガサイクル、デブロックフィルタ処理が「21」メガサイクル、動き補償処理が「21」メガサイクル、その他の処理が「29」メガサイクルである。全処理量は、「352」メガサイクルである。

【0153】

動き検出処理は、対象マクロブロックと参照マクロブロックの画素値の差分絶対値和が最も少ないポジション(動きベクトル)を選択する処理である。MPEG−4 AVCの場合、4×4のサブマクロブロック単位で動きベクトルを設定することが可能である。従って、16画素の差分絶対値和の計算が並列に処理出来る。方式2及び方式3では、この動き検出の処理を、8並列のSIMD型並列データ処理装置で処理させたものであり、方式1に比べ大幅な高速化が実現している。方式4は、16並列で差分絶対値和の計算が可能な専用ハードウェアで、動き検出を処理しているため、SIMD型並列データ処理装置よりも更に高速な処理が実現している。

【0154】

動き補償処理は、動きベクトルが指し示した参照画像を、1/4画素精度で求める処理である。この処理においても、4×4サブマクロブロック単位で処理が行われるため、並列処理が可能である。動き検出処理と同様に、方式2と方式3は、8並列のSIMD型並列データ処理装置で、方式4は、専用ハードウェアで動き補償処理を行っており、大幅な高速化を達成している。

【0155】

可変長符号化処理は、CABACと呼ばれる算術符号処理で、周辺ブロックのコンテキストに応じて対象ブロックの発生確率を変化させて復号を行う逐次処理である。方式2では、可変長符号化の処理を、4命令発行可能なMIMD型並列データ処理装置を用いて行うことを想定しているが、方式1の1命令発行のプロセッサに比べて、最大でも1/3の処理量である。方式3と方式4は、専用ハードウェアでVLC処理を行うもので、判定処理やテーブル検索が高速に行われるため、方式1に比べて、1/15に高速化が可能である。

【0156】

デブロックフィルタ処理は、方式2がMIMD型並列データ処理装置による並列処理で、方式3がSIMD型並列データ処理装置による並列処理である。MIMD型では、フィルタ処理の性能が、SIMD型では、BS判定処理の性能が改善されないため、1/3〜1/4の高速化しか得られない。一方、方式4は、デブロックフィルタ処理を専用ハードウェアで実行するもので、BS判定処理とフィルタ処理を分割し、パイプライン動作させることによって、方式1に比べ、1/15の高速化が可能である。

【0157】

以上、明らかなように、本形態のように、動き検出処理と動き補償処理と可変長符号化処理とデブロックフィルタ処理とを、専用ハードウェアで構成することによって、大幅な高速化が可能である。

【0158】

(第4の実施の形態)

図10は、本発明の第4の実施の形態におけるビデオデコーダのブロック図である。

【0159】

本形態のビデオデコーダは、MPEG−4 AVCに対応出来るデコーダであり、各構成要素には、MPEG−4 AVCに対応するビデオデコーダの各機能を的確に表現した名前が付されている。

【0160】

図10に示した本形態のビデオデコーダは、第2の実施の形態の信号処理装置によって構成されている。そこで、まず、図10の構成要素と、図2の構成要素との対応関係を示

す。

【0161】

復号制御部331の処理は、図2の命令並列プロセッサ100が行う。

【0162】

動きベクトル復号部336と動き補償部337の処理は、図2の第1データ並列プロセッサ101が行う。

【0163】

逆量子化部333、逆4×4DCT変換部334、及び、再構築部335の処理は、図2の第2データ並列プロセッサ102が行う。

【0164】

可変長復号部332は、図2の可変長符号化/復号処理ユニット105に相当し、デブロックフィルタ338は、図2のデブロックフィルタ処理ユニット104に相当し、フレームメモリ339は、図2の第1共有メモリ121に相当する。

【0165】

本形態のビデオデコーダの動作の概略を説明する。

【0166】

可変長復号部332に、算術符号で符号化された符号化ビデオ入力341が入力され、復号されて、量子化DCT係数と動きベクトルの差分が求められる。得られた量子化DCT係数は、逆量子化部333において逆量子化され、さらに、逆4×4DCT変換部334において逆DCT変換されて、差分画像データが得られる。

【0167】

一方、可変長復号部332で得られた動きベクトルの差分から、動きベクトル復号部336において、動きベクトルが求められ、動き補償部337において、フレームメモリ339に格納されている参照画像と動きベクトルとから、予測画像が求められる。

【0168】

再構築部335において、前述の差分画像データと予測画像から、新しい画像が再構築されて、ビデオ出力342として出力される。出力されたビデオ出力342は、同時に、デブロックフィルタ338においてデブロックフィルタ処理された後、フレームメモリ339に格納される。

【0169】

逆量子化部333や逆4×4DCT変換部334の制御は、復号制御部331が行う。

【0170】

デブロックフィルタ処理をはじめ、逆量子化処理、逆DCT変換処理は、上述した第3の実施の形態の場合と同様であり、ここでは説明を省略する。

【0171】

本形態においても、可変長復号処理とデブロックフィルタ処理とを、専用ハードウェアで処理することによって、大幅な高速化が実現出来ている。

【0172】

また、上述した説明は、本形態のビデオエデコーダを、図2に示す本発明の第2の実施の形態の信号処理装置で実現する例を取り上げたが、本形態のビデオエデコーダは、本発明の第1の実施の形態の信号処理装置を用いて実現することも出来る。また、各プロセッサが分担する処理対象は、適宜変更することも出来る。

【0173】

(第5の実施の形態)

図11は、本発明の第5の実施の形態におけるオーディオエンコーダのブロック図であり、図12は、同じく、本発明の第5の実施の形態におけるオーディオデコーダのブロック図である。

【0174】

図11に示すオーディオエンコーダにおいては、オーディオ入力353は、圧縮部351において、サンプリング及び量子化を含む圧縮処理が行われ、符号化部352において

、符号化が行われ、符号化オーディオ出力354として、出力される。

【0175】

図12に示すオーディオデコーダにおいては、符号化オーディオ入力363は、復号部361において、復号が行われ、伸長部362において、逆量子化され伸長処理が行われる。

【0176】

オーディオのエンコーディング及びデコーディングは、MPEG−4 AVCのビデオのエンコーディングやデコーディングに比べて、必要な処理量が少ないために、いずれのプロセッサを用いても処理出来る。

【0177】

本形態のオーディオエンコーダとオーディオデコーダとを、第1の実施の形態の信号処理装置で実現する場合には、図11に示す圧縮部351と符号化部352の処理と、図12に示す復号部361と伸長部362の処理とは、図1に示す命令並列プロセッサ100によってお行う。これらの処理は、十分な余裕を持って実行出来る。

【0178】

(第6の実施の形態)

図13は、本発明の第6の実施の形態におけるAV再生システムのブロック図である。

【0179】

本形態のAV再生システムは、再生装置801、復調/エラー訂正部802、AVデコーダ部803、メモリ804、D/A変換器805、807を備え、AVデコーダ部803は、ビデオデコーダ803Aとオーディオデコーダ803Bを有する。

【0180】

ビデオデコーダ803Aは、図10に示した、本発明の第4の実施の形態のビデオデコーダであり、本発明の第1の実施の形態の信号処理装置、あるいは、第2の実施の形態の信号処理装置を用いて実現出来る。

【0181】

オーディオデコーダ803Bは、図12に示した、本発明の第5の実施の形態のオーディオデコーダである。第5の実施の形態において述べたように、第5の実施の形態のオーディオデコーダの処理は、画像データの処理に比べれば、必要な処理量が少ないために、ビデオデコーダ803Aに適用される第1の実施の形態の信号処理装置、あるいは、第2の実施の形態の信号処理装置の命令並列プロセッサ100(図1、あるいは、図2)によって、並列に処理することが可能であり、別のプロセッサを用意する必要はない。従って、AVデコーダ部803は、第1の実施の形態における一つの信号処理装置、あるいは、第2の実施の形態における一つの信号処理装置によって構成することが出来る。

【0182】

再生装置801は、符号化AV信号を記録したメディアを再生して、再生信号を出力する。この再生装置801は、MPEG−4 AVC規格の符号化AV信号を記録したメディアを再生出来るものであれば、DVDビデオ再生機、HD(ハードディスク)ビデオ再生機、など、いずれの再生機でも良い。

【0183】

復調/エラー訂正部802は、再生装置801が再生した信号を復調し、エラー訂正を行って、AVデコーダ部803に出力する。

【0184】

AVデコーダ部803のビデオデコーダ803Aは、符号化ビデオ信号をデコードして、出力し、D/A変換器805において、アナログ信号に変換して、ビデオ出力806として出力する。

【0185】

AVデコーダ部803のオーディオデコーダ803Bは、符号化オーディオ信号をデコードして、出力し、D/A変換器807において、アナログ信号に変換して、オーディオ出力808として出力する。

【0186】

メモリ804は、デコード前、デコード中、及び/又は、デコード後のAV信号とその他のデータとを保存する。

【0187】

なお、本形態のAV再生システムにおいて、復調/エラー訂正部802の機能の一部、または全部を、再生装置801に持たせてもよい。

【0188】

本形態のAV再生システムは、CATV、インターネット、あるいは、衛星通信などから、送られてくる、MEPG−4 AVC仕様のAV信号を受信して、復調、デコードすることにも利用出来る。この場合には、受信した信号を復調/エラー訂正部802に入力して、上述したプロセスでデコードすることが出来る。さらに、ビデオ出力をディスプレイに表示すれば、ディジタルテレビとしても応用出来る。

【0189】

(第7の実施の形態)

図14は、本発明の第7の実施の形態におけるAV記録システムのブロック図である。

【0190】

本形態のAV記録システムは、AVエンコーダ部825、エラー訂正符号付与/変調部827、記録装置828、メモリ826、及び、A/D変換器822、824を備え、AVエンコーダ部825は、ビデオエンコーダ825Aとオーディオエンコーダ825Bを有する。

【0191】

ビデオエンコーダ825Aは、図3に示した、本発明の第3の実施の形態のビデオエンコーダであり、本発明の第1の実施の形態の信号処理装置、あるいは、第2の実施の形態の信号処理装置でを用いて実現出来る。

【0192】

オーディオエンコーダ825Bは、図11に示した、本発明の第5の実施の形態のオーディオエンコーダである。第5の実施の形態において述べたように、第5の実施の形態のオーディオエンコーダの処理は、画像データの処理に比べれば、必要な処理量が少ないために、ビデオエンコーダ825Aに適用される第1の実施の形態の信号処理装置、あるいは、第2の実施の形態の信号処理装置の命令並列プロセッサ100(図1、あるいは、図2)によって、並列に処理することが可能であり、別のプロセッサを用意する必要はない。従って、AVエンコーダ部825は、第1の実施の形態における一つの信号処理装置、あるいは、第2の実施の形態における一つの信号処理装置によって構成することが出来る。

【0193】

本形態のAV記録システムの動作の概略を説明する。

【0194】

ビデオ入力821は、A/D変換器822でA/D変換され、オーディオ入力823は、A/D変換器824でA/D変換され、それぞれ、AVエンコーダ部825に出力される。

【0195】

AVエンコーダ部825のビデオエンコーダ825Aは、入力されたビデオ信号を、MPEG−4 AVCの仕様に従って、エンコードして、符号化ビデオビットストリームとして出力する。同様に、オーディオエンコーダ825Bは、入力されたオーディオ信号を、MPEG−4 AVCの仕様に従って、エンコードして、符号化オーディオビットストリームとして出力する。

【0196】

エラー訂正/変調部827は、AVエンコーダ部825が出力した符号化ビデオビットストリームと符号化オーディオビットストリームとに、エラー訂正符号を付与した後、変調し記録装置に出力する。

【0197】

記録装置828は、変調されたAV信号を記録媒体に記録する。記録媒体は、DVDなどの光メディア、HD(ハードディスク)などの磁気記録媒体、半導体メモリなどである。

【0198】

メモリ826は、AVエンコーダ部825でのエンコード前、エンコード中、及び/又は、エンコード後のAV信号とその他のデータとを保存する。

【0199】

なお、本形態のAV記録システムにおいて、エラー訂正/変調部827の機能の一部、または全部を、記録装置828に含めることも出来る。

【0200】

本形態のAV記録システムは、入力にビデオカメラを接続して、その信号をMPEG−4 AVC仕様でエンコードして記録する、ビデオカメラシステムとして利用することも出来る。

【0201】

(第8の実施の形態)

図15は、本発明の第8の実施の形態におけるAV記録/再生システムのブロック図である。本形態のAV記録/再生システムは、制御部840、記録/再生装置841、変復調/エラー処理部842、AVエンコーダ/デコーダ部843、AVインターフェース845、及び、メモリ844を備え、AVエンコーダ/デコーダ部843は、ビデオエンコーダ/デコーダ843Aとオーディオエンコーダ/デコーダ843Bを有し、AVインターフェース845は、ビデオの入出力とオーディオの入出力を行う。

【0202】

AVエンコーダ/デコーダ部843は、機能的には、本発明の第3の実施の形態のビデオエンコーダと、第4の実施の形態のビデオデコーダと、第5の実施の形態のオーディオエンコーダとオーディオデコーダの、それぞれの機能と同等の機能を有しており、第1の実施の形態における一つの信号処理装置、又は、第2の実施の形態における一つの信号処理装置によって構築されている。それぞれの動作については、すでに述べたので、ここでは説明を省略する。

【0203】

記録再生装置841は、変調されたMPEG−4 AVC規格のAV信号を、記録/再生するもので、記録媒体は、DVDなどの光メディア、HD(ハードディスク)などの磁気記録媒体、半導体メモリなどである。使用する記録媒体によって、異なる記録/再生機構を有している。

【0204】

変復調/エラー処理部842は、記録時には、AVエンコーダ/デコーダ部843のエンコードしたビデオビットストリームとオーディオビットストリームとに、エラー訂正符号を付与して変調し、記録/再生装置841に送出する。変復調/エラー処理部842は、再生時には、記録/再生装置841が再生したAV信号を復調して、エラー訂正を施した後、ビデオビットストリームとオーディオビットストリームとを、AVエンコーダ/デコーダ部843に、送出する。

【0205】

AVインターフェース845は、再生時には、AVエンコーダ/デコーダ部843がデコードしたビデオ信号とオーディオ信号とを, それぞれD/A変換して、ビデオ出力846とオーディオ出力848を出力する。AVインターフェース845は、記録時には、ビデオ入力847とオーディオ入力849とを、それぞれA/D変換して、AVエンコーダ/デコーダ部843に送出する。

【0206】

メモリ844は、AVエンコーダ/デコーダ部843でのエンコード前、エンコード中、及び/又は、エンコード後のAV信号、並びに、デコード前、デコード中、及び/又は

、デコード後のAV信号と、その他のデータとを保存する。

【0207】

制御部840は、記録/再生装置841、変復調/エラー処理部842、AVエンコーダ/でコーダ部843、及び、AVインターフェース845を制御して、それぞれの記録時と、再生時の機能の切り替えと、データ転送の制御を行う。

【0208】

なお、本形態のAV記録/再生システムにおいて、変復調/エラー処理部842の機能の一部、または全部を、記録/再生装置841に含めることも出来る。

【0209】

以上、詳細に述べたように、本発明の信号処理装置及びそれを用いた電子機器は、今後、MPEG−4 AVCの符号化規格が適用される様々な電子機器への応用が期待される。このような電子機器への応用は、現在MPEG−2で行われているDVDシステムや、ビデオカメラのシステム、携帯電話におけるテレビ電話システムなど家庭内の据え置き端末から電池駆動のモバイル端末までの広い範囲に渡る。

【0210】

それらのシステムでは、MPEG−4 AVC規格を実現するLSIに対して要求される性能が、システムの応用の仕方によって異なる。据え置きのシステムでは、大きな画像サイズを扱うために処理性能が重要であり、一方、携帯端末ではバッテリ寿命を長くするために低消費電力が重要となる。本発明の信号処理装置及びそれを用いた電子機器は、そのいずれにも応用可能である。すなわち、命令並列プロセッサとデータ並列プロセッサと専用ハードウェアを組み合わせることにより、処理性能の向上と消費電力の低減を可能としている。

【0211】

本発明の信号処理装置は、複数のSIMD型プロセッサ(図1の例では、第1データ並列プロセッサ101と第2のデータ並列プロセッサ102)で構成されている。1個のSIMD型プロセッサには、8個の処理要素が含まれており、一つの命令で8種類のデータ流を並列に処理することが出来る。これらのSIMD型プロセッサの搭載数を信号処理装置の利用目的に応じて変更することにより、LSIのアーキテクチャ変更することなしに様々な要求性能に対応することが出来る。

【0212】

例えば、低消費電力が求められる携帯端末向けの信号処理装置では、SIMD型プロセッサを2つ搭載することにより、並列度を16にすることができ、低電圧動作及び動作周波数低減が可能である。

【0213】

また、16並列で使用するのではなく、8個の処理要素からなるSIMD型プロセッサを2組使い別の処理をさせることも可能である。

【0214】

第一のSIMD型プロセッサが動き補償の画素値計算をしている間に、第二のSIMD型プロセッサがDCT処理を行うといったように、全体の処理を分担して、並列処理することによって、処理要素の稼働率を維持したまま、複数の処理が出来る。この結果、演算性能の大幅な改善が可能となる。

【0215】

上記の実施の形態では、MPEG−4 AVC規格に則った応用について述べたが、本発明は、この応用のみに限定されるものではない。本発明の趣旨は、命令並列プロセッサとデータ並列プロセッサと専用ハードウェアを組み合わせることにより、処理性能の向上と消費電力の低減を実現することにあるのであって、本発明の趣旨を逸脱しない限り、種々の適用が可能である。

【産業上の利用可能性】

【0216】

本発明に係る信号処理装置は、例えば、オーディオ及び画像の圧縮伸張処理を、並列プ

ロセッサと専用ハードウェアを用いて高速に行う分野あるいはその関連分野等において利用できる。

【符号の説明】

【0217】

100 命令並列プロセッサ

101 第1データ並列プロセッサ

102 第2データ並列プロセッサ

103 動き検出ユニット

104 デブロックフィルタ処理ユニット

105 可変長符号化/復号処理ユニット

106 入出力インターフェース

110〜116 ローカルメモリ

120 ブリッジユニット

121 第1共有メモリ

122 第2共有メモリ

130 第1命令バス

131 第2命令バス

132 第1データバス

133 第2データバス

301 符号化制御部

302 差分検出部

303 モード切替部

304 4×4DCT変換部

305 量子化部

306 逆量子化部

307 逆4×4DCT変換部

308 可変長符号部

309 再構築部

310、338 デブロックフィルタ

311、339 フレームメモリ

312 動き補償部

313 動き検出部

316 動きベクトル

317 予測画像

318 イントラモード

319 インターモード

331 復号制御部

332 可変長復号部

333 逆量子化部

334 逆4×4DCT変換部

335 再構築部

336 動きベクトル復号部

337 動き補償部

351 圧縮部

352 符号化部

361 復号部

362 伸長部

401 コンテキストモデリング部

402 バイナリ化部

403 出現確立予測部

404 符号化部

405 適応2進算術符号化処理部

406 隣接ブロックA

407 隣接ブロックB

408 符号化対象ブロックC

602 BS条件判定処理部

603、606、804、826、844 メモリ

604 制御部

605 フィルタ処理部

607〜609 フィルタ

801 再生装置

802 復調/エラー訂正部

803 AVデコーダ部

803A ビデオデコーダ

803B オーディオデコーダ

805、807 D/A変換器

822、824 A/D変換器

825 AVエンコーダ部

825A ビデオエンコーダ

825B オーディオエンコーダ

827 エラー訂正符号付与/変調部

828 記録装置

840 制御部

841 記録/再生装置

842 変復調/エラー処理部

843 AVエンコーダ/でコーダ部

843A ビデオエンコーダ/デコーダ

843B オーディオエンコーダ/デコーダ

845 AVインターフェース

901 システム制御部

902 SIMD型並列データ処理装置

903 MIMD型並列データ処理装置

904 共有メモリバス

905 共有メモリ

910、920 全体制御部

911〜914、925〜928 演算器

915〜918、929〜932 ローカルメモリ

921〜924 制御部

1001 画像処理装置

1002 命令メモリ

1003 プロセッサ

1004 SIMD型演算手段

1005 VLC(可変長符号化)処理手段

1006 外部データインターフェース

1007 内部データバス

1008 ビデオデータバス

1009 ビデオ入力装置

1010 ビデオ出力装置

1011 外部メモリ

【特許請求の範囲】

【請求項1】

第1データバスと、

前記第1データバスに接続され、前記第1データバスを介して共有される第1共有メモリと、

前記第1データバスとは独立分離した状態に設けられる第2データバスと、

前記第2データバスに接続され、前記第2データバスを介して共有される第2共有メモリと、

前記第1データバスと前記第2データバスとを仲介し、前記第1データバスと前記第2データバスとを間接的に接続するブリッジユニットと、

音声オーディオの圧縮処理を行い、前記第2データバスに接続される命令並列プロセッサと、

前記第1データバスに接続されるが前記第2データバスには直接接続されず、かつ前記命令並列プロセッサとともに同時並行して画像圧縮処理を行うデータ並列プロセッサ及び専用ハードウェアとを備え、

前記命令並列プロセッサ、前記データ並列プロセッサ及び前記専用ハードウェアのそれぞれは、同時並行して圧縮処理を実行することを特徴とする画像音声信号処理装置。

【請求項2】

第1データバスと、

前記第1データバスに接続され、前記第1データバスを介して共有される第1共有メモリと、

前記第1データバスとは独立分離した状態に設けられる第2データバスと、

前記第2データバスに接続され、前記第2データバスを介して共有される第2共有メモリと、

前記第1データバスと前記第2データバスとを仲介し、前記第1データバスと前記第2データバスとを間接的に接続するブリッジユニットと、

音声オーディオの伸長処理を行い、前記第2データバスに接続される命令並列プロセッサと、

前記第1データバスに接続されるが前記第2データバスには直接接続されず、かつ前記命令並列プロセッサとともに同時並行して画像伸長処理を行うデータ並列プロセッサ及び専用ハードウェアとを備え、

前記命令並列プロセッサ、前記データ並列プロセッサ及び前記専用ハードウェアのそれぞれは、同時並行して伸長処理を実行することを特徴とする画像音声信号処理装置。

【請求項3】

前記データ並列プロセッサは第1のローカルメモリを有し、

前記専用ハードウェアは第2のローカルメモリを有し、

前記命令並列プロセッサは第3のローカルメモリを有し、

前記第1のローカルメモリと前記第2のローカルメモリは前記第1データバスに接続され、

前記第3のローカルメモリは前記第2データバスに接続され、

前記ブリッジユニットは、前記第1データバスと前記第2データバスとに互いに独立した状態で接続される第1、第2ローカルメモリと第3のローカルメモリ間のデータ転送を仲介する請求項1または2記載の画像音声信号処理装置。

【請求項4】

ローカルメモリを有する入出力インターフェイスをさらに備え、

前記入出力インターフェイスの前記ローカルメモリは前記第1データバスに接続される請求項1から3のいずれかに記載の画像音声信号処理装置。

【請求項5】

前記命令並列プロセッサは、前記入出力インターフェイスによる入出力処理を制御する請求項4記載の画像音声信号処理装置。

【請求項6】

請求項1から5のいずれかの画像音声信号処理装置を有する電子機器。

【請求項1】

第1データバスと、

前記第1データバスに接続され、前記第1データバスを介して共有される第1共有メモリと、

前記第1データバスとは独立分離した状態に設けられる第2データバスと、

前記第2データバスに接続され、前記第2データバスを介して共有される第2共有メモリと、

前記第1データバスと前記第2データバスとを仲介し、前記第1データバスと前記第2データバスとを間接的に接続するブリッジユニットと、

音声オーディオの圧縮処理を行い、前記第2データバスに接続される命令並列プロセッサと、

前記第1データバスに接続されるが前記第2データバスには直接接続されず、かつ前記命令並列プロセッサとともに同時並行して画像圧縮処理を行うデータ並列プロセッサ及び専用ハードウェアとを備え、

前記命令並列プロセッサ、前記データ並列プロセッサ及び前記専用ハードウェアのそれぞれは、同時並行して圧縮処理を実行することを特徴とする画像音声信号処理装置。

【請求項2】

第1データバスと、

前記第1データバスに接続され、前記第1データバスを介して共有される第1共有メモリと、

前記第1データバスとは独立分離した状態に設けられる第2データバスと、

前記第2データバスに接続され、前記第2データバスを介して共有される第2共有メモリと、

前記第1データバスと前記第2データバスとを仲介し、前記第1データバスと前記第2データバスとを間接的に接続するブリッジユニットと、

音声オーディオの伸長処理を行い、前記第2データバスに接続される命令並列プロセッサと、

前記第1データバスに接続されるが前記第2データバスには直接接続されず、かつ前記命令並列プロセッサとともに同時並行して画像伸長処理を行うデータ並列プロセッサ及び専用ハードウェアとを備え、

前記命令並列プロセッサ、前記データ並列プロセッサ及び前記専用ハードウェアのそれぞれは、同時並行して伸長処理を実行することを特徴とする画像音声信号処理装置。

【請求項3】

前記データ並列プロセッサは第1のローカルメモリを有し、

前記専用ハードウェアは第2のローカルメモリを有し、

前記命令並列プロセッサは第3のローカルメモリを有し、

前記第1のローカルメモリと前記第2のローカルメモリは前記第1データバスに接続され、

前記第3のローカルメモリは前記第2データバスに接続され、

前記ブリッジユニットは、前記第1データバスと前記第2データバスとに互いに独立した状態で接続される第1、第2ローカルメモリと第3のローカルメモリ間のデータ転送を仲介する請求項1または2記載の画像音声信号処理装置。

【請求項4】

ローカルメモリを有する入出力インターフェイスをさらに備え、

前記入出力インターフェイスの前記ローカルメモリは前記第1データバスに接続される請求項1から3のいずれかに記載の画像音声信号処理装置。

【請求項5】

前記命令並列プロセッサは、前記入出力インターフェイスによる入出力処理を制御する請求項4記載の画像音声信号処理装置。

【請求項6】

請求項1から5のいずれかの画像音声信号処理装置を有する電子機器。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【公開番号】特開2013−84311(P2013−84311A)

【公開日】平成25年5月9日(2013.5.9)

【国際特許分類】

【出願番号】特願2013−18161(P2013−18161)

【出願日】平成25年2月1日(2013.2.1)

【分割の表示】特願2009−271743(P2009−271743)の分割

【原出願日】平成15年8月21日(2003.8.21)

【出願人】(000005821)パナソニック株式会社 (73,050)

【Fターム(参考)】

【公開日】平成25年5月9日(2013.5.9)

【国際特許分類】

【出願日】平成25年2月1日(2013.2.1)

【分割の表示】特願2009−271743(P2009−271743)の分割

【原出願日】平成15年8月21日(2003.8.21)

【出願人】(000005821)パナソニック株式会社 (73,050)

【Fターム(参考)】

[ Back to top ]