画素回路、画素回路の駆動方法、画素回路の駆動回路及び電気光学装置

【課題】超低消費電力を実現しながら、画素回路内の素子数を削減し、さらに画素回路内のトランジスタのスレッショルド電圧の変化にも対応することが可能な画素回路を提供する。

【解決手段】電気光学素子と、第1制御信号線上の第1制御信号により制御される第1スイッチ素子と、第2制御信号線上の第2制御信号により制御される第2スイッチ素子と、第2スイッチ素子の制御端子に一方の電極端子が接続され、第2スイッチ素子の一方の電極端子に他方の電極端子が接続される第4スイッチ素子と、電気光学素子に保持された画像データに対応する電圧レベルのサンプリング結果を保持する第1容量素子及び第2容量素子と、を備え、電気光学素子に保持された画像データに対応する電圧レベルが、第1スイッチ素子を介して第1容量素子にサンプリングされ、第2スイッチ素子を介して第2容量素子にサンプリングされることを特徴とする、画素回路が提供される。

【解決手段】電気光学素子と、第1制御信号線上の第1制御信号により制御される第1スイッチ素子と、第2制御信号線上の第2制御信号により制御される第2スイッチ素子と、第2スイッチ素子の制御端子に一方の電極端子が接続され、第2スイッチ素子の一方の電極端子に他方の電極端子が接続される第4スイッチ素子と、電気光学素子に保持された画像データに対応する電圧レベルのサンプリング結果を保持する第1容量素子及び第2容量素子と、を備え、電気光学素子に保持された画像データに対応する電圧レベルが、第1スイッチ素子を介して第1容量素子にサンプリングされ、第2スイッチ素子を介して第2容量素子にサンプリングされることを特徴とする、画素回路が提供される。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、画素回路、画素回路の駆動方法、画素回路の駆動回路及び電気光学装置に関する。

【背景技術】

【0002】

消費電力を通常の電気光学装置より大幅に抑えた、超低消費電力の、LCD等のアクティブマトリックス型電気光学装置を実現する技術として、各画素にSRAM(Static Random Access Memory)ベースのメモリ回路を内蔵したMIP(Memory In Pixel)という技術が知られている。しかし、従来のSRAMベースのMIPでは、画素に少なくとも6素子以上のトランジスタが必要となり、例えばスマートフォン等で求められる表示画像の更なる高精細化要求に対応することが出来ない。また、CMOS構成ではプロセスマスク枚数削減も困難であり、低コスト要求に答えることも難しい。

【0003】

そのような高精細化要求や低コスト要求に応えるための技術として、例えば特許文献1がある。特許文献1には、画素内部のトランジスタが3個という簡便な回路構成で、超低消費電力アクティブマトリックスアレイ装置を実現可能にするという技術が開示されている。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特表2006−523323号公報

【特許文献2】特開2004−226960号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

しかし、特許文献1に開示された画素回路は、第3のスイッチのスレッショルド電圧が変動すると、正常な電圧レベルに画素をリフレッシュすることができなくなるという問題を有する。また、オフ画素に対するリフレッシュ動作が行われないためにオフ画素に書き込まれた画像データを保持し続けることができないという問題も有する。

【0006】

さらに、LCDのように極性反転駆動を行う場合、電気光学素子への印加電圧の正極方向への反転(以下、正極性リフレッシュと称する)、印加電圧の負極方向への反転(以下、負極性リフレッシュと称する)毎に各制御信号のアクティブタイミングが異なっている。そのため、周辺回路、特に走査線駆動回路の構成が複雑となり、走査線駆動回路を制御するための制御回路の回路規模も増大することから、小型化が難しくなるとともに無駄な電力が消費されてしまうという問題と、正極性リフレッシュから負極性リフレッシュの期間と、負極性リフレッシュから正極性リフレッシュの期間、すなわち電気光学素子の端子間電圧が正極性である期間と、負極性である期間が異なるため、長期的には液晶層へ直流電圧が印加されることとなり、液晶寿命に悪影響を与えるという問題を有する。

【0007】

さらに、電気光学素子の一端をコモン電極に接続し、保持容量の一端を固定電圧としていることから、液晶層への直流印加が発生し、液晶寿命に悪影響を及ぼすことになるという問題も有する。

【0008】

一方、特許文献2には、画素回路内において、電気光学素子(OLED)への電流を制御するトランジスタのスレッショルド電圧の変動を補償して、画素の輝度ばらつきを抑えることを可能にするという技術が開示されている。しかし、特許文献2に開示された画素回路は、画素外部から入力されたデータ信号に対してトランジスタのスレッショルド電圧を重畳させることはできるが、画素内部に保持されたデータ信号に対してトランジスタのスレッショルド電圧を重畳させることはできないという問題を有する。

【0009】

また、トランジスタのスレッショルド電圧をキャパシタCVTHへ保存する際には、電気光学素子(OLED)との接続を遮断するためのトランジスタ(M2)や、基準電位Vddとの接続を制御するためのトランジスタ(M4)が必要となり、画素内部の素子数増加により高精細化の妨げとなるという問題も有する。

【0010】

そこで、本発明は、上記問題に鑑みてなされたものであり、本発明の目的とするところは、超低消費電力を実現しながら、画素回路内の素子数を削減し、さらに画素回路内のトランジスタのスレッショルド電圧の変化にも対応することが可能な、新規かつ改良された画素回路、画素回路の駆動方法、画素回路の駆動回路及び電気光学装置を提供することにある。

【課題を解決するための手段】

【0011】

上記課題を解決するために、本発明のある観点によれば、電気光学素子と、第1制御信号線上の第1制御信号により制御される第1スイッチ素子と、第2制御信号線上の第2制御信号により制御される第2スイッチ素子と、前記第2スイッチ素子の制御端子に一方の電極端子が接続され、前記第2スイッチ素子の一方の電極端子に他方の電極端子が接続される第4スイッチ素子と、前記電気光学素子に保持された画像データに対応する電圧レベルのサンプリング結果を保持する第1容量素子及び第2容量素子と、を備え、前記電気光学素子の一端は対向電極に、他端は前記第2スイッチ素子の他方の電極端子に、それぞれ接続され、前記電気光学素子に保持された画像データに対応する電圧レベルが、前記第1スイッチ素子を介して前記第1容量素子にサンプリングされ、前記第4スイッチ素子をオンすることにより、前記電気光学素子に保持された画像データに対応する電圧レベルが、前記第2スイッチ素子を介して前記第2容量素子にサンプリングされることを特徴とする、画素回路が提供される。

【0012】

前記第1容量素子の一方の端子が前記第2制御信号線に接続され、他方の端子が第2容量素子の一方の端子に接続され、前記第2容量素子の他方の端子が前記第2スイッチ素子の制御端子に接続されていてもよい。

【0013】

前記第4スイッチ素子が、前記第1制御信号により制御されるようにしてもよい。

【0014】

第3制御信号線上の第3制御信号により制御される第3スイッチ素子を、さらに備えていてもよい。

【0015】

前記第3スイッチ素子が、一方の電極端子が前記第2スイッチ素子の一方の電極端子に接続され、他方の電極端子がデータ線に接続されていてもよい。

【0016】

また、上記課題を解決するために、本発明の別の観点によれば、電気光学素子を備える画素回路の駆動方法であって、前記画素回路内の、第1制御信号線上の第1制御信号により制御される第1スイッチ素子を介して、前記電気光学素子に保持された画像データに対応する電圧レベルをサンプリングする第1のサンプリング駆動ステップと、第2スイッチ素子の制御端子に一方の電極端子が接続され、前記第2スイッチ素子の一方の電極端子に他方の電極端子が接続される第4スイッチ素子をオンすることにより、前記第2スイッチ素子を介して、前記電気光学素子に保持された画像データに対応する電圧レベルをサンプリングする第2のサンプリング駆動ステップと、前記第1のサンプリング駆動ステップにおける第1のサンプリング結果と、前記第2のサンプリング駆動ステップにおける第2のサンプリング結果とを加算したサンプリング加算結果を、第2制御信号線上の第2制御信号に重畳する電圧重畳ステップと、を備え、前記サンプリング加算結果を前記第2制御信号に重畳した電圧レベルにより、前記第2スイッチ素子を制御することを特徴とする、画素回路の駆動方法が提供される。

【0017】

前記第2制御信号が、該第2制御信号がアクティブになる前に、所定の電圧レベルでプリセットされるようにしてもよい。

【0018】

前記プリセットされる所定の電圧レベルが、前記第2スイッチ素子の特性に応じた電圧レベルであってもよい。

【0019】

前記プリセットされる所定の電圧レベルが、前記第2制御信号のインアクティブ電圧と前記電気光学素子に保持された画像データに対応する電圧レベルとの中間電圧であってもよい。

【0020】

前記サンプリング加算結果を前記第2制御信号に重畳した電圧レベルにより制御される前記第2スイッチ素子を介して供給される電圧を、前記電気光学素子に印加することにより、前記電気光学素子に保持された画像データをリフレッシュするようにしてもよい。

【0021】

前記第4スイッチ素子が、前記第1制御信号により制御されるようにしてもよい。

【0022】

また、上記課題を解決するために、本発明の別の観点によれば、電気光学素子を備える画素回路の駆動回路であって、前記画素回路内の、第1制御信号線上の第1制御信号により制御される第1スイッチ素子を介して、前記電気光学素子に保持された画像データに対応する電圧レベルをサンプリングする第1のサンプリング駆動手段と、第2スイッチ素子の制御端子に一方の電極端子が接続され、前記第2スイッチ素子の一方の電極端子に他方の電極端子が接続される第4スイッチ素子をオンすることにより、前記第2スイッチ素子を介して前記電気光学素子に保持された画像データに対応する電圧レベルをサンプリングする第2のサンプリング駆動手段と、前記第1のサンプリング駆動手段における第1のサンプリング結果と、前記第2のサンプリング駆動手段における第2のサンプリング結果とを加算したサンプリング加算結果を、第2制御信号線上の第2制御信号の電圧レベルに重畳する電圧重畳手段と、を備え、前記サンプリング加算結果を前記第2制御信号に重畳した電圧レベルにより、前記第2スイッチ素子を制御することを特徴とする、画素回路の駆動回路が提供される。

【0023】

前記第2制御信号が、該前記第2制御信号がアクティブになる前に、所定の電圧レベルでプリセットされるようにしてもよい。

【0024】

前記第4スイッチ素子が、前記第1制御信号により制御されるようにしてもよい。

【0025】

上記画素回路の駆動回路は、前記画素回路内に保持された画像データのリフレッシュ後に、前記画素回路の周辺回路の動作を停止させる手段をさらに備えていてもよい。

【0026】

また、上記課題を解決するために、本発明の別の観点によれば、上記画素回路がマトリクス状に配置されたアクティブマトリクスアレイ回路と、上記画素回路を駆動する上記画素回路の駆動回路と、を備えることを特徴とする、電気光学装置が提供される。

【発明の効果】

【0027】

以上説明したように本発明によれば、超低消費電力を実現しながら、画素回路内の素子数を削減し、さらに画素回路内のトランジスタのスレッショルド電圧の変化にも対応することが可能な、新規かつ改良された画素回路、画素回路の駆動方法、画素回路の駆動回路及び電気光学装置を提供することができる。

【図面の簡単な説明】

【0028】

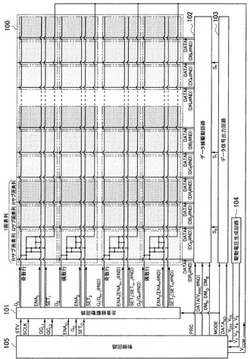

【図1】本発明の一実施形態におけるアクティブマトリクス型電気光学装置のブロック図である。

【図2】本発明の一実施形態における画素回路構成図である。

【図3】本発明の一実施形態における画素回路の駆動方法を示すタイミングチャートである。

【図4】本発明の一実施形態における画素回路の動作を説明する図である。

【図5】本発明の一実施形態におけるACタイミングチャートである。

【図6】本発明の一実施形態における走査線駆動回路構成図である。

【図7】本発明の一実施形態におけるデータ線駆動回路構成図である。

【図8】本発明の一実施形態における走査線駆動回路およびデータ線駆動回路の駆動方法を示すタイミングチャートである。

【図9】従来の発明によるアクティブマトリクス型電気光学装置における画素回路構成図である。

【図10】従来の発明によるアクティブマトリクス型電気光学装置の制御において不具合の可能性を示すACタイミングチャートである。

【発明を実施するための形態】

【0029】

以下に添付図面を参照しながら、本発明の好適な実施の形態について詳細に説明する。なお、本明細書及び図面において、実質的に同一の機能構成を有する構成要素については、同一の符号を付することにより重複説明を省略する。

【0030】

<1.本発明の一実施形態>

[1−1.画素回路を用いたアクティブマトリクス型電気光学装置の構成]

まず、本発明の一実施形態にかかる画素回路を用いたアクティブマトリクス型電気光学装置の構成について説明する。図1は、本発明の一実施形態による画素回路を用いたアクティブマトリクス型電気光学装置の構成を示す説明図である。以下、図1を用いて本発明の一実施形態による画素回路を用いたアクティブマトリクス型電気光学装置の構成について説明する。

【0031】

図1に示したように、アクティブマトリクス型電気光学装置は、画素回路がアレイ状に配置されているアクティブマトリクスアレイ回路100と、走査線駆動回路101と、データ線駆動回路102と、データ信号出力回路103と、駆動電圧生成回路104と、制御回路105と、を具備する。

【0032】

制御回路105は、走査線駆動回路101と、データ線駆動回路102と、データ信号出力回路103とを制御し、さらに、対向電極電圧信号VCOMを生成し、図示しない対向電極およびアクティブマトリクスアレイ回路100に供給するとともに、その電圧レベルを制御することで、アクティブマトリクスアレイ回路100を駆動する。

【0033】

駆動電圧生成回路104は、アクティブマトリクスアレイ回路100において、アレイ状に配置されている画素回路を制御する制御信号の電圧レベルV1,V3,V4,V5と、データ信号の高電圧レベルVDHおよび低電圧レベルVDLと、を生成し、制御回路105に供給する。

【0034】

走査線駆動回路101は、制御回路105により制御され、アクティブマトリクスアレイ回路100を駆動する制御信号を生成する。

【0035】

データ線駆動回路102とデータ信号出力回路103は、制御回路105により制御され、アクティブマトリクスアレイ回路100へ出力するデータ信号を生成する。

【0036】

ここで、アクティブマトリクス型電気光学装置における1画素は、RGBのサブ画素からなり、それぞれのサブ画素は同一の画素回路を備えている。なお、図1では、アクティブマトリクスアレイ回路100に含まれる各画素回路については、素子を省略して図示し、具体的な画素回路の構成については図2で説明することにする。

【0037】

以上、図1を用いて本発明の一実施形態による画素回路を用いたアクティブマトリクス型電気光学装置の構成について説明した。次に、アクティブマトリクスアレイ回路100の1サブ画素である画素回路の構成について説明する。

【0038】

[1−2.画素回路の構成]

図2は、図1に示したアクティブマトリクスアレイ回路100の1サブ画素である画素回路の構成を示す説明図である。以下、図2を用いて、アクティブマトリクスアレイ回路100の1サブ画素である画素回路の構成について説明する。

【0039】

図2において、画素回路201はアクティブマトリクスアレイ回路100の奇数行における画素回路の1つであり、画素回路202は偶数行における画素回路の1つである。本実施形態においてそれぞれの画素回路は同一であってよい。

【0040】

画素回路201,202は、スイッチ素子SW1,SW2,SW3,SW4と、静電容量がCSMPである画像データサンプリングキャパシタC2と、静電容量がCVTHであるスレッショルド電圧サンプリングキャパシタC3と、静電容量がCSTである保持キャパシタC1と、静電容量CLCを備えた電気光学素子LCと、を具備する。電気光学素子LCと保持キャパシタC1とは、並列に接続されており、一端には、スイッチ素子SW3,SW2を介してデータ信号DATAが供給され、保持キャパシタC1の他端には、共通信号供給線から対向電極電圧信号VCOMが供給され、電気光学素子LCの他端には、対向電極から対向電極電圧信号VCOMが供給される。

【0041】

なお、特許文献1(特表2006−523323号公報)に記載の先行技術においては、電気光学素子と保持キャパシタである第1容量性サブ素子とは、一端は本実施形態と同様に共通に接続され、該一端にデータ信号が供給され、電気光学素子の他端は、対向電極(コモン電極)に接続されている。しかし、第1容量性サブ素子の他端は、本実施形態とは異なり、例えば次列のアドレス指定導体に接続されることが述べられている。

【0042】

画素回路201,202には、データ信号DATAと、電気光学素子LCの対向電極電圧信号VCOMと、データ信号DATAの画素回路内への供給を制御する画像データ取り込み制御信号G1、G2と、ノードN1の電圧レベルに対応する電圧レベルを画像データサンプリングキャパシタC2と、スレッショルド電圧サンプリングキャパシタC3にサンプリングするタイミングを制御するサンプリング制御信号ENA1、ENA2と、画素回路201,202内の電気光学素子LCおよび保持キャパシタC1をリフレッシュするタイミングを制御する画像データリフレッシュ制御信号SET1、SET2と、が入力され、画素回路201,202を制御する。ここで、各制御信号の符号最後の1,2は奇数行に対する制御信号(1)か、偶数行に対する制御信号(2)か、を示している。

【0043】

詳細な制御及び動作は後述するが、スイッチ素子SW1,SW4は、サンプリング制御信号ENAにより制御され、ノードN1の電圧レベルに対応する電圧レベルを画像データサンプリングキャパシタC2にサンプリングするとともに、結果としてスイッチ素子SW2のスレッショルド電圧をスレッショルド電圧サンプリングキャパシタC3にサンプリングする。スイッチ素子SW2は、画像データリフレッシュ制御信号SETと画像データサンプリングキャパシタC2およびスレッショルド電圧サンプリングキャパシタC3の電圧レベルにより制御される。スイッチ素子SW3は、画像データ取り込み制御信号Gにより制御され、データ信号DATAを画素回路201,202内に供給する。

【0044】

なお、画像データサンプリングキャパシタC2の静電容量CSMPおよびスレッショルド電圧サンプリングキャパシタC3の静電容量CVTHは、保持キャパシタC1の静電容量CSTと電気光学素子LCの静電容量CLCの合計の容量に対して、1/10以下にすることが望ましい。これは、サンプリング時に保持キャパシタC1と電気光学素子LCの静電容量CLCとに保持された電荷の変動が表示に影響を与えないようにするためには、可能な限り小さい容量であることが望ましいが、一方でスイッチ素子を駆動するための十分な電圧レベルを確保するためには一定以上の容量が必要となるからである。

【0045】

以上、図2を用いて、アクティブマトリクスアレイ回路100の1サブ画素である画素回路の構成について説明した。次に、本発明の一実施形態に係る画素回路201,202の制御動作原理について説明する。

【0046】

[1−3.画素回路の制御動作原理]

図3及び図4は、本発明の一実施形態に係る画素回路201,202の制御動作原理について説明する説明図である。以下、図3及び図4を用いて本発明の一実施形態に係る画素回路201,202の制御動作原理について説明する。

【0047】

図4の(a)から(c)は、画素回路201,202の制御動作原理を示すものである。ただし、図4はあくまでも原理的なものであり、実際の画素回路201,202の制御については図5以降のACタイミングにおいてさらに詳しく説明する。

【0048】

まず、図示しない通常表示においては、画像データ取り込み制御信号Gおよび画像データリフレッシュ制御信号SETをアクティブにすることにより、スイッチ素子SW3,SW2をオンにする。したがって、スイッチ素子SW3,SW2を介して、データ信号DATAの画像データを保持キャパシタC1と電気光学素子LCへ書き込むことが可能となる。保持キャパシタC1と電気光学素子LCの静電容量CLCが画像データに対応する電圧レベルまで充電された後、画像データ取り込み制御信号Gおよび画像データリフレッシュ制御信号SETをインアクティブにして、スイッチ素子SW3,SW2をオフにする。なお、スイッチ素子SW2は画像データサンプリングキャパシタC2およびスレッショルド電圧サンプリングキャパシタC3に充電された電荷が放電されるまではオフとはならない場合があるが、スイッチ素子SW3がオフとなっているため、電気光学素子LCおよび静電容量CLCに充電された画像データを保持する。さらに、スイッチ素子SW2を確実に制御するために、画像データ取り込み制御信号Gおよび画像データ書き換え制御信号SETをアクティブにする前に、予めサンプリング制御信号ENAをアクティブにしておくことが望ましい。

【0049】

通常表示が終了後、図4の(a)に示されているサンプリング動作を行う。サンプリング動作では、サンプリング期間TSMPにおいてサンプリング制御信号ENAをアクティブにすることにより、スイッチ素子SW1,SW4をオンにする。これにより、保持キャパシタC1および電気光学素子LCの静電容量CLCに保持している画像データに対応する電圧レベルが、スイッチ素子SW1を介して、画像データサンプリングキャパシタC2にサンプリングされるとともに、ダイオード接続状態のスイッチ素子SW2を介して、スレッショルド電圧サンプリングキャパシタC3にサンプリングされる。このとき、画像データサンプリングキャパシタC2にサンプリングされた電圧レベルは、保持している画像データに対応する電圧レベルであり、一方、スレッショルド電圧サンプリングキャパシタC3には、スイッチ素子SW2のスレッショルド電圧がサンプリングされる。サンプリング後、サンプリング制御信号ENAをインアクティブにすることで、スイッチ素子SW1,SW4をオフにする。

【0050】

サンプリング動作の後、図4の(b)に示されているリフレッシュ動作を行なう。リフレッシュ動作では、リフレッシュ期間TREFにおいて画像データ取り込み制御信号Gをアクティブにし、データ信号DATAをノードN3へ取り込む。さらに画像データリフレッシュ制御信号SETを所定のアクティブレベルにし、画像データリフレッシュ制御信号SETのアクティブレベルと画像データサンプリングキャパシタC2に保持された電圧レベルおよびスレッショルド電圧サンプリングキャパシタC3に保持された電圧レベルを合算した電圧レベルと、ノードN3の電圧レベルに基づき、スイッチ素子SW2のオン/オフ制御を行なう。スイッチ素子SW2のオン/オフ状態に応じて、データ信号DATAの電圧レベルを保持キャパシタC1と電気光学素子LCへ印加する。

【0051】

リフレッシュ動作の後、図4の(c)に示されているデータ保持動作を行う。データ保持動作では、画像データ取り込み制御信号Gをインアクティブにすることで、スイッチ素子SW3をオフにし、保持期間THOLDの間、保持キャパシタC1と電気光学素子LCに印加された画像データを保持する。

【0052】

そして、サンプリング動作とリフレッシュ動作を定期的に適宜繰り返す期間(以下、低消費電力表示期間と称する)においては、各画素の自己保存データに基づいた画像データのリフレッシュが行われるため、全画素同時のリフレッシュが可能である。このため、サンプリング動作とリフレッシュ動作以外の低消費電力表示期間においては、周辺回路動作を停止することができ、かつデータ書き換えに伴うデータ線の充放電電流も生じないため、消費電力が削減可能となる。

【0053】

以上の動作原理に基づき、特許文献1(特表2006−523323号公報)の先行技術における回路および各種制御信号による制御を検討すると、図9に示す、スイッチ素子SW2のスレッショルド電圧のばらつきや、経時変化によって誤動作してしまうという問題の他にも、後述する(5)、(6)式を満たさないため、図10に示すように、オフ画素のリフレッシュ動作中に、本来オフとならなければならないスイッチ素子SW2がオフとならない場合が生じ、その結果、オフ画素がリフレッシュ動作後にオン画素となってしまう誤動作が生じる可能性があることが判明した。

【0054】

また、特許文献1においては、図9に示すように、保持キャパシタC1の一端が各走査線上で共通化または隣接する走査線に接続されている。しかし、そのような構成では、電気光学素子の対向電極に供給されるVCOM電圧と保持キャパシタC1の一端から供給される信号電圧との差分電圧と、保持キャパシタC1の静電容量CSTと電気光学素子LCの静電容量CLCとの容量比に応じて生じる電圧とが、電気光学素子の端子間電圧VLCに直流電圧として重畳されてしまい、電気光学素子の表示に不具合を生じることになる。特に電気光学素子が液晶である場合には、直流電圧の重畳が、液晶寿命に悪影響を及ぼすことは言うまでもない。

【0055】

そこで本発明の実施形態においては、画素回路201,202の制御信号の1つである画像データリフレッシュ制御信号SET1,SET2に、該制御信号のアクティブ前に所定の電圧をプリセットすることで、オフ画素における誤動作を回避するとともに制御に必要な電圧レベル数を削減する。

【0056】

また、保持キャパシタC1の一端を全画素で共通化して対向電極電圧信号VCOMを供給することにより、電気光学素子LCの一端に供給される対向電極電圧信号VCOMとの差分電圧と、保持キャパシタC1の静電容量CSTと電気光学素子LCの静電容量CLCとの容量比に応じて生じる電圧とが、電気光学素子の端子間電圧VLCに直流電圧として重畳されてしまうことを解消する。これにより、電気光学素子の端子間電圧VLCに不要な直流電圧が重畳されることはなくなり、フリッカを防止することができ、さらに、電気光学素子の長寿命化が実現できる。

【0057】

以下に、本発明の一実施形態によるACタイミングについて、図2及び図5を参照しながら詳細に説明する。

【0058】

[1−4.画素回路のACタイミング]

図5は、図2に示されている本発明の一実施形態による画素回路201,202を制御する制御信号のACタイミングチャートを示す説明図である。以下、図2及び図5を用いて、本発明の一実施形態における動作に必要な制御信号のタイミングおよび必要な電圧を明確にするために詳述する。

【0059】

図5では、結果としてライン反転駆動となるように、制御信号ENA1,G1,SET1による奇数行毎の駆動と、制御信号ENA2,G2,SET2による偶数行毎の駆動とに、グループに分けて駆動を行う例を示している。フレーム反転駆動を行う場合には、図5に示す奇数行への制御信号を偶数行にも入力することにより実現できることは言うまでもない。

【0060】

今、スイッチ素子SW1,SW2,SW3,SW4は、それぞれスレッショルド電圧Vthが1[V]のトランジスタであると仮定する。そして、電気光学素子LCにオン電圧が4[V]の垂直配向液晶を用い、対向電極電圧信号VCOMおよびデータ信号DATAの高電圧レベルVDHおよび低電圧レベルVDLをそれぞれVDH=4[V]、VDL=0[V]と仮定する。さらに各制御信号が取り得る電圧レベルは、V1=12[V]、V3=4[V]、V4=0[V]、V5=−4[V]に設定されるが、これらの電圧設定に限定されるものではない。

【0061】

例えば、電圧レベルV5はデータ信号DATAの低電圧レベルVDL(=0[V])−対向電極電圧信号VCOMの振幅電圧(=4[V])+スレッショルド電圧Vth(=1[V])以下となればよく、V1はデータ信号DATAの高電圧レベルVDH(=4[V])+対向電極電圧信号VCOMの振幅電圧(=4[V])+スレッショルド電圧Vth(=1[V])以上となればよい。

【0062】

さらに、データ信号DATAの電圧レベルVDL,VDHをオフセットさせ、それに応じて電圧レベルV1,V3,V4,V5の設定を適宜変更してもよい。また、スイッチ素子SW3やスイッチ素子SW2がオフする際のキックバック電圧等により、液晶層に直流電圧が重畳されると、フリッカ等が生じることがある。この場合には、対向電極電圧信号VCOMおよびデータ信号DATAの電圧レベルを各々独立に制御してオフセット電圧を加えてもよい。

【0063】

なお、図5に示す電圧レベルV2は、上記の各電圧レベルVDH,VDL,V1,V3,V4,V5の電圧設定に応じて必然的に定まるものであり、この場合V2=8[V]となる。

【0064】

図2に示す本発明の一実施形態である画素回路201を制御するための各制御信号の設定に必要な条件を以下に列挙する。図5に示すACタイミングは、この設定条件に基づいて、各制御信号のタイミングおよび電圧を設定したものである。

【0065】

1)VCOM信号(対向電極電圧信号)

サンプリング&リフレッシュ期間中、対向電極電圧信号VCOMは、Lレベルの期間とHレベルの期間を有すること。

【0066】

2)DATA信号(データ信号)

(a)サンプリング&リフレッシュ期間中、データ信号DATAは、対向電極電圧信号VCOMがLレベルの期間に少なくとも1回HレベルからLレベルへ遷移すること。

【0067】

(b)サンプリング&リフレッシュ期間中、データ信号DATAは、対向電極電圧信号VCOMがHレベルの期間に少なくとも1回HレベルからLレベルへ遷移すること。

【0068】

3)ENA信号(サンプリング制御信号)

(a)サンプリング&リフレッシュ期間中、サンプリング制御信号ENAは、画像データ取り込み制御信号Gがアクティブ前、かつ、対向電極電圧信号VCOMがHレベルの期間中にアクティブとなることが望ましい。

【0069】

(b)サンプリング制御信号ENAのアクティブ電圧は、電圧V1とすることが望ましい。これは、ノードN1の電圧レベルが最大で、データ信号DATAの高電圧レベルVDH(=4[V])+対向電極電圧信号VCOMの振幅電圧(=4[V])の電圧レベルV2(=8[V])となるため、アクティブ電圧としてはそれよりもスレッショルド電圧Vth分以上高い電圧レベルが必要だからである。また、アクティブ電圧を他の制御信号と一律で電圧V1とすることにより、周辺回路を簡素化することが可能となるためである。

【0070】

(c)サンプリング制御信号ENAのインアクティブ電圧は、電圧V5とすることが望ましい。これは、他の制御信号のインアクティブ電圧と同一にすることにより、周辺回路を簡素化することが可能となるためである。

【0071】

4)G信号(画像データ取り込み制御信号)

(a)サンプリング&リフレッシュ期間中、画像データ取り込み制御信号Gは、データ信号DATAのHレベル、Lレベル両方を包含する期間でアクティブとなること。

【0072】

(b)正極性リフレッシュ期間では、データ信号DATAの極性と対向電極電圧信号VCOMの極性が逆極性である期間においてアクティブとなり、データ信号DATAの極性と対向電極電圧信号VCOMの極性が同極性である期間においてインアクティブとなること(図5におけるリフレッシュ期間TRP1,TRP2)。

【0073】

(c)負極性リフレッシュ期間では、データ信号DATAの極性と対向電極電圧信号VCOMの極性が同極性である期間においてアクティブとなり、データ信号DATAの極性と対向電極電圧信号VCOMの極性が逆極性である期間においてインアクティブとなること(図5におけるリフレッシュ期間TRN1,TRN2)。

【0074】

(d)画像データ取り込み制御信号Gのアクティブ電圧は、電圧V1とすることが望ましい。これは、サンプリング制御信号ENAのアクティブ電圧と同一とすることにより、周辺回路の簡素化が可能となるためである。

【0075】

(e)画像データ取り込み制御信号Gのインアクティブ電圧は、電圧V5とすることが望ましい。これは、他の制御信号のインアクティブ電圧と同一にすることで周辺回路を簡素化することが可能となるためである。

【0076】

5)SET信号(画像データリフレッシュ制御信号)

(a)サンプリング&リフレッシュ期間中、画像データリフレッシュ制御信号SETは、データ信号DATAがHレベルであり、かつ画像データ取り込み制御信号Gがアクティブの期間において、アクティブとなること。

【0077】

(b)画像データリフレッシュ制御信号SETは、リフレッシュ期間前に、該制御信号のインアクティブ電圧とサンプリング期間におけるノードN1の電圧の中間レベルにプリセットすることが望ましい。

【0078】

より詳しくは、正極性リフレッシュ期間前にオンの画像データを保持している場合(ノードN1の電圧がVN1=0[V])、ノードN4の電圧レベルは、画像データに対応する電圧レベル(ノードN1の電圧レベル)にスイッチ素子SW2のスレッショルド電圧を加算したものとなっているので(ノードN4の電圧がVN4=VN1+Vth)、プリセット電圧VPSTは、該制御信号の立ち下がり時にスイッチ素子SW2をオフさせるために、

VPST>−(VDL+Vth)+(VN1+Vth)+V5 ・・・・(1)

となり、正極性リフレッシュ期間前にオフの画像データを保持している場合(ノードN1の電圧がVN1=4[V])、プリセット電圧VPSTは、該制御信号の立ち下がり時にスイッチ素子SW2をオンさせるために、

VPST≦−(VDL+Vth)+(VN1+Vth)+V5 ・・・・(2)

となる。よって、(1)、(2)式と上述の電圧設定条件より、正極性リフレッシュ期間におけるVPSTの設定可能な電圧範囲は、

0[V]≧VPST>−4[V] ・・・・(3)

となる。図5のサンプリング期間TSMP1,TSMP4では、(3)式の電圧範囲に基づいて、プリセット電圧VPSTを適宜設定すればよいが、電圧V4=0[V]に設定することが、より望ましい。これは、他の制御信号の電圧レベルと同一にすることで周辺回路を簡素化することが可能となるためである。

【0079】

一方、負極性リフレッシュ期間前にオンの画像データを保持している場合(ノードN1の電圧がVN1=8[V])、上述のとおりノードN4の電圧レベルは、画像データに対応する電圧レベル(ノードN1の電圧レベル)にスイッチ素子SW2のスレッショルド電圧を加算したものとなっているので(ノードN4の電圧がVN4=VN1+Vth)、プリセット電圧VPSTは、該制御信号の立ち下がり時にスイッチ素子SW2をオンさせるために、

VPST≦−(VDL+Vth)+(VN1+Vth)+V5 ・・・・(4)

となり、負極性リフレッシュ期間前にオフの画像データを保持している場合(ノードN1の電圧がVN1=4[V])、プリセット電圧VPSTは、該制御信号の立ち下がり時にスイッチ素子SW2をオフさせるために、

VPST>−(VDL+Vth)+(VN1+Vth)+V5 ・・・・(5)

となる。よって、(4)、(5)式と上述の電圧設定条件より、負極性リフレッシュ期間におけるVPSTの設定可能な電圧範囲は、

4[V]≧VPST>0[V] ・・・・(6)

となる。図5のサンプリング期間TSMP2,TSMP3では、(6)式の設定可能な電圧範囲に基づいて、プリセット電圧VPSTを適宜設定すればよいが、電圧V3=4[V]に設定することが、より望ましい。これは、他の制御信号の電圧レベルと同一にすることで周辺回路を簡素化することが可能となるためである。

【0080】

このプリセット動作を行わない場合には、負極性リフレッシュ時における画像データリフレッシュ制御信号SETのアクティブ後のインアクティブ電圧を電圧V5より低い電圧レベルに下げる必要が生じる。しかし、予め上述の条件に基づいてプリセットすることにより、画像データリフレッシュ制御信号SETのインアクティブ電圧は電圧V5に統一され、制御信号の電圧レベル数を削減することが可能になるとともに周辺回路を簡素化できる。

【0081】

また、(1)、(2)、(4)、(5)式に示したとおり、スイッチ素子SW2のスレッショルド電圧が相殺されることにより、スイッチ素子SW2のスレッショルド電圧がアクティブマトリクスアレイ回路内でばらついたり、経時変化によって変動したりしても、常に補償されることになるので、低消費電力表示期間中の誤動作を防止することができる。

【0082】

(c)画像データリフレッシュ制御信号SETのアクティブ電圧VSETは、上述のとおりノードN4の電圧レベルが、画像データに対応する電圧レベル(ノードN1の電圧レベル)にスイッチ素子SW2のスレッショルド電圧を加算したものとなっているので(ノードN4の電圧がVN4=VN1+Vth)、該制御信号の立ち上がり時にスイッチ素子SW2をオンさせるために、

VSET≧VDH+Vth−(VN1+Vth)+VPST ・・・・(7)

となる。

【0083】

正極性リフレッシュ期間前にオンの画像データを保持している場合(ノードN1の電圧がVN1=0[V])、上述のとおりプリセット電圧VPSTを電圧V4=0[V]に設定すれば、

VSET≧4[V] ・・・・(8)

となり、正極性リフレッシュ期間前にオフの画像データを保持している場合(ノードN1の電圧がVN1=4[V])、上述のとおりプリセット電圧VPSTを電圧V4=0[V]に設定すれば、

VSET≧0[V] ・・・・(9)

となる。よって、(8)、(9)式より、画像データリフレッシュ制御信号SETのアクティブ電圧VSETは、

VSET≧4[V] ・・・・(10)

となる。図5の正極性リフレッシュ期間TRP1,TRP2では、(10)式の設定可能な電圧範囲に基づいて、画像データリフレッシュ制御信号SETのアクティブ電圧VSETを適宜設定すればよいが、電圧V3=4[V]に設定することが、より望ましい。これは、該制御信号のアクティブ電圧レベルを同一にすることで周辺回路を簡素化することが可能となるためである。

【0084】

一方、負極性リフレッシュ期間前にオンの画像データを保持している場合(ノードN1の電圧がVN1=8[V])、上述のとおりプリセット電圧VPSTを電圧V3=4[V]に設定すれば、

VSET≧0[V] ・・・・(11)

となり、負極性リフレッシュ期間前にオフの画像データを保持している場合(ノードN1の電圧がVN1=4[V])、上述のとおりプリセット電圧VPSTを電圧V3=4[V]に設定すれば、

VSET≧4[V] ・・・・(12)

となる。よって、(11)、(12)式より、画像データリフレッシュ制御信号SETのアクティブ電圧VSETは、

VSET≧4[V] ・・・・(13)

となる。図5の負極性リフレッシュ期間TRN1,TRN2では、(13)式の設定可能な電圧範囲に基づいて、画像データリフレッシュ制御信号SETのアクティブ電圧VSETを適宜設定すればよいが、電圧V3=4[V]に設定することが、より望ましい。これは、該制御信号のアクティブ電圧レベルを同一にすることで周辺回路を簡素化することが可能となるためである。

【0085】

また、(7)式に示したとおり、スイッチ素子SW2のスレッショルド電圧は相殺されるので、スレッショルド電圧のばらつきや経時変化によって起こりうる低消費電力表示期間中の誤動作を防止することができる。

【0086】

(d)画像データリフレッシュ制御信号SETのインアクティブ電圧は、電圧V5とすることが望ましい。これは、他の制御信号のインアクティブ電圧と同一にすることで周辺回路を簡素化することが可能となるためである。

【0087】

以上の条件を基に、図2及び図5を参照しながら、各制御信号のタイミングおよび電圧レベルについて説明する。

【0088】

まず通常表示期間NDでは、通常のライン反転駆動による動画階調表示または静止画低消費電力表示のデータ書き込みが行われる。ここで、サンプリング制御信号ENA、画像データ取り込み制御信号G、画像データリフレッシュ制御信号SETのアクティブ電圧は、サンプリング期間およびリフレッシュ期間における制御信号のアクティブ電圧V1であり、同様にインアクティブ電圧もサンプリング期間およびリフレッシュ期間における制御信号のインアクティブ電圧V5とする。まず、サンプリング制御信号ENAをアクティブにすることで、スイッチ素子SW1,SW4をオンにし、ノードN4の電圧レベルを、ノードN1の電圧レベルにスイッチ素子SW2のスレッショルド電圧を加算した電圧レベルにする。その後、画像データ取り込み制御信号Gと画像データリフレッシュ制御信号SETをアクティブにすることで、スイッチ素子SW3およびSW2をオンにする。これにより、データ信号DATAの電圧レベルをスイッチ素子SW3,SW2を介して保持キャパシタC1と電気光学素子LCの静電容量CLCに保持させることができる。

【0089】

なお、サンプリング制御信号ENA、画像データ取り込み制御信号G、画像データリフレッシュ制御信号SETの電圧レベルについては、アクティブ電圧を電圧V1、インアクティブ電圧を電圧V5としたが、これに限られるものではない。しかし、電圧V1,V5を用いることにより周辺回路の簡素化が図れるという点において優位である。

【0090】

通常表示期間NDによるデータの書き込み後、低消費電力表示期間LDへ移行し、サンプリング動作および正極性/負極性リフレッシュ動作が行われる。

【0091】

低消費電力表示期間LDでは、まず、奇数行の正極性リフレッシュ動作のためのサンプリングを行うサンプリング期間TSMP1となる。

【0092】

サンプリング期間TSMP1では、対向電極電圧信号VCOMがHレベル(電圧VDH)の期間において、画像データリフレッシュ制御信号SET1を電圧V4にプリセットするとともに、サンプリング制御信号ENA1をアクティブにし、スイッチ素子SW1,SW4をオンにする。これにより、ノードN1の電圧(オン画素の場合は電圧V4、オフ画素の場合には電圧V3)が、スイッチ素子SW1を介して、画像データサンプリングキャパシタC2にサンプリングされるとともに、ダイオード接続状態のスイッチ素子SW2を介して、スレッショルド電圧サンプリングキャパシタC3にサンプリングされる。このとき、画像データサンプリングキャパシタC2にサンプリングされた電圧レベルは、ノードN1の電圧であり、一方、スレッショルド電圧サンプリングキャパシタC3には、結果としてスイッチ素子SW2のスレッショルド電圧がサンプリングされる。ノードN4の電圧レベルがノードN1の電圧とスイッチ素子SW2のスレッショルド電圧を合算した電圧レベルに到達した後、サンプリング制御信号ENA1はインアクティブとなり、スイッチ素子SW1,SW4はオフとなる。

【0093】

その後、正極性リフレッシュ動作または負極性リフレッシュ動作を行なうリフレッシュ期間に入る。図5では、サンプリング期間TSMP1の次には、奇数行において正極性リフレッシュ動作を行うリフレッシュ期間TRP1が示されている。

【0094】

正極性リフレッシュ期間TRP1では、対向電極電圧信号VCOMがLレベル(電圧VDL)かつデータ信号DATAがHレベル(電圧VDH)からLレベル(電圧VDL)に遷移する期間において、画像データ取り込み制御信号G1をアクティブにし、スイッチ素子SW3をオンにする。これにより、ノードN3には、スイッチ素子SW3を介してデータ信号DATAが到達する。

【0095】

そして、データ信号DATAがHレベルの期間において、画像データリフレッシュ制御信号SET1を該制御信号のプリセット電圧である電圧V4から該制御信号のアクティブ電圧である電圧V3にすることで、ノードN4の電圧を画像データリフレッシュ制御信号SET1の電圧変動分(=4[V])だけ変化させる。

【0096】

このとき、オン画素であれば、ノードN4の電圧は電圧(V3+Vth)となる。これは、ノードN3における電圧、すなわち、スイッチ素子SW3を通過してきたデータ信号DATAの電圧VDH(=電圧V3)よりも十分に高い電圧である。したがって、スイッチ素子SW2がオンとなる。これにより、データ信号DATAの電圧VDH(=電圧V3)が、スイッチ素子SW3,SW2を介して保持キャパシタC1と電気光学素子LCの静電容量CLCに印加される。

【0097】

オフ画素の場合には、ノードN4の電圧は電圧(V2+Vth)となる。これは、ノードN3における電圧、すなわち、スイッチ素子SW3を通過してきたデータ信号DATAの電圧VDH(=電圧V3)よりも十分に高い電圧である。したがって、スイッチ素子SW2がオンとなる。これにより、データ信号DATAの電圧VDH(=電圧V3)が、スイッチ素子SW3,SW2を介して保持キャパシタC1と電気光学素子LCの静電容量CLCに印加される。

【0098】

その後、データ信号DATAがLレベルの期間において、画像データリフレッシュ制御信号SET1を該制御信号のアクティブ電圧である電圧V3からインアクティブ電圧である電圧V5にすることで、ノードN4の電圧を、画像データリフレッシュ制御信号SET1の電圧変動分(=−8[V])だけ変化させる。

【0099】

このとき、オン画素であれば、ノードN4の電圧は電圧(V5+Vth)となる。これは、ノードN3における電圧、すなわち、スイッチ素子SW3を通過してきたデータ信号DATAの電圧VDL(=電圧V4)よりも十分に低い電圧である。したがって、スイッチ素子SW2がオフとなり、ノードN1がデータ信号DATAと切断されるため、ノードN1の電圧は、保持キャパシタC1と電気光学素子LCの静電容量CLCにより保持された電圧V3に維持される。

【0100】

ここで、電気光学素子LCの端子間電圧VLCは、ノードN1の電圧−対向電極電圧信号VCOMの電圧である。対向電極電圧信号VCOMはLレベルの区間であるため、電気光学素子LCの端子間電圧VLCは、ノードN1の電圧である電圧V3(4[V])−対向電極電圧信号VCOMの電圧VDL(0[V])、すなわち+4[V]となり、オン画素の正極性リフレッシュ動作が終了する。

【0101】

オフ画素の場合には、ノードN4の電圧は電圧(V4+Vth)となり、ノードN3における電圧、すなわち、スイッチ素子SW3を通過してきたデータ信号DATAの電圧VDL(=電圧V4)よりも十分に高い電圧である。したがって、スイッチ素子SW2がオンとなる。これにより、データ信号DATAの電圧VDL(=電圧V4)が、スイッチ素子SW3,SW2を介して保持キャパシタC1と電気光学素子LCの静電容量CLCに印加される。

【0102】

その後、画像データ取り込み制御信号G1がインアクティブとなり、スイッチ素子SW3をオフにする。これにより、ノードN1がデータ信号DATAと切断されるため、ノードN1の電圧は、保持キャパシタC1と電気光学素子LCの静電容量CLCにより保持された電圧V4に維持される。

【0103】

ここで、対向電極電圧信号VCOMはLレベルの区間であるため、電気光学素子LCの端子間電圧VLCは、ノードN1の電圧である電圧V4(0[V])−対向電極電圧信号VCOMの電圧VDL(0[V])、すなわち0[V]となり、オフ画素の正極性リフレッシュ動作が終了する。

【0104】

次に、偶数行の負極性リフレッシュ動作のためのサンプリングを行うサンプリング期間TSMP2となる。

【0105】

サンプリング期間TSMP2では、対向電極電圧信号VCOMがHレベル(電圧VDH)の期間において、画像データリフレッシュ制御信号SET2を電圧V3にプリセットするとともに、サンプリング制御信号ENA2をアクティブにし、スイッチ素子SW1をオンにする。これにより、ノードN1の電圧(オン画素の場合は電圧V2、オフ画素の場合には電圧V3)が、スイッチ素子SW1を介して、画像データサンプリングキャパシタC2にサンプリングされるとともに、ダイオード接続状態のスイッチ素子SW2を介して、スレッショルド電圧サンプリングキャパシタC3にサンプリングされる。このとき、画像データサンプリングキャパシタC2にサンプリングされた電圧レベルは、ノードN1の電圧であり、一方、スレッショルド電圧サンプリングキャパシタC3には、結果としてスイッチ素子SW2のスレッショルド電圧がサンプリングされる。ノードN4の電圧レベルがノードN1の電圧とスイッチ素子SW2のスレッショルド電圧を合算した電圧レベルに到達した後、サンプリング制御信号ENA1はインアクティブとなり、スイッチ素子SW1,SW4はオフとなる。

【0106】

サンプリング期間TSMP2の終了後、偶数行において負極性リフレッシュ動作をおこなう負極性リフレッシュ期間TRN2に入る。

【0107】

負極性リフレッシュ期間TRN2では、対向電極電圧信号VCOMがHレベル(電圧VDH)かつデータ信号DATAがHレベル(電圧VDH)からLレベル(電圧VDL)に遷移する期間において、画像データ取り込み制御信号G2をアクティブにし、スイッチ素子SW3をオンにする。これにより、ノードN3には、スイッチ素子SW3を介してデータ信号DATAが到達する。

【0108】

そして、データ信号DATAがHレベルの期間において、画像データリフレッシュ制御信号SET2を該制御信号のプリセット電圧である電圧V3のままに維持することで、ノードN4の電圧を維持する。

【0109】

このとき、オフ画素であれば、ノードN4の電圧は電圧(V3+Vth)となる。これは、ノードN3における電圧、すなわち、スイッチ素子SW3を通過してきたデータ信号DATAの電圧VDH(=電圧V3)よりも十分に高い電圧である。したがって、スイッチ素子SW2がオンとなる。これにより、データ信号DATAの電圧VDH(=電圧V3)が、スイッチ素子SW3,SW2を介して保持キャパシタC1と電気光学素子LCの静電容量CLCに印加される。

【0110】

オン画素の場合には、ノードN4の電圧は電圧(V2+Vth)となる。これは、ノードN3における電圧、すなわち、スイッチ素子SW3を通過してきたデータ信号DATAの電圧VDH(=電圧V3)よりも十分に高い電圧である。したがって、スイッチ素子SW2がオンとなる。これにより、データ信号DATAの電圧VDH(=電圧V3)が、スイッチ素子SW3,SW2を介して保持キャパシタC1と電気光学素子LCの静電容量CLCに印加される。

【0111】

その後、データ信号DATAがLレベルの期間において、画像データリフレッシュ制御信号SET2を該制御信号のアクティブ電圧である電圧V3からインアクティブ電圧である電圧V5にすることで、ノードN4の電圧を、画像データリフレッシュ制御信号SET2の電圧変動分(=−8[V])だけ変化させる。

【0112】

このとき、オフ画素であれば、ノードN4の電圧は電圧(V5+Vth)となる。これは、ノードN3における電圧、すなわち、スイッチ素子SW3を通過してきたデータ信号DATAの電圧VDL(=電圧V4)よりも十分に低い電圧である。したがって、スイッチ素子SW2がオフとなり、ノードN1がデータ信号DATAと切断されるため、ノードN1の電圧は、保持キャパシタC1と電気光学素子LCの静電容量CLCにより保持された電圧V3に維持される。

【0113】

ここで、対向電極電圧信号VCOMはHレベルの区間であるため、電気光学素子LCの端子間電圧VLCは、ノードN1の電圧である電圧V3(4[V])−対向電極電圧信号VCOMの電圧VDH(4[V])、すなわち0[V]となり、オフ画素の負極性リフレッシュ動作が終了する。

【0114】

オン画素の場合には、ノードN4の電圧は電圧(V4+Vth)となり、ノードN3における電圧、すなわち、スイッチ素子SW3を通過してきたデータ信号DATAの電圧VDL(=電圧V4)よりも十分に高い電圧である。したがって、スイッチ素子SW2がオンとなる。これにより、データ信号DATAの電圧VDL(=電圧V4)が、スイッチ素子SW3,SW2を介して保持キャパシタC1と電気光学素子LCの静電容量CLCに印加される。

【0115】

その後、画像データ取り込み制御信号G2がインアクティブとなり、スイッチ素子SW3をオフにする。これにより、ノードN1がデータ信号DATAと切断されるため、ノードN1の電圧は、保持キャパシタC1と電気光学素子LCの静電容量CLCにより保持された電圧V4に維持される。

【0116】

ここで、対向電極電圧信号VCOMはHレベルの区間であるため、電気光学素子LCの端子間電圧VLCは、ノードN1の電圧である電圧V4(0[V])−対向電極電圧信号VCOMの電圧VDH(4[V])、すなわち−4[V]となり、オン画素の負極性リフレッシュ動作が終了する。

【0117】

正極性/負極性リフレッシュ動作終了後から、次のサンプリング動作、リフレッシュ動作までの一定期間は、周辺駆動回路を停止させる。

【0118】

その後、奇数行のサンプリング期間TSMP3、奇数行の負極性リフレッシュ期間TRN1、偶数行のサンプリング期間TSMP4、偶数行の正極性リフレッシュ期間TRP2において、それぞれ上述と同様の制御をする。そして、以降は、同様の制御を繰り返すことになる。

【0119】

なお、画像データリフレッシュ制御信号SETのプリセットは、サンプリング制御信号ENAのアクティブと同時としたが、これに限定されるものではない。前のリフレッシュ動作終了後から、次のリフレッシュ動作における画像データリフレッシュ制御信号SETがアクティブになる前までの期間であって、かつサンプリング制御信号ENAがインアクティブである期間ならば、適宜プリセット可能である。しかし、画像データリフレッシュ制御信号SETのプリセットは、サンプリング制御信号ENAに同期させる方が、周辺回路の簡素化の観点から望ましい。

【0120】

以上説明した各制御信号のタイミング設定および電圧設定によれば、スイッチ素子SW2のスレッショルド電圧が、サンプリング時にノードN4の電圧に重畳されることにより、該スレッショルド電圧がアクティブマトリクスアレイ回路内でばらついたり、経時変化によって変動したりしても、常に補償されることになる。また、オン画素だけでなく、オフ画素へもオフ電圧を書き込み、それを維持する制御が行なわれる。これらにより、特許文献1で懸念される低消費電力表示期間LD中の誤動作と、オフ画素電圧が不定になる問題点が解消できる。

【0121】

さらに、奇数行が、あるリフレッシュ期間において正極性リフレッシュを行った場合には、偶数行は負極性リフレッシュを行い、次のリフレッシュ期間では奇数行が負極性リフレッシュを行い、偶数行が正極性リフレッシュを行うことにより、液晶印加電圧波形の交流化およびライン反転駆動が実現されている。

【0122】

上記の制御信号による駆動方法によれば、定期的なリフレッシュ動作を行うことにより通常表示期間NDに各画素に書き込まれたデータを保持することが可能となるため、消費電力を削減することができる。例えばVGA(640×480)の電気光学装置をライン反転駆動する場合を考える。ここで、消費電力Pは一般にP=CFV2で表せる。通常表示においては、各走査線に接続された各画素へのデータ書き込みのためにデータ線に入力されるデータ信号は、1フレームの間に240回振幅する。一方、本実施形態の駆動方法では、1フレーム(=奇数行/偶数行のサンプリングおよびリフレッシュ動作から次のサンプリングおよびリフレッシュ動作までの間)に入力されるデータ信号の振幅は2回のみとなる。したがって、本実施形態においては周波数Fが、通常表示よりも1/120となるため、他のC、Vを同じとすれば消費電力Pも1/120となり、大幅に消費電力を削減できる。

【0123】

さらに、通常表示では周辺回路を常に動作させておかなければならないが、本実施形態では、サンプリング動作、リフレッシュ動作の期間のみ駆動させればよく、それ以外の期間においては周辺回路の動作を停止させることができる。

【0124】

図10に示す特許文献1のACタイミングでは、正極性リフレッシュのための制御信号ENA,G,SETがアクティブとなってから、次の負極性リフレッシュのための制御信号ENA,G,SETがアクティブとなるまでのそれぞれの間隔と、負極性リフレッシュのための制御信号ENA,G,SETがアクティブとなってから、次の正極性リフレッシュのための制御信号ENA,G,SETがアクティブとなるまでのそれぞれの間隔が異なっている。

【0125】

そのため、電気光学素子の端子間電圧が正極性である区間TP1,TP2と、負極性である区間TN1,TN2の間隔が異なってしまう。したがって、この間隔の差が長期的には電気光学素子への直流印加となり、液晶寿命に影響する。またこのようなタイミングの制御信号で制御するには、走査線駆動回路の構成が複雑となってしまうため好ましくない。

【0126】

本実施形態におけるACタイミングでは対向電極電圧信号VCOM、データ信号DATAの極性反転タイミングを調整することにより、サンプリング制御信号ENA、画像データ取り込み制御信号G、画像データリフレッシュ制御信号SETのアクティブタイミングの間隔を一定に保つようにした。

【0127】

本実施形態では、これにより、特許文献1のACタイミングでのアクティブタイミングの間隔のズレに伴い生じていた液晶印加電圧への直流印加を防止でき、液晶の寿命をさらに延ばす効果がある。また本実施形態では、走査線駆動回路の構成を簡便化することも可能となる。

【0128】

以下に、本発明の一実施形態による周辺回路の構成および動作について、図6、図7、図8を参照しながら詳細に説明する。

【0129】

図6において、走査線駆動回路101は、シフトレジスタ601と、NORゲート602と、インバータゲート603と、トランスミッションゲート604と、n型チャネルトランジスタ605を具備する。

【0130】

シフトレジスタ601には、スタートパルス信号STVと、シフトクロック信号SCLKと、モード切替信号MODEが入力される。シフトレジスタ601から出力される走査線制御信号GCNm(m=1,2,...,m)は、NORゲート602の一方の入力端子に接続され、他方の入力端子には、モード切替信号MODEが接続される。

【0131】

NORゲート602の出力は、各行の制御信号の出力を制御するトランスミッションゲート604の負極性制御端子とn型チャネルトランジスタ605のゲートに接続されると共に、インバータゲート603の入力端子に接続される。インバータゲート603の出力は、トランスミッションゲート604の正極性制御端子に接続される。トランスミッションゲート604は、各行の制御信号線ENAm,Gm,SETm毎に設けられ、各トランスミッションゲート604の入力端子は、奇数行においては、対応する基本サンプリング制御信号ENAO、基本画像データ取り込み制御信号GO、基本画像データリフレッシュ制御信号SETOに接続され、偶数行においては、基本サンプリング制御信号ENAE、基本画像データ取り込み制御信号GE、基本画像データリフレッシュ制御信号SETEに接続される。n型チャネルトランジスタ605は、トランスミッションゲート604と同様、各行の制御信号線ENAm,Gm,SETm毎に設けられ、一方の電極端子は、各制御信号線に接続され、他方の電極端子は電源VSSに接続される。

【0132】

図8に示すとおり、通常表示期間NDにおいては、モード切替信号MODEがLレベルとなり、シフトレジスタ601に入力されたスタートパルス信号STVが、シフトクロック信号SCLKに同期して走査線制御信号GCNmとして順次出力される。走査線制御信号GCNmがHレベルになると、対応する行のトランスミッションゲート604がオンし、基本サンプリング制御信号ENAOと、基本画像データ取り込み制御信号GOと、基本画像データリフレッシュ制御信号SETOとが、対応する行の制御信号線と接続される。

【0133】

トランスミッションゲート604がオンすると、まずサンプリング制御信号ENAmがアクティブ電圧レベルとなり、水平帰線期間毎のプリチャージ動作が終了した後に、画像データ取り込み制御信号Gmと画像データリフレッシュ制御信号SETmがアクティブ電圧レベルとなり、サンプリング制御信号ENAmはインアクティブ電圧レベルとなる。走査線制御信号GCNmがLレベルになると、対応する行のトランスミッションゲート604がオフし、n型チャネルトランジスタ605がオンする。これによって、電源VSSが各制御信号線と接続される。電源VSSの電圧レベルを電圧V5とすることにより、各制御信号線はインアクティブ電圧レベルとなる。

【0134】

一方、低消費電力表示期間LDにおいては、モード切替信号MODEがHレベルとなり、シフトレジスタ601は動作を停止し、走査線制御信号GCNmの出力はLレベルとなる。サンプル&リフレッシュ期間においては、モード切替信号MODEがHレベルとなることにより、トランスミッションゲート604がオンし、奇数行制御信号線には、基本サンプリング制御信号ENAOと、基本画像データ取り込み制御信号GOと、基本画像データリフレッシュ制御信号SETOとが、接続され、偶数行制御信号線には、基本サンプリング制御信号ENAEと、基本画像データ取り込み制御信号GEと、基本画像データリフレッシュ制御信号SETEとが、接続される。

【0135】

サンプル&リフレッシュ期間においては、図5で説明した各制御信号のタイミング設定および電圧設定に従って、各基本制御信号のタイミングおよび電圧レベルが設定される。

【0136】

図7において、データ線駆動回路102は、デマルチプレクサ801と、プリチャージスイッチ802を具備する。図7、図8に示すとおり、通常表示期間NDにおいて、デマルチプレクサ801は、デマルチプレクサ制御信号DMR,DMG,DMBを排他的にHレベルとすることにより、データ信号出力回路103から入力されるソース信号Sn(n=1,2,...,n)を、RGBサブ画素のデータ線に振り分けて出力する。プリチャージスイッチ802は、水平帰線期間毎にプリチャージ制御信号PRCをHレベルとすることにより、データ信号線をプリチャージ電圧信号VPRC供給線に接続し、所望の電圧レベルに充電する。

【0137】

一方、低消費電力表示期間LDにおいては、モード切替信号MODEがHレベルとなり、データ信号出力回路103の動作を停止すると共に、デマルチプレクサ制御信号DMR,DMG,DMBをLレベルとし、デマルチプレクサ801の動作を停止する。また、プリチャージ制御信号PRCを常時Hレベルとし、静止画低消費電力表示用のデータ信号DATAをプリチャージ電圧信号VPRC供給線から供給する。

【0138】

<2.まとめ>

以上説明したように、上記実施形態における、上記の駆動回路構成および駆動方法によれば、低消費電力表示期間LDにおいて、周辺回路の大部分を停止することができ、停止した回路の消費電流は静止電流レベルとなるため、大幅な消費電力削減ができる。

【0139】

また、各データ線へ入力されるデータ信号も、低消費電力表示期間LDにおいては、アクティブマトリクスアレイ回路上の全画素において共通信号でよく、この点においても消費電力が削減可能となる。

【0140】

さらに、データ線駆動回路においては、プリチャージ電圧信号供給線から静止画低消費電力表示用のデータ信号を出力する構成としたので、通常の動画階調表示アクティブマトリクスアレイ型電気光学装置のデータ線駆動回路構成と何ら変更することなく、本実施形態の駆動を実現できるという点において優位である。

【0141】

上記述べた一実施形態においては、スイッチ素子SW1,SW2,SW3,SW4は、n型チャネルトランジスタで構成されているが、これに限定されるものではなく他のスイッチ素子で構成してもよい。例えば、p型チャネルトランジスタで構成する場合には、入力信号の極性等を見直すことにより適用可能である。

【0142】

さらに、電気光学素子LCは液晶として構成されているが、これに限定されるものではなく有機ELなどであってもよい。

【0143】

なお、上記実施形態における駆動回路及び駆動方法を備える電気光学装置を携帯電話といった携帯機器に用いた場合、待ち受け画面表示や時計表示など頻繁な画面書き換えを必要としない表示を行う際に、消費電力を大幅に削減することが可能となる。

【0144】

以上、添付図面を参照しながら本発明の好適な実施形態について詳細に説明したが、本発明はかかる例に限定されない。本発明の属する技術の分野における通常の知識を有する者であれば、特許請求の範囲に記載された技術的思想の範疇内において、各種の変更例または修正例に想到し得ることは明らかであり、これらについても、当然に本発明の技術的範囲に属するものと了解される。

【符号の説明】

【0145】

100 アクティブマトリクスアレイ回路

101 走査線駆動回路

102 データ線駆動回路

103 データ信号出力回路

104 駆動電圧生成回路

105 制御回路

201、202 画素回路

601 シフトレジスタ

602 NORゲート

603 インバータゲート

604 トランスミッションゲート

605 n型チャネルトランジスタ

801 デマルチプレクサ

802 プリチャージスイッチ

【技術分野】

【0001】

本発明は、画素回路、画素回路の駆動方法、画素回路の駆動回路及び電気光学装置に関する。

【背景技術】

【0002】

消費電力を通常の電気光学装置より大幅に抑えた、超低消費電力の、LCD等のアクティブマトリックス型電気光学装置を実現する技術として、各画素にSRAM(Static Random Access Memory)ベースのメモリ回路を内蔵したMIP(Memory In Pixel)という技術が知られている。しかし、従来のSRAMベースのMIPでは、画素に少なくとも6素子以上のトランジスタが必要となり、例えばスマートフォン等で求められる表示画像の更なる高精細化要求に対応することが出来ない。また、CMOS構成ではプロセスマスク枚数削減も困難であり、低コスト要求に答えることも難しい。

【0003】

そのような高精細化要求や低コスト要求に応えるための技術として、例えば特許文献1がある。特許文献1には、画素内部のトランジスタが3個という簡便な回路構成で、超低消費電力アクティブマトリックスアレイ装置を実現可能にするという技術が開示されている。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特表2006−523323号公報

【特許文献2】特開2004−226960号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

しかし、特許文献1に開示された画素回路は、第3のスイッチのスレッショルド電圧が変動すると、正常な電圧レベルに画素をリフレッシュすることができなくなるという問題を有する。また、オフ画素に対するリフレッシュ動作が行われないためにオフ画素に書き込まれた画像データを保持し続けることができないという問題も有する。

【0006】

さらに、LCDのように極性反転駆動を行う場合、電気光学素子への印加電圧の正極方向への反転(以下、正極性リフレッシュと称する)、印加電圧の負極方向への反転(以下、負極性リフレッシュと称する)毎に各制御信号のアクティブタイミングが異なっている。そのため、周辺回路、特に走査線駆動回路の構成が複雑となり、走査線駆動回路を制御するための制御回路の回路規模も増大することから、小型化が難しくなるとともに無駄な電力が消費されてしまうという問題と、正極性リフレッシュから負極性リフレッシュの期間と、負極性リフレッシュから正極性リフレッシュの期間、すなわち電気光学素子の端子間電圧が正極性である期間と、負極性である期間が異なるため、長期的には液晶層へ直流電圧が印加されることとなり、液晶寿命に悪影響を与えるという問題を有する。

【0007】

さらに、電気光学素子の一端をコモン電極に接続し、保持容量の一端を固定電圧としていることから、液晶層への直流印加が発生し、液晶寿命に悪影響を及ぼすことになるという問題も有する。

【0008】

一方、特許文献2には、画素回路内において、電気光学素子(OLED)への電流を制御するトランジスタのスレッショルド電圧の変動を補償して、画素の輝度ばらつきを抑えることを可能にするという技術が開示されている。しかし、特許文献2に開示された画素回路は、画素外部から入力されたデータ信号に対してトランジスタのスレッショルド電圧を重畳させることはできるが、画素内部に保持されたデータ信号に対してトランジスタのスレッショルド電圧を重畳させることはできないという問題を有する。

【0009】

また、トランジスタのスレッショルド電圧をキャパシタCVTHへ保存する際には、電気光学素子(OLED)との接続を遮断するためのトランジスタ(M2)や、基準電位Vddとの接続を制御するためのトランジスタ(M4)が必要となり、画素内部の素子数増加により高精細化の妨げとなるという問題も有する。

【0010】

そこで、本発明は、上記問題に鑑みてなされたものであり、本発明の目的とするところは、超低消費電力を実現しながら、画素回路内の素子数を削減し、さらに画素回路内のトランジスタのスレッショルド電圧の変化にも対応することが可能な、新規かつ改良された画素回路、画素回路の駆動方法、画素回路の駆動回路及び電気光学装置を提供することにある。

【課題を解決するための手段】

【0011】

上記課題を解決するために、本発明のある観点によれば、電気光学素子と、第1制御信号線上の第1制御信号により制御される第1スイッチ素子と、第2制御信号線上の第2制御信号により制御される第2スイッチ素子と、前記第2スイッチ素子の制御端子に一方の電極端子が接続され、前記第2スイッチ素子の一方の電極端子に他方の電極端子が接続される第4スイッチ素子と、前記電気光学素子に保持された画像データに対応する電圧レベルのサンプリング結果を保持する第1容量素子及び第2容量素子と、を備え、前記電気光学素子の一端は対向電極に、他端は前記第2スイッチ素子の他方の電極端子に、それぞれ接続され、前記電気光学素子に保持された画像データに対応する電圧レベルが、前記第1スイッチ素子を介して前記第1容量素子にサンプリングされ、前記第4スイッチ素子をオンすることにより、前記電気光学素子に保持された画像データに対応する電圧レベルが、前記第2スイッチ素子を介して前記第2容量素子にサンプリングされることを特徴とする、画素回路が提供される。

【0012】

前記第1容量素子の一方の端子が前記第2制御信号線に接続され、他方の端子が第2容量素子の一方の端子に接続され、前記第2容量素子の他方の端子が前記第2スイッチ素子の制御端子に接続されていてもよい。

【0013】

前記第4スイッチ素子が、前記第1制御信号により制御されるようにしてもよい。

【0014】

第3制御信号線上の第3制御信号により制御される第3スイッチ素子を、さらに備えていてもよい。

【0015】

前記第3スイッチ素子が、一方の電極端子が前記第2スイッチ素子の一方の電極端子に接続され、他方の電極端子がデータ線に接続されていてもよい。

【0016】

また、上記課題を解決するために、本発明の別の観点によれば、電気光学素子を備える画素回路の駆動方法であって、前記画素回路内の、第1制御信号線上の第1制御信号により制御される第1スイッチ素子を介して、前記電気光学素子に保持された画像データに対応する電圧レベルをサンプリングする第1のサンプリング駆動ステップと、第2スイッチ素子の制御端子に一方の電極端子が接続され、前記第2スイッチ素子の一方の電極端子に他方の電極端子が接続される第4スイッチ素子をオンすることにより、前記第2スイッチ素子を介して、前記電気光学素子に保持された画像データに対応する電圧レベルをサンプリングする第2のサンプリング駆動ステップと、前記第1のサンプリング駆動ステップにおける第1のサンプリング結果と、前記第2のサンプリング駆動ステップにおける第2のサンプリング結果とを加算したサンプリング加算結果を、第2制御信号線上の第2制御信号に重畳する電圧重畳ステップと、を備え、前記サンプリング加算結果を前記第2制御信号に重畳した電圧レベルにより、前記第2スイッチ素子を制御することを特徴とする、画素回路の駆動方法が提供される。

【0017】

前記第2制御信号が、該第2制御信号がアクティブになる前に、所定の電圧レベルでプリセットされるようにしてもよい。

【0018】

前記プリセットされる所定の電圧レベルが、前記第2スイッチ素子の特性に応じた電圧レベルであってもよい。

【0019】

前記プリセットされる所定の電圧レベルが、前記第2制御信号のインアクティブ電圧と前記電気光学素子に保持された画像データに対応する電圧レベルとの中間電圧であってもよい。

【0020】

前記サンプリング加算結果を前記第2制御信号に重畳した電圧レベルにより制御される前記第2スイッチ素子を介して供給される電圧を、前記電気光学素子に印加することにより、前記電気光学素子に保持された画像データをリフレッシュするようにしてもよい。

【0021】

前記第4スイッチ素子が、前記第1制御信号により制御されるようにしてもよい。

【0022】

また、上記課題を解決するために、本発明の別の観点によれば、電気光学素子を備える画素回路の駆動回路であって、前記画素回路内の、第1制御信号線上の第1制御信号により制御される第1スイッチ素子を介して、前記電気光学素子に保持された画像データに対応する電圧レベルをサンプリングする第1のサンプリング駆動手段と、第2スイッチ素子の制御端子に一方の電極端子が接続され、前記第2スイッチ素子の一方の電極端子に他方の電極端子が接続される第4スイッチ素子をオンすることにより、前記第2スイッチ素子を介して前記電気光学素子に保持された画像データに対応する電圧レベルをサンプリングする第2のサンプリング駆動手段と、前記第1のサンプリング駆動手段における第1のサンプリング結果と、前記第2のサンプリング駆動手段における第2のサンプリング結果とを加算したサンプリング加算結果を、第2制御信号線上の第2制御信号の電圧レベルに重畳する電圧重畳手段と、を備え、前記サンプリング加算結果を前記第2制御信号に重畳した電圧レベルにより、前記第2スイッチ素子を制御することを特徴とする、画素回路の駆動回路が提供される。

【0023】

前記第2制御信号が、該前記第2制御信号がアクティブになる前に、所定の電圧レベルでプリセットされるようにしてもよい。

【0024】

前記第4スイッチ素子が、前記第1制御信号により制御されるようにしてもよい。

【0025】

上記画素回路の駆動回路は、前記画素回路内に保持された画像データのリフレッシュ後に、前記画素回路の周辺回路の動作を停止させる手段をさらに備えていてもよい。

【0026】

また、上記課題を解決するために、本発明の別の観点によれば、上記画素回路がマトリクス状に配置されたアクティブマトリクスアレイ回路と、上記画素回路を駆動する上記画素回路の駆動回路と、を備えることを特徴とする、電気光学装置が提供される。

【発明の効果】

【0027】

以上説明したように本発明によれば、超低消費電力を実現しながら、画素回路内の素子数を削減し、さらに画素回路内のトランジスタのスレッショルド電圧の変化にも対応することが可能な、新規かつ改良された画素回路、画素回路の駆動方法、画素回路の駆動回路及び電気光学装置を提供することができる。

【図面の簡単な説明】

【0028】

【図1】本発明の一実施形態におけるアクティブマトリクス型電気光学装置のブロック図である。

【図2】本発明の一実施形態における画素回路構成図である。

【図3】本発明の一実施形態における画素回路の駆動方法を示すタイミングチャートである。

【図4】本発明の一実施形態における画素回路の動作を説明する図である。

【図5】本発明の一実施形態におけるACタイミングチャートである。

【図6】本発明の一実施形態における走査線駆動回路構成図である。

【図7】本発明の一実施形態におけるデータ線駆動回路構成図である。

【図8】本発明の一実施形態における走査線駆動回路およびデータ線駆動回路の駆動方法を示すタイミングチャートである。

【図9】従来の発明によるアクティブマトリクス型電気光学装置における画素回路構成図である。

【図10】従来の発明によるアクティブマトリクス型電気光学装置の制御において不具合の可能性を示すACタイミングチャートである。

【発明を実施するための形態】

【0029】

以下に添付図面を参照しながら、本発明の好適な実施の形態について詳細に説明する。なお、本明細書及び図面において、実質的に同一の機能構成を有する構成要素については、同一の符号を付することにより重複説明を省略する。

【0030】

<1.本発明の一実施形態>

[1−1.画素回路を用いたアクティブマトリクス型電気光学装置の構成]

まず、本発明の一実施形態にかかる画素回路を用いたアクティブマトリクス型電気光学装置の構成について説明する。図1は、本発明の一実施形態による画素回路を用いたアクティブマトリクス型電気光学装置の構成を示す説明図である。以下、図1を用いて本発明の一実施形態による画素回路を用いたアクティブマトリクス型電気光学装置の構成について説明する。

【0031】

図1に示したように、アクティブマトリクス型電気光学装置は、画素回路がアレイ状に配置されているアクティブマトリクスアレイ回路100と、走査線駆動回路101と、データ線駆動回路102と、データ信号出力回路103と、駆動電圧生成回路104と、制御回路105と、を具備する。

【0032】

制御回路105は、走査線駆動回路101と、データ線駆動回路102と、データ信号出力回路103とを制御し、さらに、対向電極電圧信号VCOMを生成し、図示しない対向電極およびアクティブマトリクスアレイ回路100に供給するとともに、その電圧レベルを制御することで、アクティブマトリクスアレイ回路100を駆動する。

【0033】

駆動電圧生成回路104は、アクティブマトリクスアレイ回路100において、アレイ状に配置されている画素回路を制御する制御信号の電圧レベルV1,V3,V4,V5と、データ信号の高電圧レベルVDHおよび低電圧レベルVDLと、を生成し、制御回路105に供給する。

【0034】

走査線駆動回路101は、制御回路105により制御され、アクティブマトリクスアレイ回路100を駆動する制御信号を生成する。

【0035】

データ線駆動回路102とデータ信号出力回路103は、制御回路105により制御され、アクティブマトリクスアレイ回路100へ出力するデータ信号を生成する。

【0036】

ここで、アクティブマトリクス型電気光学装置における1画素は、RGBのサブ画素からなり、それぞれのサブ画素は同一の画素回路を備えている。なお、図1では、アクティブマトリクスアレイ回路100に含まれる各画素回路については、素子を省略して図示し、具体的な画素回路の構成については図2で説明することにする。

【0037】

以上、図1を用いて本発明の一実施形態による画素回路を用いたアクティブマトリクス型電気光学装置の構成について説明した。次に、アクティブマトリクスアレイ回路100の1サブ画素である画素回路の構成について説明する。

【0038】

[1−2.画素回路の構成]

図2は、図1に示したアクティブマトリクスアレイ回路100の1サブ画素である画素回路の構成を示す説明図である。以下、図2を用いて、アクティブマトリクスアレイ回路100の1サブ画素である画素回路の構成について説明する。

【0039】

図2において、画素回路201はアクティブマトリクスアレイ回路100の奇数行における画素回路の1つであり、画素回路202は偶数行における画素回路の1つである。本実施形態においてそれぞれの画素回路は同一であってよい。

【0040】

画素回路201,202は、スイッチ素子SW1,SW2,SW3,SW4と、静電容量がCSMPである画像データサンプリングキャパシタC2と、静電容量がCVTHであるスレッショルド電圧サンプリングキャパシタC3と、静電容量がCSTである保持キャパシタC1と、静電容量CLCを備えた電気光学素子LCと、を具備する。電気光学素子LCと保持キャパシタC1とは、並列に接続されており、一端には、スイッチ素子SW3,SW2を介してデータ信号DATAが供給され、保持キャパシタC1の他端には、共通信号供給線から対向電極電圧信号VCOMが供給され、電気光学素子LCの他端には、対向電極から対向電極電圧信号VCOMが供給される。

【0041】

なお、特許文献1(特表2006−523323号公報)に記載の先行技術においては、電気光学素子と保持キャパシタである第1容量性サブ素子とは、一端は本実施形態と同様に共通に接続され、該一端にデータ信号が供給され、電気光学素子の他端は、対向電極(コモン電極)に接続されている。しかし、第1容量性サブ素子の他端は、本実施形態とは異なり、例えば次列のアドレス指定導体に接続されることが述べられている。

【0042】

画素回路201,202には、データ信号DATAと、電気光学素子LCの対向電極電圧信号VCOMと、データ信号DATAの画素回路内への供給を制御する画像データ取り込み制御信号G1、G2と、ノードN1の電圧レベルに対応する電圧レベルを画像データサンプリングキャパシタC2と、スレッショルド電圧サンプリングキャパシタC3にサンプリングするタイミングを制御するサンプリング制御信号ENA1、ENA2と、画素回路201,202内の電気光学素子LCおよび保持キャパシタC1をリフレッシュするタイミングを制御する画像データリフレッシュ制御信号SET1、SET2と、が入力され、画素回路201,202を制御する。ここで、各制御信号の符号最後の1,2は奇数行に対する制御信号(1)か、偶数行に対する制御信号(2)か、を示している。

【0043】

詳細な制御及び動作は後述するが、スイッチ素子SW1,SW4は、サンプリング制御信号ENAにより制御され、ノードN1の電圧レベルに対応する電圧レベルを画像データサンプリングキャパシタC2にサンプリングするとともに、結果としてスイッチ素子SW2のスレッショルド電圧をスレッショルド電圧サンプリングキャパシタC3にサンプリングする。スイッチ素子SW2は、画像データリフレッシュ制御信号SETと画像データサンプリングキャパシタC2およびスレッショルド電圧サンプリングキャパシタC3の電圧レベルにより制御される。スイッチ素子SW3は、画像データ取り込み制御信号Gにより制御され、データ信号DATAを画素回路201,202内に供給する。

【0044】

なお、画像データサンプリングキャパシタC2の静電容量CSMPおよびスレッショルド電圧サンプリングキャパシタC3の静電容量CVTHは、保持キャパシタC1の静電容量CSTと電気光学素子LCの静電容量CLCの合計の容量に対して、1/10以下にすることが望ましい。これは、サンプリング時に保持キャパシタC1と電気光学素子LCの静電容量CLCとに保持された電荷の変動が表示に影響を与えないようにするためには、可能な限り小さい容量であることが望ましいが、一方でスイッチ素子を駆動するための十分な電圧レベルを確保するためには一定以上の容量が必要となるからである。

【0045】

以上、図2を用いて、アクティブマトリクスアレイ回路100の1サブ画素である画素回路の構成について説明した。次に、本発明の一実施形態に係る画素回路201,202の制御動作原理について説明する。

【0046】

[1−3.画素回路の制御動作原理]

図3及び図4は、本発明の一実施形態に係る画素回路201,202の制御動作原理について説明する説明図である。以下、図3及び図4を用いて本発明の一実施形態に係る画素回路201,202の制御動作原理について説明する。

【0047】

図4の(a)から(c)は、画素回路201,202の制御動作原理を示すものである。ただし、図4はあくまでも原理的なものであり、実際の画素回路201,202の制御については図5以降のACタイミングにおいてさらに詳しく説明する。

【0048】

まず、図示しない通常表示においては、画像データ取り込み制御信号Gおよび画像データリフレッシュ制御信号SETをアクティブにすることにより、スイッチ素子SW3,SW2をオンにする。したがって、スイッチ素子SW3,SW2を介して、データ信号DATAの画像データを保持キャパシタC1と電気光学素子LCへ書き込むことが可能となる。保持キャパシタC1と電気光学素子LCの静電容量CLCが画像データに対応する電圧レベルまで充電された後、画像データ取り込み制御信号Gおよび画像データリフレッシュ制御信号SETをインアクティブにして、スイッチ素子SW3,SW2をオフにする。なお、スイッチ素子SW2は画像データサンプリングキャパシタC2およびスレッショルド電圧サンプリングキャパシタC3に充電された電荷が放電されるまではオフとはならない場合があるが、スイッチ素子SW3がオフとなっているため、電気光学素子LCおよび静電容量CLCに充電された画像データを保持する。さらに、スイッチ素子SW2を確実に制御するために、画像データ取り込み制御信号Gおよび画像データ書き換え制御信号SETをアクティブにする前に、予めサンプリング制御信号ENAをアクティブにしておくことが望ましい。

【0049】

通常表示が終了後、図4の(a)に示されているサンプリング動作を行う。サンプリング動作では、サンプリング期間TSMPにおいてサンプリング制御信号ENAをアクティブにすることにより、スイッチ素子SW1,SW4をオンにする。これにより、保持キャパシタC1および電気光学素子LCの静電容量CLCに保持している画像データに対応する電圧レベルが、スイッチ素子SW1を介して、画像データサンプリングキャパシタC2にサンプリングされるとともに、ダイオード接続状態のスイッチ素子SW2を介して、スレッショルド電圧サンプリングキャパシタC3にサンプリングされる。このとき、画像データサンプリングキャパシタC2にサンプリングされた電圧レベルは、保持している画像データに対応する電圧レベルであり、一方、スレッショルド電圧サンプリングキャパシタC3には、スイッチ素子SW2のスレッショルド電圧がサンプリングされる。サンプリング後、サンプリング制御信号ENAをインアクティブにすることで、スイッチ素子SW1,SW4をオフにする。

【0050】

サンプリング動作の後、図4の(b)に示されているリフレッシュ動作を行なう。リフレッシュ動作では、リフレッシュ期間TREFにおいて画像データ取り込み制御信号Gをアクティブにし、データ信号DATAをノードN3へ取り込む。さらに画像データリフレッシュ制御信号SETを所定のアクティブレベルにし、画像データリフレッシュ制御信号SETのアクティブレベルと画像データサンプリングキャパシタC2に保持された電圧レベルおよびスレッショルド電圧サンプリングキャパシタC3に保持された電圧レベルを合算した電圧レベルと、ノードN3の電圧レベルに基づき、スイッチ素子SW2のオン/オフ制御を行なう。スイッチ素子SW2のオン/オフ状態に応じて、データ信号DATAの電圧レベルを保持キャパシタC1と電気光学素子LCへ印加する。

【0051】

リフレッシュ動作の後、図4の(c)に示されているデータ保持動作を行う。データ保持動作では、画像データ取り込み制御信号Gをインアクティブにすることで、スイッチ素子SW3をオフにし、保持期間THOLDの間、保持キャパシタC1と電気光学素子LCに印加された画像データを保持する。

【0052】

そして、サンプリング動作とリフレッシュ動作を定期的に適宜繰り返す期間(以下、低消費電力表示期間と称する)においては、各画素の自己保存データに基づいた画像データのリフレッシュが行われるため、全画素同時のリフレッシュが可能である。このため、サンプリング動作とリフレッシュ動作以外の低消費電力表示期間においては、周辺回路動作を停止することができ、かつデータ書き換えに伴うデータ線の充放電電流も生じないため、消費電力が削減可能となる。

【0053】

以上の動作原理に基づき、特許文献1(特表2006−523323号公報)の先行技術における回路および各種制御信号による制御を検討すると、図9に示す、スイッチ素子SW2のスレッショルド電圧のばらつきや、経時変化によって誤動作してしまうという問題の他にも、後述する(5)、(6)式を満たさないため、図10に示すように、オフ画素のリフレッシュ動作中に、本来オフとならなければならないスイッチ素子SW2がオフとならない場合が生じ、その結果、オフ画素がリフレッシュ動作後にオン画素となってしまう誤動作が生じる可能性があることが判明した。

【0054】

また、特許文献1においては、図9に示すように、保持キャパシタC1の一端が各走査線上で共通化または隣接する走査線に接続されている。しかし、そのような構成では、電気光学素子の対向電極に供給されるVCOM電圧と保持キャパシタC1の一端から供給される信号電圧との差分電圧と、保持キャパシタC1の静電容量CSTと電気光学素子LCの静電容量CLCとの容量比に応じて生じる電圧とが、電気光学素子の端子間電圧VLCに直流電圧として重畳されてしまい、電気光学素子の表示に不具合を生じることになる。特に電気光学素子が液晶である場合には、直流電圧の重畳が、液晶寿命に悪影響を及ぼすことは言うまでもない。

【0055】

そこで本発明の実施形態においては、画素回路201,202の制御信号の1つである画像データリフレッシュ制御信号SET1,SET2に、該制御信号のアクティブ前に所定の電圧をプリセットすることで、オフ画素における誤動作を回避するとともに制御に必要な電圧レベル数を削減する。

【0056】

また、保持キャパシタC1の一端を全画素で共通化して対向電極電圧信号VCOMを供給することにより、電気光学素子LCの一端に供給される対向電極電圧信号VCOMとの差分電圧と、保持キャパシタC1の静電容量CSTと電気光学素子LCの静電容量CLCとの容量比に応じて生じる電圧とが、電気光学素子の端子間電圧VLCに直流電圧として重畳されてしまうことを解消する。これにより、電気光学素子の端子間電圧VLCに不要な直流電圧が重畳されることはなくなり、フリッカを防止することができ、さらに、電気光学素子の長寿命化が実現できる。

【0057】

以下に、本発明の一実施形態によるACタイミングについて、図2及び図5を参照しながら詳細に説明する。

【0058】

[1−4.画素回路のACタイミング]

図5は、図2に示されている本発明の一実施形態による画素回路201,202を制御する制御信号のACタイミングチャートを示す説明図である。以下、図2及び図5を用いて、本発明の一実施形態における動作に必要な制御信号のタイミングおよび必要な電圧を明確にするために詳述する。

【0059】

図5では、結果としてライン反転駆動となるように、制御信号ENA1,G1,SET1による奇数行毎の駆動と、制御信号ENA2,G2,SET2による偶数行毎の駆動とに、グループに分けて駆動を行う例を示している。フレーム反転駆動を行う場合には、図5に示す奇数行への制御信号を偶数行にも入力することにより実現できることは言うまでもない。

【0060】

今、スイッチ素子SW1,SW2,SW3,SW4は、それぞれスレッショルド電圧Vthが1[V]のトランジスタであると仮定する。そして、電気光学素子LCにオン電圧が4[V]の垂直配向液晶を用い、対向電極電圧信号VCOMおよびデータ信号DATAの高電圧レベルVDHおよび低電圧レベルVDLをそれぞれVDH=4[V]、VDL=0[V]と仮定する。さらに各制御信号が取り得る電圧レベルは、V1=12[V]、V3=4[V]、V4=0[V]、V5=−4[V]に設定されるが、これらの電圧設定に限定されるものではない。

【0061】

例えば、電圧レベルV5はデータ信号DATAの低電圧レベルVDL(=0[V])−対向電極電圧信号VCOMの振幅電圧(=4[V])+スレッショルド電圧Vth(=1[V])以下となればよく、V1はデータ信号DATAの高電圧レベルVDH(=4[V])+対向電極電圧信号VCOMの振幅電圧(=4[V])+スレッショルド電圧Vth(=1[V])以上となればよい。

【0062】

さらに、データ信号DATAの電圧レベルVDL,VDHをオフセットさせ、それに応じて電圧レベルV1,V3,V4,V5の設定を適宜変更してもよい。また、スイッチ素子SW3やスイッチ素子SW2がオフする際のキックバック電圧等により、液晶層に直流電圧が重畳されると、フリッカ等が生じることがある。この場合には、対向電極電圧信号VCOMおよびデータ信号DATAの電圧レベルを各々独立に制御してオフセット電圧を加えてもよい。

【0063】

なお、図5に示す電圧レベルV2は、上記の各電圧レベルVDH,VDL,V1,V3,V4,V5の電圧設定に応じて必然的に定まるものであり、この場合V2=8[V]となる。

【0064】

図2に示す本発明の一実施形態である画素回路201を制御するための各制御信号の設定に必要な条件を以下に列挙する。図5に示すACタイミングは、この設定条件に基づいて、各制御信号のタイミングおよび電圧を設定したものである。

【0065】

1)VCOM信号(対向電極電圧信号)

サンプリング&リフレッシュ期間中、対向電極電圧信号VCOMは、Lレベルの期間とHレベルの期間を有すること。

【0066】

2)DATA信号(データ信号)

(a)サンプリング&リフレッシュ期間中、データ信号DATAは、対向電極電圧信号VCOMがLレベルの期間に少なくとも1回HレベルからLレベルへ遷移すること。

【0067】

(b)サンプリング&リフレッシュ期間中、データ信号DATAは、対向電極電圧信号VCOMがHレベルの期間に少なくとも1回HレベルからLレベルへ遷移すること。

【0068】

3)ENA信号(サンプリング制御信号)

(a)サンプリング&リフレッシュ期間中、サンプリング制御信号ENAは、画像データ取り込み制御信号Gがアクティブ前、かつ、対向電極電圧信号VCOMがHレベルの期間中にアクティブとなることが望ましい。

【0069】

(b)サンプリング制御信号ENAのアクティブ電圧は、電圧V1とすることが望ましい。これは、ノードN1の電圧レベルが最大で、データ信号DATAの高電圧レベルVDH(=4[V])+対向電極電圧信号VCOMの振幅電圧(=4[V])の電圧レベルV2(=8[V])となるため、アクティブ電圧としてはそれよりもスレッショルド電圧Vth分以上高い電圧レベルが必要だからである。また、アクティブ電圧を他の制御信号と一律で電圧V1とすることにより、周辺回路を簡素化することが可能となるためである。

【0070】

(c)サンプリング制御信号ENAのインアクティブ電圧は、電圧V5とすることが望ましい。これは、他の制御信号のインアクティブ電圧と同一にすることにより、周辺回路を簡素化することが可能となるためである。

【0071】

4)G信号(画像データ取り込み制御信号)

(a)サンプリング&リフレッシュ期間中、画像データ取り込み制御信号Gは、データ信号DATAのHレベル、Lレベル両方を包含する期間でアクティブとなること。

【0072】

(b)正極性リフレッシュ期間では、データ信号DATAの極性と対向電極電圧信号VCOMの極性が逆極性である期間においてアクティブとなり、データ信号DATAの極性と対向電極電圧信号VCOMの極性が同極性である期間においてインアクティブとなること(図5におけるリフレッシュ期間TRP1,TRP2)。

【0073】

(c)負極性リフレッシュ期間では、データ信号DATAの極性と対向電極電圧信号VCOMの極性が同極性である期間においてアクティブとなり、データ信号DATAの極性と対向電極電圧信号VCOMの極性が逆極性である期間においてインアクティブとなること(図5におけるリフレッシュ期間TRN1,TRN2)。

【0074】

(d)画像データ取り込み制御信号Gのアクティブ電圧は、電圧V1とすることが望ましい。これは、サンプリング制御信号ENAのアクティブ電圧と同一とすることにより、周辺回路の簡素化が可能となるためである。

【0075】

(e)画像データ取り込み制御信号Gのインアクティブ電圧は、電圧V5とすることが望ましい。これは、他の制御信号のインアクティブ電圧と同一にすることで周辺回路を簡素化することが可能となるためである。

【0076】

5)SET信号(画像データリフレッシュ制御信号)

(a)サンプリング&リフレッシュ期間中、画像データリフレッシュ制御信号SETは、データ信号DATAがHレベルであり、かつ画像データ取り込み制御信号Gがアクティブの期間において、アクティブとなること。

【0077】

(b)画像データリフレッシュ制御信号SETは、リフレッシュ期間前に、該制御信号のインアクティブ電圧とサンプリング期間におけるノードN1の電圧の中間レベルにプリセットすることが望ましい。

【0078】

より詳しくは、正極性リフレッシュ期間前にオンの画像データを保持している場合(ノードN1の電圧がVN1=0[V])、ノードN4の電圧レベルは、画像データに対応する電圧レベル(ノードN1の電圧レベル)にスイッチ素子SW2のスレッショルド電圧を加算したものとなっているので(ノードN4の電圧がVN4=VN1+Vth)、プリセット電圧VPSTは、該制御信号の立ち下がり時にスイッチ素子SW2をオフさせるために、

VPST>−(VDL+Vth)+(VN1+Vth)+V5 ・・・・(1)

となり、正極性リフレッシュ期間前にオフの画像データを保持している場合(ノードN1の電圧がVN1=4[V])、プリセット電圧VPSTは、該制御信号の立ち下がり時にスイッチ素子SW2をオンさせるために、

VPST≦−(VDL+Vth)+(VN1+Vth)+V5 ・・・・(2)

となる。よって、(1)、(2)式と上述の電圧設定条件より、正極性リフレッシュ期間におけるVPSTの設定可能な電圧範囲は、

0[V]≧VPST>−4[V] ・・・・(3)

となる。図5のサンプリング期間TSMP1,TSMP4では、(3)式の電圧範囲に基づいて、プリセット電圧VPSTを適宜設定すればよいが、電圧V4=0[V]に設定することが、より望ましい。これは、他の制御信号の電圧レベルと同一にすることで周辺回路を簡素化することが可能となるためである。

【0079】

一方、負極性リフレッシュ期間前にオンの画像データを保持している場合(ノードN1の電圧がVN1=8[V])、上述のとおりノードN4の電圧レベルは、画像データに対応する電圧レベル(ノードN1の電圧レベル)にスイッチ素子SW2のスレッショルド電圧を加算したものとなっているので(ノードN4の電圧がVN4=VN1+Vth)、プリセット電圧VPSTは、該制御信号の立ち下がり時にスイッチ素子SW2をオンさせるために、

VPST≦−(VDL+Vth)+(VN1+Vth)+V5 ・・・・(4)

となり、負極性リフレッシュ期間前にオフの画像データを保持している場合(ノードN1の電圧がVN1=4[V])、プリセット電圧VPSTは、該制御信号の立ち下がり時にスイッチ素子SW2をオフさせるために、

VPST>−(VDL+Vth)+(VN1+Vth)+V5 ・・・・(5)

となる。よって、(4)、(5)式と上述の電圧設定条件より、負極性リフレッシュ期間におけるVPSTの設定可能な電圧範囲は、

4[V]≧VPST>0[V] ・・・・(6)

となる。図5のサンプリング期間TSMP2,TSMP3では、(6)式の設定可能な電圧範囲に基づいて、プリセット電圧VPSTを適宜設定すればよいが、電圧V3=4[V]に設定することが、より望ましい。これは、他の制御信号の電圧レベルと同一にすることで周辺回路を簡素化することが可能となるためである。

【0080】

このプリセット動作を行わない場合には、負極性リフレッシュ時における画像データリフレッシュ制御信号SETのアクティブ後のインアクティブ電圧を電圧V5より低い電圧レベルに下げる必要が生じる。しかし、予め上述の条件に基づいてプリセットすることにより、画像データリフレッシュ制御信号SETのインアクティブ電圧は電圧V5に統一され、制御信号の電圧レベル数を削減することが可能になるとともに周辺回路を簡素化できる。

【0081】

また、(1)、(2)、(4)、(5)式に示したとおり、スイッチ素子SW2のスレッショルド電圧が相殺されることにより、スイッチ素子SW2のスレッショルド電圧がアクティブマトリクスアレイ回路内でばらついたり、経時変化によって変動したりしても、常に補償されることになるので、低消費電力表示期間中の誤動作を防止することができる。

【0082】

(c)画像データリフレッシュ制御信号SETのアクティブ電圧VSETは、上述のとおりノードN4の電圧レベルが、画像データに対応する電圧レベル(ノードN1の電圧レベル)にスイッチ素子SW2のスレッショルド電圧を加算したものとなっているので(ノードN4の電圧がVN4=VN1+Vth)、該制御信号の立ち上がり時にスイッチ素子SW2をオンさせるために、

VSET≧VDH+Vth−(VN1+Vth)+VPST ・・・・(7)

となる。

【0083】

正極性リフレッシュ期間前にオンの画像データを保持している場合(ノードN1の電圧がVN1=0[V])、上述のとおりプリセット電圧VPSTを電圧V4=0[V]に設定すれば、

VSET≧4[V] ・・・・(8)

となり、正極性リフレッシュ期間前にオフの画像データを保持している場合(ノードN1の電圧がVN1=4[V])、上述のとおりプリセット電圧VPSTを電圧V4=0[V]に設定すれば、

VSET≧0[V] ・・・・(9)

となる。よって、(8)、(9)式より、画像データリフレッシュ制御信号SETのアクティブ電圧VSETは、

VSET≧4[V] ・・・・(10)

となる。図5の正極性リフレッシュ期間TRP1,TRP2では、(10)式の設定可能な電圧範囲に基づいて、画像データリフレッシュ制御信号SETのアクティブ電圧VSETを適宜設定すればよいが、電圧V3=4[V]に設定することが、より望ましい。これは、該制御信号のアクティブ電圧レベルを同一にすることで周辺回路を簡素化することが可能となるためである。

【0084】

一方、負極性リフレッシュ期間前にオンの画像データを保持している場合(ノードN1の電圧がVN1=8[V])、上述のとおりプリセット電圧VPSTを電圧V3=4[V]に設定すれば、

VSET≧0[V] ・・・・(11)

となり、負極性リフレッシュ期間前にオフの画像データを保持している場合(ノードN1の電圧がVN1=4[V])、上述のとおりプリセット電圧VPSTを電圧V3=4[V]に設定すれば、

VSET≧4[V] ・・・・(12)

となる。よって、(11)、(12)式より、画像データリフレッシュ制御信号SETのアクティブ電圧VSETは、

VSET≧4[V] ・・・・(13)

となる。図5の負極性リフレッシュ期間TRN1,TRN2では、(13)式の設定可能な電圧範囲に基づいて、画像データリフレッシュ制御信号SETのアクティブ電圧VSETを適宜設定すればよいが、電圧V3=4[V]に設定することが、より望ましい。これは、該制御信号のアクティブ電圧レベルを同一にすることで周辺回路を簡素化することが可能となるためである。

【0085】

また、(7)式に示したとおり、スイッチ素子SW2のスレッショルド電圧は相殺されるので、スレッショルド電圧のばらつきや経時変化によって起こりうる低消費電力表示期間中の誤動作を防止することができる。

【0086】

(d)画像データリフレッシュ制御信号SETのインアクティブ電圧は、電圧V5とすることが望ましい。これは、他の制御信号のインアクティブ電圧と同一にすることで周辺回路を簡素化することが可能となるためである。

【0087】

以上の条件を基に、図2及び図5を参照しながら、各制御信号のタイミングおよび電圧レベルについて説明する。

【0088】

まず通常表示期間NDでは、通常のライン反転駆動による動画階調表示または静止画低消費電力表示のデータ書き込みが行われる。ここで、サンプリング制御信号ENA、画像データ取り込み制御信号G、画像データリフレッシュ制御信号SETのアクティブ電圧は、サンプリング期間およびリフレッシュ期間における制御信号のアクティブ電圧V1であり、同様にインアクティブ電圧もサンプリング期間およびリフレッシュ期間における制御信号のインアクティブ電圧V5とする。まず、サンプリング制御信号ENAをアクティブにすることで、スイッチ素子SW1,SW4をオンにし、ノードN4の電圧レベルを、ノードN1の電圧レベルにスイッチ素子SW2のスレッショルド電圧を加算した電圧レベルにする。その後、画像データ取り込み制御信号Gと画像データリフレッシュ制御信号SETをアクティブにすることで、スイッチ素子SW3およびSW2をオンにする。これにより、データ信号DATAの電圧レベルをスイッチ素子SW3,SW2を介して保持キャパシタC1と電気光学素子LCの静電容量CLCに保持させることができる。

【0089】

なお、サンプリング制御信号ENA、画像データ取り込み制御信号G、画像データリフレッシュ制御信号SETの電圧レベルについては、アクティブ電圧を電圧V1、インアクティブ電圧を電圧V5としたが、これに限られるものではない。しかし、電圧V1,V5を用いることにより周辺回路の簡素化が図れるという点において優位である。

【0090】

通常表示期間NDによるデータの書き込み後、低消費電力表示期間LDへ移行し、サンプリング動作および正極性/負極性リフレッシュ動作が行われる。

【0091】

低消費電力表示期間LDでは、まず、奇数行の正極性リフレッシュ動作のためのサンプリングを行うサンプリング期間TSMP1となる。

【0092】

サンプリング期間TSMP1では、対向電極電圧信号VCOMがHレベル(電圧VDH)の期間において、画像データリフレッシュ制御信号SET1を電圧V4にプリセットするとともに、サンプリング制御信号ENA1をアクティブにし、スイッチ素子SW1,SW4をオンにする。これにより、ノードN1の電圧(オン画素の場合は電圧V4、オフ画素の場合には電圧V3)が、スイッチ素子SW1を介して、画像データサンプリングキャパシタC2にサンプリングされるとともに、ダイオード接続状態のスイッチ素子SW2を介して、スレッショルド電圧サンプリングキャパシタC3にサンプリングされる。このとき、画像データサンプリングキャパシタC2にサンプリングされた電圧レベルは、ノードN1の電圧であり、一方、スレッショルド電圧サンプリングキャパシタC3には、結果としてスイッチ素子SW2のスレッショルド電圧がサンプリングされる。ノードN4の電圧レベルがノードN1の電圧とスイッチ素子SW2のスレッショルド電圧を合算した電圧レベルに到達した後、サンプリング制御信号ENA1はインアクティブとなり、スイッチ素子SW1,SW4はオフとなる。

【0093】

その後、正極性リフレッシュ動作または負極性リフレッシュ動作を行なうリフレッシュ期間に入る。図5では、サンプリング期間TSMP1の次には、奇数行において正極性リフレッシュ動作を行うリフレッシュ期間TRP1が示されている。

【0094】

正極性リフレッシュ期間TRP1では、対向電極電圧信号VCOMがLレベル(電圧VDL)かつデータ信号DATAがHレベル(電圧VDH)からLレベル(電圧VDL)に遷移する期間において、画像データ取り込み制御信号G1をアクティブにし、スイッチ素子SW3をオンにする。これにより、ノードN3には、スイッチ素子SW3を介してデータ信号DATAが到達する。

【0095】

そして、データ信号DATAがHレベルの期間において、画像データリフレッシュ制御信号SET1を該制御信号のプリセット電圧である電圧V4から該制御信号のアクティブ電圧である電圧V3にすることで、ノードN4の電圧を画像データリフレッシュ制御信号SET1の電圧変動分(=4[V])だけ変化させる。

【0096】

このとき、オン画素であれば、ノードN4の電圧は電圧(V3+Vth)となる。これは、ノードN3における電圧、すなわち、スイッチ素子SW3を通過してきたデータ信号DATAの電圧VDH(=電圧V3)よりも十分に高い電圧である。したがって、スイッチ素子SW2がオンとなる。これにより、データ信号DATAの電圧VDH(=電圧V3)が、スイッチ素子SW3,SW2を介して保持キャパシタC1と電気光学素子LCの静電容量CLCに印加される。

【0097】

オフ画素の場合には、ノードN4の電圧は電圧(V2+Vth)となる。これは、ノードN3における電圧、すなわち、スイッチ素子SW3を通過してきたデータ信号DATAの電圧VDH(=電圧V3)よりも十分に高い電圧である。したがって、スイッチ素子SW2がオンとなる。これにより、データ信号DATAの電圧VDH(=電圧V3)が、スイッチ素子SW3,SW2を介して保持キャパシタC1と電気光学素子LCの静電容量CLCに印加される。

【0098】

その後、データ信号DATAがLレベルの期間において、画像データリフレッシュ制御信号SET1を該制御信号のアクティブ電圧である電圧V3からインアクティブ電圧である電圧V5にすることで、ノードN4の電圧を、画像データリフレッシュ制御信号SET1の電圧変動分(=−8[V])だけ変化させる。

【0099】

このとき、オン画素であれば、ノードN4の電圧は電圧(V5+Vth)となる。これは、ノードN3における電圧、すなわち、スイッチ素子SW3を通過してきたデータ信号DATAの電圧VDL(=電圧V4)よりも十分に低い電圧である。したがって、スイッチ素子SW2がオフとなり、ノードN1がデータ信号DATAと切断されるため、ノードN1の電圧は、保持キャパシタC1と電気光学素子LCの静電容量CLCにより保持された電圧V3に維持される。

【0100】

ここで、電気光学素子LCの端子間電圧VLCは、ノードN1の電圧−対向電極電圧信号VCOMの電圧である。対向電極電圧信号VCOMはLレベルの区間であるため、電気光学素子LCの端子間電圧VLCは、ノードN1の電圧である電圧V3(4[V])−対向電極電圧信号VCOMの電圧VDL(0[V])、すなわち+4[V]となり、オン画素の正極性リフレッシュ動作が終了する。

【0101】

オフ画素の場合には、ノードN4の電圧は電圧(V4+Vth)となり、ノードN3における電圧、すなわち、スイッチ素子SW3を通過してきたデータ信号DATAの電圧VDL(=電圧V4)よりも十分に高い電圧である。したがって、スイッチ素子SW2がオンとなる。これにより、データ信号DATAの電圧VDL(=電圧V4)が、スイッチ素子SW3,SW2を介して保持キャパシタC1と電気光学素子LCの静電容量CLCに印加される。

【0102】

その後、画像データ取り込み制御信号G1がインアクティブとなり、スイッチ素子SW3をオフにする。これにより、ノードN1がデータ信号DATAと切断されるため、ノードN1の電圧は、保持キャパシタC1と電気光学素子LCの静電容量CLCにより保持された電圧V4に維持される。

【0103】

ここで、対向電極電圧信号VCOMはLレベルの区間であるため、電気光学素子LCの端子間電圧VLCは、ノードN1の電圧である電圧V4(0[V])−対向電極電圧信号VCOMの電圧VDL(0[V])、すなわち0[V]となり、オフ画素の正極性リフレッシュ動作が終了する。

【0104】

次に、偶数行の負極性リフレッシュ動作のためのサンプリングを行うサンプリング期間TSMP2となる。

【0105】

サンプリング期間TSMP2では、対向電極電圧信号VCOMがHレベル(電圧VDH)の期間において、画像データリフレッシュ制御信号SET2を電圧V3にプリセットするとともに、サンプリング制御信号ENA2をアクティブにし、スイッチ素子SW1をオンにする。これにより、ノードN1の電圧(オン画素の場合は電圧V2、オフ画素の場合には電圧V3)が、スイッチ素子SW1を介して、画像データサンプリングキャパシタC2にサンプリングされるとともに、ダイオード接続状態のスイッチ素子SW2を介して、スレッショルド電圧サンプリングキャパシタC3にサンプリングされる。このとき、画像データサンプリングキャパシタC2にサンプリングされた電圧レベルは、ノードN1の電圧であり、一方、スレッショルド電圧サンプリングキャパシタC3には、結果としてスイッチ素子SW2のスレッショルド電圧がサンプリングされる。ノードN4の電圧レベルがノードN1の電圧とスイッチ素子SW2のスレッショルド電圧を合算した電圧レベルに到達した後、サンプリング制御信号ENA1はインアクティブとなり、スイッチ素子SW1,SW4はオフとなる。

【0106】

サンプリング期間TSMP2の終了後、偶数行において負極性リフレッシュ動作をおこなう負極性リフレッシュ期間TRN2に入る。

【0107】

負極性リフレッシュ期間TRN2では、対向電極電圧信号VCOMがHレベル(電圧VDH)かつデータ信号DATAがHレベル(電圧VDH)からLレベル(電圧VDL)に遷移する期間において、画像データ取り込み制御信号G2をアクティブにし、スイッチ素子SW3をオンにする。これにより、ノードN3には、スイッチ素子SW3を介してデータ信号DATAが到達する。

【0108】

そして、データ信号DATAがHレベルの期間において、画像データリフレッシュ制御信号SET2を該制御信号のプリセット電圧である電圧V3のままに維持することで、ノードN4の電圧を維持する。

【0109】

このとき、オフ画素であれば、ノードN4の電圧は電圧(V3+Vth)となる。これは、ノードN3における電圧、すなわち、スイッチ素子SW3を通過してきたデータ信号DATAの電圧VDH(=電圧V3)よりも十分に高い電圧である。したがって、スイッチ素子SW2がオンとなる。これにより、データ信号DATAの電圧VDH(=電圧V3)が、スイッチ素子SW3,SW2を介して保持キャパシタC1と電気光学素子LCの静電容量CLCに印加される。

【0110】

オン画素の場合には、ノードN4の電圧は電圧(V2+Vth)となる。これは、ノードN3における電圧、すなわち、スイッチ素子SW3を通過してきたデータ信号DATAの電圧VDH(=電圧V3)よりも十分に高い電圧である。したがって、スイッチ素子SW2がオンとなる。これにより、データ信号DATAの電圧VDH(=電圧V3)が、スイッチ素子SW3,SW2を介して保持キャパシタC1と電気光学素子LCの静電容量CLCに印加される。

【0111】

その後、データ信号DATAがLレベルの期間において、画像データリフレッシュ制御信号SET2を該制御信号のアクティブ電圧である電圧V3からインアクティブ電圧である電圧V5にすることで、ノードN4の電圧を、画像データリフレッシュ制御信号SET2の電圧変動分(=−8[V])だけ変化させる。

【0112】

このとき、オフ画素であれば、ノードN4の電圧は電圧(V5+Vth)となる。これは、ノードN3における電圧、すなわち、スイッチ素子SW3を通過してきたデータ信号DATAの電圧VDL(=電圧V4)よりも十分に低い電圧である。したがって、スイッチ素子SW2がオフとなり、ノードN1がデータ信号DATAと切断されるため、ノードN1の電圧は、保持キャパシタC1と電気光学素子LCの静電容量CLCにより保持された電圧V3に維持される。

【0113】

ここで、対向電極電圧信号VCOMはHレベルの区間であるため、電気光学素子LCの端子間電圧VLCは、ノードN1の電圧である電圧V3(4[V])−対向電極電圧信号VCOMの電圧VDH(4[V])、すなわち0[V]となり、オフ画素の負極性リフレッシュ動作が終了する。

【0114】

オン画素の場合には、ノードN4の電圧は電圧(V4+Vth)となり、ノードN3における電圧、すなわち、スイッチ素子SW3を通過してきたデータ信号DATAの電圧VDL(=電圧V4)よりも十分に高い電圧である。したがって、スイッチ素子SW2がオンとなる。これにより、データ信号DATAの電圧VDL(=電圧V4)が、スイッチ素子SW3,SW2を介して保持キャパシタC1と電気光学素子LCの静電容量CLCに印加される。

【0115】

その後、画像データ取り込み制御信号G2がインアクティブとなり、スイッチ素子SW3をオフにする。これにより、ノードN1がデータ信号DATAと切断されるため、ノードN1の電圧は、保持キャパシタC1と電気光学素子LCの静電容量CLCにより保持された電圧V4に維持される。

【0116】

ここで、対向電極電圧信号VCOMはHレベルの区間であるため、電気光学素子LCの端子間電圧VLCは、ノードN1の電圧である電圧V4(0[V])−対向電極電圧信号VCOMの電圧VDH(4[V])、すなわち−4[V]となり、オン画素の負極性リフレッシュ動作が終了する。

【0117】

正極性/負極性リフレッシュ動作終了後から、次のサンプリング動作、リフレッシュ動作までの一定期間は、周辺駆動回路を停止させる。

【0118】

その後、奇数行のサンプリング期間TSMP3、奇数行の負極性リフレッシュ期間TRN1、偶数行のサンプリング期間TSMP4、偶数行の正極性リフレッシュ期間TRP2において、それぞれ上述と同様の制御をする。そして、以降は、同様の制御を繰り返すことになる。

【0119】

なお、画像データリフレッシュ制御信号SETのプリセットは、サンプリング制御信号ENAのアクティブと同時としたが、これに限定されるものではない。前のリフレッシュ動作終了後から、次のリフレッシュ動作における画像データリフレッシュ制御信号SETがアクティブになる前までの期間であって、かつサンプリング制御信号ENAがインアクティブである期間ならば、適宜プリセット可能である。しかし、画像データリフレッシュ制御信号SETのプリセットは、サンプリング制御信号ENAに同期させる方が、周辺回路の簡素化の観点から望ましい。

【0120】

以上説明した各制御信号のタイミング設定および電圧設定によれば、スイッチ素子SW2のスレッショルド電圧が、サンプリング時にノードN4の電圧に重畳されることにより、該スレッショルド電圧がアクティブマトリクスアレイ回路内でばらついたり、経時変化によって変動したりしても、常に補償されることになる。また、オン画素だけでなく、オフ画素へもオフ電圧を書き込み、それを維持する制御が行なわれる。これらにより、特許文献1で懸念される低消費電力表示期間LD中の誤動作と、オフ画素電圧が不定になる問題点が解消できる。

【0121】

さらに、奇数行が、あるリフレッシュ期間において正極性リフレッシュを行った場合には、偶数行は負極性リフレッシュを行い、次のリフレッシュ期間では奇数行が負極性リフレッシュを行い、偶数行が正極性リフレッシュを行うことにより、液晶印加電圧波形の交流化およびライン反転駆動が実現されている。

【0122】

上記の制御信号による駆動方法によれば、定期的なリフレッシュ動作を行うことにより通常表示期間NDに各画素に書き込まれたデータを保持することが可能となるため、消費電力を削減することができる。例えばVGA(640×480)の電気光学装置をライン反転駆動する場合を考える。ここで、消費電力Pは一般にP=CFV2で表せる。通常表示においては、各走査線に接続された各画素へのデータ書き込みのためにデータ線に入力されるデータ信号は、1フレームの間に240回振幅する。一方、本実施形態の駆動方法では、1フレーム(=奇数行/偶数行のサンプリングおよびリフレッシュ動作から次のサンプリングおよびリフレッシュ動作までの間)に入力されるデータ信号の振幅は2回のみとなる。したがって、本実施形態においては周波数Fが、通常表示よりも1/120となるため、他のC、Vを同じとすれば消費電力Pも1/120となり、大幅に消費電力を削減できる。

【0123】

さらに、通常表示では周辺回路を常に動作させておかなければならないが、本実施形態では、サンプリング動作、リフレッシュ動作の期間のみ駆動させればよく、それ以外の期間においては周辺回路の動作を停止させることができる。

【0124】

図10に示す特許文献1のACタイミングでは、正極性リフレッシュのための制御信号ENA,G,SETがアクティブとなってから、次の負極性リフレッシュのための制御信号ENA,G,SETがアクティブとなるまでのそれぞれの間隔と、負極性リフレッシュのための制御信号ENA,G,SETがアクティブとなってから、次の正極性リフレッシュのための制御信号ENA,G,SETがアクティブとなるまでのそれぞれの間隔が異なっている。

【0125】

そのため、電気光学素子の端子間電圧が正極性である区間TP1,TP2と、負極性である区間TN1,TN2の間隔が異なってしまう。したがって、この間隔の差が長期的には電気光学素子への直流印加となり、液晶寿命に影響する。またこのようなタイミングの制御信号で制御するには、走査線駆動回路の構成が複雑となってしまうため好ましくない。

【0126】

本実施形態におけるACタイミングでは対向電極電圧信号VCOM、データ信号DATAの極性反転タイミングを調整することにより、サンプリング制御信号ENA、画像データ取り込み制御信号G、画像データリフレッシュ制御信号SETのアクティブタイミングの間隔を一定に保つようにした。

【0127】

本実施形態では、これにより、特許文献1のACタイミングでのアクティブタイミングの間隔のズレに伴い生じていた液晶印加電圧への直流印加を防止でき、液晶の寿命をさらに延ばす効果がある。また本実施形態では、走査線駆動回路の構成を簡便化することも可能となる。

【0128】

以下に、本発明の一実施形態による周辺回路の構成および動作について、図6、図7、図8を参照しながら詳細に説明する。

【0129】

図6において、走査線駆動回路101は、シフトレジスタ601と、NORゲート602と、インバータゲート603と、トランスミッションゲート604と、n型チャネルトランジスタ605を具備する。

【0130】

シフトレジスタ601には、スタートパルス信号STVと、シフトクロック信号SCLKと、モード切替信号MODEが入力される。シフトレジスタ601から出力される走査線制御信号GCNm(m=1,2,...,m)は、NORゲート602の一方の入力端子に接続され、他方の入力端子には、モード切替信号MODEが接続される。

【0131】

NORゲート602の出力は、各行の制御信号の出力を制御するトランスミッションゲート604の負極性制御端子とn型チャネルトランジスタ605のゲートに接続されると共に、インバータゲート603の入力端子に接続される。インバータゲート603の出力は、トランスミッションゲート604の正極性制御端子に接続される。トランスミッションゲート604は、各行の制御信号線ENAm,Gm,SETm毎に設けられ、各トランスミッションゲート604の入力端子は、奇数行においては、対応する基本サンプリング制御信号ENAO、基本画像データ取り込み制御信号GO、基本画像データリフレッシュ制御信号SETOに接続され、偶数行においては、基本サンプリング制御信号ENAE、基本画像データ取り込み制御信号GE、基本画像データリフレッシュ制御信号SETEに接続される。n型チャネルトランジスタ605は、トランスミッションゲート604と同様、各行の制御信号線ENAm,Gm,SETm毎に設けられ、一方の電極端子は、各制御信号線に接続され、他方の電極端子は電源VSSに接続される。

【0132】

図8に示すとおり、通常表示期間NDにおいては、モード切替信号MODEがLレベルとなり、シフトレジスタ601に入力されたスタートパルス信号STVが、シフトクロック信号SCLKに同期して走査線制御信号GCNmとして順次出力される。走査線制御信号GCNmがHレベルになると、対応する行のトランスミッションゲート604がオンし、基本サンプリング制御信号ENAOと、基本画像データ取り込み制御信号GOと、基本画像データリフレッシュ制御信号SETOとが、対応する行の制御信号線と接続される。

【0133】

トランスミッションゲート604がオンすると、まずサンプリング制御信号ENAmがアクティブ電圧レベルとなり、水平帰線期間毎のプリチャージ動作が終了した後に、画像データ取り込み制御信号Gmと画像データリフレッシュ制御信号SETmがアクティブ電圧レベルとなり、サンプリング制御信号ENAmはインアクティブ電圧レベルとなる。走査線制御信号GCNmがLレベルになると、対応する行のトランスミッションゲート604がオフし、n型チャネルトランジスタ605がオンする。これによって、電源VSSが各制御信号線と接続される。電源VSSの電圧レベルを電圧V5とすることにより、各制御信号線はインアクティブ電圧レベルとなる。

【0134】

一方、低消費電力表示期間LDにおいては、モード切替信号MODEがHレベルとなり、シフトレジスタ601は動作を停止し、走査線制御信号GCNmの出力はLレベルとなる。サンプル&リフレッシュ期間においては、モード切替信号MODEがHレベルとなることにより、トランスミッションゲート604がオンし、奇数行制御信号線には、基本サンプリング制御信号ENAOと、基本画像データ取り込み制御信号GOと、基本画像データリフレッシュ制御信号SETOとが、接続され、偶数行制御信号線には、基本サンプリング制御信号ENAEと、基本画像データ取り込み制御信号GEと、基本画像データリフレッシュ制御信号SETEとが、接続される。

【0135】

サンプル&リフレッシュ期間においては、図5で説明した各制御信号のタイミング設定および電圧設定に従って、各基本制御信号のタイミングおよび電圧レベルが設定される。

【0136】

図7において、データ線駆動回路102は、デマルチプレクサ801と、プリチャージスイッチ802を具備する。図7、図8に示すとおり、通常表示期間NDにおいて、デマルチプレクサ801は、デマルチプレクサ制御信号DMR,DMG,DMBを排他的にHレベルとすることにより、データ信号出力回路103から入力されるソース信号Sn(n=1,2,...,n)を、RGBサブ画素のデータ線に振り分けて出力する。プリチャージスイッチ802は、水平帰線期間毎にプリチャージ制御信号PRCをHレベルとすることにより、データ信号線をプリチャージ電圧信号VPRC供給線に接続し、所望の電圧レベルに充電する。

【0137】

一方、低消費電力表示期間LDにおいては、モード切替信号MODEがHレベルとなり、データ信号出力回路103の動作を停止すると共に、デマルチプレクサ制御信号DMR,DMG,DMBをLレベルとし、デマルチプレクサ801の動作を停止する。また、プリチャージ制御信号PRCを常時Hレベルとし、静止画低消費電力表示用のデータ信号DATAをプリチャージ電圧信号VPRC供給線から供給する。

【0138】

<2.まとめ>

以上説明したように、上記実施形態における、上記の駆動回路構成および駆動方法によれば、低消費電力表示期間LDにおいて、周辺回路の大部分を停止することができ、停止した回路の消費電流は静止電流レベルとなるため、大幅な消費電力削減ができる。

【0139】

また、各データ線へ入力されるデータ信号も、低消費電力表示期間LDにおいては、アクティブマトリクスアレイ回路上の全画素において共通信号でよく、この点においても消費電力が削減可能となる。

【0140】

さらに、データ線駆動回路においては、プリチャージ電圧信号供給線から静止画低消費電力表示用のデータ信号を出力する構成としたので、通常の動画階調表示アクティブマトリクスアレイ型電気光学装置のデータ線駆動回路構成と何ら変更することなく、本実施形態の駆動を実現できるという点において優位である。

【0141】

上記述べた一実施形態においては、スイッチ素子SW1,SW2,SW3,SW4は、n型チャネルトランジスタで構成されているが、これに限定されるものではなく他のスイッチ素子で構成してもよい。例えば、p型チャネルトランジスタで構成する場合には、入力信号の極性等を見直すことにより適用可能である。

【0142】

さらに、電気光学素子LCは液晶として構成されているが、これに限定されるものではなく有機ELなどであってもよい。

【0143】

なお、上記実施形態における駆動回路及び駆動方法を備える電気光学装置を携帯電話といった携帯機器に用いた場合、待ち受け画面表示や時計表示など頻繁な画面書き換えを必要としない表示を行う際に、消費電力を大幅に削減することが可能となる。

【0144】

以上、添付図面を参照しながら本発明の好適な実施形態について詳細に説明したが、本発明はかかる例に限定されない。本発明の属する技術の分野における通常の知識を有する者であれば、特許請求の範囲に記載された技術的思想の範疇内において、各種の変更例または修正例に想到し得ることは明らかであり、これらについても、当然に本発明の技術的範囲に属するものと了解される。

【符号の説明】

【0145】

100 アクティブマトリクスアレイ回路

101 走査線駆動回路

102 データ線駆動回路

103 データ信号出力回路

104 駆動電圧生成回路

105 制御回路

201、202 画素回路

601 シフトレジスタ

602 NORゲート

603 インバータゲート

604 トランスミッションゲート

605 n型チャネルトランジスタ

801 デマルチプレクサ

802 プリチャージスイッチ

【特許請求の範囲】

【請求項1】

電気光学素子と、

第1制御信号線上の第1制御信号により制御される第1スイッチ素子と、

第2制御信号線上の第2制御信号により制御される第2スイッチ素子と、

前記第2スイッチ素子の制御端子に一方の電極端子が接続され、前記第2スイッチ素子の一方の電極端子に他方の電極端子が接続される第4スイッチ素子と、

前記電気光学素子に保持された画像データに対応する電圧レベルのサンプリング結果を保持する第1容量素子及び第2容量素子と、

を備え、

前記電気光学素子の一端は対向電極に、他端は前記第2スイッチ素子の他方の電極端子に、それぞれ接続され、

前記電気光学素子に保持された画像データに対応する電圧レベルが、前記第1スイッチ素子を介して前記第1容量素子にサンプリングされ、

前記第4スイッチ素子をオンすることにより、前記電気光学素子に保持された画像データに対応する電圧レベルが、前記第2スイッチ素子を介して前記第2容量素子にサンプリングされることを特徴とする、画素回路。

【請求項2】

前記第1容量素子の一方の端子が前記第2制御信号線に接続され、他方の端子が第2容量素子の一方の端子に接続され、

前記第2容量素子の他方の端子が前記第2スイッチ素子の制御端子に接続されていることを特徴とする、請求項1に記載の画素回路。

【請求項3】

前記第4スイッチ素子が、前記第1制御信号により制御されることを特徴とする、請求項1に記載の画素回路。

【請求項4】

第3制御信号線上の第3制御信号により制御される第3スイッチ素子を、さらに備えることを特徴とする、請求項1に記載の画素回路。

【請求項5】

前記第3スイッチ素子が、一方の電極端子が前記第2スイッチ素子の一方の電極端子に接続され、他方の電極端子がデータ線に接続されていることを特徴とする、請求項4に記載の画素回路。

【請求項6】

電気光学素子を備える画素回路の駆動方法であって、

前記画素回路内の、第1制御信号線上の第1制御信号により制御される第1スイッチ素子を介して、前記電気光学素子に保持された画像データに対応する電圧レベルをサンプリングする第1のサンプリング駆動ステップと、

第2スイッチ素子の制御端子に一方の電極端子が接続され、前記第2スイッチ素子の一方の電極端子に他方の電極端子が接続される第4スイッチ素子をオンすることにより、前記第2スイッチ素子を介して、前記電気光学素子に保持された画像データに対応する電圧レベルをサンプリングする第2のサンプリング駆動ステップと、

前記第1のサンプリング駆動ステップにおける第1のサンプリング結果と、前記第2のサンプリング駆動ステップにおける第2のサンプリング結果とを加算したサンプリング加算結果を、第2制御信号線上の第2制御信号に重畳する電圧重畳ステップと、

を備え、

前記サンプリング加算結果を前記第2制御信号に重畳した電圧レベルにより、前記第2スイッチ素子を制御することを特徴とする、画素回路の駆動方法。

【請求項7】

前記第2制御信号が、該第2制御信号がアクティブになる前に、所定の電圧レベルでプリセットされることを特徴とする、請求項6に記載の画素回路の駆動方法。

【請求項8】

前記プリセットされる所定の電圧レベルが、前記第2スイッチ素子の特性に応じた電圧レベルであることを特徴とする、請求項7に記載の画素回路の駆動方法。

【請求項9】

前記プリセットされる所定の電圧レベルが、前記第2制御信号のインアクティブ電圧と前記電気光学素子に保持された画像データに対応する電圧レベルとの中間電圧であることを特徴とする、請求項8に記載の画素回路の駆動方法。

【請求項10】

前記サンプリング加算結果を前記第2制御信号に重畳した電圧レベルにより制御される前記第2スイッチ素子を介して供給される電圧を、前記電気光学素子に印加することにより、前記電気光学素子に保持された画像データをリフレッシュすることを特徴とする、請求項6に記載の画素回路の駆動方法。

【請求項11】

前記第4スイッチ素子が、前記第1制御信号により制御されることを特徴とする、請求項6に記載の画素回路の駆動方法。

【請求項12】

電気光学素子を備える画素回路の駆動回路であって、

前記画素回路内の、第1制御信号線上の第1制御信号により制御される第1スイッチ素子を介して、前記電気光学素子に保持された画像データに対応する電圧レベルをサンプリングする第1のサンプリング駆動手段と、

第2スイッチ素子の制御端子に一方の電極端子が接続され、前記第2スイッチ素子の一方の電極端子に他方の電極端子が接続される第4スイッチ素子をオンすることにより、前記第2スイッチ素子を介して前記電気光学素子に保持された画像データに対応する電圧レベルをサンプリングする第2のサンプリング駆動手段と、

前記第1のサンプリング駆動手段における第1のサンプリング結果と、前記第2のサンプリング駆動手段における第2のサンプリング結果とを加算したサンプリング加算結果を、第2制御信号線上の第2制御信号の電圧レベルに重畳する電圧重畳手段と、

を備え、

前記サンプリング加算結果を前記第2制御信号に重畳した電圧レベルにより、前記第2スイッチ素子を制御することを特徴とする、画素回路の駆動回路。

【請求項13】

前記第2制御信号が、該前記第2制御信号がアクティブになる前に、所定の電圧レベルでプリセットされることを特徴とする、請求項12に記載の画素回路の駆動回路。

【請求項14】

前記第4スイッチ素子が、前記第1制御信号により制御されることを特徴とする、請求項12に記載の画素回路の駆動回路。

【請求項15】

前記画素回路内に保持された画像データのリフレッシュ後に、前記画素回路の周辺回路の動作を停止させる手段をさらに備えることを特徴とする、請求項12に記載の画素回路の駆動回路。

【請求項16】

請求項1に記載の画素回路がマトリクス状に配置されたアクティブマトリクスアレイ回路と、

前記画素回路を駆動する請求項12に記載の画素回路の駆動回路と、

を備えることを特徴とする、電気光学装置。

【請求項1】

電気光学素子と、

第1制御信号線上の第1制御信号により制御される第1スイッチ素子と、

第2制御信号線上の第2制御信号により制御される第2スイッチ素子と、

前記第2スイッチ素子の制御端子に一方の電極端子が接続され、前記第2スイッチ素子の一方の電極端子に他方の電極端子が接続される第4スイッチ素子と、

前記電気光学素子に保持された画像データに対応する電圧レベルのサンプリング結果を保持する第1容量素子及び第2容量素子と、

を備え、

前記電気光学素子の一端は対向電極に、他端は前記第2スイッチ素子の他方の電極端子に、それぞれ接続され、

前記電気光学素子に保持された画像データに対応する電圧レベルが、前記第1スイッチ素子を介して前記第1容量素子にサンプリングされ、

前記第4スイッチ素子をオンすることにより、前記電気光学素子に保持された画像データに対応する電圧レベルが、前記第2スイッチ素子を介して前記第2容量素子にサンプリングされることを特徴とする、画素回路。

【請求項2】

前記第1容量素子の一方の端子が前記第2制御信号線に接続され、他方の端子が第2容量素子の一方の端子に接続され、

前記第2容量素子の他方の端子が前記第2スイッチ素子の制御端子に接続されていることを特徴とする、請求項1に記載の画素回路。

【請求項3】

前記第4スイッチ素子が、前記第1制御信号により制御されることを特徴とする、請求項1に記載の画素回路。

【請求項4】

第3制御信号線上の第3制御信号により制御される第3スイッチ素子を、さらに備えることを特徴とする、請求項1に記載の画素回路。

【請求項5】

前記第3スイッチ素子が、一方の電極端子が前記第2スイッチ素子の一方の電極端子に接続され、他方の電極端子がデータ線に接続されていることを特徴とする、請求項4に記載の画素回路。

【請求項6】

電気光学素子を備える画素回路の駆動方法であって、

前記画素回路内の、第1制御信号線上の第1制御信号により制御される第1スイッチ素子を介して、前記電気光学素子に保持された画像データに対応する電圧レベルをサンプリングする第1のサンプリング駆動ステップと、

第2スイッチ素子の制御端子に一方の電極端子が接続され、前記第2スイッチ素子の一方の電極端子に他方の電極端子が接続される第4スイッチ素子をオンすることにより、前記第2スイッチ素子を介して、前記電気光学素子に保持された画像データに対応する電圧レベルをサンプリングする第2のサンプリング駆動ステップと、

前記第1のサンプリング駆動ステップにおける第1のサンプリング結果と、前記第2のサンプリング駆動ステップにおける第2のサンプリング結果とを加算したサンプリング加算結果を、第2制御信号線上の第2制御信号に重畳する電圧重畳ステップと、

を備え、

前記サンプリング加算結果を前記第2制御信号に重畳した電圧レベルにより、前記第2スイッチ素子を制御することを特徴とする、画素回路の駆動方法。

【請求項7】

前記第2制御信号が、該第2制御信号がアクティブになる前に、所定の電圧レベルでプリセットされることを特徴とする、請求項6に記載の画素回路の駆動方法。

【請求項8】

前記プリセットされる所定の電圧レベルが、前記第2スイッチ素子の特性に応じた電圧レベルであることを特徴とする、請求項7に記載の画素回路の駆動方法。

【請求項9】

前記プリセットされる所定の電圧レベルが、前記第2制御信号のインアクティブ電圧と前記電気光学素子に保持された画像データに対応する電圧レベルとの中間電圧であることを特徴とする、請求項8に記載の画素回路の駆動方法。

【請求項10】

前記サンプリング加算結果を前記第2制御信号に重畳した電圧レベルにより制御される前記第2スイッチ素子を介して供給される電圧を、前記電気光学素子に印加することにより、前記電気光学素子に保持された画像データをリフレッシュすることを特徴とする、請求項6に記載の画素回路の駆動方法。

【請求項11】

前記第4スイッチ素子が、前記第1制御信号により制御されることを特徴とする、請求項6に記載の画素回路の駆動方法。

【請求項12】

電気光学素子を備える画素回路の駆動回路であって、

前記画素回路内の、第1制御信号線上の第1制御信号により制御される第1スイッチ素子を介して、前記電気光学素子に保持された画像データに対応する電圧レベルをサンプリングする第1のサンプリング駆動手段と、

第2スイッチ素子の制御端子に一方の電極端子が接続され、前記第2スイッチ素子の一方の電極端子に他方の電極端子が接続される第4スイッチ素子をオンすることにより、前記第2スイッチ素子を介して前記電気光学素子に保持された画像データに対応する電圧レベルをサンプリングする第2のサンプリング駆動手段と、

前記第1のサンプリング駆動手段における第1のサンプリング結果と、前記第2のサンプリング駆動手段における第2のサンプリング結果とを加算したサンプリング加算結果を、第2制御信号線上の第2制御信号の電圧レベルに重畳する電圧重畳手段と、

を備え、

前記サンプリング加算結果を前記第2制御信号に重畳した電圧レベルにより、前記第2スイッチ素子を制御することを特徴とする、画素回路の駆動回路。

【請求項13】

前記第2制御信号が、該前記第2制御信号がアクティブになる前に、所定の電圧レベルでプリセットされることを特徴とする、請求項12に記載の画素回路の駆動回路。

【請求項14】

前記第4スイッチ素子が、前記第1制御信号により制御されることを特徴とする、請求項12に記載の画素回路の駆動回路。

【請求項15】

前記画素回路内に保持された画像データのリフレッシュ後に、前記画素回路の周辺回路の動作を停止させる手段をさらに備えることを特徴とする、請求項12に記載の画素回路の駆動回路。

【請求項16】

請求項1に記載の画素回路がマトリクス状に配置されたアクティブマトリクスアレイ回路と、

前記画素回路を駆動する請求項12に記載の画素回路の駆動回路と、

を備えることを特徴とする、電気光学装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【公開番号】特開2012−93572(P2012−93572A)

【公開日】平成24年5月17日(2012.5.17)

【国際特許分類】

【出願番号】特願2010−241185(P2010−241185)

【出願日】平成22年10月27日(2010.10.27)

【出願人】(308040351)三星モバイルディスプレイ株式會社 (764)

【氏名又は名称原語表記】Samsung Mobile Display Co., Ltd.

【住所又は居所原語表記】San #24 Nongseo−Dong,Giheung−Gu,Yongin−City,Gyeonggi−Do 446−711 Republic of KOREA

【Fターム(参考)】

【公開日】平成24年5月17日(2012.5.17)

【国際特許分類】

【出願日】平成22年10月27日(2010.10.27)

【出願人】(308040351)三星モバイルディスプレイ株式會社 (764)

【氏名又は名称原語表記】Samsung Mobile Display Co., Ltd.

【住所又は居所原語表記】San #24 Nongseo−Dong,Giheung−Gu,Yongin−City,Gyeonggi−Do 446−711 Republic of KOREA

【Fターム(参考)】

[ Back to top ]