画素回路および表示装置

【課題】ドライブトランジスタの移動度の影響をキャンセル可能な画素回路を提供する。

【解決手段】少なくとも、サンプリングトランジスタと、ドライブトランジスタと、画素容量と、発光素子とを含み、サンプリングトランジスタにあっては、ゲートは走査線に接続されており、ソース及びドレインの一方は信号線に接続されており、ソース及びドレインの他方はドライブトランジスタのゲートに接続されており、ドライブトランジスタにあってはソース及びドレインの一方は発光素子の一端に接続されており、画素容量はドライブトランジスタのゲートとソース及びドレインの一方との間に接続されている画素回路であって、信号線から信号電位がドライブトランジスタのゲートに供給されている間に、ソース及びドレインの他方が電源に接続されたドライブトランジスタを介して流れる電流によってドライブトランジスタのソース及びドレインの一方の電位を信号電位に近づける。

【解決手段】少なくとも、サンプリングトランジスタと、ドライブトランジスタと、画素容量と、発光素子とを含み、サンプリングトランジスタにあっては、ゲートは走査線に接続されており、ソース及びドレインの一方は信号線に接続されており、ソース及びドレインの他方はドライブトランジスタのゲートに接続されており、ドライブトランジスタにあってはソース及びドレインの一方は発光素子の一端に接続されており、画素容量はドライブトランジスタのゲートとソース及びドレインの一方との間に接続されている画素回路であって、信号線から信号電位がドライブトランジスタのゲートに供給されている間に、ソース及びドレインの他方が電源に接続されたドライブトランジスタを介して流れる電流によってドライブトランジスタのソース及びドレインの一方の電位を信号電位に近づける。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、画素毎に配した発光素子を電流駆動する画素回路に関する。又この画素回路がマトリクス状(行列状)に配列された表示装置であって、特に各画素回路内に設けた絶縁ゲート型電界効果トランジスタによって、有機ELなどの発光素子に通電する電流量を制御する、いわゆるアクティブマトリクス型の表示装置に関する。

【背景技術】

【0002】

画像表示装置、例えば液晶ディスプレイなどでは、多数の液晶画素をマトリクス状に並べ、表示すべき画像情報に応じて画素毎に入射光の透過強度又は反射強度を制御することによって画像を表示する。これは、有機EL素子を画素に用いた有機ELディスプレイなどにおいても同様であるが、液晶画素と異なり有機EL素子は自発光素子である。その為、有機ELディスプレイは液晶ディスプレイに比べて画像の視認性が高く、バックライトが不要であり、応答速度が高いなどの利点を有する。又、各発光素子の輝度レベル(階調)はそれに流れる電流値によって制御可能であり、いわゆる電流制御型であるという点で液晶ディスプレイなどの電圧制御型とは大きく異なる。

【0003】

有機ELディスプレイにおいては、液晶ディスプレイと同様、その駆動方式として単純マトリクス方式とアクティブマトリクス方式とがある。前者は構造が単純であるものの、大型且つ高精細のディスプレイの実現が難しいなどの問題がある為、現在はアクティブマトリクス方式の開発が盛んに行なわれている。この方式は、各画素回路内部の発光素子に流れる電流を、画素回路内部に設けた能動素子(一般には薄膜トランジスタ、TFT)によって制御するものであり、以下の特許文献に記載がある。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2003−255856

【特許文献2】特開2003−271095

【特許文献3】特開2004−133240

【特許文献4】特開2004−029791

【特許文献5】特開2004−093682

【発明の概要】

【発明が解決しようとする課題】

【0005】

従来の画素回路は、制御信号を供給する行状の走査線と映像信号を供給する列状の信号線とが交差する部分に配され、少なくともサンプリングトランジスタと容量部とドライブトランジスタと発光素子とを含む。サンプリングトランジスタは、走査線から供給される制御信号に応じ導通して信号線から供給された映像信号をサンプリングする。容量部は、サンプリングされた映像信号に応じた入力電圧を保持する。ドライブトランジスタは、容量部に保持された入力電圧に応じて所定の発光期間に出力電流を供給する。尚一般に、出力電流はドライブトランジスタのチャネル領域のキャリア移動度及び閾電圧に対して依存性を有する。発光素子は、ドライブトランジスタから供給された出力電流により映像信号に応じた輝度で発光する。

【0006】

ドライブトランジスタは、容量部に保持された入力電圧をゲートに受けてソース/ドレイン間に出力電流を流し、発光素子に通電する。一般に発光素子の発光輝度は通電量に比例している。更にドライブトランジスタの出力電流供給量はゲート電圧すなわち容量部に書き込まれた入力電圧によって制御される。従来の画素回路は、ドライブトランジスタのゲートに印加される入力電圧を入力映像信号に応じて変化させることで、発光素子に供給する電流量を制御している。

【0007】

ここでドライブトランジスタの動作特性は以下の式1で表わされる。

Ids=(1/2)μ(W/L)Cox(Vgs−Vth)2・・・式1

このトランジスタ特性式1において、Idsはソース/ドレイン間に流れるドレイン電流を表わしており、画素回路では発光素子に供給される出力電流である。Vgsはソースを基準としてゲートに印加されるゲート電圧を表わしており、画素回路では上述した入力電圧である。Vthはトランジスタの閾電圧である。又μはトランジスタのチャネルを構成する半導体薄膜の移動度を表わしている。その他Wはチャネル幅を表わし、Lはチャネル長を表わし、Coxはゲート容量を表わしている。このトランジスタ特性式1から明らかな様に、薄膜トランジスタは飽和領域で動作する時、ゲート電圧Vgsが閾電圧Vthを超えて大きくなると、オン状態となってドレイン電流Idsが流れる。原理的に見ると上記のトランジスタ特性式1が示す様に、ゲート電圧Vgsが一定であれば常に同じ量のドレイン電流Idsが発光素子に供給される。従って、画面を構成する各画素に全て同一のレベルの映像信号を供給すれば、全画素が同一輝度で発光し、画面の一様性(ユニフォーミティ)が得られるはずである。

【0008】

しかしながら実際には、ポリシリコンなどの半導体薄膜で構成された薄膜トランジスタ(TFT)は、個々のデバイス特性にばらつきがある。特に、閾電圧Vthは一定ではなく、各画素毎にばらつきがある。前述のトランジスタ特性式1から明らかな様に、各ドライブトランジスタの閾電圧Vthがばらつくと、ゲート電圧Vgsが一定であっても、ドレイン電流Idsにばらつきが生じ、画素毎に輝度がばらついてしまう為、画面のユニフォーミティを損なう。従来からドライブトランジスタの閾電圧のばらつきをキャンセルする機能を組み込んだ画素回路が開発されており、例えば前記の特許文献3に開示がある。

【0009】

閾電圧のばらつきをキャンセルする機能を組み込んだ画素回路は、ある程度画面のユニフォーミティを改善することが可能である。しかしながら、ポリシリコン薄膜トランジスタの特性は、閾電圧ばかりでなく移動度μも素子毎にばらつきがある。前述のトランジスタ特性式1から明らかな様に、移動度μがばらつくと、ゲート電圧Vgsが一定であってもドレイン電流Idsにばらつきが出てしまう。この結果発光輝度が画素毎に変化する為、画面のユニフォーミティを損なうという課題がある。

【課題を解決するための手段】

【0010】

上述した従来の技術の課題に鑑み、本発明は移動度の影響をキャンセルし、以ってドライブトランジスタが供給するドレイン電流(出力電流)のばらつきを補償可能な画素回路及び表示装置とその駆動方法を提供することを目的とする。係る目的を達成する為に以下の手段を講じた。即ち本発明は、制御信号を供給する行状の走査線と映像信号を供給する列状の信号線とが交差する部分に配され、少なくともサンプリングトランジスタと、これに接続する容量部と、これに接続するドライブトランジスタと、これに接続する発光素子とを含み、前記サンプリングトランジスタは、所定のサンプリング期間に走査線から供給される制御信号に応じ導通して信号線から供給された映像信号を該容量部にサンプリングし、前記容量部は、該サンプリングされた映像信号に応じて該ドライブトランジスタのゲートとソース間に入力電圧を印加し、前記ドライブトランジスタは、所定の発光期間中該入力電圧に応じた出力電流を該発光素子に供給し、該出力電流は該ドライブトランジスタのチャネル領域のキャリア移動度に対して依存性を有し、前記発光素子は、該ドライブトランジスタから供給された出力電流により該映像信号に応じた輝度で発光する画素回路において、該出力電流のキャリア移動度に対する依存性を打ち消すために、あらかじめ該発光期間の前又は先頭で該容量部に保持された該入力電圧を補正する補正手段を備えており、前記補正手段は走査線から供給される制御信号に応じて該サンプリング期間の一部で動作し、該映像信号がサンプリングされている状態で該ドライブトランジスタから出力電流を取り出し、これを該容量部に負帰還して該入力電圧を補正することを特徴とする。

【0011】

好ましくは、前記ドライブトランジスタは、その出力電流がチャネル領域のキャリア移動度に加え閾電圧に対しても依存性を有し、前記補正手段は、該出力電流の閾電圧に対する依存性を打ち消すために、あらかじめサンプリング期間に先立って該ドライブトランジスタの閾電圧を検出し、且つ該検出された閾電圧を該入力電圧に足し込む様にしたことを特徴とする。一態様では、前記ドライブトランジスタは、Nチャネル型トランジスタでドレインが電源側に接続する一方ソースが発光素子側に接続し、前記補正手段は、該サンプリング期間の後部分に重なる該発光期間の先頭部分で該ドライブトランジスタから該出力電流を取り出して、該容量部側に負帰還する。この場合、前記補正手段は、該発光期間の先頭部分で該ドライブトランジスタのソース側から取り出した該出力電流が、該発光素子の有する容量に流れ込む様にする。更に、前記発光素子はアノード及びカソードを備えたダイオード型の発光素子からなり、アノード側が該ドライブトランジスタのソースに接続する一方カソード側が接地されており、前記補正手段は、あらかじめ該発光素子のアノード/カソード間を逆バイアス状態にセットしておき、該ドライブトランジスタのソース側から取り出した該出力電流が該発光素子に流れ込むとき、該ダイオード型の発光素子が容量性素子として機能するように制御する。他の態様では、前記ドライブトランジスタは、Pチャネル型トランジスタでソースが電源側に接続する一方ドレインが発光素子側に接続し、前記補正手段は、該発光期間よりも先行する該サンプリング期間の一部で、該ドライブトランジスタから該出力電流を取り出して該容量部側に負帰還する。好ましくは、前記補正手段は、該サンプリング期間内で該ドライブトランジスタから出力電流を取り出す時間幅を調整可能であり、これにより該容量部に対する出力電流の負帰還量を最適化する。

【0012】

又本発明は、画素アレイ部とスキャナ部と信号部とを含み、前記画素アレイ部は、行状に配された走査線と列状に配された信号線と両者が交差する部分に配された行列状の画素とからなり、前記信号部は、該信号線に映像信号を供給し、前記スキャナ部は、該走査線に制御信号を供給して順次行ごとに画素を走査し、各画素は、少なくともサンプリングトランジスタと、これに接続する容量部と、これに接続するドライブトランジスタと、これに接続する発光素子とを含み、前記サンプリングトランジスタは、所定のサンプリング期間に走査線から供給される制御信号に応じ導通して信号線から供給された映像信号を該容量部にサンプリングし、前記容量部は、該サンプリングされた映像信号に応じて該ドライブトランジスタのゲートとソース間に入力電圧を印加し、前記ドライブトランジスタは、所定の発光期間中該入力電圧に応じた出力電流を該発光素子に供給し、該出力電流は該ドライブトランジスタのチャネル領域のキャリア移動度に対して依存性を有し、前記発光素子は、該ドライブトランジスタから供給された出力電流により該映像信号に応じた輝度で発光する表示装置において、各画素は、該ドライブトランジスタの出力電流のキャリア移動度に対する依存性を打ち消すために、あらかじめ該発光期間の前又は先頭で該容量部に保持された該入力電圧を補正する補正手段を備えており、前記補正手段は走査線から供給される制御信号に応じて該サンプリング期間の一部で動作し、該映像信号がサンプリングされている状態で該ドライブトランジスタから出力電流を取り出し、これを該容量部に負帰還して該入力電圧を補正することを特徴とする。

【0013】

好ましくは、前記ドライブトランジスタは、その出力電流がチャネル領域のキャリア移動度に加え閾電圧に対しても依存性を有し、前記補正手段は、該出力電流の閾電圧に対する依存性を打ち消すために、あらかじめサンプリング期間に先立って該ドライブトランジスタの閾電圧を検出し、且つ該検出された閾電圧を該入力電圧に足し込む様にしたことを特徴とする。一態様では、前記ドライブトランジスタは、Nチャネル型トランジスタでドレインが電源側に接続する一方ソースが発光素子側に接続し、前記補正手段は、該サンプリング期間の後部分に重なる該発光期間の先頭部分で該ドライブトランジスタから該出力電流を取り出して、該容量部側に負帰還する。この場合、前記補正手段は、該発光期間の先頭部分で該ドライブトランジスタのソース側から取り出した該出力電流が、該発光素子の有する容量に流れ込む様にする。更に、前記発光素子はアノード及びカソードを備えたダイオード型の発光素子からなり、アノード側が該ドライブトランジスタのソースに接続する一方カソード側が接地されており、前記補正手段は、あらかじめ該発光素子のアノード/カソード間を逆バイアス状態にセットしておき、該ドライブトランジスタのソース側から取り出した該出力電流が該発光素子に流れ込むとき、該ダイオード型の発光素子が容量性素子として機能するように制御する。他の態様では、前記ドライブトランジスタは、Pチャネル型トランジスタでソースが電源側に接続する一方ドレインが発光素子側に接続し、前記補正手段は、該発光期間よりも先行する該サンプリング期間の一部で、該ドライブトランジスタから該出力電流を取り出して該容量部側に負帰還する。好ましくは、前記補正手段は、該サンプリング期間内で該ドライブトランジスタから出力電流を取り出す時間幅を調整可能であり、これにより該容量部に対する出力電流の負帰還量を最適化する。

【0014】

更に本発明は、画素アレイ部とスキャナ部と信号部とを含み、前記画素アレイ部は行状に配された走査線と列状に配された信号線と両者が交差する部分に配された行列状の画素とからなり、前記信号部は該信号線に映像信号を供給し、前記スキャナ部は該走査線に制御信号を供給して順次行ごとに画素を走査し、各画素は少なくともサンプリングトランジスタと、これに接続する容量部と、これに接続するドライブトランジスタと、これに接続する発光素子とを含む表示装置の駆動方法であって、前記スキャナ部は所定のサンプリング期間に走査線から該サンプリングトランジスタに制御信号を供給し導通させて、信号線から供給された映像信号を該容量部にサンプリングし、前記容量部は、該サンプリングされた映像信号に応じて該ドライブトランジスタのゲートとソース間に入力電圧を印加し、前記ドライブトランジスタは、所定の発光期間中該入力電圧に応じた出力電流を該発光素子に供給し、該出力電流は該ドライブトランジスタのチャネル領域のキャリア移動度に対して依存性を有し、前記発光素子は、該ドライブトランジスタから供給された出力電流により該映像信号に応じた輝度で発光し、更に前記スキャナ部は、該該ドライブトランジスタの出力電流のキャリア移動度に対する依存性を打ち消すために、あらかじめ該発光期間の前又は先頭で該容量部に保持された該入力電圧を補正する補正手順を該画素に行わせ、前記補正手順は、該サンプリング期間内で該映像信号がサンプリングされている間に該ドライブトランジスタから出力電流を取り出し、これを該容量部に負帰還して該入力電圧を補正する。

【発明の効果】

【0015】

本発明によれば、ドライブトランジスタの出力電流のキャリア移動度に対する依存性を打ち消す為、画素回路は発光期間の前または先頭でドライブトランジスタに対する入力電圧(ゲート電圧)を補正する補正手段を備えている。この補正手段はサンプリング期間の一部で動作し、映像信号の電位(信号電位)がサンプリングされている状態でドライブトランジスタから出力電流(ドレイン電流)を取り出し、これを容量部に負帰還して入力電圧(ゲート電圧)を補正している。前述のトランジスタ特性式1から明らかな様に、出力電流(ドレイン電流)は移動度に比例している。したがって、ある画素のドライブトランジスタの移動度が高いと、出力電流は相対的に大きくなる。これを容量部に負帰還して入力電圧(ゲート電圧)を補正する。移動度が大きいと結果的に負帰還量が大きくなるので、入力電圧(ゲート電圧)はその分大きく下方修正される。ゲート電圧が下がるので、結果的にドレイン電流は抑制される事になる。一方、別の画素のドライブトランジスタの移動度が相対的に小さい場合、ドレイン電流も少なくなる。したがって容量部に対する負帰還量も小さいので、ゲート電圧の下方修正分が小さい。結果的に、ドライブトランジスタの移動度が小さいと出力電流はさほど低く補正されない。この様に、本発明の補正手段は、移動度のばらつきをキャンセルする様に、入力電圧をフィードバック補正するので、画面のユニフォーミティが改善される。特に、信号電位をサンプリングしている状態で移動度補正をかけている。映像信号電位は黒レベルから白レベルまで振幅が変化するが、どのレベルにおいても適切に移動度補正を行う事が可能である。また、入力電圧にかける負帰還量は、出力電流の取り出し時間に依存している。取り出し時間を長く取るほど、負帰還量が大きくなる。本発明では、サンプリング期間中における出力電流の取り出し時間を可変調整して、負帰還量の最適化を測る事ができる。なお本発明では、映像信号電位をサンプリングして発光素子を電流駆動している。映像信号電位をサンプリングする点では、従来の液晶ディスプレイと同じである。したがって、アクティブマトリクス型の液晶ディスプレイで従来から広く用いられている電圧シグナルドライバを本発明の信号部に用いる事ができる。さらには、従来のポリシリコントランジスタを集積形成したアクティブマトリクス型の液晶パネルと同じ様に、本発明の表示装置でも、周辺のスキャナ部や信号部を画素アレイ部と一体的に形成した周辺回路内蔵型のパネルにまとめる事も可能である。

【図面の簡単な説明】

【0016】

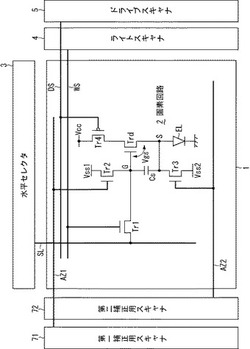

【図1】表示装置の参考例を示すブロック図である。

【図2】図1に示した表示装置に含まれる画素回路の構成を示す回路図である。

【図3】図2に示した画素回路の動作説明に供する参考タイミングチャートである。

【図4】ドライブトランジスタの入力電圧/出力電流特性を示すグラフである。

【図5】本発明にかかる表示装置の第1実施形態を示すブロック図である。

【図6】図5に示した表示装置に含まれる画素回路を取り出した模式図である。

【図7】図6に示した画素回路の動作説明に供するタイミングチャートである。

【図8】図6に示した画素回路の動作説明に供する模式図である。

【図9】同じく動作説明に供するグラフである。

【図10】同じく動作説明に供する模式図である。

【図11】図6に示した画素回路に含まれるドライブトランジスタの動作特性を示すグラフである。

【図12】本発明にかかる表示装置の第2実施形態を示すブロック図である。

【図13】図12に示した表示装置に含まれる画素回路の動作説明に供するタイミングチャートである。

【図14】同じく動作説明に供する画素回路図である。

【図15】本発明にかかる表示装置の第3実施形態を示すブロック図である。

【図16】図15に示した表示装置に含まれる画素回路の動作説明に供する模式図である。

【図17】同じく動作説明に供するタイミングチャートである。

【図18】同じく動作説明に供する模式図である。

【発明を実施するための形態】

【0017】

以下図面を参照して本発明の実施の形態を詳細に説明する。まず最初に本発明の背景を明らかにする為、図1を参照してVth補正機能を備えたアクティブマトリクス表示装置の参考例を説明する。図示する様に、アクティブマトリクス表示装置は主要部となる画素アレイ1と周辺の回路部とで構成されている。周辺の回路部は水平セレクタ3、ライトスキャナ4、ドライブスキャナ5、補正用スキャナ7などを含んでいる。画素アレイ1は行状の走査線WSと列状の信号線SLと両者の交差する部分にマトリクス状に配列した画素R,G,Bとで構成されている。カラー表示を可能とする為、RGBの三原色画素を用意しているが、本発明はこれに限られるものではない。各画素R,G,Bは夫々画素回路2で構成されている。信号線SLは水平セレクタ3によって駆動される。水平セレクタ3は信号部を構成し、信号線SLに映像信号を供給する。走査線WSはライトスキャナ4によって走査される。尚、走査線WSと平行に別の走査線DS及びAZも配線されている。走査線DSはドライブスキャナ5によって走査される。走査線AZは補正用スキャナ7によって走査される。ライトスキャナ4、ドライブスキャナ5及び補正用スキャナ7はスキャナ部を構成しており、1水平期間毎画素の行を順次走査する。各画素回路2は走査線WSによって選択された時信号線SLから映像信号をサンプリングする。更に走査線DSによって選択された時、サンプリングされた映像信号に応じて画素回路2内に含まれている発光素子を駆動する。加えて画素回路2は走査線AZによって走査された時、あらかじめ決められた補正動作を行なう。

【0018】

上述した画素アレイ1は通常ガラスなどの絶縁基板上に形成されており、フラットパネルとなっている。各画素回路2はアモルファスシリコン薄膜トランジスタ(TFT)又は低温ポリシリコンTFTで形成されている。アモルファスシリコンTFTの場合、スキャナ部はパネルとは別のTABなどで構成され、フレキシブルケーブルにてフラットパネルに接続される。低温ポリシリコンTFTの場合、信号部及びスキャナ部も同じ低温ポリシリコンTFTで形成できるので、フラットパネル上に画素アレイ部と信号部とスキャナ部を一体的に形成できる。

【0019】

図2は、図1に示した画素アレイに含まれる画素回路の構成を示す回路図である。図示する様に、画素回路2は5個の薄膜トランジスタTr1〜Tr4,Trdと2個の容量素子Cs1,Cs2と1個の発光素子ELとで構成されている。トランジスタTr1〜Tr4,Trdは全てPチャネル型のポリシリコンTFTである。但し本発明はこれに限られるものではなく、Nチャネル型のポリシリコンTFTを混在させてもよい。あるいは、Nチャネル型のアモルファスシリコンTFTで画素回路を構成してもよい。2個の容量素子Cs1とCs2は両者合わせて画素回路2の容量部を構成している。発光素子ELは例えばアノード及びカソードを備えたダイオード型の有機EL素子からなる。但し本発明はこれに限られるものではなく、発光素子は一般的に電流駆動で発光する全てのデバイスを含む。

【0020】

画素回路2の中心となるドライブトランジスタTrdはゲート(G)がG点に接続され、ソース(S)がS点に接続され、ドレイン(D)がD点に接続されている。発光素子ELはアノードがD点に接続され、カソードが接地されている。スイッチングトランジスタTr4は電源電位VccとS点との間に接続されており、発光素子ELのオン/オフを制御する。トランジスタTr4のゲートは走査線DSに接続されている。

【0021】

一方サンプリングトランジスタTr1は信号線SLとA点との間に接続されている。サンプリングトランジスタTr1のゲートは走査線WSに接続している。A点とS点との間に検出トランジスタTr5が接続されている。そのゲートは走査線AZに接続している。又スイッチングトランジスタTr3はG点と所定のオフセット電位Vofsとの間に接続されている。そのゲートは走査線AZに接続されている。尚、検出トランジスタTr5とスイッチングトランジスタTr3はVthキャンセル用の補正手段を構成している。一方の容量素子Cs1はA点とG点との間に接続され、他方の容量素子Cs2は電源電位VccとA点との間に接続されている。

【0022】

ドライブトランジスタTrdはソース/ゲート間に印加されるゲート電圧Vgsに応じてソース/ドレイン間にドレイン電流Idsを流し、これで発光素子ELを駆動する。本明細書ではゲート電圧Vgsを入力電圧とし、ドレイン電流Idsを出力電流と定義している。信号線SLから供給される映像信号Vsigに応じてゲート電圧Vgsを設定し、これによりドレイン電流Idsを流すことで、映像信号の階調に従って発光素子ELの発光輝度を制御できる。

【0023】

ドライブトランジスタTrdの閾電圧Vthは画素毎に変動する。これをキャンセルする為あらかじめドライブトランジスタTrdの閾電圧Vthを検出し、容量素子Cs1に保持しておく。この後サンプリングトランジスタTr1をオンして容量素子Cs2に信号電位Vsigを書き込む。この様にして設定されたゲート電圧Vgsにより、ドライブトランジスタTrdを駆動する。

【0024】

図3は、図2に示した画素回路の動作説明に供するタイミングチャートである。時間軸Tに沿って各走査線WS,AZ及びDSに印加される制御信号の波形を表わしてある。表記を簡略化する為、以下本明細書では制御信号も対応する走査線の符号と同じ符号で表わす。トランジスタは全てPチャネル型なので、走査線がハイレベルの時オフし、ローレベルの時オンする。そこで表記を簡略化する為、本参考例では制御信号がハイレベルからローレベルに立ち下がる場合を「オン」と表わし、ローレベルからハイレベルに立ち上がる場合を「オフ」と呼ぶ。各制御信号WS,AZ,DSの波形とともに、A点及びG点の電位変化も表わしてある。なおNチャネル型の場合は、逆に制御信号がハイレベルからローレベルに立ち下がる場合を「オフ」と表わし、ローレベルからハイレベルに立ち上がる場合を「オン」と呼ぶ。

【0025】

図示のタイミングチャートではタイミングT1〜T7までを1フィールド(1f)としてある。1フィールドの間に画素アレイの各行が1回順次走査される。タイミングチャートは、1行分の画素に印加される各制御信号WS,AZ,DSの波形を表わしてある。

【0026】

当該フィールドが始まる前のタイミングT0で、制御信号WS及びAZはオフであるのに対し、制御信号DSがオンしている。従ってサンプリングトランジスタTr1、検出トランジスタTr5及びスイッチングトランジスタTr3がオフ状態であるのに対し、スイッチングトランジスタTr4のみがオン状態にある。この状態で、A点電位は信号電位Vsigにあり、G点電位はVsigからVthだけ下がった電位にある。この時S点はトランジスタTr4がオンしているのでVccとなっている。従ってトランジスタTrdのソースとゲートとの間にはVthを超える十分な電圧が印加されており、出力電流Idsが発光素子ELに供給されている。従ってタイミングT0では発光素子ELは発光状態にある。

【0027】

この後当該フィールドに入りタイミングT1で制御信号AZがオンし、トランジスタTr5及びTr3が導通する。この結果A点とS点が直接つながるので、A点電位は電源電位Vccに急激に立ち上がる。一方トランジスタTr3がオンする為、G点電位は所定のオフセット電位Vofsまで急激に立ち下がる。

【0028】

この直後タイミングT2で制御信号DSがオフになり、スイッチングトランジスタTr4が非導通状態となる。これによりS点が電源電位Vccから切り離され、非発光状態に変わる。タイミングT1からタイミングT2までの期間T1−T2で、A点電位がVccとなりG点電位がVofsとなって各容量素子Cs1,Cs2の電位がリセットされる。このリセット動作は、次に続く検出動作を安定化する為の準備であって、期間T1−T2をリセット期間と呼ぶ。

【0029】

タイミングT2で制御信号DSがオフするとS点がVccから切り離されるので、電源からの給電が遮断される一方容量素子Cs1の放電が始まり過徒電流がトランジスタTr5を通して流れ、A点電位がVccから低下していく。G点電位に対してA点電位がVthまで低下した時、過徒電流が流れなくなる。この結果A点とG点の電位差がVthとなり、これが容量素子Cs1に保持される。

【0030】

タイミングT3で制御信号AZがオフし、トランジスタTr5及びTr3がオフして、容量素子Cs1のG点側がVofsから切り離されるとともに、A点側がS点から切り離される。タイミングT2〜T3までの期間でVthを検出し且つCs1に保持するので、期間T2−T3を特に検出期間と呼ぶ。この検出期間T2−T3はドライブトランジスタに流れる過徒電流が0になる様十分な時間幅を取ってある。

【0031】

以上説明した様に、リセット期間T1−T2におけるリセット動作と検出期間T2−T3における検出動作とで閾電圧Vthの補正動作が行なわれる。そこでリセット期間と検出期間を合わせた期間T1−T3をVth補正期間と呼ぶ。場合によっては、期間T2−T3をVth補正期間と呼ぶこともある。図3のタイミングチャートから明らかな様に、Vth補正期間T1−T3は制御信号AZによって規定される。一方、Vth補正期間T1−T3内でリセット期間T1−T2と検出期間T2−T3を区分するのが制御信号DSである。制御信号DSは基本的にスイッチングトランジスタTr4のオン/オフを制御するパルスであり、従って非発光期間と発光期間を規定している。

【0032】

Vth補正期間T1−T3が経過した後、タイミングT4で制御信号WSがオンし、サンプリングトランジスタTr1が導通する。この結果、信号線SLから供給された映像信号Vsigが容量素子Cs2にサンプリングされる。これによりA点電位はVthから信号電位Vsigに上昇する。この上昇に連動してG点電位も差分Vthを維持したまま上昇する。タイミングチャートから明らかな様に、サンプリング後でもA点電位とG点電位の電位差はVthに維持されている。この後1水平期間が経過するタイミングT5で制御信号WSはオフし、サンプリングトランジスタTr1が非導通状態となる。VsigをサンプリングしてCs2に保持するサンプリング動作は期間T4−T5で行なわれる為、これをサンプリング期間と呼ぶ。サンプリング期間T4−T5は1水平期間1Hに等しい。

【0033】

この後タイミングT6で制御信号DSが再びオンし、スイッチングトランジスタTr4が導通する。この結果ドライブトランジスタTrdはS点電位とG点電位との差Vgsに応じてドレイン電流Idsを発光素子ELに供給する。発光素子ELはこれによりVgsに応じた輝度で発光する。

【0034】

この後タイミングT7に至り当該フィールドが終了するとともに、次のフィールドに移行する。次のフィールドでは最初にリセット期間に入る。

【0035】

図3のタイミングチャートに基づいて、サンプリング期間T4−T5及びその後の発光期間における入力電圧Vgsを求める。入力電圧VgsはS点を基準にしたG点の電位である。サンプリング期間T4−T5の後の発光期間ではトランジスタTr4がオンしている為、S点電位は電源に接続されVccとなっている。一方A点電位は前述した様にVccよりもVsigだけ低い。更にG点電位はA点電位からVthだけ低い。従ってS点電位を基準にしたG点電位を表わすVgsはVcc−(Vsig−Vth)となる。前述のトランジスタ特性式1のVgsにここで求めたVcc−(Vsig−Vth)を代入すると、以下の式が得られる。

Ids=(1/2)μ(W/L)Cox(Vcc−Vsig)2

上記特性式では先の基本特性式1に含まれていたVthの項がキャンセルされ、Vcc−Vsigで置き換えられている。従って図2に示した画素回路2は、ドライブトランジスタTrdのVthに依存することなく、Vsigの値に応じた出力電流Idsを発光素子ELに供給することができる。従ってドライブトランジスタTrdのVthが画素毎にばらついていても、画素アレイとしてはそのばらつきを取り除いた出力電流を各画素の発光素子ELに供給することができる。

【0036】

図4は、上記特性式をグラフ化したものであり、縦軸に出力電流Idsを取り、横軸に入力電圧Vcc−Vsigを取ってある。合わせてグラフの傍に上記特性式を再掲してある。上記特性式から明らかな様に、ドライブトランジスタのVthの項は消えている。しかしながら移動度μが残されている。この移動度μはVthと同じくデバイス依存性があり、各画素毎にばらついている。従って、Vthをキャンセルしたのみでは出力電流Idsのばらつきは完全に抑えることはできない。グラフではμの大きいトランジスタ特性を実線で表わし、μの小さなトランジスタ特性を点線で表わしている。グラフから明らかな様に、特性式の係数μが大きくなる程、特性カーブは急峻になっている。従って入力電圧Vcc−Vsig=V0で一定であっても、移動度μのばらつきが画素間で生じる為、出力電流Idsはμに依存して変動し、画素間で輝度のばらつきが生じてしまう。特にVcc−Vsigがグレーから白表示の階調にある時移動度μに依存する輝度ばらつきが顕著となり、表示ムラが生じて解決すべき課題である。

【0037】

図5は、本発明にかかる表示装置の第1実施形態を示す回路図である。図示する様に、アクティブマトリクス表示装置は主要部となる画素アレイ1と周辺の回路部とで構成されている。周辺の回路部は水平セレクタ3、ライトスキャナ4、ドライブスキャナ5、第一補正用スキャナ71、第二補正用スキャナ72などを含んでいる。画素アレイ1は行状の走査線WSと列状の信号線SLと両者の交差する部分にマトリクス状に配列した画素回路2とで構成されている。図では理解を容易にする為、1個の画素回路2のみを拡大表示してある。信号線SLは水平セレクタ3によって駆動される。水平セレクタ3は信号部を構成し、信号線SLに映像信号を供給する。走査線WSはライトスキャナ4によって走査される。なお、走査線WSと平行に別の走査線DS,AZ1及びAZ2も配線されている。走査線DSはドライブスキャナ5によって走査される。走査線AZ1は第一補正用スキャナ71によって走査される。走査線AZ2は第二補正用スキャナ72によって走査される。ライトスキャナ4、ドライブスキャナ5、第一補正用スキャナ71及び第二補正用スキャナ72はスキャナ部を構成しており、1水平期間ごと画素の行を順次走査する。各画素回路2は走査線WSによって選択されたとき信号線SLから映像信号をサンプリングする。さらに走査線DSによって選択されたとき、サンプリングされた映像信号に応じて画素回路2内に含まれている発光素子ELを駆動する。加えて画素回路2は走査線AZ1,AZ2によって走査された時、予め決められた補正動作を行う。

【0038】

画素回路2は、5個の薄膜トランジスタTr1〜Tr4及びTrdと1個の容量素子(画素容量)Csと1個の発光素子ELとで構成されている。トランジスタTr1〜Tr3とTrdはNチャネル型のポリシリコンTFTである。トランジスタTr4のみPチャネル型のポリシリコンTFTである。1個の容量素子Csは本画素回路2の容量部を構成している。発光素子ELは例えばアノード及びカソードを備えたダイオード型の有機EL素子である。但し本発明はこれに限られるものではなく、発光素子は一般的に電流駆動で発光する全てのデバイスを含む。

【0039】

画素回路2の中心となるドライブトランジスタTrdはそのゲートGが画素容量Csの一端に接続され、そのソースSが同じく画素容量Csの他端に接続されている。またドライブトランジスタTrdのゲートGはスイッチングトランジスタTr2を介して別の基準電位Vss1に接続されている。ドライブトランジスタTrdのドレインはスイッチングトランジスタTr4を介して電源Vccに接続されている。このスイッチングトランジスタTr2のゲートは走査線AZ1に接続されている。スイッチングトランジスタTr4のゲートは走査線DSに接続している。発光素子ELのアノードはドライブトランジスタTrdのソースSに接続し、カソードは接地されている。この接地電位はVcathで表される場合がある。また、ドライブトランジスタTrdのソースSと所定の基準電位Vss2との間にスイッチングトランジスタTr3が介在している。このトランジスタTr3のゲートは走査線AZ2に接続している。一方サンプリングトランジスタTr1は信号線SLとドライブトランジスタTrdのゲートGとの間に接続されている。サンプリングトランジスタTr1のゲートは走査線WSに接続している。

【0040】

かかる構成において、サンプリングトランジスタTr1は、所定のサンプリング期間に走査線WSから供給される制御信号WSに応じ導通して信号線SLから供給された映像信号Vsigを容量部Csにサンプリングする。容量部Csは、サンプリングされた映像信号Vsigに応じてドライブトランジスタのゲートGとソースS間に入力電圧Vgsを印加する。ドライブトランジスタTrdは、所定の発光期間中入力電圧Vgsに応じた出力電流Idsを発光素子ELに供給する。なおこの出力電流(ドレイン電流)IdsはドライブトランジスタTrdのチャネル領域のキャリア移動度μ及び閾電圧Vthに対して依存性を有する。発光素子ELは、ドライブトランジスタTrdから供給された出力電流Idsにより映像信号Vsigに応じた輝度で発光する。

【0041】

本発明の特徴事項として、画素回路2はスイッチングトランジスタTr2〜Tr4で構成される補正手段を備えており、出力電流Idsのキャリア移動度μに対する依存性を打ち消す為に、予め発光期間の先頭で容量部Csに保持された入力電圧Vgsを補正する。具体的には、この補正手段(Tr2〜Tr4)は、走査線WS及びDSから供給される制御信号WS,DSに応じてサンプリング期間の一部で動作し、映像信号Vsigがサンプリングされている状態でドライブトランジスタTrdから出力電流Idsを取り出し、これを容量部Csに負帰還して入力電圧Vgsを補正する。さらにこの補正手段(Tr2〜Tr4)は、出力電流Idsの閾電圧Vthに対する依存性を打ち消すために、予めサンプリング期間に先立ってドライブトランジスタTrdの閾電圧Vthを検出し、且つ検出された閾電圧Vthを入力電圧Vgsに足し込む様にしている。

【0042】

本実施形態の場合、ドライブトランジスタTrdはNチャネル型トランジスタでドレインが電源Vcc側に接続する一方、ソースSが発光素子EL側に接続している。この場合、前述した補正手段は、サンプリング期間の後部分に重なる発光期間の先頭部分でドライブトランジスタTrdから出力電流Idsを取り出して、容量部Cs側に負帰還する。その際本補正手段は、発光期間の先頭部分でドライブトランジスタTrdのソースS側から取り出した出力電流Idsが、発光素子ELの有する容量に流れ込むようにしている。具体的には、発光素子ELはアノード及びカソードを備えたダイオード型の発光素子からなり、アノード側がドライブトランジスタTrdのソースSに接続する一方カソード側が接地されている。この構成で、本補正手段(Tr2〜Tr4)は、予め発光素子ELのアノード/カソード間を逆バイアス状態にセットしておき、ドライブトランジスタTrdのソースS側から取り出した出力電流Idsが発光素子ELに流れ込む時、このダイオード型の発光素子ELを容量性素子として機能させている。なお本補正手段は、サンプリング期間内でドライブトランジスタTrdから出力電流Idsを取り出す時間幅tを調整可能であり、これにより容量部Csに対する出力電流Idsの負帰還量を最適化している。

【0043】

図6は、図5に示した表示装置から画素回路の部分を取り出した模式図である。理解を容易にする為、サンプリングトランジスタTr1によってサンプリングされる映像信号Vsigや、ドライブトランジスタTrdの入力電圧Vgs及び出力電流Ids、さらには発光素子ELが有する容量成分Coledなどを書き加えてある。以下図6に基づいて、本画素回路2の基本的な動作を説明する。

【0044】

図7は、図6に示した画素回路のタイミングチャートである。図7を参照して、図6に示した画素回路の動作をより具体的且つ詳細に説明する。図7は、時間軸Tに沿って各走査線WS,AZ1,AZ2及びDSに印加される制御信号の波形を表してある。表記を簡略化する為、制御信号も対応する走査線の符号と同じ符号で表してある。トランジスタTr1,Tr2,Tr3はNチャネル型なので、走査線WS,AZ1,AZ2がそれぞれハイレベルの時オンし、ローレベルの時オフする。一方トランジスタTr4はPチャネル型なので、走査線DSがハイレベルの時オフし、ローレベルの時オンする。なおこのタイミングチャートは、各制御信号WS,AZ1,AZ2,DSの波形と共に、ドライブトランジスタTrdのゲートGの電位変化及びソースSの電位変化も表してある。

【0045】

図7のタイミングチャートではタイミングT1〜T8までを1フィールド(1f)としてある。1フィールドの間に画素アレイの各行が一回順次走査される。タイミングチャートは、1行分の画素に印加される各制御信号WS,AZ1,AZ2,DSの波形を表してある。

【0046】

当該フィールドが始まる前のタイミングT0で、全ての制御線号WS,AZ1,AZ2,DSがローレベルにある。したがってNチャネル型のトランジスタTr1,Tr2,Tr3はオフ状態にある一方、Pチャネル型のトランジスタTr4のみオン状態である。したがってドライブトランジスタTrdはオン状態のトランジスタTr4を介して電源Vccに接続しているので、所定の入力電圧Vgsに応じて出力電流Idsを発光素子ELに供給している。したがってタイミングT0で発光素子ELは発光している。この時ドライブトランジスタTrdに印加される入力電圧Vgsは、ゲート電位(G)とソース電位(S)の差で表される。

【0047】

当該フィールドが始まるタイミングT1で、制御信号DSがローレベルからハイレベルに切り替わる。これによりトランジスタTr4がオフし、ドライブトランジスタTrdは電源Vccから切り離されるので、発光が停止し非発光期間に入る。したがってタイミングT1に入ると、全てのトランジスタTr1〜Tr4がオフ状態になる。

【0048】

続いてタイミングT2に進むと、制御信号AZ1及びAZ2がハイレベルになるので、スイッチングトランジスタTr2及びTr3がオンする。この結果、ドライブトランジスタTrdのゲートGが基準電位Vss1に接続し、ソースSが基準電位Vss2に接続される。ここでVss1−Vss2>Vthを満たしており、Vss1−Vss2=Vgs>Vthとする事で、その後タイミングT3で行われるVth補正の準備を行う。換言すると期間T2‐T3は、ドライブトランジスタTrdのリセット期間に相当する。また、発光素子ELの閾電圧をVthELとすると、VthEL>Vss2に設定されている。これにより、発光素子ELにはマイナスバイアスが印加され、いわゆる逆バイアス状態となる。この逆バイアス状態は、後で行うVth補正動作及び移動度補正動作を正常に行うために必要である。

【0049】

タイミングT3では制御信号AZ2をローレベルにし且つ直後制御信号DSもローレベルにしている。これによりトランジスタTr3がオフする一方トランジスタTr4がオンする。この結果ドレイン電流Idsが画素容量Csに流れ込み、Vth補正動作を開始する。この時ドライブトランジスタTrdのゲートGはVss1に保持されており、ドライブトランジスタTrdがカットオフするまで電流Idsが流れる。カットオフするとドライブトランジスタTrdのソース電位(S)はVss1−Vthとなる。ドレイン電流がカットオフした後のタイミングT4で制御信号DSを再びハイレベルに戻し、スイッチングトランジスタTr4をオフする。さらに制御信号AZ1もローレベルに戻し、スイッチングトランジスタTr2もオフする。この結果、画素容量CsにVthが保持固定される。この様にタイミングT3‐T4はドライブトランジスタTrdの閾電圧Vthを検出する期間である。ここでは、この検出期間T3‐T4をVth補正期間と呼んでいる。

【0050】

この様にVth補正を行った後タイミングT5で制御信号WSをハイレベルに切り替え、サンプリングトランジスタTr1をオンして映像信号Vsigを画素容量Csに書き込む。発光素子ELの等価容量Coledに比べて画素容量Csは充分に小さい。この結果、映像信号Vsigのほとんど大部分が画素容量Csに書き込まれる。正確には、Vss1に対する。Vsigの差分Vsig−Vss1が画素容量Csに書き込まれる。したがってドライブトランジスタTrdのゲートGとソースS間の電圧Vgsは、先に検出保持されたVthと今回サンプリングされたVsig−Vss1を加えたレベル(Vsig−Vss1+Vth)となる。以降説明簡易化の為Vss1=0Vとすると、ゲート/ソース間電圧Vgsは図7のタイミングチャートに示すようにVsig+Vthとなる。かかる映像信号Vsigのサンプリングは制御信号WSがローレベルに戻るタイミングT7まで行われる。すなわちタイミングT5‐T7がサンプリング期間に相当する。

【0051】

サンプリング期間の終了するタイミングT7より前のタイミングT6で制御信号DSがローレベルとなりスイッチングトランジスタTr4がオンする。これによりドライブトランジスタTrdが電源Vccに接続されるので、画素回路は非発光期間から発光期間に進む。この様にサンプリングトランジスタTr1がまだオン状態で且つスイッチングトランジスタTr4がオン状態に入った期間T6‐T7で、ドライブトランジスタTrdの移動度補正を行う。即ち本実施形態では、サンプリング期間の後部分と発光期間の先頭部分とが重なる期間T6‐T7で移動度補正を行っている。なお、この移動度補正を行う発光期間の先頭では、発光素子ELは実際には逆バイアス状態にあるので発光する事はない。この移動度補正期間T6‐T7では、ドライブトランジスタTrdのゲートGが映像信号Vsigのレベルに固定された状態で、ドライブトランジスタTrdにドレイン電流Idsが流れる。ここでVss1−Vth<VthELと設定しておく事で、発光素子ELは逆バイアス状態におかれる為、ダイオード特性ではなく単純な容量特性を示すようになる。よってドライブトランジスタTrdに流れる電流Idsは画素容量Csと発光素子ELの等価容量Coledの両者を結合した容量C=Cs+Coledに書き込まれていく。これによりドライブトランジスタTrdのソース電位(S)は上昇していく。図7のタイミングチャートではこの上昇分をΔVで表してある。この上昇分ΔVは結局画素容量Csに保持されたゲート/ソース間電圧Vgsから差し引かれる事になるので、負帰還をかけた事になる。この様にドライブトランジスタTrdの出力電流Idsを同じくドライブトランジスタTrdの入力電圧Vgsに負帰還する事で、移動度μを補正する事が可能である。なお負帰還量ΔVは移動度補正期間T6‐T7の時間幅tを調整する事で最適化可能である。

【0052】

タイミングT7では制御信号WSがローレベルとなりサンプリングトランジスタTr1がオフする。この結果ドライブトランジスタTrdのゲートGは信号線SLから切り離される。映像信号Vsigの印加が解除されるので、ドライブトランジスタTrdのゲート電位(G)は上昇可能となり、ソース電位(S)と共に上昇していく。その間画素容量Csに保持されたゲート/ソース間電圧Vgsは(Vsig−ΔV+Vth)の値を維持する。ソース電位(S)の上昇に伴い、発光素子ELの逆バイアス状態は解消されるので、出力電流Idsの流入により発光素子ELは実際に発光を開始する。この時のドレイン電流Ids対ゲート電圧Vgsの関係は、先のトランジスタ特性式1のVgsにVsig−ΔV+Vthを代入する事で、以下の式2のように与えられる。

Ids=kμ(Vgs−Vth)2=kμ(Vsig−ΔV)2・・・式2

上記式2において、k=(1/2)(W/L)Coxである。この特性式2からVthの項がキャンセルされており、発光素子ELに供給される出力電流IdsはドライブトランジスタTrdの閾電圧Vthに依存しない事が分かる。基本的にドレイン電流Idsは映像信号の信号電圧Vsigによって決まる。換言すると、発光素子ELは映像信号Vsigに応じた輝度で発光する事になる。その際Vsigは帰還量ΔVで補正されている。この補正量ΔVは丁度特性式2の係数部に位置する移動度μの効果を打ち消すように働く。したがって、ドレイン電流Idsは実質的に映像信号Vsigのみに依存する事になる。

【0053】

最後にタイミングT8に至ると制御信号DSがハイレベルとなってスイッチングトランジスタTr4がオフし、発光が終了すると共に当該フィールドが終わる。この後次のフィールドに移って再びVth補正動作、移動度補正動作及び発光動作が繰り返される事になる。

【0054】

図8は、移動度補正期間T6‐T7における画素回路2の状態を示す回路図である。図示するように、移動度補正期間T6‐T7では、サンプリングトランジスタTr1及びスイッチングトランジスタTr4がオンしている一方、残りのスイッチングトランジスタTr2及びTr3がオフしている。この状態でドライブトランジスタTr4のソース電位(S)はVss1−Vthである。このソース電位Sは発光素子ELのアノード電位でもある。前述したようにVss1−Vth<VthELと設定しておく事で、発光素子ELは逆バイアス状態におかれ、ダイオード特性ではなく単純な容量特性を示す事になる。よってドライブトランジスタTrdに流れる電流Idsは画素容量Csと発光素子ELの等価容量Coledとの合成容量C=Cs+Coledに流れ込む事になる。換言すると、ドレイン電流Idsの一部が画素容量Csに負帰還され、移動度の補正が行われる。

【0055】

図9は上述したトランジスタ特性式2をグラフ化したものであり、縦軸にIdsを取り横軸にVsigを取ってある。このグラフの下方に特性式2も合わせて示してある。図9のグラフは、画素1と画素2を比較した状態で特性カーブを描いてある。画素1のドライブトランジスタの移動度μは相対的に大きい。逆に画素2に含まれるドライブトランジスタの移動度μは相対的に小さい。この様にドライブトランジスタをポリシリコン薄膜トランジスタなどで構成した場合、画素間で移動度μがばらつく事は避けられない。例えば両画素1,2に同レベルの映像信号Vsigを書き込んだ場合、何ら移動度の補正を行わないと、移動度μの大きい画素1に流れる出力電流Ids1´は、移動度μの小さい画素2に流れる出力電流Ids2´に比べて大きな差が生じてしまう。この様に移動度μのばらつきに起因して出力電流Idsの間に大きな差が生じるので、画面のユニフォーミティを損なう事になる。

【0056】

そこで本発明では出力電流を入力電圧側に負帰還させる事で移動度のばらつきをキャンセルしている。トランジスタ特性式から明らかなように、移動度が大きいとドレイン電流Idsが大きくなる。したがって負帰還量ΔVは移動度が大きいほど大きくなる。図9のグラフに示すように、移動度μの大きな画素1の負帰還量ΔV1は移動度の小さな画素2の負帰還量ΔV2に比べて大きい。したがって、移動度μが大きいほど負帰還が大きくかかる事となって、ばらつきを抑制する事が可能である。図示するように、移動度μの大きな画素1でΔV1の補正をかけると、出力電流はIds1´からIds1まで大きく下降する。一方移動度μの小さな画素2の補正量ΔV2は小さいので、出力電流Ids2´はIds2までそれ程大きく下降しない。結果的に、Ids1とIds2は略等しくなり、移動度のばらつきがキャンセルされる。この移動度のばらつきのキャンセルは黒レベルから白レベルまでVsigの全範囲で行われるので、画面のユニフォーミティは極めて高くなる。以上をまとめると、移動度の異なる画素1と2があった場合、移動度の大きい画素1の補正量ΔV1は移動度の小さい画素2の補正量ΔV2に対して小さくなる。つまり移動度が大きいほどΔVが大きくIdsの減少値は大きくなる。これにより移動度の異なる画素電流値は均一化され、移動度のばらつきを補正する事ができる。

【0057】

以下参考の為図10を参照して、上述した移動度補正の数値解析を行う。図10に示すように、トランジスタTr1及びTr4がオンした状態で、ドライブトランジスタTrdのソース電位を変数Vに取って解析を行う。ドライブトランジスタTrdのソース電位(S)をVとすると、ドライブトランジスタTrdを流れるドレイン電流Idsは以下の式3に示す通りである。

【数1】

【0058】

またドレイン電流Idsと容量C(=Cs+Coled)の関係により、以下の式4に示す様にIds=dQ/dt=CdV/dtが成り立つ。

【数2】

【0059】

式4に式3を代入して両辺積分する。ここで、ソース電圧V初期状態は−Vthであり、移動度ばらつき補正時間(T6‐T7)をtとする。この微分方程式を解くと、移動度補正時間tに対する画素電流が以下の数式5のように与えられる。

【数3】

【0060】

移動度の異なる画素において、式5を用いてt=0usと2.5us時の電流値のグラフを図11に示す。なおこのグラフの下部に合わせて式5も載せておく。t=0usの移動度補正をかけない状態に比べ、t=2.5usでは移動度ばらつきに対する補正が充分にかかっている事が分かる。移動度補正無しでは40%のばらつきがあったものが、移動度補正をかけると10%以下に抑えられている。移動度補正動作時は、常にV<VthELを満たしている必要がある。上述した第1実施形態の画素回路では移動度補正時に画素容量Csと発光素子ELの等価容量Coledを使用している。ColedはCsに対して大きいので合成容量Cも大きくなり、移動度補正時間マージンを稼ぐ事ができる。

【0061】

以上の動作を行うことで、映像信号電位サンプル方式の画素回路においても移動度ばらつきの補正を行う事ができる事が分かる。既に実用化されている液晶ディスプレイの駆動方式は基本的に映像信号電位をサンプリングする電圧駆動である。よって有機ELパネルにおいても電圧駆動にて移動度ばらつき補正が可能となる事で、従来液晶ディスプレイで用いていた外付けソースドライバや低温ポリシリコンTFTなどを用いたパネル内蔵型ソースドライバなどを利用する事が可能となり、低コストにて有機ELパネルモジュールを作成する事ができる。また第1実施形態の画素回路ではドライブトランジスタ以外のスイッチングトランジスタはNチャネル型とPチャネル型を混在して用いているが、各トランジスタの特性はNチャネルでもPチャネルでも構わない。

【0062】

図12は、本発明にかかる表示装置の第2実施形態を示すブロック図である。理解を容易にする為図5に示した第1実施形態と対応する部分には対応する参照番号を用いてある。本表示措置は、画素アレイ1とこれを囲む周辺の回路とで構成されている。周辺回路は、水平セレクタ3とライトスキャナ4とドライブスキャナ5と第一補正用スキャナ71と第二補正用スキャナ72とを含む。画素アレイ1はマトリクス状に配列した画素回路2で構成されている。図では理解を容易にする為1個の画素回路2のみを示してある。画素回路2は6個のトランジスタTr1,Trd,Tr3〜Tr6と、2個の容量素子Cs1,Cs2と1個の発光素子ELとで構成されている。トランジスタは全てNチャネル型である。本画素回路2の主要部となるドライブトランジスタTrdは、そのゲートGが各容量素子Cs1,Cs2の一端に接続されている。一方の容量素子Cs1は本画素回路2の出力側と入力側を結ぶ結合容量である。他方の容量素子Cs2は結合容量Cs1を介して映像信号が書き込まれる画素容量である。ドライブトランジスタTrdのソースSは画素容量Cs2の他端に接続すると共に、発光素子ELに接続している。発光素子ELはダイオード型のデバイスであり、そのアノードがドライブトランジスタTrdのソースSに接続する一方、カソードKが接地電位Vcathに接続されている。またドライブトランジスタTrdのソースSと所定の基準電位Vss2との間にスイッチングトランジスタTr3が介在している。このトランジスタTr3のゲートは走査線AZ2に接続している。ドライブトランジスタTrdのドレインはスイッチングトランジスタTr4を介して電源Vccに接続されている。スイッチングトランジスタTr4のゲートは走査線DSに接続している。加えてドライブトランジスタTrdのゲートGとドレインとの間にスイッチングトランジスタTr5が介在している。このトランジスタTr5のゲートは走査線AZ1に接続している。一方入力側のサンプリングトランジスタTr1は信号線SLと結合容量Cs1の他端との間に接続されている。サンプリングトランジスタTr1のゲートは走査線WSに接続されている。結合容量Cs1の他端と所定の基準電位Vss1との間にトランジスタTr6が介在している。このトランジスタTr6のゲートは走査線AZ1に接続している。

【0063】

図13は、図12に示した画素回路の動作説明に供するタイミングチャートである。時間軸Tに沿って制御信号WS,DS,AZ1,AZ2の波形を表すと共に、ドライブトランジスタTrdのゲート電位(G)及びソース電位(S)の変化も表してある。当該フィールドが開始するタイミングT1では、制御信号WS,AZ1,AZ2がローレベルで、制御信号DSのみがハイレベルである。したがって、タイミングT1ではスイッチングトランジスタTr4のみがオン状態にあり、残りのトランジスタTr1,Tr3,Tr5,Tr6はオフ状態にある。この時ドライブトランジスタTrdはオン状態にあるスイッチングトランジスタTr4を介して電源Vccに接続されているので、所定のドレイン電流Idsが発光素子ELに流れる為、発光状態となっている。

【0064】

タイミングT2になると制御信号AZ1とAZ2とがハイレベルとなり、スイッチングトランジスタTr5,Tr6がオンする。ドライブトランジスタTrdのゲートGはトランジスタTr5を通して電源Vcc側に接続するので、ゲート電位(G)は急激に上昇する。

【0065】

この後タイミングT3で制御信号DSがローレベルとなり、トランジスタTr4がオフする。ドライブトランジスタTrdに対する電源供給が遮断されるので、ドレイン電流Idsは減衰していく。これによりソース電位(S)及びゲート電位(G)は共に下降するが、丁度両者の電位差がVthとなったところで電流が流れなくなる。この時のVthが画素容量Cs2に保持される。画素容量Cs2に保持されたVthはドライブトランジスタTrdの閾電圧のキャンセルに用いられる。また、スイッチングトランジスタTr3はオンしており、ドライブトランジスタTr2のソースSはトランジスタTr3を介して基準電位Vss2に接続される。このVss2は発光素子ELの閾電圧よりも低く設定されており、発光素子ELは逆バイアス状態におかれる。

【0066】

この後タイミングT4になったとき制御信号AZ1がローレベルとなり、トランジスタTr5,Tr6がオフして、Cs2に書き込まれたVthが固定される。タイミングT2からT4までVth補正期間(T2‐T4)と呼ぶ。なおVth補正期間ではTr6がオンしている為、結合容量Cs1の他端は所定の基準電位Vss1に保持される。

【0067】

タイミングT5になると制御信号WS及びAZ2がハイレベルになり、サンプリングトランジスタTr1がオンする。この結果、ドライブトランジスタTrdのゲートGは結合容量Cs1及びオンしたサンプリングトランジスタTr1を介して信号線SLに接続される。この結果映像信号が結合容量Cs1を介してドライブトランジスタTrdのゲートGにカップリングされ、その電位が上昇する。図13のタイミングチャートでは映像信号のカップリング分とVthを合わせた電圧をVinで表してある。画素容量Cs2にこのVinが保持された事になる。この後タイミングT7で制御信号WSがローレベルに戻り、画素容量Cs2に書き込まれた電位が保持固定される。この様にして映像信号が結合容量Cs1を介して画素容量Cs2に書き込まれる期間をサンプリング期間T5‐T7と呼ぶ。このサンプリング期間T5‐T7は通常1水平期間(1H)に相当する。

【0068】

本実施形態では、サンプリング期間が終了するタイミングT7の前のタイミングT6で、制御信号DSがハイレベルになる一方制御信号AZ2がローレベルになる。この結果ドライブトランジスタTrdのソースSがVss2から切り離される一方ドレイン側からソースS側に向かって電流が流れる。一方サンプリングトランジスタTr1は引き続きオン状態なのでドライブトランジスタTrdのゲート電位(G)は映像信号側に保持されている。この様な状態でドライブトランジスタTrdに出力電流が流れるので、画素容量Cs2及び逆バイアス状態にある発光素子ELの等価容量を充電する事になる。これによりドライブトランジスタTrdのソース電位(S)はΔVだけ上昇し、その分だけCs2に保持されていた電圧Vinが減少する。換言すると、期間T6‐T7の間でソースS側の出力電流がゲートG側の入力電圧に負帰還される。この負帰還量がΔVで表される。この負帰還動作により、ドライブトランジスタTrdの移動度補正が行われる。

【0069】

この後タイミングT7で制御信号WSがローレベルとなり、映像信号の印加が解除されると、いわゆるブートストラップ動作が行われゲート電位(G)及びソース電位(S)は両者の差(Vin−ΔV)を維持したまま上昇する。ソース電位(S)の上昇に伴い発光素子ELの逆バイアス状態は解消されるので、出力電流Idsが発光素子ELに流れ込み、映像信号に応じた輝度で発光が行われる。この後タイミングT8で当該フィールド1fが終わると次のフィールドに進む。次のフィールドでも、Vth補正、信号書き込み、移動度補正の各動作を行う。

【0070】

図14は、図13に示した移動度補正期間T6‐T7における画素回路2の状態を表している。この画素回路2もスイッチングトランジスタTr3,Tr4,Tr5などで構成される補正手段を備えている。この補正手段は出力電流Idsのキャリア移動度μに対する依存性を打ち消す為、予め発光期間T6‐T8の前または先頭で画素容量Cs2に保持された入力電圧Vin(Vgs)を補正する。この補正手段は走査線WS及びDSから供給される制御信号WS,DSに応じてサンプリング期間T5‐T7の一部で動作し、映像信号Vsigがサンプリングされている状態でドライブトランジスタTrdから出力電流Idsを取り出し、これを画素容量Cs2に負帰還して入力電圧Vgsを補正する。加えてこの補正手段(Tr3,Tr4,Tr5)は、出力電流Idsの閾電圧Vthに対する依存性を打ち消す為に、予めサンプリング期間T5‐T7に先立つ期間T2‐T4でドライブトランジスタTrdの閾電圧Vthを検出し、且つ検出された閾電圧Vthを入力電圧Vgsに足し込む様にしてある。

【0071】

本実施形態においても、ドライブトランジスタTrdはNチャネル型トランジスタでドレインが電源Vcc側に接続する一方ソースSが発光素子EL側に接続している。この構成において本補正手段は、サンプリング期間T5‐T7の後部分に重なる発光期間T6‐T8の先頭部分(T6‐T7)でドライブトランジスタTrdから出力電流Idsを取り出して、画素容量Cs2側に負帰還する。その際本補正手段は、発光期間の先頭部分(T6‐T7)でドライブトランジスタTrdのソースS側から取り出した出力電流Idsが、発光素子ELの有する等価容量Coledに流れ込むようにしている。発光素子ELはアノード及びカソードを備えたダイオード型の発光素子からなり、アノード側がドライブトランジスタTrdのソースSに接続する一方カソード側がVcathに接地されている。本補正手段は前述したように予め発光素子ELのアノード/カソード間を逆バイアス状態にセットしておき、ドライブトランジスタTrdのソースS側から取り出した出力電流Idsが発光素子ELに流れ込む時、ダイオード型の発光素子ELを容量性素子Coledとして機能させている。

【0072】

図15は、本発明にかかる表示装置の第3実施形態を示すブロック図である。理解を容易にする為、図5に示した第1実施形態と対応する部分には対応する参照番号を付してある。本表示装置も中央の画素アレイ1とこれを囲む周辺回路とで構成されている。周辺回路は水平セレクタ3、ライトスキャナ4、ドライブスキャナ5、第一補正用スキャナ71、第二補正用スキャナ72を含んでいる。画素アレイ1はマトリクス状に配列された画素回路から構成されている。図では理解を容易にする為1個の画素回路2のみを拡大表示してある。

【0073】

画素回路2は5個のトランジスタTr1,Tr2,Tr4,Tr5,Trdと2個の容量素子Cs1,Cs2と1個の発光素子ELとで構成されている。第1実施形態及び第2実施形態と異なり、ドライブトランジスタTrdはPチャネル型である。残りのトランジスタTr1,Tr2,Tr4,Tr5は全てNチャネル型である。なお画素サイズや発光素子ELの特性にもよるが、一般的にドライブトランジスタはNチャネル型の方が移動度補正値の容量を大きく取る事ができ、移動度補正のマージンがある。

【0074】

ドライブトランジスタTrdのソースは電源Vccに接続している。ゲートは画素容量Cs1の一端に接続している。ドライブトランジスタTrdがPチャネル型の場合、ゲート電圧Vgsはソース側となる電源Vccを基準にして定義される。ドライブトランジスタTrdのドレインはスイッチングトランジスタTr4を介して発光素子ELに接続している。発光素子ELはダイオード型であり、アノードがスイッチングトランジスタTr4を介してドライブトランジスタTrdのドレインに接続する一方、カソードが接地されている。なおスイッチングトランジスタTr4のゲートは走査線DSに接続している。ドライブトランジスタTrdのゲートとドレインとの間にスイッチングトランジスタTr5が介在している。そのゲートは走査線AZ1に接続している。

【0075】

一方画素回路2の入力側となるサンプリングトランジスタTr1は信号線SLと画素容量Cs1の他端との間に接続されている。サンプリングトランジスタTr1のゲートは走査線WSに接続されている。画素容量Cs1の他端と電源Vccとの間に別の画素容量Cs2が接続している。また画素容量Cs1の他端と所定のオフセット電位Vofsとの間にスイッチングトランジスタTr2が接続している。このトランジスタTr2のゲートは走査線AZ2に接続している。

【0076】

図16は、図15に示した画素回路の各トランジスタとこれらに対応する制御信号との関係を明示した回路図である。合わせてドライブトランジスタTrdのゲートを記号Gで明示し、発光素子ELのアノードを記号Xで明示してある。各トランジスタTr1,Tr2,Tr4,Tr5のゲートに印加される制御信号を対応する走査線と同じ記号で表してある。

【0077】

図17は、図16に示した画素回路の動作説明に供するタイミングチャートである。時間軸Tに沿って制御信号WS,AZ1,AZ2,DSの波形を表すと共に、ドライブトランジスタTrdのゲート電位(G)と発光素子ELのアノード電位(X)の変化も表してある。

【0078】

当該フィールドに入る前のタイミングT0で、制御信号WS,AZ1,AZ2はローレベルにある一方、制御信号DSはハイレベルにある。したがってタイミングT0ではトランジスタTr4がオン状態にある一方、残りのトランジスタTr1,Tr2,Tr5はオフ状態にある。ドライブトランジスタTrdはオン状態のトランジスタTr4を介して発光素子ELに接続している。したがって発光素子ELにはゲート電圧Vgsに応じた出力電流が流れて発光している。なお、図17のタイミングチャートではゲート電圧Vgsは電源電位Vccとゲート電位(G)との間の差で表される。

【0079】

当該フィールドに入るタイミングT1で、制御信号AZ1及びAZ2がハイレベルになり、トランジスタTr2,Tr5がオンする。これにより画素容量Cs1の他端は所定のオフセット電位Vofsに固定される。またドライブトランジスタTrdのドレインとゲートが直結する。この為ゲート電位(G)はドレイン電位に引かれて急激に下降する一方、アノード電位(X)は発光素子EL内に生じた電圧降下で急激に上昇する。この動作でドライブトランジスタTrdは閾電圧検出の準備状態となる。

【0080】

続いてタイミングT2で制御信号DSがローレベルとなり、スイッチングトランジスタTr4がオフする。ここまでの期間T1‐T2はリセット期間もしくはオーバーラップ期間と呼ばれる。スイッチングトランジスタTr4がオフするとドライブトランジスタの電流路が遮断され、ゲート容量Cgs及び画素容量Cs1を充電していく。この結果ゲート電位(G)が上昇する。丁度電源電位Vccとゲート電位(G)の差がVthとなった所でドライブトランジスタTrdがカットオフする。カットオフした後のタイミングT3で制御信号AZ1,AZ2がローレベルに戻り、トランジスタTr2,Tr5がオフする。この結果画素容量Cs1に書き込まれた閾電圧Vthが保持される。この期間T2‐T3をVth補正期間もしくはVth検出期間と呼ぶ。なお発光素子ELに対する通電が遮断されるので、アノード電位(X)は接地電位GNDまで下がる。

【0081】

この後タイミングT4に進むと制御信号WSがハイレベルになりサンプリングトランジスタTr1がオンする。この結果映像信号Vsigがサンプリングされ、画素容量Cs2にVofs−Vsigが書き込まれる。この電圧Vofs−Vsigは画素容量Cs1を介してドライブトランジスタTrdのゲートG側にカップリングされる。その量はCs1(Vofs−Vsig)/(Cs1+Cgs)で与えられる。なおCgsはドライブトランジスタのソース/ゲート間容量である。このカップリング電圧分だけさらにゲート電位(G)が下がるので、結局ゲート電圧VgsはVth+Cs1(Vofs−Vsig)/(Cs1+Cgs)となる。この後1水平期間(1H)経過後のタイミングT7で制御信号WSはローレベルに戻り、サンプリングトランジスタTr1がオフする。この1Hに相当する期間T4‐T7で映像信号Vsigのサンプリングが行われる。

【0082】

このサンプリング期間T4‐T7の一部の期間T5‐T6で制御信号AZ1がハイレベルになり、トランジスタTr5が導通する。この結果電源Vcc側(ドライブトランジスタTrdのソース側)からドレイン側を通ってゲートG側にドレイン電流が流れ込む。このドレイン電流の流れ込みによりゲート電位(G)はΔV分だけ上昇する。ΔVはドライブトランジスタの移動度に比例している。ドライブトランジスタの移動度が大きいほどΔVは大きくなりゲート電位(G)が上昇するので、ゲート電圧Vgsはその分圧縮され出力電流が抑制される。この様にドライブトランジスタTrdのドレイン側からゲート側に向かって負のフォードバックをかける事で、移動度のばらつきを抑制可能である。サンプリング期間T4‐T7の中に設定された期間T5‐T6を移動度補正期間と呼ぶ。この移動度補正を行うことで、ドライブトランジスタTrdのゲート電圧Vgsは結局Vth+Cs1(Vofs−Vsig)/(Cs1+Cgs)−ΔVで与えられる。このゲート電圧Vgsには正味の信号成分に加え、ドライブトランジスタの閾電圧をキャンセルするための成分Vthと移動度を補正する為の成分ΔVが含まれている。

【0083】

タイミングT8になると制御信号DSがハイレベルとなりスイッチングトランジスタTr4がオンする。これによりドライブトランジスタTrdは発光素子ELに直結し、閾電圧Vth及び移動度μのばらつきが補正された出力電流が発光素子ELに流れる。この後タイミングT9で当該フィールドが終了すると、次のフィールドに移って再びVth補正、映像信号サンプリング、移動度補正の各動作が行われる。

【0084】

図18は、移動度補正期間T5‐T6における画素回路の状態を示す回路図である。前述したように移動度補正期間T5‐T6ではサンプリングトランジスタTr1とスイッチングトランジスタTr5がオンしている為、ドレイン電流Idsは画素容量Cs1に書き込まれる。これによりドライブトランジスタTrdのゲート電位(G)はΔV上昇する。この時に流れるドレイン電流Idsは以下の式6により表される。なお、式6ではカップリング係数Cs1/(Cs1+Cgs)を1として省略してある。実際Cgsに比べてCs1はかなり大きい。

【数4】

【0085】

前述したようにΔV=Ids・t/Cs1より、移動度の異なる画素ではΔVも異なる。移動度が大きい画素ほどΔVは大きくなり、Idsの補正量も大きくなる。これらの動作により、移動度ばらつきがある画素においても、Idsを均一化する事ができ、移動度ばらつき補正を行う事ができる。

【0086】

詳細な計算式は先の実施形態1と同様な解析によって、以下の式7に示すように与えられる。

【数5】

【0087】

上記式7の右辺は移動度μを2つ含む。係数部のμと左辺の分母に位置するμは互いにキャンセルしあうので、結果的にドレイン電流Idsから移動度μの影響を除く事ができる。式7の分母にあるμの効果は移動度補正期間T5‐T6の時間幅tによって調整できる。これにより本発明の移動度補正を最適化可能である。

【符号の説明】

【0088】

1・・・画素アレイ、2・・・画素回路、3・・・水平セレクタ、4・・・ライトスキャナ、5・・・ドライブスキャナ、7・・・補正用スキャナ、Tr1・・・サンプリングトランジスタ、Trd・・・ドライブトランジスタ、EL・・・発光素子、Cs・・・容量素子

【技術分野】

【0001】

本発明は、画素毎に配した発光素子を電流駆動する画素回路に関する。又この画素回路がマトリクス状(行列状)に配列された表示装置であって、特に各画素回路内に設けた絶縁ゲート型電界効果トランジスタによって、有機ELなどの発光素子に通電する電流量を制御する、いわゆるアクティブマトリクス型の表示装置に関する。

【背景技術】

【0002】

画像表示装置、例えば液晶ディスプレイなどでは、多数の液晶画素をマトリクス状に並べ、表示すべき画像情報に応じて画素毎に入射光の透過強度又は反射強度を制御することによって画像を表示する。これは、有機EL素子を画素に用いた有機ELディスプレイなどにおいても同様であるが、液晶画素と異なり有機EL素子は自発光素子である。その為、有機ELディスプレイは液晶ディスプレイに比べて画像の視認性が高く、バックライトが不要であり、応答速度が高いなどの利点を有する。又、各発光素子の輝度レベル(階調)はそれに流れる電流値によって制御可能であり、いわゆる電流制御型であるという点で液晶ディスプレイなどの電圧制御型とは大きく異なる。

【0003】

有機ELディスプレイにおいては、液晶ディスプレイと同様、その駆動方式として単純マトリクス方式とアクティブマトリクス方式とがある。前者は構造が単純であるものの、大型且つ高精細のディスプレイの実現が難しいなどの問題がある為、現在はアクティブマトリクス方式の開発が盛んに行なわれている。この方式は、各画素回路内部の発光素子に流れる電流を、画素回路内部に設けた能動素子(一般には薄膜トランジスタ、TFT)によって制御するものであり、以下の特許文献に記載がある。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2003−255856

【特許文献2】特開2003−271095

【特許文献3】特開2004−133240

【特許文献4】特開2004−029791

【特許文献5】特開2004−093682

【発明の概要】

【発明が解決しようとする課題】

【0005】

従来の画素回路は、制御信号を供給する行状の走査線と映像信号を供給する列状の信号線とが交差する部分に配され、少なくともサンプリングトランジスタと容量部とドライブトランジスタと発光素子とを含む。サンプリングトランジスタは、走査線から供給される制御信号に応じ導通して信号線から供給された映像信号をサンプリングする。容量部は、サンプリングされた映像信号に応じた入力電圧を保持する。ドライブトランジスタは、容量部に保持された入力電圧に応じて所定の発光期間に出力電流を供給する。尚一般に、出力電流はドライブトランジスタのチャネル領域のキャリア移動度及び閾電圧に対して依存性を有する。発光素子は、ドライブトランジスタから供給された出力電流により映像信号に応じた輝度で発光する。

【0006】

ドライブトランジスタは、容量部に保持された入力電圧をゲートに受けてソース/ドレイン間に出力電流を流し、発光素子に通電する。一般に発光素子の発光輝度は通電量に比例している。更にドライブトランジスタの出力電流供給量はゲート電圧すなわち容量部に書き込まれた入力電圧によって制御される。従来の画素回路は、ドライブトランジスタのゲートに印加される入力電圧を入力映像信号に応じて変化させることで、発光素子に供給する電流量を制御している。

【0007】

ここでドライブトランジスタの動作特性は以下の式1で表わされる。

Ids=(1/2)μ(W/L)Cox(Vgs−Vth)2・・・式1

このトランジスタ特性式1において、Idsはソース/ドレイン間に流れるドレイン電流を表わしており、画素回路では発光素子に供給される出力電流である。Vgsはソースを基準としてゲートに印加されるゲート電圧を表わしており、画素回路では上述した入力電圧である。Vthはトランジスタの閾電圧である。又μはトランジスタのチャネルを構成する半導体薄膜の移動度を表わしている。その他Wはチャネル幅を表わし、Lはチャネル長を表わし、Coxはゲート容量を表わしている。このトランジスタ特性式1から明らかな様に、薄膜トランジスタは飽和領域で動作する時、ゲート電圧Vgsが閾電圧Vthを超えて大きくなると、オン状態となってドレイン電流Idsが流れる。原理的に見ると上記のトランジスタ特性式1が示す様に、ゲート電圧Vgsが一定であれば常に同じ量のドレイン電流Idsが発光素子に供給される。従って、画面を構成する各画素に全て同一のレベルの映像信号を供給すれば、全画素が同一輝度で発光し、画面の一様性(ユニフォーミティ)が得られるはずである。

【0008】

しかしながら実際には、ポリシリコンなどの半導体薄膜で構成された薄膜トランジスタ(TFT)は、個々のデバイス特性にばらつきがある。特に、閾電圧Vthは一定ではなく、各画素毎にばらつきがある。前述のトランジスタ特性式1から明らかな様に、各ドライブトランジスタの閾電圧Vthがばらつくと、ゲート電圧Vgsが一定であっても、ドレイン電流Idsにばらつきが生じ、画素毎に輝度がばらついてしまう為、画面のユニフォーミティを損なう。従来からドライブトランジスタの閾電圧のばらつきをキャンセルする機能を組み込んだ画素回路が開発されており、例えば前記の特許文献3に開示がある。

【0009】

閾電圧のばらつきをキャンセルする機能を組み込んだ画素回路は、ある程度画面のユニフォーミティを改善することが可能である。しかしながら、ポリシリコン薄膜トランジスタの特性は、閾電圧ばかりでなく移動度μも素子毎にばらつきがある。前述のトランジスタ特性式1から明らかな様に、移動度μがばらつくと、ゲート電圧Vgsが一定であってもドレイン電流Idsにばらつきが出てしまう。この結果発光輝度が画素毎に変化する為、画面のユニフォーミティを損なうという課題がある。

【課題を解決するための手段】

【0010】

上述した従来の技術の課題に鑑み、本発明は移動度の影響をキャンセルし、以ってドライブトランジスタが供給するドレイン電流(出力電流)のばらつきを補償可能な画素回路及び表示装置とその駆動方法を提供することを目的とする。係る目的を達成する為に以下の手段を講じた。即ち本発明は、制御信号を供給する行状の走査線と映像信号を供給する列状の信号線とが交差する部分に配され、少なくともサンプリングトランジスタと、これに接続する容量部と、これに接続するドライブトランジスタと、これに接続する発光素子とを含み、前記サンプリングトランジスタは、所定のサンプリング期間に走査線から供給される制御信号に応じ導通して信号線から供給された映像信号を該容量部にサンプリングし、前記容量部は、該サンプリングされた映像信号に応じて該ドライブトランジスタのゲートとソース間に入力電圧を印加し、前記ドライブトランジスタは、所定の発光期間中該入力電圧に応じた出力電流を該発光素子に供給し、該出力電流は該ドライブトランジスタのチャネル領域のキャリア移動度に対して依存性を有し、前記発光素子は、該ドライブトランジスタから供給された出力電流により該映像信号に応じた輝度で発光する画素回路において、該出力電流のキャリア移動度に対する依存性を打ち消すために、あらかじめ該発光期間の前又は先頭で該容量部に保持された該入力電圧を補正する補正手段を備えており、前記補正手段は走査線から供給される制御信号に応じて該サンプリング期間の一部で動作し、該映像信号がサンプリングされている状態で該ドライブトランジスタから出力電流を取り出し、これを該容量部に負帰還して該入力電圧を補正することを特徴とする。

【0011】

好ましくは、前記ドライブトランジスタは、その出力電流がチャネル領域のキャリア移動度に加え閾電圧に対しても依存性を有し、前記補正手段は、該出力電流の閾電圧に対する依存性を打ち消すために、あらかじめサンプリング期間に先立って該ドライブトランジスタの閾電圧を検出し、且つ該検出された閾電圧を該入力電圧に足し込む様にしたことを特徴とする。一態様では、前記ドライブトランジスタは、Nチャネル型トランジスタでドレインが電源側に接続する一方ソースが発光素子側に接続し、前記補正手段は、該サンプリング期間の後部分に重なる該発光期間の先頭部分で該ドライブトランジスタから該出力電流を取り出して、該容量部側に負帰還する。この場合、前記補正手段は、該発光期間の先頭部分で該ドライブトランジスタのソース側から取り出した該出力電流が、該発光素子の有する容量に流れ込む様にする。更に、前記発光素子はアノード及びカソードを備えたダイオード型の発光素子からなり、アノード側が該ドライブトランジスタのソースに接続する一方カソード側が接地されており、前記補正手段は、あらかじめ該発光素子のアノード/カソード間を逆バイアス状態にセットしておき、該ドライブトランジスタのソース側から取り出した該出力電流が該発光素子に流れ込むとき、該ダイオード型の発光素子が容量性素子として機能するように制御する。他の態様では、前記ドライブトランジスタは、Pチャネル型トランジスタでソースが電源側に接続する一方ドレインが発光素子側に接続し、前記補正手段は、該発光期間よりも先行する該サンプリング期間の一部で、該ドライブトランジスタから該出力電流を取り出して該容量部側に負帰還する。好ましくは、前記補正手段は、該サンプリング期間内で該ドライブトランジスタから出力電流を取り出す時間幅を調整可能であり、これにより該容量部に対する出力電流の負帰還量を最適化する。

【0012】

又本発明は、画素アレイ部とスキャナ部と信号部とを含み、前記画素アレイ部は、行状に配された走査線と列状に配された信号線と両者が交差する部分に配された行列状の画素とからなり、前記信号部は、該信号線に映像信号を供給し、前記スキャナ部は、該走査線に制御信号を供給して順次行ごとに画素を走査し、各画素は、少なくともサンプリングトランジスタと、これに接続する容量部と、これに接続するドライブトランジスタと、これに接続する発光素子とを含み、前記サンプリングトランジスタは、所定のサンプリング期間に走査線から供給される制御信号に応じ導通して信号線から供給された映像信号を該容量部にサンプリングし、前記容量部は、該サンプリングされた映像信号に応じて該ドライブトランジスタのゲートとソース間に入力電圧を印加し、前記ドライブトランジスタは、所定の発光期間中該入力電圧に応じた出力電流を該発光素子に供給し、該出力電流は該ドライブトランジスタのチャネル領域のキャリア移動度に対して依存性を有し、前記発光素子は、該ドライブトランジスタから供給された出力電流により該映像信号に応じた輝度で発光する表示装置において、各画素は、該ドライブトランジスタの出力電流のキャリア移動度に対する依存性を打ち消すために、あらかじめ該発光期間の前又は先頭で該容量部に保持された該入力電圧を補正する補正手段を備えており、前記補正手段は走査線から供給される制御信号に応じて該サンプリング期間の一部で動作し、該映像信号がサンプリングされている状態で該ドライブトランジスタから出力電流を取り出し、これを該容量部に負帰還して該入力電圧を補正することを特徴とする。

【0013】

好ましくは、前記ドライブトランジスタは、その出力電流がチャネル領域のキャリア移動度に加え閾電圧に対しても依存性を有し、前記補正手段は、該出力電流の閾電圧に対する依存性を打ち消すために、あらかじめサンプリング期間に先立って該ドライブトランジスタの閾電圧を検出し、且つ該検出された閾電圧を該入力電圧に足し込む様にしたことを特徴とする。一態様では、前記ドライブトランジスタは、Nチャネル型トランジスタでドレインが電源側に接続する一方ソースが発光素子側に接続し、前記補正手段は、該サンプリング期間の後部分に重なる該発光期間の先頭部分で該ドライブトランジスタから該出力電流を取り出して、該容量部側に負帰還する。この場合、前記補正手段は、該発光期間の先頭部分で該ドライブトランジスタのソース側から取り出した該出力電流が、該発光素子の有する容量に流れ込む様にする。更に、前記発光素子はアノード及びカソードを備えたダイオード型の発光素子からなり、アノード側が該ドライブトランジスタのソースに接続する一方カソード側が接地されており、前記補正手段は、あらかじめ該発光素子のアノード/カソード間を逆バイアス状態にセットしておき、該ドライブトランジスタのソース側から取り出した該出力電流が該発光素子に流れ込むとき、該ダイオード型の発光素子が容量性素子として機能するように制御する。他の態様では、前記ドライブトランジスタは、Pチャネル型トランジスタでソースが電源側に接続する一方ドレインが発光素子側に接続し、前記補正手段は、該発光期間よりも先行する該サンプリング期間の一部で、該ドライブトランジスタから該出力電流を取り出して該容量部側に負帰還する。好ましくは、前記補正手段は、該サンプリング期間内で該ドライブトランジスタから出力電流を取り出す時間幅を調整可能であり、これにより該容量部に対する出力電流の負帰還量を最適化する。

【0014】

更に本発明は、画素アレイ部とスキャナ部と信号部とを含み、前記画素アレイ部は行状に配された走査線と列状に配された信号線と両者が交差する部分に配された行列状の画素とからなり、前記信号部は該信号線に映像信号を供給し、前記スキャナ部は該走査線に制御信号を供給して順次行ごとに画素を走査し、各画素は少なくともサンプリングトランジスタと、これに接続する容量部と、これに接続するドライブトランジスタと、これに接続する発光素子とを含む表示装置の駆動方法であって、前記スキャナ部は所定のサンプリング期間に走査線から該サンプリングトランジスタに制御信号を供給し導通させて、信号線から供給された映像信号を該容量部にサンプリングし、前記容量部は、該サンプリングされた映像信号に応じて該ドライブトランジスタのゲートとソース間に入力電圧を印加し、前記ドライブトランジスタは、所定の発光期間中該入力電圧に応じた出力電流を該発光素子に供給し、該出力電流は該ドライブトランジスタのチャネル領域のキャリア移動度に対して依存性を有し、前記発光素子は、該ドライブトランジスタから供給された出力電流により該映像信号に応じた輝度で発光し、更に前記スキャナ部は、該該ドライブトランジスタの出力電流のキャリア移動度に対する依存性を打ち消すために、あらかじめ該発光期間の前又は先頭で該容量部に保持された該入力電圧を補正する補正手順を該画素に行わせ、前記補正手順は、該サンプリング期間内で該映像信号がサンプリングされている間に該ドライブトランジスタから出力電流を取り出し、これを該容量部に負帰還して該入力電圧を補正する。

【発明の効果】

【0015】

本発明によれば、ドライブトランジスタの出力電流のキャリア移動度に対する依存性を打ち消す為、画素回路は発光期間の前または先頭でドライブトランジスタに対する入力電圧(ゲート電圧)を補正する補正手段を備えている。この補正手段はサンプリング期間の一部で動作し、映像信号の電位(信号電位)がサンプリングされている状態でドライブトランジスタから出力電流(ドレイン電流)を取り出し、これを容量部に負帰還して入力電圧(ゲート電圧)を補正している。前述のトランジスタ特性式1から明らかな様に、出力電流(ドレイン電流)は移動度に比例している。したがって、ある画素のドライブトランジスタの移動度が高いと、出力電流は相対的に大きくなる。これを容量部に負帰還して入力電圧(ゲート電圧)を補正する。移動度が大きいと結果的に負帰還量が大きくなるので、入力電圧(ゲート電圧)はその分大きく下方修正される。ゲート電圧が下がるので、結果的にドレイン電流は抑制される事になる。一方、別の画素のドライブトランジスタの移動度が相対的に小さい場合、ドレイン電流も少なくなる。したがって容量部に対する負帰還量も小さいので、ゲート電圧の下方修正分が小さい。結果的に、ドライブトランジスタの移動度が小さいと出力電流はさほど低く補正されない。この様に、本発明の補正手段は、移動度のばらつきをキャンセルする様に、入力電圧をフィードバック補正するので、画面のユニフォーミティが改善される。特に、信号電位をサンプリングしている状態で移動度補正をかけている。映像信号電位は黒レベルから白レベルまで振幅が変化するが、どのレベルにおいても適切に移動度補正を行う事が可能である。また、入力電圧にかける負帰還量は、出力電流の取り出し時間に依存している。取り出し時間を長く取るほど、負帰還量が大きくなる。本発明では、サンプリング期間中における出力電流の取り出し時間を可変調整して、負帰還量の最適化を測る事ができる。なお本発明では、映像信号電位をサンプリングして発光素子を電流駆動している。映像信号電位をサンプリングする点では、従来の液晶ディスプレイと同じである。したがって、アクティブマトリクス型の液晶ディスプレイで従来から広く用いられている電圧シグナルドライバを本発明の信号部に用いる事ができる。さらには、従来のポリシリコントランジスタを集積形成したアクティブマトリクス型の液晶パネルと同じ様に、本発明の表示装置でも、周辺のスキャナ部や信号部を画素アレイ部と一体的に形成した周辺回路内蔵型のパネルにまとめる事も可能である。

【図面の簡単な説明】

【0016】

【図1】表示装置の参考例を示すブロック図である。

【図2】図1に示した表示装置に含まれる画素回路の構成を示す回路図である。

【図3】図2に示した画素回路の動作説明に供する参考タイミングチャートである。

【図4】ドライブトランジスタの入力電圧/出力電流特性を示すグラフである。

【図5】本発明にかかる表示装置の第1実施形態を示すブロック図である。

【図6】図5に示した表示装置に含まれる画素回路を取り出した模式図である。

【図7】図6に示した画素回路の動作説明に供するタイミングチャートである。

【図8】図6に示した画素回路の動作説明に供する模式図である。

【図9】同じく動作説明に供するグラフである。

【図10】同じく動作説明に供する模式図である。

【図11】図6に示した画素回路に含まれるドライブトランジスタの動作特性を示すグラフである。

【図12】本発明にかかる表示装置の第2実施形態を示すブロック図である。

【図13】図12に示した表示装置に含まれる画素回路の動作説明に供するタイミングチャートである。

【図14】同じく動作説明に供する画素回路図である。

【図15】本発明にかかる表示装置の第3実施形態を示すブロック図である。

【図16】図15に示した表示装置に含まれる画素回路の動作説明に供する模式図である。

【図17】同じく動作説明に供するタイミングチャートである。

【図18】同じく動作説明に供する模式図である。

【発明を実施するための形態】

【0017】

以下図面を参照して本発明の実施の形態を詳細に説明する。まず最初に本発明の背景を明らかにする為、図1を参照してVth補正機能を備えたアクティブマトリクス表示装置の参考例を説明する。図示する様に、アクティブマトリクス表示装置は主要部となる画素アレイ1と周辺の回路部とで構成されている。周辺の回路部は水平セレクタ3、ライトスキャナ4、ドライブスキャナ5、補正用スキャナ7などを含んでいる。画素アレイ1は行状の走査線WSと列状の信号線SLと両者の交差する部分にマトリクス状に配列した画素R,G,Bとで構成されている。カラー表示を可能とする為、RGBの三原色画素を用意しているが、本発明はこれに限られるものではない。各画素R,G,Bは夫々画素回路2で構成されている。信号線SLは水平セレクタ3によって駆動される。水平セレクタ3は信号部を構成し、信号線SLに映像信号を供給する。走査線WSはライトスキャナ4によって走査される。尚、走査線WSと平行に別の走査線DS及びAZも配線されている。走査線DSはドライブスキャナ5によって走査される。走査線AZは補正用スキャナ7によって走査される。ライトスキャナ4、ドライブスキャナ5及び補正用スキャナ7はスキャナ部を構成しており、1水平期間毎画素の行を順次走査する。各画素回路2は走査線WSによって選択された時信号線SLから映像信号をサンプリングする。更に走査線DSによって選択された時、サンプリングされた映像信号に応じて画素回路2内に含まれている発光素子を駆動する。加えて画素回路2は走査線AZによって走査された時、あらかじめ決められた補正動作を行なう。

【0018】

上述した画素アレイ1は通常ガラスなどの絶縁基板上に形成されており、フラットパネルとなっている。各画素回路2はアモルファスシリコン薄膜トランジスタ(TFT)又は低温ポリシリコンTFTで形成されている。アモルファスシリコンTFTの場合、スキャナ部はパネルとは別のTABなどで構成され、フレキシブルケーブルにてフラットパネルに接続される。低温ポリシリコンTFTの場合、信号部及びスキャナ部も同じ低温ポリシリコンTFTで形成できるので、フラットパネル上に画素アレイ部と信号部とスキャナ部を一体的に形成できる。

【0019】

図2は、図1に示した画素アレイに含まれる画素回路の構成を示す回路図である。図示する様に、画素回路2は5個の薄膜トランジスタTr1〜Tr4,Trdと2個の容量素子Cs1,Cs2と1個の発光素子ELとで構成されている。トランジスタTr1〜Tr4,Trdは全てPチャネル型のポリシリコンTFTである。但し本発明はこれに限られるものではなく、Nチャネル型のポリシリコンTFTを混在させてもよい。あるいは、Nチャネル型のアモルファスシリコンTFTで画素回路を構成してもよい。2個の容量素子Cs1とCs2は両者合わせて画素回路2の容量部を構成している。発光素子ELは例えばアノード及びカソードを備えたダイオード型の有機EL素子からなる。但し本発明はこれに限られるものではなく、発光素子は一般的に電流駆動で発光する全てのデバイスを含む。

【0020】

画素回路2の中心となるドライブトランジスタTrdはゲート(G)がG点に接続され、ソース(S)がS点に接続され、ドレイン(D)がD点に接続されている。発光素子ELはアノードがD点に接続され、カソードが接地されている。スイッチングトランジスタTr4は電源電位VccとS点との間に接続されており、発光素子ELのオン/オフを制御する。トランジスタTr4のゲートは走査線DSに接続されている。

【0021】

一方サンプリングトランジスタTr1は信号線SLとA点との間に接続されている。サンプリングトランジスタTr1のゲートは走査線WSに接続している。A点とS点との間に検出トランジスタTr5が接続されている。そのゲートは走査線AZに接続している。又スイッチングトランジスタTr3はG点と所定のオフセット電位Vofsとの間に接続されている。そのゲートは走査線AZに接続されている。尚、検出トランジスタTr5とスイッチングトランジスタTr3はVthキャンセル用の補正手段を構成している。一方の容量素子Cs1はA点とG点との間に接続され、他方の容量素子Cs2は電源電位VccとA点との間に接続されている。

【0022】

ドライブトランジスタTrdはソース/ゲート間に印加されるゲート電圧Vgsに応じてソース/ドレイン間にドレイン電流Idsを流し、これで発光素子ELを駆動する。本明細書ではゲート電圧Vgsを入力電圧とし、ドレイン電流Idsを出力電流と定義している。信号線SLから供給される映像信号Vsigに応じてゲート電圧Vgsを設定し、これによりドレイン電流Idsを流すことで、映像信号の階調に従って発光素子ELの発光輝度を制御できる。

【0023】

ドライブトランジスタTrdの閾電圧Vthは画素毎に変動する。これをキャンセルする為あらかじめドライブトランジスタTrdの閾電圧Vthを検出し、容量素子Cs1に保持しておく。この後サンプリングトランジスタTr1をオンして容量素子Cs2に信号電位Vsigを書き込む。この様にして設定されたゲート電圧Vgsにより、ドライブトランジスタTrdを駆動する。

【0024】

図3は、図2に示した画素回路の動作説明に供するタイミングチャートである。時間軸Tに沿って各走査線WS,AZ及びDSに印加される制御信号の波形を表わしてある。表記を簡略化する為、以下本明細書では制御信号も対応する走査線の符号と同じ符号で表わす。トランジスタは全てPチャネル型なので、走査線がハイレベルの時オフし、ローレベルの時オンする。そこで表記を簡略化する為、本参考例では制御信号がハイレベルからローレベルに立ち下がる場合を「オン」と表わし、ローレベルからハイレベルに立ち上がる場合を「オフ」と呼ぶ。各制御信号WS,AZ,DSの波形とともに、A点及びG点の電位変化も表わしてある。なおNチャネル型の場合は、逆に制御信号がハイレベルからローレベルに立ち下がる場合を「オフ」と表わし、ローレベルからハイレベルに立ち上がる場合を「オン」と呼ぶ。

【0025】

図示のタイミングチャートではタイミングT1〜T7までを1フィールド(1f)としてある。1フィールドの間に画素アレイの各行が1回順次走査される。タイミングチャートは、1行分の画素に印加される各制御信号WS,AZ,DSの波形を表わしてある。

【0026】

当該フィールドが始まる前のタイミングT0で、制御信号WS及びAZはオフであるのに対し、制御信号DSがオンしている。従ってサンプリングトランジスタTr1、検出トランジスタTr5及びスイッチングトランジスタTr3がオフ状態であるのに対し、スイッチングトランジスタTr4のみがオン状態にある。この状態で、A点電位は信号電位Vsigにあり、G点電位はVsigからVthだけ下がった電位にある。この時S点はトランジスタTr4がオンしているのでVccとなっている。従ってトランジスタTrdのソースとゲートとの間にはVthを超える十分な電圧が印加されており、出力電流Idsが発光素子ELに供給されている。従ってタイミングT0では発光素子ELは発光状態にある。

【0027】

この後当該フィールドに入りタイミングT1で制御信号AZがオンし、トランジスタTr5及びTr3が導通する。この結果A点とS点が直接つながるので、A点電位は電源電位Vccに急激に立ち上がる。一方トランジスタTr3がオンする為、G点電位は所定のオフセット電位Vofsまで急激に立ち下がる。

【0028】

この直後タイミングT2で制御信号DSがオフになり、スイッチングトランジスタTr4が非導通状態となる。これによりS点が電源電位Vccから切り離され、非発光状態に変わる。タイミングT1からタイミングT2までの期間T1−T2で、A点電位がVccとなりG点電位がVofsとなって各容量素子Cs1,Cs2の電位がリセットされる。このリセット動作は、次に続く検出動作を安定化する為の準備であって、期間T1−T2をリセット期間と呼ぶ。

【0029】

タイミングT2で制御信号DSがオフするとS点がVccから切り離されるので、電源からの給電が遮断される一方容量素子Cs1の放電が始まり過徒電流がトランジスタTr5を通して流れ、A点電位がVccから低下していく。G点電位に対してA点電位がVthまで低下した時、過徒電流が流れなくなる。この結果A点とG点の電位差がVthとなり、これが容量素子Cs1に保持される。

【0030】

タイミングT3で制御信号AZがオフし、トランジスタTr5及びTr3がオフして、容量素子Cs1のG点側がVofsから切り離されるとともに、A点側がS点から切り離される。タイミングT2〜T3までの期間でVthを検出し且つCs1に保持するので、期間T2−T3を特に検出期間と呼ぶ。この検出期間T2−T3はドライブトランジスタに流れる過徒電流が0になる様十分な時間幅を取ってある。

【0031】

以上説明した様に、リセット期間T1−T2におけるリセット動作と検出期間T2−T3における検出動作とで閾電圧Vthの補正動作が行なわれる。そこでリセット期間と検出期間を合わせた期間T1−T3をVth補正期間と呼ぶ。場合によっては、期間T2−T3をVth補正期間と呼ぶこともある。図3のタイミングチャートから明らかな様に、Vth補正期間T1−T3は制御信号AZによって規定される。一方、Vth補正期間T1−T3内でリセット期間T1−T2と検出期間T2−T3を区分するのが制御信号DSである。制御信号DSは基本的にスイッチングトランジスタTr4のオン/オフを制御するパルスであり、従って非発光期間と発光期間を規定している。

【0032】

Vth補正期間T1−T3が経過した後、タイミングT4で制御信号WSがオンし、サンプリングトランジスタTr1が導通する。この結果、信号線SLから供給された映像信号Vsigが容量素子Cs2にサンプリングされる。これによりA点電位はVthから信号電位Vsigに上昇する。この上昇に連動してG点電位も差分Vthを維持したまま上昇する。タイミングチャートから明らかな様に、サンプリング後でもA点電位とG点電位の電位差はVthに維持されている。この後1水平期間が経過するタイミングT5で制御信号WSはオフし、サンプリングトランジスタTr1が非導通状態となる。VsigをサンプリングしてCs2に保持するサンプリング動作は期間T4−T5で行なわれる為、これをサンプリング期間と呼ぶ。サンプリング期間T4−T5は1水平期間1Hに等しい。

【0033】

この後タイミングT6で制御信号DSが再びオンし、スイッチングトランジスタTr4が導通する。この結果ドライブトランジスタTrdはS点電位とG点電位との差Vgsに応じてドレイン電流Idsを発光素子ELに供給する。発光素子ELはこれによりVgsに応じた輝度で発光する。

【0034】

この後タイミングT7に至り当該フィールドが終了するとともに、次のフィールドに移行する。次のフィールドでは最初にリセット期間に入る。

【0035】

図3のタイミングチャートに基づいて、サンプリング期間T4−T5及びその後の発光期間における入力電圧Vgsを求める。入力電圧VgsはS点を基準にしたG点の電位である。サンプリング期間T4−T5の後の発光期間ではトランジスタTr4がオンしている為、S点電位は電源に接続されVccとなっている。一方A点電位は前述した様にVccよりもVsigだけ低い。更にG点電位はA点電位からVthだけ低い。従ってS点電位を基準にしたG点電位を表わすVgsはVcc−(Vsig−Vth)となる。前述のトランジスタ特性式1のVgsにここで求めたVcc−(Vsig−Vth)を代入すると、以下の式が得られる。

Ids=(1/2)μ(W/L)Cox(Vcc−Vsig)2

上記特性式では先の基本特性式1に含まれていたVthの項がキャンセルされ、Vcc−Vsigで置き換えられている。従って図2に示した画素回路2は、ドライブトランジスタTrdのVthに依存することなく、Vsigの値に応じた出力電流Idsを発光素子ELに供給することができる。従ってドライブトランジスタTrdのVthが画素毎にばらついていても、画素アレイとしてはそのばらつきを取り除いた出力電流を各画素の発光素子ELに供給することができる。

【0036】

図4は、上記特性式をグラフ化したものであり、縦軸に出力電流Idsを取り、横軸に入力電圧Vcc−Vsigを取ってある。合わせてグラフの傍に上記特性式を再掲してある。上記特性式から明らかな様に、ドライブトランジスタのVthの項は消えている。しかしながら移動度μが残されている。この移動度μはVthと同じくデバイス依存性があり、各画素毎にばらついている。従って、Vthをキャンセルしたのみでは出力電流Idsのばらつきは完全に抑えることはできない。グラフではμの大きいトランジスタ特性を実線で表わし、μの小さなトランジスタ特性を点線で表わしている。グラフから明らかな様に、特性式の係数μが大きくなる程、特性カーブは急峻になっている。従って入力電圧Vcc−Vsig=V0で一定であっても、移動度μのばらつきが画素間で生じる為、出力電流Idsはμに依存して変動し、画素間で輝度のばらつきが生じてしまう。特にVcc−Vsigがグレーから白表示の階調にある時移動度μに依存する輝度ばらつきが顕著となり、表示ムラが生じて解決すべき課題である。

【0037】

図5は、本発明にかかる表示装置の第1実施形態を示す回路図である。図示する様に、アクティブマトリクス表示装置は主要部となる画素アレイ1と周辺の回路部とで構成されている。周辺の回路部は水平セレクタ3、ライトスキャナ4、ドライブスキャナ5、第一補正用スキャナ71、第二補正用スキャナ72などを含んでいる。画素アレイ1は行状の走査線WSと列状の信号線SLと両者の交差する部分にマトリクス状に配列した画素回路2とで構成されている。図では理解を容易にする為、1個の画素回路2のみを拡大表示してある。信号線SLは水平セレクタ3によって駆動される。水平セレクタ3は信号部を構成し、信号線SLに映像信号を供給する。走査線WSはライトスキャナ4によって走査される。なお、走査線WSと平行に別の走査線DS,AZ1及びAZ2も配線されている。走査線DSはドライブスキャナ5によって走査される。走査線AZ1は第一補正用スキャナ71によって走査される。走査線AZ2は第二補正用スキャナ72によって走査される。ライトスキャナ4、ドライブスキャナ5、第一補正用スキャナ71及び第二補正用スキャナ72はスキャナ部を構成しており、1水平期間ごと画素の行を順次走査する。各画素回路2は走査線WSによって選択されたとき信号線SLから映像信号をサンプリングする。さらに走査線DSによって選択されたとき、サンプリングされた映像信号に応じて画素回路2内に含まれている発光素子ELを駆動する。加えて画素回路2は走査線AZ1,AZ2によって走査された時、予め決められた補正動作を行う。

【0038】

画素回路2は、5個の薄膜トランジスタTr1〜Tr4及びTrdと1個の容量素子(画素容量)Csと1個の発光素子ELとで構成されている。トランジスタTr1〜Tr3とTrdはNチャネル型のポリシリコンTFTである。トランジスタTr4のみPチャネル型のポリシリコンTFTである。1個の容量素子Csは本画素回路2の容量部を構成している。発光素子ELは例えばアノード及びカソードを備えたダイオード型の有機EL素子である。但し本発明はこれに限られるものではなく、発光素子は一般的に電流駆動で発光する全てのデバイスを含む。

【0039】

画素回路2の中心となるドライブトランジスタTrdはそのゲートGが画素容量Csの一端に接続され、そのソースSが同じく画素容量Csの他端に接続されている。またドライブトランジスタTrdのゲートGはスイッチングトランジスタTr2を介して別の基準電位Vss1に接続されている。ドライブトランジスタTrdのドレインはスイッチングトランジスタTr4を介して電源Vccに接続されている。このスイッチングトランジスタTr2のゲートは走査線AZ1に接続されている。スイッチングトランジスタTr4のゲートは走査線DSに接続している。発光素子ELのアノードはドライブトランジスタTrdのソースSに接続し、カソードは接地されている。この接地電位はVcathで表される場合がある。また、ドライブトランジスタTrdのソースSと所定の基準電位Vss2との間にスイッチングトランジスタTr3が介在している。このトランジスタTr3のゲートは走査線AZ2に接続している。一方サンプリングトランジスタTr1は信号線SLとドライブトランジスタTrdのゲートGとの間に接続されている。サンプリングトランジスタTr1のゲートは走査線WSに接続している。

【0040】

かかる構成において、サンプリングトランジスタTr1は、所定のサンプリング期間に走査線WSから供給される制御信号WSに応じ導通して信号線SLから供給された映像信号Vsigを容量部Csにサンプリングする。容量部Csは、サンプリングされた映像信号Vsigに応じてドライブトランジスタのゲートGとソースS間に入力電圧Vgsを印加する。ドライブトランジスタTrdは、所定の発光期間中入力電圧Vgsに応じた出力電流Idsを発光素子ELに供給する。なおこの出力電流(ドレイン電流)IdsはドライブトランジスタTrdのチャネル領域のキャリア移動度μ及び閾電圧Vthに対して依存性を有する。発光素子ELは、ドライブトランジスタTrdから供給された出力電流Idsにより映像信号Vsigに応じた輝度で発光する。

【0041】

本発明の特徴事項として、画素回路2はスイッチングトランジスタTr2〜Tr4で構成される補正手段を備えており、出力電流Idsのキャリア移動度μに対する依存性を打ち消す為に、予め発光期間の先頭で容量部Csに保持された入力電圧Vgsを補正する。具体的には、この補正手段(Tr2〜Tr4)は、走査線WS及びDSから供給される制御信号WS,DSに応じてサンプリング期間の一部で動作し、映像信号Vsigがサンプリングされている状態でドライブトランジスタTrdから出力電流Idsを取り出し、これを容量部Csに負帰還して入力電圧Vgsを補正する。さらにこの補正手段(Tr2〜Tr4)は、出力電流Idsの閾電圧Vthに対する依存性を打ち消すために、予めサンプリング期間に先立ってドライブトランジスタTrdの閾電圧Vthを検出し、且つ検出された閾電圧Vthを入力電圧Vgsに足し込む様にしている。

【0042】

本実施形態の場合、ドライブトランジスタTrdはNチャネル型トランジスタでドレインが電源Vcc側に接続する一方、ソースSが発光素子EL側に接続している。この場合、前述した補正手段は、サンプリング期間の後部分に重なる発光期間の先頭部分でドライブトランジスタTrdから出力電流Idsを取り出して、容量部Cs側に負帰還する。その際本補正手段は、発光期間の先頭部分でドライブトランジスタTrdのソースS側から取り出した出力電流Idsが、発光素子ELの有する容量に流れ込むようにしている。具体的には、発光素子ELはアノード及びカソードを備えたダイオード型の発光素子からなり、アノード側がドライブトランジスタTrdのソースSに接続する一方カソード側が接地されている。この構成で、本補正手段(Tr2〜Tr4)は、予め発光素子ELのアノード/カソード間を逆バイアス状態にセットしておき、ドライブトランジスタTrdのソースS側から取り出した出力電流Idsが発光素子ELに流れ込む時、このダイオード型の発光素子ELを容量性素子として機能させている。なお本補正手段は、サンプリング期間内でドライブトランジスタTrdから出力電流Idsを取り出す時間幅tを調整可能であり、これにより容量部Csに対する出力電流Idsの負帰還量を最適化している。

【0043】

図6は、図5に示した表示装置から画素回路の部分を取り出した模式図である。理解を容易にする為、サンプリングトランジスタTr1によってサンプリングされる映像信号Vsigや、ドライブトランジスタTrdの入力電圧Vgs及び出力電流Ids、さらには発光素子ELが有する容量成分Coledなどを書き加えてある。以下図6に基づいて、本画素回路2の基本的な動作を説明する。

【0044】

図7は、図6に示した画素回路のタイミングチャートである。図7を参照して、図6に示した画素回路の動作をより具体的且つ詳細に説明する。図7は、時間軸Tに沿って各走査線WS,AZ1,AZ2及びDSに印加される制御信号の波形を表してある。表記を簡略化する為、制御信号も対応する走査線の符号と同じ符号で表してある。トランジスタTr1,Tr2,Tr3はNチャネル型なので、走査線WS,AZ1,AZ2がそれぞれハイレベルの時オンし、ローレベルの時オフする。一方トランジスタTr4はPチャネル型なので、走査線DSがハイレベルの時オフし、ローレベルの時オンする。なおこのタイミングチャートは、各制御信号WS,AZ1,AZ2,DSの波形と共に、ドライブトランジスタTrdのゲートGの電位変化及びソースSの電位変化も表してある。

【0045】

図7のタイミングチャートではタイミングT1〜T8までを1フィールド(1f)としてある。1フィールドの間に画素アレイの各行が一回順次走査される。タイミングチャートは、1行分の画素に印加される各制御信号WS,AZ1,AZ2,DSの波形を表してある。

【0046】

当該フィールドが始まる前のタイミングT0で、全ての制御線号WS,AZ1,AZ2,DSがローレベルにある。したがってNチャネル型のトランジスタTr1,Tr2,Tr3はオフ状態にある一方、Pチャネル型のトランジスタTr4のみオン状態である。したがってドライブトランジスタTrdはオン状態のトランジスタTr4を介して電源Vccに接続しているので、所定の入力電圧Vgsに応じて出力電流Idsを発光素子ELに供給している。したがってタイミングT0で発光素子ELは発光している。この時ドライブトランジスタTrdに印加される入力電圧Vgsは、ゲート電位(G)とソース電位(S)の差で表される。

【0047】

当該フィールドが始まるタイミングT1で、制御信号DSがローレベルからハイレベルに切り替わる。これによりトランジスタTr4がオフし、ドライブトランジスタTrdは電源Vccから切り離されるので、発光が停止し非発光期間に入る。したがってタイミングT1に入ると、全てのトランジスタTr1〜Tr4がオフ状態になる。

【0048】

続いてタイミングT2に進むと、制御信号AZ1及びAZ2がハイレベルになるので、スイッチングトランジスタTr2及びTr3がオンする。この結果、ドライブトランジスタTrdのゲートGが基準電位Vss1に接続し、ソースSが基準電位Vss2に接続される。ここでVss1−Vss2>Vthを満たしており、Vss1−Vss2=Vgs>Vthとする事で、その後タイミングT3で行われるVth補正の準備を行う。換言すると期間T2‐T3は、ドライブトランジスタTrdのリセット期間に相当する。また、発光素子ELの閾電圧をVthELとすると、VthEL>Vss2に設定されている。これにより、発光素子ELにはマイナスバイアスが印加され、いわゆる逆バイアス状態となる。この逆バイアス状態は、後で行うVth補正動作及び移動度補正動作を正常に行うために必要である。

【0049】

タイミングT3では制御信号AZ2をローレベルにし且つ直後制御信号DSもローレベルにしている。これによりトランジスタTr3がオフする一方トランジスタTr4がオンする。この結果ドレイン電流Idsが画素容量Csに流れ込み、Vth補正動作を開始する。この時ドライブトランジスタTrdのゲートGはVss1に保持されており、ドライブトランジスタTrdがカットオフするまで電流Idsが流れる。カットオフするとドライブトランジスタTrdのソース電位(S)はVss1−Vthとなる。ドレイン電流がカットオフした後のタイミングT4で制御信号DSを再びハイレベルに戻し、スイッチングトランジスタTr4をオフする。さらに制御信号AZ1もローレベルに戻し、スイッチングトランジスタTr2もオフする。この結果、画素容量CsにVthが保持固定される。この様にタイミングT3‐T4はドライブトランジスタTrdの閾電圧Vthを検出する期間である。ここでは、この検出期間T3‐T4をVth補正期間と呼んでいる。

【0050】

この様にVth補正を行った後タイミングT5で制御信号WSをハイレベルに切り替え、サンプリングトランジスタTr1をオンして映像信号Vsigを画素容量Csに書き込む。発光素子ELの等価容量Coledに比べて画素容量Csは充分に小さい。この結果、映像信号Vsigのほとんど大部分が画素容量Csに書き込まれる。正確には、Vss1に対する。Vsigの差分Vsig−Vss1が画素容量Csに書き込まれる。したがってドライブトランジスタTrdのゲートGとソースS間の電圧Vgsは、先に検出保持されたVthと今回サンプリングされたVsig−Vss1を加えたレベル(Vsig−Vss1+Vth)となる。以降説明簡易化の為Vss1=0Vとすると、ゲート/ソース間電圧Vgsは図7のタイミングチャートに示すようにVsig+Vthとなる。かかる映像信号Vsigのサンプリングは制御信号WSがローレベルに戻るタイミングT7まで行われる。すなわちタイミングT5‐T7がサンプリング期間に相当する。

【0051】

サンプリング期間の終了するタイミングT7より前のタイミングT6で制御信号DSがローレベルとなりスイッチングトランジスタTr4がオンする。これによりドライブトランジスタTrdが電源Vccに接続されるので、画素回路は非発光期間から発光期間に進む。この様にサンプリングトランジスタTr1がまだオン状態で且つスイッチングトランジスタTr4がオン状態に入った期間T6‐T7で、ドライブトランジスタTrdの移動度補正を行う。即ち本実施形態では、サンプリング期間の後部分と発光期間の先頭部分とが重なる期間T6‐T7で移動度補正を行っている。なお、この移動度補正を行う発光期間の先頭では、発光素子ELは実際には逆バイアス状態にあるので発光する事はない。この移動度補正期間T6‐T7では、ドライブトランジスタTrdのゲートGが映像信号Vsigのレベルに固定された状態で、ドライブトランジスタTrdにドレイン電流Idsが流れる。ここでVss1−Vth<VthELと設定しておく事で、発光素子ELは逆バイアス状態におかれる為、ダイオード特性ではなく単純な容量特性を示すようになる。よってドライブトランジスタTrdに流れる電流Idsは画素容量Csと発光素子ELの等価容量Coledの両者を結合した容量C=Cs+Coledに書き込まれていく。これによりドライブトランジスタTrdのソース電位(S)は上昇していく。図7のタイミングチャートではこの上昇分をΔVで表してある。この上昇分ΔVは結局画素容量Csに保持されたゲート/ソース間電圧Vgsから差し引かれる事になるので、負帰還をかけた事になる。この様にドライブトランジスタTrdの出力電流Idsを同じくドライブトランジスタTrdの入力電圧Vgsに負帰還する事で、移動度μを補正する事が可能である。なお負帰還量ΔVは移動度補正期間T6‐T7の時間幅tを調整する事で最適化可能である。

【0052】

タイミングT7では制御信号WSがローレベルとなりサンプリングトランジスタTr1がオフする。この結果ドライブトランジスタTrdのゲートGは信号線SLから切り離される。映像信号Vsigの印加が解除されるので、ドライブトランジスタTrdのゲート電位(G)は上昇可能となり、ソース電位(S)と共に上昇していく。その間画素容量Csに保持されたゲート/ソース間電圧Vgsは(Vsig−ΔV+Vth)の値を維持する。ソース電位(S)の上昇に伴い、発光素子ELの逆バイアス状態は解消されるので、出力電流Idsの流入により発光素子ELは実際に発光を開始する。この時のドレイン電流Ids対ゲート電圧Vgsの関係は、先のトランジスタ特性式1のVgsにVsig−ΔV+Vthを代入する事で、以下の式2のように与えられる。

Ids=kμ(Vgs−Vth)2=kμ(Vsig−ΔV)2・・・式2

上記式2において、k=(1/2)(W/L)Coxである。この特性式2からVthの項がキャンセルされており、発光素子ELに供給される出力電流IdsはドライブトランジスタTrdの閾電圧Vthに依存しない事が分かる。基本的にドレイン電流Idsは映像信号の信号電圧Vsigによって決まる。換言すると、発光素子ELは映像信号Vsigに応じた輝度で発光する事になる。その際Vsigは帰還量ΔVで補正されている。この補正量ΔVは丁度特性式2の係数部に位置する移動度μの効果を打ち消すように働く。したがって、ドレイン電流Idsは実質的に映像信号Vsigのみに依存する事になる。

【0053】

最後にタイミングT8に至ると制御信号DSがハイレベルとなってスイッチングトランジスタTr4がオフし、発光が終了すると共に当該フィールドが終わる。この後次のフィールドに移って再びVth補正動作、移動度補正動作及び発光動作が繰り返される事になる。

【0054】

図8は、移動度補正期間T6‐T7における画素回路2の状態を示す回路図である。図示するように、移動度補正期間T6‐T7では、サンプリングトランジスタTr1及びスイッチングトランジスタTr4がオンしている一方、残りのスイッチングトランジスタTr2及びTr3がオフしている。この状態でドライブトランジスタTr4のソース電位(S)はVss1−Vthである。このソース電位Sは発光素子ELのアノード電位でもある。前述したようにVss1−Vth<VthELと設定しておく事で、発光素子ELは逆バイアス状態におかれ、ダイオード特性ではなく単純な容量特性を示す事になる。よってドライブトランジスタTrdに流れる電流Idsは画素容量Csと発光素子ELの等価容量Coledとの合成容量C=Cs+Coledに流れ込む事になる。換言すると、ドレイン電流Idsの一部が画素容量Csに負帰還され、移動度の補正が行われる。

【0055】

図9は上述したトランジスタ特性式2をグラフ化したものであり、縦軸にIdsを取り横軸にVsigを取ってある。このグラフの下方に特性式2も合わせて示してある。図9のグラフは、画素1と画素2を比較した状態で特性カーブを描いてある。画素1のドライブトランジスタの移動度μは相対的に大きい。逆に画素2に含まれるドライブトランジスタの移動度μは相対的に小さい。この様にドライブトランジスタをポリシリコン薄膜トランジスタなどで構成した場合、画素間で移動度μがばらつく事は避けられない。例えば両画素1,2に同レベルの映像信号Vsigを書き込んだ場合、何ら移動度の補正を行わないと、移動度μの大きい画素1に流れる出力電流Ids1´は、移動度μの小さい画素2に流れる出力電流Ids2´に比べて大きな差が生じてしまう。この様に移動度μのばらつきに起因して出力電流Idsの間に大きな差が生じるので、画面のユニフォーミティを損なう事になる。

【0056】

そこで本発明では出力電流を入力電圧側に負帰還させる事で移動度のばらつきをキャンセルしている。トランジスタ特性式から明らかなように、移動度が大きいとドレイン電流Idsが大きくなる。したがって負帰還量ΔVは移動度が大きいほど大きくなる。図9のグラフに示すように、移動度μの大きな画素1の負帰還量ΔV1は移動度の小さな画素2の負帰還量ΔV2に比べて大きい。したがって、移動度μが大きいほど負帰還が大きくかかる事となって、ばらつきを抑制する事が可能である。図示するように、移動度μの大きな画素1でΔV1の補正をかけると、出力電流はIds1´からIds1まで大きく下降する。一方移動度μの小さな画素2の補正量ΔV2は小さいので、出力電流Ids2´はIds2までそれ程大きく下降しない。結果的に、Ids1とIds2は略等しくなり、移動度のばらつきがキャンセルされる。この移動度のばらつきのキャンセルは黒レベルから白レベルまでVsigの全範囲で行われるので、画面のユニフォーミティは極めて高くなる。以上をまとめると、移動度の異なる画素1と2があった場合、移動度の大きい画素1の補正量ΔV1は移動度の小さい画素2の補正量ΔV2に対して小さくなる。つまり移動度が大きいほどΔVが大きくIdsの減少値は大きくなる。これにより移動度の異なる画素電流値は均一化され、移動度のばらつきを補正する事ができる。

【0057】

以下参考の為図10を参照して、上述した移動度補正の数値解析を行う。図10に示すように、トランジスタTr1及びTr4がオンした状態で、ドライブトランジスタTrdのソース電位を変数Vに取って解析を行う。ドライブトランジスタTrdのソース電位(S)をVとすると、ドライブトランジスタTrdを流れるドレイン電流Idsは以下の式3に示す通りである。

【数1】

【0058】

またドレイン電流Idsと容量C(=Cs+Coled)の関係により、以下の式4に示す様にIds=dQ/dt=CdV/dtが成り立つ。

【数2】

【0059】

式4に式3を代入して両辺積分する。ここで、ソース電圧V初期状態は−Vthであり、移動度ばらつき補正時間(T6‐T7)をtとする。この微分方程式を解くと、移動度補正時間tに対する画素電流が以下の数式5のように与えられる。

【数3】

【0060】

移動度の異なる画素において、式5を用いてt=0usと2.5us時の電流値のグラフを図11に示す。なおこのグラフの下部に合わせて式5も載せておく。t=0usの移動度補正をかけない状態に比べ、t=2.5usでは移動度ばらつきに対する補正が充分にかかっている事が分かる。移動度補正無しでは40%のばらつきがあったものが、移動度補正をかけると10%以下に抑えられている。移動度補正動作時は、常にV<VthELを満たしている必要がある。上述した第1実施形態の画素回路では移動度補正時に画素容量Csと発光素子ELの等価容量Coledを使用している。ColedはCsに対して大きいので合成容量Cも大きくなり、移動度補正時間マージンを稼ぐ事ができる。

【0061】

以上の動作を行うことで、映像信号電位サンプル方式の画素回路においても移動度ばらつきの補正を行う事ができる事が分かる。既に実用化されている液晶ディスプレイの駆動方式は基本的に映像信号電位をサンプリングする電圧駆動である。よって有機ELパネルにおいても電圧駆動にて移動度ばらつき補正が可能となる事で、従来液晶ディスプレイで用いていた外付けソースドライバや低温ポリシリコンTFTなどを用いたパネル内蔵型ソースドライバなどを利用する事が可能となり、低コストにて有機ELパネルモジュールを作成する事ができる。また第1実施形態の画素回路ではドライブトランジスタ以外のスイッチングトランジスタはNチャネル型とPチャネル型を混在して用いているが、各トランジスタの特性はNチャネルでもPチャネルでも構わない。

【0062】

図12は、本発明にかかる表示装置の第2実施形態を示すブロック図である。理解を容易にする為図5に示した第1実施形態と対応する部分には対応する参照番号を用いてある。本表示措置は、画素アレイ1とこれを囲む周辺の回路とで構成されている。周辺回路は、水平セレクタ3とライトスキャナ4とドライブスキャナ5と第一補正用スキャナ71と第二補正用スキャナ72とを含む。画素アレイ1はマトリクス状に配列した画素回路2で構成されている。図では理解を容易にする為1個の画素回路2のみを示してある。画素回路2は6個のトランジスタTr1,Trd,Tr3〜Tr6と、2個の容量素子Cs1,Cs2と1個の発光素子ELとで構成されている。トランジスタは全てNチャネル型である。本画素回路2の主要部となるドライブトランジスタTrdは、そのゲートGが各容量素子Cs1,Cs2の一端に接続されている。一方の容量素子Cs1は本画素回路2の出力側と入力側を結ぶ結合容量である。他方の容量素子Cs2は結合容量Cs1を介して映像信号が書き込まれる画素容量である。ドライブトランジスタTrdのソースSは画素容量Cs2の他端に接続すると共に、発光素子ELに接続している。発光素子ELはダイオード型のデバイスであり、そのアノードがドライブトランジスタTrdのソースSに接続する一方、カソードKが接地電位Vcathに接続されている。またドライブトランジスタTrdのソースSと所定の基準電位Vss2との間にスイッチングトランジスタTr3が介在している。このトランジスタTr3のゲートは走査線AZ2に接続している。ドライブトランジスタTrdのドレインはスイッチングトランジスタTr4を介して電源Vccに接続されている。スイッチングトランジスタTr4のゲートは走査線DSに接続している。加えてドライブトランジスタTrdのゲートGとドレインとの間にスイッチングトランジスタTr5が介在している。このトランジスタTr5のゲートは走査線AZ1に接続している。一方入力側のサンプリングトランジスタTr1は信号線SLと結合容量Cs1の他端との間に接続されている。サンプリングトランジスタTr1のゲートは走査線WSに接続されている。結合容量Cs1の他端と所定の基準電位Vss1との間にトランジスタTr6が介在している。このトランジスタTr6のゲートは走査線AZ1に接続している。

【0063】

図13は、図12に示した画素回路の動作説明に供するタイミングチャートである。時間軸Tに沿って制御信号WS,DS,AZ1,AZ2の波形を表すと共に、ドライブトランジスタTrdのゲート電位(G)及びソース電位(S)の変化も表してある。当該フィールドが開始するタイミングT1では、制御信号WS,AZ1,AZ2がローレベルで、制御信号DSのみがハイレベルである。したがって、タイミングT1ではスイッチングトランジスタTr4のみがオン状態にあり、残りのトランジスタTr1,Tr3,Tr5,Tr6はオフ状態にある。この時ドライブトランジスタTrdはオン状態にあるスイッチングトランジスタTr4を介して電源Vccに接続されているので、所定のドレイン電流Idsが発光素子ELに流れる為、発光状態となっている。

【0064】

タイミングT2になると制御信号AZ1とAZ2とがハイレベルとなり、スイッチングトランジスタTr5,Tr6がオンする。ドライブトランジスタTrdのゲートGはトランジスタTr5を通して電源Vcc側に接続するので、ゲート電位(G)は急激に上昇する。

【0065】

この後タイミングT3で制御信号DSがローレベルとなり、トランジスタTr4がオフする。ドライブトランジスタTrdに対する電源供給が遮断されるので、ドレイン電流Idsは減衰していく。これによりソース電位(S)及びゲート電位(G)は共に下降するが、丁度両者の電位差がVthとなったところで電流が流れなくなる。この時のVthが画素容量Cs2に保持される。画素容量Cs2に保持されたVthはドライブトランジスタTrdの閾電圧のキャンセルに用いられる。また、スイッチングトランジスタTr3はオンしており、ドライブトランジスタTr2のソースSはトランジスタTr3を介して基準電位Vss2に接続される。このVss2は発光素子ELの閾電圧よりも低く設定されており、発光素子ELは逆バイアス状態におかれる。

【0066】

この後タイミングT4になったとき制御信号AZ1がローレベルとなり、トランジスタTr5,Tr6がオフして、Cs2に書き込まれたVthが固定される。タイミングT2からT4までVth補正期間(T2‐T4)と呼ぶ。なおVth補正期間ではTr6がオンしている為、結合容量Cs1の他端は所定の基準電位Vss1に保持される。

【0067】

タイミングT5になると制御信号WS及びAZ2がハイレベルになり、サンプリングトランジスタTr1がオンする。この結果、ドライブトランジスタTrdのゲートGは結合容量Cs1及びオンしたサンプリングトランジスタTr1を介して信号線SLに接続される。この結果映像信号が結合容量Cs1を介してドライブトランジスタTrdのゲートGにカップリングされ、その電位が上昇する。図13のタイミングチャートでは映像信号のカップリング分とVthを合わせた電圧をVinで表してある。画素容量Cs2にこのVinが保持された事になる。この後タイミングT7で制御信号WSがローレベルに戻り、画素容量Cs2に書き込まれた電位が保持固定される。この様にして映像信号が結合容量Cs1を介して画素容量Cs2に書き込まれる期間をサンプリング期間T5‐T7と呼ぶ。このサンプリング期間T5‐T7は通常1水平期間(1H)に相当する。

【0068】

本実施形態では、サンプリング期間が終了するタイミングT7の前のタイミングT6で、制御信号DSがハイレベルになる一方制御信号AZ2がローレベルになる。この結果ドライブトランジスタTrdのソースSがVss2から切り離される一方ドレイン側からソースS側に向かって電流が流れる。一方サンプリングトランジスタTr1は引き続きオン状態なのでドライブトランジスタTrdのゲート電位(G)は映像信号側に保持されている。この様な状態でドライブトランジスタTrdに出力電流が流れるので、画素容量Cs2及び逆バイアス状態にある発光素子ELの等価容量を充電する事になる。これによりドライブトランジスタTrdのソース電位(S)はΔVだけ上昇し、その分だけCs2に保持されていた電圧Vinが減少する。換言すると、期間T6‐T7の間でソースS側の出力電流がゲートG側の入力電圧に負帰還される。この負帰還量がΔVで表される。この負帰還動作により、ドライブトランジスタTrdの移動度補正が行われる。

【0069】

この後タイミングT7で制御信号WSがローレベルとなり、映像信号の印加が解除されると、いわゆるブートストラップ動作が行われゲート電位(G)及びソース電位(S)は両者の差(Vin−ΔV)を維持したまま上昇する。ソース電位(S)の上昇に伴い発光素子ELの逆バイアス状態は解消されるので、出力電流Idsが発光素子ELに流れ込み、映像信号に応じた輝度で発光が行われる。この後タイミングT8で当該フィールド1fが終わると次のフィールドに進む。次のフィールドでも、Vth補正、信号書き込み、移動度補正の各動作を行う。

【0070】

図14は、図13に示した移動度補正期間T6‐T7における画素回路2の状態を表している。この画素回路2もスイッチングトランジスタTr3,Tr4,Tr5などで構成される補正手段を備えている。この補正手段は出力電流Idsのキャリア移動度μに対する依存性を打ち消す為、予め発光期間T6‐T8の前または先頭で画素容量Cs2に保持された入力電圧Vin(Vgs)を補正する。この補正手段は走査線WS及びDSから供給される制御信号WS,DSに応じてサンプリング期間T5‐T7の一部で動作し、映像信号Vsigがサンプリングされている状態でドライブトランジスタTrdから出力電流Idsを取り出し、これを画素容量Cs2に負帰還して入力電圧Vgsを補正する。加えてこの補正手段(Tr3,Tr4,Tr5)は、出力電流Idsの閾電圧Vthに対する依存性を打ち消す為に、予めサンプリング期間T5‐T7に先立つ期間T2‐T4でドライブトランジスタTrdの閾電圧Vthを検出し、且つ検出された閾電圧Vthを入力電圧Vgsに足し込む様にしてある。

【0071】

本実施形態においても、ドライブトランジスタTrdはNチャネル型トランジスタでドレインが電源Vcc側に接続する一方ソースSが発光素子EL側に接続している。この構成において本補正手段は、サンプリング期間T5‐T7の後部分に重なる発光期間T6‐T8の先頭部分(T6‐T7)でドライブトランジスタTrdから出力電流Idsを取り出して、画素容量Cs2側に負帰還する。その際本補正手段は、発光期間の先頭部分(T6‐T7)でドライブトランジスタTrdのソースS側から取り出した出力電流Idsが、発光素子ELの有する等価容量Coledに流れ込むようにしている。発光素子ELはアノード及びカソードを備えたダイオード型の発光素子からなり、アノード側がドライブトランジスタTrdのソースSに接続する一方カソード側がVcathに接地されている。本補正手段は前述したように予め発光素子ELのアノード/カソード間を逆バイアス状態にセットしておき、ドライブトランジスタTrdのソースS側から取り出した出力電流Idsが発光素子ELに流れ込む時、ダイオード型の発光素子ELを容量性素子Coledとして機能させている。

【0072】

図15は、本発明にかかる表示装置の第3実施形態を示すブロック図である。理解を容易にする為、図5に示した第1実施形態と対応する部分には対応する参照番号を付してある。本表示装置も中央の画素アレイ1とこれを囲む周辺回路とで構成されている。周辺回路は水平セレクタ3、ライトスキャナ4、ドライブスキャナ5、第一補正用スキャナ71、第二補正用スキャナ72を含んでいる。画素アレイ1はマトリクス状に配列された画素回路から構成されている。図では理解を容易にする為1個の画素回路2のみを拡大表示してある。

【0073】

画素回路2は5個のトランジスタTr1,Tr2,Tr4,Tr5,Trdと2個の容量素子Cs1,Cs2と1個の発光素子ELとで構成されている。第1実施形態及び第2実施形態と異なり、ドライブトランジスタTrdはPチャネル型である。残りのトランジスタTr1,Tr2,Tr4,Tr5は全てNチャネル型である。なお画素サイズや発光素子ELの特性にもよるが、一般的にドライブトランジスタはNチャネル型の方が移動度補正値の容量を大きく取る事ができ、移動度補正のマージンがある。

【0074】

ドライブトランジスタTrdのソースは電源Vccに接続している。ゲートは画素容量Cs1の一端に接続している。ドライブトランジスタTrdがPチャネル型の場合、ゲート電圧Vgsはソース側となる電源Vccを基準にして定義される。ドライブトランジスタTrdのドレインはスイッチングトランジスタTr4を介して発光素子ELに接続している。発光素子ELはダイオード型であり、アノードがスイッチングトランジスタTr4を介してドライブトランジスタTrdのドレインに接続する一方、カソードが接地されている。なおスイッチングトランジスタTr4のゲートは走査線DSに接続している。ドライブトランジスタTrdのゲートとドレインとの間にスイッチングトランジスタTr5が介在している。そのゲートは走査線AZ1に接続している。

【0075】

一方画素回路2の入力側となるサンプリングトランジスタTr1は信号線SLと画素容量Cs1の他端との間に接続されている。サンプリングトランジスタTr1のゲートは走査線WSに接続されている。画素容量Cs1の他端と電源Vccとの間に別の画素容量Cs2が接続している。また画素容量Cs1の他端と所定のオフセット電位Vofsとの間にスイッチングトランジスタTr2が接続している。このトランジスタTr2のゲートは走査線AZ2に接続している。

【0076】

図16は、図15に示した画素回路の各トランジスタとこれらに対応する制御信号との関係を明示した回路図である。合わせてドライブトランジスタTrdのゲートを記号Gで明示し、発光素子ELのアノードを記号Xで明示してある。各トランジスタTr1,Tr2,Tr4,Tr5のゲートに印加される制御信号を対応する走査線と同じ記号で表してある。

【0077】

図17は、図16に示した画素回路の動作説明に供するタイミングチャートである。時間軸Tに沿って制御信号WS,AZ1,AZ2,DSの波形を表すと共に、ドライブトランジスタTrdのゲート電位(G)と発光素子ELのアノード電位(X)の変化も表してある。

【0078】

当該フィールドに入る前のタイミングT0で、制御信号WS,AZ1,AZ2はローレベルにある一方、制御信号DSはハイレベルにある。したがってタイミングT0ではトランジスタTr4がオン状態にある一方、残りのトランジスタTr1,Tr2,Tr5はオフ状態にある。ドライブトランジスタTrdはオン状態のトランジスタTr4を介して発光素子ELに接続している。したがって発光素子ELにはゲート電圧Vgsに応じた出力電流が流れて発光している。なお、図17のタイミングチャートではゲート電圧Vgsは電源電位Vccとゲート電位(G)との間の差で表される。

【0079】

当該フィールドに入るタイミングT1で、制御信号AZ1及びAZ2がハイレベルになり、トランジスタTr2,Tr5がオンする。これにより画素容量Cs1の他端は所定のオフセット電位Vofsに固定される。またドライブトランジスタTrdのドレインとゲートが直結する。この為ゲート電位(G)はドレイン電位に引かれて急激に下降する一方、アノード電位(X)は発光素子EL内に生じた電圧降下で急激に上昇する。この動作でドライブトランジスタTrdは閾電圧検出の準備状態となる。

【0080】

続いてタイミングT2で制御信号DSがローレベルとなり、スイッチングトランジスタTr4がオフする。ここまでの期間T1‐T2はリセット期間もしくはオーバーラップ期間と呼ばれる。スイッチングトランジスタTr4がオフするとドライブトランジスタの電流路が遮断され、ゲート容量Cgs及び画素容量Cs1を充電していく。この結果ゲート電位(G)が上昇する。丁度電源電位Vccとゲート電位(G)の差がVthとなった所でドライブトランジスタTrdがカットオフする。カットオフした後のタイミングT3で制御信号AZ1,AZ2がローレベルに戻り、トランジスタTr2,Tr5がオフする。この結果画素容量Cs1に書き込まれた閾電圧Vthが保持される。この期間T2‐T3をVth補正期間もしくはVth検出期間と呼ぶ。なお発光素子ELに対する通電が遮断されるので、アノード電位(X)は接地電位GNDまで下がる。

【0081】

この後タイミングT4に進むと制御信号WSがハイレベルになりサンプリングトランジスタTr1がオンする。この結果映像信号Vsigがサンプリングされ、画素容量Cs2にVofs−Vsigが書き込まれる。この電圧Vofs−Vsigは画素容量Cs1を介してドライブトランジスタTrdのゲートG側にカップリングされる。その量はCs1(Vofs−Vsig)/(Cs1+Cgs)で与えられる。なおCgsはドライブトランジスタのソース/ゲート間容量である。このカップリング電圧分だけさらにゲート電位(G)が下がるので、結局ゲート電圧VgsはVth+Cs1(Vofs−Vsig)/(Cs1+Cgs)となる。この後1水平期間(1H)経過後のタイミングT7で制御信号WSはローレベルに戻り、サンプリングトランジスタTr1がオフする。この1Hに相当する期間T4‐T7で映像信号Vsigのサンプリングが行われる。

【0082】

このサンプリング期間T4‐T7の一部の期間T5‐T6で制御信号AZ1がハイレベルになり、トランジスタTr5が導通する。この結果電源Vcc側(ドライブトランジスタTrdのソース側)からドレイン側を通ってゲートG側にドレイン電流が流れ込む。このドレイン電流の流れ込みによりゲート電位(G)はΔV分だけ上昇する。ΔVはドライブトランジスタの移動度に比例している。ドライブトランジスタの移動度が大きいほどΔVは大きくなりゲート電位(G)が上昇するので、ゲート電圧Vgsはその分圧縮され出力電流が抑制される。この様にドライブトランジスタTrdのドレイン側からゲート側に向かって負のフォードバックをかける事で、移動度のばらつきを抑制可能である。サンプリング期間T4‐T7の中に設定された期間T5‐T6を移動度補正期間と呼ぶ。この移動度補正を行うことで、ドライブトランジスタTrdのゲート電圧Vgsは結局Vth+Cs1(Vofs−Vsig)/(Cs1+Cgs)−ΔVで与えられる。このゲート電圧Vgsには正味の信号成分に加え、ドライブトランジスタの閾電圧をキャンセルするための成分Vthと移動度を補正する為の成分ΔVが含まれている。

【0083】

タイミングT8になると制御信号DSがハイレベルとなりスイッチングトランジスタTr4がオンする。これによりドライブトランジスタTrdは発光素子ELに直結し、閾電圧Vth及び移動度μのばらつきが補正された出力電流が発光素子ELに流れる。この後タイミングT9で当該フィールドが終了すると、次のフィールドに移って再びVth補正、映像信号サンプリング、移動度補正の各動作が行われる。

【0084】

図18は、移動度補正期間T5‐T6における画素回路の状態を示す回路図である。前述したように移動度補正期間T5‐T6ではサンプリングトランジスタTr1とスイッチングトランジスタTr5がオンしている為、ドレイン電流Idsは画素容量Cs1に書き込まれる。これによりドライブトランジスタTrdのゲート電位(G)はΔV上昇する。この時に流れるドレイン電流Idsは以下の式6により表される。なお、式6ではカップリング係数Cs1/(Cs1+Cgs)を1として省略してある。実際Cgsに比べてCs1はかなり大きい。

【数4】

【0085】

前述したようにΔV=Ids・t/Cs1より、移動度の異なる画素ではΔVも異なる。移動度が大きい画素ほどΔVは大きくなり、Idsの補正量も大きくなる。これらの動作により、移動度ばらつきがある画素においても、Idsを均一化する事ができ、移動度ばらつき補正を行う事ができる。

【0086】

詳細な計算式は先の実施形態1と同様な解析によって、以下の式7に示すように与えられる。

【数5】

【0087】

上記式7の右辺は移動度μを2つ含む。係数部のμと左辺の分母に位置するμは互いにキャンセルしあうので、結果的にドレイン電流Idsから移動度μの影響を除く事ができる。式7の分母にあるμの効果は移動度補正期間T5‐T6の時間幅tによって調整できる。これにより本発明の移動度補正を最適化可能である。

【符号の説明】

【0088】

1・・・画素アレイ、2・・・画素回路、3・・・水平セレクタ、4・・・ライトスキャナ、5・・・ドライブスキャナ、7・・・補正用スキャナ、Tr1・・・サンプリングトランジスタ、Trd・・・ドライブトランジスタ、EL・・・発光素子、Cs・・・容量素子

【特許請求の範囲】

【請求項1】

制御信号を供給する行状の走査線と映像信号を供給する列状の信号線とが交差する部分に配され、少なくともサンプリングトランジスタと、これに接続する容量部と、これに接続するドライブトランジスタと、これに接続する発光素子とを含み、

前記サンプリングトランジスタは、所定のサンプリング期間に走査線から供給される制御信号に応じ導通して信号線から供給された映像信号を該容量部にサンプリングし、

前記容量部は、該サンプリングされた映像信号に応じて該ドライブトランジスタのゲートとソース間に入力電圧を印加し、

前記ドライブトランジスタは、所定の発光期間中該入力電圧に応じた出力電流を該発光素子に供給し、該出力電流は該ドライブトランジスタのチャネル領域のキャリア移動度に対して依存性を有し、

前記発光素子は、該ドライブトランジスタから供給された出力電流により該映像信号に応じた輝度で発光する画素回路において、

該出力電流のキャリア移動度に対する依存性を打ち消すために、あらかじめ該発光期間の前又は先頭で該容量部に保持された該入力電圧を補正する補正手段を備えており、

前記補正手段は走査線から供給される制御信号に応じて該サンプリング期間の一部で動作し、該映像信号がサンプリングされている状態で該ドライブトランジスタから出力電流を取り出し、これを該容量部に負帰還して該入力電圧を補正することを特徴とする画素回路。

【請求項2】

前記ドライブトランジスタは、その出力電流がチャネル領域のキャリア移動度に加え閾電圧に対しても依存性を有し、

前記補正手段は、該出力電流の閾電圧に対する依存性を打ち消すために、あらかじめサンプリング期間に先立って該ドライブトランジスタの閾電圧を検出し、且つ該検出された閾電圧を該入力電圧に足し込む様にしたことを特徴とする請求項1記載の画素回路。

【請求項3】

前記ドライブトランジスタは、Nチャネル型トランジスタでドレインが電源側に接続する一方ソースが発光素子側に接続し、

前記補正手段は、該サンプリング期間の後部分に重なる該発光期間の先頭部分で該ドライブトランジスタから該出力電流を取り出して、該容量部側に負帰還することを特徴とする請求項1記載の画素回路。

【請求項4】

前記補正手段は、該発光期間の先頭部分で該ドライブトランジスタのソース側から取り出した該出力電流が、該発光素子の有する容量に流れ込む様にしたことを特徴とする請求項3記載の画素回路。

【請求項5】

前記発光素子はアノード及びカソードを備えたダイオード型の発光素子からなり、アノード側が該ドライブトランジスタのソースに接続する一方カソード側が接地されており、

前記補正手段は、あらかじめ該発光素子のアノード/カソード間を逆バイアス状態にセットしておき、該ドライブトランジスタのソース側から取り出した該出力電流が該発光素子に流れ込むとき、該ダイオード型の発光素子が容量性素子として機能するように制御することを特徴とする請求項4記載の画素回路。

【請求項6】

前記ドライブトランジスタは、Pチャネル型トランジスタでソースが電源側に接続する一方ドレインが発光素子側に接続し、

前記補正手段は、該発光期間よりも先行する該サンプリング期間の一部で、該ドライブトランジスタから該出力電流を取り出して該容量部側に負帰還することを特徴とする請求項1記載の画素回路。

【請求項7】

前記補正手段は、該サンプリング期間内で該ドライブトランジスタから出力電流を取り出す時間幅を調整可能であり、これにより該容量部に対する出力電流の負帰還量を最適化することを特徴とする請求項1記載の画素回路。

【請求項8】

画素アレイ部とスキャナ部と信号部とを含み、

前記画素アレイ部は、行状に配された走査線と列状に配された信号線と両者が交差する部分に配された行列状の画素とからなり、

前記信号部は、該信号線に映像信号を供給し、

前記スキャナ部は、該走査線に制御信号を供給して順次行ごとに画素を走査し、

各画素は、少なくともサンプリングトランジスタと、これに接続する容量部と、これに接続するドライブトランジスタと、これに接続する発光素子とを含み、

前記サンプリングトランジスタは、所定のサンプリング期間に走査線から供給される制御信号に応じ導通して信号線から供給された映像信号を該容量部にサンプリングし、

前記容量部は、該サンプリングされた映像信号に応じて該ドライブトランジスタのゲートとソース間に入力電圧を印加し、

前記ドライブトランジスタは、所定の発光期間中該入力電圧に応じた出力電流を該発光素子に供給し、該出力電流は該ドライブトランジスタのチャネル領域のキャリア移動度に対して依存性を有し、

前記発光素子は、該ドライブトランジスタから供給された出力電流により該映像信号に応じた輝度で発光する表示装置において、

各画素は、該ドライブトランジスタの出力電流のキャリア移動度に対する依存性を打ち消すために、あらかじめ該発光期間の前又は先頭で該容量部に保持された該入力電圧を補正する補正手段を備えており、

前記補正手段は走査線から供給される制御信号に応じて該サンプリング期間の一部で動作し、該映像信号がサンプリングされている状態で該ドライブトランジスタから出力電流を取り出し、これを該容量部に負帰還して該入力電圧を補正することを特徴とする表示装置。

【請求項9】

前記ドライブトランジスタは、その出力電流がチャネル領域のキャリア移動度に加え閾電圧に対しても依存性を有し、

前記補正手段は、該出力電流の閾電圧に対する依存性を打ち消すために、あらかじめサンプリング期間に先立って該ドライブトランジスタの閾電圧を検出し、且つ該検出された閾電圧を該入力電圧に足し込む様にしたことを特徴とする請求項8記載の表示装置。

【請求項10】

前記ドライブトランジスタは、Nチャネル型トランジスタでドレインが電源側に接続する一方ソースが発光素子側に接続し、

前記補正手段は、該サンプリング期間の後部分に重なる該発光期間の先頭部分で該ドライブトランジスタから該出力電流を取り出して、該容量部側に負帰還することを特徴とする請求項8記載の表示装置。

【請求項11】

前記補正手段は、該発光期間の先頭部分で該ドライブトランジスタのソース側から取り出した該出力電流が、該発光素子の有する容量に流れ込む様にしたことを特徴とする請求項10記載の表示装置。

【請求項12】

前記発光素子はアノード及びカソードを備えたダイオード型の発光素子からなり、アノード側が該ドライブトランジスタのソースに接続する一方カソード側が接地されており、 前記補正手段は、あらかじめ該発光素子のアノード/カソード間を逆バイアス状態にセットしておき、該ドライブトランジスタのソース側から取り出した該出力電流が該発光素子に流れ込むとき、該ダイオード型の発光素子が容量性素子として機能するように制御することを特徴とする請求項11記載の表示装置。

【請求項13】

前記ドライブトランジスタは、Pチャネル型トランジスタでソースが電源側に接続する一方ドレインが発光素子側に接続し、

前記補正手段は、該発光期間よりも先行する該サンプリング期間の一部で、該ドライブトランジスタから該出力電流を取り出して該容量部側に負帰還することを特徴とする請求項8記載の表示装置。

【請求項14】

前記補正手段は、該サンプリング期間内で該ドライブトランジスタから出力電流を取り出す時間幅を調整可能であり、これにより該容量部に対する出力電流の負帰還量を最適化することを特徴とする請求項8記載の表示装置。

【請求項15】

画素アレイ部とスキャナ部と信号部とを含み、前記画素アレイ部は行状に配された走査線と列状に配された信号線と両者が交差する部分に配された行列状の画素とからなり、前記信号部は該信号線に映像信号を供給し、前記スキャナ部は該走査線に制御信号を供給して順次行ごとに画素を走査し、各画素は少なくともサンプリングトランジスタと、これに接続する容量部と、これに接続するドライブトランジスタと、これに接続する発光素子とを含む表示装置の駆動方法であって、

前記スキャナ部は所定のサンプリング期間に走査線から該サンプリングトランジスタに制御信号を供給し導通させて、信号線から供給された映像信号を該容量部にサンプリングし、

前記容量部は、該サンプリングされた映像信号に応じて該ドライブトランジスタのゲートとソース間に入力電圧を印加し、

前記ドライブトランジスタは、所定の発光期間中該入力電圧に応じた出力電流を該発光素子に供給し、該出力電流は該ドライブトランジスタのチャネル領域のキャリア移動度に対して依存性を有し、

前記発光素子は、該ドライブトランジスタから供給された出力電流により該映像信号に応じた輝度で発光し、

更に前記スキャナ部は、該該ドライブトランジスタの出力電流のキャリア移動度に対する依存性を打ち消すために、あらかじめ該発光期間の前又は先頭で該容量部に保持された該入力電圧を補正する補正手順を該画素に行わせ、

前記補正手順は、該サンプリング期間内で該映像信号がサンプリングされている間に該ドライブトランジスタから出力電流を取り出し、これを該容量部に負帰還して該入力電圧を補正することを特徴とする表示装置の駆動方法。

【請求項1】

制御信号を供給する行状の走査線と映像信号を供給する列状の信号線とが交差する部分に配され、少なくともサンプリングトランジスタと、これに接続する容量部と、これに接続するドライブトランジスタと、これに接続する発光素子とを含み、

前記サンプリングトランジスタは、所定のサンプリング期間に走査線から供給される制御信号に応じ導通して信号線から供給された映像信号を該容量部にサンプリングし、

前記容量部は、該サンプリングされた映像信号に応じて該ドライブトランジスタのゲートとソース間に入力電圧を印加し、

前記ドライブトランジスタは、所定の発光期間中該入力電圧に応じた出力電流を該発光素子に供給し、該出力電流は該ドライブトランジスタのチャネル領域のキャリア移動度に対して依存性を有し、

前記発光素子は、該ドライブトランジスタから供給された出力電流により該映像信号に応じた輝度で発光する画素回路において、

該出力電流のキャリア移動度に対する依存性を打ち消すために、あらかじめ該発光期間の前又は先頭で該容量部に保持された該入力電圧を補正する補正手段を備えており、

前記補正手段は走査線から供給される制御信号に応じて該サンプリング期間の一部で動作し、該映像信号がサンプリングされている状態で該ドライブトランジスタから出力電流を取り出し、これを該容量部に負帰還して該入力電圧を補正することを特徴とする画素回路。

【請求項2】

前記ドライブトランジスタは、その出力電流がチャネル領域のキャリア移動度に加え閾電圧に対しても依存性を有し、

前記補正手段は、該出力電流の閾電圧に対する依存性を打ち消すために、あらかじめサンプリング期間に先立って該ドライブトランジスタの閾電圧を検出し、且つ該検出された閾電圧を該入力電圧に足し込む様にしたことを特徴とする請求項1記載の画素回路。

【請求項3】

前記ドライブトランジスタは、Nチャネル型トランジスタでドレインが電源側に接続する一方ソースが発光素子側に接続し、

前記補正手段は、該サンプリング期間の後部分に重なる該発光期間の先頭部分で該ドライブトランジスタから該出力電流を取り出して、該容量部側に負帰還することを特徴とする請求項1記載の画素回路。

【請求項4】

前記補正手段は、該発光期間の先頭部分で該ドライブトランジスタのソース側から取り出した該出力電流が、該発光素子の有する容量に流れ込む様にしたことを特徴とする請求項3記載の画素回路。

【請求項5】

前記発光素子はアノード及びカソードを備えたダイオード型の発光素子からなり、アノード側が該ドライブトランジスタのソースに接続する一方カソード側が接地されており、

前記補正手段は、あらかじめ該発光素子のアノード/カソード間を逆バイアス状態にセットしておき、該ドライブトランジスタのソース側から取り出した該出力電流が該発光素子に流れ込むとき、該ダイオード型の発光素子が容量性素子として機能するように制御することを特徴とする請求項4記載の画素回路。

【請求項6】

前記ドライブトランジスタは、Pチャネル型トランジスタでソースが電源側に接続する一方ドレインが発光素子側に接続し、

前記補正手段は、該発光期間よりも先行する該サンプリング期間の一部で、該ドライブトランジスタから該出力電流を取り出して該容量部側に負帰還することを特徴とする請求項1記載の画素回路。

【請求項7】

前記補正手段は、該サンプリング期間内で該ドライブトランジスタから出力電流を取り出す時間幅を調整可能であり、これにより該容量部に対する出力電流の負帰還量を最適化することを特徴とする請求項1記載の画素回路。

【請求項8】

画素アレイ部とスキャナ部と信号部とを含み、

前記画素アレイ部は、行状に配された走査線と列状に配された信号線と両者が交差する部分に配された行列状の画素とからなり、

前記信号部は、該信号線に映像信号を供給し、

前記スキャナ部は、該走査線に制御信号を供給して順次行ごとに画素を走査し、

各画素は、少なくともサンプリングトランジスタと、これに接続する容量部と、これに接続するドライブトランジスタと、これに接続する発光素子とを含み、

前記サンプリングトランジスタは、所定のサンプリング期間に走査線から供給される制御信号に応じ導通して信号線から供給された映像信号を該容量部にサンプリングし、

前記容量部は、該サンプリングされた映像信号に応じて該ドライブトランジスタのゲートとソース間に入力電圧を印加し、

前記ドライブトランジスタは、所定の発光期間中該入力電圧に応じた出力電流を該発光素子に供給し、該出力電流は該ドライブトランジスタのチャネル領域のキャリア移動度に対して依存性を有し、

前記発光素子は、該ドライブトランジスタから供給された出力電流により該映像信号に応じた輝度で発光する表示装置において、

各画素は、該ドライブトランジスタの出力電流のキャリア移動度に対する依存性を打ち消すために、あらかじめ該発光期間の前又は先頭で該容量部に保持された該入力電圧を補正する補正手段を備えており、

前記補正手段は走査線から供給される制御信号に応じて該サンプリング期間の一部で動作し、該映像信号がサンプリングされている状態で該ドライブトランジスタから出力電流を取り出し、これを該容量部に負帰還して該入力電圧を補正することを特徴とする表示装置。

【請求項9】

前記ドライブトランジスタは、その出力電流がチャネル領域のキャリア移動度に加え閾電圧に対しても依存性を有し、

前記補正手段は、該出力電流の閾電圧に対する依存性を打ち消すために、あらかじめサンプリング期間に先立って該ドライブトランジスタの閾電圧を検出し、且つ該検出された閾電圧を該入力電圧に足し込む様にしたことを特徴とする請求項8記載の表示装置。

【請求項10】

前記ドライブトランジスタは、Nチャネル型トランジスタでドレインが電源側に接続する一方ソースが発光素子側に接続し、

前記補正手段は、該サンプリング期間の後部分に重なる該発光期間の先頭部分で該ドライブトランジスタから該出力電流を取り出して、該容量部側に負帰還することを特徴とする請求項8記載の表示装置。

【請求項11】

前記補正手段は、該発光期間の先頭部分で該ドライブトランジスタのソース側から取り出した該出力電流が、該発光素子の有する容量に流れ込む様にしたことを特徴とする請求項10記載の表示装置。

【請求項12】

前記発光素子はアノード及びカソードを備えたダイオード型の発光素子からなり、アノード側が該ドライブトランジスタのソースに接続する一方カソード側が接地されており、 前記補正手段は、あらかじめ該発光素子のアノード/カソード間を逆バイアス状態にセットしておき、該ドライブトランジスタのソース側から取り出した該出力電流が該発光素子に流れ込むとき、該ダイオード型の発光素子が容量性素子として機能するように制御することを特徴とする請求項11記載の表示装置。

【請求項13】

前記ドライブトランジスタは、Pチャネル型トランジスタでソースが電源側に接続する一方ドレインが発光素子側に接続し、

前記補正手段は、該発光期間よりも先行する該サンプリング期間の一部で、該ドライブトランジスタから該出力電流を取り出して該容量部側に負帰還することを特徴とする請求項8記載の表示装置。

【請求項14】

前記補正手段は、該サンプリング期間内で該ドライブトランジスタから出力電流を取り出す時間幅を調整可能であり、これにより該容量部に対する出力電流の負帰還量を最適化することを特徴とする請求項8記載の表示装置。

【請求項15】

画素アレイ部とスキャナ部と信号部とを含み、前記画素アレイ部は行状に配された走査線と列状に配された信号線と両者が交差する部分に配された行列状の画素とからなり、前記信号部は該信号線に映像信号を供給し、前記スキャナ部は該走査線に制御信号を供給して順次行ごとに画素を走査し、各画素は少なくともサンプリングトランジスタと、これに接続する容量部と、これに接続するドライブトランジスタと、これに接続する発光素子とを含む表示装置の駆動方法であって、

前記スキャナ部は所定のサンプリング期間に走査線から該サンプリングトランジスタに制御信号を供給し導通させて、信号線から供給された映像信号を該容量部にサンプリングし、

前記容量部は、該サンプリングされた映像信号に応じて該ドライブトランジスタのゲートとソース間に入力電圧を印加し、

前記ドライブトランジスタは、所定の発光期間中該入力電圧に応じた出力電流を該発光素子に供給し、該出力電流は該ドライブトランジスタのチャネル領域のキャリア移動度に対して依存性を有し、

前記発光素子は、該ドライブトランジスタから供給された出力電流により該映像信号に応じた輝度で発光し、

更に前記スキャナ部は、該該ドライブトランジスタの出力電流のキャリア移動度に対する依存性を打ち消すために、あらかじめ該発光期間の前又は先頭で該容量部に保持された該入力電圧を補正する補正手順を該画素に行わせ、

前記補正手順は、該サンプリング期間内で該映像信号がサンプリングされている間に該ドライブトランジスタから出力電流を取り出し、これを該容量部に負帰還して該入力電圧を補正することを特徴とする表示装置の駆動方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【公開番号】特開2012−88724(P2012−88724A)

【公開日】平成24年5月10日(2012.5.10)

【国際特許分類】

【出願番号】特願2011−264386(P2011−264386)

【出願日】平成23年12月2日(2011.12.2)

【分割の表示】特願2005−27028(P2005−27028)の分割

【原出願日】平成17年2月2日(2005.2.2)

【出願人】(000002185)ソニー株式会社 (34,172)

【Fターム(参考)】

【公開日】平成24年5月10日(2012.5.10)

【国際特許分類】

【出願日】平成23年12月2日(2011.12.2)

【分割の表示】特願2005−27028(P2005−27028)の分割

【原出願日】平成17年2月2日(2005.2.2)

【出願人】(000002185)ソニー株式会社 (34,172)

【Fターム(参考)】

[ Back to top ]