画素回路及びそれを利用した発光表示装置

【課題】 複数の発光素子が一つの画素回路に連結されて発光するようにし,発光表示装置の開口率を高めるようにすることが可能な画素回路及び発光表示装置を提供すること。

【解決手段】 複数の発光素子OLED1a,OLED2aと,画素回路110aと,を備え,画素回路110aは,所定の電流に対応して上記発光素子に流れる駆動電流を生成する駆動回路111aと,上記複数の発光素子OLED1a,OLED2a及び上記駆動回路111aに連結されて上記駆動電流を上記複数の発光素子に順次伝達するスイッチング回路112a,113aを有する。上記駆動回路111aに1つに対して複数の発光素子OLED1a,OLED2aが連結され,複数の発光素子OLED1a,OLED2aがすべて発光すれば一つのフレームが完成される。

【解決手段】 複数の発光素子OLED1a,OLED2aと,画素回路110aと,を備え,画素回路110aは,所定の電流に対応して上記発光素子に流れる駆動電流を生成する駆動回路111aと,上記複数の発光素子OLED1a,OLED2a及び上記駆動回路111aに連結されて上記駆動電流を上記複数の発光素子に順次伝達するスイッチング回路112a,113aを有する。上記駆動回路111aに1つに対して複数の発光素子OLED1a,OLED2aが連結され,複数の発光素子OLED1a,OLED2aがすべて発光すれば一つのフレームが完成される。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は,画素回路及びそれを利用した発光表示装置に関し,さらに詳しく説明すれば,複数の発光素子が一つの画素回路に連結されて発光するようにし,発光表示装置の開口率を高めるようにする画素回路及びそれを利用した発光表示装置に関する。

【背景技術】

【0002】

近年,陰極線管に比べて重さと嵩が小さな各種平板表示装置が開発されており,特に発光效率,輝度及び視野角にすぐれて応答速度の速い発光表示装置が注目されている。

【0003】

発光素子は,光を発散する薄膜である発光層がカソード電極とアノード電極の間に位置する構造を持っており,発光層に電子及び正孔を入れ込んでこれらを再結合させることで,励気磁が生成されて励気磁の低いエネルギーに落ちながら発光する特性を持っている。

【0004】

このような発光素子は,発光層が無機物または有機物で構成され,発光層の種類によって無機発光素子と有機発光素子に区分される。

【0005】

図1は,従来の技術による電流書き込み方式の画素が採用されている画像表示部の一部を示す回路図である。

【0006】

図1を参照すれば,4個の画素が隣接して形成され,各画素は発光素子OLED及び画素回路を含む。画素回路は,第1トランジスタM1〜第4トランジスタM4及びキャパシタCstを含む。そして,第1トランジスタM1〜第4トランジスタM4はそれぞれゲート,ソース及びドレインを持ち,キャパシタCstは第1電極と第2電極を持つ。

【0007】

各画素は同一の構成をし,一番左側上位にある画素を説明すれば,発光素子OLEDに第1トランジスタM1が連結されて発光のための電流を供給する。

【0008】

第1トランジスタM1の電流量は,第2トランジスタM2を介して印加されるデータ電流によって制御されるようになっている。この時,印加された電流は,第1トランジスタM1のソースとゲートの間に連結されているキャパシタCstによって所定期間維持される。

【0009】

第3及び第4トランジスタM3,M4のゲートには,走査線Snが連結されており,第2トランジスタM2のソース側にはデータ線Dmが連結され,第4トランジスタM4のゲートには発光制御線Enが連結されている。

【0010】

このような構造の画素の動作をよく見れば,図5に示されたように,第3及び第4トランジスタM3,M4のゲートに印加される走査信号snが,ローになって第3及び第4トランジスタM3,M4がオンになれば,第1トランジスタM1はダイオード連結状態になってデータ電流Idata値に当たる電圧がキャパシタCstに充電される。

【0011】

走査信号snがハイになって第3及び第4トランジスタM3,M4がオフになり,発光制御信号enがローになって第4トランジスタM4がオンになれば,電源が供給されて第1トランジスタM1からキャパシタCstに充電された電圧値に対応する電流が発光素子OLEDに流れて発光がなされる。この時,発光素子OLEDに流れる電流は次の数学式1のようである。

【0012】

【数1】

【0013】

ここで,Idataはデータ電流,Vgsは第1トランジスタM1のソースとゲートの間の電圧,Vthは第1トランジスタM1のしきい値電圧,IOLEDは発光素子OLEDに流れる電流,βは第1トランジスタM1の利得係数を示す。

【0014】

上記数式1に示されたように,図5に示された画素回路によれば,発光素子に流れる電流IOLEDは,第1トランジスタM1のしきい値電圧Vth及び移動度(mobility)にバラ付きがあってもデータ電流Idataと同一のであるので,データ駆動部の書き込み電流源がパネル全体を介して均一であるとすれば,均一なディスプレイ特性を得ることができる。

【0015】

上記のような電流書き込み方式の画素回路では,微細電流をコントロールしなければならないからデータ信号を充電するのに多くの時間が必要であるという問題点がある。例えば,データ線負荷キャパシタンスが30pFであると仮定する場合,数十nAから数百nA水準である電流にデータ線の負荷を充電しようとすれば,数msecの時間が必要である。

【0016】

これは数十us水準であるライン時間を考慮して見る時,充電時間が十分でなく,特に低い輝度を表現する場合,電流値が小さくて充電時間がさらに多く必要になるような問題点がある。

【0017】

また,このような従来の発光表示装置に採用された画素は,一つの画素回路に一つの発光素子OLEDが連結され,複数の発光素子を発光させるためには複数の画素回路が必要であり画素回路を具現する素子の数が多くなるという問題点がある。そして,画素行に一本の発光制御線が連結されることによって,発光制御線による発光表示装置の開口率が低下するという問題点がある。

【0018】

一方,従来の画素回路及びこれを利用した発光表示装置に関する技術を記載した文献としては,下記特許文献1及び2等がある。

【特許文献1】特開2003−43999号明細書

【特許文献2】米国特許公開第2002−0021293A1号明細書

【発明の開示】

【発明が解決しようとする課題】

【0019】

このように,従来の発光表示装置によれば,微細電流をコントロールしなければならないからデータ信号を充電するのに多くの時間が必要であり,特に低い輝度を表現する場合電流値が小さくて充電時間がさらに多く必要になるという問題がある。また,一つの画素回路に一つの発光素子OLEDが連結されると画素回路を具現する素子の数が多くなり,画素行に1本の発光制御線が連結されることにより,開口率が低下するという問題もある。

【0020】

そこで,本発明は,このような問題に鑑みてなされたもので,その目的は,データ信号の電流量を大きくし,低い輝度値を持つ場合にも電流書き込み時間を減らすようにし,一つの画素回路に複数の発光素子が連結されるようにして発光表示装置の素子数を減らし,開口率を高め,色分離現象を最小化することが可能な,新規かつ改良された画素回路及びそれを利用した発光表示装置を提供することにある。

【課題を解決するための手段】

【0021】

上記課題を解決するために,本発明のある観点によれば,複数の発光素子と;画素回路と;を備え,上記画素回路は,所定の電流に対応して上記発光素子に流れる駆動電流を生成する駆動回路と;上記複数の発光素子及び上記駆動回路に連結されて上記駆動電流を上記複数の発光素子に順次伝達するスイッチング回路と;を有することを特徴とする,画素が提供される。上記駆動回路1つに対して,上記複数の発光素子が連結され,上記駆動回路はそれぞれの発光素子を駆動する。また複数の発光素子がすべて発光すると一つのフレームが完成される。

【0022】

また,上記駆動回路は,ゲートに印加された電圧によって電流を流す第1トランジスタと,上記走査信号によって選択的に上記第1トランジスタをダイオード連結する第2トランジスタと,上記走査信号によってデータ電流を上記第1トランジスタに伝達する第3トランジスタと,上記第1トランジスタに伝達された上記データ電流に対応する第1レベルの電圧を充電する第1キャパシタと,上記第1キャパシタと直列連結されて上記第1キャパシタに充電されている電圧を第1レベルから第2レベルの電圧に変更させる第2キャパシタと,を有してもよい。

【0023】

また,上記第1スイッチング回路は,第1発光素子に連結されて第1発光制御信号に連結されている第4トランジスタを有し,上記第2スイッチング回路は,第2発光素子に連結されて第2発光制御信号に連結されている第5トランジスタを有してもよい。

【0024】

また,上記第1発光制御信号及び上記第2発光制御信号は,第1区間及び第2区間を繰り返す周期的な信号であり,上記第1区間において,上記第1発光制御信号はロー信号であり,上記第2発光制御信号はハイ信号であり,上記第2区間において,上記第1発光制御信号はハイ信号であり,上記第2発光制御信号はロー信号であってもよい。

【0025】

また,上記第1レベルの電圧は,上記第1トランジスタに流れる電流に対応される電圧であってもよい。

【0026】

また,上記第2レベルは,上記第2キャパシタがブースト信号の印加を受け,上記第1キャパシタと上記第2キャパシタによって分圧された電圧であってもよい。

【0027】

また,上記ブースト信号は,上記第2トランジスタがオン状態の時,上記第2キャパシタに充電される電圧を変動させてもよい。

【0028】

上記課題を解決するために,本発明の別の観点によれば,第1〜第4発光素子と;画素回路と;を備え,上記画素回路は,所定の電流に対応して上記第1〜第4発光素子に流れる駆動電流を生成する駆動回路と;上記第1〜第4発光素子及び上記駆動回路間に連結され,上記第1〜第4発光素子の駆動を順次制御するためのスイッチング回路と;を有することを特徴とする画素が提供される。上記駆動回路1つに対して,上記第1〜第4発光素子が連結され,上記駆動回路は,それぞれの発光素子を駆動する。また複数の発光素子がすべて発光すると一つのフレームが完成される。

【0029】

また,上記駆動回路は,ゲートに印加された電圧によって電流を流れるようにする第1トランジスタと,上記走査信号によって選択的に上記第1トランジスタをダイオード連結する第2トランジスタと,上記走査信号によってデータ電流を上記第1トランジスタに伝達する第3トランジスタと,上記第1トランジスタに伝達された上記データ電流に対応する第1レベルの電圧を充電する第1キャパシタと,上記第1キャパシタと直列連結されて上記第1キャパシタに充電されている電圧を第1レベルから第2レベルに変更させる第2キャパシタと,を有してもよい。

【0030】

また,上記スイッチング回路は,上記第1及び第2発光素子の駆動を制御する第1スイッチング回路と,上記第3及び第4発光素子の駆動を制御する第2スイッチング回路と,

を有し,上記第1スイッチング回路は,第1発光制御信号によって上記電流を伝達する第4トランジスタと,第2発光制御信号によって上記第4トランジスタによって伝達された上記電流を上記第1発光素子に伝達する第5トランジスタと,上記第3発光制御信号によって上記第5トランジスタと異なる状態を維持し,上記第4トランジスタによって伝達された上記電流を第2発光素子に伝達する第6トランジスタと,を有し,上記第2スイッチング回路は,上記第2発光制御信号によって上記電流を伝達する第7トランジスタと,上記第3発光制御信号によって上記第7トランジスタによって伝達された上記電流を第3発光素子に伝達する第8トランジスタと,上記第3発光制御信号によって上記第8トランジスタと異なる状態を維持し,上記第7トランジスタによって伝達された上記電流を第4発光素子に伝達する第9トランジスタと,を有してもよい

【0031】

また,上記第1レベルの電圧は,上記第1トランジスタに流れる電流に対応される電圧であってもよい。

【0032】

また,上記第2レベルの電圧は,上記第2キャパシタがブースト信号の印加を受け,上記第1キャパシタと上記第2キャパシタによって分圧された電圧であってもよい。

【0033】

上記課題を解決するために,本発明の別の観点によれば,複数の画素を含む画像表示部と;上記画素にデータ信号を伝達するデータ駆動部と;上記画素に走査信号と第1〜第3発光制御信号を伝達する走査駆動部と;を備え,上記画素は,上記のいずれかに記載の発光表示装置が提供される。

【0034】

また,上記走査駆動部は,ブースト信号をさらに伝達してもよい。

【0035】

また,上記複数の画素のうち,同一のデータ線を介して上記データ信号の伝達を受ける隣接した第1及び第2画素は,上記第1画素の第1発光素子及び第2発光素子の発光手順と,上記第2画素の第1発光素子及び第2発光素子の発光手順が異なるように具現され,

上記第1画素の第3発光素子及び第4発光素子の発光手順と上記第2画素の第3発光素子と第4発光素子の発光手順が異なるように具現されてもよい。

【0036】

また,上記第1〜第3発光制御信号は,第1区間〜第4区間を持つ周期的な信号であり,上記第1発光制御信号と上記第2発光制御信号は,互いに異なる状態を維持し,各区間でハイ状態とロー状態を繰り返し,上記第3発光制御信号は,上記第1区間及び上記第2区間は信号に変化のない同じ状態を維持し,上記第3区間及び上記第4区間は信号に変化のない同じ状態を維持し,上記第3区間及び上記第4区間の状態は,上記第1区間及び第2区間の状態を反転させたものであってもよい。

【発明の効果】

【0037】

以上説明したように,本発明によれば,一つの画素回路に複数の発光素子が連結されることによって発光表示装置の画素回路の数が減るようになり,さらに少ない素子で画像を表現することができ,画素回路の数が減少することによって信号を伝達する走査,データ線及び発光制御線の数が減って走査駆動部とデータ駆動部の大きさを小さく具現することができ,不要な空間を減らすことができる。

【0038】

また,配線の数が減少することによって発光表示装置の開口率が高くなる。

【0039】

そして,一つの発光素子の発光する時間が減って輝度を一定に維持するためにはさらに大きい電流が必要になるので,低階調を表現する場合にも電流が充電される時間を減らすことができる。

【発明を実施するための最良の形態】

【0040】

以下に,添付した図面を参照しながら,本発明の好適な実施の形態について詳細に説明する。なお,本明細書及び図面において,実質的に同一の機能構成を有する発明特定事項については,同一の符号を付することにより重複説明を省略する。

【0041】

図2は,本発明による発光表示装置第1実施形態の構造を示す構造図である。

【0042】

図2を参照して説明すれば,発光表示装置は画像表示部100a,データ駆動部200a及び走査駆動部300aを含む。

【0043】

画像表示部100aは,複数の画素110a,行方向に配列された複数の走査線S1,S2,・・・Sn−1,Sn,行方向に配列された複数のブースト信号線B1,B2,・・・Bn−1,Bn,行方向に配列された複数の第1発光制御線E11,E12,・・・E1n−1,E1n及び第2発光制御線E21,E22,・・・E2n−1,E2n,列方向に配列された複数のデータ線D1,D2,・・・Dm−1,Dm及び画素電源を供給する複数の画素電源線(図示せず。)を含む。画素電源線は外部から電源の印加を受けて画素電源を供給する。

【0044】

そして,走査線S1,S2,・・・Sn−1,Snを介して伝達される走査信号とブースト信号線B1,B2,・・・Bn−1,Bnを介して伝達されるブースト信号によってデータ線D1,D2,・・・Dm−1,Dmに伝達されるデータ信号が画素回路110aに伝達され,画素回路110aはデータ信号に対応される駆動電流を生成し,第1発光制御線E11,E12,・・・E1n−1,E1n及び第2発光制御線E21,E22,・・・E2n−1,E2nを介して伝達される発光制御信号によって駆動電流が発光素子OLEDに伝達されて画像が表現される。

【0045】

データ駆動部200aは,データ線D1,D2,・・・Dm−1,Dmに連結されて画像表示部100aにデータ信号を伝達する。そして,データ駆動部200aは一本のデータ線に赤と緑,緑と青または青と赤のデータを順次伝達する。

【0046】

走査駆動部300aは,画像表示部100aの側面に構成され,複数の走査線S1,S2,・・・Sn−1,Sn,複数のブースト信号線B1,B2,・・・Bn−1,Bnと複数の第1発光制御線E11,E12,・・・E1n−1,E1n及び第2発光制御線E21,E22,・・・E2n−1,E2nに連結されて走査信号と発光制御信号を画像表示部100aに伝達する。複数のブースト信号線B1,B2,・・・Bn−1,Bnは走査駆動部300aを介して伝達を受けるように図示されているが,別途の構成部分(図示せず。)から伝達を受けることも可能である。

【0047】

図3は,本発明による発光表示装置の第2実施形態の構造を示す構造図である。図3を参照すると,発光表示装置は画像表示部100b,データ駆動部200b及び走査駆動部300bを含む。

【0048】

画像表示部100bは,複数の画素110b,行方向に配列された複数の走査線S1,S2,・・・Sn−1,Sn,行方向に配列された複数のブースト信号線B1,B2,・・・Bn−1,Bn,行方向に配列された複数の第1発光制御線E11,E12,・・・E1n−1,E1n,第2発光制御線E21,E22,・・・E2n−1,E2n及び第3発光制御線E31,E32,・・・E3n−1,E3n,列方向に配列された複数のデータ線D1,D2,・・・Dm−1,Dm及び画素電源を供給する複数の画素電源線(図示せず。)を含む。画素電源線は外部から電源の印加を受けて画素電源を供給する。

【0049】

そして,走査線S1,S2,・・・Sn−1,Snを介して伝達される走査信号とブースト信号線B1,B2,・・・Bn−1,Bnを介して伝達されるブースト信号によってデータ線D1,D2,・・・Dm−1,Dmから伝達されるデータ信号が画素110に伝達され,画素110bはデータ信号に対応される駆動電流を生成し,第1発光制御線E11,E12,・・・E1n−1,E1n,第2発光制御線E21,E22,・・・E2n−1,E2n,第3発光制御線E31,E32,・・・E3n−1,E3nを介して伝達される発光制御信号によって電流が発光素子OLEDに伝達されて画像表示部100bで画像が表現される。

【0050】

データ駆動部200bは,データ線D1,D2,・・・Dm−1,Dmに連結されて画像表示部100bにデータ信号を伝達する。データ駆動部200bは,一本のデータ線に赤と緑,緑と青または青と赤のデータを順次伝達する。

【0051】

走査駆動部300bは,画像表示部100の側面に構成され,複数の走査線S1,S2,・・・Sn−1,Sn,複数のブースト信号線B1,B2,・・・Bn−1,Bnと複数の第1発光制御線E11,E12,・・・E1n−1,E1n〜第3発光制御線E31,E32,・・・E3n−1,E3nに連結されて走査信号と発光制御信号を画像表示部100bに伝達する。複数のブースト信号線B1,B2,・・・Bn−1,Bnは走査駆動部300aを介して伝達を受けるように図示されているが,別途の構成部分(図示せず。)から伝達を受けることも可能である。

【0052】

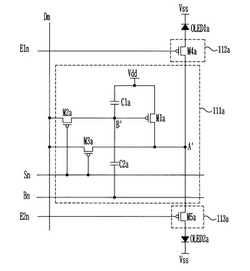

図4は,図2の発光表示装置に採用された画素の第1実施形態を示す回路図である。

【0053】

図4を参照して説明すれば,画素110aは,発光素子と画素回路を含み,一つの画素回路に2個の発光素子OLEDが連結されている。各画素回路110aは,第1トランジスタ〜第5トランジスタM1a〜M5aと第1キャパシタC1a及び第2キャパシタC2aを含む。

【0054】

画素回路は,駆動回路111a,第1スイッチング回路112及び第2スイッチング回路113に区分され,駆動回路111は第1〜第3トランジスタM1a〜M3aと第1及び第2キャパシタC1a及びC2aを含み,第1スイッチング回路112aは第4トランジスタM4aを含み,第2スイッチング回路113aは第5トランジスタM5aを含む。

【0055】

第1〜第5トランジスタM1a〜M5aは,PMOS形態のトランジスタに具現され,それぞれのトランジスタのソースとドレインは物理的な差がなく,第1電極と第2電極と称することができる。また,第1キャパシタC1a及び第2キャパシタC2aは,第1電極と第2電極を具備する。そして,2個の発光素子は第1及び第2発光素子OLED1a及びOLED2aと称する。

【0056】

第1トランジスタM1aは,ソースは画素電源線Vddに連結され,ドレインは第1ノードA’に連結される。そして,ゲートは第2ノードB’に連結され,第2ノードB’に印加される電圧によって第1ノードA’に電流を供給する。

【0057】

第2トランジスタM2aは,ソースはデータ線Dmに連結され,ドレインは第2ノードBに連結される。そして,ゲートは走査線Snに連結されて走査線Snを介して伝達される走査信号によってデータ信号を第2ノードB’に伝達する。

【0058】

第3トランジスタM3aは,ソースは第1ノードA’に連結され,ドレインはデータ線Dmに連結される。そして,ゲートは走査線Snに連結され,走査線Snを介して伝達される走査信号によって第1トランジスタM1aのソースからドレインに流れる電流が第3トランジスタM3aのソースからドレインに流れるようにする。

【0059】

第1キャパシタC1aは,第1電極は画素電源線Vddに連結され,第2電極は第2ノードB’に連結されてデータ信号に対応する電圧を所定時間の間維持する。

【0060】

第2キャパシタC2aは,第1電極が第2ノードB’に連結され,第2電極はブースト信号線Bnに連結されてブースト信号によって第1トランジスタM1のゲート電圧が変わるようにする。本実施形態において,第1レベルの電圧とは,データ線を介して流れるデータ電流に対応して第1キャパシタC1aに充電される電圧であり,第2レベルの電圧とは,ブースト信号によって第1キャパシタC1aと第2キャパシタC2aに電圧分配が行われた状態でのB’ノードの電圧である。

【0061】

第4トランジスタM4aは,ソースは第1ノードA’に連結され,ドレインは第1発光素子OLED1aに連結される。そして,ゲートは第1発光制御線に連結されて第1発光制御線E1nを介して伝達される第1発光制御信号e1nによって第1トランジスタで生成して第1ノードA’に流れるようにする電流を第1発光素子OLED1aに伝達する。

【0062】

第5トランジスタM5aは,ソースは第1ノードA’に連結され,ドレインは第2発光素子OLED2aに連結される。そして,ゲートは第2発光制御線E2nに連結され,第2発光制御線E2nを介して伝達される第2発光制御線E2nによって第1トランジスタM1aで生成して第1ノードA’に流れるようにする電流を第2発光素子OLED2aに伝達する。

【0063】

図5は,図4に示された画素が採用された発光表示装置に伝達される信号の波形を示す波形図である。

【0064】

図5を参照して説明すれば,画素は走査信号sn,データ信号,ブースト信号bn及び第1及び第2発光制御線e1n及びe2nによって動作する。

【0065】

まず,第1及び第2発光制御線e1n及びe2nが同時にハイ状態である区間内でブースト信号bnがローになり,走査信号snはブースト信号bnがロー状態である区間内でローになる。

【0066】

走査信号snがローになれば,第2トランジスタM2aと第3トランジスタM3aがオン状態になり,第1トランジスタM1aのソースからドレイン方向にデータ電流Idataが流れる。この時,流れるデータ電流によって第1トランジスタM1aのソースとゲートの間の電圧値が変わるようになる。ここで,電圧値を次の数式2に示す。

【0067】

【数2】

【0068】

ここで,Idataは印加されたデータ電流,Vgsは第1トランジスタM1aのソースとゲートの間の電圧,Vthは第1トランジスタM1aのしきい値電圧,βは第1トランジスタM1の利得係数を示す。

【0069】

そして,走査信号snによって第2トランジスタM2aと第3トランジスタM3aがオフ状態になった後,第1発光制御信号Enによって第4トランジスタM4aがオン状態になれば第1トランジスタM1aに流れる電流が第4トランジスタM4aを介して発光素子OLED1aに流れて発光するようになる。

【0070】

上記の場合,第2トランジスタM2aがオフされる時,第1キャパシタC1aと第2キャパシタC2aのカップリングによって第1トランジスタM1aのゲート電圧値が増加するようになる。この場合,増加する電圧値を数式3に示す。

【0071】

【数3】

【0072】

ここで,△Vgは第1キャパシタC1aと第2キャパシタC2aのカップリングによって増加する第1トランジスタM1aのゲートの電圧値,△Vboostはブースト信号の電圧幅を示す。

【0073】

そして,第1発光制御線E1nがロー状態になれば,第4トランジスタM4がオン状態になり,第1発光素子OLED1aに電流が流れる。第1発光素子OLED1aに流れる電流を次の数式4に示す。

【0074】

【数4】

【0075】

ここで,IOLEDは第1発光素子OLED1に流れる電流,Vgsは第1トランジスタM1aにデータ電流が流れる時,第1トランジスタM1aのソースとゲートの間の電圧,△Vgは第1キャパシタC1aと第2キャパシタC2aのカップリングによって増加する第1トランジスタM1aのゲートの電圧値,Vthは第1トランジスタM1aのしきい値電圧,βは第1トランジスタM1aの利得係数を示す。

【0076】

上記数式3と数式4を通じて分かるように,大きいデータ電流として発光素子OLED1aで電流を調節することができる。すなわち,データ線に大きい電流を供給することによって一ライン時間の間,データ線の充電時間を確保することができる。つまり,△Vgが正電圧である場合,数式1のIOLEDより数式4のIOLEDが小さくなる。よってIOLEDにさらに大きい電流を流すためにはIdataの電流を大きくすべきである。Idataの電流を大きくすることにより,データ線を早く充電することができる。

【0077】

また,走査信号とブースト信号がロー信号になって第1発光制御信号と第2発光制御信号がハイ信号になれば,再度画素回路が動作して数式2にあたるデータ電流が生成され,走査信号とブースト信号がハイ信号になって第2発光制御信号がロー信号になれば,第5トランジスタM5aがオン状態になって数式4にあたる電流が第2発光素子OLED2aに流れる。

【0078】

図6は,図3の発光表示装置で採用された画素の第1実施形態を示す回路図である。

【0079】

図6を参照して説明すれば,画素は発光素子と画素回路を含み,一つの画素回路に4個の発光素子OLED1b〜OLED4bが連結されている。各画素回路110は,第1トランジスタ〜第9トランジスタM1b〜M9bと第1キャパシタC1b及び第2キャパシタC2bを含む。

【0080】

画素回路は,駆動回路111b,第1スイッチング回路112b及び第2スイッチング回路113bに区分され,駆動回路111bは第1〜第3トランジスタM1b〜M3bと,第1及び第2キャパシタC1b及びC2bを含み,第1スイッチング回路112bは第4トランジスタ〜第6トランジスタM4b〜M6bを含み,第2スイッチング回路113bは第7トランジスタ〜第9トランジスタM7b〜M9bを含む。

【0081】

第1〜第5トランジスタM1b〜M5b及び第7及び第8トランジスタM7b,M8bは,PMOS形態のトランジスタに具現され,第6及び第9トランジスタM6b及びM9bはNMOS形態のトランジスタに具現される。

【0082】

それぞれのトランジスタのソースとドレインは物理的な差がなく,第1電極と第2電極と称することができる。また,第1キャパシタC1b及び第2キャパシタC2bは,第1電極と第2電極を具備する。そして,4個の発光素子は第1〜第4発光素子OLED1b〜OLED4bと称する。

【0083】

第1トランジスタM1bは,ソースは画素電源線Vddに連結され,ドレインは第1ノードA’’に連結される。そして,ゲートは第2ノードB’’に連結されて第2ノードB’’に印加される電圧によって第1ノードA’’に電流を供給する。

【0084】

第2トランジスタM2bは,ソースはデータ線Dmに連結され,ドレインは第2ノードB’’に連結される。そして,ゲートは走査線Snに連結されて走査線Snを介して伝達される走査信号によってデータ信号を第2ノードB’’に伝達する。

【0085】

第3トランジスタM3bは,ソースは第1ノードA’’に連結され,ドレインはデータ線Dmに連結される。そして,ゲートは走査線Snに連結されて走査線Snを介して伝達される走査信号によって第1トランジスタM1bのソースからドレインに流れる電流が第3トランジスタM3bのソースからドレインに流れるようにする。

【0086】

第1キャパシタC1bは,第1電極は画素電源線Vddに連結され,第2電極は第2ノードB’’に連結されてデータ信号に対応される電圧を所定時間の間維持する。

【0087】

第2キャパシタC2bは,第1電極が第2ノードB’’に連結され,第2電極はブースト信号線Bnに連結され,ブースト信号bnによって第1トランジスタM1bのゲート電圧を高める。本実施形態において,第1レベルの電圧とは,データ線を介して流れるデータ電流に対応して第1キャパシタC1bに充電される電圧であり,第2レベルの電圧とは,ブースト信号によって第1キャパシタC1bと第2キャパシタC2bに電圧分配が行われた状態でのB’’ノードの電圧である。

【0088】

第4トランジスタM4bは,ソースは第1ノードA’’に連結され,ドレインは第3ノードC’’に連結され,ゲートは第1発光制御線E1nに連結されて第1発光制御線E1nを介して伝達される第1発光制御線E1nによって第1ノードA’’に流れる電流を選択的に第3ノードC’’に伝達する。

【0089】

第5トランジスタM5bは,ソースは第1ノードA’’に連結され,ドレインは第4ノードD’’に連結され,ゲートは第2発光制御線E2nに連結されて第2発光制御線E2nを介して伝達される第2発光制御線E2nによって第2ノードB’’に流れる電流を選択的に第4ノードD’’に伝達する。

【0090】

第6トランジスタM6bは,ソースは第3ノードC’’に連結され,ドレインは第1発光素子OLED1bに連結される。そして,ゲートは第3発光制御線E3nに連結されて第3発光制御線E3nを介して伝達される第3発光制御信号e3nによって第3ノードC’’に伝達された電流を選択的に第1発光素子OLED1bに伝達する。

【0091】

第7トランジスタM7bは,ソースは第3ノードC’’に連結され,ドレインは第2発光素子OLED2bに連結される。そして,ゲートは第3発光制御線E3nに連結されて第3発光制御線E3nを介して伝達される第3発光制御線E3nによって第3ノードC’’に伝達された電流を選択的に第2発光素子OLED2bに伝達する。

【0092】

第6トランジスタM6bは,NMOS形態のトランジスタであり,第7トランジスタM7bはPMOS形態のトランジスタなので,第3発光制御信号e3nは第6トランジスタM6bと第7トランジスタM7bのうち一つのトランジスタがオン状態になる。よって第1発光素子OLED1bと第2発光素子OLED2bのうち一つの発光素子を選択して発光させる。

【0093】

第8トランジスタM8bは,ソースは第4ノードD’’に連結され,ドレインは第3発光素子OLED3に連結される。そして,ゲートは第3発光制御線E3nに連結されて第3発光制御線E3nを介して伝達される第3発光制御線E3nによって第4ノードD’’に伝達された電流を選択的に第3発光素子OLED3bに伝達する。

【0094】

第9トランジスタM9bは,ソースは第4ノードD’’に連結され,ドレインは第4発光素子OLED4bに連結される。そして,ゲートは第3発光制御線E3nに連結されて第3発光制御線E3nを介して伝達される第3発光制御線E3nによって第4ノードD’’に伝達された電流を選択的に第4発光素子OLED4bに伝達する。

【0095】

第8トランジスタM8bは,PMOS形態のトランジスタであり,第9トランジスタM9bは,NMOS形態のトランジスタなので,第3発光制御信号e3nは第8トランジスタM8bと第9トランジスタM9bのうち一つのトランジスタがオン状態になる。よって第3発光素子OLED3bと第4発光素子OLED4bのうち一つの発光素子を選択して発光させる。

【0096】

図7は,図6に示された画素が採用された発光表示装置に伝達する信号の波形を示す波形図である。

【0097】

図7を参照して説明すれば,画素は走査信号sn,データ信号,ブースト信号bn及び第1〜第3発光制御信号e1n〜e3nによって動作する。

【0098】

第1区間Td1は,第1発光制御信号e1nがロー状態で,第2発光制御信号e1n及び第3発光制御信号e3nがハイ状態であり,第2区間Td2は,第1発光制御信号e1nと第3発光制御信号e3nハイ状態で,第2発光制御信号e2nがロー状態であり,第3区間Td3は,第1発光制御信号e1nと第3発光制御信号e3nがロー状態で,第2発光制御信号e2nはハイ状態である。また,第4区間Td4では,第1発光制御信号e1nはハイ状態で,第2発光制御信号e2nと第3発光制御信号e3nはロー状態であり,走査信号snは順次各区間の開始時点でしばらくロー状態になり,ブースト信号bnは走査信号snがロー状態である時点でロー状態になる。

【0099】

まず,第1区間Td1で第1発光制御信号e1nと第3発光制御信号e3nによって,上記数式4に記載された電流が第1発光素子OLED1bで流れるようになり,第2区間T2では第2発光制御信号e2nと第3発光制御信号e3nによって上記数式4に記載された電流が第4発光素子OLED4bに流れるようになり,第3区間Td3では第1発光制御信号e1nと第3発光制御信号e3nによって第2発光素子OLED2bに上記数式4に記載された電流が流れるようになる。また,第4区間Td4では第2発光制御信号e2nと第3発光制御信号e3nによって第3発光素子OLED3bに上記数式4に記載された電流が流れるようになる。

【0100】

上記図2〜図7に示されているように,電流を利用して第1トランジスタM1a,M1bのソースとゲート間の電圧を調節して発光させる場合には,電流が充電される時間が必要であり,一つの画素回路に一つの発光素子が連結されている場合に比べ,一つの画素回路に2個の発光素子が連結されている場合は発光する時間が1/2になり,4個の発光素子が連結されている場合は発光する時間が1/4に減る。

【0101】

したがって,発光する時間が減少することによって一つの画素回路に流れる電流と同一の電流が流れるようになれば,輝度が下がるようになり,2個の発光素子または4個の発光素子を発光させるためには2倍または4倍の電流が流れるようにし,これによって電流が大きくなれば電流が一つの画素回路に充電される時間が短くなり,特に低階調を表現する場合には,少ない電流量を持って表現するのでさらに好ましい。つまり,高階調を表現する場合には流れる電流量が大きいため,データ線を充電する時間が問題にならないが,低階調を表現する場合,輝度が低く,発光素子に流れる電流量が高階調に比べて小さくなり,画素回路に充電する時間は,高階調に比べて長くなる。よって従来技術に比較すると本実施形態では,大きい電流をデータ信号として使用するので,画素回路に充電される時間が従来より短くなる。

【0102】

図8a〜図8dは,図6に示された発光表示装置において発光過程を示す図である。

【0103】

画像表示部100bは,3個の画素回路が垂直配列され,12個の発光素子が2×6の形態に配列される。そして上位にある画素回路を第1画素回路とし,中央にある画素回路を第2画素回路,下位にある画素回路を第3画素回路とする。

【0104】

図8a〜図8dを参照して説明すれば,1フレームの間4個の発光素子が順次発光するので,1フレームの時間を4個のサブフィールドに分けることができる。

【0105】

第1画素回路は,第3発光制御信号e3nの伝達を受けてスイッチング動作をする第6トランジスタM6bと第9トランジスタM9bがNMOS形態のトランジスタに具現され,第7トランジスタM7bと第8トレジストM8bがPMOS形態のトランジスタに具現される。

【0106】

そして,第2画素回路は,第6トランジスタM6bと第9トランジスタM9bがPMOS形態のトランジスタに具現され,第7トランジスタM7bと第8トレジストM8bがNMOS形態のトランジスタに具現される。

【0107】

また,第3画素回路は,第6トランジスタM6bと第9トランジスタM9bがNMOS形態のトランジスタに具現され,第7トランジスタM7bと第8トレジストM8bがPMOS形態のトランジスタに具現される。そして,各画素回路の第1発光素子OLED1bと第3発光素子OLED3bは,赤データ信号の伝達を受けて発光し,第2発光素子OLED2bと第4発光素子OLED4bは緑データ信号の伝達を受けて発光する。

【0108】

したがって,図8aは4個のサブフィールドの中で第1サブフィールドを示すものであり,図8aに示されているように第1画素回路は,第6トランジスタM6bに連結されている第1発光素子OLED1bが発光をし,第2画素回路は第7トランジスタM7bに連結されている第2発光素子OLED2bが発光し,第3画素回路は第6トランジスタM6bに連結されている第1発光素子OLED1bが発光する。

【0109】

したがって,第1サブフィールドでは第1画素回路と第3画素回路に連結されている第1発光素子OLED1bが発光し,第2画素回路に連結されている第2発光素子OLED2bが発光して赤と緑が同時に発光するようにする。

【0110】

そして,第2サブフィールドを示す図8bは,第1画素回路は第9トランジスタM9bに連結されている第4発光素子OLED4bが発光し,第2画素回路は第8トランジスタM8bに連結されている第3発光素子OLED3bが発光し,第3画素回路は第7トランジスタM7bに連結されている第4発光素子OLED4bが発光する。

【0111】

したがって,第2サブフィールドでは第1画素回路と第3画素回路に連結されている第4発光素子OLED4bが発光し,第2画素回路と連結されている第3発光素子OLED3bが発光して赤と緑が同時に発光するようになる。

【0112】

また,第3サブフィールドを示す図8cは,第1画素回路は第7トランジスタM7bに連結されている第2発光素子OLED2bが発光し,第2画素回路は第6トランジスタM6bに連結されている第1発光素子OLED1bが発光し,第3画素回路は第7トランジスタM7bに連結されている第2発光素子OLED2bが発光して赤と緑が同時に発光するようになる。

【0113】

最後に,第4サブフィールドを示す図8dは,第1画素回路は第8トランジスタM8bに連結されている第3発光素子OLED3bが発光し,第2画素回路は第9トランジスタM9bに連結されている第4発光素子OLED4bが発光し,第3画素回路は第8トランジスタM8bに連結されている第3発光素子OLED3bが発光して赤と緑が同時に発光するようになる。

【0114】

一つのサブフィールドで一つの色だけが発光する場合に,色分離現象が現われるようになるが,各サブフィールドで赤と緑が同時に発光するようになり,画像表示部全体をよく見れば,赤,緑及び青が各サブフィールドで同時に発光するようになって色分離現象を防止することができる。

【0115】

以上,添付図面を参照しながら本発明の好適な実施形態について説明したが,本発明はかかる例に限定されない。当業者であれば,特許請求の範囲に記載された技術的思想の範疇内において,各種の変更例または修正例に想到し得ることは明らかであり,それらについても当然に本発明の技術的範囲に属するものと了解される。

【0116】

例えば,本実施形態では,1つの駆動回路に対して2個の発光素子(図4),4個の発光素子(図6)について示したが,これと異なる数の発光素子を1つの駆動回路で制御してもよい。

【産業上の利用可能性】

【0117】

本発明は,画素回路及びそれを利用した発光表示装置に適用可能である。

【図面の簡単な説明】

【0118】

【図1】従来の技術による電流書き込み方式の画素が採用されている画像表示部の一部を示す回路図である。

【図2】本発明の第1実施形態にかかる発光表示装置の構造を示す構造図である。

【図3】本発明による発光表示装置の第2実施形態の構造を示す構造図である。

【図4】図2の発光表示装置に採用された画素の第1実施形態を示す回路図である。

【図5】図4に示された画素が採用された発光表示装置に伝達される信号の波形を示す波形図である。

【図6】図3の発光表示装置に採用された画素の第1実施形態を示す回路図である。

【図7】図6に示された画素が採用された発光表示装置に伝達される信号の波形を示す波形図である。

【図8a】図6に示された発光表示装置においての発光過程(第1サブフィールド)を示す図である。

【図8b】図6に示された発光表示装置においての発光過程(第2サブフィールド)を示す図である。

【図8c】図6に示された発光表示装置においての発光過程(第3サブフィールド)を示す図である。

【図8d】図6に示された発光表示装置においての発光過程(第4サブフィールド)を示す図である。

【符号の説明】

【0119】

100 画像表示部

200 データ駆動部

300 走査駆動部

OLED 発光素子

【技術分野】

【0001】

本発明は,画素回路及びそれを利用した発光表示装置に関し,さらに詳しく説明すれば,複数の発光素子が一つの画素回路に連結されて発光するようにし,発光表示装置の開口率を高めるようにする画素回路及びそれを利用した発光表示装置に関する。

【背景技術】

【0002】

近年,陰極線管に比べて重さと嵩が小さな各種平板表示装置が開発されており,特に発光效率,輝度及び視野角にすぐれて応答速度の速い発光表示装置が注目されている。

【0003】

発光素子は,光を発散する薄膜である発光層がカソード電極とアノード電極の間に位置する構造を持っており,発光層に電子及び正孔を入れ込んでこれらを再結合させることで,励気磁が生成されて励気磁の低いエネルギーに落ちながら発光する特性を持っている。

【0004】

このような発光素子は,発光層が無機物または有機物で構成され,発光層の種類によって無機発光素子と有機発光素子に区分される。

【0005】

図1は,従来の技術による電流書き込み方式の画素が採用されている画像表示部の一部を示す回路図である。

【0006】

図1を参照すれば,4個の画素が隣接して形成され,各画素は発光素子OLED及び画素回路を含む。画素回路は,第1トランジスタM1〜第4トランジスタM4及びキャパシタCstを含む。そして,第1トランジスタM1〜第4トランジスタM4はそれぞれゲート,ソース及びドレインを持ち,キャパシタCstは第1電極と第2電極を持つ。

【0007】

各画素は同一の構成をし,一番左側上位にある画素を説明すれば,発光素子OLEDに第1トランジスタM1が連結されて発光のための電流を供給する。

【0008】

第1トランジスタM1の電流量は,第2トランジスタM2を介して印加されるデータ電流によって制御されるようになっている。この時,印加された電流は,第1トランジスタM1のソースとゲートの間に連結されているキャパシタCstによって所定期間維持される。

【0009】

第3及び第4トランジスタM3,M4のゲートには,走査線Snが連結されており,第2トランジスタM2のソース側にはデータ線Dmが連結され,第4トランジスタM4のゲートには発光制御線Enが連結されている。

【0010】

このような構造の画素の動作をよく見れば,図5に示されたように,第3及び第4トランジスタM3,M4のゲートに印加される走査信号snが,ローになって第3及び第4トランジスタM3,M4がオンになれば,第1トランジスタM1はダイオード連結状態になってデータ電流Idata値に当たる電圧がキャパシタCstに充電される。

【0011】

走査信号snがハイになって第3及び第4トランジスタM3,M4がオフになり,発光制御信号enがローになって第4トランジスタM4がオンになれば,電源が供給されて第1トランジスタM1からキャパシタCstに充電された電圧値に対応する電流が発光素子OLEDに流れて発光がなされる。この時,発光素子OLEDに流れる電流は次の数学式1のようである。

【0012】

【数1】

【0013】

ここで,Idataはデータ電流,Vgsは第1トランジスタM1のソースとゲートの間の電圧,Vthは第1トランジスタM1のしきい値電圧,IOLEDは発光素子OLEDに流れる電流,βは第1トランジスタM1の利得係数を示す。

【0014】

上記数式1に示されたように,図5に示された画素回路によれば,発光素子に流れる電流IOLEDは,第1トランジスタM1のしきい値電圧Vth及び移動度(mobility)にバラ付きがあってもデータ電流Idataと同一のであるので,データ駆動部の書き込み電流源がパネル全体を介して均一であるとすれば,均一なディスプレイ特性を得ることができる。

【0015】

上記のような電流書き込み方式の画素回路では,微細電流をコントロールしなければならないからデータ信号を充電するのに多くの時間が必要であるという問題点がある。例えば,データ線負荷キャパシタンスが30pFであると仮定する場合,数十nAから数百nA水準である電流にデータ線の負荷を充電しようとすれば,数msecの時間が必要である。

【0016】

これは数十us水準であるライン時間を考慮して見る時,充電時間が十分でなく,特に低い輝度を表現する場合,電流値が小さくて充電時間がさらに多く必要になるような問題点がある。

【0017】

また,このような従来の発光表示装置に採用された画素は,一つの画素回路に一つの発光素子OLEDが連結され,複数の発光素子を発光させるためには複数の画素回路が必要であり画素回路を具現する素子の数が多くなるという問題点がある。そして,画素行に一本の発光制御線が連結されることによって,発光制御線による発光表示装置の開口率が低下するという問題点がある。

【0018】

一方,従来の画素回路及びこれを利用した発光表示装置に関する技術を記載した文献としては,下記特許文献1及び2等がある。

【特許文献1】特開2003−43999号明細書

【特許文献2】米国特許公開第2002−0021293A1号明細書

【発明の開示】

【発明が解決しようとする課題】

【0019】

このように,従来の発光表示装置によれば,微細電流をコントロールしなければならないからデータ信号を充電するのに多くの時間が必要であり,特に低い輝度を表現する場合電流値が小さくて充電時間がさらに多く必要になるという問題がある。また,一つの画素回路に一つの発光素子OLEDが連結されると画素回路を具現する素子の数が多くなり,画素行に1本の発光制御線が連結されることにより,開口率が低下するという問題もある。

【0020】

そこで,本発明は,このような問題に鑑みてなされたもので,その目的は,データ信号の電流量を大きくし,低い輝度値を持つ場合にも電流書き込み時間を減らすようにし,一つの画素回路に複数の発光素子が連結されるようにして発光表示装置の素子数を減らし,開口率を高め,色分離現象を最小化することが可能な,新規かつ改良された画素回路及びそれを利用した発光表示装置を提供することにある。

【課題を解決するための手段】

【0021】

上記課題を解決するために,本発明のある観点によれば,複数の発光素子と;画素回路と;を備え,上記画素回路は,所定の電流に対応して上記発光素子に流れる駆動電流を生成する駆動回路と;上記複数の発光素子及び上記駆動回路に連結されて上記駆動電流を上記複数の発光素子に順次伝達するスイッチング回路と;を有することを特徴とする,画素が提供される。上記駆動回路1つに対して,上記複数の発光素子が連結され,上記駆動回路はそれぞれの発光素子を駆動する。また複数の発光素子がすべて発光すると一つのフレームが完成される。

【0022】

また,上記駆動回路は,ゲートに印加された電圧によって電流を流す第1トランジスタと,上記走査信号によって選択的に上記第1トランジスタをダイオード連結する第2トランジスタと,上記走査信号によってデータ電流を上記第1トランジスタに伝達する第3トランジスタと,上記第1トランジスタに伝達された上記データ電流に対応する第1レベルの電圧を充電する第1キャパシタと,上記第1キャパシタと直列連結されて上記第1キャパシタに充電されている電圧を第1レベルから第2レベルの電圧に変更させる第2キャパシタと,を有してもよい。

【0023】

また,上記第1スイッチング回路は,第1発光素子に連結されて第1発光制御信号に連結されている第4トランジスタを有し,上記第2スイッチング回路は,第2発光素子に連結されて第2発光制御信号に連結されている第5トランジスタを有してもよい。

【0024】

また,上記第1発光制御信号及び上記第2発光制御信号は,第1区間及び第2区間を繰り返す周期的な信号であり,上記第1区間において,上記第1発光制御信号はロー信号であり,上記第2発光制御信号はハイ信号であり,上記第2区間において,上記第1発光制御信号はハイ信号であり,上記第2発光制御信号はロー信号であってもよい。

【0025】

また,上記第1レベルの電圧は,上記第1トランジスタに流れる電流に対応される電圧であってもよい。

【0026】

また,上記第2レベルは,上記第2キャパシタがブースト信号の印加を受け,上記第1キャパシタと上記第2キャパシタによって分圧された電圧であってもよい。

【0027】

また,上記ブースト信号は,上記第2トランジスタがオン状態の時,上記第2キャパシタに充電される電圧を変動させてもよい。

【0028】

上記課題を解決するために,本発明の別の観点によれば,第1〜第4発光素子と;画素回路と;を備え,上記画素回路は,所定の電流に対応して上記第1〜第4発光素子に流れる駆動電流を生成する駆動回路と;上記第1〜第4発光素子及び上記駆動回路間に連結され,上記第1〜第4発光素子の駆動を順次制御するためのスイッチング回路と;を有することを特徴とする画素が提供される。上記駆動回路1つに対して,上記第1〜第4発光素子が連結され,上記駆動回路は,それぞれの発光素子を駆動する。また複数の発光素子がすべて発光すると一つのフレームが完成される。

【0029】

また,上記駆動回路は,ゲートに印加された電圧によって電流を流れるようにする第1トランジスタと,上記走査信号によって選択的に上記第1トランジスタをダイオード連結する第2トランジスタと,上記走査信号によってデータ電流を上記第1トランジスタに伝達する第3トランジスタと,上記第1トランジスタに伝達された上記データ電流に対応する第1レベルの電圧を充電する第1キャパシタと,上記第1キャパシタと直列連結されて上記第1キャパシタに充電されている電圧を第1レベルから第2レベルに変更させる第2キャパシタと,を有してもよい。

【0030】

また,上記スイッチング回路は,上記第1及び第2発光素子の駆動を制御する第1スイッチング回路と,上記第3及び第4発光素子の駆動を制御する第2スイッチング回路と,

を有し,上記第1スイッチング回路は,第1発光制御信号によって上記電流を伝達する第4トランジスタと,第2発光制御信号によって上記第4トランジスタによって伝達された上記電流を上記第1発光素子に伝達する第5トランジスタと,上記第3発光制御信号によって上記第5トランジスタと異なる状態を維持し,上記第4トランジスタによって伝達された上記電流を第2発光素子に伝達する第6トランジスタと,を有し,上記第2スイッチング回路は,上記第2発光制御信号によって上記電流を伝達する第7トランジスタと,上記第3発光制御信号によって上記第7トランジスタによって伝達された上記電流を第3発光素子に伝達する第8トランジスタと,上記第3発光制御信号によって上記第8トランジスタと異なる状態を維持し,上記第7トランジスタによって伝達された上記電流を第4発光素子に伝達する第9トランジスタと,を有してもよい

【0031】

また,上記第1レベルの電圧は,上記第1トランジスタに流れる電流に対応される電圧であってもよい。

【0032】

また,上記第2レベルの電圧は,上記第2キャパシタがブースト信号の印加を受け,上記第1キャパシタと上記第2キャパシタによって分圧された電圧であってもよい。

【0033】

上記課題を解決するために,本発明の別の観点によれば,複数の画素を含む画像表示部と;上記画素にデータ信号を伝達するデータ駆動部と;上記画素に走査信号と第1〜第3発光制御信号を伝達する走査駆動部と;を備え,上記画素は,上記のいずれかに記載の発光表示装置が提供される。

【0034】

また,上記走査駆動部は,ブースト信号をさらに伝達してもよい。

【0035】

また,上記複数の画素のうち,同一のデータ線を介して上記データ信号の伝達を受ける隣接した第1及び第2画素は,上記第1画素の第1発光素子及び第2発光素子の発光手順と,上記第2画素の第1発光素子及び第2発光素子の発光手順が異なるように具現され,

上記第1画素の第3発光素子及び第4発光素子の発光手順と上記第2画素の第3発光素子と第4発光素子の発光手順が異なるように具現されてもよい。

【0036】

また,上記第1〜第3発光制御信号は,第1区間〜第4区間を持つ周期的な信号であり,上記第1発光制御信号と上記第2発光制御信号は,互いに異なる状態を維持し,各区間でハイ状態とロー状態を繰り返し,上記第3発光制御信号は,上記第1区間及び上記第2区間は信号に変化のない同じ状態を維持し,上記第3区間及び上記第4区間は信号に変化のない同じ状態を維持し,上記第3区間及び上記第4区間の状態は,上記第1区間及び第2区間の状態を反転させたものであってもよい。

【発明の効果】

【0037】

以上説明したように,本発明によれば,一つの画素回路に複数の発光素子が連結されることによって発光表示装置の画素回路の数が減るようになり,さらに少ない素子で画像を表現することができ,画素回路の数が減少することによって信号を伝達する走査,データ線及び発光制御線の数が減って走査駆動部とデータ駆動部の大きさを小さく具現することができ,不要な空間を減らすことができる。

【0038】

また,配線の数が減少することによって発光表示装置の開口率が高くなる。

【0039】

そして,一つの発光素子の発光する時間が減って輝度を一定に維持するためにはさらに大きい電流が必要になるので,低階調を表現する場合にも電流が充電される時間を減らすことができる。

【発明を実施するための最良の形態】

【0040】

以下に,添付した図面を参照しながら,本発明の好適な実施の形態について詳細に説明する。なお,本明細書及び図面において,実質的に同一の機能構成を有する発明特定事項については,同一の符号を付することにより重複説明を省略する。

【0041】

図2は,本発明による発光表示装置第1実施形態の構造を示す構造図である。

【0042】

図2を参照して説明すれば,発光表示装置は画像表示部100a,データ駆動部200a及び走査駆動部300aを含む。

【0043】

画像表示部100aは,複数の画素110a,行方向に配列された複数の走査線S1,S2,・・・Sn−1,Sn,行方向に配列された複数のブースト信号線B1,B2,・・・Bn−1,Bn,行方向に配列された複数の第1発光制御線E11,E12,・・・E1n−1,E1n及び第2発光制御線E21,E22,・・・E2n−1,E2n,列方向に配列された複数のデータ線D1,D2,・・・Dm−1,Dm及び画素電源を供給する複数の画素電源線(図示せず。)を含む。画素電源線は外部から電源の印加を受けて画素電源を供給する。

【0044】

そして,走査線S1,S2,・・・Sn−1,Snを介して伝達される走査信号とブースト信号線B1,B2,・・・Bn−1,Bnを介して伝達されるブースト信号によってデータ線D1,D2,・・・Dm−1,Dmに伝達されるデータ信号が画素回路110aに伝達され,画素回路110aはデータ信号に対応される駆動電流を生成し,第1発光制御線E11,E12,・・・E1n−1,E1n及び第2発光制御線E21,E22,・・・E2n−1,E2nを介して伝達される発光制御信号によって駆動電流が発光素子OLEDに伝達されて画像が表現される。

【0045】

データ駆動部200aは,データ線D1,D2,・・・Dm−1,Dmに連結されて画像表示部100aにデータ信号を伝達する。そして,データ駆動部200aは一本のデータ線に赤と緑,緑と青または青と赤のデータを順次伝達する。

【0046】

走査駆動部300aは,画像表示部100aの側面に構成され,複数の走査線S1,S2,・・・Sn−1,Sn,複数のブースト信号線B1,B2,・・・Bn−1,Bnと複数の第1発光制御線E11,E12,・・・E1n−1,E1n及び第2発光制御線E21,E22,・・・E2n−1,E2nに連結されて走査信号と発光制御信号を画像表示部100aに伝達する。複数のブースト信号線B1,B2,・・・Bn−1,Bnは走査駆動部300aを介して伝達を受けるように図示されているが,別途の構成部分(図示せず。)から伝達を受けることも可能である。

【0047】

図3は,本発明による発光表示装置の第2実施形態の構造を示す構造図である。図3を参照すると,発光表示装置は画像表示部100b,データ駆動部200b及び走査駆動部300bを含む。

【0048】

画像表示部100bは,複数の画素110b,行方向に配列された複数の走査線S1,S2,・・・Sn−1,Sn,行方向に配列された複数のブースト信号線B1,B2,・・・Bn−1,Bn,行方向に配列された複数の第1発光制御線E11,E12,・・・E1n−1,E1n,第2発光制御線E21,E22,・・・E2n−1,E2n及び第3発光制御線E31,E32,・・・E3n−1,E3n,列方向に配列された複数のデータ線D1,D2,・・・Dm−1,Dm及び画素電源を供給する複数の画素電源線(図示せず。)を含む。画素電源線は外部から電源の印加を受けて画素電源を供給する。

【0049】

そして,走査線S1,S2,・・・Sn−1,Snを介して伝達される走査信号とブースト信号線B1,B2,・・・Bn−1,Bnを介して伝達されるブースト信号によってデータ線D1,D2,・・・Dm−1,Dmから伝達されるデータ信号が画素110に伝達され,画素110bはデータ信号に対応される駆動電流を生成し,第1発光制御線E11,E12,・・・E1n−1,E1n,第2発光制御線E21,E22,・・・E2n−1,E2n,第3発光制御線E31,E32,・・・E3n−1,E3nを介して伝達される発光制御信号によって電流が発光素子OLEDに伝達されて画像表示部100bで画像が表現される。

【0050】

データ駆動部200bは,データ線D1,D2,・・・Dm−1,Dmに連結されて画像表示部100bにデータ信号を伝達する。データ駆動部200bは,一本のデータ線に赤と緑,緑と青または青と赤のデータを順次伝達する。

【0051】

走査駆動部300bは,画像表示部100の側面に構成され,複数の走査線S1,S2,・・・Sn−1,Sn,複数のブースト信号線B1,B2,・・・Bn−1,Bnと複数の第1発光制御線E11,E12,・・・E1n−1,E1n〜第3発光制御線E31,E32,・・・E3n−1,E3nに連結されて走査信号と発光制御信号を画像表示部100bに伝達する。複数のブースト信号線B1,B2,・・・Bn−1,Bnは走査駆動部300aを介して伝達を受けるように図示されているが,別途の構成部分(図示せず。)から伝達を受けることも可能である。

【0052】

図4は,図2の発光表示装置に採用された画素の第1実施形態を示す回路図である。

【0053】

図4を参照して説明すれば,画素110aは,発光素子と画素回路を含み,一つの画素回路に2個の発光素子OLEDが連結されている。各画素回路110aは,第1トランジスタ〜第5トランジスタM1a〜M5aと第1キャパシタC1a及び第2キャパシタC2aを含む。

【0054】

画素回路は,駆動回路111a,第1スイッチング回路112及び第2スイッチング回路113に区分され,駆動回路111は第1〜第3トランジスタM1a〜M3aと第1及び第2キャパシタC1a及びC2aを含み,第1スイッチング回路112aは第4トランジスタM4aを含み,第2スイッチング回路113aは第5トランジスタM5aを含む。

【0055】

第1〜第5トランジスタM1a〜M5aは,PMOS形態のトランジスタに具現され,それぞれのトランジスタのソースとドレインは物理的な差がなく,第1電極と第2電極と称することができる。また,第1キャパシタC1a及び第2キャパシタC2aは,第1電極と第2電極を具備する。そして,2個の発光素子は第1及び第2発光素子OLED1a及びOLED2aと称する。

【0056】

第1トランジスタM1aは,ソースは画素電源線Vddに連結され,ドレインは第1ノードA’に連結される。そして,ゲートは第2ノードB’に連結され,第2ノードB’に印加される電圧によって第1ノードA’に電流を供給する。

【0057】

第2トランジスタM2aは,ソースはデータ線Dmに連結され,ドレインは第2ノードBに連結される。そして,ゲートは走査線Snに連結されて走査線Snを介して伝達される走査信号によってデータ信号を第2ノードB’に伝達する。

【0058】

第3トランジスタM3aは,ソースは第1ノードA’に連結され,ドレインはデータ線Dmに連結される。そして,ゲートは走査線Snに連結され,走査線Snを介して伝達される走査信号によって第1トランジスタM1aのソースからドレインに流れる電流が第3トランジスタM3aのソースからドレインに流れるようにする。

【0059】

第1キャパシタC1aは,第1電極は画素電源線Vddに連結され,第2電極は第2ノードB’に連結されてデータ信号に対応する電圧を所定時間の間維持する。

【0060】

第2キャパシタC2aは,第1電極が第2ノードB’に連結され,第2電極はブースト信号線Bnに連結されてブースト信号によって第1トランジスタM1のゲート電圧が変わるようにする。本実施形態において,第1レベルの電圧とは,データ線を介して流れるデータ電流に対応して第1キャパシタC1aに充電される電圧であり,第2レベルの電圧とは,ブースト信号によって第1キャパシタC1aと第2キャパシタC2aに電圧分配が行われた状態でのB’ノードの電圧である。

【0061】

第4トランジスタM4aは,ソースは第1ノードA’に連結され,ドレインは第1発光素子OLED1aに連結される。そして,ゲートは第1発光制御線に連結されて第1発光制御線E1nを介して伝達される第1発光制御信号e1nによって第1トランジスタで生成して第1ノードA’に流れるようにする電流を第1発光素子OLED1aに伝達する。

【0062】

第5トランジスタM5aは,ソースは第1ノードA’に連結され,ドレインは第2発光素子OLED2aに連結される。そして,ゲートは第2発光制御線E2nに連結され,第2発光制御線E2nを介して伝達される第2発光制御線E2nによって第1トランジスタM1aで生成して第1ノードA’に流れるようにする電流を第2発光素子OLED2aに伝達する。

【0063】

図5は,図4に示された画素が採用された発光表示装置に伝達される信号の波形を示す波形図である。

【0064】

図5を参照して説明すれば,画素は走査信号sn,データ信号,ブースト信号bn及び第1及び第2発光制御線e1n及びe2nによって動作する。

【0065】

まず,第1及び第2発光制御線e1n及びe2nが同時にハイ状態である区間内でブースト信号bnがローになり,走査信号snはブースト信号bnがロー状態である区間内でローになる。

【0066】

走査信号snがローになれば,第2トランジスタM2aと第3トランジスタM3aがオン状態になり,第1トランジスタM1aのソースからドレイン方向にデータ電流Idataが流れる。この時,流れるデータ電流によって第1トランジスタM1aのソースとゲートの間の電圧値が変わるようになる。ここで,電圧値を次の数式2に示す。

【0067】

【数2】

【0068】

ここで,Idataは印加されたデータ電流,Vgsは第1トランジスタM1aのソースとゲートの間の電圧,Vthは第1トランジスタM1aのしきい値電圧,βは第1トランジスタM1の利得係数を示す。

【0069】

そして,走査信号snによって第2トランジスタM2aと第3トランジスタM3aがオフ状態になった後,第1発光制御信号Enによって第4トランジスタM4aがオン状態になれば第1トランジスタM1aに流れる電流が第4トランジスタM4aを介して発光素子OLED1aに流れて発光するようになる。

【0070】

上記の場合,第2トランジスタM2aがオフされる時,第1キャパシタC1aと第2キャパシタC2aのカップリングによって第1トランジスタM1aのゲート電圧値が増加するようになる。この場合,増加する電圧値を数式3に示す。

【0071】

【数3】

【0072】

ここで,△Vgは第1キャパシタC1aと第2キャパシタC2aのカップリングによって増加する第1トランジスタM1aのゲートの電圧値,△Vboostはブースト信号の電圧幅を示す。

【0073】

そして,第1発光制御線E1nがロー状態になれば,第4トランジスタM4がオン状態になり,第1発光素子OLED1aに電流が流れる。第1発光素子OLED1aに流れる電流を次の数式4に示す。

【0074】

【数4】

【0075】

ここで,IOLEDは第1発光素子OLED1に流れる電流,Vgsは第1トランジスタM1aにデータ電流が流れる時,第1トランジスタM1aのソースとゲートの間の電圧,△Vgは第1キャパシタC1aと第2キャパシタC2aのカップリングによって増加する第1トランジスタM1aのゲートの電圧値,Vthは第1トランジスタM1aのしきい値電圧,βは第1トランジスタM1aの利得係数を示す。

【0076】

上記数式3と数式4を通じて分かるように,大きいデータ電流として発光素子OLED1aで電流を調節することができる。すなわち,データ線に大きい電流を供給することによって一ライン時間の間,データ線の充電時間を確保することができる。つまり,△Vgが正電圧である場合,数式1のIOLEDより数式4のIOLEDが小さくなる。よってIOLEDにさらに大きい電流を流すためにはIdataの電流を大きくすべきである。Idataの電流を大きくすることにより,データ線を早く充電することができる。

【0077】

また,走査信号とブースト信号がロー信号になって第1発光制御信号と第2発光制御信号がハイ信号になれば,再度画素回路が動作して数式2にあたるデータ電流が生成され,走査信号とブースト信号がハイ信号になって第2発光制御信号がロー信号になれば,第5トランジスタM5aがオン状態になって数式4にあたる電流が第2発光素子OLED2aに流れる。

【0078】

図6は,図3の発光表示装置で採用された画素の第1実施形態を示す回路図である。

【0079】

図6を参照して説明すれば,画素は発光素子と画素回路を含み,一つの画素回路に4個の発光素子OLED1b〜OLED4bが連結されている。各画素回路110は,第1トランジスタ〜第9トランジスタM1b〜M9bと第1キャパシタC1b及び第2キャパシタC2bを含む。

【0080】

画素回路は,駆動回路111b,第1スイッチング回路112b及び第2スイッチング回路113bに区分され,駆動回路111bは第1〜第3トランジスタM1b〜M3bと,第1及び第2キャパシタC1b及びC2bを含み,第1スイッチング回路112bは第4トランジスタ〜第6トランジスタM4b〜M6bを含み,第2スイッチング回路113bは第7トランジスタ〜第9トランジスタM7b〜M9bを含む。

【0081】

第1〜第5トランジスタM1b〜M5b及び第7及び第8トランジスタM7b,M8bは,PMOS形態のトランジスタに具現され,第6及び第9トランジスタM6b及びM9bはNMOS形態のトランジスタに具現される。

【0082】

それぞれのトランジスタのソースとドレインは物理的な差がなく,第1電極と第2電極と称することができる。また,第1キャパシタC1b及び第2キャパシタC2bは,第1電極と第2電極を具備する。そして,4個の発光素子は第1〜第4発光素子OLED1b〜OLED4bと称する。

【0083】

第1トランジスタM1bは,ソースは画素電源線Vddに連結され,ドレインは第1ノードA’’に連結される。そして,ゲートは第2ノードB’’に連結されて第2ノードB’’に印加される電圧によって第1ノードA’’に電流を供給する。

【0084】

第2トランジスタM2bは,ソースはデータ線Dmに連結され,ドレインは第2ノードB’’に連結される。そして,ゲートは走査線Snに連結されて走査線Snを介して伝達される走査信号によってデータ信号を第2ノードB’’に伝達する。

【0085】

第3トランジスタM3bは,ソースは第1ノードA’’に連結され,ドレインはデータ線Dmに連結される。そして,ゲートは走査線Snに連結されて走査線Snを介して伝達される走査信号によって第1トランジスタM1bのソースからドレインに流れる電流が第3トランジスタM3bのソースからドレインに流れるようにする。

【0086】

第1キャパシタC1bは,第1電極は画素電源線Vddに連結され,第2電極は第2ノードB’’に連結されてデータ信号に対応される電圧を所定時間の間維持する。

【0087】

第2キャパシタC2bは,第1電極が第2ノードB’’に連結され,第2電極はブースト信号線Bnに連結され,ブースト信号bnによって第1トランジスタM1bのゲート電圧を高める。本実施形態において,第1レベルの電圧とは,データ線を介して流れるデータ電流に対応して第1キャパシタC1bに充電される電圧であり,第2レベルの電圧とは,ブースト信号によって第1キャパシタC1bと第2キャパシタC2bに電圧分配が行われた状態でのB’’ノードの電圧である。

【0088】

第4トランジスタM4bは,ソースは第1ノードA’’に連結され,ドレインは第3ノードC’’に連結され,ゲートは第1発光制御線E1nに連結されて第1発光制御線E1nを介して伝達される第1発光制御線E1nによって第1ノードA’’に流れる電流を選択的に第3ノードC’’に伝達する。

【0089】

第5トランジスタM5bは,ソースは第1ノードA’’に連結され,ドレインは第4ノードD’’に連結され,ゲートは第2発光制御線E2nに連結されて第2発光制御線E2nを介して伝達される第2発光制御線E2nによって第2ノードB’’に流れる電流を選択的に第4ノードD’’に伝達する。

【0090】

第6トランジスタM6bは,ソースは第3ノードC’’に連結され,ドレインは第1発光素子OLED1bに連結される。そして,ゲートは第3発光制御線E3nに連結されて第3発光制御線E3nを介して伝達される第3発光制御信号e3nによって第3ノードC’’に伝達された電流を選択的に第1発光素子OLED1bに伝達する。

【0091】

第7トランジスタM7bは,ソースは第3ノードC’’に連結され,ドレインは第2発光素子OLED2bに連結される。そして,ゲートは第3発光制御線E3nに連結されて第3発光制御線E3nを介して伝達される第3発光制御線E3nによって第3ノードC’’に伝達された電流を選択的に第2発光素子OLED2bに伝達する。

【0092】

第6トランジスタM6bは,NMOS形態のトランジスタであり,第7トランジスタM7bはPMOS形態のトランジスタなので,第3発光制御信号e3nは第6トランジスタM6bと第7トランジスタM7bのうち一つのトランジスタがオン状態になる。よって第1発光素子OLED1bと第2発光素子OLED2bのうち一つの発光素子を選択して発光させる。

【0093】

第8トランジスタM8bは,ソースは第4ノードD’’に連結され,ドレインは第3発光素子OLED3に連結される。そして,ゲートは第3発光制御線E3nに連結されて第3発光制御線E3nを介して伝達される第3発光制御線E3nによって第4ノードD’’に伝達された電流を選択的に第3発光素子OLED3bに伝達する。

【0094】

第9トランジスタM9bは,ソースは第4ノードD’’に連結され,ドレインは第4発光素子OLED4bに連結される。そして,ゲートは第3発光制御線E3nに連結されて第3発光制御線E3nを介して伝達される第3発光制御線E3nによって第4ノードD’’に伝達された電流を選択的に第4発光素子OLED4bに伝達する。

【0095】

第8トランジスタM8bは,PMOS形態のトランジスタであり,第9トランジスタM9bは,NMOS形態のトランジスタなので,第3発光制御信号e3nは第8トランジスタM8bと第9トランジスタM9bのうち一つのトランジスタがオン状態になる。よって第3発光素子OLED3bと第4発光素子OLED4bのうち一つの発光素子を選択して発光させる。

【0096】

図7は,図6に示された画素が採用された発光表示装置に伝達する信号の波形を示す波形図である。

【0097】

図7を参照して説明すれば,画素は走査信号sn,データ信号,ブースト信号bn及び第1〜第3発光制御信号e1n〜e3nによって動作する。

【0098】

第1区間Td1は,第1発光制御信号e1nがロー状態で,第2発光制御信号e1n及び第3発光制御信号e3nがハイ状態であり,第2区間Td2は,第1発光制御信号e1nと第3発光制御信号e3nハイ状態で,第2発光制御信号e2nがロー状態であり,第3区間Td3は,第1発光制御信号e1nと第3発光制御信号e3nがロー状態で,第2発光制御信号e2nはハイ状態である。また,第4区間Td4では,第1発光制御信号e1nはハイ状態で,第2発光制御信号e2nと第3発光制御信号e3nはロー状態であり,走査信号snは順次各区間の開始時点でしばらくロー状態になり,ブースト信号bnは走査信号snがロー状態である時点でロー状態になる。

【0099】

まず,第1区間Td1で第1発光制御信号e1nと第3発光制御信号e3nによって,上記数式4に記載された電流が第1発光素子OLED1bで流れるようになり,第2区間T2では第2発光制御信号e2nと第3発光制御信号e3nによって上記数式4に記載された電流が第4発光素子OLED4bに流れるようになり,第3区間Td3では第1発光制御信号e1nと第3発光制御信号e3nによって第2発光素子OLED2bに上記数式4に記載された電流が流れるようになる。また,第4区間Td4では第2発光制御信号e2nと第3発光制御信号e3nによって第3発光素子OLED3bに上記数式4に記載された電流が流れるようになる。

【0100】

上記図2〜図7に示されているように,電流を利用して第1トランジスタM1a,M1bのソースとゲート間の電圧を調節して発光させる場合には,電流が充電される時間が必要であり,一つの画素回路に一つの発光素子が連結されている場合に比べ,一つの画素回路に2個の発光素子が連結されている場合は発光する時間が1/2になり,4個の発光素子が連結されている場合は発光する時間が1/4に減る。

【0101】

したがって,発光する時間が減少することによって一つの画素回路に流れる電流と同一の電流が流れるようになれば,輝度が下がるようになり,2個の発光素子または4個の発光素子を発光させるためには2倍または4倍の電流が流れるようにし,これによって電流が大きくなれば電流が一つの画素回路に充電される時間が短くなり,特に低階調を表現する場合には,少ない電流量を持って表現するのでさらに好ましい。つまり,高階調を表現する場合には流れる電流量が大きいため,データ線を充電する時間が問題にならないが,低階調を表現する場合,輝度が低く,発光素子に流れる電流量が高階調に比べて小さくなり,画素回路に充電する時間は,高階調に比べて長くなる。よって従来技術に比較すると本実施形態では,大きい電流をデータ信号として使用するので,画素回路に充電される時間が従来より短くなる。

【0102】

図8a〜図8dは,図6に示された発光表示装置において発光過程を示す図である。

【0103】

画像表示部100bは,3個の画素回路が垂直配列され,12個の発光素子が2×6の形態に配列される。そして上位にある画素回路を第1画素回路とし,中央にある画素回路を第2画素回路,下位にある画素回路を第3画素回路とする。

【0104】

図8a〜図8dを参照して説明すれば,1フレームの間4個の発光素子が順次発光するので,1フレームの時間を4個のサブフィールドに分けることができる。

【0105】

第1画素回路は,第3発光制御信号e3nの伝達を受けてスイッチング動作をする第6トランジスタM6bと第9トランジスタM9bがNMOS形態のトランジスタに具現され,第7トランジスタM7bと第8トレジストM8bがPMOS形態のトランジスタに具現される。

【0106】

そして,第2画素回路は,第6トランジスタM6bと第9トランジスタM9bがPMOS形態のトランジスタに具現され,第7トランジスタM7bと第8トレジストM8bがNMOS形態のトランジスタに具現される。

【0107】

また,第3画素回路は,第6トランジスタM6bと第9トランジスタM9bがNMOS形態のトランジスタに具現され,第7トランジスタM7bと第8トレジストM8bがPMOS形態のトランジスタに具現される。そして,各画素回路の第1発光素子OLED1bと第3発光素子OLED3bは,赤データ信号の伝達を受けて発光し,第2発光素子OLED2bと第4発光素子OLED4bは緑データ信号の伝達を受けて発光する。

【0108】

したがって,図8aは4個のサブフィールドの中で第1サブフィールドを示すものであり,図8aに示されているように第1画素回路は,第6トランジスタM6bに連結されている第1発光素子OLED1bが発光をし,第2画素回路は第7トランジスタM7bに連結されている第2発光素子OLED2bが発光し,第3画素回路は第6トランジスタM6bに連結されている第1発光素子OLED1bが発光する。

【0109】

したがって,第1サブフィールドでは第1画素回路と第3画素回路に連結されている第1発光素子OLED1bが発光し,第2画素回路に連結されている第2発光素子OLED2bが発光して赤と緑が同時に発光するようにする。

【0110】

そして,第2サブフィールドを示す図8bは,第1画素回路は第9トランジスタM9bに連結されている第4発光素子OLED4bが発光し,第2画素回路は第8トランジスタM8bに連結されている第3発光素子OLED3bが発光し,第3画素回路は第7トランジスタM7bに連結されている第4発光素子OLED4bが発光する。

【0111】

したがって,第2サブフィールドでは第1画素回路と第3画素回路に連結されている第4発光素子OLED4bが発光し,第2画素回路と連結されている第3発光素子OLED3bが発光して赤と緑が同時に発光するようになる。

【0112】

また,第3サブフィールドを示す図8cは,第1画素回路は第7トランジスタM7bに連結されている第2発光素子OLED2bが発光し,第2画素回路は第6トランジスタM6bに連結されている第1発光素子OLED1bが発光し,第3画素回路は第7トランジスタM7bに連結されている第2発光素子OLED2bが発光して赤と緑が同時に発光するようになる。

【0113】

最後に,第4サブフィールドを示す図8dは,第1画素回路は第8トランジスタM8bに連結されている第3発光素子OLED3bが発光し,第2画素回路は第9トランジスタM9bに連結されている第4発光素子OLED4bが発光し,第3画素回路は第8トランジスタM8bに連結されている第3発光素子OLED3bが発光して赤と緑が同時に発光するようになる。

【0114】

一つのサブフィールドで一つの色だけが発光する場合に,色分離現象が現われるようになるが,各サブフィールドで赤と緑が同時に発光するようになり,画像表示部全体をよく見れば,赤,緑及び青が各サブフィールドで同時に発光するようになって色分離現象を防止することができる。

【0115】

以上,添付図面を参照しながら本発明の好適な実施形態について説明したが,本発明はかかる例に限定されない。当業者であれば,特許請求の範囲に記載された技術的思想の範疇内において,各種の変更例または修正例に想到し得ることは明らかであり,それらについても当然に本発明の技術的範囲に属するものと了解される。

【0116】

例えば,本実施形態では,1つの駆動回路に対して2個の発光素子(図4),4個の発光素子(図6)について示したが,これと異なる数の発光素子を1つの駆動回路で制御してもよい。

【産業上の利用可能性】

【0117】

本発明は,画素回路及びそれを利用した発光表示装置に適用可能である。

【図面の簡単な説明】

【0118】

【図1】従来の技術による電流書き込み方式の画素が採用されている画像表示部の一部を示す回路図である。

【図2】本発明の第1実施形態にかかる発光表示装置の構造を示す構造図である。

【図3】本発明による発光表示装置の第2実施形態の構造を示す構造図である。

【図4】図2の発光表示装置に採用された画素の第1実施形態を示す回路図である。

【図5】図4に示された画素が採用された発光表示装置に伝達される信号の波形を示す波形図である。

【図6】図3の発光表示装置に採用された画素の第1実施形態を示す回路図である。

【図7】図6に示された画素が採用された発光表示装置に伝達される信号の波形を示す波形図である。

【図8a】図6に示された発光表示装置においての発光過程(第1サブフィールド)を示す図である。

【図8b】図6に示された発光表示装置においての発光過程(第2サブフィールド)を示す図である。

【図8c】図6に示された発光表示装置においての発光過程(第3サブフィールド)を示す図である。

【図8d】図6に示された発光表示装置においての発光過程(第4サブフィールド)を示す図である。

【符号の説明】

【0119】

100 画像表示部

200 データ駆動部

300 走査駆動部

OLED 発光素子

【特許請求の範囲】

【請求項1】

複数の発光素子と;

画素回路と;

を備え,

前記画素回路は,

所定の電流に対応して前記発光素子に流れる駆動電流を生成する駆動回路と;

前記複数の発光素子及び前記駆動回路に連結されて前記駆動電流を前記複数の発光素子に順次伝達するスイッチング回路と;

を有することを特徴とする,画素。

【請求項2】

前記駆動回路は,

ゲートに印加された電圧によって電流を流す第1トランジスタと,

前記走査信号によって選択的に前記第1トランジスタをダイオード連結する第2トランジスタと,

前記走査信号によってデータ電流を前記第1トランジスタに伝達する第3トランジスタと,

前記第1トランジスタに伝達された前記データ電流に対応する第1レベルの電圧を充電する第1キャパシタと,

前記第1キャパシタと直列連結されて前記第1キャパシタに充電されている電圧を第1レベルから第2レベルの電圧に変更させる第2キャパシタと,

を有することを特徴とする,請求項1に記載の画素。

【請求項3】

前記第1スイッチング回路は,第1発光素子に連結されて第1発光制御信号に連結されている第4トランジスタを有し,

前記第2スイッチング回路は,第2発光素子に連結されて第2発光制御信号に連結されている第5トランジスタを有することを特徴とする,請求項1または2のいずれかに記載の画素。

【請求項4】

前記第1発光制御信号及び前記第2発光制御信号は,第1区間及び第2区間を繰り返す周期的な信号であり,

前記第1区間において,前記第1発光制御信号はロー信号であり,前記第2発光制御信号はハイ信号であり,

前記第2区間において,前記第1発光制御信号はハイ信号であり,前記第2発光制御信号はロー信号であることを特徴とする,請求項3に記載の画素。

【請求項5】

前記第1レベルの電圧は,前記第1トランジスタに流れる電流に対応される電圧であることを特徴とする請求項2〜4のいずれかに記載の画素。

【請求項6】

前記第2レベルは,前記第2キャパシタがブースト信号の印加を受け,前記第1キャパシタと前記第2キャパシタによって分圧された電圧であることを特徴とする,請求項2〜5のいずれかに記載の画素。

【請求項7】

前記ブースト信号は,前記第2トランジスタがオン状態の時,前記第2キャパシタに充電される電圧を変動させることを特徴とする,請求項6に記載の画素。

【請求項8】

第1〜第4発光素子と;

画素回路と;

を備え,

前記画素回路は,

所定の電流に対応して前記第1〜第4発光素子に流れる駆動電流を生成する駆動回路と;

前記第1〜第4発光素子及び前記駆動回路間に連結され,前記第1〜第4発光素子の駆動を順次制御するためのスイッチング回路と;を有することを特徴とする,画素。

【請求項9】

前記駆動回路は,

ゲートに印加された電圧によって電流を流れるようにする第1トランジスタと,

前記走査信号によって選択的に前記第1トランジスタをダイオード連結する第2トランジスタと,

前記走査信号によってデータ電流を前記第1トランジスタに伝達する第3トランジスタと,

前記第1トランジスタに伝達された前記データ電流に対応する第1レベルの電圧を充電する第1キャパシタと,

前記第1キャパシタと直列連結されて前記第1キャパシタに充電されている電圧を第1レベルから第2レベルに変更させる第2キャパシタと,

を有することを特徴とする,請求項8に記載の画素。

【請求項10】

前記スイッチング回路は,

前記第1及び第2発光素子の駆動を制御する第1スイッチング回路と,

前記第3及び第4発光素子の駆動を制御する第2スイッチング回路と,

を有し,

前記第1スイッチング回路は,

第1発光制御信号によって前記電流を伝達する第4トランジスタと,

第2発光制御信号によって前記第4トランジスタによって伝達された前記電流を前記第1発光素子に伝達する第5トランジスタと,

前記第3発光制御信号によって前記第5トランジスタと異なる状態を維持し,前記第4トランジスタによって伝達された前記電流を第2発光素子に伝達する第6トランジスタと,を有し,

前記第2スイッチング回路は,

前記第2発光制御信号によって前記電流を伝達する第7トランジスタと,

前記第3発光制御信号によって前記第7トランジスタによって伝達された前記電流を第3発光素子に伝達する第8トランジスタと,

前記第3発光制御信号によって前記第8トランジスタと異なる状態を維持し,前記第7トランジスタによって伝達された前記電流を第4発光素子に伝達する第9トランジスタと,を有することを特徴とする,請求項9に記載の画素。

【請求項11】

前記第1レベルの電圧は,前記第1トランジスタに流れる電流に対応される電圧であることを特徴とする,請求項9に記載の画素。

【請求項12】

前記第2レベルの電圧は,前記第2キャパシタがブースト信号の印加を受け,前記第1キャパシタと前記第2キャパシタによって分圧された電圧であることを特徴とする,請求項9に記載の画素。

【請求項13】

複数の画素を含む画像表示部と;

前記画素にデータ信号を伝達するデータ駆動部と;

前記画素に走査信号と第1〜第3発光制御信号を伝達する走査駆動部と;

を備え,

前記画素は,請求項1〜12のうち,いずれか1項に記載の発光表示装置。

【請求項14】

前記走査駆動部は,ブースト信号をさらに伝達することを特徴とする,請求項13に記載の発光表示装置。

【請求項15】

前記複数の画素のうち,同一のデータ線を介して前記データ信号の伝達を受ける隣接した第1及び第2画素は,第1画素の第1発光素子及び第2発光素子の発光手順と,第2画素の第1発光素子及び第2発光素子の発光手順が異なるように具現され,

前記第1画素の第3発光素子及び第4発光素子の発光手順と第2画素の第3発光素子と第4発光素子の発光手順が異なるように具現されることを特徴とする,請求項13に記載の発光表示装置。

【請求項16】

前記第1〜第3発光制御信号は,第1区間〜第4区間を持つ周期的な信号であり,

前記第1発光制御信号と前記第2発光制御信号は,互いに異なる状態を維持し,各区間でハイ状態とロー状態を繰り返し,

前記第3発光制御信号は,前記第1区間及び前記第2区間は信号に変化のない同じ状態を維持し,前記第3区間及び前記第4区間は信号に変化のない同じ状態を維持し,前記第3区間及び前記第4区間の状態は,前記第1区間及び第2区間の状態を反転させたものであることを特徴とする,請求項13〜15のいずれかに記載の発光表示装置。

【請求項1】

複数の発光素子と;

画素回路と;

を備え,

前記画素回路は,

所定の電流に対応して前記発光素子に流れる駆動電流を生成する駆動回路と;

前記複数の発光素子及び前記駆動回路に連結されて前記駆動電流を前記複数の発光素子に順次伝達するスイッチング回路と;

を有することを特徴とする,画素。

【請求項2】

前記駆動回路は,

ゲートに印加された電圧によって電流を流す第1トランジスタと,

前記走査信号によって選択的に前記第1トランジスタをダイオード連結する第2トランジスタと,

前記走査信号によってデータ電流を前記第1トランジスタに伝達する第3トランジスタと,

前記第1トランジスタに伝達された前記データ電流に対応する第1レベルの電圧を充電する第1キャパシタと,

前記第1キャパシタと直列連結されて前記第1キャパシタに充電されている電圧を第1レベルから第2レベルの電圧に変更させる第2キャパシタと,

を有することを特徴とする,請求項1に記載の画素。

【請求項3】

前記第1スイッチング回路は,第1発光素子に連結されて第1発光制御信号に連結されている第4トランジスタを有し,

前記第2スイッチング回路は,第2発光素子に連結されて第2発光制御信号に連結されている第5トランジスタを有することを特徴とする,請求項1または2のいずれかに記載の画素。

【請求項4】

前記第1発光制御信号及び前記第2発光制御信号は,第1区間及び第2区間を繰り返す周期的な信号であり,

前記第1区間において,前記第1発光制御信号はロー信号であり,前記第2発光制御信号はハイ信号であり,

前記第2区間において,前記第1発光制御信号はハイ信号であり,前記第2発光制御信号はロー信号であることを特徴とする,請求項3に記載の画素。

【請求項5】

前記第1レベルの電圧は,前記第1トランジスタに流れる電流に対応される電圧であることを特徴とする請求項2〜4のいずれかに記載の画素。

【請求項6】

前記第2レベルは,前記第2キャパシタがブースト信号の印加を受け,前記第1キャパシタと前記第2キャパシタによって分圧された電圧であることを特徴とする,請求項2〜5のいずれかに記載の画素。

【請求項7】

前記ブースト信号は,前記第2トランジスタがオン状態の時,前記第2キャパシタに充電される電圧を変動させることを特徴とする,請求項6に記載の画素。

【請求項8】

第1〜第4発光素子と;

画素回路と;

を備え,

前記画素回路は,

所定の電流に対応して前記第1〜第4発光素子に流れる駆動電流を生成する駆動回路と;

前記第1〜第4発光素子及び前記駆動回路間に連結され,前記第1〜第4発光素子の駆動を順次制御するためのスイッチング回路と;を有することを特徴とする,画素。

【請求項9】

前記駆動回路は,

ゲートに印加された電圧によって電流を流れるようにする第1トランジスタと,

前記走査信号によって選択的に前記第1トランジスタをダイオード連結する第2トランジスタと,

前記走査信号によってデータ電流を前記第1トランジスタに伝達する第3トランジスタと,

前記第1トランジスタに伝達された前記データ電流に対応する第1レベルの電圧を充電する第1キャパシタと,

前記第1キャパシタと直列連結されて前記第1キャパシタに充電されている電圧を第1レベルから第2レベルに変更させる第2キャパシタと,

を有することを特徴とする,請求項8に記載の画素。

【請求項10】

前記スイッチング回路は,

前記第1及び第2発光素子の駆動を制御する第1スイッチング回路と,

前記第3及び第4発光素子の駆動を制御する第2スイッチング回路と,

を有し,

前記第1スイッチング回路は,

第1発光制御信号によって前記電流を伝達する第4トランジスタと,

第2発光制御信号によって前記第4トランジスタによって伝達された前記電流を前記第1発光素子に伝達する第5トランジスタと,

前記第3発光制御信号によって前記第5トランジスタと異なる状態を維持し,前記第4トランジスタによって伝達された前記電流を第2発光素子に伝達する第6トランジスタと,を有し,

前記第2スイッチング回路は,

前記第2発光制御信号によって前記電流を伝達する第7トランジスタと,

前記第3発光制御信号によって前記第7トランジスタによって伝達された前記電流を第3発光素子に伝達する第8トランジスタと,

前記第3発光制御信号によって前記第8トランジスタと異なる状態を維持し,前記第7トランジスタによって伝達された前記電流を第4発光素子に伝達する第9トランジスタと,を有することを特徴とする,請求項9に記載の画素。

【請求項11】

前記第1レベルの電圧は,前記第1トランジスタに流れる電流に対応される電圧であることを特徴とする,請求項9に記載の画素。

【請求項12】

前記第2レベルの電圧は,前記第2キャパシタがブースト信号の印加を受け,前記第1キャパシタと前記第2キャパシタによって分圧された電圧であることを特徴とする,請求項9に記載の画素。

【請求項13】

複数の画素を含む画像表示部と;

前記画素にデータ信号を伝達するデータ駆動部と;

前記画素に走査信号と第1〜第3発光制御信号を伝達する走査駆動部と;

を備え,

前記画素は,請求項1〜12のうち,いずれか1項に記載の発光表示装置。

【請求項14】

前記走査駆動部は,ブースト信号をさらに伝達することを特徴とする,請求項13に記載の発光表示装置。

【請求項15】

前記複数の画素のうち,同一のデータ線を介して前記データ信号の伝達を受ける隣接した第1及び第2画素は,第1画素の第1発光素子及び第2発光素子の発光手順と,第2画素の第1発光素子及び第2発光素子の発光手順が異なるように具現され,

前記第1画素の第3発光素子及び第4発光素子の発光手順と第2画素の第3発光素子と第4発光素子の発光手順が異なるように具現されることを特徴とする,請求項13に記載の発光表示装置。

【請求項16】

前記第1〜第3発光制御信号は,第1区間〜第4区間を持つ周期的な信号であり,

前記第1発光制御信号と前記第2発光制御信号は,互いに異なる状態を維持し,各区間でハイ状態とロー状態を繰り返し,

前記第3発光制御信号は,前記第1区間及び前記第2区間は信号に変化のない同じ状態を維持し,前記第3区間及び前記第4区間は信号に変化のない同じ状態を維持し,前記第3区間及び前記第4区間の状態は,前記第1区間及び第2区間の状態を反転させたものであることを特徴とする,請求項13〜15のいずれかに記載の発光表示装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8a】

【図8b】

【図8c】

【図8d】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8a】

【図8b】

【図8c】

【図8d】

【公開番号】特開2006−146168(P2006−146168A)

【公開日】平成18年6月8日(2006.6.8)

【国際特許分類】

【出願番号】特願2005−275852(P2005−275852)

【出願日】平成17年9月22日(2005.9.22)

【出願人】(590002817)三星エスディアイ株式会社 (2,784)

【Fターム(参考)】

【公開日】平成18年6月8日(2006.6.8)

【国際特許分類】

【出願日】平成17年9月22日(2005.9.22)

【出願人】(590002817)三星エスディアイ株式会社 (2,784)

【Fターム(参考)】

[ Back to top ]