異なる絶縁体の側壁スペーサを有するメモリ回路を形成するための方法

本発明はメモリ回路を形成する方法を含んでいる。一つの実施の形態として、メモリアレイ回路領域(14)および周辺回路領域(16)を有する基板(12)を設けている。前記メモリアレイ回路領域は、第一の最小配線間隙(D1)をともなうトランジスタゲート配線(15)を含んでいる。前記周辺回路領域は、前記第一の最小配線間隙よりも大きい第二の最小配線間隙(D2)をともなうトランジスタゲート配線(17)を含んでいる。前記メモリアレイ領域内の個々の前記トランジスタゲート配線の向かいあう側壁上方に異方性エッチングされた絶縁体の側壁スペーサ(40)を形成するよりも先に、前記周辺回路領域内の個々の前記トランジスタゲート配線に向かいあう側壁上に異方性エッチングされた絶縁体の側壁スペーサ(34)を形成している。他の特徴と実施の形態が考えられる。

【発明の詳細な説明】

【技術分野】

【0001】

本発明はメモリ回路を形成する方法に関する。

【背景技術】

【0002】

集積回路の作成は、基板上の導線の形成と関連がある。このような導線は、デバイス素子に接続するあるいはデバイス素子と接続するために使われる。集積回路の一つの形態はメモリ回路である。メモリ回路は、ウェハの空間を節約するために、リソグラフィや他の処理ができるようにできるだけ近接するようにストレージデバイスを作成するメモリアレイ回路領域を一般的に含んでいる。また、メモリ回路は、その空間の必要性がそのメモリアレイにおけるほど重要でない周辺回路を一般的に含んでいる。したがって、多くの例にあるように、周辺回路領域内のデバイスは、一般的にそのメモリアレイ回路領域内のデバイスと比較してかなり離間している。

【0003】

トランジスタゲート配線は一般的にメモリ回路および周辺回路内で用いられる。そのような配線はトランジスタゲート配線の側面を電気的に絶縁する側壁スペーサを一般に含む。そのようなスペーサは、基板上に絶縁物質層を形成してトランジスタゲート配線の側壁周辺にスペーサを残すようにその層を異方性エッチングすることによって設けられる。

【0004】

メモリアレイ内のスペーサの横方向の幅は、隣接するトランジスタゲート配線間の距離が減少するにつれて狭くなり続けている。さらなるいくつかの例として、周辺回路領域内だけでなくメモリアレイ領域内で形成されるトランジスタのソース/ドレイン領域の一部として基礎となる基板物質から単結晶シリコンなどのエピタキシャル半導体物質を成長させている。そのような成長は、一般的にメモリアレイ回路性能を最適にし、そして、周辺回路アレイにおける所望の動作回路を達成するために周辺回路に関する処理の変更が必要である。

【0005】

さらに、そのメモリアレイ回路領域内のスペーサの幅の減少は、そのスペーサとトランジスタゲート間の寄生容量を増加させる好ましくない結果となる。これは個々のトランジスタのスピードおよび/または他の性能特性に不利な影響を与えることになる。一対の導体間の誘電体の厚みを減らすこと、および/または、そのような導体間の誘電体物質の誘電率定数“k”を増やすことによって、その寄生容量は増加される、あるいは、最大化される。周辺回路領域内のそのようなスペーサ等の形成とは、異なるように、あるいは、別々にメモリアレイ回路領域内のトランジスタゲート配線上で異方性エッチングされたスペーサ幅の最適化を可能とするさらなる方法を改良することが望まれている。

【0006】

上記で特定された課題を解決することにおいて本発明は動機づけられたが、それは決してそのように限定されるものではない。本発明は、本明細書に対して解釈的、あるいは、他の制限的参照がなされることなく、伴っている請求項の文字通りの言葉および均等物の原理に従ってのみ限定される。

【発明の開示】

【0007】

本発明はメモリ回路を形成する方法を含んでいる。一つの実施の形態として、メモリアレイ回路領域および周辺回路領域を有する基板を設けている。メモリアレイ回路領域は、第一の最小配線間隙をともなうトランジスタゲート配線を含んでいる。周辺回路領域は、第一の最小配線間隙よりも大きい第二の最小配線間隙をともなうトランジスタゲート配線を含んでいる。メモリアレイ領域内の個々の前記トランジスタゲート配線の向かいあう側壁上に異方性エッチングされた絶縁体の側壁スペーサを形成するよりも先に、周辺回路領

域内の個々の前記トランジスタゲート配線に向かいあう側壁上に異方性エッチングされた絶縁体の側壁スペーサを形成している。

【0008】

一つの実施の形態として、前記周辺回路領域内のトランジスタゲート配線上、および、前記メモリアレイ回路領域内のトランジスタゲート配線間の間隙以外に、異方性エッチングされた絶縁体の側壁スペーサを形成している間は、メモリアレイ回路領域内のトランジスタゲート配線間の間隙をマスクする。また、前記メモリアレイ回路領域内のトランジスタゲート配線上、および、前記周辺回路領域内のトランジスタゲート配線間の間隙以外に、異方性エッチングされた絶縁体の側壁スペーサを形成している間は、前記周辺回路領域内のトランジスタゲート配線間の間隙をマスクする。

【0009】

一つの実施の形態として、前記メモリアレイ回路領域内のトランジスタゲート配線間の間隙内、および、前記周辺回路領域内のトランジスタゲート配線間の間隙以外に、エピタキシャル成長の半導体物質を含む隆起したソース/ドレイン領域を形成する。

【0010】

一つの実施の形態として、前記メモリアレイ回路領域および前記周辺回路領域内のトランジスタゲート配線上に第一の絶縁体のスペーサ物質を形成する。その第一の絶縁体のスペーサ物質上、ならびに、メモリアレイ回路領域および周辺回路領域内のトランジスタゲート配線上、に第二の絶縁体のスペーサ物質を形成する。その第二の絶縁体のスペーサ物質は第一の絶縁体のスペーサ物質に対して選択的にエッチングすることが可能である。その第二の絶縁体のスペーサ物質はメモリアレイ回路領域内のトランジスタゲート配線間の間隙を満たしているが、周辺回路領域内のトランジスタゲート配線間の間隙を満たしていない。周辺回路領域内の個々の前記トランジスタゲート配線の向かいあう側壁上に絶縁体の側壁スペーサを効果的に形成するために第一の絶縁体のスペーサ物質に対して第二の絶縁体のスペーサ物質が選択的に異方性エッチングされる。周辺回路領域内に前記側壁スペーサを形成した後に、周辺回路領域内の前記側壁スペーサをマスクしながら、メモリアレイ回路領域内で第一の絶縁体のスペーサ物質に対して第二の絶縁体のスペーサ物質が選択的にエッチングされる。メモリアレイ回路領域内の個々の前記トランジスタゲート配線の向かいあう側壁上に絶縁体の側壁スペーサを効果的に形成するために第一の絶縁体のスペーサ物質が異方性エッチングされる。

【0011】

他の特徴および実施形態が想定される。

以下に添付してある図面を参照しながら本発明の好適な実施の形態を以下で記載する。

【発明を実施するための最良の形態】

【0012】

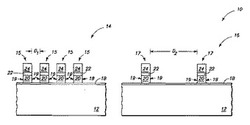

図1〜図16を参照しながら、メモリ回路を形成するための様々な方法の好適な実施の形態の例を記載する。図1では、処理工程の半導体ウェハ断片を参照番号10で一般的に示しており、半導体の基板12を含んでいる。本明細書の記述中では、「半導体基板」あるいは「半導体の基板」という用語を、(単独のもしくはその上にあるその他の物質を含む組立体内におけるどちらかの)半導体ウェハ、(単独のもしくはその他の物質を含んでいる組立体内におけるどちらかの)半導体物質層などのバルク(bulk)半導体物質を含んでいる、しかしながらこれらに限定はされない、半導体物質を含むいかなる構成も意味するように定義している。「基板」と言う用語は、上述した半導体基板を含む、しかしながらこれらに限定はされない、何か支持する構造のことを述べている。基板12の半導体物質の好適な例は、バルク単結晶シリコンであり、もちろん他の基板が想定されるが、例えば絶縁体上に半導体がある基板である。

【0013】

図示されている基板12は、メモリアレイ回路領域14および周辺回路領域16を含んでいる。一つの好適な実施の形態としては、製造されるメモリ回路はDRAM回路を含んでいる。メモリアレイ回路領域を、第一の最小配線間隙D1をともなういくつか複数のト

ランジスタゲート配線15を含むように描いている。周辺回路領域16を、第一の最小配線間隙D1よりも大きい第二の最小配線間隙D2をともなういくつかの複数のトランジスタゲート配線17を含むように描いている。現在の世代での処理における典型的な配線間隙D1は780Åであり、もちろん次世代の処理における間隙の縮小が期待される。現在の世代でのD1の780Åの配線間隙に対するD2の配線間隙の例としては、1500Åから2000Åである。個々のトランジスタゲート配線15および17は、側壁19を有するように考慮されてもよい。

【0014】

図示されているトランジスタゲート配線15および17を、ゲート誘電層18、例えば20Å〜70Åの厚みを有する二酸化シリコン、の上方に形成するように描いている。また、ほんの一例として、導電性を有するドープされた半導体物質領域20(すなわち、ポリシリコン)、より大きい導電性を有する領域22(すなわち、高融点金属および高融点金属シリサイドの一つもしくは両方)、および上を覆っている絶縁キャップ24(すなわち、シリコン窒化物および二酸化シリコンの一つもしくは両方)を含むようにゲート配線15および17を描いている。描図されているトランジスタゲート配線構造15および17を形成するための好適な方法例としては、もちろんいくつか他の方法が考えられるけれども、フォトリソグラフィのパターンニングおよびエッチング、ならびに既知もしくは未知である手法のどちらかによる方法がある。一つの好適な実施の形態の例として、本発明の処理工程が行われるトランジスタゲート配線は浮遊ゲートを有さず、例えば、ここで図示されているゲート配線は層20および22によって形成されている単一の導電性塊を含む。

【0015】

好ましくは、図1の基板は、ソース/ドレイン再酸化がなされるのがよく、さらなる好ましい実施の形態として、各種の導電性変更をする注入物(implants)を受けてもよい。そのような注入物およびその他の処理工程は、一例でありより好ましいだけであり、解析に基づいて請求項として特に記載されているものを除いては本発明の一部を構成するものではない。一般的に好ましくは、メモリアレイ回路のトランジスタは、nチャネルデバイスを含んで製造され、周辺回路領域はnチャネルデバイスおよびpチャネルデバイスの組合体を含んで製造される。一つの好ましい実施の形態として、図1の基板はブランケットLDD注入、例えば、照射量の例として1×1012イオン数/cm2までのヒ素の注入、を行ってもよい。さらに、一つの実施の形態として、pチャネルデバイスをマスクすることでnチャネルデバイスの図1の基板にp型ハロ注入(halo implants)を行ってもよく、さらに、p型ハロ注入は、nチャネルデバイスを最適にするために、照射量の例として1×1014イオン数/cm2でのヒ素を用いた別のLDD注入を含んでもよい。その後段もしくは前段に、同様の処理をpチャネルデバイスに行ってもよい。特に、ハロ領域を形成するためのpチャネルデバイスにリンやヒ素を含む注入を行っている間にnチャネルデバイスをマスクしてもよく、おそらく、pチャネルデバイスのLDD領域を最適にするためにホウ素を含む注入もなされる。

【0016】

図2では、メモリアレイ回路領域14内のトランジスタゲート配線15上および周辺回路領域16内のトランジスタゲート配線17上に 第一の絶縁体のスペーサ物質30を形成している。それらは、メモリアレイ回路領域14内のトランジスタゲート配線15間の空間31、および周辺回路領域16内のトランジスタゲート配線17間の空間33に残る。より好ましい物質の例は、シリコン窒化物、アルミニウム酸化物、およびハフニウム酸化物、ならびに、もちろんそれらの混合物および/または多層を含んでいるもの、の少なくとも一つを含んでいる物質である。スペーサ物質30の好ましい厚さの範囲の例としては、50Å〜好ましくは最小間隙D1の1/3よりも大きくない厚さである。

【0017】

図3では、第一の絶縁体のスペーサ物質30上、および、メモリアレイ回路領域14内のトランジスタゲート配線15上、ならびに、周辺回路領域16内のトランジスタゲート

配線17上、に第二の絶縁体のスペーサ物質32を形成している。第二の絶縁体のスペーサ物質32は、第一の絶縁体のスペーサ物質30に対して都合よく選択的にエッチングすることが可能である。ここで、 第一のスペーサ物質30としては、例えば、シリコン窒化物、アルミニウム酸化物、およびハフニウム酸化物のいずれか一つもしくは複合物を含み、好ましい物質32の例はドープされていない二酸化シリコンである。本明細書の内容において「ドープされていない二酸化シリコン」は、ホウ素およびリンの一つもしくは複合物が1at.%(原子百分率)よりも多くない二酸化シリコン物質と定義している。ドープされていない二酸化シリコン32を堆積するための好ましい手段は、テトラエチルオルトケイ酸塩(TEOS)を使用する手段であり、そしてその結果として、堆積された二酸化シリコンは後述される好ましい選択的なウェットエッチングを容易にするように(その処理工程のこの時点では少なくとも)高濃度化(densify)されない。本明細書の記述中では、「高濃度化されない」ドープされていない二酸化シリコン層は700℃よりも低温で堆積しており、それは後段で或る温度すなわち少なくとも700℃で暴露されない限り、単に“高濃度化されない”状態のままである。描画されている好ましい実施の形態において、第二の絶縁体のスペーサ物質32は、メモリアレイ回路領域14内のトランジスタゲート配線15間の間隙31を効果的に満たす一方で、周辺回路領域16内のトランジスタゲート配線17間の間隙33を満たさないような厚みで堆積される。ほんの一例であるが、物質32の好適な厚みの例は100Å〜500Åである。

【0018】

図4では、周辺回路領域16内の個々のトランジスタゲート配線17の向かいあう側壁19上に絶縁体の側壁スペーサ34を効果的に形成するために第一の絶縁体のスペーサ物質30に対して選択的に第二の絶縁体のスペーサ物質32が異方性エッチングされている。より好ましいエッチング化学物質の例としては、シリコン窒化物上で支持されている二酸化シリコン物質に対して作用するC4F8、CF4、Arを含む。本明細書の記述中においては、少なくとも2:1の除去比で一つの物質に対してもう一方の物質の除去の選択的なエッチングをしている。

【0019】

図5では、周辺回路領域16内の側壁スペーサ34がマスクされている。より好ましくは、周辺回路領域16内のトランジスタゲート配線17間の間隙33をマスクするマスク層36を用いることでそれを行い、さらに好ましくは、周辺回路領域16の全体をマスク層36でマスクすることにより行うとよい。より好ましい物質の例としては、もちろん他の物質も考えられるが、フォトレジストである。

【0020】

図6では、 周辺回路領域16内の物質32である側壁スペーサ34をマスクしながら、メモリアレイ回路領域14内の第一の絶縁体のスペーサ物質30に対して選択的に第二の絶縁体のスペーサ物質32(不図示)をエッチングしている。エッチングの好ましい手段としては、スペーサ物質30がドープされていない二酸化シリコンを含んでおり、スペーサ物質32がシリコン窒化物を含んでいる場合、大気圧および20℃〜100℃の温度範囲で、例えば酸化緩衝剤や希HFのエッチング用化学物質を使用するウェットエッチングを含んでいる。上述においてより好ましく、スペーサ物質がドープされていない二酸化シリコンを含む場合、図6で描かれているように、例え高濃度化されるとしても、第二の絶縁体のスペーサ物質のエッチングの後までは、スペーサ物質が高濃度化されないことがかなり好ましい。

【0021】

図7では、メモリアレイ回路領域14内の個々のトランジスタゲート配線15の向かいあう側壁19上に絶縁体の側壁スペーサ40を効果的に形成するように第一の絶縁体のスペーサ物質30が異方性エッチングされている。そのような異方性エッチングの好ましいエッチング化学物質の例としては、物質30がシリコン窒化物を含んでいる場合、多重ステップエッチング処理(multistep etching process)においてAr、CF4、CH2F2、CHF3、およびO2を用いる多重ステップエッチングを含んでいる。また、図7はメモリ

アレイ回路領域14内の半導体基板12の半導体物質を効果的に露出するための基板12上のゲート誘電体層18の露出部分のエッチングを描いている。描図されたそしてより好ましい例として、周辺回路領域16内の絶縁体の側壁スペーサ34は、メモリアレイ回路領域14内の絶縁体の側壁スペーサ40の最大幅W1よりも大きい最大幅W2を有している。

【0022】

図8では、マスクしている物質36(不図示)を基板10から除去している。

本発明の一つの特徴として、本発明は、メモリアレイ回路領域内の個々のトランジスタゲート配線の向かいあう側壁上に異方性エッチングされた絶縁体の側壁スペーサを形成するよりも先に、周辺回路領域内の個々のトランジスタゲート配線に向かい合う側壁上に異方性エッチングされた絶縁体の側壁スペーサを形成することを含んでいる。上述の工程はそれを行う一つの手段の例であり、勿論、今後開発される方法も含め同様のことを行う何か他の手段を想定できる。

【0023】

さらに、本発明の一つの特徴にしたがってメモリ回路を形成する方法は、処理する順序に依存せず、周辺回路領域内のトランジスタゲート配線上、および、メモリアレイ回路領域内のトランジスタゲート配線間の間隙以外に、異方性エッチングされた絶縁体の側壁スペーサを形成している間に、前記メモリアレイ回路領域内のトランジスタゲート配線間の間隙をマスクすることを含んでいる。一例として、図4は、そのようにする手段の例の一つを描いている。さらに、本発明のこの特徴に従うことに続けて、メモリアレイ回路領域内のトランジスタゲート配線上、および、周辺回路領域内のトランジスタゲート配線間の間隙以外に、異方性エッチングされた絶縁体の側壁スペーサを形成している間に、周辺回路領域内のトランジスタゲート配線間の間隙をマスクしている。ほんの一例として、図7は、そのようにする手段の例の一つを描いている。さらに、上述の好ましい処理としては、周辺回路領域内をマスクする前にメモリアレイ回路領域内のマスクを行っている。逆に、本発明の特徴としては、描かれているスペーサを形成する際にメモリアレイ領域内をマスクするより先に周辺回路領域内をマスクすることも含んでいる。例えば、および、ほんの一例として、スペーサ34の形成よりも先に、描かれている異方性エッチングされたスペーサ40を形成してもよい。

【0024】

さらに、描かれている好ましい実施の形態によらず、周辺回路領域内のスペーサを形成するためのエッチングをしている間にメモリアレイ回路領域内で行われるマスクは、メモリアレイ回路領域内のトランジスタゲート配線間のあらゆる間隙に対してなされる。さらに好ましい実施の形態の一例として、メモリアレイ回路領域内の絶縁体の側壁スペーサを形成するための異方性エッチングをしている間に周辺回路領域内でのマスクが、周辺回路領域内のトランジスタゲート配線間のあらゆる間隙に対してなされる。

【0025】

さらに、好ましい実施の形態の一例として、メモリアレイ回路領域内でのマスクは、周辺回路領域における絶縁体の側壁スペーサが異方的にエッチングされるときの層(すなわち層32)をマスクとして用いることを含んでおり、そしてまた、一つの実施の形態として、メモリアレイ回路領域における絶縁体の側壁スペーサが異方的にエッチングされるときの層(すなわち層30)をマスクとして用いることも含んでいる。

【0026】

さらに、上述の実施の形態の例として、メモリアレイ回路領域内におけるマスクは、フォトレジストを用いておらず、そして、一つの実施の形態として、周辺回路領域内でのマスクはフォトレジストを用いている。

【0027】

メモリアレイ回路領域内にエピタキシャル成長の半導体物質を少なくとも絶縁体の側壁スペーサに隣接するように形成した後で処理をしてもよい。例えば、またほんの一例として、上述および描かれているエッチングならびにスペーサ形成の一連の作業によって図8

のようになり、ここでメモリアレイ回路領域14内の基板12の半導体物質は外界に露出され、周辺回路領域16内の基板12の半導体物質は物質30および18で覆われている。一つの好適な実施の形態として、周辺回路領域16内の絶縁体の側壁スペーサ36に隣接するエピタキシャル成長の半導体物質の成長が行われない間に、メモリアレイ回路領域14内の絶縁体の側壁スペーサ40に隣接するエピタキシャル成長の半導体物質を成長させるためにそのようなことを有効に用いてもよい。例えばそのような例として、図8における基板に、エピタキシャル成長の半導体物質の成長より先に、洗浄ステップ、例えば温度27℃および大気圧下で60秒間より短時間のHF溶液への暴露、を課すことが好ましい。HF溶液の例としては、水と49wt.%HF水溶液とが100:1の体積比のものである。

【0028】

図9では、半導体基板12の半導体物質からエピタキシャル成長の半導体物質44を成長させている。好ましい材料の一例は、エピタキシャル成長の単結晶シリコンであり、ここで、そのような成長をさせる基礎となる物質は単結晶シリコンを含んでいる。他の半導体物質が勿論考えられ、例えばそのほんの一例としては、ガリウムとシリコンの合金である。シリコン以外の材料も勿論考えられる。基礎となる基板からの物質44の厚みの例としては、200Å〜600Åである。単結晶シリコンのそのようなエピタキシャル成長の半導体物質44を成長させるための方法の例としては、シランに基づく選択的なエピタキシャル成長を含む。

【0029】

図10では、周辺回路領域16で露出している物質30、および、その後に露出する物質18をエッチングしている。

図11において、アレイおよび周辺回路に対して所望の最も高いインプラント投与量のソース/ドレイン領域45を形成するために適切にインプラントドーピングを行っている。そのようなことは、マスクおよび/またはインプラントステップのいくつかの組み合わせによって、そして、周辺回路領域内の一般的なpチャネルデバイスおよびnチャネルデバイスを作成するためのいくつかの手順の例の中で、かつ、ドーピング物質44および直下の基板に対して行ってよい。さらに、そのようなものの形成およびインプラントならびにマスクは、ソース/ドレイン領域上の物質30および18の好ましい除去に関連するいくつかの手順中に行ってもよい。

【0030】

メモリ回路を形成する好ましい方法の一例としては、上述のような例、および、ほんの一例として、本発明の特徴は、例えば図9で示されているように、メモリアレイ回路領域内のトランジスタゲート配線間の間隙31内、および、周辺回路領域内のトランジスタゲート間の間隙33以外にエピタキシャル成長の半導体物質を含む隆起したソース/ドレイン領域を形成することができる。一つの好ましい例および実施例(ならびに示されているような例)として、エピタキシャル成長の半導体物質は、例えば図9で描かれている断面のように少なくとも一つの断面のメモリアレイ回路領域内のトランジスタゲート配線間の間隙(すなわち、間隙31)に及んでいる。本発明の特徴は、スペーサの形成と独立したこのようなエピタキシャル成長の半導体物質の作成、およびエピタキシャル成長の半導体物質の成長と独立したスペーサの上述したような作成を含んでいる。本発明の特徴は、また、当業者によって選択され最適にすることができるように、他の物質と同じ、もしくは、他の物質よりも大きいあるいは小さい“k”の静電容量値であるような異なるスペーサ物質を形成することも含んでいる。

【0031】

上述されているインプラントの例としては、当業者が正しく理解しているように、マスクがされていないもしくはされていなくとも、いつでも行うことができる。ほんの一例として、そして限定するわけではないが、上述の工程の全体もしくは一部は、与えられるon/offのターゲット電流に対する速度性能の向上をともない、様々なトランジスタに対し寄生容量を減らすことを可能にすることができる。好ましい処理によって、メモリアレイ回

路領域もしくは周辺回路領域内のどちらかでエピタキシャルシリコンの選択的形成をも可能とすることができる。さらに、周辺回路領域に対してメモリアレイ回路領域内でスペーサ幅を最適にするようにそのような処理を用いることができる。さらに、ほんの一例として、間隙をつくっているより厚みのある周辺回路領域のスペーサは、ソース/ドレインインプラントをさらに周辺のチャネルから離すことを可能とし、また、p+接点がそれらの下方にあるより深いソース/ドレイン接合点を有することができる。

【0032】

図12は、DRAMメモリセルの内部に組み込まれているトランジスタゲート配線15の一つを描いている。エピタキシャル半導体物質44は、DRAMメモリトランジスタ90のソース/ドレイン領域を含んでいる。ソース/ドレイン領域の一方はストレージデバイス150と電気的に接続してあり、ソース/ドレイン領域の他方はビットライン152に電気的に接続してある。ストレージデバイス150は、例えばキャパシタを含んでいる、いくつかの適するデバイスを含むことができる。ビットライン152は、いくつかの適した構成を含むことができる。特徴/トランジスタ(Feature/transistor)90を集積回路、例えばここで述べているDRAM集積回路、の部分として考えることができる。

【0033】

図13は、一つの例として、しかし限定するわけではないが、本発明の特徴に準じているコンピュータシステム400の実施形態を一般化して描いている。コンピュータシステム400は、モニタ401またはその他のコミュニケーション出力デバイス、キーボード402またはその他のコミュニケーション入力デバイス、ならびにマザーボード404を含んでいる。マザーボード404は、マイクロプロセッサ406またはその他のデータ処理装置、ならびに少なくとも一つのメモリデバイス408を搭載することができる。メモリデバイス408は、例えば、一つもしくはそれ以上のワードライン、ビットラインならびにDRAMユニットセルを含んでいる上述の本発明の様々な特徴を含むことができる。メモリデバイス408は、メモリセルのアレイを含むことができ、そして、そのようなアレイをアレイの中の個々のメモリセルにアクセスするためのアドレス回路と接続することができる。さらに、メモリセルアレイを、メモリセルからデータを読み込むための読み込み回路に接続することができる。アドレス回路および読み込み回路をメモリデバイス408およびプロセッサ406間の情報の伝達を行うために使用することができる。それらを図14で示されているマザーボード404のブロック図で描いている。そのブロック図では、アドレス回路を410として描いており、読み込み装置を412として描いている。

【0034】

特に本発明の特徴として、メモリデバイス408がメモリモジュールに相当することもある。例えば、シングルインラインメモリモジュール(シム:SIMM)およびディアルインラインメモリモジュール(ディム:DIMM)を本発明で教示していることを用いている実施の形態の中で用いることができる。デバイスのメモリセルからの読み込みおよびメモリセルへの書き込みに関して異なる方法を与えるいくつかの多様な設計を本メモリデバイスに施すことができる。そのような方法の一つは、ページモード制御(page mode operation)である。メモリセルアレイの行にアクセスする方法、およびアレイの異なる列に無作為にアクセスするための方法としてDRAMにおけるページモード制御を定義している。行および列の交差部に蓄積されているデータを列にアクセスしている間に読み込んで出力することができる。

【0035】

デバイスの一つの代替物としては、アドレスされた列が閉じられた後の出力としてメモリアレイアドレスで蓄積されたデータを使用することができる拡張データ出力(EDO)メモリがある。このメモリはメモリバス上でメモリ出力データを取得する時間を遅くすることなく、より短いアクセス信号とすることができるのでいくつかの接続速度を向上させることができる。デバイスの他の代替物の種類としては、ほんの一例ではあるけれども、SRAMまたはフラッシュメモリなどの他の物品のみならずSDRAM、DDR SDRAM、SLDRAM、VRAMおよびDirect RDRAMを含む。

【0036】

図15は、本発明の電気制御系の例700における多様な実施形態のハイレベル構成を単純化したブロック図を描いている。制御系700は、例えば、コンピュータシステム、処理制御系、あるいはプロセッサおよび関連するメモリを備えているいくつか他の制御系に相当することもある。電気制御系700は、プロセッサまたは演算/論理部(ALU)702、制御部704、メモリデバイス部706および入力/出力(I/O)デバイス708を含めた機能を有する構成要素を有している。一般的に、電気制御系700は、プロセッサ702、ならびに、プロセッサ702、メモリデバイス部706およびI/Oデバイス708間のその他の相互関連物によってデータでやりとりするための演算を特定するネィティブな一組の命令を有する。制御部704は、メモリデバイス706からフェッチされ、実行される命令によって生じる一組の演算をとおした連続的なサイクルによってプロセッサ702、メモリデバイス部706およびI/Oデバイス708の全ての制御を調整している。様々な実施の形態として、メモリデバイス706は、限定する訳ではないが、ランダムアクセスメモリ(RAM)デバイス、読み込み専用メモリ(ROM)デバイス、およびフロッピーディスクドライブおよびコンパクトディスクCD-ROMドライブなどの周辺デバイスを含む。当業者は、本明細書を読み理解した上で、本発明の様々な特徴に準じているDRAMセル、ワードラインおよびビットラインを含むようにいくつかの描かれている電気的な構成物を作成することが可能であることを理解できる。

【0037】

図16は、電気制御系の例800における多様な実施形態のハイレベル構成を単純化したブロック図である。そのシステム800は、メモリセル804のアレイ、アドレスデコーダ806、行アクセス回路808、列アクセス回路810、動作を制御するための読み込み/書き込み制御回路812、および入力/出力回路814を有するメモリデバイス802を含んでいる。メモリデバイス802は、電力回路816、およびメモリセルが低閾値稼働状態にあるか、もしくは、高閾値非稼働状態にあるかどうかを決定するための電流センサーなどのセンサー820をさらに含んでいる。図示されている電力回路816は、電源回路880、参照電圧を供給するための回路882、第一のワードラインにパルスを供給するための回路884、第ニのワードラインにパルスを供給するための回路886、およびビットラインにパルスを供給するための回路888を含んでいる。また、制御系800は、プロセッサ822またはメモリアクセスをするためのメモリコントローラも含んでいる。

【0038】

メモリデバイス802は、ワイヤー配線または金属(matallization)配線を介してプロセッサ822からの制御信号824を受信する。メモリデバイス802は、I/O配線を介してアクセスされるデータを蓄積するために使用される。付加回路および制御信号を供給できることと、メモリデバイス802が本発明における理解を助けるために単純化されていることは当業者によって正しく理解することができる。プロセッサ822もしくはメモリデバイス802の少なくとも一つは、本開示において前述した形態のDRAMセルを含むことができる。

【0039】

本開示中の様々に図示されている制御系は、本発明の回路と構造の様々な用途に関する一般的な理解を与えることを意図しており、本発明の特徴に準じているメモリセルを用いている電気制御系の全ての構成要素および特徴が完全な記載どおりに提供されることを意図していない。当業者は、プロセッサおよびメモリデバイス(群)間の接続時間を短縮するために単一パッケージの制御部の中、もしくは、同様の単一の半導体チップ上で様々な電気制御系を作成できるということが理解できる。

【0040】

メモリセル、ワードラインおよびビットラインの用途としては、メモリモジュール、デバイスドライバ、パワーモジュール、接続モデム、プロセッサモジュール、およびアプリケーション用の特定のモジュールに使用するための電気制御系を含んでおり、そして、多

層モジュール、マルチチップモジュールを含んでいてもよい。そのような回路は、さらに、時計、テレビ、携帯電話、パーソナルコンピュータ、自動車、産業用制御系、航空機、およびその他の機器等の多様な電気制御系の補完的な構成要素であってもよい。

【図面の簡単な説明】

【0041】

【図1】本発明の特徴に従う処理工程における基板断片の概略図である。

【図2】図1によって描かれている処理の後段の処理ステップでの図1の基板断片の図である。

【図3】図2によって描かれている処理の後段の処理ステップでの図2の基板断片の図である。

【図4】図3によって描かれている処理の後段の処理ステップでの図3の基板断片の図である。

【図5】図4によって描かれている処理の後段の処理ステップでの図4の基板断片の図である。

【図6】図5によって描かれている処理の後段の処理ステップでの図5の基板断片の図である。

【図7】図6によって描かれている処理の後段の処理ステップでの図6の基板断片の図である。

【図8】図8は、図7によって描かれている処理の後段の処理ステップでの図7の基板断片の図である。

【図9】図8によって描かれている処理の後段の処理ステップでの図8の基板断片の図である。

【図10】図9によって描かれている処理の後段の処理ステップでの図9の基板断片の図である。

【図11】図10によって描かれている処理の後段の処理ステップでの図10の基板断片の図である。

【図12】本発明の特徴に従って処理している基板の図である。

【図13】本発明の応用例として描いているコンピュータの概略図である。

【図14】図15のコンピュータのマザーボードの特定の特徴を示しているブロック図である。

【図15】本発明の例示的特徴に従う電子システムのハイレベルブロック図である。

【図16】本発明の特徴に従う例示的電子システムの簡略化したブロック図である。

【技術分野】

【0001】

本発明はメモリ回路を形成する方法に関する。

【背景技術】

【0002】

集積回路の作成は、基板上の導線の形成と関連がある。このような導線は、デバイス素子に接続するあるいはデバイス素子と接続するために使われる。集積回路の一つの形態はメモリ回路である。メモリ回路は、ウェハの空間を節約するために、リソグラフィや他の処理ができるようにできるだけ近接するようにストレージデバイスを作成するメモリアレイ回路領域を一般的に含んでいる。また、メモリ回路は、その空間の必要性がそのメモリアレイにおけるほど重要でない周辺回路を一般的に含んでいる。したがって、多くの例にあるように、周辺回路領域内のデバイスは、一般的にそのメモリアレイ回路領域内のデバイスと比較してかなり離間している。

【0003】

トランジスタゲート配線は一般的にメモリ回路および周辺回路内で用いられる。そのような配線はトランジスタゲート配線の側面を電気的に絶縁する側壁スペーサを一般に含む。そのようなスペーサは、基板上に絶縁物質層を形成してトランジスタゲート配線の側壁周辺にスペーサを残すようにその層を異方性エッチングすることによって設けられる。

【0004】

メモリアレイ内のスペーサの横方向の幅は、隣接するトランジスタゲート配線間の距離が減少するにつれて狭くなり続けている。さらなるいくつかの例として、周辺回路領域内だけでなくメモリアレイ領域内で形成されるトランジスタのソース/ドレイン領域の一部として基礎となる基板物質から単結晶シリコンなどのエピタキシャル半導体物質を成長させている。そのような成長は、一般的にメモリアレイ回路性能を最適にし、そして、周辺回路アレイにおける所望の動作回路を達成するために周辺回路に関する処理の変更が必要である。

【0005】

さらに、そのメモリアレイ回路領域内のスペーサの幅の減少は、そのスペーサとトランジスタゲート間の寄生容量を増加させる好ましくない結果となる。これは個々のトランジスタのスピードおよび/または他の性能特性に不利な影響を与えることになる。一対の導体間の誘電体の厚みを減らすこと、および/または、そのような導体間の誘電体物質の誘電率定数“k”を増やすことによって、その寄生容量は増加される、あるいは、最大化される。周辺回路領域内のそのようなスペーサ等の形成とは、異なるように、あるいは、別々にメモリアレイ回路領域内のトランジスタゲート配線上で異方性エッチングされたスペーサ幅の最適化を可能とするさらなる方法を改良することが望まれている。

【0006】

上記で特定された課題を解決することにおいて本発明は動機づけられたが、それは決してそのように限定されるものではない。本発明は、本明細書に対して解釈的、あるいは、他の制限的参照がなされることなく、伴っている請求項の文字通りの言葉および均等物の原理に従ってのみ限定される。

【発明の開示】

【0007】

本発明はメモリ回路を形成する方法を含んでいる。一つの実施の形態として、メモリアレイ回路領域および周辺回路領域を有する基板を設けている。メモリアレイ回路領域は、第一の最小配線間隙をともなうトランジスタゲート配線を含んでいる。周辺回路領域は、第一の最小配線間隙よりも大きい第二の最小配線間隙をともなうトランジスタゲート配線を含んでいる。メモリアレイ領域内の個々の前記トランジスタゲート配線の向かいあう側壁上に異方性エッチングされた絶縁体の側壁スペーサを形成するよりも先に、周辺回路領

域内の個々の前記トランジスタゲート配線に向かいあう側壁上に異方性エッチングされた絶縁体の側壁スペーサを形成している。

【0008】

一つの実施の形態として、前記周辺回路領域内のトランジスタゲート配線上、および、前記メモリアレイ回路領域内のトランジスタゲート配線間の間隙以外に、異方性エッチングされた絶縁体の側壁スペーサを形成している間は、メモリアレイ回路領域内のトランジスタゲート配線間の間隙をマスクする。また、前記メモリアレイ回路領域内のトランジスタゲート配線上、および、前記周辺回路領域内のトランジスタゲート配線間の間隙以外に、異方性エッチングされた絶縁体の側壁スペーサを形成している間は、前記周辺回路領域内のトランジスタゲート配線間の間隙をマスクする。

【0009】

一つの実施の形態として、前記メモリアレイ回路領域内のトランジスタゲート配線間の間隙内、および、前記周辺回路領域内のトランジスタゲート配線間の間隙以外に、エピタキシャル成長の半導体物質を含む隆起したソース/ドレイン領域を形成する。

【0010】

一つの実施の形態として、前記メモリアレイ回路領域および前記周辺回路領域内のトランジスタゲート配線上に第一の絶縁体のスペーサ物質を形成する。その第一の絶縁体のスペーサ物質上、ならびに、メモリアレイ回路領域および周辺回路領域内のトランジスタゲート配線上、に第二の絶縁体のスペーサ物質を形成する。その第二の絶縁体のスペーサ物質は第一の絶縁体のスペーサ物質に対して選択的にエッチングすることが可能である。その第二の絶縁体のスペーサ物質はメモリアレイ回路領域内のトランジスタゲート配線間の間隙を満たしているが、周辺回路領域内のトランジスタゲート配線間の間隙を満たしていない。周辺回路領域内の個々の前記トランジスタゲート配線の向かいあう側壁上に絶縁体の側壁スペーサを効果的に形成するために第一の絶縁体のスペーサ物質に対して第二の絶縁体のスペーサ物質が選択的に異方性エッチングされる。周辺回路領域内に前記側壁スペーサを形成した後に、周辺回路領域内の前記側壁スペーサをマスクしながら、メモリアレイ回路領域内で第一の絶縁体のスペーサ物質に対して第二の絶縁体のスペーサ物質が選択的にエッチングされる。メモリアレイ回路領域内の個々の前記トランジスタゲート配線の向かいあう側壁上に絶縁体の側壁スペーサを効果的に形成するために第一の絶縁体のスペーサ物質が異方性エッチングされる。

【0011】

他の特徴および実施形態が想定される。

以下に添付してある図面を参照しながら本発明の好適な実施の形態を以下で記載する。

【発明を実施するための最良の形態】

【0012】

図1〜図16を参照しながら、メモリ回路を形成するための様々な方法の好適な実施の形態の例を記載する。図1では、処理工程の半導体ウェハ断片を参照番号10で一般的に示しており、半導体の基板12を含んでいる。本明細書の記述中では、「半導体基板」あるいは「半導体の基板」という用語を、(単独のもしくはその上にあるその他の物質を含む組立体内におけるどちらかの)半導体ウェハ、(単独のもしくはその他の物質を含んでいる組立体内におけるどちらかの)半導体物質層などのバルク(bulk)半導体物質を含んでいる、しかしながらこれらに限定はされない、半導体物質を含むいかなる構成も意味するように定義している。「基板」と言う用語は、上述した半導体基板を含む、しかしながらこれらに限定はされない、何か支持する構造のことを述べている。基板12の半導体物質の好適な例は、バルク単結晶シリコンであり、もちろん他の基板が想定されるが、例えば絶縁体上に半導体がある基板である。

【0013】

図示されている基板12は、メモリアレイ回路領域14および周辺回路領域16を含んでいる。一つの好適な実施の形態としては、製造されるメモリ回路はDRAM回路を含んでいる。メモリアレイ回路領域を、第一の最小配線間隙D1をともなういくつか複数のト

ランジスタゲート配線15を含むように描いている。周辺回路領域16を、第一の最小配線間隙D1よりも大きい第二の最小配線間隙D2をともなういくつかの複数のトランジスタゲート配線17を含むように描いている。現在の世代での処理における典型的な配線間隙D1は780Åであり、もちろん次世代の処理における間隙の縮小が期待される。現在の世代でのD1の780Åの配線間隙に対するD2の配線間隙の例としては、1500Åから2000Åである。個々のトランジスタゲート配線15および17は、側壁19を有するように考慮されてもよい。

【0014】

図示されているトランジスタゲート配線15および17を、ゲート誘電層18、例えば20Å〜70Åの厚みを有する二酸化シリコン、の上方に形成するように描いている。また、ほんの一例として、導電性を有するドープされた半導体物質領域20(すなわち、ポリシリコン)、より大きい導電性を有する領域22(すなわち、高融点金属および高融点金属シリサイドの一つもしくは両方)、および上を覆っている絶縁キャップ24(すなわち、シリコン窒化物および二酸化シリコンの一つもしくは両方)を含むようにゲート配線15および17を描いている。描図されているトランジスタゲート配線構造15および17を形成するための好適な方法例としては、もちろんいくつか他の方法が考えられるけれども、フォトリソグラフィのパターンニングおよびエッチング、ならびに既知もしくは未知である手法のどちらかによる方法がある。一つの好適な実施の形態の例として、本発明の処理工程が行われるトランジスタゲート配線は浮遊ゲートを有さず、例えば、ここで図示されているゲート配線は層20および22によって形成されている単一の導電性塊を含む。

【0015】

好ましくは、図1の基板は、ソース/ドレイン再酸化がなされるのがよく、さらなる好ましい実施の形態として、各種の導電性変更をする注入物(implants)を受けてもよい。そのような注入物およびその他の処理工程は、一例でありより好ましいだけであり、解析に基づいて請求項として特に記載されているものを除いては本発明の一部を構成するものではない。一般的に好ましくは、メモリアレイ回路のトランジスタは、nチャネルデバイスを含んで製造され、周辺回路領域はnチャネルデバイスおよびpチャネルデバイスの組合体を含んで製造される。一つの好ましい実施の形態として、図1の基板はブランケットLDD注入、例えば、照射量の例として1×1012イオン数/cm2までのヒ素の注入、を行ってもよい。さらに、一つの実施の形態として、pチャネルデバイスをマスクすることでnチャネルデバイスの図1の基板にp型ハロ注入(halo implants)を行ってもよく、さらに、p型ハロ注入は、nチャネルデバイスを最適にするために、照射量の例として1×1014イオン数/cm2でのヒ素を用いた別のLDD注入を含んでもよい。その後段もしくは前段に、同様の処理をpチャネルデバイスに行ってもよい。特に、ハロ領域を形成するためのpチャネルデバイスにリンやヒ素を含む注入を行っている間にnチャネルデバイスをマスクしてもよく、おそらく、pチャネルデバイスのLDD領域を最適にするためにホウ素を含む注入もなされる。

【0016】

図2では、メモリアレイ回路領域14内のトランジスタゲート配線15上および周辺回路領域16内のトランジスタゲート配線17上に 第一の絶縁体のスペーサ物質30を形成している。それらは、メモリアレイ回路領域14内のトランジスタゲート配線15間の空間31、および周辺回路領域16内のトランジスタゲート配線17間の空間33に残る。より好ましい物質の例は、シリコン窒化物、アルミニウム酸化物、およびハフニウム酸化物、ならびに、もちろんそれらの混合物および/または多層を含んでいるもの、の少なくとも一つを含んでいる物質である。スペーサ物質30の好ましい厚さの範囲の例としては、50Å〜好ましくは最小間隙D1の1/3よりも大きくない厚さである。

【0017】

図3では、第一の絶縁体のスペーサ物質30上、および、メモリアレイ回路領域14内のトランジスタゲート配線15上、ならびに、周辺回路領域16内のトランジスタゲート

配線17上、に第二の絶縁体のスペーサ物質32を形成している。第二の絶縁体のスペーサ物質32は、第一の絶縁体のスペーサ物質30に対して都合よく選択的にエッチングすることが可能である。ここで、 第一のスペーサ物質30としては、例えば、シリコン窒化物、アルミニウム酸化物、およびハフニウム酸化物のいずれか一つもしくは複合物を含み、好ましい物質32の例はドープされていない二酸化シリコンである。本明細書の内容において「ドープされていない二酸化シリコン」は、ホウ素およびリンの一つもしくは複合物が1at.%(原子百分率)よりも多くない二酸化シリコン物質と定義している。ドープされていない二酸化シリコン32を堆積するための好ましい手段は、テトラエチルオルトケイ酸塩(TEOS)を使用する手段であり、そしてその結果として、堆積された二酸化シリコンは後述される好ましい選択的なウェットエッチングを容易にするように(その処理工程のこの時点では少なくとも)高濃度化(densify)されない。本明細書の記述中では、「高濃度化されない」ドープされていない二酸化シリコン層は700℃よりも低温で堆積しており、それは後段で或る温度すなわち少なくとも700℃で暴露されない限り、単に“高濃度化されない”状態のままである。描画されている好ましい実施の形態において、第二の絶縁体のスペーサ物質32は、メモリアレイ回路領域14内のトランジスタゲート配線15間の間隙31を効果的に満たす一方で、周辺回路領域16内のトランジスタゲート配線17間の間隙33を満たさないような厚みで堆積される。ほんの一例であるが、物質32の好適な厚みの例は100Å〜500Åである。

【0018】

図4では、周辺回路領域16内の個々のトランジスタゲート配線17の向かいあう側壁19上に絶縁体の側壁スペーサ34を効果的に形成するために第一の絶縁体のスペーサ物質30に対して選択的に第二の絶縁体のスペーサ物質32が異方性エッチングされている。より好ましいエッチング化学物質の例としては、シリコン窒化物上で支持されている二酸化シリコン物質に対して作用するC4F8、CF4、Arを含む。本明細書の記述中においては、少なくとも2:1の除去比で一つの物質に対してもう一方の物質の除去の選択的なエッチングをしている。

【0019】

図5では、周辺回路領域16内の側壁スペーサ34がマスクされている。より好ましくは、周辺回路領域16内のトランジスタゲート配線17間の間隙33をマスクするマスク層36を用いることでそれを行い、さらに好ましくは、周辺回路領域16の全体をマスク層36でマスクすることにより行うとよい。より好ましい物質の例としては、もちろん他の物質も考えられるが、フォトレジストである。

【0020】

図6では、 周辺回路領域16内の物質32である側壁スペーサ34をマスクしながら、メモリアレイ回路領域14内の第一の絶縁体のスペーサ物質30に対して選択的に第二の絶縁体のスペーサ物質32(不図示)をエッチングしている。エッチングの好ましい手段としては、スペーサ物質30がドープされていない二酸化シリコンを含んでおり、スペーサ物質32がシリコン窒化物を含んでいる場合、大気圧および20℃〜100℃の温度範囲で、例えば酸化緩衝剤や希HFのエッチング用化学物質を使用するウェットエッチングを含んでいる。上述においてより好ましく、スペーサ物質がドープされていない二酸化シリコンを含む場合、図6で描かれているように、例え高濃度化されるとしても、第二の絶縁体のスペーサ物質のエッチングの後までは、スペーサ物質が高濃度化されないことがかなり好ましい。

【0021】

図7では、メモリアレイ回路領域14内の個々のトランジスタゲート配線15の向かいあう側壁19上に絶縁体の側壁スペーサ40を効果的に形成するように第一の絶縁体のスペーサ物質30が異方性エッチングされている。そのような異方性エッチングの好ましいエッチング化学物質の例としては、物質30がシリコン窒化物を含んでいる場合、多重ステップエッチング処理(multistep etching process)においてAr、CF4、CH2F2、CHF3、およびO2を用いる多重ステップエッチングを含んでいる。また、図7はメモリ

アレイ回路領域14内の半導体基板12の半導体物質を効果的に露出するための基板12上のゲート誘電体層18の露出部分のエッチングを描いている。描図されたそしてより好ましい例として、周辺回路領域16内の絶縁体の側壁スペーサ34は、メモリアレイ回路領域14内の絶縁体の側壁スペーサ40の最大幅W1よりも大きい最大幅W2を有している。

【0022】

図8では、マスクしている物質36(不図示)を基板10から除去している。

本発明の一つの特徴として、本発明は、メモリアレイ回路領域内の個々のトランジスタゲート配線の向かいあう側壁上に異方性エッチングされた絶縁体の側壁スペーサを形成するよりも先に、周辺回路領域内の個々のトランジスタゲート配線に向かい合う側壁上に異方性エッチングされた絶縁体の側壁スペーサを形成することを含んでいる。上述の工程はそれを行う一つの手段の例であり、勿論、今後開発される方法も含め同様のことを行う何か他の手段を想定できる。

【0023】

さらに、本発明の一つの特徴にしたがってメモリ回路を形成する方法は、処理する順序に依存せず、周辺回路領域内のトランジスタゲート配線上、および、メモリアレイ回路領域内のトランジスタゲート配線間の間隙以外に、異方性エッチングされた絶縁体の側壁スペーサを形成している間に、前記メモリアレイ回路領域内のトランジスタゲート配線間の間隙をマスクすることを含んでいる。一例として、図4は、そのようにする手段の例の一つを描いている。さらに、本発明のこの特徴に従うことに続けて、メモリアレイ回路領域内のトランジスタゲート配線上、および、周辺回路領域内のトランジスタゲート配線間の間隙以外に、異方性エッチングされた絶縁体の側壁スペーサを形成している間に、周辺回路領域内のトランジスタゲート配線間の間隙をマスクしている。ほんの一例として、図7は、そのようにする手段の例の一つを描いている。さらに、上述の好ましい処理としては、周辺回路領域内をマスクする前にメモリアレイ回路領域内のマスクを行っている。逆に、本発明の特徴としては、描かれているスペーサを形成する際にメモリアレイ領域内をマスクするより先に周辺回路領域内をマスクすることも含んでいる。例えば、および、ほんの一例として、スペーサ34の形成よりも先に、描かれている異方性エッチングされたスペーサ40を形成してもよい。

【0024】

さらに、描かれている好ましい実施の形態によらず、周辺回路領域内のスペーサを形成するためのエッチングをしている間にメモリアレイ回路領域内で行われるマスクは、メモリアレイ回路領域内のトランジスタゲート配線間のあらゆる間隙に対してなされる。さらに好ましい実施の形態の一例として、メモリアレイ回路領域内の絶縁体の側壁スペーサを形成するための異方性エッチングをしている間に周辺回路領域内でのマスクが、周辺回路領域内のトランジスタゲート配線間のあらゆる間隙に対してなされる。

【0025】

さらに、好ましい実施の形態の一例として、メモリアレイ回路領域内でのマスクは、周辺回路領域における絶縁体の側壁スペーサが異方的にエッチングされるときの層(すなわち層32)をマスクとして用いることを含んでおり、そしてまた、一つの実施の形態として、メモリアレイ回路領域における絶縁体の側壁スペーサが異方的にエッチングされるときの層(すなわち層30)をマスクとして用いることも含んでいる。

【0026】

さらに、上述の実施の形態の例として、メモリアレイ回路領域内におけるマスクは、フォトレジストを用いておらず、そして、一つの実施の形態として、周辺回路領域内でのマスクはフォトレジストを用いている。

【0027】

メモリアレイ回路領域内にエピタキシャル成長の半導体物質を少なくとも絶縁体の側壁スペーサに隣接するように形成した後で処理をしてもよい。例えば、またほんの一例として、上述および描かれているエッチングならびにスペーサ形成の一連の作業によって図8

のようになり、ここでメモリアレイ回路領域14内の基板12の半導体物質は外界に露出され、周辺回路領域16内の基板12の半導体物質は物質30および18で覆われている。一つの好適な実施の形態として、周辺回路領域16内の絶縁体の側壁スペーサ36に隣接するエピタキシャル成長の半導体物質の成長が行われない間に、メモリアレイ回路領域14内の絶縁体の側壁スペーサ40に隣接するエピタキシャル成長の半導体物質を成長させるためにそのようなことを有効に用いてもよい。例えばそのような例として、図8における基板に、エピタキシャル成長の半導体物質の成長より先に、洗浄ステップ、例えば温度27℃および大気圧下で60秒間より短時間のHF溶液への暴露、を課すことが好ましい。HF溶液の例としては、水と49wt.%HF水溶液とが100:1の体積比のものである。

【0028】

図9では、半導体基板12の半導体物質からエピタキシャル成長の半導体物質44を成長させている。好ましい材料の一例は、エピタキシャル成長の単結晶シリコンであり、ここで、そのような成長をさせる基礎となる物質は単結晶シリコンを含んでいる。他の半導体物質が勿論考えられ、例えばそのほんの一例としては、ガリウムとシリコンの合金である。シリコン以外の材料も勿論考えられる。基礎となる基板からの物質44の厚みの例としては、200Å〜600Åである。単結晶シリコンのそのようなエピタキシャル成長の半導体物質44を成長させるための方法の例としては、シランに基づく選択的なエピタキシャル成長を含む。

【0029】

図10では、周辺回路領域16で露出している物質30、および、その後に露出する物質18をエッチングしている。

図11において、アレイおよび周辺回路に対して所望の最も高いインプラント投与量のソース/ドレイン領域45を形成するために適切にインプラントドーピングを行っている。そのようなことは、マスクおよび/またはインプラントステップのいくつかの組み合わせによって、そして、周辺回路領域内の一般的なpチャネルデバイスおよびnチャネルデバイスを作成するためのいくつかの手順の例の中で、かつ、ドーピング物質44および直下の基板に対して行ってよい。さらに、そのようなものの形成およびインプラントならびにマスクは、ソース/ドレイン領域上の物質30および18の好ましい除去に関連するいくつかの手順中に行ってもよい。

【0030】

メモリ回路を形成する好ましい方法の一例としては、上述のような例、および、ほんの一例として、本発明の特徴は、例えば図9で示されているように、メモリアレイ回路領域内のトランジスタゲート配線間の間隙31内、および、周辺回路領域内のトランジスタゲート間の間隙33以外にエピタキシャル成長の半導体物質を含む隆起したソース/ドレイン領域を形成することができる。一つの好ましい例および実施例(ならびに示されているような例)として、エピタキシャル成長の半導体物質は、例えば図9で描かれている断面のように少なくとも一つの断面のメモリアレイ回路領域内のトランジスタゲート配線間の間隙(すなわち、間隙31)に及んでいる。本発明の特徴は、スペーサの形成と独立したこのようなエピタキシャル成長の半導体物質の作成、およびエピタキシャル成長の半導体物質の成長と独立したスペーサの上述したような作成を含んでいる。本発明の特徴は、また、当業者によって選択され最適にすることができるように、他の物質と同じ、もしくは、他の物質よりも大きいあるいは小さい“k”の静電容量値であるような異なるスペーサ物質を形成することも含んでいる。

【0031】

上述されているインプラントの例としては、当業者が正しく理解しているように、マスクがされていないもしくはされていなくとも、いつでも行うことができる。ほんの一例として、そして限定するわけではないが、上述の工程の全体もしくは一部は、与えられるon/offのターゲット電流に対する速度性能の向上をともない、様々なトランジスタに対し寄生容量を減らすことを可能にすることができる。好ましい処理によって、メモリアレイ回

路領域もしくは周辺回路領域内のどちらかでエピタキシャルシリコンの選択的形成をも可能とすることができる。さらに、周辺回路領域に対してメモリアレイ回路領域内でスペーサ幅を最適にするようにそのような処理を用いることができる。さらに、ほんの一例として、間隙をつくっているより厚みのある周辺回路領域のスペーサは、ソース/ドレインインプラントをさらに周辺のチャネルから離すことを可能とし、また、p+接点がそれらの下方にあるより深いソース/ドレイン接合点を有することができる。

【0032】

図12は、DRAMメモリセルの内部に組み込まれているトランジスタゲート配線15の一つを描いている。エピタキシャル半導体物質44は、DRAMメモリトランジスタ90のソース/ドレイン領域を含んでいる。ソース/ドレイン領域の一方はストレージデバイス150と電気的に接続してあり、ソース/ドレイン領域の他方はビットライン152に電気的に接続してある。ストレージデバイス150は、例えばキャパシタを含んでいる、いくつかの適するデバイスを含むことができる。ビットライン152は、いくつかの適した構成を含むことができる。特徴/トランジスタ(Feature/transistor)90を集積回路、例えばここで述べているDRAM集積回路、の部分として考えることができる。

【0033】

図13は、一つの例として、しかし限定するわけではないが、本発明の特徴に準じているコンピュータシステム400の実施形態を一般化して描いている。コンピュータシステム400は、モニタ401またはその他のコミュニケーション出力デバイス、キーボード402またはその他のコミュニケーション入力デバイス、ならびにマザーボード404を含んでいる。マザーボード404は、マイクロプロセッサ406またはその他のデータ処理装置、ならびに少なくとも一つのメモリデバイス408を搭載することができる。メモリデバイス408は、例えば、一つもしくはそれ以上のワードライン、ビットラインならびにDRAMユニットセルを含んでいる上述の本発明の様々な特徴を含むことができる。メモリデバイス408は、メモリセルのアレイを含むことができ、そして、そのようなアレイをアレイの中の個々のメモリセルにアクセスするためのアドレス回路と接続することができる。さらに、メモリセルアレイを、メモリセルからデータを読み込むための読み込み回路に接続することができる。アドレス回路および読み込み回路をメモリデバイス408およびプロセッサ406間の情報の伝達を行うために使用することができる。それらを図14で示されているマザーボード404のブロック図で描いている。そのブロック図では、アドレス回路を410として描いており、読み込み装置を412として描いている。

【0034】

特に本発明の特徴として、メモリデバイス408がメモリモジュールに相当することもある。例えば、シングルインラインメモリモジュール(シム:SIMM)およびディアルインラインメモリモジュール(ディム:DIMM)を本発明で教示していることを用いている実施の形態の中で用いることができる。デバイスのメモリセルからの読み込みおよびメモリセルへの書き込みに関して異なる方法を与えるいくつかの多様な設計を本メモリデバイスに施すことができる。そのような方法の一つは、ページモード制御(page mode operation)である。メモリセルアレイの行にアクセスする方法、およびアレイの異なる列に無作為にアクセスするための方法としてDRAMにおけるページモード制御を定義している。行および列の交差部に蓄積されているデータを列にアクセスしている間に読み込んで出力することができる。

【0035】

デバイスの一つの代替物としては、アドレスされた列が閉じられた後の出力としてメモリアレイアドレスで蓄積されたデータを使用することができる拡張データ出力(EDO)メモリがある。このメモリはメモリバス上でメモリ出力データを取得する時間を遅くすることなく、より短いアクセス信号とすることができるのでいくつかの接続速度を向上させることができる。デバイスの他の代替物の種類としては、ほんの一例ではあるけれども、SRAMまたはフラッシュメモリなどの他の物品のみならずSDRAM、DDR SDRAM、SLDRAM、VRAMおよびDirect RDRAMを含む。

【0036】

図15は、本発明の電気制御系の例700における多様な実施形態のハイレベル構成を単純化したブロック図を描いている。制御系700は、例えば、コンピュータシステム、処理制御系、あるいはプロセッサおよび関連するメモリを備えているいくつか他の制御系に相当することもある。電気制御系700は、プロセッサまたは演算/論理部(ALU)702、制御部704、メモリデバイス部706および入力/出力(I/O)デバイス708を含めた機能を有する構成要素を有している。一般的に、電気制御系700は、プロセッサ702、ならびに、プロセッサ702、メモリデバイス部706およびI/Oデバイス708間のその他の相互関連物によってデータでやりとりするための演算を特定するネィティブな一組の命令を有する。制御部704は、メモリデバイス706からフェッチされ、実行される命令によって生じる一組の演算をとおした連続的なサイクルによってプロセッサ702、メモリデバイス部706およびI/Oデバイス708の全ての制御を調整している。様々な実施の形態として、メモリデバイス706は、限定する訳ではないが、ランダムアクセスメモリ(RAM)デバイス、読み込み専用メモリ(ROM)デバイス、およびフロッピーディスクドライブおよびコンパクトディスクCD-ROMドライブなどの周辺デバイスを含む。当業者は、本明細書を読み理解した上で、本発明の様々な特徴に準じているDRAMセル、ワードラインおよびビットラインを含むようにいくつかの描かれている電気的な構成物を作成することが可能であることを理解できる。

【0037】

図16は、電気制御系の例800における多様な実施形態のハイレベル構成を単純化したブロック図である。そのシステム800は、メモリセル804のアレイ、アドレスデコーダ806、行アクセス回路808、列アクセス回路810、動作を制御するための読み込み/書き込み制御回路812、および入力/出力回路814を有するメモリデバイス802を含んでいる。メモリデバイス802は、電力回路816、およびメモリセルが低閾値稼働状態にあるか、もしくは、高閾値非稼働状態にあるかどうかを決定するための電流センサーなどのセンサー820をさらに含んでいる。図示されている電力回路816は、電源回路880、参照電圧を供給するための回路882、第一のワードラインにパルスを供給するための回路884、第ニのワードラインにパルスを供給するための回路886、およびビットラインにパルスを供給するための回路888を含んでいる。また、制御系800は、プロセッサ822またはメモリアクセスをするためのメモリコントローラも含んでいる。

【0038】

メモリデバイス802は、ワイヤー配線または金属(matallization)配線を介してプロセッサ822からの制御信号824を受信する。メモリデバイス802は、I/O配線を介してアクセスされるデータを蓄積するために使用される。付加回路および制御信号を供給できることと、メモリデバイス802が本発明における理解を助けるために単純化されていることは当業者によって正しく理解することができる。プロセッサ822もしくはメモリデバイス802の少なくとも一つは、本開示において前述した形態のDRAMセルを含むことができる。

【0039】

本開示中の様々に図示されている制御系は、本発明の回路と構造の様々な用途に関する一般的な理解を与えることを意図しており、本発明の特徴に準じているメモリセルを用いている電気制御系の全ての構成要素および特徴が完全な記載どおりに提供されることを意図していない。当業者は、プロセッサおよびメモリデバイス(群)間の接続時間を短縮するために単一パッケージの制御部の中、もしくは、同様の単一の半導体チップ上で様々な電気制御系を作成できるということが理解できる。

【0040】

メモリセル、ワードラインおよびビットラインの用途としては、メモリモジュール、デバイスドライバ、パワーモジュール、接続モデム、プロセッサモジュール、およびアプリケーション用の特定のモジュールに使用するための電気制御系を含んでおり、そして、多

層モジュール、マルチチップモジュールを含んでいてもよい。そのような回路は、さらに、時計、テレビ、携帯電話、パーソナルコンピュータ、自動車、産業用制御系、航空機、およびその他の機器等の多様な電気制御系の補完的な構成要素であってもよい。

【図面の簡単な説明】

【0041】

【図1】本発明の特徴に従う処理工程における基板断片の概略図である。

【図2】図1によって描かれている処理の後段の処理ステップでの図1の基板断片の図である。

【図3】図2によって描かれている処理の後段の処理ステップでの図2の基板断片の図である。

【図4】図3によって描かれている処理の後段の処理ステップでの図3の基板断片の図である。

【図5】図4によって描かれている処理の後段の処理ステップでの図4の基板断片の図である。

【図6】図5によって描かれている処理の後段の処理ステップでの図5の基板断片の図である。

【図7】図6によって描かれている処理の後段の処理ステップでの図6の基板断片の図である。

【図8】図8は、図7によって描かれている処理の後段の処理ステップでの図7の基板断片の図である。

【図9】図8によって描かれている処理の後段の処理ステップでの図8の基板断片の図である。

【図10】図9によって描かれている処理の後段の処理ステップでの図9の基板断片の図である。

【図11】図10によって描かれている処理の後段の処理ステップでの図10の基板断片の図である。

【図12】本発明の特徴に従って処理している基板の図である。

【図13】本発明の応用例として描いているコンピュータの概略図である。

【図14】図15のコンピュータのマザーボードの特定の特徴を示しているブロック図である。

【図15】本発明の例示的特徴に従う電子システムのハイレベルブロック図である。

【図16】本発明の特徴に従う例示的電子システムの簡略化したブロック図である。

【特許請求の範囲】

【請求項1】

メモリアレイ回路領域および周辺回路領域を有し、前記メモリアレイ回路領域が第一の最小配線間隙をともなうトランジスタゲート配線を含み、前記周辺回路領域が前記第一の最小配線間隙よりも大きい第二の最小配線間隙をともなうトランジスタゲート配線を含む基板を設けるステップと、

前記メモリアレイ領域内の個々の前記トランジスタゲート配線の向かいあう側壁上に異方性エッチングされた絶縁体の側壁スペーサを形成するよりも先に、前記周辺回路領域内の個々の前記トランジスタゲート配線の向かいあう側壁上に異方性エッチングされた絶縁体の側壁スペーサを形成するステップと、

を含むことを特徴とするメモリ回路を形成するための方法。

【請求項2】

前記メモリ回路がDRAM回路を含むことを特徴とする請求項1記載の方法。

【請求項3】

前記メモリアレイ回路領域内の前記トランジスタゲート配線が浮遊ゲートを有さないことを特徴とする請求項1記載の方法。

【請求項4】

前記メモリアレイ回路領域内の前記絶縁体の側壁スペーサが、シリコン窒化物、アルミニウム酸化物、およびハフニウム酸化物の少なくとも一つを含んでいることを特徴とする請求項1記載の方法。

【請求項5】

前記周辺回路領域内の前記絶縁体の側壁スペーサが、ドープされていない二酸化シリコンを含んでいることを特徴とする請求項1記載の方法。

【請求項6】

前記メモリアレイ回路領域内の前記絶縁体の側壁スペーサが、シリコン窒化物、アルミニウム酸化物、ハフニウム酸化物の少なくとも一つを含んでいることを特徴とする請求項5記載の方法。

【請求項7】

前記周辺回路領域内の前記絶縁体の側壁スペーサが、前記メモリアレイ回路領域内の前記絶縁体の側壁スペーサの最大幅よりも大きい最大幅を有していることを特徴とする請求項1記載の方法。

【請求項8】

前記周辺回路領域内の前記絶縁体の側壁スペーサおよび前記メモリアレイ回路領域内の前記絶縁体の側壁スペーサを形成した後、前記メモリアレイ回路領域内の前記絶縁体の側壁スペーサに隣接するエピタキシャル成長の半導体物質を含むことを特徴とする請求項1記載の方法。

【請求項9】

前記周辺回路領域内の前記絶縁体の側壁スペーサおよび前記メモリアレイ回路領域内の前記絶縁体の側壁スペーサを形成した後、前記メモリアレイ回路領域内で前記絶縁体の側壁スペーサに隣接するエピタキシャル成長の半導体物質を含む一方で、前記周辺回路領域内の前記絶縁体の側壁スペーサに隣接するエピタキシャル成長の半導体物質を含まないことを特徴とする請求項1記載の方法。

【請求項10】

メモリアレイ回路領域および周辺回路領域を有し、前記メモリアレイ回路領域が第一の最小配線間隙をともなうトランジスタゲート配線を含み、前記周辺回路領域が前記第一の最小配線間隙よりも大きい第二の最小配線間隙をともなうトランジスタゲート配線を含む基板を設けるステップと、

前記周辺回路領域内の前記トランジスタゲート配線上、および、前記メモリアレイ回路領域内の前記トランジスタゲート配線間の前記間隙以外に、異方性エッチングされた絶縁体の側壁スペーサを形成している間に、前記メモリアレイ回路領域内の前記トランジスタ

ゲート配線間の間隙をマスクするステップと、

前記メモリアレイ回路領域内の前記トランジスタゲート配線上、および、前記周辺回路領域内の前記トランジスタゲート配線間の前記間隙以外に、異方性エッチングされた絶縁体の側壁スペーサを形成している間に、前記周辺回路領域内の前記トランジスタゲート配線間の間隙をマスクするステップと、

を含むことを特徴とするメモリ回路を形成するための方法。

【請求項11】

前記メモリアレイ回路領域内をマスクするステップが、マスクとして、前記周辺回路領域内の前記絶縁体の側壁スペーサが異方性エッチングされる層を用いるステップを含んでいることを特徴とする請求項10記載の方法。

【請求項12】

前記メモリアレイ回路領域内をマスクするステップが、マスクとして、前記周辺回路領域内の前記絶縁体の側壁スペーサが異方性エッチングされる層を用いるステップ、および、マスクとして、前記メモリアレイ回路領域内の前記絶縁体の側壁スペーサが異方性エッチングされる層を用いるステップ、を含むことを特徴とする請求項10記載の方法。

【請求項13】

前記周辺回路領域内を前記マスクするステップより先に、前記メモリアレイ回路領域内の前記マスクが行われることを特徴とする請求項10記載の方法。

【請求項14】

前記メモリアレイ回路領域内を前記マスクするステップより先に、前記周辺回路領域内の前記マスクが行われることを特徴とする請求項10記載の方法。

【請求項15】

前記周辺回路領域内の前記絶縁体の側壁スペーサが、前記メモリアレイ回路領域内の前記絶縁体の側壁スペーサの最大幅より大きい最大幅を有することを特徴とする請求項10記載の方法。

【請求項16】

メモリアレイ回路領域および周辺回路領域を有し、前記メモリアレイ回路領域が第一の最小配線間隙をともなうトランジスタゲート配線を含み、前記周辺回路領域が前記第一の最小配線間隙よりも大きい第二の最小配線間隙をともなうトランジスタゲート配線を含む基板を設けるステップと、

前記メモリアレイ回路領域および前記周辺回路領域内の前記トランジスタゲート配線上に第一の絶縁体のスペーサ物質を形成するステップと、

前記第一の絶縁体のスペーサ物質上および前記メモリアレイ回路領域内の前記トランジスタゲート配線上ならびに前記周辺回路領域内の前記トランジスタゲート配線上に第二の絶縁体のスペーサ物質を形成し、前記第二の絶縁体のスペーサ物質は前記第一の絶縁体のスペーサ物質に対して選択的にエッチングされることができ、前記第二の絶縁体のスペーサ物質は前記メモリアレイ回路領域内の前記トランジスタゲート配線間の間隙を満たしているが、前記周辺回路領域内の前記トランジスタゲート配線間の間隙を満たしていないステップと、

前記周辺回路領域内の個々の前記トランジスタゲート配線の向かいあう側壁上に絶縁体の側壁スペーサを効果的に形成するために前記第一の絶縁体のスペーサ物質に対して選択的に前記第二の絶縁体のスペーサ物質を異方性エッチングするステップと、

前記周辺回路領域内に前記側壁スペーサを形成した後に、前記周辺回路領域内の前記側壁スペーサをマスクしながら、前記メモリアレイ回路領域内の前記第一の絶縁体のスペーサ物質に対して選択的に前記第二の絶縁体のスペーサ物質をエッチングするステップと、

前記メモリアレイ回路領域内の個々の前記トランジスタゲート配線の向かいあう側壁上に絶縁体の側壁スペーサを効果的に形成するために前記第一の絶縁体のスペーサ物質を異方性エッチングするステップと、

を含むことを特徴とするメモリ回路を形成するための方法。

【請求項17】

前記第一の絶縁体のスペーサ物質が、シリコン窒化物、アルミニウム酸化物、ハフニウム酸化物の少なくとも一つを含んでいることを特徴とする請求項16記載の方法。

【請求項18】

メモリアレイ回路領域および周辺回路領域を有し、前記メモリアレイ回路領域が第一の最小配線間隙をともなうトランジスタゲート配線を含み、前記周辺回路領域が前記第一の最小配線間隙よりも大きい第二の最小配線間隙をともなうトランジスタゲート配線を含む基板を設けるステップと、

前記メモリアレイ回路領域内の前記トランジスタゲート配線間の間隙内および前記周辺回路領域内の前記トランジスタゲート配線間の間隙以外にエピタキシャル成長の半導体物質を含む隆起したソース/ドレイン領域を形成するステップと、

を含むことを特徴とするメモリ回路を形成するための方法。

【請求項19】

前記エピタキシャル成長の半導体物質が、少なくとも一つの断面において前記メモリアレイ回路領域内の前記トランジスタゲート配線間の前記間隙をまたいでいることを特徴とする請求項18記載の方法。

【請求項20】

前記メモリ回路がDRAM回路を含んでいることを特徴とする請求項18記載の方法。

【請求項21】

前記メモリアレイ回路領域内の前記トランジスタゲート配線が浮遊ゲートを有さないことを特徴とする請求項18記載の方法。

【請求項22】

前記エピタキシャル成長の半導体物質が、少なくとも一つの断面において前記メモリアレイ回路領域内の前記トランジスタゲート配線間の前記間隙をまたいでおり、

前記メモリ回路がDRAM回路を含んでいる、

ことを特徴とする請求項18記載の方法。

【請求項1】

メモリアレイ回路領域および周辺回路領域を有し、前記メモリアレイ回路領域が第一の最小配線間隙をともなうトランジスタゲート配線を含み、前記周辺回路領域が前記第一の最小配線間隙よりも大きい第二の最小配線間隙をともなうトランジスタゲート配線を含む基板を設けるステップと、

前記メモリアレイ領域内の個々の前記トランジスタゲート配線の向かいあう側壁上に異方性エッチングされた絶縁体の側壁スペーサを形成するよりも先に、前記周辺回路領域内の個々の前記トランジスタゲート配線の向かいあう側壁上に異方性エッチングされた絶縁体の側壁スペーサを形成するステップと、

を含むことを特徴とするメモリ回路を形成するための方法。

【請求項2】

前記メモリ回路がDRAM回路を含むことを特徴とする請求項1記載の方法。

【請求項3】

前記メモリアレイ回路領域内の前記トランジスタゲート配線が浮遊ゲートを有さないことを特徴とする請求項1記載の方法。

【請求項4】

前記メモリアレイ回路領域内の前記絶縁体の側壁スペーサが、シリコン窒化物、アルミニウム酸化物、およびハフニウム酸化物の少なくとも一つを含んでいることを特徴とする請求項1記載の方法。

【請求項5】

前記周辺回路領域内の前記絶縁体の側壁スペーサが、ドープされていない二酸化シリコンを含んでいることを特徴とする請求項1記載の方法。

【請求項6】

前記メモリアレイ回路領域内の前記絶縁体の側壁スペーサが、シリコン窒化物、アルミニウム酸化物、ハフニウム酸化物の少なくとも一つを含んでいることを特徴とする請求項5記載の方法。

【請求項7】

前記周辺回路領域内の前記絶縁体の側壁スペーサが、前記メモリアレイ回路領域内の前記絶縁体の側壁スペーサの最大幅よりも大きい最大幅を有していることを特徴とする請求項1記載の方法。

【請求項8】

前記周辺回路領域内の前記絶縁体の側壁スペーサおよび前記メモリアレイ回路領域内の前記絶縁体の側壁スペーサを形成した後、前記メモリアレイ回路領域内の前記絶縁体の側壁スペーサに隣接するエピタキシャル成長の半導体物質を含むことを特徴とする請求項1記載の方法。

【請求項9】

前記周辺回路領域内の前記絶縁体の側壁スペーサおよび前記メモリアレイ回路領域内の前記絶縁体の側壁スペーサを形成した後、前記メモリアレイ回路領域内で前記絶縁体の側壁スペーサに隣接するエピタキシャル成長の半導体物質を含む一方で、前記周辺回路領域内の前記絶縁体の側壁スペーサに隣接するエピタキシャル成長の半導体物質を含まないことを特徴とする請求項1記載の方法。

【請求項10】

メモリアレイ回路領域および周辺回路領域を有し、前記メモリアレイ回路領域が第一の最小配線間隙をともなうトランジスタゲート配線を含み、前記周辺回路領域が前記第一の最小配線間隙よりも大きい第二の最小配線間隙をともなうトランジスタゲート配線を含む基板を設けるステップと、

前記周辺回路領域内の前記トランジスタゲート配線上、および、前記メモリアレイ回路領域内の前記トランジスタゲート配線間の前記間隙以外に、異方性エッチングされた絶縁体の側壁スペーサを形成している間に、前記メモリアレイ回路領域内の前記トランジスタ

ゲート配線間の間隙をマスクするステップと、

前記メモリアレイ回路領域内の前記トランジスタゲート配線上、および、前記周辺回路領域内の前記トランジスタゲート配線間の前記間隙以外に、異方性エッチングされた絶縁体の側壁スペーサを形成している間に、前記周辺回路領域内の前記トランジスタゲート配線間の間隙をマスクするステップと、

を含むことを特徴とするメモリ回路を形成するための方法。

【請求項11】

前記メモリアレイ回路領域内をマスクするステップが、マスクとして、前記周辺回路領域内の前記絶縁体の側壁スペーサが異方性エッチングされる層を用いるステップを含んでいることを特徴とする請求項10記載の方法。

【請求項12】

前記メモリアレイ回路領域内をマスクするステップが、マスクとして、前記周辺回路領域内の前記絶縁体の側壁スペーサが異方性エッチングされる層を用いるステップ、および、マスクとして、前記メモリアレイ回路領域内の前記絶縁体の側壁スペーサが異方性エッチングされる層を用いるステップ、を含むことを特徴とする請求項10記載の方法。

【請求項13】

前記周辺回路領域内を前記マスクするステップより先に、前記メモリアレイ回路領域内の前記マスクが行われることを特徴とする請求項10記載の方法。

【請求項14】

前記メモリアレイ回路領域内を前記マスクするステップより先に、前記周辺回路領域内の前記マスクが行われることを特徴とする請求項10記載の方法。

【請求項15】

前記周辺回路領域内の前記絶縁体の側壁スペーサが、前記メモリアレイ回路領域内の前記絶縁体の側壁スペーサの最大幅より大きい最大幅を有することを特徴とする請求項10記載の方法。

【請求項16】

メモリアレイ回路領域および周辺回路領域を有し、前記メモリアレイ回路領域が第一の最小配線間隙をともなうトランジスタゲート配線を含み、前記周辺回路領域が前記第一の最小配線間隙よりも大きい第二の最小配線間隙をともなうトランジスタゲート配線を含む基板を設けるステップと、

前記メモリアレイ回路領域および前記周辺回路領域内の前記トランジスタゲート配線上に第一の絶縁体のスペーサ物質を形成するステップと、

前記第一の絶縁体のスペーサ物質上および前記メモリアレイ回路領域内の前記トランジスタゲート配線上ならびに前記周辺回路領域内の前記トランジスタゲート配線上に第二の絶縁体のスペーサ物質を形成し、前記第二の絶縁体のスペーサ物質は前記第一の絶縁体のスペーサ物質に対して選択的にエッチングされることができ、前記第二の絶縁体のスペーサ物質は前記メモリアレイ回路領域内の前記トランジスタゲート配線間の間隙を満たしているが、前記周辺回路領域内の前記トランジスタゲート配線間の間隙を満たしていないステップと、

前記周辺回路領域内の個々の前記トランジスタゲート配線の向かいあう側壁上に絶縁体の側壁スペーサを効果的に形成するために前記第一の絶縁体のスペーサ物質に対して選択的に前記第二の絶縁体のスペーサ物質を異方性エッチングするステップと、

前記周辺回路領域内に前記側壁スペーサを形成した後に、前記周辺回路領域内の前記側壁スペーサをマスクしながら、前記メモリアレイ回路領域内の前記第一の絶縁体のスペーサ物質に対して選択的に前記第二の絶縁体のスペーサ物質をエッチングするステップと、

前記メモリアレイ回路領域内の個々の前記トランジスタゲート配線の向かいあう側壁上に絶縁体の側壁スペーサを効果的に形成するために前記第一の絶縁体のスペーサ物質を異方性エッチングするステップと、

を含むことを特徴とするメモリ回路を形成するための方法。

【請求項17】

前記第一の絶縁体のスペーサ物質が、シリコン窒化物、アルミニウム酸化物、ハフニウム酸化物の少なくとも一つを含んでいることを特徴とする請求項16記載の方法。

【請求項18】

メモリアレイ回路領域および周辺回路領域を有し、前記メモリアレイ回路領域が第一の最小配線間隙をともなうトランジスタゲート配線を含み、前記周辺回路領域が前記第一の最小配線間隙よりも大きい第二の最小配線間隙をともなうトランジスタゲート配線を含む基板を設けるステップと、

前記メモリアレイ回路領域内の前記トランジスタゲート配線間の間隙内および前記周辺回路領域内の前記トランジスタゲート配線間の間隙以外にエピタキシャル成長の半導体物質を含む隆起したソース/ドレイン領域を形成するステップと、

を含むことを特徴とするメモリ回路を形成するための方法。

【請求項19】

前記エピタキシャル成長の半導体物質が、少なくとも一つの断面において前記メモリアレイ回路領域内の前記トランジスタゲート配線間の前記間隙をまたいでいることを特徴とする請求項18記載の方法。

【請求項20】

前記メモリ回路がDRAM回路を含んでいることを特徴とする請求項18記載の方法。

【請求項21】

前記メモリアレイ回路領域内の前記トランジスタゲート配線が浮遊ゲートを有さないことを特徴とする請求項18記載の方法。

【請求項22】

前記エピタキシャル成長の半導体物質が、少なくとも一つの断面において前記メモリアレイ回路領域内の前記トランジスタゲート配線間の前記間隙をまたいでおり、

前記メモリ回路がDRAM回路を含んでいる、

ことを特徴とする請求項18記載の方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【公表番号】特表2009−503891(P2009−503891A)

【公表日】平成21年1月29日(2009.1.29)

【国際特許分類】

【出願番号】特願2008−524979(P2008−524979)

【出願日】平成18年7月13日(2006.7.13)

【国際出願番号】PCT/US2006/027366

【国際公開番号】WO2007/018967

【国際公開日】平成19年2月15日(2007.2.15)

【公序良俗違反の表示】

(特許庁注:以下のものは登録商標)

1.フロッピー

【出願人】(595168543)マイクロン テクノロジー, インク. (444)

【Fターム(参考)】

【公表日】平成21年1月29日(2009.1.29)

【国際特許分類】

【出願日】平成18年7月13日(2006.7.13)

【国際出願番号】PCT/US2006/027366

【国際公開番号】WO2007/018967

【国際公開日】平成19年2月15日(2007.2.15)

【公序良俗違反の表示】

(特許庁注:以下のものは登録商標)

1.フロッピー

【出願人】(595168543)マイクロン テクノロジー, インク. (444)

【Fターム(参考)】

[ Back to top ]