異電源接続検証方法及び異電源接続検証用プログラム並びに記録媒体

【課題】真のエラーか否かの判定を可能とする検証技術を提供する。

【解決手段】異電源接続検証はコンピュータによって行われる。コンピュータ内の中央処理装置は、電位伝搬と違反の虞れのあるトランジスタを検索する第1処理と、その処理結果に基づいて、擬似違反を抑制する第2処理とを含む。上記第2処理は、トランジスタの違反を除外する第3処理を含む。この第3処理において、違反の虞れがあるトランジスタとゲート接続ノードを同一とするトランジスタを全てオン状態と仮定し(S804)、仮定されたトランジスタがオンするために必要なトランジスタのオン状態を探索し(S805)、オン状態又はオフ状態が決定される周辺トランジスタを探索する(S806)。そして貫通電流パスが無い場合には、擬似違反のMOSトランジスタを違反対象から除外する。

【解決手段】異電源接続検証はコンピュータによって行われる。コンピュータ内の中央処理装置は、電位伝搬と違反の虞れのあるトランジスタを検索する第1処理と、その処理結果に基づいて、擬似違反を抑制する第2処理とを含む。上記第2処理は、トランジスタの違反を除外する第3処理を含む。この第3処理において、違反の虞れがあるトランジスタとゲート接続ノードを同一とするトランジスタを全てオン状態と仮定し(S804)、仮定されたトランジスタがオンするために必要なトランジスタのオン状態を探索し(S805)、オン状態又はオフ状態が決定される周辺トランジスタを探索する(S806)。そして貫通電流パスが無い場合には、擬似違反のMOSトランジスタを違反対象から除外する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、異電源接続検証技術、さらには異電源接続の検出結果に対して貫通電流パスを検出して、真のエラーか否かを判定を行うための技術に関する。

【背景技術】

【0002】

電子回路においては、低電圧で動作する回路と高電圧で動作する回路との間で信号のやり取りが行われる場合がある。かかる場合、低電圧で動作する回路と高電圧で動作する回路との間に、電圧レベルを変換するための昇圧回路(レベルシフタ)が挿入される。また、内部の動作電圧と出力電圧レベルとが異なる場合にも、出力段に昇圧または減圧のためのレベルシフタが必要である。レベルシフタが必要な電子回路において、製造前の設計段階でレベルシフタの入れ忘れを漏れなくチェックするために、回路全体に対して回路シミュレーションが行われる。このような回路シミュレーションの一例として、複数の電源で駆動される多電源電子回路において、その設計の際に、レベルシフタの入れ忘れ、および各回路に供給すべき電源の誤りを、アナログ回路を含む設計か否か、セルライブラリ中のセルを使用した設計か否かにかかわらず、短時間で確実に発見できるようにした多電源電子回路の検証方法として、特許文献1記載の技術が知られている。この技術によれば、読み込んだネットリストに基づき、全ての電源と全ての入力ポートとから回路内の配線の経路探索が行われ、回路中の個々の回路素子およびノードが、いずれの電源または入力ポートで駆動されるかがそれぞれ判定されてマーキングされ、さらに、回路図上の個々の回路素子、回路ブロック、ノードを、そのマーキング結果に基づいて駆動される電源別または入力ポート別に色分け表示される。

【0003】

【特許文献1】特開2005−190442号公報

【発明の開示】

【発明が解決しようとする課題】

【0004】

上記従来技術によれば、例えば図25に示される回路において、電源(VDD,VCC)と入力ポート(IN1、IN2、IN3)から接続トレース(色分け表示)され、素子マーキングの上、問題となる可能性のある箇所(251で示される)が、違反とするルール設定に基づいて指摘される。上記「問題となる可能性のある箇所」を指摘するルール設定は二通りある。第1のルール設定は、図26に示されるように、MOSトランジスタのソース端子又はドレイン端子と、ゲート端子にかかる電源名で、違反とする接続関係を定義するものである。第2のルール設定は、MOSトランジスタのソース端子又はドレイン端子と、ゲート端子とにかかる電圧の差が、許容電圧範囲を越えた場合に違反とする接続関係を定義する。例えば図27に示されるように、VDDを1.5V、VCCを3.3Vとした場合に、それらの電圧差(|3.3−1.5|)が所定の許容範囲(0.01V)を越えた場合に違反として指摘される。

【0005】

しかしながら、上記従来技術について本願発明者が検討したところ、実際には違反とすべきではないのに違反とされる場合(これを「擬似違反」という)が生じるおそれのあることが見いだされた。例えば図28に示される構成のレベルシフタにおいて、pチャネル型MOSトランジスタ281,282がクロスカップルされており、283,284で示されるパス中のMOSトランジスタが全てオンすることは無く、リーク電流は発生しないのに、上記第1のルール設定又は上記第2のルール設定により、pチャネル型MOSトランジスタ281,282が違反とされてしまう。

【0006】

また、実際にMOSトランジスタを使用した電子回路では、レベルシフタ以外にも、内部電圧を昇圧する回路、例えば図29の(A)に示されるポンプ回路や、図29の(B)に示されるレギュレータが組み込まれるケースが多くある。これらの回路は、MOSトランジスタのソース・ドレイン間を介して出力側にΔVが加算されることにより、出力電圧レベルが変動するため、上記第1のルール設定や上記第2のルール設定は対応できない。

【0007】

本発明の目的は、真のエラーか否かの判定を可能とする検証技術を提供することにある。

【0008】

本発明の前記並びにその他の目的と新規な特徴は本明細書の記述及び添付図面から明らかになるであろう。

【課題を解決するための手段】

【0009】

本願において開示される発明のうち代表的なものについて簡単に説明すれば下記のとおりである。

【0010】

すなわち、異電源接続検証は、中央処理装置を備えたコンピュータを用いて行われる。上記中央処理装置は、電位伝搬と違反の虞れのあるトランジスタを検索する第1処理と、上記第1処理の結果に基づいて、擬似違反を抑制する第2処理とを含む。上記第2処理は、上記検証対象回路の貫通電流パスの有無を判定してトランジスタの違反を除外する第3処理を含む。上記第3処理は、違反の虞れがあるトランジスタとゲート接続ノードを同一とするトランジスタを全てオン状態と仮定する第1ステップと、上記第1ステップで仮定されたトランジスタがオンするために必要なトランジスタのオン状態を後方探索する第2ステップと、上記第1ステップと上記第2ステップでのトランジスタの伝搬電位に基づき、オン状態又はオフ状態が決定される周辺トランジスタを探索する第3ステップとを含む。貫通電流パスの有無を判定し、貫通電流パスが無い場合には、擬似違反のトランジスタが違反対象から除外される。

【発明の効果】

【0011】

本願において開示される発明のうち代表的なものによって得られる効果を簡単に説明すれば下記の通りである。

【0012】

すなわち、擬似違反のトランジスタが違反対象から除外されることにより、真のエラーか否かの判定を可能とする検証技術を提供することができる。

【発明を実施するための最良の形態】

【0013】

1.代表的な実施の形態

先ず、本願において開示される発明の代表的な実施の形態について概要を説明する。代表的な実施の形態についての概要説明で括弧を付して参照する図面の参照符号はそれが付された構成要素の概念に含まれるものを例示するに過ぎない。

【0014】

〔1〕本発明の代表的な実施の形態に係る異電源接続検証方法は、予め設定されたプログラムを実行する中央処理装置(31)を備えたコンピュータ(30)を用いて行われる。上記中央処理装置は、電位伝搬と違反の虞れのあるトランジスタを検索する第1処理(S103)と、上記第1処理の結果に基づいて、擬似違反を抑制する第2処理(S104)とを含む。上記第2処理は、上記検証対象回路の貫通電流パスの有無を判定してトランジスタの違反を除外する第3処理(S602)を含む。上記第3処理は、違反の虞れがあるトランジスタとゲート接続ノードを同一とするトランジスタを全てオン状態と仮定する第1ステップ(S804)と、上記第1ステップで仮定されたトランジスタがオンするために必要なトランジスタのオン状態を探索(前方探索)する第2ステップ(S805)と、上記第1ステップと上記第2ステップでのトランジスタの伝搬電位に基づき、オン状態又はオフ状態が決定される周辺トランジスタを探索(後方探索)する第3ステップと(S806)を含む。

【0015】

上記の構成によれば、貫通電流パスの有無を判定し、貫通電流パスが無い場合には、違反の虞れのあるMOSトランジスタが違反対象から除外されることから、貫通電流パスの検出によって擬似違反を排除することができる。

【0016】

〔2〕さらに上記第3処理には、違反の虞れのあるMOSトランジスタにシリアルに接続されるトランジスタを挟んだ異電源間の全てのパスを探索する第4ステップ(S807)と、上記第4ステップで探索されたパス毎に、オフ状態となるトランジスタを含むパスを除外し、全てのパスが除外された場合に、違反の虞れのあるトランジスタを違反対象から除外する第5ステップ(S808)とを含めることができる。

【0017】

〔3〕上記第3処理は、トポロジーマッチングによりトランジスタの違反を除外する第4処理(S601)を含む。上記第4処理は、事前情報として付与されたトポロジーと上記異電源接続検証を可能とする異電源接続検証用プログラムとが一致するか否かを判別し、その判別結果に基づいて該当トランジスタを違反対象から除外する第6ステップ(S704)を含む。

【0018】

〔4〕上記第1処理は、オン状態のトランジスタでの固定電位伝搬により、オン状態又はオフ状態が決定されるトランジスタを探索(後方探索)する第6ステップ(S501)と、上記第6ステップでオフ状態となるトランジスタを探索する第7ステップ(S502)と、上記第7ステップで探索されたトランジスタを、ソース又はドレイン方向により電源電圧レベルを伝搬させる対象トランジスタから除外する第8ステップ(S503)とを含む。そして上記第1処理は、トランジスタのソース・ドレイン間で伝搬する可能性のある電位を伝搬させる第9ステップ(S504)と、ゲート端子とソース端子又はドレイン端子とに正の電源電圧レベルが伝搬されるpチャネル型MOSトランジスタと、ゲート端子とソース端子又はドレイン端子に0V以下の電源電圧レベルが伝搬されるnチャネル型MOSトランジスタとを探索する第10ステップ(S505)とを含む。さらに上記第1処理は、上記第10ステップで、各電源電圧レベルが印加される場合のその電圧値について、ゲート端子の最小電圧値が、ソース又はドレイン端子の最大電圧値よりも小さくなるトランジスタと、ゲート端子の最大電圧値がソース又はドレイン端子の最小電圧値よりも大きくなるトランジスタとを探索し、それを、違反の虞れのあるトランジスタとしてリストアップする第11ステップ(S506)とを含む。

【0019】

2.実施の形態の説明

次に、実施の形態について更に詳述する。

【0020】

図35には、異電源接続検証のためのプログラムが実行されるコンピュータの構成例が示される。図35に示されるコンピュータ30は、特に制限されないが、CPU(中央処理装置)31、記憶装置32、入力装置33、表示装置34、及メモリ35を含み、それらは、バス36を介して互いに結合されている。CPU31は、所定のプログラムを実行する。本例においてこのCPU31は、異電源接続検証のためのプログラムを実行する。記憶装置32には、上記CPU31で実行される各種プログラムや、チェック対象回路のネットリストなど、各種情報が格納される。特に制限されないが、記憶装置32の記録媒体321は、磁気ディスクであり、記憶装置32に着脱自在とされる。記録媒体321は、記憶装置32に装着された状態で、コンピュータ30によって読み書き可能とされる。

【0021】

CPU31は、異電源接続検証のためのプログラムを記憶装置32の記録媒体321から読み出して実行することで、所定の演算処理を行う。メモリ35は、上記CPU31における演算処理の作業領域などに利用される。このメモリ35には、例えばランダムアクセス可能なRAM(ランダム・アクセス・メモリ)とされる。入力装置33は、このコンピュータに対して各種情報の入力を可能とするもので、この入力装置33には、キーボードやマウス等の各種入力デバイスが含まれる。表示装置34は、このコンピュータ30での各種情報を必要に応じて表示するもので、例えば液晶ディスプレイ装置とされる。

【0022】

ここで、上記CPU31で行われる異電源接続検証における基本的な処理について説明する。

【0023】

この異電源接続検証では、トポロジーマッチング又はサブ回路名により、特殊回路を事前認識させる第1手法と、貫通電流パスの有無を判定し、擬似違反を抑制する第2手法とが採用される。

【0024】

〔1〕第1手法

例えば図32に示されるように、レベルシフタ324の回路トポロジーと違反をマスクするMOSトランジスタの情報が事前情報として予め付与されているものとする。この場合、図32における回路321,322は、上記レベルシフタ324の回路トポロジーと一致するため、違反対象から除外される。回路323は、上記レベルシフタ324の回路トポロジーと一致しないため、違反対象から除外されない。このようにレベルシフタを認識した場合には、擬似違反の抑制に使用され、その結果、真の違反だけを指摘することができる。

【0025】

また、図33に示されるように、ポンプ回路やレギュレータに適用される昇圧回路334のトポロジー情報(MOSトランジスタのゲートサイズ等のパラメータ情報を含む)が事前情報として付与されている場合には、回路331〜333は昇圧回路334と一致するため、昇圧回路と認識される。そして、335〜337で示されるように、回路認識の都度、ΔV(指定値)分の電位を加算して伝搬することで、内部電源を考慮した検証が可能とされる。回路333の出力node_outは、3.3V+(ΔV×N)Vの内部電源として認識可能とされる。また、後段回路を内部電源の電位でチェックすることもできる。尚、ΔVは負の場合もあり得る。

【0026】

上記第1手法において、例えばレベルシフタを認識した場合には、擬似違反の抑制に使用され、ポンプ回路やレギュレータを認識した場合には、伝搬電位の補正に使用される。

【0027】

〔2〕第2手法

違反の虞れのあるMOSトランジスタに対して以下の手順により貫通電流の有無を判定する。

【0028】

(2−1)先ず、違反の虞れのあるMOSトランジスタとゲート接続ノードを同一とする全MOSトランジスタをオン(導通)状態と仮定する。

【0029】

(2−2)上記手順(2−1)において、上記MOSトランジスタがオンするために必要とされるMOSトランジスタのオン状態を探索(前方探索)する。例えば図30に示されるように、3個のインバータが結合される場合、以下のように探索(前方探索)される。

【0030】

pチャネル型MOSトランジスタ301とnチャネル型MOSトランジスタ302が結合されて第1インバータが形成され、pチャネル型MOSトランジスタ303とnチャネル型MOSトランジスタ304とが結合されて第2インバータが形成され、pチャネル型MOSトランジスタ305とnチャネル型MOSトランジスタ306とが結合されて第3インバータが形成される。ここで、pチャネル型MOSトランジスタ305をオン状態と仮定した場合、その前段に配置されているnチャネル型MOSトランジスタ304がオン状態であることが必要であり、また、そのためにはpチャネル型MOSトランジスタ301がオン状態であることが必要である。このようにしてMOSトランジスタのオン状態が探索(前方探索)される。

【0031】

(2−3)上記手順(2−1)と(2−2)におけるMOSトランジスタのオン状態に基づいてオン状態又はオフ状態が決定されるMOSトランジスタを探索(後方探索)する。例えば図31に示されるように、pチャネル型MOSトランジスタ301がオン状態であれば、高電位側電源VDDからの電位伝搬により、pチャネル型MOSトランジスタ303のオフ状態が決定され、nチャネル型MOSトランジスタ304のオン状態が決定される。それにより、後段へのグランド(GND)レベルの電位伝搬が行われるため、pチャネル型MOSトランジスタ305のオン状態が決定され、nチャネル型MOSトランジスタ306のオフ状態が決定される。このようにして、オン状態又はオフ状態が決定されるMOSトランジスタの探索(後方探索)が行われる。

【0032】

(2−4)違反とされるMOSトランジスタに直列接続されるMOSトランジスタを挟んだ異電源間の全パスを探索する。

【0033】

(2−5)上記手順(2−4)で探索されたパス毎に、オフ状態とされるMOSトランジスタを含むパスを除外し、全パスが除外された場合には、違反の虞れのあるMOSトランジスタを違反対象から除外する。換言すれば、上記手順(2−4)で探索されたパス毎に、貫通電流パスの有無が判定され、貫通電流パスが無い場合には、違反の虞れのあるMOSトランジスタが違反対象から除外される。例えば図34に示されるように、pチャネル型MOSトランジスタ341,342,343,345、nチャネル型MOSトランジスタ344,346、インバータ347,348,349を含んで、レベルシフタが形成される場合には、次のようにMOSトランジスタが違反対象から除外される。

【0034】

pチャンネル型MOSトランジスタ343,345に違反の虞れがあるものとする。MOSトランジスタ343,344のゲートには、高電位側電源VDD(1.5V)の電圧が印加されているものと仮定し、このMOSトランジスタ343,344の双方がオン状態と仮定する。この場合、pチャネル型MOSトランジスタ342はオン状態、pチャネル型MOSトランジスタ345はオン状態とされるから、pチャネル型MOSトランジスタ341はオフ状態となる。この結果、高電位側電源VCCからMOSトランジスタ341,343,344を介してグランド(GND)に至る貫通電流パス350は形成されないから、pチャネル型MOSトランジスタ343は違反対象から除外される。同様に違反の虞れのあるpチャネル型MOSトランジスタ345については、nチャネル型MOSトランジスタ346がオフ状態とされることで、高電位側電源VCCからMOSトランジスタ342,345,346を介してグランド(GND)に至る貫通電流パスは形成されないから、pチャネル型MOSトランジスタ345は違反対象から除外される。

【0035】

次に、上記CPU31で行われる異電源接続検証処理をフローチャートに従って具体的に説明する。

【0036】

図1には、上記構成のコンピュータ30によって行われる異電源接続検証処理の全体的な流れが示される。この処理では、コンピュータ30に対して与えられた各種情報に基づいて対象回路の異電源接続検証が行われ、その検証結果として、違反MOSトランジスタ情報ファイルが形成される。

【0037】

オペレータによって伝搬電位補正手法の指定、及び擬似違反抑制手法の指定が行われる。伝搬電位補正手法の指定には、トポロジーマッチング使用の有無、及びサブ回路名指定の使用の有無が含まれ、それは伝搬電位補正手法指定ファイル12として記憶装置32に書き込まれる。また、擬似違反抑制手法の指定には、トポロジーマッチング使用の有無、及び貫通電流パス有無判定の使用の有無が含まれ、それは違反抑制手法指定ファイル13として記憶装置32に書き込まれる。尚、伝搬電位補正の対象とされる回路についての回路素子ネットリスト11は、予め記憶装置32に格納されているものとする。

【0038】

先ずCPU31において、回路素子ネットリスト11、伝搬電位補正手法指定ファイル12、違反抑制手法指定ファイル13の読み込み処理が行われる(S101)。そして、CPU31により、伝搬電位補正手法の選択処理が行われ(S102)、電位伝搬と違反の虞れのあるMOSトランジスタ(MOS Tr.)の検索処理が行われる(S103)。さらに、CPU31により、擬似違反抑制手法の選択処理が行われ(S104)、違反抑制されずに残ったMOSトランジスタを異電源リークエラー(OFFされないMOSトランジスタ)としてレポートされ(S105)、それは違反MOSトランジスタ情報ファイル14として記憶装置32に書き込まれる。

【0039】

ここで、上記サブ回路を使用した回路接続例とサブ回路のネットリスト例について説明する。

【0040】

図4には上記サブ回路を使用した回路接続例が示され、図5には上記サブ回路のネットリストが示される。

【0041】

図4に示されるように二つのサブ回路(PUMP)が結合され、サブ回路(PUMP)の端子inからoutへの電位伝搬時は、ΔV加算の属性が指定される場合を考える。この場合のネットリストは、図5に示されるようになる。図5(1)はサブ回路名がPUMPであることが示される。同図(2)では、サブ回路(PUMP)をコールするインスタンス名(XPUMP1,XPUMP2)が示される。同図(3)には実体回路(インスタンス記述)でのin1からout1へのΔV加算属性が付与され、同図(4)には実体回路(インスタンス記述)でのout1からout2へのΔV加算属性が付与される。

【0042】

図2には、図1における「伝搬電位補正手法の選択処理(S102)」の詳細が示される。

【0043】

上記伝搬電位補正手法の選択処理(S102)では、先ず、伝搬電位補正手法指定ファイル12に基づいてサブ回路名指定の使用有無が判別される。この判別で、サブ回路名指定が使用されている(Yes)と判断された場合には、伝搬電位補正回路のサブ回路名での探索と電位補正属性付与が行われる(S201)。そして、伝搬電位補正手法指定ファイルに基づいてトポロジーマッチング使用有無の判別が行われる。この判別において、トポロジーマッチングが使用されている(Yes)と判断された場合には、伝搬電位補正回路のトポロジーマッチングと電位補正属性が付与され(S202)、この伝搬電位補正手法の選択処理が終了される。また、上記サブ回路名指定の使用有無の判別において、サブ回路名指定が使用されない(No)と判断された場合には、上記ステップS201の処理を行うことなく、上記トポロジーマッチング使用有無の判別が行われる。そして、この上記トポロジーマッチング使用有無の判別において、トポロジーマッチングが使用されない(No)と判断された場合には、上記ステップS202の処理を行うことなく、この伝搬電位補正手法の選択処理が終了される。

【0044】

図3には、図2における「伝搬電位補正回路のサブ回路名での探索と電位補正属性付与(S201)」の詳細が示される。

【0045】

上記伝搬電位補正回路のサブ回路名での探索と電位補正属性付与(S201)では、先ず、図5(1)に示されるように指定サブ回路名が一つ選択され(S301)、図5(2)に示されるように指定サブ回路をコールするインスタンスが検索され(S302)、図5(3),(4)に示されるように該当インスタンスでの伝搬時は電位補正(ΔV加算)の属性付与が行われる(S303)。そして、全ての指定サブ回路を選択したか否かの判別が行われ、未だ全ての指定サブ回路の選択を行っていない(No)と判断された場合には、上記ステップS301の処理に戻り、全ての指定サブ回路の選択を行った(Yes)と判断された場合には、この伝搬電位補正回路のサブ回路名での探索と電位補正属性付与が終了される。

【0046】

図6には、図2における「伝搬電位補正回路のトポロジーマッチングと電位補正属性付与(S202)」の詳細が示される。

【0047】

伝搬電位補正回路のトポロジーマッチングと電位補正属性付与(S202)では、先ず、指定の電位伝搬補正回路が一つ選択され(S401)、指定の補正回路側の端子直結素子を基点に、トポロジーのマッチする部分回路が探索される(S402)。そして、既に付与されている属性との競合が無いか否かの判別が行われる。この判別において、競合がない(Yes)と判断された場合には、該当インスタンスでの伝搬時は電位補正(ΔV加算)の属性が付与される(S403)。そして、指定の電位伝搬補正回路を全て選択したか否かの判別が行われる。この判別において、全て選択した(Yes)と判断された場合には、伝搬電位補正回路のトポロジーマッチングと電位補正属性付与の処理が終了され、全て選択していない(No)と判断された場合には、上記ステップS401の処理に戻される。このようにして指定の電位伝搬補正回路の全てについてトポロジーマッチングと電位補正属性付与が行われる。尚、既に付与されている属性との競合が無いか否かの判別において、競合がある(No)と判断された場合には、競合発生インスタンスと競合する補正値をレポートし(S404)、エラーにより全実行が中断される。

【0048】

図7には、図1における「電位伝搬と違反の虞れのあるMOSトランジスタ検索処理(S103)」の詳細が示される。

【0049】

電位伝搬と違反の虞れのあるMOSトランジスタ検索処理では、先ず、オン状態のMOSトランジスタでの固定電位伝搬により、オン状態又はオフ状態が決定されるMOSトランジスタが探索(後方検索)される(S501)。そして、上記ステップS501でオフ状態となるMOSトランジスタが探索される(S502)。上記ステップS502で探索されたMOSトランジスタが、ソース/ドレイン(S/D)方向により電源電圧レベルを伝搬させる対象MOSトランジスタから除外される(S503)。

【0050】

次に、MOSトランジスタのソース・ドレイン間で伝搬する可能性のある電位が伝搬される(S504)。そして、ゲート(G)端子とソース(S)又はドレイン(D)端子に正の電源電圧レベルが伝搬されるpチャネル型MOSトランジスタと、ゲート(G)端子とソース(S)又はドレイン(D)端子に0V以下の電源電圧レベル(グランドレベル)が伝搬されるnチャネル型MOSトランジスタとが探索される(S505)。上記ステップS505で、各電源電圧レベルが印加される場合のその電圧値について、ゲート端子の最小電圧値が、ソース又はドレイン端子の最大電圧値よりも小さくなるpチャネル型MOSトランジスタと、ゲート端子の最大電圧値がソース又はドレイン端子の最小電圧値よりも大きくなるnチャネル型MOSトランジスタとが探索され、それが、違反の虞れのあるMOSトランジスタとしてリストアップされる(S506)。尚、上記ステップS506において、各電源電圧レベルが印加される場合のその電圧値には、伝搬電位補正等により正規の電源電圧レベルとは若干異なる場合も含まれるものとする。

【0051】

図8には、図1における「擬似違反抑制手法の選択処理(S104)」の詳細が示される。

【0052】

擬似違反抑制手法の選択処理では、先ず、トポロジーマッチング使用有無が判別される。この判別において、トポロジーマッチングが使用される(Yes)と判断された場合、トポロジーマッチング処理と、該当するMOSトランジスタの違反除外処理が行われる(S601)。そして、貫通電流パス有無判定の使用有無の判別が行われる。尚、トポロジーマッチングが使用されない場合には、上記ステップS601の処理を行うことなく、貫通電流パス有無判定の使用有無の判別が行われる。この判別において、貫通電流パス有無判定が使用される(Yes)と判断された場合には、貫通電流パス有無判定処理と、該当するMOSトランジスタの違反除外処理とが行われるが(S602)、貫通電流パス有無判定が使用されない(No)と判断された場合には、貫通電流パス有無判定処理と、該当するMOSトランジスタの違反除外処理とは行われない。

【0053】

図9には、図8における「トポロジーマッチング処理と該当MOSトランジスタの違反除外処理(S601)」の詳細が示される。

【0054】

トポロジーマッチング処理と該当MOSトランジスタの違反除外処理では、先ず、違反の虞れのあるMOSトランジスタが一つ選択され(S701)、指定のトポロジー中に含まれるマスク指定されたMOSトランジスタの一つとの対応付けが行われ(S702)。上記ステップS701のMOSトランジスタに繋がる周辺素子から、検証対象回路の回路トポロジーが認識される(S703)。そして、指定トポロジーと一致するか否かの判別が行われる。この判別において、指定トポロジーと一致する(Yes)と判断された場合には、上記ステップS701のMOSトランジスタが違反対象から除外され(S704)、マスク指定された全MOSトランジスタを選択したか否かの判別が行われる。この判別で、マスク指定された全MOSトランジスタを選択していない(No)と判断された場合には、上記ステップS702の処理に戻される。マスク指定された全MOSトランジスタを選択した(Yes)と判断された場合には、違反の虞れのある全MOSトランジスタを選択したか否かの判別が行われ、この判別において、違反の虞れのある全MOSトランジスタを選択した(Yes)と判断されるまで、上記の処理が繰返される。違反の虞れのある全MOSトランジスタを選択した(Yes)と判断された場合には、トポロジーマッチング処理と該当MOSトランジスタの違反除外処理が終了される。

【0055】

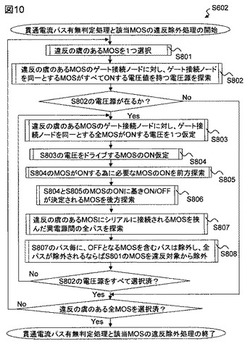

図10には、図8における「貫通電流パス有無判定処理と該当MOSトランジスタの違反除外処理(S602)」の詳細が示される。

【0056】

貫通電流パス有無判定処理と該当MOSトランジスタの違反除外処理では、先ず、違反の虞れのあるMOSトランジスタが一つ選択され(S801)、違反の虞れのあるMOSトランジスタのゲート接続ノードに対して、ゲート接続ノードを同一とするMOSトランジスタが全てオンする電圧値を持つ電圧源が探索される(S802)。そして、上記ステップS802の電圧源が在るか否かの判別が行われる。この判別において、上記ステップS802の電圧源が在る(Yes)と判断された場合には、違反の虞れがあるMOSトランジスタのゲート接続ノードに対して、ゲート接続ノードを同一とする全MOSトランジスタがオンする電圧が一つ仮定される(S803)。そして、上記ステップS803の電圧をドライブするMOSトランジスタのオン状態を仮定する(S804)。このステップS804の処理は、上記手順(2−1)に相当する。上記ステップS804のMOSトランジスタがオンするために必要なMOSトランジスタのオン状態を探索(前方探索)する(S805)。このステップSS805の処理は、上記手順(2−2)に相当する。さらに、上記ステップS804とS805のMOSトランジスタのオン状態に基づいて、オン状態又はオフ状態が決定されるMOSトランジスタを探索(後方探索)する(S806)。このステップS806の処理は、上記手順(2−3)に相当する。そして、違反の虞れのあるMOSトランジスタにシリアルに接続されるMOSトランジスタを挟んだ異電源間の全パスが探索される(S807)。このステップS807の処理は、上記手順(2−4)に相当する。さらに、上記ステップS807のパス毎に、オフ状態となるMOSトランジスタを含むパスが除外され、全パスが除外されるならば上記ステップS801のMOSトランジスタが違反対象から除外される(S808)。このステップS808の処理は、上記手順(2−5)に相当する。そして、上記ステップS802の電圧源を全て選択したか否かの判別が行われ、全て選択した(Yes)と判断されるまで、上記ステップS803〜S808までの処理が繰返される。そして、上記ステップS802の電圧源を全て選択した(Yes)と判断された場合には、違反の虞れのある全MOSトランジスタを選択したか否かの判別が行われ、この判別において、違反の虞れのある全MOSトランジスタを選択した(Yes)と判断されるまで、上記の処理が繰返される。

【0057】

図11には、図10における「電圧源探索処理(S802)」の詳細が示される。

【0058】

上記ステップS802の電圧源探索処理では、先ず、ステップS801における違反の虞れのあるMOSトランジスタのソース又はドレイン方向の接続がトレースされ、違反の虞れがあるMOSトランジスタがpチャンネル型MOSトランジスタであるならば、給電される正の電圧源がリストアップされ、違反の虞れのあるMOSトランジスタがnチャンネル型MOSトランジスタであるならば、給電される0V以下の電圧源がリストアップされる(S901)。例えば図12に示されるように、pチャネル型MOSトランジスタ1201,1202,1203,1205、nチャネル型MOSトランジスタ1204,1206、インバータ1207,1208,1209を含んで、レベルシフタが形成される場合において、今、違反の虞れのあるMOSトランジスタがpチャンネル型MOSトランジスタ1203の場合、給電される正の電圧源、すなわちVCC(3.3V)がリストアップされる。

【0059】

次に、上記ステップS801における違反の虞れのあるMOSトランジスタのゲート接続ノードをドライブするMOSトランジスタのソース又はドレイン方向の接続がトレースされ、違反の虞れのあるMOSトランジスタがpチャネル型MOSトランジスタであるならば、給電される正の電圧源がリストアップされ、違反の虞れのあるMOSトランジスタがnチャンネル型MOSトランジスタならば、給電される0V以下の電圧源がリストアップされる(S902)。例えば図12に示される回路の場合、違反の虞れのあるpチャネル型MOSトランジスタ1203のゲート接続ノードをドライブするMOSトランジスタのソース又はドレイン方向の接続がトレースされ、給電される正の電圧源として、VDD(1.5V)がリストアップされる。

【0060】

次に、上記ステップS901の電圧源と、上記ステップS902の電圧源との組み合わせのうち、各電圧源にドライブされる、その電圧値が異なる電圧源の組み合わせがリストアップされる(S903)。例えば図12に示される回路において、異なる電圧値をドライブする電圧源の組み合わせは、pチャネル型MOSトランジスタ1203のゲートに印加されるVDD(1.5V)、pチャネル型MOSトランジスタ1203のソースに印加されるVCC(3.3V)となる。尚、上記ステップS903において、各電源電圧レベルが印加される場合のその電圧値には、伝搬電位補正等により正規の電源電圧レベルとは若干異なる場合も含まれるものとする。

【0061】

次に、上記ステップS903の電圧源の組み合わせのうち、ステップS801における違反の虞れのあるMOSトランジスタとゲート接続ノードを同一とする、全MOSトランジスタがオンする組み合わせのみがリストアップされる(S904)。例えば図12に示される回路において、ステップS801における違反の虞れのあるpチャネル型MOSトランジスタ1203とゲート接続ノードを同一とする、全MOSトランジスタがオンする組み合わせは、pチャネル型MOSトランジスタ1203のゲートに印加されるVDD(1.5V)と、pチャネル型MOSトランジスタ1203のソースに印加されるVCC(3.3V)とされる。これにより、上記S802の電圧源探索処理が終了される。

【0062】

図13には、図10における電圧仮定処理(S803)の詳細が示される。

【0063】

上記ステップS803の電圧仮定処理では、先ず、上記ステップS904の電圧源の組み合わせが一つ選択される(S1001)。例えば図14に示される構成において、違反の虞れのあるpチャネル型MOSトランジスタ1203とゲート接続ノードを同一とする、全MOSトランジスタがオンする組み合わせとして、pチャネル型MOSトランジスタ1203のゲートに印加されるVDD(1.5V)と、pチャネル型MOSトランジスタ1203のソースに印加されるVCC(3.3V)とされる。

【0064】

次に、上記ステップS1001で選択された電源の組み合わせに従い、違反の虞れのあるMOSトランジスタのゲート端子に対して、その電圧源の伝搬を仮定する(S1002)。例えば図14に示される構成においては、違反の虞れのあるpチャネル型MOSトランジスタ1203のゲート端子にVDD(1.5V)の伝搬が仮定される。これにより、上記電圧仮定処理(S803)が終了される。

【0065】

図15には、図10におけるMOSトランジスタのオン仮定処理(S804)の詳細が示される。

【0066】

上記ステップS804のMOSトランジスタのオン仮定処理では、先ず、上記ステップS1002の電圧源を伝搬するMOSトランジスタのオン状態を仮定する(S1101)。例えば図16に示される回路において、161で示されるように、インバータ1209においてVDD(1.5V)をドライブするpチャンネル型MOSトランジスタのオン状態が仮定される。

【0067】

次に、上記ステップS1002のMOSトランジスタがオンするための上記ステップS1002のMOSトランジスタのゲート端子の電圧値が認識される(S1102)。例えば図16において、162で示されるように、上記インバータ1209においてVDD(1.5V)をドライブするpチャンネル型MOSトランジスタがオンするためのゲート電圧値は「0V」と認識される。これにより、上記ステップS804のMOSトランジスタのオン仮定処理が終了される。

【0068】

図17には、図10における前方探索処理(S805)の詳細が示される。

【0069】

前方探索処理(S805)では、先ず、ステップS1102又はS1204のMOSトランジスタのゲート端子への接続ノードをドライブするMOSトランジスタとそのMOSトランジスタに給電される電圧源の探索が行われる(S1201)。例えば図18に示されるインバータ1209におけるpチャンネル型MOSトランジスタのゲート端子への接続ノードをドライブするMOSトランジスタは、インバータ1208におけるpチャネル型MOSトランジスタ1801とそれに直列接続されたnチャネル型MOSトランジスタ1802である。そしてこのインバータ1208におけるMOSトランジスタに給電される電圧源は、VDD(1.5V)と、0Vとされる。

【0070】

そして、上記ステップS1201で探索されたMOSトランジスタのうち、上記ステップS1102で認識されたゲート端子に必要な電圧値を供給可能なMOSトランジスタを全て選択する(S1202)。例えば図18において、インバータ1208を形成するMOSトランジスタ1801,1802のうち、インバータ1209内のpチャンネル型MOSトランジスタのゲートに0Vを供給可能なMOSトランジスタとして、nチャンネル型MOSトランジスタ1802が選択される。

【0071】

次に、上記ステップS1202で選択された全MOSトランジスタのオン状態をMOSトランジスタの探索(前方探索)により仮定する(S1203)。例えば図18においては、nチャンネル型MOSトランジスタ1802のオン状態が仮定される。

【0072】

そして、上記ステップS1202の各MOSトランジスタがオンするための上記ステップS1202の各MOSトランジスタのゲート端子の電圧値を認識する(S1204)。例えば図18においては、MOSトランジスタ1801,1802のゲート端子に供給される正の電圧が、必要な電圧値として認識される。

【0073】

次に、探索(前方探索)が終了していないMOSトランジスタが存在するか否かの判別が行われ、この判別において、探索(前方探索)が終了していないMOSトランジスタは存在しない(Yes)と判断されるまで、上記ステップS1201〜S1204までの処理が繰返される。

【0074】

図19には、上記後方探索処理(S806)の詳細が示される。

【0075】

後方探索処理(S806)では、先ず、ステップS1101とS1203、又はS1302でオン状態と仮定されたMOSトランジスタ1802でドライブされる電圧源(0V)と、その電圧値が後方のMOSトランジスタへ伝搬される(S1301)。例えば図20において、0Vがインバータ1209のpチャンネル型MOSトランジスタに伝達され、このpチャンネル型MOSトランジスタがオンされることにより、VDD(1.5V)がpチャンネル型MOSトランジスタ1203に伝達される。また、0Vがpチャンネル型MOSトランジスタ1205及びnチャンネル型MOSトランジスタ1206に伝達される。

【0076】

次に、上記ステップS1201で伝搬された電圧値がゲート端子へ到達するMOSトランジスタについて、オン又はオフが決定されるMOSトランジスタが探索(後方探索)される(S1302)。例えば図20において、pチャンネル型MOSトランジスタ1202,1203,1205及びnチャンネル型MOSトランジスタ1204がオン状態と判定され、pチャンネル型MOSトランジスタ1201及びnチャンネル型MOSトランジスタ1206がオフ状態と判定される。

【0077】

そして、探索(後方探索)が終了していないMOSトランジスタが存在するか否かの判別が行われ、この判別で探索(後方探索)が終了していないMOSトランジスタが存在しない(No)と判断されまで、上記ステップS1301,S1302の処理が繰返される。

【0078】

図21には、上記異電圧間の全パス探索処理(S807)の詳細が示される。

【0079】

異電圧間の全パス探索処理(S807)では、先ず、上記ステップS801で選択された違反の虞れのあるMOSトランジスタのソース又はドレイン方向の接続がトレースされ、ソース端子又はドレイン端子それぞれに給電される電圧源がリストアップされる(S1401)。例えば図22において、違反の虞れのあるMOSトランジスタ1203のソース方向の接続がトレースされることにより、VCC(3.3V)がリストアップされ、違反の虞れのあるMOSトランジスタ1203のドレイン方向の接続がトレースされることにより、0Vがリストアップされる。

【0080】

次に、上記ステップS1401でのソース端子とドレイン端子に供給される電圧源の組み合わせのうち、異なる電圧源が供給されるような異電圧源のパスがリストアップされる(S1402)。例えば図22において、VCC(3.3V)と0Vとは、互いに異なる電圧源であり、違反の虞れのあるMOSトランジスタ1203を介してVCC(3.3V)から0Vに至るパス221がリストアップされる。

【0081】

図23には、上記違反対象からの除外処理(S808)の詳細が示される。

【0082】

違反対象からの除外処理(S808)では、先ず、上記ステップS1402のパス、すなわち、上記ステップS1401でのソース端子とドレイン端子に供給される電圧源の組み合わせのうち、異なる電圧源が供給されるような異電圧源パスの一つを選択する。例えば図24において、nチャネル型MOSトランジスタ1204がオン状態とされることでpチャネル型MOSトランジスタ1203のドレイン端子は0Vが供給され、さらにこのpチャネル型MOSトランジスタ1203のソース端子にはVCC(3.3V)が供給されることから、VCC(3.3V)から上記pチャネル型MOSトランジスタ1203及びnチャネル型MOSトランジスタ1204を介してグランドに至るパスが選択される(S1501)。そして、上記ステップS1501で選択されたパスを構成するMOSトランジスタのうち、オフ判定となっているMOSトランジスタが在るか否かの判別が行われる。この判別において、オフ判定となっているMOSトランジスタが在る(Yes)と判定された場合には、上記ステップS1402のパスを全て選択済みか否かの判別が行われ、上記ステップS1402のパスを全て選択済みと判断された場合に、上記ステップS801で選択した違反の虞れのあるMOSトランジスタが違反対象から除外される(S1502)。例えば図24において、MOSトランジスタ1201がオフ判定とされるMOSトランジスタであり、オフ判定とされるMOSトランジスタが存在するから、このMOSトランジスタ1201が存在するパス224は、貫通電流が流れるパスとはなり得ない。また、図24では、他に上記ステップS1402のパスが存在しないため、現在、選択されている違反の虞れがあるMOSトランジスタのみが、上記ステップS1502の処理で違反対象から除外される。このようにして違反対象からの除外処理(S808)が行われる。

【0083】

上記の例によれば、以下の作用効果を得ることができる。

【0084】

(1)トポロジーマッチング処理と該当MOSトランジスタの違反除外処理では、指定のトポロジー中に含まれるマスク指定されたMOSトランジスタの一つとの対応付けが行われ(S702)、検証対象回路の回路トポロジーが認識される(S703)。そして、指定トポロジーと一致するか否かの判別が行われ、指定トポロジーと一致する(Yes)と判断された場合には、上記ステップS701のMOSトランジスタが違反対象から除外される(S704)。このようにトポロジーと一致する場合には違反対象から除外され、トポロジーと一致しない場合には違反対象から除外されない。その結果、真の違反を指摘することができる。

【0085】

(2)ポンプ回路やレギュレータに適用される昇圧回路のトポロジー情報(MOSトランジスタのゲートサイズ等のパラメータ情報を含む)が事前情報として付与されている場合には、回路認識の都度、ΔV(指定値)分の電位を加算して伝搬することで、内部電源を考慮した検証が可能とされる。従って、出力電圧レベルが変動する場合にも、擬似違反を排除することができる。

【0086】

(3)貫通電流パスの有無を判定し、貫通電流パスが無い場合には、違反の虞れのあるMOSトランジスタが違反対象から除外されることから、貫通電流パスの検出によって擬似違反を排除することができる。

【0087】

以上本発明者によってなされた発明を具体的に説明したが、本発明はそれに限定されるものではなく、その要旨を逸脱しない範囲で種々変更可能であることはいうまでもない。

【図面の簡単な説明】

【0088】

【図1】コンピュータによって行われる異電源接続検証処理の全体的な流れを示すフローチャートである。

【図2】図1における主要処理の詳細なフローチャートである。

【図3】図2における主要処理の詳細なフローチャートである。

【図4】サブ回路を使用した回路接続例の説明図である。

【図5】上記サブ回路のネットリストを示す説明図である。

【図6】図2における主要処理の詳細なフローチャートである。

【図7】図1における主要処理の詳細なフローチャートである。

【図8】図1における主要処理の詳細なフローチャートである。

【図9】図8における主要処理の詳細なフローチャートである。

【図10】図8における主要処理の詳細なフローチャートである。

【図11】図10における主要処理の詳細なフローチャートである。

【図12】図10における主要処理を説明するための回路図である。

【図13】図10における主要処理の詳細なフローチャートである。

【図14】図13における主要処理を説明するための回路図である。

【図15】図10における主要処理の詳細なフローチャートである。

【図16】図15における主要処理を説明するための回路図である。

【図17】図10における主要処理の詳細なフローチャートである。

【図18】図17における主要処理を説明するための回路図である。

【図19】図10における主要処理の詳細なフローチャートである。

【図20】図19における主要処理を説明するための回路図である。

【図21】図10における主要処理の詳細なフローチャートである。

【図22】図21における主要処理を説明するための回路図である。

【図23】図10における主要処理の詳細なフローチャートである。

【図24】図21における主要処理を説明するための回路図である。

【図25】本発明の比較対象とされる検証方法を説明するための回路図である。

【図26】本発明の比較対象とされる検証方法を説明するための回路図である。

【図27】本発明の比較対象とされる検証方法を説明するための回路図である。

【図28】本発明の比較対象とされる検証方法を説明するための回路図である。

【図29】本発明の比較対象とされる検証方法を説明するための回路図である。

【図30】本発明にかかる異電源接続検証方法における主要処理を説明するための回路図である。

【図31】本発明にかかる異電源接続検証方法における主要処理を説明するための回路図である。

【図32】本発明にかかる異電源接続検証方法における主要処理を説明するための回路図である。

【図33】本発明にかかる異電源接続検証方法における主要処理を説明するための回路図である。

【図34】本発明にかかる異電源接続検証方法における主要処理を説明するための回路図である。

【図35】本発明にかかる異電源接続検証用方法が実施されるコンピュータの全体的な構成例ブロック図である。

【符号の説明】

【0089】

31 CPU

32 記憶装置

33 入力装置

34 表示装置

35 メモリ

36 バス

【技術分野】

【0001】

本発明は、異電源接続検証技術、さらには異電源接続の検出結果に対して貫通電流パスを検出して、真のエラーか否かを判定を行うための技術に関する。

【背景技術】

【0002】

電子回路においては、低電圧で動作する回路と高電圧で動作する回路との間で信号のやり取りが行われる場合がある。かかる場合、低電圧で動作する回路と高電圧で動作する回路との間に、電圧レベルを変換するための昇圧回路(レベルシフタ)が挿入される。また、内部の動作電圧と出力電圧レベルとが異なる場合にも、出力段に昇圧または減圧のためのレベルシフタが必要である。レベルシフタが必要な電子回路において、製造前の設計段階でレベルシフタの入れ忘れを漏れなくチェックするために、回路全体に対して回路シミュレーションが行われる。このような回路シミュレーションの一例として、複数の電源で駆動される多電源電子回路において、その設計の際に、レベルシフタの入れ忘れ、および各回路に供給すべき電源の誤りを、アナログ回路を含む設計か否か、セルライブラリ中のセルを使用した設計か否かにかかわらず、短時間で確実に発見できるようにした多電源電子回路の検証方法として、特許文献1記載の技術が知られている。この技術によれば、読み込んだネットリストに基づき、全ての電源と全ての入力ポートとから回路内の配線の経路探索が行われ、回路中の個々の回路素子およびノードが、いずれの電源または入力ポートで駆動されるかがそれぞれ判定されてマーキングされ、さらに、回路図上の個々の回路素子、回路ブロック、ノードを、そのマーキング結果に基づいて駆動される電源別または入力ポート別に色分け表示される。

【0003】

【特許文献1】特開2005−190442号公報

【発明の開示】

【発明が解決しようとする課題】

【0004】

上記従来技術によれば、例えば図25に示される回路において、電源(VDD,VCC)と入力ポート(IN1、IN2、IN3)から接続トレース(色分け表示)され、素子マーキングの上、問題となる可能性のある箇所(251で示される)が、違反とするルール設定に基づいて指摘される。上記「問題となる可能性のある箇所」を指摘するルール設定は二通りある。第1のルール設定は、図26に示されるように、MOSトランジスタのソース端子又はドレイン端子と、ゲート端子にかかる電源名で、違反とする接続関係を定義するものである。第2のルール設定は、MOSトランジスタのソース端子又はドレイン端子と、ゲート端子とにかかる電圧の差が、許容電圧範囲を越えた場合に違反とする接続関係を定義する。例えば図27に示されるように、VDDを1.5V、VCCを3.3Vとした場合に、それらの電圧差(|3.3−1.5|)が所定の許容範囲(0.01V)を越えた場合に違反として指摘される。

【0005】

しかしながら、上記従来技術について本願発明者が検討したところ、実際には違反とすべきではないのに違反とされる場合(これを「擬似違反」という)が生じるおそれのあることが見いだされた。例えば図28に示される構成のレベルシフタにおいて、pチャネル型MOSトランジスタ281,282がクロスカップルされており、283,284で示されるパス中のMOSトランジスタが全てオンすることは無く、リーク電流は発生しないのに、上記第1のルール設定又は上記第2のルール設定により、pチャネル型MOSトランジスタ281,282が違反とされてしまう。

【0006】

また、実際にMOSトランジスタを使用した電子回路では、レベルシフタ以外にも、内部電圧を昇圧する回路、例えば図29の(A)に示されるポンプ回路や、図29の(B)に示されるレギュレータが組み込まれるケースが多くある。これらの回路は、MOSトランジスタのソース・ドレイン間を介して出力側にΔVが加算されることにより、出力電圧レベルが変動するため、上記第1のルール設定や上記第2のルール設定は対応できない。

【0007】

本発明の目的は、真のエラーか否かの判定を可能とする検証技術を提供することにある。

【0008】

本発明の前記並びにその他の目的と新規な特徴は本明細書の記述及び添付図面から明らかになるであろう。

【課題を解決するための手段】

【0009】

本願において開示される発明のうち代表的なものについて簡単に説明すれば下記のとおりである。

【0010】

すなわち、異電源接続検証は、中央処理装置を備えたコンピュータを用いて行われる。上記中央処理装置は、電位伝搬と違反の虞れのあるトランジスタを検索する第1処理と、上記第1処理の結果に基づいて、擬似違反を抑制する第2処理とを含む。上記第2処理は、上記検証対象回路の貫通電流パスの有無を判定してトランジスタの違反を除外する第3処理を含む。上記第3処理は、違反の虞れがあるトランジスタとゲート接続ノードを同一とするトランジスタを全てオン状態と仮定する第1ステップと、上記第1ステップで仮定されたトランジスタがオンするために必要なトランジスタのオン状態を後方探索する第2ステップと、上記第1ステップと上記第2ステップでのトランジスタの伝搬電位に基づき、オン状態又はオフ状態が決定される周辺トランジスタを探索する第3ステップとを含む。貫通電流パスの有無を判定し、貫通電流パスが無い場合には、擬似違反のトランジスタが違反対象から除外される。

【発明の効果】

【0011】

本願において開示される発明のうち代表的なものによって得られる効果を簡単に説明すれば下記の通りである。

【0012】

すなわち、擬似違反のトランジスタが違反対象から除外されることにより、真のエラーか否かの判定を可能とする検証技術を提供することができる。

【発明を実施するための最良の形態】

【0013】

1.代表的な実施の形態

先ず、本願において開示される発明の代表的な実施の形態について概要を説明する。代表的な実施の形態についての概要説明で括弧を付して参照する図面の参照符号はそれが付された構成要素の概念に含まれるものを例示するに過ぎない。

【0014】

〔1〕本発明の代表的な実施の形態に係る異電源接続検証方法は、予め設定されたプログラムを実行する中央処理装置(31)を備えたコンピュータ(30)を用いて行われる。上記中央処理装置は、電位伝搬と違反の虞れのあるトランジスタを検索する第1処理(S103)と、上記第1処理の結果に基づいて、擬似違反を抑制する第2処理(S104)とを含む。上記第2処理は、上記検証対象回路の貫通電流パスの有無を判定してトランジスタの違反を除外する第3処理(S602)を含む。上記第3処理は、違反の虞れがあるトランジスタとゲート接続ノードを同一とするトランジスタを全てオン状態と仮定する第1ステップ(S804)と、上記第1ステップで仮定されたトランジスタがオンするために必要なトランジスタのオン状態を探索(前方探索)する第2ステップ(S805)と、上記第1ステップと上記第2ステップでのトランジスタの伝搬電位に基づき、オン状態又はオフ状態が決定される周辺トランジスタを探索(後方探索)する第3ステップと(S806)を含む。

【0015】

上記の構成によれば、貫通電流パスの有無を判定し、貫通電流パスが無い場合には、違反の虞れのあるMOSトランジスタが違反対象から除外されることから、貫通電流パスの検出によって擬似違反を排除することができる。

【0016】

〔2〕さらに上記第3処理には、違反の虞れのあるMOSトランジスタにシリアルに接続されるトランジスタを挟んだ異電源間の全てのパスを探索する第4ステップ(S807)と、上記第4ステップで探索されたパス毎に、オフ状態となるトランジスタを含むパスを除外し、全てのパスが除外された場合に、違反の虞れのあるトランジスタを違反対象から除外する第5ステップ(S808)とを含めることができる。

【0017】

〔3〕上記第3処理は、トポロジーマッチングによりトランジスタの違反を除外する第4処理(S601)を含む。上記第4処理は、事前情報として付与されたトポロジーと上記異電源接続検証を可能とする異電源接続検証用プログラムとが一致するか否かを判別し、その判別結果に基づいて該当トランジスタを違反対象から除外する第6ステップ(S704)を含む。

【0018】

〔4〕上記第1処理は、オン状態のトランジスタでの固定電位伝搬により、オン状態又はオフ状態が決定されるトランジスタを探索(後方探索)する第6ステップ(S501)と、上記第6ステップでオフ状態となるトランジスタを探索する第7ステップ(S502)と、上記第7ステップで探索されたトランジスタを、ソース又はドレイン方向により電源電圧レベルを伝搬させる対象トランジスタから除外する第8ステップ(S503)とを含む。そして上記第1処理は、トランジスタのソース・ドレイン間で伝搬する可能性のある電位を伝搬させる第9ステップ(S504)と、ゲート端子とソース端子又はドレイン端子とに正の電源電圧レベルが伝搬されるpチャネル型MOSトランジスタと、ゲート端子とソース端子又はドレイン端子に0V以下の電源電圧レベルが伝搬されるnチャネル型MOSトランジスタとを探索する第10ステップ(S505)とを含む。さらに上記第1処理は、上記第10ステップで、各電源電圧レベルが印加される場合のその電圧値について、ゲート端子の最小電圧値が、ソース又はドレイン端子の最大電圧値よりも小さくなるトランジスタと、ゲート端子の最大電圧値がソース又はドレイン端子の最小電圧値よりも大きくなるトランジスタとを探索し、それを、違反の虞れのあるトランジスタとしてリストアップする第11ステップ(S506)とを含む。

【0019】

2.実施の形態の説明

次に、実施の形態について更に詳述する。

【0020】

図35には、異電源接続検証のためのプログラムが実行されるコンピュータの構成例が示される。図35に示されるコンピュータ30は、特に制限されないが、CPU(中央処理装置)31、記憶装置32、入力装置33、表示装置34、及メモリ35を含み、それらは、バス36を介して互いに結合されている。CPU31は、所定のプログラムを実行する。本例においてこのCPU31は、異電源接続検証のためのプログラムを実行する。記憶装置32には、上記CPU31で実行される各種プログラムや、チェック対象回路のネットリストなど、各種情報が格納される。特に制限されないが、記憶装置32の記録媒体321は、磁気ディスクであり、記憶装置32に着脱自在とされる。記録媒体321は、記憶装置32に装着された状態で、コンピュータ30によって読み書き可能とされる。

【0021】

CPU31は、異電源接続検証のためのプログラムを記憶装置32の記録媒体321から読み出して実行することで、所定の演算処理を行う。メモリ35は、上記CPU31における演算処理の作業領域などに利用される。このメモリ35には、例えばランダムアクセス可能なRAM(ランダム・アクセス・メモリ)とされる。入力装置33は、このコンピュータに対して各種情報の入力を可能とするもので、この入力装置33には、キーボードやマウス等の各種入力デバイスが含まれる。表示装置34は、このコンピュータ30での各種情報を必要に応じて表示するもので、例えば液晶ディスプレイ装置とされる。

【0022】

ここで、上記CPU31で行われる異電源接続検証における基本的な処理について説明する。

【0023】

この異電源接続検証では、トポロジーマッチング又はサブ回路名により、特殊回路を事前認識させる第1手法と、貫通電流パスの有無を判定し、擬似違反を抑制する第2手法とが採用される。

【0024】

〔1〕第1手法

例えば図32に示されるように、レベルシフタ324の回路トポロジーと違反をマスクするMOSトランジスタの情報が事前情報として予め付与されているものとする。この場合、図32における回路321,322は、上記レベルシフタ324の回路トポロジーと一致するため、違反対象から除外される。回路323は、上記レベルシフタ324の回路トポロジーと一致しないため、違反対象から除外されない。このようにレベルシフタを認識した場合には、擬似違反の抑制に使用され、その結果、真の違反だけを指摘することができる。

【0025】

また、図33に示されるように、ポンプ回路やレギュレータに適用される昇圧回路334のトポロジー情報(MOSトランジスタのゲートサイズ等のパラメータ情報を含む)が事前情報として付与されている場合には、回路331〜333は昇圧回路334と一致するため、昇圧回路と認識される。そして、335〜337で示されるように、回路認識の都度、ΔV(指定値)分の電位を加算して伝搬することで、内部電源を考慮した検証が可能とされる。回路333の出力node_outは、3.3V+(ΔV×N)Vの内部電源として認識可能とされる。また、後段回路を内部電源の電位でチェックすることもできる。尚、ΔVは負の場合もあり得る。

【0026】

上記第1手法において、例えばレベルシフタを認識した場合には、擬似違反の抑制に使用され、ポンプ回路やレギュレータを認識した場合には、伝搬電位の補正に使用される。

【0027】

〔2〕第2手法

違反の虞れのあるMOSトランジスタに対して以下の手順により貫通電流の有無を判定する。

【0028】

(2−1)先ず、違反の虞れのあるMOSトランジスタとゲート接続ノードを同一とする全MOSトランジスタをオン(導通)状態と仮定する。

【0029】

(2−2)上記手順(2−1)において、上記MOSトランジスタがオンするために必要とされるMOSトランジスタのオン状態を探索(前方探索)する。例えば図30に示されるように、3個のインバータが結合される場合、以下のように探索(前方探索)される。

【0030】

pチャネル型MOSトランジスタ301とnチャネル型MOSトランジスタ302が結合されて第1インバータが形成され、pチャネル型MOSトランジスタ303とnチャネル型MOSトランジスタ304とが結合されて第2インバータが形成され、pチャネル型MOSトランジスタ305とnチャネル型MOSトランジスタ306とが結合されて第3インバータが形成される。ここで、pチャネル型MOSトランジスタ305をオン状態と仮定した場合、その前段に配置されているnチャネル型MOSトランジスタ304がオン状態であることが必要であり、また、そのためにはpチャネル型MOSトランジスタ301がオン状態であることが必要である。このようにしてMOSトランジスタのオン状態が探索(前方探索)される。

【0031】

(2−3)上記手順(2−1)と(2−2)におけるMOSトランジスタのオン状態に基づいてオン状態又はオフ状態が決定されるMOSトランジスタを探索(後方探索)する。例えば図31に示されるように、pチャネル型MOSトランジスタ301がオン状態であれば、高電位側電源VDDからの電位伝搬により、pチャネル型MOSトランジスタ303のオフ状態が決定され、nチャネル型MOSトランジスタ304のオン状態が決定される。それにより、後段へのグランド(GND)レベルの電位伝搬が行われるため、pチャネル型MOSトランジスタ305のオン状態が決定され、nチャネル型MOSトランジスタ306のオフ状態が決定される。このようにして、オン状態又はオフ状態が決定されるMOSトランジスタの探索(後方探索)が行われる。

【0032】

(2−4)違反とされるMOSトランジスタに直列接続されるMOSトランジスタを挟んだ異電源間の全パスを探索する。

【0033】

(2−5)上記手順(2−4)で探索されたパス毎に、オフ状態とされるMOSトランジスタを含むパスを除外し、全パスが除外された場合には、違反の虞れのあるMOSトランジスタを違反対象から除外する。換言すれば、上記手順(2−4)で探索されたパス毎に、貫通電流パスの有無が判定され、貫通電流パスが無い場合には、違反の虞れのあるMOSトランジスタが違反対象から除外される。例えば図34に示されるように、pチャネル型MOSトランジスタ341,342,343,345、nチャネル型MOSトランジスタ344,346、インバータ347,348,349を含んで、レベルシフタが形成される場合には、次のようにMOSトランジスタが違反対象から除外される。

【0034】

pチャンネル型MOSトランジスタ343,345に違反の虞れがあるものとする。MOSトランジスタ343,344のゲートには、高電位側電源VDD(1.5V)の電圧が印加されているものと仮定し、このMOSトランジスタ343,344の双方がオン状態と仮定する。この場合、pチャネル型MOSトランジスタ342はオン状態、pチャネル型MOSトランジスタ345はオン状態とされるから、pチャネル型MOSトランジスタ341はオフ状態となる。この結果、高電位側電源VCCからMOSトランジスタ341,343,344を介してグランド(GND)に至る貫通電流パス350は形成されないから、pチャネル型MOSトランジスタ343は違反対象から除外される。同様に違反の虞れのあるpチャネル型MOSトランジスタ345については、nチャネル型MOSトランジスタ346がオフ状態とされることで、高電位側電源VCCからMOSトランジスタ342,345,346を介してグランド(GND)に至る貫通電流パスは形成されないから、pチャネル型MOSトランジスタ345は違反対象から除外される。

【0035】

次に、上記CPU31で行われる異電源接続検証処理をフローチャートに従って具体的に説明する。

【0036】

図1には、上記構成のコンピュータ30によって行われる異電源接続検証処理の全体的な流れが示される。この処理では、コンピュータ30に対して与えられた各種情報に基づいて対象回路の異電源接続検証が行われ、その検証結果として、違反MOSトランジスタ情報ファイルが形成される。

【0037】

オペレータによって伝搬電位補正手法の指定、及び擬似違反抑制手法の指定が行われる。伝搬電位補正手法の指定には、トポロジーマッチング使用の有無、及びサブ回路名指定の使用の有無が含まれ、それは伝搬電位補正手法指定ファイル12として記憶装置32に書き込まれる。また、擬似違反抑制手法の指定には、トポロジーマッチング使用の有無、及び貫通電流パス有無判定の使用の有無が含まれ、それは違反抑制手法指定ファイル13として記憶装置32に書き込まれる。尚、伝搬電位補正の対象とされる回路についての回路素子ネットリスト11は、予め記憶装置32に格納されているものとする。

【0038】

先ずCPU31において、回路素子ネットリスト11、伝搬電位補正手法指定ファイル12、違反抑制手法指定ファイル13の読み込み処理が行われる(S101)。そして、CPU31により、伝搬電位補正手法の選択処理が行われ(S102)、電位伝搬と違反の虞れのあるMOSトランジスタ(MOS Tr.)の検索処理が行われる(S103)。さらに、CPU31により、擬似違反抑制手法の選択処理が行われ(S104)、違反抑制されずに残ったMOSトランジスタを異電源リークエラー(OFFされないMOSトランジスタ)としてレポートされ(S105)、それは違反MOSトランジスタ情報ファイル14として記憶装置32に書き込まれる。

【0039】

ここで、上記サブ回路を使用した回路接続例とサブ回路のネットリスト例について説明する。

【0040】

図4には上記サブ回路を使用した回路接続例が示され、図5には上記サブ回路のネットリストが示される。

【0041】

図4に示されるように二つのサブ回路(PUMP)が結合され、サブ回路(PUMP)の端子inからoutへの電位伝搬時は、ΔV加算の属性が指定される場合を考える。この場合のネットリストは、図5に示されるようになる。図5(1)はサブ回路名がPUMPであることが示される。同図(2)では、サブ回路(PUMP)をコールするインスタンス名(XPUMP1,XPUMP2)が示される。同図(3)には実体回路(インスタンス記述)でのin1からout1へのΔV加算属性が付与され、同図(4)には実体回路(インスタンス記述)でのout1からout2へのΔV加算属性が付与される。

【0042】

図2には、図1における「伝搬電位補正手法の選択処理(S102)」の詳細が示される。

【0043】

上記伝搬電位補正手法の選択処理(S102)では、先ず、伝搬電位補正手法指定ファイル12に基づいてサブ回路名指定の使用有無が判別される。この判別で、サブ回路名指定が使用されている(Yes)と判断された場合には、伝搬電位補正回路のサブ回路名での探索と電位補正属性付与が行われる(S201)。そして、伝搬電位補正手法指定ファイルに基づいてトポロジーマッチング使用有無の判別が行われる。この判別において、トポロジーマッチングが使用されている(Yes)と判断された場合には、伝搬電位補正回路のトポロジーマッチングと電位補正属性が付与され(S202)、この伝搬電位補正手法の選択処理が終了される。また、上記サブ回路名指定の使用有無の判別において、サブ回路名指定が使用されない(No)と判断された場合には、上記ステップS201の処理を行うことなく、上記トポロジーマッチング使用有無の判別が行われる。そして、この上記トポロジーマッチング使用有無の判別において、トポロジーマッチングが使用されない(No)と判断された場合には、上記ステップS202の処理を行うことなく、この伝搬電位補正手法の選択処理が終了される。

【0044】

図3には、図2における「伝搬電位補正回路のサブ回路名での探索と電位補正属性付与(S201)」の詳細が示される。

【0045】

上記伝搬電位補正回路のサブ回路名での探索と電位補正属性付与(S201)では、先ず、図5(1)に示されるように指定サブ回路名が一つ選択され(S301)、図5(2)に示されるように指定サブ回路をコールするインスタンスが検索され(S302)、図5(3),(4)に示されるように該当インスタンスでの伝搬時は電位補正(ΔV加算)の属性付与が行われる(S303)。そして、全ての指定サブ回路を選択したか否かの判別が行われ、未だ全ての指定サブ回路の選択を行っていない(No)と判断された場合には、上記ステップS301の処理に戻り、全ての指定サブ回路の選択を行った(Yes)と判断された場合には、この伝搬電位補正回路のサブ回路名での探索と電位補正属性付与が終了される。

【0046】

図6には、図2における「伝搬電位補正回路のトポロジーマッチングと電位補正属性付与(S202)」の詳細が示される。

【0047】

伝搬電位補正回路のトポロジーマッチングと電位補正属性付与(S202)では、先ず、指定の電位伝搬補正回路が一つ選択され(S401)、指定の補正回路側の端子直結素子を基点に、トポロジーのマッチする部分回路が探索される(S402)。そして、既に付与されている属性との競合が無いか否かの判別が行われる。この判別において、競合がない(Yes)と判断された場合には、該当インスタンスでの伝搬時は電位補正(ΔV加算)の属性が付与される(S403)。そして、指定の電位伝搬補正回路を全て選択したか否かの判別が行われる。この判別において、全て選択した(Yes)と判断された場合には、伝搬電位補正回路のトポロジーマッチングと電位補正属性付与の処理が終了され、全て選択していない(No)と判断された場合には、上記ステップS401の処理に戻される。このようにして指定の電位伝搬補正回路の全てについてトポロジーマッチングと電位補正属性付与が行われる。尚、既に付与されている属性との競合が無いか否かの判別において、競合がある(No)と判断された場合には、競合発生インスタンスと競合する補正値をレポートし(S404)、エラーにより全実行が中断される。

【0048】

図7には、図1における「電位伝搬と違反の虞れのあるMOSトランジスタ検索処理(S103)」の詳細が示される。

【0049】

電位伝搬と違反の虞れのあるMOSトランジスタ検索処理では、先ず、オン状態のMOSトランジスタでの固定電位伝搬により、オン状態又はオフ状態が決定されるMOSトランジスタが探索(後方検索)される(S501)。そして、上記ステップS501でオフ状態となるMOSトランジスタが探索される(S502)。上記ステップS502で探索されたMOSトランジスタが、ソース/ドレイン(S/D)方向により電源電圧レベルを伝搬させる対象MOSトランジスタから除外される(S503)。

【0050】

次に、MOSトランジスタのソース・ドレイン間で伝搬する可能性のある電位が伝搬される(S504)。そして、ゲート(G)端子とソース(S)又はドレイン(D)端子に正の電源電圧レベルが伝搬されるpチャネル型MOSトランジスタと、ゲート(G)端子とソース(S)又はドレイン(D)端子に0V以下の電源電圧レベル(グランドレベル)が伝搬されるnチャネル型MOSトランジスタとが探索される(S505)。上記ステップS505で、各電源電圧レベルが印加される場合のその電圧値について、ゲート端子の最小電圧値が、ソース又はドレイン端子の最大電圧値よりも小さくなるpチャネル型MOSトランジスタと、ゲート端子の最大電圧値がソース又はドレイン端子の最小電圧値よりも大きくなるnチャネル型MOSトランジスタとが探索され、それが、違反の虞れのあるMOSトランジスタとしてリストアップされる(S506)。尚、上記ステップS506において、各電源電圧レベルが印加される場合のその電圧値には、伝搬電位補正等により正規の電源電圧レベルとは若干異なる場合も含まれるものとする。

【0051】

図8には、図1における「擬似違反抑制手法の選択処理(S104)」の詳細が示される。

【0052】

擬似違反抑制手法の選択処理では、先ず、トポロジーマッチング使用有無が判別される。この判別において、トポロジーマッチングが使用される(Yes)と判断された場合、トポロジーマッチング処理と、該当するMOSトランジスタの違反除外処理が行われる(S601)。そして、貫通電流パス有無判定の使用有無の判別が行われる。尚、トポロジーマッチングが使用されない場合には、上記ステップS601の処理を行うことなく、貫通電流パス有無判定の使用有無の判別が行われる。この判別において、貫通電流パス有無判定が使用される(Yes)と判断された場合には、貫通電流パス有無判定処理と、該当するMOSトランジスタの違反除外処理とが行われるが(S602)、貫通電流パス有無判定が使用されない(No)と判断された場合には、貫通電流パス有無判定処理と、該当するMOSトランジスタの違反除外処理とは行われない。

【0053】

図9には、図8における「トポロジーマッチング処理と該当MOSトランジスタの違反除外処理(S601)」の詳細が示される。

【0054】

トポロジーマッチング処理と該当MOSトランジスタの違反除外処理では、先ず、違反の虞れのあるMOSトランジスタが一つ選択され(S701)、指定のトポロジー中に含まれるマスク指定されたMOSトランジスタの一つとの対応付けが行われ(S702)。上記ステップS701のMOSトランジスタに繋がる周辺素子から、検証対象回路の回路トポロジーが認識される(S703)。そして、指定トポロジーと一致するか否かの判別が行われる。この判別において、指定トポロジーと一致する(Yes)と判断された場合には、上記ステップS701のMOSトランジスタが違反対象から除外され(S704)、マスク指定された全MOSトランジスタを選択したか否かの判別が行われる。この判別で、マスク指定された全MOSトランジスタを選択していない(No)と判断された場合には、上記ステップS702の処理に戻される。マスク指定された全MOSトランジスタを選択した(Yes)と判断された場合には、違反の虞れのある全MOSトランジスタを選択したか否かの判別が行われ、この判別において、違反の虞れのある全MOSトランジスタを選択した(Yes)と判断されるまで、上記の処理が繰返される。違反の虞れのある全MOSトランジスタを選択した(Yes)と判断された場合には、トポロジーマッチング処理と該当MOSトランジスタの違反除外処理が終了される。

【0055】

図10には、図8における「貫通電流パス有無判定処理と該当MOSトランジスタの違反除外処理(S602)」の詳細が示される。

【0056】

貫通電流パス有無判定処理と該当MOSトランジスタの違反除外処理では、先ず、違反の虞れのあるMOSトランジスタが一つ選択され(S801)、違反の虞れのあるMOSトランジスタのゲート接続ノードに対して、ゲート接続ノードを同一とするMOSトランジスタが全てオンする電圧値を持つ電圧源が探索される(S802)。そして、上記ステップS802の電圧源が在るか否かの判別が行われる。この判別において、上記ステップS802の電圧源が在る(Yes)と判断された場合には、違反の虞れがあるMOSトランジスタのゲート接続ノードに対して、ゲート接続ノードを同一とする全MOSトランジスタがオンする電圧が一つ仮定される(S803)。そして、上記ステップS803の電圧をドライブするMOSトランジスタのオン状態を仮定する(S804)。このステップS804の処理は、上記手順(2−1)に相当する。上記ステップS804のMOSトランジスタがオンするために必要なMOSトランジスタのオン状態を探索(前方探索)する(S805)。このステップSS805の処理は、上記手順(2−2)に相当する。さらに、上記ステップS804とS805のMOSトランジスタのオン状態に基づいて、オン状態又はオフ状態が決定されるMOSトランジスタを探索(後方探索)する(S806)。このステップS806の処理は、上記手順(2−3)に相当する。そして、違反の虞れのあるMOSトランジスタにシリアルに接続されるMOSトランジスタを挟んだ異電源間の全パスが探索される(S807)。このステップS807の処理は、上記手順(2−4)に相当する。さらに、上記ステップS807のパス毎に、オフ状態となるMOSトランジスタを含むパスが除外され、全パスが除外されるならば上記ステップS801のMOSトランジスタが違反対象から除外される(S808)。このステップS808の処理は、上記手順(2−5)に相当する。そして、上記ステップS802の電圧源を全て選択したか否かの判別が行われ、全て選択した(Yes)と判断されるまで、上記ステップS803〜S808までの処理が繰返される。そして、上記ステップS802の電圧源を全て選択した(Yes)と判断された場合には、違反の虞れのある全MOSトランジスタを選択したか否かの判別が行われ、この判別において、違反の虞れのある全MOSトランジスタを選択した(Yes)と判断されるまで、上記の処理が繰返される。

【0057】

図11には、図10における「電圧源探索処理(S802)」の詳細が示される。

【0058】

上記ステップS802の電圧源探索処理では、先ず、ステップS801における違反の虞れのあるMOSトランジスタのソース又はドレイン方向の接続がトレースされ、違反の虞れがあるMOSトランジスタがpチャンネル型MOSトランジスタであるならば、給電される正の電圧源がリストアップされ、違反の虞れのあるMOSトランジスタがnチャンネル型MOSトランジスタであるならば、給電される0V以下の電圧源がリストアップされる(S901)。例えば図12に示されるように、pチャネル型MOSトランジスタ1201,1202,1203,1205、nチャネル型MOSトランジスタ1204,1206、インバータ1207,1208,1209を含んで、レベルシフタが形成される場合において、今、違反の虞れのあるMOSトランジスタがpチャンネル型MOSトランジスタ1203の場合、給電される正の電圧源、すなわちVCC(3.3V)がリストアップされる。

【0059】

次に、上記ステップS801における違反の虞れのあるMOSトランジスタのゲート接続ノードをドライブするMOSトランジスタのソース又はドレイン方向の接続がトレースされ、違反の虞れのあるMOSトランジスタがpチャネル型MOSトランジスタであるならば、給電される正の電圧源がリストアップされ、違反の虞れのあるMOSトランジスタがnチャンネル型MOSトランジスタならば、給電される0V以下の電圧源がリストアップされる(S902)。例えば図12に示される回路の場合、違反の虞れのあるpチャネル型MOSトランジスタ1203のゲート接続ノードをドライブするMOSトランジスタのソース又はドレイン方向の接続がトレースされ、給電される正の電圧源として、VDD(1.5V)がリストアップされる。

【0060】

次に、上記ステップS901の電圧源と、上記ステップS902の電圧源との組み合わせのうち、各電圧源にドライブされる、その電圧値が異なる電圧源の組み合わせがリストアップされる(S903)。例えば図12に示される回路において、異なる電圧値をドライブする電圧源の組み合わせは、pチャネル型MOSトランジスタ1203のゲートに印加されるVDD(1.5V)、pチャネル型MOSトランジスタ1203のソースに印加されるVCC(3.3V)となる。尚、上記ステップS903において、各電源電圧レベルが印加される場合のその電圧値には、伝搬電位補正等により正規の電源電圧レベルとは若干異なる場合も含まれるものとする。

【0061】

次に、上記ステップS903の電圧源の組み合わせのうち、ステップS801における違反の虞れのあるMOSトランジスタとゲート接続ノードを同一とする、全MOSトランジスタがオンする組み合わせのみがリストアップされる(S904)。例えば図12に示される回路において、ステップS801における違反の虞れのあるpチャネル型MOSトランジスタ1203とゲート接続ノードを同一とする、全MOSトランジスタがオンする組み合わせは、pチャネル型MOSトランジスタ1203のゲートに印加されるVDD(1.5V)と、pチャネル型MOSトランジスタ1203のソースに印加されるVCC(3.3V)とされる。これにより、上記S802の電圧源探索処理が終了される。

【0062】

図13には、図10における電圧仮定処理(S803)の詳細が示される。

【0063】

上記ステップS803の電圧仮定処理では、先ず、上記ステップS904の電圧源の組み合わせが一つ選択される(S1001)。例えば図14に示される構成において、違反の虞れのあるpチャネル型MOSトランジスタ1203とゲート接続ノードを同一とする、全MOSトランジスタがオンする組み合わせとして、pチャネル型MOSトランジスタ1203のゲートに印加されるVDD(1.5V)と、pチャネル型MOSトランジスタ1203のソースに印加されるVCC(3.3V)とされる。

【0064】

次に、上記ステップS1001で選択された電源の組み合わせに従い、違反の虞れのあるMOSトランジスタのゲート端子に対して、その電圧源の伝搬を仮定する(S1002)。例えば図14に示される構成においては、違反の虞れのあるpチャネル型MOSトランジスタ1203のゲート端子にVDD(1.5V)の伝搬が仮定される。これにより、上記電圧仮定処理(S803)が終了される。

【0065】

図15には、図10におけるMOSトランジスタのオン仮定処理(S804)の詳細が示される。

【0066】

上記ステップS804のMOSトランジスタのオン仮定処理では、先ず、上記ステップS1002の電圧源を伝搬するMOSトランジスタのオン状態を仮定する(S1101)。例えば図16に示される回路において、161で示されるように、インバータ1209においてVDD(1.5V)をドライブするpチャンネル型MOSトランジスタのオン状態が仮定される。

【0067】

次に、上記ステップS1002のMOSトランジスタがオンするための上記ステップS1002のMOSトランジスタのゲート端子の電圧値が認識される(S1102)。例えば図16において、162で示されるように、上記インバータ1209においてVDD(1.5V)をドライブするpチャンネル型MOSトランジスタがオンするためのゲート電圧値は「0V」と認識される。これにより、上記ステップS804のMOSトランジスタのオン仮定処理が終了される。

【0068】

図17には、図10における前方探索処理(S805)の詳細が示される。

【0069】

前方探索処理(S805)では、先ず、ステップS1102又はS1204のMOSトランジスタのゲート端子への接続ノードをドライブするMOSトランジスタとそのMOSトランジスタに給電される電圧源の探索が行われる(S1201)。例えば図18に示されるインバータ1209におけるpチャンネル型MOSトランジスタのゲート端子への接続ノードをドライブするMOSトランジスタは、インバータ1208におけるpチャネル型MOSトランジスタ1801とそれに直列接続されたnチャネル型MOSトランジスタ1802である。そしてこのインバータ1208におけるMOSトランジスタに給電される電圧源は、VDD(1.5V)と、0Vとされる。

【0070】

そして、上記ステップS1201で探索されたMOSトランジスタのうち、上記ステップS1102で認識されたゲート端子に必要な電圧値を供給可能なMOSトランジスタを全て選択する(S1202)。例えば図18において、インバータ1208を形成するMOSトランジスタ1801,1802のうち、インバータ1209内のpチャンネル型MOSトランジスタのゲートに0Vを供給可能なMOSトランジスタとして、nチャンネル型MOSトランジスタ1802が選択される。

【0071】

次に、上記ステップS1202で選択された全MOSトランジスタのオン状態をMOSトランジスタの探索(前方探索)により仮定する(S1203)。例えば図18においては、nチャンネル型MOSトランジスタ1802のオン状態が仮定される。

【0072】

そして、上記ステップS1202の各MOSトランジスタがオンするための上記ステップS1202の各MOSトランジスタのゲート端子の電圧値を認識する(S1204)。例えば図18においては、MOSトランジスタ1801,1802のゲート端子に供給される正の電圧が、必要な電圧値として認識される。

【0073】

次に、探索(前方探索)が終了していないMOSトランジスタが存在するか否かの判別が行われ、この判別において、探索(前方探索)が終了していないMOSトランジスタは存在しない(Yes)と判断されるまで、上記ステップS1201〜S1204までの処理が繰返される。

【0074】

図19には、上記後方探索処理(S806)の詳細が示される。

【0075】

後方探索処理(S806)では、先ず、ステップS1101とS1203、又はS1302でオン状態と仮定されたMOSトランジスタ1802でドライブされる電圧源(0V)と、その電圧値が後方のMOSトランジスタへ伝搬される(S1301)。例えば図20において、0Vがインバータ1209のpチャンネル型MOSトランジスタに伝達され、このpチャンネル型MOSトランジスタがオンされることにより、VDD(1.5V)がpチャンネル型MOSトランジスタ1203に伝達される。また、0Vがpチャンネル型MOSトランジスタ1205及びnチャンネル型MOSトランジスタ1206に伝達される。

【0076】

次に、上記ステップS1201で伝搬された電圧値がゲート端子へ到達するMOSトランジスタについて、オン又はオフが決定されるMOSトランジスタが探索(後方探索)される(S1302)。例えば図20において、pチャンネル型MOSトランジスタ1202,1203,1205及びnチャンネル型MOSトランジスタ1204がオン状態と判定され、pチャンネル型MOSトランジスタ1201及びnチャンネル型MOSトランジスタ1206がオフ状態と判定される。

【0077】

そして、探索(後方探索)が終了していないMOSトランジスタが存在するか否かの判別が行われ、この判別で探索(後方探索)が終了していないMOSトランジスタが存在しない(No)と判断されまで、上記ステップS1301,S1302の処理が繰返される。

【0078】

図21には、上記異電圧間の全パス探索処理(S807)の詳細が示される。

【0079】

異電圧間の全パス探索処理(S807)では、先ず、上記ステップS801で選択された違反の虞れのあるMOSトランジスタのソース又はドレイン方向の接続がトレースされ、ソース端子又はドレイン端子それぞれに給電される電圧源がリストアップされる(S1401)。例えば図22において、違反の虞れのあるMOSトランジスタ1203のソース方向の接続がトレースされることにより、VCC(3.3V)がリストアップされ、違反の虞れのあるMOSトランジスタ1203のドレイン方向の接続がトレースされることにより、0Vがリストアップされる。

【0080】

次に、上記ステップS1401でのソース端子とドレイン端子に供給される電圧源の組み合わせのうち、異なる電圧源が供給されるような異電圧源のパスがリストアップされる(S1402)。例えば図22において、VCC(3.3V)と0Vとは、互いに異なる電圧源であり、違反の虞れのあるMOSトランジスタ1203を介してVCC(3.3V)から0Vに至るパス221がリストアップされる。

【0081】

図23には、上記違反対象からの除外処理(S808)の詳細が示される。

【0082】

違反対象からの除外処理(S808)では、先ず、上記ステップS1402のパス、すなわち、上記ステップS1401でのソース端子とドレイン端子に供給される電圧源の組み合わせのうち、異なる電圧源が供給されるような異電圧源パスの一つを選択する。例えば図24において、nチャネル型MOSトランジスタ1204がオン状態とされることでpチャネル型MOSトランジスタ1203のドレイン端子は0Vが供給され、さらにこのpチャネル型MOSトランジスタ1203のソース端子にはVCC(3.3V)が供給されることから、VCC(3.3V)から上記pチャネル型MOSトランジスタ1203及びnチャネル型MOSトランジスタ1204を介してグランドに至るパスが選択される(S1501)。そして、上記ステップS1501で選択されたパスを構成するMOSトランジスタのうち、オフ判定となっているMOSトランジスタが在るか否かの判別が行われる。この判別において、オフ判定となっているMOSトランジスタが在る(Yes)と判定された場合には、上記ステップS1402のパスを全て選択済みか否かの判別が行われ、上記ステップS1402のパスを全て選択済みと判断された場合に、上記ステップS801で選択した違反の虞れのあるMOSトランジスタが違反対象から除外される(S1502)。例えば図24において、MOSトランジスタ1201がオフ判定とされるMOSトランジスタであり、オフ判定とされるMOSトランジスタが存在するから、このMOSトランジスタ1201が存在するパス224は、貫通電流が流れるパスとはなり得ない。また、図24では、他に上記ステップS1402のパスが存在しないため、現在、選択されている違反の虞れがあるMOSトランジスタのみが、上記ステップS1502の処理で違反対象から除外される。このようにして違反対象からの除外処理(S808)が行われる。

【0083】

上記の例によれば、以下の作用効果を得ることができる。

【0084】

(1)トポロジーマッチング処理と該当MOSトランジスタの違反除外処理では、指定のトポロジー中に含まれるマスク指定されたMOSトランジスタの一つとの対応付けが行われ(S702)、検証対象回路の回路トポロジーが認識される(S703)。そして、指定トポロジーと一致するか否かの判別が行われ、指定トポロジーと一致する(Yes)と判断された場合には、上記ステップS701のMOSトランジスタが違反対象から除外される(S704)。このようにトポロジーと一致する場合には違反対象から除外され、トポロジーと一致しない場合には違反対象から除外されない。その結果、真の違反を指摘することができる。

【0085】

(2)ポンプ回路やレギュレータに適用される昇圧回路のトポロジー情報(MOSトランジスタのゲートサイズ等のパラメータ情報を含む)が事前情報として付与されている場合には、回路認識の都度、ΔV(指定値)分の電位を加算して伝搬することで、内部電源を考慮した検証が可能とされる。従って、出力電圧レベルが変動する場合にも、擬似違反を排除することができる。

【0086】

(3)貫通電流パスの有無を判定し、貫通電流パスが無い場合には、違反の虞れのあるMOSトランジスタが違反対象から除外されることから、貫通電流パスの検出によって擬似違反を排除することができる。

【0087】

以上本発明者によってなされた発明を具体的に説明したが、本発明はそれに限定されるものではなく、その要旨を逸脱しない範囲で種々変更可能であることはいうまでもない。

【図面の簡単な説明】

【0088】

【図1】コンピュータによって行われる異電源接続検証処理の全体的な流れを示すフローチャートである。

【図2】図1における主要処理の詳細なフローチャートである。

【図3】図2における主要処理の詳細なフローチャートである。

【図4】サブ回路を使用した回路接続例の説明図である。

【図5】上記サブ回路のネットリストを示す説明図である。

【図6】図2における主要処理の詳細なフローチャートである。

【図7】図1における主要処理の詳細なフローチャートである。

【図8】図1における主要処理の詳細なフローチャートである。

【図9】図8における主要処理の詳細なフローチャートである。

【図10】図8における主要処理の詳細なフローチャートである。

【図11】図10における主要処理の詳細なフローチャートである。

【図12】図10における主要処理を説明するための回路図である。

【図13】図10における主要処理の詳細なフローチャートである。

【図14】図13における主要処理を説明するための回路図である。

【図15】図10における主要処理の詳細なフローチャートである。

【図16】図15における主要処理を説明するための回路図である。

【図17】図10における主要処理の詳細なフローチャートである。

【図18】図17における主要処理を説明するための回路図である。

【図19】図10における主要処理の詳細なフローチャートである。

【図20】図19における主要処理を説明するための回路図である。

【図21】図10における主要処理の詳細なフローチャートである。

【図22】図21における主要処理を説明するための回路図である。

【図23】図10における主要処理の詳細なフローチャートである。

【図24】図21における主要処理を説明するための回路図である。

【図25】本発明の比較対象とされる検証方法を説明するための回路図である。

【図26】本発明の比較対象とされる検証方法を説明するための回路図である。

【図27】本発明の比較対象とされる検証方法を説明するための回路図である。

【図28】本発明の比較対象とされる検証方法を説明するための回路図である。

【図29】本発明の比較対象とされる検証方法を説明するための回路図である。

【図30】本発明にかかる異電源接続検証方法における主要処理を説明するための回路図である。

【図31】本発明にかかる異電源接続検証方法における主要処理を説明するための回路図である。

【図32】本発明にかかる異電源接続検証方法における主要処理を説明するための回路図である。

【図33】本発明にかかる異電源接続検証方法における主要処理を説明するための回路図である。

【図34】本発明にかかる異電源接続検証方法における主要処理を説明するための回路図である。

【図35】本発明にかかる異電源接続検証用方法が実施されるコンピュータの全体的な構成例ブロック図である。

【符号の説明】

【0089】

31 CPU

32 記憶装置

33 入力装置

34 表示装置

35 メモリ

36 バス

【特許請求の範囲】

【請求項1】

予め設定されたプログラムを実行する中央処理装置を備えたコンピュータを用いて検証対象回路の異電源接続検証を行う異電源接続検証方法であって、

上記中央処理装置は、電位伝搬と違反の虞れのあるトランジスタを検索する第1処理と、

上記第1処理の結果に基づいて、擬似違反を抑制する第2処理と、を含み、

上記第2処理は、上記検証対象回路の貫通電流パスの有無を判定してトランジスタの違反を除外する第3処理を含み、

上記第3処理は、違反の虞れがあるトランジスタとゲート接続ノードを同一とするトランジスタを全てオン状態と仮定する第1ステップと、

上記第1ステップで仮定されたトランジスタがオンするために必要なトランジスタのオン状態を探索する第2ステップと、

上記第1ステップと上記第2ステップでのトランジスタの伝搬電位に基づき、オン状態又はオフ状態が決定される周辺トランジスタを探索する第3ステップと、を含むことを特徴とする異電源接続検証方法。

【請求項2】

予め設定されたプログラムを実行する中央処理装置を備えたコンピュータを用いて検証対象回路の異電源接続検証を行う異電源接続検証方法であって、

上記中央処理装置は、電位伝搬と違反の虞れのあるトランジスタを検索する第1処理と、

上記第1処理の結果に基づいて、擬似違反を抑制する第2処理と、を含み、

上記第2処理は、上記検証対象回路の貫通電流パスの有無を判定してトランジスタの違反を除外する第3処理を含み、

上記第3処理は、違反の虞れがあるトランジスタとゲート接続ノードを同一とするトランジスタを全てオン状態と仮定する第1ステップと、

上記第1ステップで仮定されたトランジスタがオンするために必要なトランジスタのオン状態を後方探索する第2ステップと、

上記第1ステップと上記第2ステップでのトランジスタの伝搬電位に基づき、オン状態又はオフ状態が決定される周辺トランジスタを探索する第3ステップと、

違反の虞れのあるMOSトランジスタにシリアルに接続されるトランジスタを挟んだ異電源間の全てのパスを探索する第4ステップと、

上記第4ステップで探索されたパス毎に、オフ状態となるトランジスタを含むパスを除外し、全てのパスが除外された場合に、違反の虞れのあるトランジスタを違反対象から除外する第5ステップと、を含むことを特徴とする異電源接続検証方法。

【請求項3】

上記第3処理は、トポロジーマッチングによりトランジスタの違反を除外する第4処理を含み、

上記第4処理は、事前情報として付与されたトポロジーと上記異電源接続検証を可能とする異電源接続検証用プログラムとが一致するか否かを判別し、その判別結果に基づいて該当トランジスタを違反対象から除外する第6ステップを含む請求項1又は2記載の異電源接続検証方法。

【請求項4】

上記第1処理は、オン状態のトランジスタでの固定電位伝搬により、オン状態又はオフ状態が決定されるトランジスタを探索する第6ステップと、

上記第6ステップでオフ状態となるトランジスタを探索する第7ステップと、

上記第7ステップで探索されたトランジスタを、ソース又はドレイン方向により電源電圧レベルを伝搬させる対象トランジスタから除外する第8ステップと、

トランジスタのソース・ドレイン間で伝搬する可能性のある電位を伝搬させる第9ステップと、

ゲート端子とソース端子又はドレイン端子とに正の電源電圧レベルが伝搬されるpチャネル型MOSトランジスタと、ゲート端子とソース端子又はドレイン端子に0V以下の電源電圧レベルが伝搬されるnチャネル型MOSトランジスタとを探索する第10ステップと、

上記第10ステップで、各電源電圧レベルが印加される場合のその電圧値について、ゲート端子の最小電圧値が、ソース又はドレイン端子の最大電圧値よりも小さくなるトランジスタと、ゲート端子の最大電圧値がソース又はドレイン端子の最小電圧値よりも大きくなるトランジスタとを探索し、それを、違反の虞れのあるトランジスタとしてリストアップする第11ステップと、を含む請求項1又は2記載の異電源接続検証方法。

【請求項5】

電位伝搬と違反の虞れのあるトランジスタを検索する第1処理と、上記第1処理の結果に基づいて、擬似違反を抑制する第2処理と、をコンピュータに実行させることで、検証対象回路の異電源接続検証を可能とする異電源接続検証用プログラムであって、

上記第2処理は、上記検証対象回路の貫通電流パスの有無を判定してトランジスタの違反を除外する第3処理を含み、

上記第3処理は、違反の虞れがあるトランジスタとゲート接続ノードを同一とするトランジスタを全てオン状態と仮定する第1ステップと、

上記第1ステップで仮定されたトランジスタがオンするために必要なトランジスタのオン状態を後方探索する第2ステップと、

上記第1ステップと上記第2ステップでのトランジスタの伝搬電位に基づき、オン状態又はオフ状態が決定される周辺トランジスタを探索する第3ステップと、を含むことを特徴とする異電源接続検証用プログラム。

【請求項6】

電位伝搬と違反の虞れのあるトランジスタを検索する第1処理と、上記第1処理の結果に基づいて、擬似違反を抑制する第2処理と、をコンピュータに実行させることで、検証対象回路の異電源接続検証を可能とする異電源接続検証用プログラムであって、

上記第2処理は、上記検証対象回路の貫通電流パスの有無を判定してトランジスタの違反を除外する第3処理を含み、

上記第3処理は、違反の虞れがあるトランジスタとゲート接続ノードを同一とするトランジスタを全てオン状態と仮定する第1ステップと、

上記第1ステップで仮定されたトランジスタがオンするために必要なトランジスタのオン状態を後方探索する第2ステップと、

上記第1ステップと上記第2ステップでのトランジスタの伝搬電位に基づき、オン状態又はオフ状態が決定される周辺トランジスタを探索する第3ステップと、

違反の虞れのあるMOSトランジスタにシリアルに接続されるトランジスタを挟んだ異電源間の全てのパスを探索する第4ステップと、

上記第4ステップで探索されたパス毎に、オフ状態となるトランジスタを含むパスを除外し、全てのパスが除外された場合に、違反の虞れのあるトランジスタを違反対象から除外する第5ステップと、を含むことを特徴とする異電源接続検証用プログラム。

【請求項7】

上記第3処理は、トポロジーマッチングによりトランジスタの違反を除外する第4処理を含み、

上記第4処理は、事前情報として付与さえたトポロジーと上記異電源接続検証を可能とする異電源接続検証用プログラムとが一致するか否かを判別し、その判別結果に基づいて該当トランジスタを違反対象から除外する第6ステップを含む請求項5又は6記載の異電源接続検証用プログラム。

【請求項8】

上記第1処理は、オン状態のトランジスタでの固定電位伝搬により、オン状態又はオフ状態が決定されるトランジスタを後方探索する第6ステップと、

上記第6ステップでオフ状態となるトランジスタを探索する第7ステップと、

上記第7ステップで探索されたトランジスタを、ソース又はドレイン方向により電源電圧レベルを伝搬させる対象トランジスタから除外する第8ステップと、

トランジスタのソース・ドレイン間で伝搬する可能性のある電位を伝搬させる第9ステップと、

ゲート端子とソース端子又はドレイン端子とに正の電源電圧レベルが伝搬されるトランジスタと、ゲート端子とソース端子又はドレイン端子に0V以下の電源電圧レベルが伝搬されるトランジスタとを探索する第10ステップと、

上記第10ステップで、各電源電圧レベルが印加される場合のその電圧値について、ゲート端子の最小電圧値が、ソース又はドレイン端子の最大電圧値よりも小さくなるトランジスタと、ゲート端子の最大電圧値がソース又はドレイン端子の最小電圧値よりも大きくなるトランジスタとを探索し、それを、違反の虞れのあるトランジスタとしてリストアップする第11ステップと、を含む請求項5又は6記載の異電源接続検証用プログラム。

【請求項9】

請求項5乃至8の何れか1項記載の異電源接続検証用プログラムを記録したコンピュータ読み取り可能な記録媒体。

【請求項1】

予め設定されたプログラムを実行する中央処理装置を備えたコンピュータを用いて検証対象回路の異電源接続検証を行う異電源接続検証方法であって、

上記中央処理装置は、電位伝搬と違反の虞れのあるトランジスタを検索する第1処理と、

上記第1処理の結果に基づいて、擬似違反を抑制する第2処理と、を含み、

上記第2処理は、上記検証対象回路の貫通電流パスの有無を判定してトランジスタの違反を除外する第3処理を含み、

上記第3処理は、違反の虞れがあるトランジスタとゲート接続ノードを同一とするトランジスタを全てオン状態と仮定する第1ステップと、

上記第1ステップで仮定されたトランジスタがオンするために必要なトランジスタのオン状態を探索する第2ステップと、

上記第1ステップと上記第2ステップでのトランジスタの伝搬電位に基づき、オン状態又はオフ状態が決定される周辺トランジスタを探索する第3ステップと、を含むことを特徴とする異電源接続検証方法。

【請求項2】

予め設定されたプログラムを実行する中央処理装置を備えたコンピュータを用いて検証対象回路の異電源接続検証を行う異電源接続検証方法であって、

上記中央処理装置は、電位伝搬と違反の虞れのあるトランジスタを検索する第1処理と、

上記第1処理の結果に基づいて、擬似違反を抑制する第2処理と、を含み、

上記第2処理は、上記検証対象回路の貫通電流パスの有無を判定してトランジスタの違反を除外する第3処理を含み、

上記第3処理は、違反の虞れがあるトランジスタとゲート接続ノードを同一とするトランジスタを全てオン状態と仮定する第1ステップと、

上記第1ステップで仮定されたトランジスタがオンするために必要なトランジスタのオン状態を後方探索する第2ステップと、

上記第1ステップと上記第2ステップでのトランジスタの伝搬電位に基づき、オン状態又はオフ状態が決定される周辺トランジスタを探索する第3ステップと、

違反の虞れのあるMOSトランジスタにシリアルに接続されるトランジスタを挟んだ異電源間の全てのパスを探索する第4ステップと、

上記第4ステップで探索されたパス毎に、オフ状態となるトランジスタを含むパスを除外し、全てのパスが除外された場合に、違反の虞れのあるトランジスタを違反対象から除外する第5ステップと、を含むことを特徴とする異電源接続検証方法。

【請求項3】

上記第3処理は、トポロジーマッチングによりトランジスタの違反を除外する第4処理を含み、

上記第4処理は、事前情報として付与されたトポロジーと上記異電源接続検証を可能とする異電源接続検証用プログラムとが一致するか否かを判別し、その判別結果に基づいて該当トランジスタを違反対象から除外する第6ステップを含む請求項1又は2記載の異電源接続検証方法。

【請求項4】

上記第1処理は、オン状態のトランジスタでの固定電位伝搬により、オン状態又はオフ状態が決定されるトランジスタを探索する第6ステップと、

上記第6ステップでオフ状態となるトランジスタを探索する第7ステップと、

上記第7ステップで探索されたトランジスタを、ソース又はドレイン方向により電源電圧レベルを伝搬させる対象トランジスタから除外する第8ステップと、

トランジスタのソース・ドレイン間で伝搬する可能性のある電位を伝搬させる第9ステップと、

ゲート端子とソース端子又はドレイン端子とに正の電源電圧レベルが伝搬されるpチャネル型MOSトランジスタと、ゲート端子とソース端子又はドレイン端子に0V以下の電源電圧レベルが伝搬されるnチャネル型MOSトランジスタとを探索する第10ステップと、

上記第10ステップで、各電源電圧レベルが印加される場合のその電圧値について、ゲート端子の最小電圧値が、ソース又はドレイン端子の最大電圧値よりも小さくなるトランジスタと、ゲート端子の最大電圧値がソース又はドレイン端子の最小電圧値よりも大きくなるトランジスタとを探索し、それを、違反の虞れのあるトランジスタとしてリストアップする第11ステップと、を含む請求項1又は2記載の異電源接続検証方法。

【請求項5】

電位伝搬と違反の虞れのあるトランジスタを検索する第1処理と、上記第1処理の結果に基づいて、擬似違反を抑制する第2処理と、をコンピュータに実行させることで、検証対象回路の異電源接続検証を可能とする異電源接続検証用プログラムであって、

上記第2処理は、上記検証対象回路の貫通電流パスの有無を判定してトランジスタの違反を除外する第3処理を含み、

上記第3処理は、違反の虞れがあるトランジスタとゲート接続ノードを同一とするトランジスタを全てオン状態と仮定する第1ステップと、

上記第1ステップで仮定されたトランジスタがオンするために必要なトランジスタのオン状態を後方探索する第2ステップと、

上記第1ステップと上記第2ステップでのトランジスタの伝搬電位に基づき、オン状態又はオフ状態が決定される周辺トランジスタを探索する第3ステップと、を含むことを特徴とする異電源接続検証用プログラム。

【請求項6】

電位伝搬と違反の虞れのあるトランジスタを検索する第1処理と、上記第1処理の結果に基づいて、擬似違反を抑制する第2処理と、をコンピュータに実行させることで、検証対象回路の異電源接続検証を可能とする異電源接続検証用プログラムであって、

上記第2処理は、上記検証対象回路の貫通電流パスの有無を判定してトランジスタの違反を除外する第3処理を含み、

上記第3処理は、違反の虞れがあるトランジスタとゲート接続ノードを同一とするトランジスタを全てオン状態と仮定する第1ステップと、

上記第1ステップで仮定されたトランジスタがオンするために必要なトランジスタのオン状態を後方探索する第2ステップと、

上記第1ステップと上記第2ステップでのトランジスタの伝搬電位に基づき、オン状態又はオフ状態が決定される周辺トランジスタを探索する第3ステップと、

違反の虞れのあるMOSトランジスタにシリアルに接続されるトランジスタを挟んだ異電源間の全てのパスを探索する第4ステップと、

上記第4ステップで探索されたパス毎に、オフ状態となるトランジスタを含むパスを除外し、全てのパスが除外された場合に、違反の虞れのあるトランジスタを違反対象から除外する第5ステップと、を含むことを特徴とする異電源接続検証用プログラム。

【請求項7】

上記第3処理は、トポロジーマッチングによりトランジスタの違反を除外する第4処理を含み、

上記第4処理は、事前情報として付与さえたトポロジーと上記異電源接続検証を可能とする異電源接続検証用プログラムとが一致するか否かを判別し、その判別結果に基づいて該当トランジスタを違反対象から除外する第6ステップを含む請求項5又は6記載の異電源接続検証用プログラム。

【請求項8】

上記第1処理は、オン状態のトランジスタでの固定電位伝搬により、オン状態又はオフ状態が決定されるトランジスタを後方探索する第6ステップと、

上記第6ステップでオフ状態となるトランジスタを探索する第7ステップと、

上記第7ステップで探索されたトランジスタを、ソース又はドレイン方向により電源電圧レベルを伝搬させる対象トランジスタから除外する第8ステップと、

トランジスタのソース・ドレイン間で伝搬する可能性のある電位を伝搬させる第9ステップと、

ゲート端子とソース端子又はドレイン端子とに正の電源電圧レベルが伝搬されるトランジスタと、ゲート端子とソース端子又はドレイン端子に0V以下の電源電圧レベルが伝搬されるトランジスタとを探索する第10ステップと、

上記第10ステップで、各電源電圧レベルが印加される場合のその電圧値について、ゲート端子の最小電圧値が、ソース又はドレイン端子の最大電圧値よりも小さくなるトランジスタと、ゲート端子の最大電圧値がソース又はドレイン端子の最小電圧値よりも大きくなるトランジスタとを探索し、それを、違反の虞れのあるトランジスタとしてリストアップする第11ステップと、を含む請求項5又は6記載の異電源接続検証用プログラム。

【請求項9】

請求項5乃至8の何れか1項記載の異電源接続検証用プログラムを記録したコンピュータ読み取り可能な記録媒体。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図26】

【図27】

【図28】

【図29】

【図30】

【図31】

【図32】

【図33】

【図34】

【図35】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図26】

【図27】

【図28】

【図29】

【図30】

【図31】

【図32】

【図33】

【図34】

【図35】

【公開番号】特開2010−146423(P2010−146423A)

【公開日】平成22年7月1日(2010.7.1)

【国際特許分類】

【出願番号】特願2008−324931(P2008−324931)

【出願日】平成20年12月22日(2008.12.22)

【出願人】(503121103)株式会社ルネサステクノロジ (4,790)

【Fターム(参考)】

【公開日】平成22年7月1日(2010.7.1)

【国際特許分類】

【出願日】平成20年12月22日(2008.12.22)

【出願人】(503121103)株式会社ルネサステクノロジ (4,790)

【Fターム(参考)】

[ Back to top ]