発光素子の製造方法

【課題】低光吸収率の透明導電膜を安定的に成膜できることで、高い品質が確保できる発光素子の製造方法を提供する。

【解決手段】発光素子は、透光性基板11に、n型半導体層121、発光層122およびp型半導体層123が積層された半導体層12と、半導体層12に積層され、金属酸化物からなる成膜材料により成膜された透明導電膜13と、透明導電膜13に積層された反射部14とを備えている。この透明導電膜を成膜する際には、半導体層に透明導電膜の原膜をスパッタにより成膜するスパッタ工程と、原膜を酸素含有雰囲気ガスによりアニールする第1アニール工程と、酸素非含有雰囲気ガスによりアニールする第2アニール工程との2段階アニールを行う。第1アニール工程または第2アニール工程では、雰囲気温度が600℃より高く、680℃より低くなるような範囲で行う。

【解決手段】発光素子は、透光性基板11に、n型半導体層121、発光層122およびp型半導体層123が積層された半導体層12と、半導体層12に積層され、金属酸化物からなる成膜材料により成膜された透明導電膜13と、透明導電膜13に積層された反射部14とを備えている。この透明導電膜を成膜する際には、半導体層に透明導電膜の原膜をスパッタにより成膜するスパッタ工程と、原膜を酸素含有雰囲気ガスによりアニールする第1アニール工程と、酸素非含有雰囲気ガスによりアニールする第2アニール工程との2段階アニールを行う。第1アニール工程または第2アニール工程では、雰囲気温度が600℃より高く、680℃より低くなるような範囲で行う。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、基板に発光層を含む半導体層が積層され、発光層からの光を基板方向へ反射する反射部を備えた発光素子の製造方法に関するものである。

【背景技術】

【0002】

実装基板にフリップチップ実装される従来の発光素子として、例えば、特許文献1に記載のものが知られている。

【0003】

この特許文献1に記載の発光素子を図6に基づいて説明する。発光素子100は、ベース基板101にn型半導体層102と発光層103とp型半導体層104とが積層され、更に、アノード電極110が形成されている。

【0004】

このアノード電極110は、p型半導体層104上に、Ni,Pd,Pt,Cr,Mn,Ta,Cu,Feなどの材料により形成された第1の透明導電膜111と、第1の透明導電膜111上に、ITO,IZO,ZnO,In2O3,SnO2,MgxZn1-xO(x≦0.5),アモルファスAlGaN,GaN,SiONの群から選択される1つの材料により形成された第2の透明導電膜112と、第2の透明導電膜112上に形成され発光層103から放射された光を反射する屈折率が異なる2種類の誘電体膜が交互に積層された複数の多層反射膜層113と、発光層103からの光に対して高い反射率を有するAgの金属材料からなる金属反射膜114と、金属反射膜114上に形成されたバリアメタル膜115と、バリアメタル膜115上に形成された金属材料からなる外部接続用金属膜116とにより構成されている。

【0005】

発光素子100では、透明導電膜を、金属酸化物からなる透明金属材料を用いることにより、発光層103からの光を効率よく多層反射膜層113や金属反射膜114の方向へ、また多層反射膜層113や金属反射膜114にて反射した光を効率よくベース基板101の方向へ透過させることができる。

【0006】

透明導電膜については、フリップチップタイプではないが、特許文献2に記載された技術が知られている。

【0007】

特許文献2には、透明導電膜(透光性の正極)がITO(In2O3−SnO2),AZnO(ZnO−Al2O3),IZnO(In2O3−ZnO),GZO(ZnO−GeO2)からなる少なくとも一種類を含んだ材料により成膜されている。この透明導電膜をp型半導体層上に成膜するときには、透光性酸化物導電材料の透光性正極を化学量論組成よりも酸素不足にした状態でスパッタまたは蒸着により形成した後、0.1%〜50%の酸素含有雰囲気中において20℃/分〜500℃/分の範囲の昇温速度で加熱し、250℃〜600℃の範囲の温度で30秒〜10分程度保持するアニール処理し、その後、99.9%以上で露点−30℃以下のN2ガスによる無酸素雰囲気において200℃〜500℃の範囲で1分から20分の範囲の温度で再アニール処理することが記載されている。この製造方法により透明導電膜を成膜することで、標準順電圧(Vf)が低く、透光性正極の高い透光性と低いシート抵抗、低い標準順電圧(Vf)、並びにp型半導体層に対する高い接合強度を得ることができる。

【先行技術文献】

【特許文献】

【0008】

【特許文献1】特開2007−258276号公報

【特許文献2】特開2007−287786号公報

【発明の概要】

【発明が解決しようとする課題】

【0009】

従来の発光素子100では、p型半導体層104上に第1,2の透明導電膜111,112が設けられ、第2の透明導電膜112上に誘電体膜からなる多層反射膜層113を設けているため、多層反射膜層113で多くの光を反射させ、光取り出し効率を向上させるためには、第2の透明導電膜112で発光層103からの光を遮ることなく多くの光を透過させることが重要である。

【0010】

しかし、特許文献2に記載の半導体発光素子の製造方法によれば、透明導電膜を酸素含有雰囲気中でアニール処理し、無酸素雰囲気中で再アニール処理することで抵抗値を下げることができるものの、透明導電膜の光吸収率がばらつくという問題があることがわかった。つまり、光吸収率が高い透明導電膜が成膜されてしまうことがある。そうなると、輝度が低い発光素子となってしまう。

【0011】

従って、特許文献2に記載の半導体発光素子の製造方法は、順方向電圧の低減には有効な方法であっても、量産性を確保するためには、透明導電膜の光吸収率が低いことだけでなく、光吸収率のばらつきが少ない透明導電膜が成膜できるような技術が必要である。

【0012】

そこで本発明は、低光吸収率の透明導電膜を安定的に成膜できることで、高い品質が確保できる発光素子の製造方法を提供することを目的とする。

【課題を解決するための手段】

【0013】

本発明の発光素子の製造方法は、透明導電膜となる原膜を、金属酸化物からなる成膜材料をターゲットとすると共に、酸素非含有雰囲気ガスにより半導体層にスパッタにより成膜し、この原膜を酸素非含有雰囲気ガスによりアニールした後、酸素含有雰囲気ガスによりアニールすることを特徴とする。

【発明の効果】

【0014】

本発明の発光素子の製造方法によれば、第1アニール工程または第2アニール工程のいずれか一方、または両方のアニールを、600℃より高く、680℃より低くした雰囲気温度で行うことで、透明導電膜の光吸収率が抑えることができると共に、光吸収率のばらつきを抑えることができるので、低光吸収率の透明導電膜を安定的に成膜できることで、高い品質が確保できる。

【図面の簡単な説明】

【0015】

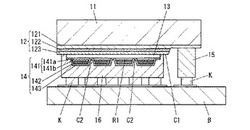

【図1】本発明の実施の形態に係る発光素子の断面図

【図2】図1に示す発光素子の透明導電膜上の導通領域と反射領域とを説明するための図

【図3】(A)は2段階アニールの時間と雰囲気温度との関係を示す図、(B)は2段階アニールの時間とガス量との関係を示す図

【図4】実施例1における2段階アニールによる発明品と1段階アニールによる比較品との波長と光吸収率の関係を示す図

【図5】実施例2における光吸収率のばらつきを示す図

【図6】従来の発光素子を示す断面図

【発明を実施するための形態】

【0016】

本願の第1の発明は、光透過性を有する基板と、基板に、n型半導体層、発光層およびp型半導体層が積層された半導体層と、半導体層に積層され、金属酸化物からなる成膜材料により成膜された透明導電膜と、透明導電膜に積層された反射部とを備えた発光素子の製造方法であって、金属酸化物からなる成膜材料をターゲットとすると共に、酸素非含有雰囲気ガスにより半導体層に透明導電膜の原膜をスパッタにより成膜するスパッタ工程と、原膜を酸素含有雰囲気ガスによりアニールする第1アニール工程と、第1アニール工程の後に、酸素非含有雰囲気ガスによりアニールする第2アニール工程とを含み、第1アニール工程または第2アニール工程のいずれか一方、または両方の雰囲気温度が600℃より高いことを特徴とした発光素子の製造方法である。

【0017】

第1の発明によれば、酸素非含有雰囲気ガスでスパッタにより成膜された透明導電膜の原膜を、第1アニール工程または第2アニール工程のいずれか一方、または両方のアニールを、600℃より高くした雰囲気温度で行うことで、透明導電膜の光吸収率が抑えることができると共に、光吸収率のばらつきを抑えることができる。

【0018】

本願の第2の発明は、第1アニール工程または第2アニール工程のいずれか一方、または両方の雰囲気温度が630℃より高いことを特徴とした発光素子の製造方法である。

【0019】

第2の発明によれば、第1アニール工程または第2アニール工程のいずれか一方、または両方の雰囲気温度を600℃より高く、更に、630℃より高くすることで、透明導電膜の光吸収率を低く抑えつつ、光吸収率のばらつきを更に抑えることができる。

【0020】

本願の第3の発明は、第1の発明において、透明導電膜を、InとSnとGaとを含む金属酸化物あるいはInとZnとGaとを含む金属酸化物で成膜することを特徴とした発光素子の製造方法である。

【0021】

第3の発明によれば、透明導電膜を、InとSnとGaとAlとを含む金属酸化物あるいはInとZnとGaとAlとを含む金属酸化物で成膜することができる。そうすることで、透明導電膜でIn濃度を最適化させると、半導体層とのコンタクト抵抗を良好な値に調整することができる。

【0022】

本願の第4の発明は、第3の発明において、透明導電膜を、ITOにより成膜することを特徴とした発光素子の製造方法である。

【0023】

第4の発明によれば、透明導電膜を、ITOにより成膜することができる。

【0024】

本願の第5の発明は、第1から第3のいずれかの発明において、透明導電膜を、10nm以上で成膜することを特徴とした発光素子の製造方法である。

【0025】

第5の発明によれば、透明導電膜を、10nm以上で成膜することができる。

【0026】

(実施の形態)

本発明の実施の形態に係る発光素子を図1、図2に基づいて説明する。図1に示す発光素子は、バンプKを介在させて実装基板Bにフリップチップ実装される発光波長が455nmの青色LEDチップである。

【0027】

発光素子には、絶縁性基板の透光性基板11に、n型半導体層121と、発光層122と、p型半導体層123とが積層された半導体層12が設けられている。透光性基板11とn型半導体層121との間にバッファ層を設けてもよい。

【0028】

透光性基板11は、発光層122からの光を透過させるものが使用できる。透光性基板11としては、例えば、サファイア基板、SiC基板、ZnO基板などが使用できる。

【0029】

n型半導体層121は、n型GaN層とすることができる。また、n型半導体層121は、単層構造に限らず、多層構造でもよい。例えば、透光性基板11がサファイア基板の場合には、AlN層やAlGaN層などのバッファ層を介在させ、n型半導体層121を、n型AlGaN層と、n型AlGaN層上にn型GaN層とを積層した構成としてもよい。

【0030】

発光層122は、少なくともGaとNとを含み、必要に応じて適量のInを含ませることで、所望の発光波長を得ることができる。また、発光層122としては、1層構造とすることもできるが、例えば、InGaN層とGaN層を交互に少なくとも一対積層した多量子井戸構造とすることも可能である。発光層122を多量子井戸構造とすることができる。本実施の形態では、発光層122による発光ピーク波長が450nmとなるようにInGaN層の組成を設定してある。なお、発光層122は、単一量子井戸構造としたり、単層構造としたりすることも可能である。

【0031】

p型半導体層123は、p型GaN層とすることができる。また、p型半導体層123は、単層構造に限らず、多層構造とすることも可能である。その場合には、例えば、p型半導体層123をp型AlGaN層とp型GaN層とを積層した多層膜とすることができる。

【0032】

半導体層12には、p型半導体層123よりも屈折率が小さいGZO膜、例えば、GZO(GaをドープしたZnO),AZO(AlをドーピングしたZnO),ITOの群から選択される三元系の金属酸化物を成膜材料から形成された透明導電膜13が成膜されている。本実施の形態では、透明導電膜13の膜厚が10nmに設定されている。

【0033】

このような材料により透明導電膜13を成膜することで、透明導電膜13とp型半導体層123との接触をオーミック接触とすることができる。

【0034】

透明導電膜13には、反射部14が積層されている。この反射部14は、低屈折率誘電膜141と、接着誘電膜142と、反射導電膜143とを備えている。

【0035】

低屈折率誘電膜141は、透明導電膜13の周縁部C1と、円形領域を縦列および横列に配置した格子部C2とを透明導電膜13と反射導電膜143との導通を図る導通領域として除いた領域であって、透明導電膜13から透過した光を反射する反射領域R1として割り当てた領域に設けられている。低屈折率誘電膜141は、p型半導体層123より屈折率が小さく、かつ透明導電膜13の屈折率より小さいものである。

【0036】

この低屈折率誘電膜141は、第1の低屈折率誘電膜141aと第2の低屈折率誘電膜141bとにより形成されている。第1の低屈折率誘電膜141aの膜厚は、酸素量の観点から、3nm以上とするのが好ましく、5nm以上であるのがより好ましい。更に、6nm以上とするのが好ましい。

【0037】

低屈折率誘電膜141は、例えば、屈折率が1.46のSiO2から成膜された誘電体である。SiO2膜とした低屈折率誘電膜141は、膜厚が300nmに設定されている。低屈折率誘電膜141はSiO2膜とする以外に、p型半導体層123より屈折率が小さいシリコン化合物であればよく、SiON膜などとすることができる。また、屈折率が1.6〜1.9程度のAl2O3により成膜することもできる。

【0038】

接着誘電膜142は、金属元素との酸化物からなる誘電体により形成され、低屈折率誘電膜141上に成膜されている。本実施の形態では、接着誘電膜142を、屈折率が1.6〜1.9程度のAl2O3により成膜している。Al2O3膜とした接着誘電膜142の膜厚は、30nmである。接着誘電膜142は、Al2O3膜とする以外に、Ta2O6膜、ZrO2膜、NbO2膜、TiO2膜とすることができる。

【0039】

反射導電膜143は、透明導電膜13との導通を図る導通領域(周縁部C1および格子部C2)と、低屈折率誘電膜141および接着誘電膜142を通過した光を反射する反射領域R1とを被覆する金属膜である。本実施の形態1では、反射導電膜143を、高い反射率を有するAg膜としている。Ag膜とした反射導電膜143は、膜厚を100nmとすることができる。この膜厚は、例えば、50nm〜200nm程度の範囲で設定することが可能である。反射導電膜143は、Ag膜とする以外に、Al膜とすることができる。しかし、反射導電膜143は、Al膜よりAg膜の方が、反射率が高いので、Ag膜とするのが好ましい。

【0040】

n電極15は、p型半導体層123と発光層122とn型半導体層121の一部とをエッチングしたn型半導体層121上の領域に設けられたカソード電極である。n電極15は、矩形状に形成された透光性基板11の対角となる位置に設けられている。n電極15は、Ti層とAu層とが積層されて形成されている。n型半導体層121上に積層されるn電極15のTi層は、n型半導体層121に対するオーミックコンタクト層として機能する。オーミックコンタクト層の材料は、例えば、Ti,V,Alやこれらのいずれか一種類の金属を含む合金などとすることができる。Ti層に積層されたAu層はnパッド層として機能する。

【0041】

p電極16は、エッチングされた残余のp型半導体層123上に積層されたアノード電極である。p電極16は、n電極15が設けられている残余の範囲に設けられている。p電極16は、反射導電膜143上に積層されたAu層と、Ti層と、Au層とが積層されて形成されている。最表面のAu層がpパッド層として機能する。p電極16は、等間隔のマトリクス状に配置されたバンプKを介在させて実装基板Bに導通搭載されている。本実施の形態では、n電極15を導通させるためのバンプKも含めて5×5のバンプKにより発光素子が実装基板Bに導通搭載されている。

【0042】

以上のように構成された本発明の実施の形態に係る発光素子の製造方法を図面に基づいて説明する。

【0043】

半導体層12は、透光性基板11にMOVPE法のようなエピタキシャル成長技術により成膜することができるが、例えば、ハイドライド気相成長法(HVPE法)や、分子線エピタキシー法(MBE法)などにより積層することも可能である。

【0044】

透明導電膜13をGZO,AZO,ITOなどにより成膜する。ここで、透明導電膜13の成膜方法を、図面に基づいて詳細に説明する。

【0045】

まず、透明導電膜13を成膜するときには、一般的なスパッタ装置により、まず原膜を成膜するスパッタ工程を行う。スパッタ装置は、マイクロ波発生装置(図示せず)からのマイクロ波により、プラズマ室にて気体分子にエネルギーを与えてプラズマを発生させ、このプラズマを成膜材料であるターゲットへ衝突させ、ターゲットから飛び出した成膜材料を成膜室の基板に付着させて薄膜を成膜するECR(Electron Cyclotron Resonance)スパッタ装置である。プラズマを磁界内で回転させて、高密度のプラズマを発生させることで緻密な膜を形成することが可能である。

【0046】

このようにしてスパッタ工程により透明導電膜13の原膜が成膜されると、第1アニール工程を行う。このアニール工程は、一般的な温度調整が可能なアニール装置により行うことができる。

【0047】

アニール工程は、図3(A)および図3(B)に示すように、酸素含有雰囲気ガスによりアニールする第1アニール工程と、酸素非含有雰囲気ガスによりアニールする第2アニール工程とを備えている。以下、この第1アニール工程と第2アニール工程との2回に分けてアニールすることを2段階アニールと称す。

【0048】

第1アニール工程では、酸素含有雰囲気ガスとして、O2ガスに、不活性ガスとしてアルゴンガス、窒素ガス、クリプトンガス、キセノンガス、ネオンガス、ラドンガス、またはこれらを混合させた混合ガスが使用できる。

【0049】

この第1アニール工程にて、原膜を酸素含有雰囲気ガスでアニールすることで、光吸収率が低いITO膜とすることができる。

【0050】

第1アニール工程が終了すれば、雰囲気ガスを排出するための真空引きを行って連続的に、第2アニール工程を行う。

【0051】

第2アニール工程では、酸素非含有雰囲気ガスとして、第1アニール工程で使用した不活性ガスを採用することができる。例えば、アルゴンガス、窒素ガス、クリプトンガス、キセノンガス、ネオンガス、ラドンガス、またはこれらを混合させた混合ガスが使用できる。

【0052】

この第2アニール工程にて、第1アニール工程後の原膜を酸素非含有雰囲気ガスでアニールすることで、酸素欠損を一定程度残したまま、結晶粒を大きくすることができるので、結晶粒界での光吸収率を低減させる効果を得ることができる。また、透明導電膜13に酸素欠損が一定量残っているので半導体層12との良好なコンタクト抵抗を維持したまま、光吸収率の低減を図ることが可能である。

【0053】

第1アニール工程と第2アニール工程とにおける雰囲気温度としては、600℃より高い温度とするのが、光吸収率のばらつきを抑えることができるので望ましく、更に、630℃以上とすると更にばらつき度合いを抑えることができるので望ましい。

【0054】

アニールの際の雰囲気温度が600℃より低ければ、透明導電膜13の光吸収率のばらつきが大きくなる。雰囲気温度の上限については、発光素子として動作する範囲であれば、特に制限されない。しかし、雰囲気温度の上限については、順方向電流が小さくなり輝度低下したり、電圧降下が大きくなったりするような発光素子の特性悪化が生じない程度の温度とするのが望ましい。

【0055】

次に、低屈折率誘電膜141を成膜する。低屈折率誘電膜141は、スパッタ法により成膜することができる。ここで、低屈折率誘電膜141の成膜方法について、詳細に説明する。

【0056】

まず、透明導電膜13と接する第1の低屈折率誘電膜141aおよび第2の低屈折率誘電膜141bは、透明導電膜13の原膜を成膜したときと同様のスパッタ装置により成膜することができる。

【0057】

まず、オキサイドモードによるスパッタで第1の低屈折率誘電膜141aを成膜する。そして、次に、メタルモードによるスパッタで第2の低屈折率誘電膜141bを成膜する。第2の低屈折率誘電膜141bをメタルモードによるスパッタで成膜することで、スパッタレートをオキサイドモードによるスパッタより大きくすることができるので、より反射率の高い膜厚の第2の低屈折率誘電膜141bを効率よく成膜することができる。従って、量産性を高めることができる。

【0058】

なお、オキサイドモードとは、ターゲット表面が酸化されて酸化物として飛び出した成膜材料を付着させて成膜するモードを指す。メタルモードとは、ターゲットから金属粒子がスパッタされて基板上で酸化反応させて成膜するモードを指す。

【0059】

第1の低屈折率誘電膜141aとなる誘電膜と、第2の低屈折率誘電膜141bとなる誘電膜とが成膜されれば、接着誘電膜142となる誘電膜を成膜する。

【0060】

そして、透明導電膜13との導通領域となる透明導電膜13の周縁部C1と格子部C2とを除く反射領域となる領域に、マスクを形成する。

【0061】

次に、マスクされた反射領域以外の領域を透明導電膜13が露出するまでエッチングにより除去することで、第1の低屈折率誘電膜141aと第2の低屈折率誘電膜141bと接着誘電膜142とが形成される。そして、第1の低屈折率誘電膜141aと第2の低屈折率誘電膜141bとが形成されれば、マスクの除去を行う。

【0062】

次に、反射導電膜143を導通領域および反射領域全体にAg膜またはAl膜により成膜する。そして、p型半導体層123と発光層122とn型半導体層121の一部とがエッチングにより除去された領域にn電極15を、透明導電膜13および反射部14全体を覆うようにp電極16を形成することで発光素子を作製することができる。

【0063】

(実施例1)

本実施例1では、発明品1として、基板上にITOによる単膜を成膜して透明導電膜13とし、波長が455nmの光を照射して、その光吸収率を測定した。

【0064】

なお、スパッタの条件は以下である。

【0065】

(a)ターゲット:Al

(b)雰囲気ガス:Arガス(流量:50sccm 圧力:0.2Pa)

(c)マイクロ波パワー:500W/RFパワー:500W

(d)オキサイドモードにおけるO2ガスの流量:11ccm

(e)メタルモードにおけるO2ガスの流量:10ccm

低屈折率誘電膜141としてスパッタで成膜されるAl2O3膜の膜厚は30nmである。

【0066】

第1アニール工程は以下の条件で行った。

【0067】

(a)雰囲気ガス:N2ガス(流量:20L/分 圧力:0.2Pa)

O2ガス(流量: 5L/分 圧力:0.2Pa)

(b)雰囲気温度:650℃

(c)加熱時間:3分間

第2アニール工程は以下の条件で行った。

【0068】

(a)雰囲気ガス:N2ガス(流量: 5L/分 圧力:0.2Pa)

(b)雰囲気温度:650℃

(c)加熱時間:10分間

また、比較品1として、スパッタによる原膜の成膜までは同じで、アニールを2段階アニールとせずに、1回のアニールとした。その場合の条件を以下に示す。

【0069】

(a)雰囲気ガス:O2ガス(流量:20L/分 圧力:0.2Pa)

(b)雰囲気温度:650℃

(c)加熱時間:13分間

結果を図4に示す。図4に示すグラフからもわかるように、波長455nmの光吸収率は、発明品が0.09%であるのに対して、比較品1では0.24%で、約63%改善した。

【0070】

(実施例2)

本実施例2では、実施例1における発明品1と、第1アニール工程、第2アニール工程のそれぞれの雰囲気温度を630℃(発明品2)としたものとの透明導電膜13の光吸収率のばらつきを測定した。また、比較品2として、スパッタによる原膜の成膜までは同じで、アニール条件を2段階アニールとせずに、1回のアニールとした。但し、雰囲気温度は600℃である。

【0071】

図5から分かるように、1段階アニールの比較品2よりも雰囲気温度を630℃とした2段階アニールの発明品2の方が光吸収率が低減していることがわかる。また、アニールの際の雰囲気温度を630℃とした発明品2より雰囲気温度を650℃とした発明品1の方がばらつきが抑えられていることがわかる。

【産業上の利用可能性】

【0072】

本発明は、低光吸収率の透明導電膜を安定的に成膜できることで、高い品質が確保できるので、基板に発光層を含む半導体層が積層され、発光層からの光を基板方向へ反射する反射部を備えた発光素子の製造方法に好適である。

【符号の説明】

【0073】

11 透光性基板

12 半導体層

13 透明導電膜

14 反射部

15 n電極

16 p電極

121 n型半導体層

122 発光層

123 p型半導体層

141 低屈折率誘電膜

141a 第1の低屈折率誘電膜

141b 第2の低屈折率誘電膜

142 接着誘電膜

143 反射導電膜

B 実装基板

K バンプ

【技術分野】

【0001】

本発明は、基板に発光層を含む半導体層が積層され、発光層からの光を基板方向へ反射する反射部を備えた発光素子の製造方法に関するものである。

【背景技術】

【0002】

実装基板にフリップチップ実装される従来の発光素子として、例えば、特許文献1に記載のものが知られている。

【0003】

この特許文献1に記載の発光素子を図6に基づいて説明する。発光素子100は、ベース基板101にn型半導体層102と発光層103とp型半導体層104とが積層され、更に、アノード電極110が形成されている。

【0004】

このアノード電極110は、p型半導体層104上に、Ni,Pd,Pt,Cr,Mn,Ta,Cu,Feなどの材料により形成された第1の透明導電膜111と、第1の透明導電膜111上に、ITO,IZO,ZnO,In2O3,SnO2,MgxZn1-xO(x≦0.5),アモルファスAlGaN,GaN,SiONの群から選択される1つの材料により形成された第2の透明導電膜112と、第2の透明導電膜112上に形成され発光層103から放射された光を反射する屈折率が異なる2種類の誘電体膜が交互に積層された複数の多層反射膜層113と、発光層103からの光に対して高い反射率を有するAgの金属材料からなる金属反射膜114と、金属反射膜114上に形成されたバリアメタル膜115と、バリアメタル膜115上に形成された金属材料からなる外部接続用金属膜116とにより構成されている。

【0005】

発光素子100では、透明導電膜を、金属酸化物からなる透明金属材料を用いることにより、発光層103からの光を効率よく多層反射膜層113や金属反射膜114の方向へ、また多層反射膜層113や金属反射膜114にて反射した光を効率よくベース基板101の方向へ透過させることができる。

【0006】

透明導電膜については、フリップチップタイプではないが、特許文献2に記載された技術が知られている。

【0007】

特許文献2には、透明導電膜(透光性の正極)がITO(In2O3−SnO2),AZnO(ZnO−Al2O3),IZnO(In2O3−ZnO),GZO(ZnO−GeO2)からなる少なくとも一種類を含んだ材料により成膜されている。この透明導電膜をp型半導体層上に成膜するときには、透光性酸化物導電材料の透光性正極を化学量論組成よりも酸素不足にした状態でスパッタまたは蒸着により形成した後、0.1%〜50%の酸素含有雰囲気中において20℃/分〜500℃/分の範囲の昇温速度で加熱し、250℃〜600℃の範囲の温度で30秒〜10分程度保持するアニール処理し、その後、99.9%以上で露点−30℃以下のN2ガスによる無酸素雰囲気において200℃〜500℃の範囲で1分から20分の範囲の温度で再アニール処理することが記載されている。この製造方法により透明導電膜を成膜することで、標準順電圧(Vf)が低く、透光性正極の高い透光性と低いシート抵抗、低い標準順電圧(Vf)、並びにp型半導体層に対する高い接合強度を得ることができる。

【先行技術文献】

【特許文献】

【0008】

【特許文献1】特開2007−258276号公報

【特許文献2】特開2007−287786号公報

【発明の概要】

【発明が解決しようとする課題】

【0009】

従来の発光素子100では、p型半導体層104上に第1,2の透明導電膜111,112が設けられ、第2の透明導電膜112上に誘電体膜からなる多層反射膜層113を設けているため、多層反射膜層113で多くの光を反射させ、光取り出し効率を向上させるためには、第2の透明導電膜112で発光層103からの光を遮ることなく多くの光を透過させることが重要である。

【0010】

しかし、特許文献2に記載の半導体発光素子の製造方法によれば、透明導電膜を酸素含有雰囲気中でアニール処理し、無酸素雰囲気中で再アニール処理することで抵抗値を下げることができるものの、透明導電膜の光吸収率がばらつくという問題があることがわかった。つまり、光吸収率が高い透明導電膜が成膜されてしまうことがある。そうなると、輝度が低い発光素子となってしまう。

【0011】

従って、特許文献2に記載の半導体発光素子の製造方法は、順方向電圧の低減には有効な方法であっても、量産性を確保するためには、透明導電膜の光吸収率が低いことだけでなく、光吸収率のばらつきが少ない透明導電膜が成膜できるような技術が必要である。

【0012】

そこで本発明は、低光吸収率の透明導電膜を安定的に成膜できることで、高い品質が確保できる発光素子の製造方法を提供することを目的とする。

【課題を解決するための手段】

【0013】

本発明の発光素子の製造方法は、透明導電膜となる原膜を、金属酸化物からなる成膜材料をターゲットとすると共に、酸素非含有雰囲気ガスにより半導体層にスパッタにより成膜し、この原膜を酸素非含有雰囲気ガスによりアニールした後、酸素含有雰囲気ガスによりアニールすることを特徴とする。

【発明の効果】

【0014】

本発明の発光素子の製造方法によれば、第1アニール工程または第2アニール工程のいずれか一方、または両方のアニールを、600℃より高く、680℃より低くした雰囲気温度で行うことで、透明導電膜の光吸収率が抑えることができると共に、光吸収率のばらつきを抑えることができるので、低光吸収率の透明導電膜を安定的に成膜できることで、高い品質が確保できる。

【図面の簡単な説明】

【0015】

【図1】本発明の実施の形態に係る発光素子の断面図

【図2】図1に示す発光素子の透明導電膜上の導通領域と反射領域とを説明するための図

【図3】(A)は2段階アニールの時間と雰囲気温度との関係を示す図、(B)は2段階アニールの時間とガス量との関係を示す図

【図4】実施例1における2段階アニールによる発明品と1段階アニールによる比較品との波長と光吸収率の関係を示す図

【図5】実施例2における光吸収率のばらつきを示す図

【図6】従来の発光素子を示す断面図

【発明を実施するための形態】

【0016】

本願の第1の発明は、光透過性を有する基板と、基板に、n型半導体層、発光層およびp型半導体層が積層された半導体層と、半導体層に積層され、金属酸化物からなる成膜材料により成膜された透明導電膜と、透明導電膜に積層された反射部とを備えた発光素子の製造方法であって、金属酸化物からなる成膜材料をターゲットとすると共に、酸素非含有雰囲気ガスにより半導体層に透明導電膜の原膜をスパッタにより成膜するスパッタ工程と、原膜を酸素含有雰囲気ガスによりアニールする第1アニール工程と、第1アニール工程の後に、酸素非含有雰囲気ガスによりアニールする第2アニール工程とを含み、第1アニール工程または第2アニール工程のいずれか一方、または両方の雰囲気温度が600℃より高いことを特徴とした発光素子の製造方法である。

【0017】

第1の発明によれば、酸素非含有雰囲気ガスでスパッタにより成膜された透明導電膜の原膜を、第1アニール工程または第2アニール工程のいずれか一方、または両方のアニールを、600℃より高くした雰囲気温度で行うことで、透明導電膜の光吸収率が抑えることができると共に、光吸収率のばらつきを抑えることができる。

【0018】

本願の第2の発明は、第1アニール工程または第2アニール工程のいずれか一方、または両方の雰囲気温度が630℃より高いことを特徴とした発光素子の製造方法である。

【0019】

第2の発明によれば、第1アニール工程または第2アニール工程のいずれか一方、または両方の雰囲気温度を600℃より高く、更に、630℃より高くすることで、透明導電膜の光吸収率を低く抑えつつ、光吸収率のばらつきを更に抑えることができる。

【0020】

本願の第3の発明は、第1の発明において、透明導電膜を、InとSnとGaとを含む金属酸化物あるいはInとZnとGaとを含む金属酸化物で成膜することを特徴とした発光素子の製造方法である。

【0021】

第3の発明によれば、透明導電膜を、InとSnとGaとAlとを含む金属酸化物あるいはInとZnとGaとAlとを含む金属酸化物で成膜することができる。そうすることで、透明導電膜でIn濃度を最適化させると、半導体層とのコンタクト抵抗を良好な値に調整することができる。

【0022】

本願の第4の発明は、第3の発明において、透明導電膜を、ITOにより成膜することを特徴とした発光素子の製造方法である。

【0023】

第4の発明によれば、透明導電膜を、ITOにより成膜することができる。

【0024】

本願の第5の発明は、第1から第3のいずれかの発明において、透明導電膜を、10nm以上で成膜することを特徴とした発光素子の製造方法である。

【0025】

第5の発明によれば、透明導電膜を、10nm以上で成膜することができる。

【0026】

(実施の形態)

本発明の実施の形態に係る発光素子を図1、図2に基づいて説明する。図1に示す発光素子は、バンプKを介在させて実装基板Bにフリップチップ実装される発光波長が455nmの青色LEDチップである。

【0027】

発光素子には、絶縁性基板の透光性基板11に、n型半導体層121と、発光層122と、p型半導体層123とが積層された半導体層12が設けられている。透光性基板11とn型半導体層121との間にバッファ層を設けてもよい。

【0028】

透光性基板11は、発光層122からの光を透過させるものが使用できる。透光性基板11としては、例えば、サファイア基板、SiC基板、ZnO基板などが使用できる。

【0029】

n型半導体層121は、n型GaN層とすることができる。また、n型半導体層121は、単層構造に限らず、多層構造でもよい。例えば、透光性基板11がサファイア基板の場合には、AlN層やAlGaN層などのバッファ層を介在させ、n型半導体層121を、n型AlGaN層と、n型AlGaN層上にn型GaN層とを積層した構成としてもよい。

【0030】

発光層122は、少なくともGaとNとを含み、必要に応じて適量のInを含ませることで、所望の発光波長を得ることができる。また、発光層122としては、1層構造とすることもできるが、例えば、InGaN層とGaN層を交互に少なくとも一対積層した多量子井戸構造とすることも可能である。発光層122を多量子井戸構造とすることができる。本実施の形態では、発光層122による発光ピーク波長が450nmとなるようにInGaN層の組成を設定してある。なお、発光層122は、単一量子井戸構造としたり、単層構造としたりすることも可能である。

【0031】

p型半導体層123は、p型GaN層とすることができる。また、p型半導体層123は、単層構造に限らず、多層構造とすることも可能である。その場合には、例えば、p型半導体層123をp型AlGaN層とp型GaN層とを積層した多層膜とすることができる。

【0032】

半導体層12には、p型半導体層123よりも屈折率が小さいGZO膜、例えば、GZO(GaをドープしたZnO),AZO(AlをドーピングしたZnO),ITOの群から選択される三元系の金属酸化物を成膜材料から形成された透明導電膜13が成膜されている。本実施の形態では、透明導電膜13の膜厚が10nmに設定されている。

【0033】

このような材料により透明導電膜13を成膜することで、透明導電膜13とp型半導体層123との接触をオーミック接触とすることができる。

【0034】

透明導電膜13には、反射部14が積層されている。この反射部14は、低屈折率誘電膜141と、接着誘電膜142と、反射導電膜143とを備えている。

【0035】

低屈折率誘電膜141は、透明導電膜13の周縁部C1と、円形領域を縦列および横列に配置した格子部C2とを透明導電膜13と反射導電膜143との導通を図る導通領域として除いた領域であって、透明導電膜13から透過した光を反射する反射領域R1として割り当てた領域に設けられている。低屈折率誘電膜141は、p型半導体層123より屈折率が小さく、かつ透明導電膜13の屈折率より小さいものである。

【0036】

この低屈折率誘電膜141は、第1の低屈折率誘電膜141aと第2の低屈折率誘電膜141bとにより形成されている。第1の低屈折率誘電膜141aの膜厚は、酸素量の観点から、3nm以上とするのが好ましく、5nm以上であるのがより好ましい。更に、6nm以上とするのが好ましい。

【0037】

低屈折率誘電膜141は、例えば、屈折率が1.46のSiO2から成膜された誘電体である。SiO2膜とした低屈折率誘電膜141は、膜厚が300nmに設定されている。低屈折率誘電膜141はSiO2膜とする以外に、p型半導体層123より屈折率が小さいシリコン化合物であればよく、SiON膜などとすることができる。また、屈折率が1.6〜1.9程度のAl2O3により成膜することもできる。

【0038】

接着誘電膜142は、金属元素との酸化物からなる誘電体により形成され、低屈折率誘電膜141上に成膜されている。本実施の形態では、接着誘電膜142を、屈折率が1.6〜1.9程度のAl2O3により成膜している。Al2O3膜とした接着誘電膜142の膜厚は、30nmである。接着誘電膜142は、Al2O3膜とする以外に、Ta2O6膜、ZrO2膜、NbO2膜、TiO2膜とすることができる。

【0039】

反射導電膜143は、透明導電膜13との導通を図る導通領域(周縁部C1および格子部C2)と、低屈折率誘電膜141および接着誘電膜142を通過した光を反射する反射領域R1とを被覆する金属膜である。本実施の形態1では、反射導電膜143を、高い反射率を有するAg膜としている。Ag膜とした反射導電膜143は、膜厚を100nmとすることができる。この膜厚は、例えば、50nm〜200nm程度の範囲で設定することが可能である。反射導電膜143は、Ag膜とする以外に、Al膜とすることができる。しかし、反射導電膜143は、Al膜よりAg膜の方が、反射率が高いので、Ag膜とするのが好ましい。

【0040】

n電極15は、p型半導体層123と発光層122とn型半導体層121の一部とをエッチングしたn型半導体層121上の領域に設けられたカソード電極である。n電極15は、矩形状に形成された透光性基板11の対角となる位置に設けられている。n電極15は、Ti層とAu層とが積層されて形成されている。n型半導体層121上に積層されるn電極15のTi層は、n型半導体層121に対するオーミックコンタクト層として機能する。オーミックコンタクト層の材料は、例えば、Ti,V,Alやこれらのいずれか一種類の金属を含む合金などとすることができる。Ti層に積層されたAu層はnパッド層として機能する。

【0041】

p電極16は、エッチングされた残余のp型半導体層123上に積層されたアノード電極である。p電極16は、n電極15が設けられている残余の範囲に設けられている。p電極16は、反射導電膜143上に積層されたAu層と、Ti層と、Au層とが積層されて形成されている。最表面のAu層がpパッド層として機能する。p電極16は、等間隔のマトリクス状に配置されたバンプKを介在させて実装基板Bに導通搭載されている。本実施の形態では、n電極15を導通させるためのバンプKも含めて5×5のバンプKにより発光素子が実装基板Bに導通搭載されている。

【0042】

以上のように構成された本発明の実施の形態に係る発光素子の製造方法を図面に基づいて説明する。

【0043】

半導体層12は、透光性基板11にMOVPE法のようなエピタキシャル成長技術により成膜することができるが、例えば、ハイドライド気相成長法(HVPE法)や、分子線エピタキシー法(MBE法)などにより積層することも可能である。

【0044】

透明導電膜13をGZO,AZO,ITOなどにより成膜する。ここで、透明導電膜13の成膜方法を、図面に基づいて詳細に説明する。

【0045】

まず、透明導電膜13を成膜するときには、一般的なスパッタ装置により、まず原膜を成膜するスパッタ工程を行う。スパッタ装置は、マイクロ波発生装置(図示せず)からのマイクロ波により、プラズマ室にて気体分子にエネルギーを与えてプラズマを発生させ、このプラズマを成膜材料であるターゲットへ衝突させ、ターゲットから飛び出した成膜材料を成膜室の基板に付着させて薄膜を成膜するECR(Electron Cyclotron Resonance)スパッタ装置である。プラズマを磁界内で回転させて、高密度のプラズマを発生させることで緻密な膜を形成することが可能である。

【0046】

このようにしてスパッタ工程により透明導電膜13の原膜が成膜されると、第1アニール工程を行う。このアニール工程は、一般的な温度調整が可能なアニール装置により行うことができる。

【0047】

アニール工程は、図3(A)および図3(B)に示すように、酸素含有雰囲気ガスによりアニールする第1アニール工程と、酸素非含有雰囲気ガスによりアニールする第2アニール工程とを備えている。以下、この第1アニール工程と第2アニール工程との2回に分けてアニールすることを2段階アニールと称す。

【0048】

第1アニール工程では、酸素含有雰囲気ガスとして、O2ガスに、不活性ガスとしてアルゴンガス、窒素ガス、クリプトンガス、キセノンガス、ネオンガス、ラドンガス、またはこれらを混合させた混合ガスが使用できる。

【0049】

この第1アニール工程にて、原膜を酸素含有雰囲気ガスでアニールすることで、光吸収率が低いITO膜とすることができる。

【0050】

第1アニール工程が終了すれば、雰囲気ガスを排出するための真空引きを行って連続的に、第2アニール工程を行う。

【0051】

第2アニール工程では、酸素非含有雰囲気ガスとして、第1アニール工程で使用した不活性ガスを採用することができる。例えば、アルゴンガス、窒素ガス、クリプトンガス、キセノンガス、ネオンガス、ラドンガス、またはこれらを混合させた混合ガスが使用できる。

【0052】

この第2アニール工程にて、第1アニール工程後の原膜を酸素非含有雰囲気ガスでアニールすることで、酸素欠損を一定程度残したまま、結晶粒を大きくすることができるので、結晶粒界での光吸収率を低減させる効果を得ることができる。また、透明導電膜13に酸素欠損が一定量残っているので半導体層12との良好なコンタクト抵抗を維持したまま、光吸収率の低減を図ることが可能である。

【0053】

第1アニール工程と第2アニール工程とにおける雰囲気温度としては、600℃より高い温度とするのが、光吸収率のばらつきを抑えることができるので望ましく、更に、630℃以上とすると更にばらつき度合いを抑えることができるので望ましい。

【0054】

アニールの際の雰囲気温度が600℃より低ければ、透明導電膜13の光吸収率のばらつきが大きくなる。雰囲気温度の上限については、発光素子として動作する範囲であれば、特に制限されない。しかし、雰囲気温度の上限については、順方向電流が小さくなり輝度低下したり、電圧降下が大きくなったりするような発光素子の特性悪化が生じない程度の温度とするのが望ましい。

【0055】

次に、低屈折率誘電膜141を成膜する。低屈折率誘電膜141は、スパッタ法により成膜することができる。ここで、低屈折率誘電膜141の成膜方法について、詳細に説明する。

【0056】

まず、透明導電膜13と接する第1の低屈折率誘電膜141aおよび第2の低屈折率誘電膜141bは、透明導電膜13の原膜を成膜したときと同様のスパッタ装置により成膜することができる。

【0057】

まず、オキサイドモードによるスパッタで第1の低屈折率誘電膜141aを成膜する。そして、次に、メタルモードによるスパッタで第2の低屈折率誘電膜141bを成膜する。第2の低屈折率誘電膜141bをメタルモードによるスパッタで成膜することで、スパッタレートをオキサイドモードによるスパッタより大きくすることができるので、より反射率の高い膜厚の第2の低屈折率誘電膜141bを効率よく成膜することができる。従って、量産性を高めることができる。

【0058】

なお、オキサイドモードとは、ターゲット表面が酸化されて酸化物として飛び出した成膜材料を付着させて成膜するモードを指す。メタルモードとは、ターゲットから金属粒子がスパッタされて基板上で酸化反応させて成膜するモードを指す。

【0059】

第1の低屈折率誘電膜141aとなる誘電膜と、第2の低屈折率誘電膜141bとなる誘電膜とが成膜されれば、接着誘電膜142となる誘電膜を成膜する。

【0060】

そして、透明導電膜13との導通領域となる透明導電膜13の周縁部C1と格子部C2とを除く反射領域となる領域に、マスクを形成する。

【0061】

次に、マスクされた反射領域以外の領域を透明導電膜13が露出するまでエッチングにより除去することで、第1の低屈折率誘電膜141aと第2の低屈折率誘電膜141bと接着誘電膜142とが形成される。そして、第1の低屈折率誘電膜141aと第2の低屈折率誘電膜141bとが形成されれば、マスクの除去を行う。

【0062】

次に、反射導電膜143を導通領域および反射領域全体にAg膜またはAl膜により成膜する。そして、p型半導体層123と発光層122とn型半導体層121の一部とがエッチングにより除去された領域にn電極15を、透明導電膜13および反射部14全体を覆うようにp電極16を形成することで発光素子を作製することができる。

【0063】

(実施例1)

本実施例1では、発明品1として、基板上にITOによる単膜を成膜して透明導電膜13とし、波長が455nmの光を照射して、その光吸収率を測定した。

【0064】

なお、スパッタの条件は以下である。

【0065】

(a)ターゲット:Al

(b)雰囲気ガス:Arガス(流量:50sccm 圧力:0.2Pa)

(c)マイクロ波パワー:500W/RFパワー:500W

(d)オキサイドモードにおけるO2ガスの流量:11ccm

(e)メタルモードにおけるO2ガスの流量:10ccm

低屈折率誘電膜141としてスパッタで成膜されるAl2O3膜の膜厚は30nmである。

【0066】

第1アニール工程は以下の条件で行った。

【0067】

(a)雰囲気ガス:N2ガス(流量:20L/分 圧力:0.2Pa)

O2ガス(流量: 5L/分 圧力:0.2Pa)

(b)雰囲気温度:650℃

(c)加熱時間:3分間

第2アニール工程は以下の条件で行った。

【0068】

(a)雰囲気ガス:N2ガス(流量: 5L/分 圧力:0.2Pa)

(b)雰囲気温度:650℃

(c)加熱時間:10分間

また、比較品1として、スパッタによる原膜の成膜までは同じで、アニールを2段階アニールとせずに、1回のアニールとした。その場合の条件を以下に示す。

【0069】

(a)雰囲気ガス:O2ガス(流量:20L/分 圧力:0.2Pa)

(b)雰囲気温度:650℃

(c)加熱時間:13分間

結果を図4に示す。図4に示すグラフからもわかるように、波長455nmの光吸収率は、発明品が0.09%であるのに対して、比較品1では0.24%で、約63%改善した。

【0070】

(実施例2)

本実施例2では、実施例1における発明品1と、第1アニール工程、第2アニール工程のそれぞれの雰囲気温度を630℃(発明品2)としたものとの透明導電膜13の光吸収率のばらつきを測定した。また、比較品2として、スパッタによる原膜の成膜までは同じで、アニール条件を2段階アニールとせずに、1回のアニールとした。但し、雰囲気温度は600℃である。

【0071】

図5から分かるように、1段階アニールの比較品2よりも雰囲気温度を630℃とした2段階アニールの発明品2の方が光吸収率が低減していることがわかる。また、アニールの際の雰囲気温度を630℃とした発明品2より雰囲気温度を650℃とした発明品1の方がばらつきが抑えられていることがわかる。

【産業上の利用可能性】

【0072】

本発明は、低光吸収率の透明導電膜を安定的に成膜できることで、高い品質が確保できるので、基板に発光層を含む半導体層が積層され、発光層からの光を基板方向へ反射する反射部を備えた発光素子の製造方法に好適である。

【符号の説明】

【0073】

11 透光性基板

12 半導体層

13 透明導電膜

14 反射部

15 n電極

16 p電極

121 n型半導体層

122 発光層

123 p型半導体層

141 低屈折率誘電膜

141a 第1の低屈折率誘電膜

141b 第2の低屈折率誘電膜

142 接着誘電膜

143 反射導電膜

B 実装基板

K バンプ

【特許請求の範囲】

【請求項1】

光透過性を有する基板と、前記基板に、n型半導体層、発光層およびp型半導体層が積層された半導体層と、前記半導体層に積層され、金属酸化物からなる成膜材料により成膜された透明導電膜と、前記透明導電膜に積層された反射部とを備えた発光素子の製造方法であって、

前記金属酸化物からなる成膜材料をターゲットとすると共に、酸素非含有雰囲気ガスにより前記半導体層に前記透明導電膜の原膜をスパッタにより成膜するスパッタ工程と、

前記原膜を酸素含有雰囲気ガスによりアニールする第1アニール工程と、

前記第1アニール工程の後に、酸素非含有雰囲気ガスによりアニールする第2アニール工程とを含み、

前記第1アニール工程または前記第2アニール工程のいずれか一方、または両方の雰囲気温度が600℃より高いことを特徴する発光素子の製造方法。

【請求項2】

前記第1アニール工程または前記第2アニール工程のいずれか一方、または両方の雰囲気温度が630℃より高い請求項1記載の発光素子の製造方法。

【請求項3】

前記透明導電膜を、InとSnとGaとAlとを含む金属酸化物あるいはInとZnとGaとAlとを含む金属酸化物で成膜する請求項1または2記載の発光素子の製造方法。

【請求項4】

前記透明導電膜を、ITOにより成膜する請求項3記載の発光素子の製造方法。

【請求項5】

前記透明導電膜を、10nm以上で成膜する請求項1から4のいずれかの項に記載の発光素子の製造方法。

【請求項1】

光透過性を有する基板と、前記基板に、n型半導体層、発光層およびp型半導体層が積層された半導体層と、前記半導体層に積層され、金属酸化物からなる成膜材料により成膜された透明導電膜と、前記透明導電膜に積層された反射部とを備えた発光素子の製造方法であって、

前記金属酸化物からなる成膜材料をターゲットとすると共に、酸素非含有雰囲気ガスにより前記半導体層に前記透明導電膜の原膜をスパッタにより成膜するスパッタ工程と、

前記原膜を酸素含有雰囲気ガスによりアニールする第1アニール工程と、

前記第1アニール工程の後に、酸素非含有雰囲気ガスによりアニールする第2アニール工程とを含み、

前記第1アニール工程または前記第2アニール工程のいずれか一方、または両方の雰囲気温度が600℃より高いことを特徴する発光素子の製造方法。

【請求項2】

前記第1アニール工程または前記第2アニール工程のいずれか一方、または両方の雰囲気温度が630℃より高い請求項1記載の発光素子の製造方法。

【請求項3】

前記透明導電膜を、InとSnとGaとAlとを含む金属酸化物あるいはInとZnとGaとAlとを含む金属酸化物で成膜する請求項1または2記載の発光素子の製造方法。

【請求項4】

前記透明導電膜を、ITOにより成膜する請求項3記載の発光素子の製造方法。

【請求項5】

前記透明導電膜を、10nm以上で成膜する請求項1から4のいずれかの項に記載の発光素子の製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図2】

【図3】

【図4】

【図5】

【図6】

【公開番号】特開2013−51247(P2013−51247A)

【公開日】平成25年3月14日(2013.3.14)

【国際特許分類】

【出願番号】特願2011−187202(P2011−187202)

【出願日】平成23年8月30日(2011.8.30)

【出願人】(000005821)パナソニック株式会社 (73,050)

【Fターム(参考)】

【公開日】平成25年3月14日(2013.3.14)

【国際特許分類】

【出願日】平成23年8月30日(2011.8.30)

【出願人】(000005821)パナソニック株式会社 (73,050)

【Fターム(参考)】

[ Back to top ]