発光表示装置の作製方法

【課題】トランジスタの作製工程を簡略化し、フォトマスクの枚数を従来よりも少なくするだけでなく、新たな工程を増やすことなく発光表示装置を作製することを目的とする。

【解決手段】トランジスタを構成する半導体層に真性または実質的に真性な高抵抗の酸化物半導体を使用することによって、個々のトランジスタに対して半導体層を島状に加工する工程を省くことができる。半導体層の上層に形成した絶縁層を開口する工程において該半導体層の不要な部分を同時にエッチングし、フォトリソグラフィ工程を削減する。

【解決手段】トランジスタを構成する半導体層に真性または実質的に真性な高抵抗の酸化物半導体を使用することによって、個々のトランジスタに対して半導体層を島状に加工する工程を省くことができる。半導体層の上層に形成した絶縁層を開口する工程において該半導体層の不要な部分を同時にエッチングし、フォトリソグラフィ工程を削減する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、トランジスタを有する発光表示装置の作製方法に関する。

【背景技術】

【0002】

近年、ガラス基板等の絶縁性表面を有する基板上に形成された、厚さ数nm〜数百nm程度の半導体薄膜により構成される薄膜トランジスタが注目されている。薄膜トランジスタは、IC(Integrated Circuit)及び電気光学装置を始めとした電子デバイスに広く応用されている。薄膜トランジスタは、特にEL(Electro Luminescence)表示装置等に代表される、画像表示装置のスイッチング素子として開発が急がれている。

【0003】

アクティブマトリクス型EL表示装置では、選択された画素内に設けられた発光素子の一方の電極と、該電極とともにEL層(発光層を含む)を挟持する他方の電極の間に電圧が印加されることにより、EL層に電流が生じ、発光層が発光する。この発光が表示パターンとして観察者に認識される。ここで、アクティブマトリクス型EL表示装置とは、マトリクス状に配置された画素をスイッチング素子により駆動することによって、画面上に表示パターンが形成される方式を採用したEL表示装置をいう。

【0004】

上記のようなアクティブマトリクス型EL表示装置の用途は拡大しており、画面サイズの大面積化、高精細化及び高開口率化の要求が高まっている。また、アクティブマトリクス型表示装置には高い信頼性が求められ、その生産方法には高い生産性及び生産コストの低減が求められる。生産性を高め、生産コストを低減する方法の一つに、工程の簡略化が挙げられる。

【0005】

アクティブマトリクス型表示装置では、スイッチング素子として主に薄膜トランジスタが用いられている。薄膜トランジスタの作製において、フォトリソグラフィ工程を削減または簡略化することは、工程全体の簡略化のために重要である。例えばフォトリソグラフィ工程が1つ増加すると、レジスト塗布、プリベーク、露光、現像、ポストベーク等の工程と、その前後の工程において、被膜の形成及びエッチング工程、更にはレジスト剥離、洗浄及び乾燥工程等が必要になる。そのため、作製工程におけるフォトリソグラフィ工程が1つ増加するだけで、それに関する工程数が大幅に増加する。そのため、作製工程におけるフォトリソグラフィ工程を削減または簡略化するために、数多くの技術開発がなされている。

【0006】

薄膜トランジスタは、チャネル形成領域がゲート電極より下層に設けられるトップゲート型と、チャネル形成領域がゲート電極より上層に設けられるボトムゲート型に大別される。これらの薄膜トランジスタは、少なくとも5枚のフォトマスクにより作製されることが一般的である。

【0007】

フォトリソグラフィ工程を簡略化させる従来の技術としては、裏面露光、レジストリフロー又はリフトオフ法といった複雑な技術を用いるものが多く、特殊な装置を必要とするものが多い。このような複雑な技術を用いることで、これに起因する様々な問題が生じ、歩留まりの低下の一因となっている。また、薄膜トランジスタの電気的特性を犠牲にせざるを得ないことも多い。

【0008】

また、薄膜トランジスタの作製工程における、フォトリソグラフィ工程を簡略化するための代表的な手段として、多階調マスク(ハーフトーンマスク又はグレートーンマスクと呼ばれるもの)を用いた技術が広く知られている。多階調マスクを用いて作製工程を低減する技術として、例えば特許文献1が挙げられる。

【先行技術文献】

【特許文献】

【0009】

【特許文献1】特開2003−179069号公報

【発明の概要】

【発明が解決しようとする課題】

【0010】

多階調マスクを用いる場合は、マスク数を減らすことはできるが、レジストマスクを新たな形状とするにはアッシングなどの新たな工程が必要である。

【0011】

本発明の一態様は、フォトマスクの枚数を従来よりも少なくするだけでなく、新たな工程を増やすことなく発光表示装置を作製することを目的とする。

【課題を解決するための手段】

【0012】

本明細書で開示する本発明の一態様は、トランジスタを構成する半導体層に高抵抗の酸化物半導体を使用することによって、個々のトランジスタに対して半導体層を島状に加工する工程を省き、フォトリソグラフィ工程を削減する発光表示装置の作製方法に関する。

【0013】

本明細書で開示する本発明の一態様は、基板上に第1の導電膜を形成し、第1の導電膜上に第1のレジストマスクを形成し、第1のレジストマスクを用いて第1の導電膜を選択的にエッチングして、第1のゲート電極と第2のゲート電極を形成し、第1のゲート電極及び第2のゲート電極上にゲート絶縁層となる第1の絶縁膜を形成し、ゲート絶縁層上に半導体膜を形成し、半導体膜上に第2のレジストマスクを形成し、第2のレジストマスクを用いて第2のゲート電極上の半導体膜及び第1の絶縁膜の一部を選択的にエッチングして、第1の開口部を形成し、半導体膜及び第1の開口部を覆うように第2の導電膜を形成し、第2の導電膜上に第3のレジストマスクを形成し、第3のレジストマスクを用いて第2の導電膜を選択的にエッチングして、ソースドレイン配線と電気的に接続される第1のソース電極及びドレイン電極の一方と、第2のゲート電極と電気的に接続される第1のソース電極及びドレイン電極の他方と、電源配線に接続される第2のソース電極及びドレイン電極の一方と、第2のソース電極及びドレイン電極の他方を形成することによって、第1のゲート電極、第1のソース電極及びドレイン電極を有する第1のトランジスタ、及び第2のゲート電極、第2のソース電極及びドレイン電極を有する第2のトランジスタを形成し、第1のソース電極及びドレイン電極、第2のソース電極及びドレイン電極、及び半導体膜上に保護絶縁膜となる第2の絶縁膜を形成し、第2の絶縁膜上に第4のレジストマスクを形成し、第4のレジストマスクを用いて第2の絶縁膜及び半導体膜を選択的にエッチングして第2の開口部を形成すると同時に、第2のソース電極及びドレイン電極の他方の一部が露出するように第2の絶縁膜に第3の開口部を形成し、第3の開口部を覆うように第2の絶縁膜上に第3の導電膜を形成し、第3の導電膜上に第5のレジストマスクを形成し、第5のレジストマスクを用いて第3の導電膜を選択的にエッチングして第1の画素電極を形成し、第2の開口部、第3の開口部、及び画素電極の周囲を覆うように第3の絶縁膜を形成し、画素電極上に有機化合物を含む層を選択的に形成し、有機化合物を含む層上に第2の画素電極を形成することを特徴とする発光表示装置の作製方法である。

【0014】

なお、本明細書等における「第1」、「第2」、「第3」などの序数詞は、構成要素の混同を避けるために付すものであり、数的に限定するものではないことを付記する。

【0015】

また、本明細書で開示する本発明の他の一態様は、基板上に第1の導電膜を形成し、第1の導電膜上に第1のレジストマスクを形成し、第1のレジストマスクを用いて第1の導電膜を選択的にエッチングして、第1のゲート電極と第2のゲート電極を形成し、第1のゲート電極及び第2のゲート電極上にゲート絶縁層となる第1の絶縁膜を形成し、ゲート絶縁層上に半導体膜を形成し、半導体膜上に第2のレジストマスクを形成し、第2のレジストマスクを用いて第2のゲート電極上の半導体膜及び第1の絶縁膜の一部を選択的にエッチングして、第1の開口部を形成し、半導体膜及び第1の開口部を覆うように第2の導電膜を形成し、第2の導電膜上に第3のレジストマスクを形成し、第3のレジストマスクを用いて第2の導電膜を選択的にエッチングして、ソースドレイン配線と電気的に接続される第1のソース電極及びドレイン電極の一方と、第2のゲート電極と電気的に接続される第1のソース電極及びドレイン電極の他方と、電源配線に接続される第2のソース電極及びドレイン電極の一方と、第2のソース電極及びドレイン電極の他方を形成することによって、第1のゲート電極、第1のソース電極及びドレイン電極を有する第1のトランジスタ、及び第2のゲート電極、第2のソース電極及びドレイン電極を有する第2のトランジスタを形成し、第1のソース電極及びドレイン電極、第2のソース電極及びドレイン電極、及び半導体膜上に保護絶縁膜となる第2の絶縁膜を形成し、第2の絶縁膜上に平坦化絶縁膜として第3の絶縁膜を形成し、第3の絶縁膜上に第4のレジストマスクを形成し、第4のレジストマスクを用いて第3の絶縁膜、第2の絶縁膜及び半導体膜を選択的にエッチングして、第2の開口部を形成すると同時に、第2のソース電極及びドレイン電極の他方の一部が露出するように第2の絶縁膜に第3の開口部を形成し、第3の開口部を覆うように第3の絶縁膜上に第3の導電膜を形成し、第3の導電膜上に第5のレジストマスクを形成し、第5のレジストマスクを用いて第3の導電膜を選択的にエッチングして第1の画素電極を形成し、第2の開口部、第3の開口部、及び画素電極の周囲を覆うように第4の絶縁膜を形成し、画素電極上に有機化合物を含む層を選択的に形成し、有機化合物を含む層上に第2の画素電極を形成することを特徴とする発光表示装置の作製方法である。

【0016】

上記半導体膜には酸化物半導体を用いることが好ましい。i型化または実質的にi型化された酸化物半導体は、極めて抵抗が高く、回路を構成する上では絶縁体とみなすことができる。従って、同一島状の半導体層に複数のトランジスタが構成されていても互いに干渉することはなく、各トランジスタを動作させることができる。

【発明の効果】

【0017】

酸化物半導体は絶縁体とみなすことができるため、トランジスタ毎に島状の半導体層を形成する工程を省くことができ、フォトリソグラフィ工程を削減する発光表示装置の作製方法を提供することができる。

【図面の簡単な説明】

【0018】

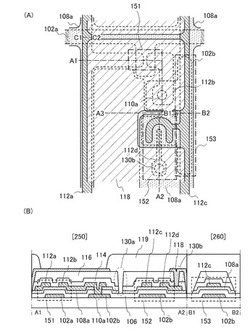

【図1】発光表示装置の一態様を説明する平面図及び断面図。

【図2】容量素子を有さない発光表示装置の平面図。

【図3】発光表示装置の画素部の等価回路図。

【図4】発光表示装置の作製方法の一態様を説明する断面図。

【図5】発光表示装置の作製方法の一態様を説明する断面図。

【図6】発光表示装置の作製方法の一態様を説明する断面図。

【図7】発光表示装置の作製方法の一態様を説明する断面図。

【図8】発光表示装置の作製方法の一態様を説明する断面図。

【図9】発光素子の構成を説明する断面図。

【図10】電子機器を示す図。

【図11】電子機器を示す図。

【図12】電子機器を示す図。

【図13】表示装置の映像と同期する専用の眼鏡を用いて動画または静止画である3D映像を視認する装置の一例を説明する図。

【図14】発光表示装置の一態様を説明する平面図及び断面図。

【図15】発光素子の構成を説明する断面図。

【図16】酸化物材料の構造を説明する図。

【図17】酸化物材料の構造を説明する図。

【図18】酸化物材料の構造を説明する図。

【図19】酸化物材料の構造を説明する図。

【発明を実施するための形態】

【0019】

以下では、本発明の実施の形態について図面を用いて詳細に説明する。ただし、本発明は以下の説明に限定されず、その形態及び詳細を様々に変更し得ることは、当業者であれば容易に理解される。また、本発明は以下に示す実施の形態の記載内容に限定して解釈されるものではない。なお、図面を用いて発明の構成を説明するにあたり、同じものを指す符号は異なる図面間でも共通して用いる。また、同様のものを指す際にはハッチパターンを同じくし、特に符号を付さない場合がある。

【0020】

(実施の形態1)

本実施の形態では、本発明の一態様における発光表示装置が有する画素部の構成の例を示す。

【0021】

図1(A)、(B)は、本発明の一態様を適用したアクティブマトリクス型の発光表示装置の画素部の一例である。図1(A)は発光表示装置の画素部の平面図であり、図1(B)は図1(A)における線A1−A2の断面図である。また、図3(A)は図1に示したアクティブマトリクス型発光表示装置の画素部の等価回路である。なお、図3(A)に示すEL層160及び第2の画素電極層(共通電極)170は、図1(A)、(B)には図示されていない。

【0022】

なお、本明細書において、EL層とは発光素子の一対の電極間に設けられた層を示すものとする。従って、電極間に挟まれた発光物質である有機化合物を含む層はEL層の一態様である。

【0023】

本実施の形態は、発光表示装置の画素部の構成及び作製方法について説明するものである。従って、本実施の形態におけるトランジスタとは、図1(A)、(B)に示す第1のトランジスタ151及び第2のトランジスタ152の両方またはいずれかのことを言う。また、該トランジスタは、後述する酸化物半導体を用いたnチャネル型である。

【0024】

図1(A)、(B)に示すアクティブマトリクス型の発光表示装置の画素部は、第1のゲート電極層102a、ゲート絶縁層106、半導体層108a、第1のソース電極層及びドレイン電極層112a、112bを含む第1のトランジスタ151と、第2のゲート電極層102b、ゲート絶縁層106、半導体層108a、第2のソース電極層及びドレイン電極層112c、112dを含む第2のトランジスタ152を有する。

【0025】

ここで、第1のゲート電極層102aはゲート配線と接続され、第1のソース電極層及びドレイン電極層112aはソースドレイン配線と接続され、第1のソース電極層及びドレイン電極層112bは第1の開口部110aにおいて第2のゲート電極層102bに接続され、第2のソース電極層及びドレイン電極層112cは電源配線に接続され、第2のソース電極層及びドレイン電極層112dは第3の開口部130bにおいて第1の画素電極層118と接続されている。なお、図1(A)において、ゲート配線と第1のゲート電極層、ソースドレイン配線と第1のソース電極層及びドレイン電極層の一方、電源配線と第2のソース電極層及びドレイン電極層の一方のそれぞれは一体であり、同じ符号を付してある。

【0026】

なお、図1では第1のトランジスタ151をシングルゲート構造で図示しているが、マルチゲート構造としても良い。マルチゲート構造のトランジスタは、オフ電流が小さく、該トランジスタを含む発光表示装置の表示特性を高めることができる。

【0027】

また、第2のゲート電極層102bと電源配線(第2のソース電極層及びドレイン電極層112c)は、ゲート絶縁層106及び半導体層108aを介して重なる領域を有しており、容量素子153を形成している。この様に、誘電体層を多層構造とすることで、一つの誘電体層にピンホールが生じても、ピンホールは他の誘電体層で被覆されるため、容量素子153を正常に機能させることができる。また、酸化物半導体の比誘電率は14乃至16と大きいため、半導体層108aに酸化物半導体を用いると、容量素子153の容量値を大きくすることが可能となる。

【0028】

第1のトランジスタ151及び第2のトランジスタ152上には保護絶縁層114及び平坦化絶縁層116が形成されており、その一部が開口されて、ゲート絶縁層106が露出する第2の開口部130aと第2のソース電極層及びドレイン電極層112dの一部が露出する第3の開口部130bが形成されている。また、平坦化絶縁層116を省いた構成とすることもできる。

【0029】

第3の開口部130bは第1の画素電極層118の一部で覆い、第2の開口部130aには隔壁119となる絶縁材料が充填される。ここで、隔壁119は図1(A)には図示されていないが、第1の画素電極層118の端部及び上記の構成において凹凸のある領域などを覆うように形成する。隔壁119によって、後に第1の画素電極層118上などに形成するEL層160や第2の画素電極層170の断切れを防止することができる。

【0030】

なお、図2に示すような容量素子を設けない構成としてもよい。図2では第2のゲート電極層102cを電源配線(第2のソース電極層及びドレイン電極層112c)と重ねない構成とし、容量素子を形成していない。この構成の等価回路は、図3(B)である。

【0031】

半導体層108aに用いる材料としては、酸化物半導体が好ましい。酸化物半導体層は、化学式InMO3(ZnO)m(m>0)で表記される材料を用いた薄膜により形成することができる。ここで、Mは、Sn、Zn、Ga、Al、Mn及びCoから選ばれた一つ、または複数の金属元素を示す。例えば、Mとして、Ga、Ga及びAl、Ga及びMnまたはGa及びCoなどを用いることができる。

【0032】

例えば、In:Ga:Zn=1:1:1(=1/3:1/3:1/3)あるいはIn:Ga:Zn=2:2:1(=2/5:2/5:1/5)の原子数比のIn−Ga−Zn−O系酸化物やその組成の近傍の酸化物を用いることができる。あるいは、In:Sn:Zn=1:1:1(=1/3:1/3:1/3)、In:Sn:Zn=2:1:3(=1/3:1/6:1/2)あるいはIn:Sn:Zn=2:1:5(=1/4:1/8:5/8)の原子数比のIn−Sn−Zn−O系酸化物やその組成の近傍の酸化物を用いるとよい。

【0033】

しかし、これらに限られず、必要とする半導体特性(移動度、しきい値、ばらつき等)に応じて適切な組成のものを用いればよい。また、必要とする半導体特性を得るために、キャリア濃度や不純物濃度、欠陥密度、金属元素と酸素の原子数比、原子間結合距離、密度等を適切なものとすることが好ましい。

【0034】

例えば、In−Sn−Zn−O系酸化物では比較的容易に高い移動度が得られる。しかしながら、In−Ga−Zn−O系酸化物でも、バルク内欠陥密度を低減することにより移動度を上げることができる。

【0035】

なお、例えば、In、Ga、Znの原子数比がIn:Ga:Zn=a:b:c(a+b+c=1)である酸化物が、原子数比がIn:Ga:Zn=A:B:C(A+B+C=1)の酸化物のrだけ近傍であるとは、a、b、cが、(a―A)2+(b―B)2+(c―C)2≦r2を満たすことを言う。rとしては、例えば、0.05とすればよい。他の酸化物でも同様である。

【0036】

酸化物半導体は単結晶でも、非単結晶でもよい。後者の場合、アモルファスでも、多結晶でもよい。また、アモルファス中に結晶性を有する部分を含む構造でも、非アモルファスでもよい。

【0037】

アモルファス状態の酸化物半導体は、比較的容易に平坦な表面を得ることができるため、これを用いてトランジスタを作製した際の界面散乱を低減でき、比較的容易に、比較的高い移動度を得ることができる。

【0038】

また、結晶性を有する酸化物半導体では、よりバルク内欠陥を低減することができ、表面の平坦性を高めればアモルファス状態の酸化物半導体以上の移動度を得ることができる。表面の平坦性を高めるためには、平坦な表面上に酸化物半導体を形成することが好ましく、具体的には、平均面粗さ(Ra)が1nm以下、好ましくは0.3nm以下、より好ましくは0.1nm以下の表面上に形成するとよい。

【0039】

なお、Raは、JIS B0601で定義されている中心線平均粗さを面に対して適用できるよう三次元に拡張したものであり、「基準面から指定面までの偏差の絶対値を平均した値」と表現でき、以下の式にて定義される。

【0040】

【数1】

【0041】

なお、上記において、S0は、測定面(座標(x1,y1)(x1,y2)(x2,y1)(x2,y2)で表される4点によって囲まれる長方形の領域)の面積を指し、Z0は測定面の平均高さを指す。Raは原子間力顕微鏡(AFM:Atomic Force Microscope)にて評価可能である。

【0042】

半導体層108aに酸化物半導体を用いたトランジスタは、極めてオフ電流が小さい電気特性を有する。酸化物半導体は、水素などの不純物が十分に除去されることにより、または、十分な酸素が供給されることにより、高純度化されたものであることが望ましい。具体的には、例えば、酸化物半導体の水素濃度は5×1019atoms/cm3以下、望ましくは5×1018atoms/cm3以下、より望ましくは5×1017atoms/cm3以下とする。なお、上述の酸化物半導体中の水素濃度は、二次イオン質量分析法(SIMS:Secondary Ion Mass Spectrometry)で測定されるものである。このように、水素濃度が十分に低減されて高純度化され、十分な酸素の供給により酸素欠損に起因するエネルギーギャップ中の欠陥準位が低減された酸化物半導体では、水素等のドナーに起因するキャリア密度が1×1012/cm3未満、望ましくは、1×1011/cm3未満、より望ましくは1.45×1010/cm3未満となる。また、例えば、室温(25℃)でのオフ電流(ここでは、単位チャネル幅(1μm)あたりの値)は100zA(1zA(ゼプトアンペア)は1×10−21A)以下、望ましくは10zA以下となる。このように、i型化(真性化)または実質的にi型化された酸化物半導体を用いることで、極めて優れたオフ電流特性のトランジスタを得ることができる。

【0043】

従って、画素に保持された電荷の保持特性が極めて高く、容量素子が無い場合、または図1(A)、(B)に示す構成より保持容量の面積を小さくした場合においても一般的なフレーム周波数(60Hz)もしくはそれ以下のフレーム周波数においても、何ら問題なく画像を保持することができる。

【0044】

また、酸化物半導体は不純物に対して鈍感であり、膜中にはかなりの金属不純物が含まれていても問題がなく、ナトリウムのようなアルカリ金属が多量に含まれる廉価なソーダ石灰ガラスも使えると指摘されている(神谷、野村、細野、「アモルファス酸化物半導体の物性とデバイス開発の現状」、固体物理、2009年9月号、Vol.44、p.621−633)しかし、このような指摘は適切でない。酸化物半導体中のアルカリ金属は、二次イオン質量分析法による含有量の最低値で、ナトリウム(Na)が5×1016cm−3以下、好ましくは1×1016cm−3以下、さらに好ましくは1×1015cm−3以下、リチウム(Li)が5×1015cm−3以下、好ましくは1×1015cm−3以下、カリウム(K)が5×1015cm−3以下、好ましくは1×1015cm−3以下である。

【0045】

アルカリ金属、及びアルカリ土類金属は酸化物半導体にとっては悪性の不純物であり、少ないほうがよい。特にアルカリ金属のうち、Naは酸化物半導体に接する絶縁膜が酸化物であった場合、その中に拡散し、Na+となる。また、酸化物半導体内において、金属と酸素の結合を分断し、あるいは結合中に割り込む。その結果、トランジスタ特性の劣化(例えば、ノーマリオン化(しきい値の負へのシフト)、移動度の低下等)をもたらす。加えて、特性のばらつきの原因ともなる。このような問題は、特に酸化物半導体中の水素の濃度が十分に低い場合において顕著となる。したがって、酸化物半導体中の水素の濃度が5×1019cm−3以下、特に5×1018cm−3以下である場合には、アルカリ金属の濃度を上記の値にすることが強く求められる。

【0046】

また、i型化または実質的にi型化された酸化物半導体は、極めて抵抗が高く、回路を構成する上では絶縁体とみなすことができる。従って、同一島状の半導体層に複数のトランジスタが構成されていても互いに干渉することはなく、各トランジスタを動作させることができる。なお、本実施の形態では2つのトランジスタが同一島状の半導体層に形成されているが、容量素子部に半導体層を残さない構造とすれば、2つのトランジスタの半導体層を分離することもできる。

【0047】

また、図1(B)の構成においては、第1の画素電極層118が半導体層108aの側面に接して形成されている領域があるが、上記と同様にi型化または実質的にi型化された酸化物半導体は、ほぼ絶縁物とみなすことができるため、第1の画素電極層118と半導体層108aの端部が接しても、漏れ電流等の問題は生じない。

【0048】

また、半導体層108aに酸化物半導体を用いる場合は、図14(A)、(B)に示すように、画素領域全面に半導体層を残す構成としても良い。酸化物半導体層は上述のように高抵抗であることと、可視光に対して透光性を有するため、発光素子からの発光方向がトランジスタ側であっても光を透過させることができる。

【0049】

本実施の形態に示す第2のトランジスタ152は、第2のソース電極層及びドレイン電極層112dを、U字型(C字型、コの字型、または馬蹄型)の第2のソース電極層及びドレイン電極層112cで囲む形状としている。このような形状とすることで、トランジスタの面積が少なくても、十分なチャネル幅を確保することが可能となり、トランジスタの導通時に流れる電流(オン電流ともいう)の量を増やすことが可能となる。

【0050】

本発明の一態様は、保護絶縁層114と半導体膜108のエッチングを連続して行うことによりフォトリソグラフィ工程が削減できるという特徴があり、次に図4乃至7を用いて作製方法の一例の詳細を説明する。

【0051】

なお、ここではトランジスタ部250の作製方法を主として説明するが、図示してあるように容量素子部260、配線交差部270、及びFPC接続部280についても必要に応じて説明する。

【0052】

まず、絶縁表面を有する基板100上に第1の導電膜を形成した後、第1のフォトリソグラフィ工程、及びエッチング工程により第1のゲート電極層102a、第2のゲート電極層102bを形成する(図4(A)参照)。

【0053】

なお、フォトリソグラフィ工程に用いるレジストマスクはインクジェット法で形成してもよい。インクジェット法では、フォトマスクを使用しないため、更に製造コストを低減することができる。また、レジストマスクはエッチング工程の後に剥離するものとし、各フォトリソグラフィ工程における説明は省くこととする。

【0054】

ここで、基板100には、少なくとも、後の熱処理に耐えうる程度の耐熱性を有しているものを用いることができる。例えば、バリウムホウケイ酸ガラスやアルミノホウケイ酸ガラスなどのガラス基板、セラミック基板、石英基板、サファイア基板などを用いることができる。また、シリコンや炭化シリコンなどの単結晶半導体基板、多結晶半導体基板、シリコンゲルマニウムなどの化合物半導体基板、SOI基板などを用いることもできる。

【0055】

基板100と第1のゲート電極層102a、第2のゲート電極層102bとの間には、下地膜となる絶縁膜を設けてもよい。下地膜は、基板100からの不純物元素の拡散を防止する機能があり、酸化シリコン、酸窒化シリコン、窒化シリコン、酸化ハフニウム、酸化アルミニウム、酸化ガリウム、酸化ガリウムアルミニウムから選ばれた膜で形成することができる。また、該下地膜は単層に限らず、上記の複数の膜の積層であっても良い。

【0056】

第1のゲート電極層102a、第2のゲート電極層102bは、モリブデン、チタン、タンタル、タングステン、アルミニウム、銅、ネオジム、スカンジウム等の金属材料、またはこれらを主成分とする合金材料をスパッタ法等で形成することができる。また、該ゲート電極層は単層に限らず、上記複数の材料の積層であっても良い。例えば、アルミニウムとモリブデンの積層、アルミニウムとチタンの積層、銅とモリブデンの積層、または銅とタングステンの積層などがある。ここでは、銅上にモリブデンを形成した積層を用いる。

【0057】

次いで、第1のゲート電極層102a、第2のゲート電極層102b上にゲート絶縁層106をCVD法やスパッタ法等を用いて形成する。ゲート絶縁層106は、酸化シリコン、窒化シリコン、酸窒化シリコン、酸化アルミニウム、酸化タンタル、酸化ハフニウム、酸化イットリウム、酸化ガリウム、酸化ランタン、ハフニウムシリケート(HfSixOy(x>0、y>0))、窒素が添加されたハフニウムシリケート(HfSiOxNy(x>0、y>0))、窒素が添加されたハフニウムアルミネート(HfAlOxNy(x>0、y>0))、などを含むように形成するのが好適である。またはこれらの混合材料をプラズマCVD法、またはスパッタ法等により形成することもできる。また、ゲート絶縁層106は単層に限らず、上記複数の材料の積層であっても良い。また、その厚さは特に限定されないが、例えば、酸化シリコンを用いる場合には、1nm以上100nm以下、好ましくは10nm以上50nm以下とすることができる。

【0058】

なお、ゲート絶縁層106には、後に形成される半導体膜と同種の成分を含む絶縁材料を用いることが好ましい。この様な材料は、半導体膜との界面の状態を良好に保つことができる。ここで、「半導体膜と同種の成分」とは、半導体膜の構成元素から選択される一つまたは複数の元素を含むことを意味する。例えば、半導体膜がIn−Ga−Zn−O系の酸化物半導体材料によって構成される場合、同種の成分を含む絶縁材料としては酸化ガリウムなどがある。

【0059】

また、ゲート絶縁層106の形成には、緻密で絶縁耐圧の高い高品質な絶縁層を形成できるマイクロ波(例えば周波数2.45GHz)を用いた高密度プラズマCVDを用いることが好ましい。半導体層と高品質ゲート絶縁層が密接することにより、界面準位を低減することができる。

【0060】

また、成膜後の熱処理によってゲート絶縁層の膜質や、半導体層との界面特性が改質される絶縁層であっても良い。いずれにしても、ゲート絶縁層は、膜質が良好であることは勿論のこと、半導体層との界面準位密度を低減し、良好な界面を形成できるものが好ましい。

【0061】

また、ゲート絶縁層106上に形成される半導体膜(ここでは酸化物半導体膜)に水素、水酸基及び水分が極力含まれない様にするために、ゲート絶縁層106までが形成された基板100を成膜装置の予備加熱室で真空加熱し、基板100に吸着した水素、水分などの不純物を脱離させて排気することが好ましい。なお、予備加熱室に設ける排気手段には、クライオポンプを用いることが好ましい。なお、この予備加熱の処理は省略することもできる。

【0062】

次いで、ゲート絶縁層106上に、膜厚2nm以上200nm以下、好ましくは5nm以上30nm以下の半導体膜108を形成する(図4(B)参照)。

【0063】

半導体膜108には酸化物半導体を用いることが好ましい。また、用いる酸化物半導体としては、少なくともインジウム(In)あるいは亜鉛(Zn)を含むことが好ましい。特にInとZnを含むことが好ましい。また、該酸化物半導体を用いたトランジスタの電気特性のばらつきを減らすためのスタビライザーとして、それらに加えてガリウム(Ga)を有することが好ましい。また、スタビライザーとしてスズ(Sn)を有することが好ましい。また、スタビライザーとしてハフニウム(Hf)を有することが好ましい。また、スタビライザーとしてアルミニウム(Al)を有することが好ましい。

【0064】

また、他のスタビライザーとして、ランタノイドである、ランタン(La)、セリウム(Ce)、プラセオジム(Pr)、ネオジム(Nd)、サマリウム(Sm)、ユウロピウム(Eu)、ガドリニウム(Gd)、テルビウム(Tb)、ジスプロシウム(Dy)、ホルミウム(Ho)、エルビウム(Er)、ツリウム(Tm)、イッテルビウム(Yb)、ルテチウム(Lu)のいずれか一種あるいは複数種を有してもよい。

【0065】

例えば、酸化物半導体として、酸化インジウム、酸化スズ、酸化亜鉛、二元系金属の酸化物であるIn−Zn−O系酸化物、Sn−Zn−O系酸化物、Al−Zn−O系酸化物、Zn−Mg−O系酸化物、Sn−Mg−O系酸化物、In−Mg−O系酸化物、In−Ga−O系酸化物、三元系金属の酸化物であるIn−Ga−Zn−O系酸化物(IGZOとも表記する)、In−Al−Zn−O系酸化物、In−Sn−Zn−O系酸化物、Sn−Ga−Zn−O系酸化物、Al−Ga−Zn−O系酸化物、Sn−Al−Zn−O系酸化物、In−Hf−Zn−O系酸化物、In−La−Zn−O系酸化物、In−Ce−Zn−O系酸化物、In−Pr−Zn−O系酸化物、In−Nd−Zn−O系酸化物、In−Sm−Zn−O系酸化物、In−Eu−Zn−O系酸化物、In−Gd−Zn−O系酸化物、In−Tb−Zn−O系酸化物、In−Dy−Zn−O系酸化物、In−Ho−Zn−O系酸化物、In−Er−Zn−O系酸化物、In−Tm−Zn−O系酸化物、In−Yb−Zn−O系酸化物、In−Lu−Zn−O系酸化物、四元系金属の酸化物であるIn−Sn−Ga−Zn−O系酸化物、In−Hf−Ga−Zn−O系酸化物、In−Al−Ga−Zn−O系酸化物、In−Sn−Al−Zn−O系酸化物、In−Sn−Hf−Zn−O系酸化物、In−Hf−Al−Zn−O系酸化物を用いることができる。

【0066】

なお、ここで、例えば、In−Ga−Zn−O系酸化物とは、InとGaとZnを主成分として有する酸化物という意味であり、InとGaとZnの比率は問わない。また、InとGaとZn以外の金属元素が入っていてもよい。

【0067】

特にインジウムを含む酸化物半導体、インジウム及びガリウムを含む酸化物半導体などを用いると電気特性が良好なトランジスタを形成することができる。本実施の形態では、半導体膜108としてIn−Ga−Zn−O系酸化物からなる膜をスパッタ法により成膜する。

【0068】

上記スパッタ法に用いるターゲットには、例えば、組成比として、In2O3:Ga2O3:ZnO=1:1:1[mol数比]の酸化物ターゲットを用いる。また、In2O3:Ga2O3:ZnO=1:1:2[mol数比]の酸化物ターゲットを用いてもよい。

【0069】

また、酸化物半導体としてIn−Zn−O系酸化物を用いる場合、用いる酸化物ターゲットの組成比は、原子数比で、In:Zn=50:1〜1:2(mol数比に換算するとIn2O3:ZnO=25:1〜1:4)、好ましくはIn:Zn=20:1〜1:1(mol数比に換算するとIn2O3:ZnO=10:1〜1:2)、さらに好ましくはIn:Zn=15:1〜1.5:1(mol数比に換算するとIn2O3:ZnO=15:2〜3:4)とする。例えば、In−Zn−O系酸化物半導体の形成に用いる酸化物ターゲットは、原子数比がIn:Zn:O=X:Y:Zのとき、Z>1.5X+Yとする。

【0070】

また、In−Sn−Zn−O系酸化物は、ITZOと呼ぶことができ、用いるターゲットの組成比は、In:Sn:Znが原子数比で、1:2:2、2:1:3、1:1:1、または20:45:35などとなる酸化物ターゲットを用いる。

【0071】

また、ターゲットの充填率は90%以上100%以下、好ましくは95%以上100%以下である。充填率の高いターゲットを用いることにより、成膜した酸化物半導体膜は緻密な膜とすることができる。

【0072】

また、スパッタガスとしては、希ガス(代表的にはアルゴン)、酸素、または希ガスと酸素の混合ガスを用いることができる。なお、該スパッタガスには、水素、水、水酸基または水素化物などの不純物が除去された高純度ガスを用いることが好ましい。

【0073】

酸化物半導体膜の成膜は、基板を加熱しながら成膜することが好ましい。減圧状態に保持された成膜室内に基板を保持し、基板温度を200℃以上450℃以下として成膜することで、酸化物半導体膜に含まれる不純物濃度を低減することができる。ただし、ゲート電極層に用いる材料により上限の温度がことなり、本実施の形態のように融点が高い銅とモリブデンの積層と用いる場合や、銅とタングステンの積層を用いる場合は、450℃を上限とすることができるが、融点が低いアルミニウムを含む積層を用いる場合は、上限を380℃とすることが好ましい。

【0074】

また、成膜室内の残留水分を除去するためには、吸着型の真空ポンプ、例えば、クライオポンプ、イオンポンプ、チタンサブリメーションポンプを用いることが好ましい。また、排気手段としては、ターボ分子ポンプにコールドトラップを加えたものであってもよい。クライオポンプを用いて排気した成膜室は、例えば、水素原子、水など水素原子を含む化合物、及び炭素原子を含む化合物等が排気されるため、該成膜室で成膜した酸化物半導体膜に含まれる不純物の濃度を低減することができる。

【0075】

成膜条件の一例としては、基板とターゲットの間との距離を100mm、圧力0.6Pa、直流(DC)電源0.5kW、酸素(酸素流量比率100%)雰囲気下の条件が挙げられる。なお、パルス直流電源を用いると、成膜時に発生する粉状物質(パーティクル、ごみともいう)を軽減でき、膜厚分布も均一にすることができる。

【0076】

次いで、第1の熱処理による半導体膜108の脱水化または脱水素化を行う。本明細書において、脱水化または脱水素化とは、水や水素分子を脱離させていることのみを示すものではなく、水素原子や水酸基などを脱離することも含まれる。

【0077】

熱処理は、例えば、抵抗発熱体などを用いた電気炉に被処理物を導入し、窒素雰囲気下、450℃、1時間の条件で行うことができる。この間、半導体膜108は大気に触れさせず、水や水素の混入が生じないようにする。

【0078】

この熱処理によって過剰な水素(水や水酸基を含む)を除去し、酸化物半導体膜の構造を整え、エネルギーギャップ中の欠陥準位を低減することができる。熱処理の温度は、250℃以上450℃以下とする。また、熱処理時間は、上記好適な温度範囲であれば1時間程度行えば良い。ただし、低温で長時間、または高温で短時間の処理を行っても良く、実施者が適宜決定すれば良い。なお、上限の温度はゲート電極層に用いる材料に依存するため、上述したように銅を含む材料を用いる場合は、450℃を上限とすることができるが、アルミニウムを含む材料を用いる場合は、380℃が上限となる。

【0079】

熱処理装置は電気炉に限られず、加熱されたガスなどの媒体からの熱伝導、または熱輻射によって、被処理物を加熱する装置を用いても良い。例えば、GRTA(Gas Rapid Thermal Anneal)装置、LRTA(Lamp Rapid Thermal Anneal)装置等のRTA(Rapid Thermal Anneal)装置を用いることができる。LRTA装置は、ハロゲンランプ、メタルハライドランプ、キセノンアークランプ、カーボンアークランプ、高圧ナトリウムランプ、高圧水銀ランプなどのランプから発する光(電磁波)の輻射により、被処理物を加熱する装置である。GRTA装置は、高温のガスを用いて熱処理を行う装置である。ガスとしては、アルゴンなどの希ガス、または窒素のような、熱処理によって被処理物と反応しない不活性気体が用いられる。

【0080】

例えば、第1の熱処理として、熱せられた不活性ガス雰囲気中に被処理物を投入し、数分間熱した後、当該不活性ガス雰囲気から被処理物を取り出すGRTA処理を行ってもよい。GRTA処理を用いると短時間での高温熱処理が可能となる。また、被処理物の耐熱温度を超える温度条件であっても適用が可能となる。なお、処理中に、不活性ガスを、酸素を含むガスに切り替えても良い。酸素を含む雰囲気において第1の熱処理を行うことで、酸素欠損に起因するエネルギーギャップ中の欠陥準位を低減することができるためである。

【0081】

なお、不活性ガス雰囲気としては、窒素、または希ガス(ヘリウム、ネオン、アルゴン等)を主成分とする雰囲気であって、水、水素などが含まれない雰囲気を適用するのが望ましい。例えば、熱処理装置に導入する窒素や、ヘリウム、ネオン、アルゴン等の希ガスの純度を、6N(99.9999%)以上、好ましくは7N(99.99999%)以上(すなわち、不純物濃度が1ppm以下、好ましくは0.1ppm以下)とする。

【0082】

いずれにしても、第1の熱処理によって不純物を低減し、i型(真性半導体)またはi型に限りなく近い酸化物半導体膜を形成することで、極めて優れた特性のトランジスタを実現することができる。

【0083】

なお、上述の熱処理は、このタイミングに限らず、ソース電極及びドレイン電極形成後や保護絶縁膜形成後に行ってもよい。また、一回に限らず複数回行っても良い。

【0084】

次いで、第2のフォトリソグラフィ工程、及びエッチング工程により、第2のゲート電極層102b、及び第1のゲート電極層102a上の半導体膜108及びゲート絶縁層106の一部を開口した第1の開口部110a、110bを形成する。ここで、第1の開口部110aは、後に第1のトランジスタ151の第1のソース電極層及びドレイン電極層112bと第2のゲート電極102bとの接続のために用いられ、FPC接続部に形成される第1の開口部110bは、第1のゲート電極層102aを露出させるための開口である(図4(C)参照)。

【0085】

ここで、半導体膜108及びゲート絶縁層106のエッチングは、ドライエッチング、またはウェットエッチングのどちらを用いても良い。また、両方を用いてもよい。例えば、酸化物半導体である半導体膜108のエッチング液としては、燐酸、酢酸、及び硝酸を混ぜた溶液などを用いることができる。また、ITO−07N(関東化学社製)を用いてもよい。また、ゲート絶縁層106は、フッ酸系のエッチング液を用いれば良い。

【0086】

次いで、第2のゲート電極層102b、第1のゲート電極層102a、及び半導体膜108上に、トランジスタのソース電極層及びドレイン電極層(これと同じ層で形成される配線を含む)となる第2の導電膜112を形成する(図5(A)参照)。

【0087】

第2の導電膜112としては、例えば、アルミニウム、クロム、銅、タンタル、チタン、モリブデン、タングステンからから選ばれた元素を含む金属膜、または上述した元素を成分とする金属窒化物膜(窒化チタン膜、窒化モリブデン膜、窒化タングステン膜)等を用いることができる。また、アルミニウム、銅などの金属膜の一方の面または双方の面にチタン、モリブデン、タングステンなどの高融点金属膜またはそれらの窒化膜(窒化チタン膜、窒化モリブデン膜、窒化タングステン膜等)を積層させた構成としても良い。例えば、タングステンと銅の積層、タングステン、窒化タングステン、銅、タングステンの積層、モリブデン、窒化モリブデン、銅、モリブデンの積層、モリブデン、アルミニウム、モリブデンの積層などがある。本実施の形態では、タングステン上に銅を形成した積層を用いる。

【0088】

次いで、第3のフォトリソグラフィ工程により第2の導電膜112上にレジストマスクを形成し、選択的にエッチングを行って、第1のソース電極層及びドレイン電極層112a、112b、第2のソース電極層及びドレイン電極層112c、112dを形成する。また、容量素子部においては、ゲート絶縁層106及び半導体膜108を介して第2のゲート電極と重なるように電源配線(第2のソース電極層及びドレイン電極層112c)を形成する。また、FPC接続部には第1のゲート電極層102aと電気的に接続される導電層112eを形成する(図5(B)参照)。

【0089】

なお、第2の導電膜112のエッチングの際に、半導体膜108が極力エッチングされない様にすることが好ましい。しかしながら、第2の導電膜112のみをエッチングする条件を得ることは難しく、第2の導電膜112のエッチングの際に半導体膜108の一部がエッチングされ、溝部(凹部)を有する形状となることもある。

【0090】

以上の工程で第1のトランジスタ151、第2のトランジスタ152、及び容量素子153が形成される。該トランジスタは、水素、水分、水酸基または水素化物(水素化合物ともいう)などの不純物を半導体膜108より意図的に排除し、高純度化された酸化物半導体を含むトランジスタである。よって、該トランジスタは、電気的特性変動が抑制されており、電気的に安定である。

【0091】

次に、基板100上に形成した上記の構成を覆うように保護絶縁層114を形成する(図5(C)参照)。保護絶縁層114は、少なくとも1nm以上の膜厚とし、保護絶縁層114に水、水素等の不純物を極力混入させない上述した方法を適宜用いて形成することができる。本実施の形態では、スパッタ法を用いて保護絶縁層114を形成する。保護絶縁層114に水素が含まれていると、その水素が半導体膜108へ侵入する場合や、半導体膜108中の酸素を水素が引き抜く現象が生じることがある。この様な現象が起こると、半導体膜108のバックチャネル側が低抵抗化(n型化)してしまい、寄生チャネルが形成されてしまうことがある。従って、保護絶縁層114はできるだけ水素を含まない膜になる様にすることが重要である。

【0092】

保護絶縁層114は、PVD法やCVD法などを用いて形成することができる。また、酸化シリコン、酸窒化シリコン、窒化シリコン、酸化ハフニウム、酸化アルミニウム、酸化ガリウム、酸化ガリウムアルミニウム等の無機絶縁材料を含む材料を用いて、単層または積層で形成することができる。

【0093】

なお、保護絶縁層114には、ゲート絶縁層106と同様に、半導体膜108と同種の成分を含む絶縁材料を用いると好ましい。この様な材料は半導体膜108との界面の状態を良好に保つことができる。例えば、半導体膜108がIn−Ga−Zn−O系の酸化物半導体材料によって構成される場合、同種の成分でなる絶縁材料としては酸化ガリウムなどがある。

【0094】

また、保護絶縁層114を積層構造とする場合には、半導体膜108と同種の成分を含む絶縁膜(以下、膜a)と、膜aの成分材料とは異なる材料を含む膜(以下、膜b)との積層構造とするとなお良い。膜aと膜bとを半導体膜108側から順に積層した構造とすることで、電荷は膜aと膜bとの界面の電荷捕獲中心に優先的に捕獲される(半導体膜108と膜aとの界面との比較)ため、半導体膜108の界面での電荷捕獲を十分に抑制することができる様になり、トランジスタの信頼性が向上するためである。

【0095】

例えば、保護絶縁層114として半導体膜108側から酸化ガリウム膜と酸化シリコン膜との積層、または酸化ガリウム膜と窒化シリコン膜との積層などを用いることが好適である。

【0096】

本実施の形態では、保護絶縁層114に酸化シリコン膜を用いる。酸化シリコン膜は、希ガス、酸素、または希ガスと酸素の混合ガスを用いて、スパッタ法で成膜することができる。成膜時の基板温度は、室温以上300℃以下とすればよく、本実施の形態では100℃とする。また、ターゲットには、酸化シリコンターゲットまたはシリコンターゲットを用いることができる。例えば、シリコンターゲットを用いて、酸素をスパッタガスとして酸化シリコンを形成することができる。

【0097】

また、保護絶縁層114形成時においても、半導体膜108の成膜時と同様に成膜室内の残留水分を除去するため、吸着型の真空ポンプ(クライオポンプなど)を用いることが好ましい。クライオポンプを用いて排気した成膜室では、例えば、水素原子、水など水素原子を含む化合物、及び炭素原子を含む化合物等が排気されるため、成膜した保護絶縁層114に含まれる不純物の濃度を低減できる。また、成膜室内の残留水分を除去するための排気手段としては、ターボ分子ポンプにコールドトラップを加えたものであってもよい。

【0098】

保護絶縁層114を成膜する際に用いるスパッタガスには、水素、水、水酸基または水素化物などの不純物が除去された高純度ガスを用いることが好ましい。

【0099】

上述の保護絶縁層114の形成後に第2の熱処理を行っても良い。熱処理の方法や雰囲気には、前述した第1の熱処理と同様の方法を用いることができる。第1の熱処理と同様にゲート電極層、ソース電極層及びドレイン電極層に用いる材料によって熱処理の上限温度は異なり、該電極層が銅、モリブデン、タングステンなどの融点の高い金属で構成されている場合は450℃を上限温度とすることができる。一方、該電極層がアルミニウムなどの融点の低い金属が含まれて構成されている場合は、380℃を上限温度とすることができる。また、大気中、100℃以上200℃以下、1時間以上30時間以下の熱処理を行ってもよい。この熱処理は一定温度を1回で行うだけでなく、室温から100℃以上200℃以下の温度への昇温と、その温度から室温までの降温を複数回繰り返して行ってもよい。

【0100】

半導体膜108と酸素を含む保護絶縁層114を接した状態で熱処理を行うと、酸素を含む保護絶縁層114より酸素をさらに半導体膜108へ供給することができる。

【0101】

次いで、保護絶縁層114上に平坦化絶縁層116を形成する(図6(A)参照)。平坦化絶縁層116は、アクリル、ポリイミド、ポリアミドなどの有機樹脂、またはシロキサンを用いて形成することが好ましい。

【0102】

上記樹脂として、感光性樹脂を用いればフォトレジストが不要となり、露光することで所望の形状が得られるため、工程を簡略化することができる。また、露光して所望の形状に硬化させた感光性樹脂をレジストマスクとすることができる。

【0103】

本実施の形態では、平坦化絶縁層116に感光性アクリル樹脂を用い、露光(第4のフォトリソグラフィ工程)によって開口部を有する形状を得た後、該感光性アクリル樹脂をマスクとして保護絶縁層114及び半導体膜108をエッチングし、第2の開口部130a、第3の開口部130bを形成する(図6(B)参照)。

【0104】

エッチングは、ドライエッチングでもウェットエッチングでもよく、両方を用いてもよい。ドライエッチングに用いるエッチングガスとしては、塩素を含むガス(塩素系ガス、例えば塩素(Cl2)、三塩化硼素(BCl3)、四塩化珪素(SiCl4)、四塩化炭素(CCl4)など)を用いることができる。ドライエッチング法としては、平行平板型RIE(Reactive Ion Etching)法や、ICP(Inductively Coupled Plasma:誘導結合型プラズマ)エッチング法を用いることができる。

【0105】

第2の開口部130aは、保護絶縁層114及び半導体膜108をエッチングして形成される。ここで、半導体膜108の不要な領域は取り除かれ、半導体層108aが形成される。従って、半導体膜を島状に加工するような工程を省くことができる。すなわち、フォトリソグラフィ工程を削減することができる。

【0106】

第3の開口部130bは、保護絶縁層114の下部にある第2のソース電極層及びドレイン電極層112d、及び導電層112eがエッチングストッパーとなるため、保護絶縁層114のみがエッチングされて形成される。

【0107】

また、本実施の形態に示す作製工程によれば、半導体層108a上にフォトレジストが直接形成されることがなく、フォトレジストの剥離洗浄工程などにおいて半導体層108aを汚染することがないため、トランジスタの電気特性の変動を抑えることができる。

【0108】

次いで、第3の開口部130bを覆うように第3の導電膜を形成する。本実施の形態では、第1のトランジスタ151、第2のトランジスタ152は半導体層108aに酸化物半導体を用いたnチャネル型であり、第1の画素電極層118となる第3の導電膜としては発光素子の陰極となる材料を用いるのが望ましい。具体的には、陰極としては、仕事関数が小さい材料、例えば、Ca、Al、CaF、MgAg、AlLi等を用いることができる。なお、発光方向を制御するために第3の導電膜として透光性導電膜を用いても良い。この場合は、透光性導電膜上に陰極となる上記材料を形成すれば良い。なお、透光性導電膜としては、例えば酸化タングステンを含むインジウム酸化物、酸化タングステンを含むインジウム亜鉛酸化物、酸化チタンを含むインジウム酸化物、酸化チタンを含むインジウム錫酸化物、インジウム錫酸化物(以下、ITOと示す。)、インジウム亜鉛酸化物、酸化ケイ素を添加したインジウム錫酸化物などがある。また、1枚乃至10枚のグラフェンシート(グラファイトの1層分)よりなる材料を用いてもよい。

【0109】

次いで、第5のフォトリソグラフィ工程により第3の導電膜上にレジストマスクを形成し、選択的にエッチングを行って、第1の画素電極層118を形成する。このとき、第2の開口部に第1の画素電極層118が形成されても良い。なお、第3の導電膜にITO等の酸化物導電層を用いると、FPC接続部において下層の金属導電層の表面酸化によるFPC端子との接触抵抗の増加を抑えることができ、半導体装置の信頼性を向上させることができる。

【0110】

次いで、第2の開口部130a、第3の開口部130b、及び第1の画素電極層118の周囲を覆うように隔壁119を形成する(図6(C)参照)。

【0111】

次いで、図示はしないが、第1の画素電極層118上にEL層及び第2の画素電極層を選択的に形成する。

【0112】

以上の工程を含む作製方法によって発光表示装置を完成させることができる。なお、上記の方法で形成される構成とは異なり、容量素子153を形成しない構成では、図4(A)において、容量素子を形成する領域に第2のゲート電極層102bを設けない構成とすれば良い。

【0113】

また、平坦化絶縁層116を設けない構成とすることもできる。この構成の作製方法は、図5(C)までは上述の方法と同様であり、第4のフォトリソグラフィ工程によって、第2の開口部120a、第3の開口部120bを形成する(図7(A)参照)。

【0114】

次いで、少なくとも第3の開口部120bを覆うように保護絶縁層114上に第3の導電膜を形成し、第5のフォトリソグラフィ工程により第3の導電膜上にレジストマスクを形成し、選択的にエッチングを行って、第1の画素電極層118を形成する。このとき、第2の開口部120aの一部に第1の画素電極層118が形成されても良い。

【0115】

次いで、第2の開口部120a、第3の開口部120b、及び第1の画素電極層118の周囲を覆うように隔壁119を形成する(図7(B)参照)。

【0116】

以上により、保護絶縁層114に設ける開口部の開口と半導体膜108の不要な領域の除去を同時に行うことでフォトリソグラフィ工程を削減した発光表示装置の作製方法を提供することができる。

【0117】

なお、本実施の形態は他の実施の形態と自由に組み合わせることができる。

【0118】

(実施の形態2)

本実施の形態では、実施の形態1と一部異なる工程例を図8を用いて説明する。なお、図8において、図4と同一の箇所には同じ符号を用い、同じ符号の詳細な説明はここでは省略する。

【0119】

まず、実施の形態1と同様に、絶縁表面を有する基板100上に導電膜を形成した後、第1のフォトリソグラフィ工程、及びエッチング工程によりゲート電極層142を形成する。

【0120】

基板100とゲート電極層との間には、下地膜となる絶縁膜を設けてもよく、本実施の形態では下地膜101を設ける。下地膜101は、基板100からの不純物元素(Naなど)の拡散を防止する機能があり、酸化シリコン、酸窒化シリコン、窒化シリコン、酸化ハフニウム、酸化アルミニウム、酸化ガリウム、酸化ガリウムアルミニウムから選ばれた膜で形成することができる。また、該下地膜は単層に限らず、上記の複数の膜の積層であっても良い。

【0121】

本実施の形態では、後に成膜する半導体膜の成膜温度が200℃以上450℃以下、半導体膜の成膜後の加熱処理の温度が200℃以上450℃以下であるため、ゲート電極層142の材料として、銅を下層とし、モリブデンを上層とする積層、または銅を下層とし、タングステンを上層とする積層を用いる。

【0122】

次いで、実施の形態1と同様に、ゲート電極層142上にゲート絶縁層106をCVD法やスパッタ法等を用いて形成する。ここまでの工程を経た断面図を図8(A)に示す。

【0123】

次いで、ゲート絶縁層106上に、1nm以上10nm以下の第1の酸化物半導体膜を形成する。本実施の形態では、酸化物半導体用ターゲット(In−Ga−Zn−O系酸化物半導体用ターゲット(In2O3:Ga2O3:ZnO=1:1:2[mol数比])を用いて、基板とターゲットの間との距離を170mm、基板温度250℃、圧力0.4Pa、直流(DC)電源0.5kW、酸素のみ、アルゴンのみ、又はアルゴン及び酸素雰囲気下で膜厚5nmの第1の酸化物半導体膜を成膜する。

【0124】

次いで、基板を配置する雰囲気を窒素、または乾燥空気とし、第1の加熱処理を行う。第1の加熱処理の温度は、200℃以上450℃以下とする。また、第1の加熱処理の加熱時間は1時間以上24時間以下とする。第1の加熱処理によって第1の結晶性酸化物半導体層148aを形成する(図8(B)参照)。

【0125】

次いで、第1の結晶性酸化物半導体層148a上に10nmよりも厚い第2の酸化物半導体膜を形成する。本実施の形態では、In−Ga−Zn−O系酸化物ターゲット(In2O3:Ga2O3:ZnO=1:1:2[mol数比])を用いて、基板と該ターゲットの間との距離を170mm、基板温度400℃、圧力0.4Pa、直流(DC)電源0.5kW、酸素のみ、アルゴンのみ、又はアルゴン及び酸素雰囲気下で膜厚25nmの第2の酸化物半導体膜を成膜する。

【0126】

次いで、基板を配置する雰囲気を窒素、または乾燥空気とし、第2の加熱処理を行う。第2の加熱処理の温度は、200℃以上450℃以下とする。また、第2の加熱処理の加熱時間は1時間以上24時間以下とする。第2の加熱処理によって第2の結晶性酸化物半導体層148bを形成する(図8(C)参照)。

【0127】

以降の工程は、実施の形態1に従って、第2の導電膜112や保護絶縁層114などを形成し、保護絶縁層114、第1の結晶性酸化物半導体層148a、及び第2の結晶性酸化物半導体層148bを同一のレジストマスクを用いてエッチングすることによって、フォトリソグラフィ工程を削減する。

【0128】

こうして、実施の形態1に従って図6(B)に示す第1のトランジスタ151、第2のトランジスタ152を含む構成を得ることができる。ただし、本実施の形態を用いた場合、これらのトランジスタのチャネル形成領域を含む半導体層は、第1の結晶性酸化物半導体層148a、及び第2の結晶性酸化物半導体層148bの積層となる。第1の結晶性酸化物半導体層148a、及び第2の結晶性酸化物半導体層148bは、C軸配向を有する結晶性酸化物半導体である。

【0129】

該結晶性酸化物半導体は、c軸配向し、かつab面、表面または界面の方向から見て三角形状または六角形状の原子配列を有し、c軸においては金属原子が層状または金属原子と酸素原子とが層状に配列しており、ab面においてはa軸またはb軸の向きが異なる(c軸を中心に回転した)結晶(CAAC:C Axis Aligned Crystalともいう。)を含む酸化物である。

【0130】

なお、CAACは、上記の第1の結晶性酸化物半導体層148a、及び第2の結晶性酸化物半導体層148bのような積層に限らず、単層でも形成することができる。

【0131】

なお、CAACを形成するには、下地となる層の表面の平坦性をCMP等で極力向上させ、平均粗さをシリコンの熱酸化膜と同等レベルまたはそれ以下とすることが好ましい。表面の平坦性の高い層上にCAACを形成することで、CAACを構成する結晶の結晶性及び連続性を高めることができる。

【0132】

また、成膜時においては、スパッタガス中の酸素比率を高めて成膜することが好ましい。例えば、スパッタガスにアルゴンと酸素を用いる場合は、酸素の流量比率を30%以上とすることでCAACを構成する結晶の結晶性を高めることができ、かつ膜中の酸素欠損への酸素の補填を行うことができる。また、150℃以上の高温で成膜することで、CAACを構成する結晶の結晶性を更に高めることができる。

【0133】

また、膜形成後の加熱処理においては、窒素雰囲気または減圧下で加熱処理した後、酸素雰囲気または窒素と酸素の混合雰囲気で加熱処理することによりCAAC中の酸素を過剰とし、効果的に酸素欠損を補填することができる。なお、該加熱処理の温度は、450℃程度であることが好ましい。

【0134】

CAACを含む酸化物とは、広義に、非単結晶であって、そのab面に垂直な方向から見て、三角形、六角形、正三角形または正六角形の原子配列を有し、かつc軸方向に垂直な方向から見て、金属原子が層状、または金属原子と酸素原子が層状に配列した相を含む酸化物をいう。

【0135】

CAACは単結晶ではないが、非晶質のみから形成されているものでもない。また、CAACは結晶化した部分(結晶部分)を含むが、1つの結晶部分と他の結晶部分の境界を明確に判別できないこともある。

【0136】

CAACに酸素が含まれる場合、酸素の一部は窒素で置換されてもよい。また、CAACを構成する個々の結晶部分のc軸は一定の方向(例えば、CAACを支持する基板面、CAACの表面などに垂直な方向)に揃っていてもよい。または、CAACを構成する個々の結晶部分のab面の法線は一定の方向(例えば、CAACを支持する基板面、CAACの表面などに垂直な方向)を向いていてもよい。

【0137】

CAACは、その組成などに応じて、導体であったり、半導体であったり、絶縁体であったりする。また、その組成などに応じて、可視光に対して透明であったり不透明であったりする。

【0138】

このようなCAACの例として、膜状に形成され、膜表面または支持する基板面に垂直な方向から観察すると三角形または六角形の原子配列が認められ、かつその膜断面を観察すると金属原子または金属原子および酸素原子(または窒素原子)の層状配列が認められる結晶を挙げることもできる。

【0139】

CAACに含まれる結晶構造の一例について図16乃至図18を用いて詳細に説明する。なお、特に断りがない限り、図16乃至図18は縦方向をc軸方向とし、c軸方向と直交する面をab面とする。なお、単に上半分、下半分という場合、ab面を境にした場合の上半分、下半分をいう。

【0140】

図16(A)に、1個の6配位のInと、Inに近接の6個の4配位の酸素原子(以下4配位のO)と、を有する構造を示す。ここでは、金属原子が1個に対して、近接の酸素原子のみ示した構造を小グループと呼ぶ。図16(A)の構造は、八面体構造をとるが、簡単のため平面構造で示している。なお、図16(A)の上半分および下半分にはそれぞれ3個ずつ4配位のOがある。図16(A)に示す小グループは電荷が0である。

【0141】

図16(B)に、1個の5配位のGaと、Gaに近接の3個の3配位の酸素原子(以下3配位のO)と、Gaに近接の2個の4配位のOと、を有する構造を示す。3配位のOは、いずれもab面に存在する。図16(B)の上半分および下半分にはそれぞれ1個ずつ4配位のOがある。また、Inも5配位をとるため、図16(B)に示す構造をとりうる。図16(B)に示す小グループは電荷が0である。

【0142】

図16(C)に、1個の4配位のZnと、Znに近接の4個の4配位のOと、を有する構造を示す。図16(C)の上半分には1個の4配位のOがあり、下半分には3個の4配位のOがある。または、図16(C)の上半分に3個の4配位のOがあり、下半分に1個の4配位のOがあってもよい。図16(C)に示す小グループは電荷が0である。

【0143】

図16(D)に、1個の6配位のSnと、Snに近接の6個の4配位のOと、を有する構造を示す。図16(D)の上半分には3個の4配位のOがあり、下半分には3個の4配位のOがある。図16(D)に示す小グループは電荷が+1となる。

【0144】

図16(E)に、2個のZnを含む小グループを示す。図16(E)の上半分には1個の4配位のOがあり、下半分には1個の4配位のOがある。図16(E)に示す小グループは電荷が−1となる。

【0145】

ここでは、複数の小グループの集合体を中グループと呼び、複数の中グループの集合体を大グループ(ユニットセルともいう。)と呼ぶ。

【0146】

ここで、これらの小グループ同士が結合する規則について説明する。図16(A)に示す6配位のInの上半分の3個のOは下方向にそれぞれ3個の近接Inを有し、下半分の3個のOは上方向にそれぞれ3個の近接Inを有する。5配位のGaの上半分の1個のOは下方向に1個の近接Gaを有し、下半分の1個のOは上方向に1個の近接Gaを有する。4配位のZnの上半分の1個のOは下方向に1個の近接Znを有し、下半分の3個のOは上方向に3個の近接Znを有する。この様に、金属原子の上方向の4配位のOの数と、そのOの下方向にある近接金属原子の数は等しく、同様に金属原子の下方向の4配位のOの数と、そのOの上方向にある近接金属原子の数は等しい。Oは4配位なので、下方向にある近接金属原子の数と、上方向にある近接金属原子の数の和は4になる。従って、金属原子の上方向にある4配位のOの数と、別の金属原子の下方向にある4配位のOの数との和が4個のとき、金属原子を有する二種の小グループ同士は結合することができる。例えば、6配位の金属原子(InまたはSn)が下半分の4配位のOを介して結合する場合、4配位のOが3個であるため、5配位の金属原子(GaまたはIn)または4配位の金属原子(Zn)のいずれかと結合することになる。

【0147】

これらの配位数を有する金属原子は、c軸方向において、4配位のOを介して結合する。また、このほかにも、層構造の合計の電荷が0となるように複数の小グループが結合して中グループを構成する。

【0148】

図17(A)に、In−Sn−Zn−O系の層構造を構成する中グループのモデル図を示す。図17(B)に、3つの中グループで構成される大グループを示す。なお、図17(C)は、図17(B)の層構造をc軸方向から観察した場合の原子配列を示す。

【0149】

図17(A)においては、簡単のため、3配位のOは省略し、4配位のOは個数のみ示し、例えば、Snの上半分および下半分にはそれぞれ3個ずつ4配位のOがあることを丸枠の3として示している。同様に、図17(A)において、Inの上半分および下半分にはそれぞれ1個ずつ4配位のOがあり、丸枠の1として示している。また、同様に、図17(A)において、下半分には1個の4配位のOがあり、上半分には3個の4配位のOがあるZnと、上半分には1個の4配位のOがあり、下半分には3個の4配位のOがあるZnとを示している。

【0150】

図17(A)において、In−Sn−Zn−O系の層構造を構成する中グループは、上から順に4配位のOが3個ずつ上半分および下半分にあるSnが、4配位のOが1個ずつ上半分および下半分にあるInと結合し、そのInが、上半分に3個の4配位のOがあるZnと結合し、そのZnの下半分の1個の4配位のOを介して4配位のOが3個ずつ上半分および下半分にあるInと結合し、そのInが、上半分に1個の4配位のOがあるZn2個からなる小グループと結合し、この小グループの下半分の1個の4配位のOを介して4配位のOが3個ずつ上半分および下半分にあるSnと結合している構成である。この中グループが複数結合して大グループを構成する。

【0151】

ここで、3配位のOおよび4配位のOの場合、結合1本当たりの電荷はそれぞれ−0.667、−0.5と考えることができる。例えば、In(6配位または5配位)、Zn(4配位)、Sn(5配位または6配位)の電荷は、それぞれ+3、+2、+4である。従って、Snを含む小グループは電荷が+1となる。そのため、Snを含む層構造を形成するためには、電荷+1を打ち消す電荷−1が必要となる。電荷−1をとる構造として、図16(E)に示すように、2個のZnを含む小グループが挙げられる。例えば、Snを含む小グループが1個に対し、2個のZnを含む小グループが1個あれば、電荷が打ち消されるため、層構造の合計の電荷を0とすることができる。

【0152】

具体的には、図17(B)に示した大グループが繰り返されることで、In−Sn−Zn−O系の結晶(In2SnZn3O8)を得ることができる。なお、得られるIn−Sn−Zn−O系の層構造は、In2SnZn2O7(ZnO)m(mは0または自然数。)とする組成式で表すことができる。

【0153】

また、このほかにも、四元系金属の酸化物であるIn−Sn−Ga−Zn−O系酸化物や、三元系金属の酸化物であるIn−Ga−Zn−O系酸化物(IGZOとも表記する。)、In−Al−Zn−O系酸化物、Sn−Ga−Zn−O系酸化物、Al−Ga−Zn−O系酸化物、Sn−Al−Zn−O系酸化物や、In−Hf−Zn−O系酸化物、In−La−Zn−O系酸化物、In−Ce−Zn−O系酸化物、In−Pr−Zn−O系酸化物、In−Nd−Zn−O系酸化物、In−Sm−Zn−O系酸化物、In−Eu−Zn−O系酸化物、In−Gd−Zn−O系酸化物、In−Tb−Zn−O系酸化物、In−Dy−Zn−O系酸化物、In−Ho−Zn−O系酸化物、In−Er−Zn−O系酸化物、In−Tm−Zn−O系酸化物、In−Yb−Zn−O系酸化物、In−Lu−Zn−O系酸化物や、二元系金属の酸化物であるIn−Zn−O系酸化物、Sn−Zn−O系酸化物、Al−Zn−O系酸化物、Zn−Mg−O系酸化物、Sn−Mg−O系酸化物、In−Mg−O系酸化物や、In−Ga−O系酸化物などを用いた場合も同様である。

【0154】

例えば、図18(A)に、In−Ga−Zn−O系の層構造を構成する中グループのモデル図を示す。

【0155】

図18(A)において、In−Ga−Zn−O系の層構造を構成する中グループは、上から順に4配位のOが3個ずつ上半分および下半分にあるInが、4配位のOが1個上半分にあるZnと結合し、そのZnの下半分の3個の4配位のOを介して、4配位のOが1個ずつ上半分および下半分にあるGaと結合し、そのGaの下半分の1個の4配位のOを介して、4配位のOが3個ずつ上半分および下半分にあるInと結合している構成である。この中グループが複数結合して大グループを構成する。

【0156】

図18(B)に3つの中グループで構成される大グループを示す。なお、図18(C)は、図18(B)の層構造をc軸方向から観察した場合の原子配列を示している。

【0157】

ここで、In(6配位または5配位)、Zn(4配位)、Ga(5配位)の電荷は、それぞれ+3、+2、+3であるため、In、ZnおよびGaのいずれかを含む小グループは、電荷が0となる。そのため、これらの小グループの組み合わせであれば中グループの合計の電荷は常に0となる。

【0158】

また、In−Ga−Zn−O系の層構造を構成する中グループは、図18(A)に示した中グループに限定されず、In、Ga、Znの配列が異なる中グループを組み合わせた大グループも取りうる。

【0159】

具体的には、図18(B)に示した大グループが繰り返されることで、In−Ga−Zn−O系の結晶を得ることができる。なお、得られるIn−Ga−Zn−O系の層構造は、InGaO3(ZnO)n(nは自然数。)とする組成式で表すことができる。

【0160】

n=1(InGaZnO4)の場合は、例えば、図19(A)に示す結晶構造を取りうる。なお、図19(A)に示す結晶構造において、図16(B)で説明したように、Ga及びInは5配位をとるため、GaがInに置き換わった構造も取りうる。

【0161】

また、n=2(InGaZn2O5)の場合は、例えば、図19(B)に示す結晶構造を取りうる。なお、図19(B)に示す結晶構造において、図16(B)で説明したように、Ga及びInは5配位をとるため、GaがInに置き換わった構造も取りうる。

【0162】

上述したようなCAACをトランジスタに用いることで、光照射及びバイアス−熱(BT)ストレス試験におけるトランジスタのしきい値電圧の変化を小さくすることができる。

【0163】

本実施の形態は、他の実施の形態と自由に組み合わせることができる。

【0164】

(実施の形態3)

本実施の形態では、本発明の一態様における発光表示装置の例を示す。表示装置の有する表示素子としては、ここではエレクトロルミネッセンスを利用する発光素子を用いて示す。エレクトロルミネッセンスを利用する発光素子は、発光材料が有機化合物であるか、無機化合物であるかによって区別され、一般的に、前者は有機EL素子、後者は無機EL素子と呼ばれている。

【0165】

有機EL素子は、発光素子に電圧を印加することにより、一対の電極から電子および正孔がそれぞれ発光性の有機化合物を含む層に注入され、電流が流れる。そして、それらキャリア(電子および正孔)が再結合することにより、発光性の有機化合物が励起状態を形成し、その励起状態が基底状態に戻る際に発光する。このようなメカニズムから、このような発光素子は、電流励起型の発光素子と呼ばれる。

【0166】

無機EL素子は、その素子構成により、分散型無機EL素子と薄膜型無機EL素子とに分類される。分散型無機EL素子は、発光材料の粒子をバインダ中に分散させた発光層を有するものであり、発光メカニズムはドナー準位とアクセプター準位を利用するドナー−アクセプター再結合型発光である。薄膜型無機EL素子は、発光層を誘電体層で挟み込み、さらにそれを電極で挟んだ構造であり、発光メカニズムは金属イオンの内殻電子遷移を利用する局在型発光である。なお、ここでは、発光素子として有機EL素子を用いて説明する。

【0167】

本実施の形態で説明する発光表示装置は、実施の形態1で説明した画素部の構成を有するものであり、基板100、第1のトランジスタ151、第2のトランジスタ152、保護絶縁層114、平坦化絶縁層116、隔壁119、及び発光素子に用いる第1の画素電極層118を有する(図1(A)、(B)参照)。また、第1の画素電極層118上にはEL層、第2の画素電極層を有する。

【0168】

本実施の形態では画素の第1のトランジスタ151、第2のトランジスタ152がnチャネル型であるので、第1の画素電極層118として、陰極を用いるのが望ましい。具体的には、陰極としては、仕事関数が小さい材料、例えば、Ca、Al、CaF、MgAg、AlLi等を用いることができる。

【0169】

隔壁119は、有機樹脂膜、無機絶縁膜または有機ポリシロキサンを用いて形成する。特に感光性の材料を用い、第1の画素電極層118上に開口部を形成し、その開口部の側壁が連続した曲率を持って形成される傾斜面となるように形成することが好ましい。

【0170】

なお、EL層は、単数の層で構成されていても、複数の層が積層されるように構成されていてもどちらでも良い。

【0171】

陽極となる第2の画素電極層は、EL層を覆うように形成する。第2の画素電極層には、酸化タングステンを含むインジウム酸化物、酸化タングステンを含むインジウム亜鉛酸化物、酸化チタンを含むインジウム酸化物、酸化チタンを含むインジウム錫酸化物、インジウム錫酸化物(以下、ITOと示す。)、インジウム亜鉛酸化物、酸化ケイ素を添加したインジウム錫酸化物などの透光性を有する導電性材料を用いることができる。また、1枚乃至10枚のグラフェンシート(グラファイトの1層分)よりなる材料を用いてもよい。また、上記透光性導電膜の他に、窒化チタン膜またはチタン膜を用いても良い。第1の画素電極層118とEL層と第2の画素電極層とが重なり合うことで、発光素子が形成される。この後、発光素子に酸素、水素、水分、二酸化炭素等が侵入しないように、第2の電極層及び隔壁119上に保護膜を形成してもよい。保護膜としては、窒化珪素膜、窒化酸化珪素膜、DLC膜等を形成することができる。

【0172】

さらに外気に曝されないように気密性が高く、脱ガスの少ない保護フィルム(貼り合わせフィルム、紫外線硬化樹脂フィルム等)やカバー材でパッケージング(封入)することが好ましい。

【0173】

次に、発光素子の構成について、図9(A)、(B)、(C)を用いて説明する。なお、図9(A)、(B)、(C)は、図1(A)のA2−A3の断面の構成にEL層及び第2の画素電極層等を加えて図示したものである。

【0174】

発光素子は発光を取り出すために少なくとも陽極又は陰極の一方が透明であればよい。そして、基板上にトランジスタ及び発光素子を形成し、基板とは逆側の面から発光を取り出す上面射出や、基板側の面から発光を取り出す下面射出や、基板側及び基板とは反対側の面から発光を取り出す両面射出構造の発光素子があり、本発明の一態様に係る画素構成はどの射出構造の発光素子にも適用することができる。

【0175】

上面射出構造の発光素子について図9(A)を用いて説明する。

【0176】

図9(A)に、第2のトランジスタ152がnチャネル型で、発光素子7002から発せられる光が陽極7005側に抜ける場合の、画素の断面図を示す。図9(A)では、発光素子7002の陰極7003と第2のトランジスタ152が電気的に接続されており、陰極7003上に発光層7004、陽極7005が順に積層されている。陰極7003は仕事関数が小さく、なおかつ光を反射する導電膜であれば様々の材料を用いることができる。例えば、Ca、Al、MgAg、AlLi等が望ましい。そして発光層7004は、単数の層で構成されていても、複数の層が積層されるように構成されていてもどちらでも良い。複数の層で構成されている場合、陰極7003上に電子注入層、電子輸送層、発光層、ホール輸送層、ホール注入層の順に積層する。なおこれらの層を全て設ける必要はない。陽極7005は透光性を有する導電性材料を用いて形成し、例えば酸化タングステンを含むインジウム酸化物、酸化タングステンを含むインジウム亜鉛酸化物、酸化チタンを含むインジウム酸化物、酸化チタンを含むインジウム錫酸化物、インジウム錫酸化物(以下、ITOと示す。)、インジウム亜鉛酸化物、酸化ケイ素を添加したインジウム錫酸化物などの透光性を有する導電膜を用いても良い。また、1枚乃至10枚のグラフェンシート(グラファイトの1層分)よりなる材料を用いてもよい。

【0177】

陰極7003及び陽極7005で発光層7004を挟んでいる領域が発光素子7002に相当する。図9(A)に示した画素の場合、発光素子7002から発せられる光は、矢印で示すように陽極7005側に射出する。

【0178】

次に、下面射出構造の発光素子について図9(B)を用いて説明する。図9(B)に、第2のトランジスタ152がnチャネル型で、発光素子7012から発せられる光が陰極7013側に射出する場合の、画素の断面図を示す。図9(B)では、第2のトランジスタ152と電気的に接続された透光性を有する導電膜7017上に、発光素子7012の陰極7013が成膜されており、陰極7013上に発光層7014、陽極7015が順に積層されている。なお、陽極7015が透光性を有する場合、陽極上を覆うように、光を反射または遮蔽するための遮蔽膜7016が成膜されていてもよい。陰極7013は、図9(A)の場合と同様に、仕事関数が小さい導電性材料であれば様々な材料を用いることができる。ただしその膜厚は、光を透過する程度(好ましくは、5nm以上30nm以下)とする。例えば20nmの膜厚を有するアルミニウム膜を、陰極7013として用いることができる。そして発光層7014は、図9(A)と同様に、単数の層で構成されていても、複数の層が積層されるように構成されていてもどちらでも良い。陽極7015は光を透過する必要はないが、図9(A)と同様に、透光性を有する導電性材料を用いて形成することができる。そして遮蔽膜7016は、例えば光を反射する金属等を用いることができるが、金属膜に限定されない。例えば黒の顔料添加した樹脂等を用いることもできる。

【0179】

陰極7013及び陽極7015で、発光層7014を挟んでいる領域が発光素子7012に相当する。図9(B)に示した画素の場合、発光素子7012から発せられる光は、矢印で示すように陰極7013側に射出する。

【0180】

次に、両面射出構造の発光素子について、図9(C)を用いて説明する。図9(C)では、第2のトランジスタ152と電気的に接続された透光性を有する導電膜7027上に、発光素子7022の陰極7023が成膜されており、陰極7023上に発光層7024、陽極7025が順に積層されている。陰極7023は、図9(A)の場合と同様に、仕事関数が小さい導電性材料であれば様々な材料を用いることができる。ただしその膜厚は、光を透過する程度とする。例えば20nmの膜厚を有するアルミニウム膜を、陰極7023として用いることができる。そして発光層7024は、図9(A)と同様に、単数の層で構成されていても、複数の層が積層されるように構成されていてもどちらでも良い。陽極7025は、図9(A)と同様に、透光性を有する導電性材料を用いて形成することができる。

【0181】

陰極7023と、発光層7024と、陽極7025とが重なっている部分が発光素子7022に相当する。図9(C)に示した画素の場合、発光素子7022から発せられる光は、矢印で示すように陽極7025側と陰極7023側の両方に射出する。

【0182】

なお、ここでは、発光素子として有機EL素子について述べたが、発光素子として無機EL素子を設けることも可能である。

【0183】

また、実施の形態1で説明した図14(A)、(B)に示す画素領域全面に半導体層108aを残す構成においても、発光素子の構成は図9と同様にすることができる。この場合の発光素子の構成を図15(A)、(B)、(C)に示す。図15(A)は図9(A)と同じ上面射出構造、図15(B)は図9(B)と同じ下面射出構造、図15(C)は図9(C)と同じ両面射出構造であり、それぞれの詳細は上述の図9(A)、(B)、(C)の説明と同じである。なお、図15(B)、(C)の構成における下面方向への光の透過は、半導体層108aに可視光に対して透光性を有する酸化物半導体層を用いることで実現することができる。

【0184】

なお本実施の形態で示す発光表示装置は、図9または図15に示した構成に限定されるものではなく、本発明の技術的思想に基づく各種の変形が可能である。

【0185】

本実施の形態は、他の実施の形態と自由に組み合わせることができる。

【0186】

(実施の形態4)

本発明の一態様に係る発光表示装置は、さまざまな電子機器(遊技機も含む)に適用することができる。電子機器としては、例えば、テレビジョン装置(テレビ、またはテレビジョン受信機ともいう)、コンピュータ用などのモニタ、デジタルカメラやデジタルビデオカメラ等のカメラ、デジタルフォトフレーム、携帯電話機(携帯電話、携帯電話装置ともいう)、携帯型ゲーム機、携帯情報端末、音響再生装置、パチンコ機などの大型ゲーム機などが挙げられる。

【0187】

図10(A)は、テレビジョン装置の一例を示している。テレビジョン装置9600は、筐体9601に表示部9603が組み込まれている。表示部9603により、映像を表示することが可能である。また、ここでは、スタンド9605により筐体9601を支持した構成を示している。

【0188】

テレビジョン装置9600の操作は、筐体9601が備える操作スイッチや、別体のリモートコントローラ9610により行うことができる。リモートコントローラ9610が備える操作キー9609により、チャンネルや音量の操作を行うことができ、表示部9603に表示される映像を操作することができる。また、リモートコントローラ9610に、当該リモートコントローラから出力する情報を表示する表示部9607を設ける構成としてもよい。

【0189】

なお、テレビジョン装置9600は、受信機やモデムなどを備えた構成とする。受信機により一般のテレビ放送の受信を行うことができ、さらにモデムを介して有線または無線による通信ネットワークに接続することにより、一方向(送信者から受信者)または双方向(送信者と受信者間、あるいは受信者間同士など)の情報通信を行うことも可能である。

【0190】

図10(B)は、デジタルフォトフレームの一例を示している。例えば、デジタルフォトフレーム9700は、筐体9701に表示部9703が組み込まれている。表示部9703は、各種画像を表示することが可能であり、例えばデジタルカメラなどで撮影した画像データを表示させることで、通常の写真立てと同様に機能させることができる。

【0191】

なお、デジタルフォトフレーム9700は、操作部、外部接続用端子(USB端子、USBケーブルなどの各種ケーブルと接続可能な端子など)、記録媒体挿入部などを備える構成とする。これらの構成は、表示部と同一面に組み込まれていてもよいが、側面や裏面に備えるとデザイン性が向上するため好ましい。例えば、デジタルフォトフレームの記録媒体挿入部に、デジタルカメラで撮影した画像データを記憶したメモリを挿入して画像データを取り込み、取り込んだ画像データを表示部9703に表示させることができる。

【0192】

また、デジタルフォトフレーム9700は、無線で情報を送受信出来る構成としてもよい。無線により、所望の画像データを取り込み、表示させる構成とすることもできる。

【0193】

図11(A)は携帯型遊技機であり、筐体9881と筐体9891の2つの筐体で構成されており、連結部9893により、開閉可能に連結されている。筐体9881には表示部9882が組み込まれ、筐体9891には表示部9883が組み込まれている。また、図11(A)に示す携帯型遊技機は、その他、スピーカ部9884、記録媒体挿入部9886、LEDランプ9890、入力手段(操作キー9885、接続端子9887、センサ9888(力、変位、位置、速度、加速度、角速度、回転数、距離、光、液、磁気、温度、化学物質、音声、時間、硬度、電場、電流、電圧、電力、放射線、流量、湿度、傾度、振動、におい又は赤外線を測定する機能を含むもの)、マイクロフォン9889)等を備えている。もちろん、携帯型遊技機の構成は上述のものに限定されず、その他付属設備が適宜設けられた構成とすることができる。図11(A)に示す携帯型遊技機は、記録媒体に記録されているプログラム又はデータを読み出して表示部に表示する機能や、他の携帯型遊技機と無線通信を行って情報を共有する機能を有する。なお、図11(A)に示す携帯型遊技機が有する機能はこれに限定されず、様々な機能を有することができる。

【0194】

図11(B)は大型遊技機であるスロットマシンの一例を示している。スロットマシン9900は、筐体9901に表示部9903が組み込まれている。また、スロットマシン9900は、その他、スタートレバーやストップスイッチなどの操作手段、コイン投入口、スピーカなどを備えている。もちろん、スロットマシン9900の構成は上述のものに限定されず、その他付属設備が適宜設けられた構成とすることができる。

【0195】

図12(A)は、携帯電話機の一例を示している。携帯電話機1000は、筐体1001に組み込まれた表示部1002の他、操作ボタン1003、外部接続ポート1004、スピーカ1005、マイクロフォン1006などを備えている。

【0196】

図12(A)に示す携帯電話機1000は、表示部1002を指などで触れることで、情報を入力することができる。また、電話を掛ける、或いはメールを送信するなどの操作は、表示部1002を指などで触れることにより行うことができる。

【0197】

表示部1002の画面は主として3つのモードがある。第1は、画像の表示を主とする表示モードであり、第2は、文字等の情報の入力を主とする入力モードである。第3は表示モードと入力モードの2つのモードが混合した表示+入力モードである。

【0198】

例えば、電話を掛ける、或いはメールを作成する場合は、表示部1002を文字の入力を主とする文字入力モードとし、画面に表示させた文字の入力操作を行えばよい。この場合、表示部1002の画面のほとんどにキーボードまたは番号ボタンを表示させることが好ましい。

【0199】

また、携帯電話機1000内部に、ジャイロ、加速度センサ等の傾きを検出するセンサを有する検出装置を設けることで、携帯電話機1000の向き(縦か横か)を判断して、表示部1002の画面表示を自動的に切り替えるようにすることができる。

【0200】

また、画面モードの切り替えは、表示部1002を触れること、又は筐体1001の操作ボタン1003の操作により行われる。また、表示部1002に表示される画像の種類によって切り替えるようにすることもできる。例えば、表示部に表示する画像信号が動画のデータであれば表示モード、テキストデータであれば入力モードに切り替える。

【0201】

また、入力モードにおいて、表示部1002の光センサで検出される信号を検知し、表示部1002のタッチ操作による入力が一定期間ない場合には、画面のモードを入力モードから表示モードに切り替えるように制御してもよい。

【0202】

表示部1002は、イメージセンサとして機能させることもできる。例えば、表示部1002に掌や指を触れることで、掌紋、指紋等を撮像することで、本人認証を行うことができる。また、表示部に近赤外光を発光するバックライトまたは近赤外光を発光するセンシング用光源を用いれば、指静脈、掌静脈などを撮像することもできる。

【0203】

図12(B)は、電子書籍の一例を示している。例えば、電子書籍2700は、筐体2701および筐体2703の2つの筐体で構成されている。筐体2701および筐体2703は、軸部2711により結合されており、該軸部2711を軸として開閉動作を行うことができる。このような構成により、紙の書籍のような動作を行うことが可能となる。

【0204】

筐体2701には表示部2705が組み込まれ、筐体2703には表示部2707が組み込まれている。表示部2705および表示部2707は、続き画面を表示する構成としてもよいし、異なる画面を表示する構成としてもよい。異なる画面を表示する構成とすることで、例えば右側の表示部(図12(B)では表示部2705)に文章を表示し、左側の表示部(図12(B)では表示部2707)に画像を表示することができる。

【0205】

また、図12(B)では、筐体2701に操作部などを備えた例を示している。例えば、筐体2701において、電源スイッチ2721、操作キー2723、スピーカ2725などを備えている。操作キー2723により、頁を送ることができる。なお、筐体の表示部と同一面にキーボードやポインティングディバイスなどを備える構成としてもよい。また、筐体の裏面や側面に、外部接続用端子(イヤホン端子、USB端子、またはACアダプタおよびUSBケーブルなどの各種ケーブルと接続可能な端子など)、記録媒体挿入部などを備える構成としてもよい。さらに、電子書籍2700は、電子辞書としての機能を持たせた構成としてもよい。

【0206】

また、電子書籍2700は、無線で情報を送受信できる構成としてもよい。無線により、電子書籍サーバから、所望の書籍データなどを購入し、ダウンロードする構成とすることも可能である。

【0207】

本実施の形態は、他の実施の形態と自由に組み合わせることができる。

【0208】

(実施の形態5)

本実施の形態では、左目用の映像と右目の映像を高速で切り換える発光表示装置を用いて、表示装置の映像と同期する専用の眼鏡を用いて動画または静止画である3D映像を視認する例を図13を用いて示す。

【0209】

図13(A)は発光表示装置3711と、専用の眼鏡本体3701がケーブル3703で接続されている外観図を示す。専用の眼鏡本体3701は、左目用パネル3702aと右目用パネル3702bに設けられているシャッターが交互に開閉することによって使用者が発光表示装置3711の画像を3Dとして認識することができる。

【0210】

また、発光表示装置3711と専用の眼鏡本体3701の主要な構成についてのブロック図を図13(B)に示す。

【0211】

図13(B)に示す発光表示装置3711は、表示制御回路3716、表示部3717、タイミング発生器3713、ソース線側駆動回路3718、外部操作手段3722及びゲート線側駆動回路3719を有する。なお、キーボード等の外部操作手段3722による操作に応じて、出力する信号を可変する。

【0212】

タイミング発生器3713では、スタートパルス信号などを形成するとともに、左目用映像と左目用パネル3702aのシャッターとを同期させるための信号、右目用映像と右目用パネル3702bのシャッターとを同期させるための信号などを形成する。

【0213】

左目用映像の同期信号3731aを表示制御回路3716に入力して表示部3717に表示すると同時に、左目用パネル3702aのシャッターを開ける同期信号3730aを左目用パネル3702aに入力する。また、右目用映像の同期信号3731bを表示制御回路3716に入力して表示部3717に表示すると同時に、右目用パネル3702bのシャッターを開ける同期信号3730bを右目用パネル3702bに入力する。

【0214】

また、左目用の映像と右目の映像を高速で切り換えるため、発光表示装置3711は、例えば120Hzや、240Hzのフレーム周波数で駆動する表示パネルを用いることが好ましい。120Hzや、240Hzのフレーム周波数で高速駆動させるため、応答速度の速い有機EL素子を用いた発光表示パネルは、3D映像を視認する表示装置として適している。また、120Hzや、240Hzのフレーム周波数で高速駆動させるため、スイッチング素子は、アモルファスシリコンを用いたトランジスタよりも移動度の高い酸化物半導体材料を活性層に用いたトランジスタが適している。

【0215】

本実施の形態は、他の実施の形態と自由に組み合わせることができる。

【符号の説明】

【0216】

100 基板

101 下地膜

102a 第1のゲート電極層

102b 第2のゲート電極層

102c 第2のゲート電極層

106 ゲート絶縁層

108 半導体膜

108a 半導体層

110a 第1の開口部

110b 第1の開口部

112 第2の導電膜

112a ソース電極層及びドレイン電極層

112b ソース電極層及びドレイン電極層

112c ソース電極層及びドレイン電極層

112d ソース電極層及びドレイン電極層

112e 導電層

114 保護絶縁層

116 平坦化絶縁層

118 画素電極層

119 隔壁

120a 第2の開口部

120b 第3の開口部

130a 第2の開口部

130b 第3の開口部

142 ゲート電極層

148a 結晶性酸化物半導体層

148b 結晶性酸化物半導体層

151 第1のトランジスタ

152 第2のトランジスタ

153 容量素子

160 EL層

170 第2の画素電極層(共通電極)

250 トランジスタ部

260 容量素子部

270 配線交差部

280 FPC接続部

1000 携帯電話機

1001 筐体

1002 表示部

1003 操作ボタン

1004 外部接続ポート

1005 スピーカ

1006 マイクロフォン

2700 電子書籍

2701 筐体

2703 筐体

2705 表示部

2707 表示部

2711 軸部

2721 電源スイッチ

2723 操作キー

2725 スピーカ

3701 眼鏡本体

3703 ケーブル

3702a 左目用パネル

3702b 右目用パネル

3711 発光表示装置

3713 タイミング発生器

3716 表示制御回路

3717 表示部

3718 ソース線側駆動回路

3719 ゲート線側駆動回路

3722 外部操作手段

3730a 同期信号

3730b 同期信号

3731a 同期信号

3731b 同期信号

7002 発光素子

7003 陰極

7004 発光層

7005 陽極

7012 発光素子

7013 陰極

7014 発光層

7015 陽極

7016 遮蔽膜

7017 導電膜

7022 発光素子

7023 陰極

7024 発光層

7025 陽極

7027 導電膜

9600 テレビジョン装置

9601 筐体

9603 表示部

9605 スタンド

9607 表示部

9609 操作キー

9610 リモートコントローラ

9700 デジタルフォトフレーム

9701 筐体

9703 表示部

9881 筐体

9882 表示部

9883 表示部

9884 スピーカ部

9885 操作キー

9886 記録媒体挿入部

9887 接続端子

9888 センサ

9889 マイクロフォン

9890 LEDランプ

9891 筐体

9893 連結部

9900 スロットマシン

9901 筐体

9903 表示部

【技術分野】

【0001】

本発明は、トランジスタを有する発光表示装置の作製方法に関する。

【背景技術】

【0002】

近年、ガラス基板等の絶縁性表面を有する基板上に形成された、厚さ数nm〜数百nm程度の半導体薄膜により構成される薄膜トランジスタが注目されている。薄膜トランジスタは、IC(Integrated Circuit)及び電気光学装置を始めとした電子デバイスに広く応用されている。薄膜トランジスタは、特にEL(Electro Luminescence)表示装置等に代表される、画像表示装置のスイッチング素子として開発が急がれている。

【0003】

アクティブマトリクス型EL表示装置では、選択された画素内に設けられた発光素子の一方の電極と、該電極とともにEL層(発光層を含む)を挟持する他方の電極の間に電圧が印加されることにより、EL層に電流が生じ、発光層が発光する。この発光が表示パターンとして観察者に認識される。ここで、アクティブマトリクス型EL表示装置とは、マトリクス状に配置された画素をスイッチング素子により駆動することによって、画面上に表示パターンが形成される方式を採用したEL表示装置をいう。

【0004】

上記のようなアクティブマトリクス型EL表示装置の用途は拡大しており、画面サイズの大面積化、高精細化及び高開口率化の要求が高まっている。また、アクティブマトリクス型表示装置には高い信頼性が求められ、その生産方法には高い生産性及び生産コストの低減が求められる。生産性を高め、生産コストを低減する方法の一つに、工程の簡略化が挙げられる。

【0005】

アクティブマトリクス型表示装置では、スイッチング素子として主に薄膜トランジスタが用いられている。薄膜トランジスタの作製において、フォトリソグラフィ工程を削減または簡略化することは、工程全体の簡略化のために重要である。例えばフォトリソグラフィ工程が1つ増加すると、レジスト塗布、プリベーク、露光、現像、ポストベーク等の工程と、その前後の工程において、被膜の形成及びエッチング工程、更にはレジスト剥離、洗浄及び乾燥工程等が必要になる。そのため、作製工程におけるフォトリソグラフィ工程が1つ増加するだけで、それに関する工程数が大幅に増加する。そのため、作製工程におけるフォトリソグラフィ工程を削減または簡略化するために、数多くの技術開発がなされている。

【0006】

薄膜トランジスタは、チャネル形成領域がゲート電極より下層に設けられるトップゲート型と、チャネル形成領域がゲート電極より上層に設けられるボトムゲート型に大別される。これらの薄膜トランジスタは、少なくとも5枚のフォトマスクにより作製されることが一般的である。

【0007】

フォトリソグラフィ工程を簡略化させる従来の技術としては、裏面露光、レジストリフロー又はリフトオフ法といった複雑な技術を用いるものが多く、特殊な装置を必要とするものが多い。このような複雑な技術を用いることで、これに起因する様々な問題が生じ、歩留まりの低下の一因となっている。また、薄膜トランジスタの電気的特性を犠牲にせざるを得ないことも多い。

【0008】

また、薄膜トランジスタの作製工程における、フォトリソグラフィ工程を簡略化するための代表的な手段として、多階調マスク(ハーフトーンマスク又はグレートーンマスクと呼ばれるもの)を用いた技術が広く知られている。多階調マスクを用いて作製工程を低減する技術として、例えば特許文献1が挙げられる。

【先行技術文献】

【特許文献】

【0009】

【特許文献1】特開2003−179069号公報

【発明の概要】

【発明が解決しようとする課題】

【0010】

多階調マスクを用いる場合は、マスク数を減らすことはできるが、レジストマスクを新たな形状とするにはアッシングなどの新たな工程が必要である。

【0011】

本発明の一態様は、フォトマスクの枚数を従来よりも少なくするだけでなく、新たな工程を増やすことなく発光表示装置を作製することを目的とする。

【課題を解決するための手段】

【0012】

本明細書で開示する本発明の一態様は、トランジスタを構成する半導体層に高抵抗の酸化物半導体を使用することによって、個々のトランジスタに対して半導体層を島状に加工する工程を省き、フォトリソグラフィ工程を削減する発光表示装置の作製方法に関する。

【0013】

本明細書で開示する本発明の一態様は、基板上に第1の導電膜を形成し、第1の導電膜上に第1のレジストマスクを形成し、第1のレジストマスクを用いて第1の導電膜を選択的にエッチングして、第1のゲート電極と第2のゲート電極を形成し、第1のゲート電極及び第2のゲート電極上にゲート絶縁層となる第1の絶縁膜を形成し、ゲート絶縁層上に半導体膜を形成し、半導体膜上に第2のレジストマスクを形成し、第2のレジストマスクを用いて第2のゲート電極上の半導体膜及び第1の絶縁膜の一部を選択的にエッチングして、第1の開口部を形成し、半導体膜及び第1の開口部を覆うように第2の導電膜を形成し、第2の導電膜上に第3のレジストマスクを形成し、第3のレジストマスクを用いて第2の導電膜を選択的にエッチングして、ソースドレイン配線と電気的に接続される第1のソース電極及びドレイン電極の一方と、第2のゲート電極と電気的に接続される第1のソース電極及びドレイン電極の他方と、電源配線に接続される第2のソース電極及びドレイン電極の一方と、第2のソース電極及びドレイン電極の他方を形成することによって、第1のゲート電極、第1のソース電極及びドレイン電極を有する第1のトランジスタ、及び第2のゲート電極、第2のソース電極及びドレイン電極を有する第2のトランジスタを形成し、第1のソース電極及びドレイン電極、第2のソース電極及びドレイン電極、及び半導体膜上に保護絶縁膜となる第2の絶縁膜を形成し、第2の絶縁膜上に第4のレジストマスクを形成し、第4のレジストマスクを用いて第2の絶縁膜及び半導体膜を選択的にエッチングして第2の開口部を形成すると同時に、第2のソース電極及びドレイン電極の他方の一部が露出するように第2の絶縁膜に第3の開口部を形成し、第3の開口部を覆うように第2の絶縁膜上に第3の導電膜を形成し、第3の導電膜上に第5のレジストマスクを形成し、第5のレジストマスクを用いて第3の導電膜を選択的にエッチングして第1の画素電極を形成し、第2の開口部、第3の開口部、及び画素電極の周囲を覆うように第3の絶縁膜を形成し、画素電極上に有機化合物を含む層を選択的に形成し、有機化合物を含む層上に第2の画素電極を形成することを特徴とする発光表示装置の作製方法である。

【0014】

なお、本明細書等における「第1」、「第2」、「第3」などの序数詞は、構成要素の混同を避けるために付すものであり、数的に限定するものではないことを付記する。

【0015】

また、本明細書で開示する本発明の他の一態様は、基板上に第1の導電膜を形成し、第1の導電膜上に第1のレジストマスクを形成し、第1のレジストマスクを用いて第1の導電膜を選択的にエッチングして、第1のゲート電極と第2のゲート電極を形成し、第1のゲート電極及び第2のゲート電極上にゲート絶縁層となる第1の絶縁膜を形成し、ゲート絶縁層上に半導体膜を形成し、半導体膜上に第2のレジストマスクを形成し、第2のレジストマスクを用いて第2のゲート電極上の半導体膜及び第1の絶縁膜の一部を選択的にエッチングして、第1の開口部を形成し、半導体膜及び第1の開口部を覆うように第2の導電膜を形成し、第2の導電膜上に第3のレジストマスクを形成し、第3のレジストマスクを用いて第2の導電膜を選択的にエッチングして、ソースドレイン配線と電気的に接続される第1のソース電極及びドレイン電極の一方と、第2のゲート電極と電気的に接続される第1のソース電極及びドレイン電極の他方と、電源配線に接続される第2のソース電極及びドレイン電極の一方と、第2のソース電極及びドレイン電極の他方を形成することによって、第1のゲート電極、第1のソース電極及びドレイン電極を有する第1のトランジスタ、及び第2のゲート電極、第2のソース電極及びドレイン電極を有する第2のトランジスタを形成し、第1のソース電極及びドレイン電極、第2のソース電極及びドレイン電極、及び半導体膜上に保護絶縁膜となる第2の絶縁膜を形成し、第2の絶縁膜上に平坦化絶縁膜として第3の絶縁膜を形成し、第3の絶縁膜上に第4のレジストマスクを形成し、第4のレジストマスクを用いて第3の絶縁膜、第2の絶縁膜及び半導体膜を選択的にエッチングして、第2の開口部を形成すると同時に、第2のソース電極及びドレイン電極の他方の一部が露出するように第2の絶縁膜に第3の開口部を形成し、第3の開口部を覆うように第3の絶縁膜上に第3の導電膜を形成し、第3の導電膜上に第5のレジストマスクを形成し、第5のレジストマスクを用いて第3の導電膜を選択的にエッチングして第1の画素電極を形成し、第2の開口部、第3の開口部、及び画素電極の周囲を覆うように第4の絶縁膜を形成し、画素電極上に有機化合物を含む層を選択的に形成し、有機化合物を含む層上に第2の画素電極を形成することを特徴とする発光表示装置の作製方法である。

【0016】

上記半導体膜には酸化物半導体を用いることが好ましい。i型化または実質的にi型化された酸化物半導体は、極めて抵抗が高く、回路を構成する上では絶縁体とみなすことができる。従って、同一島状の半導体層に複数のトランジスタが構成されていても互いに干渉することはなく、各トランジスタを動作させることができる。

【発明の効果】

【0017】

酸化物半導体は絶縁体とみなすことができるため、トランジスタ毎に島状の半導体層を形成する工程を省くことができ、フォトリソグラフィ工程を削減する発光表示装置の作製方法を提供することができる。

【図面の簡単な説明】

【0018】

【図1】発光表示装置の一態様を説明する平面図及び断面図。

【図2】容量素子を有さない発光表示装置の平面図。

【図3】発光表示装置の画素部の等価回路図。

【図4】発光表示装置の作製方法の一態様を説明する断面図。

【図5】発光表示装置の作製方法の一態様を説明する断面図。

【図6】発光表示装置の作製方法の一態様を説明する断面図。

【図7】発光表示装置の作製方法の一態様を説明する断面図。

【図8】発光表示装置の作製方法の一態様を説明する断面図。

【図9】発光素子の構成を説明する断面図。

【図10】電子機器を示す図。

【図11】電子機器を示す図。

【図12】電子機器を示す図。

【図13】表示装置の映像と同期する専用の眼鏡を用いて動画または静止画である3D映像を視認する装置の一例を説明する図。

【図14】発光表示装置の一態様を説明する平面図及び断面図。

【図15】発光素子の構成を説明する断面図。

【図16】酸化物材料の構造を説明する図。

【図17】酸化物材料の構造を説明する図。

【図18】酸化物材料の構造を説明する図。

【図19】酸化物材料の構造を説明する図。

【発明を実施するための形態】

【0019】

以下では、本発明の実施の形態について図面を用いて詳細に説明する。ただし、本発明は以下の説明に限定されず、その形態及び詳細を様々に変更し得ることは、当業者であれば容易に理解される。また、本発明は以下に示す実施の形態の記載内容に限定して解釈されるものではない。なお、図面を用いて発明の構成を説明するにあたり、同じものを指す符号は異なる図面間でも共通して用いる。また、同様のものを指す際にはハッチパターンを同じくし、特に符号を付さない場合がある。

【0020】

(実施の形態1)

本実施の形態では、本発明の一態様における発光表示装置が有する画素部の構成の例を示す。

【0021】

図1(A)、(B)は、本発明の一態様を適用したアクティブマトリクス型の発光表示装置の画素部の一例である。図1(A)は発光表示装置の画素部の平面図であり、図1(B)は図1(A)における線A1−A2の断面図である。また、図3(A)は図1に示したアクティブマトリクス型発光表示装置の画素部の等価回路である。なお、図3(A)に示すEL層160及び第2の画素電極層(共通電極)170は、図1(A)、(B)には図示されていない。

【0022】

なお、本明細書において、EL層とは発光素子の一対の電極間に設けられた層を示すものとする。従って、電極間に挟まれた発光物質である有機化合物を含む層はEL層の一態様である。

【0023】

本実施の形態は、発光表示装置の画素部の構成及び作製方法について説明するものである。従って、本実施の形態におけるトランジスタとは、図1(A)、(B)に示す第1のトランジスタ151及び第2のトランジスタ152の両方またはいずれかのことを言う。また、該トランジスタは、後述する酸化物半導体を用いたnチャネル型である。

【0024】

図1(A)、(B)に示すアクティブマトリクス型の発光表示装置の画素部は、第1のゲート電極層102a、ゲート絶縁層106、半導体層108a、第1のソース電極層及びドレイン電極層112a、112bを含む第1のトランジスタ151と、第2のゲート電極層102b、ゲート絶縁層106、半導体層108a、第2のソース電極層及びドレイン電極層112c、112dを含む第2のトランジスタ152を有する。

【0025】

ここで、第1のゲート電極層102aはゲート配線と接続され、第1のソース電極層及びドレイン電極層112aはソースドレイン配線と接続され、第1のソース電極層及びドレイン電極層112bは第1の開口部110aにおいて第2のゲート電極層102bに接続され、第2のソース電極層及びドレイン電極層112cは電源配線に接続され、第2のソース電極層及びドレイン電極層112dは第3の開口部130bにおいて第1の画素電極層118と接続されている。なお、図1(A)において、ゲート配線と第1のゲート電極層、ソースドレイン配線と第1のソース電極層及びドレイン電極層の一方、電源配線と第2のソース電極層及びドレイン電極層の一方のそれぞれは一体であり、同じ符号を付してある。

【0026】

なお、図1では第1のトランジスタ151をシングルゲート構造で図示しているが、マルチゲート構造としても良い。マルチゲート構造のトランジスタは、オフ電流が小さく、該トランジスタを含む発光表示装置の表示特性を高めることができる。

【0027】

また、第2のゲート電極層102bと電源配線(第2のソース電極層及びドレイン電極層112c)は、ゲート絶縁層106及び半導体層108aを介して重なる領域を有しており、容量素子153を形成している。この様に、誘電体層を多層構造とすることで、一つの誘電体層にピンホールが生じても、ピンホールは他の誘電体層で被覆されるため、容量素子153を正常に機能させることができる。また、酸化物半導体の比誘電率は14乃至16と大きいため、半導体層108aに酸化物半導体を用いると、容量素子153の容量値を大きくすることが可能となる。

【0028】

第1のトランジスタ151及び第2のトランジスタ152上には保護絶縁層114及び平坦化絶縁層116が形成されており、その一部が開口されて、ゲート絶縁層106が露出する第2の開口部130aと第2のソース電極層及びドレイン電極層112dの一部が露出する第3の開口部130bが形成されている。また、平坦化絶縁層116を省いた構成とすることもできる。

【0029】

第3の開口部130bは第1の画素電極層118の一部で覆い、第2の開口部130aには隔壁119となる絶縁材料が充填される。ここで、隔壁119は図1(A)には図示されていないが、第1の画素電極層118の端部及び上記の構成において凹凸のある領域などを覆うように形成する。隔壁119によって、後に第1の画素電極層118上などに形成するEL層160や第2の画素電極層170の断切れを防止することができる。

【0030】

なお、図2に示すような容量素子を設けない構成としてもよい。図2では第2のゲート電極層102cを電源配線(第2のソース電極層及びドレイン電極層112c)と重ねない構成とし、容量素子を形成していない。この構成の等価回路は、図3(B)である。

【0031】

半導体層108aに用いる材料としては、酸化物半導体が好ましい。酸化物半導体層は、化学式InMO3(ZnO)m(m>0)で表記される材料を用いた薄膜により形成することができる。ここで、Mは、Sn、Zn、Ga、Al、Mn及びCoから選ばれた一つ、または複数の金属元素を示す。例えば、Mとして、Ga、Ga及びAl、Ga及びMnまたはGa及びCoなどを用いることができる。

【0032】

例えば、In:Ga:Zn=1:1:1(=1/3:1/3:1/3)あるいはIn:Ga:Zn=2:2:1(=2/5:2/5:1/5)の原子数比のIn−Ga−Zn−O系酸化物やその組成の近傍の酸化物を用いることができる。あるいは、In:Sn:Zn=1:1:1(=1/3:1/3:1/3)、In:Sn:Zn=2:1:3(=1/3:1/6:1/2)あるいはIn:Sn:Zn=2:1:5(=1/4:1/8:5/8)の原子数比のIn−Sn−Zn−O系酸化物やその組成の近傍の酸化物を用いるとよい。

【0033】

しかし、これらに限られず、必要とする半導体特性(移動度、しきい値、ばらつき等)に応じて適切な組成のものを用いればよい。また、必要とする半導体特性を得るために、キャリア濃度や不純物濃度、欠陥密度、金属元素と酸素の原子数比、原子間結合距離、密度等を適切なものとすることが好ましい。

【0034】

例えば、In−Sn−Zn−O系酸化物では比較的容易に高い移動度が得られる。しかしながら、In−Ga−Zn−O系酸化物でも、バルク内欠陥密度を低減することにより移動度を上げることができる。

【0035】

なお、例えば、In、Ga、Znの原子数比がIn:Ga:Zn=a:b:c(a+b+c=1)である酸化物が、原子数比がIn:Ga:Zn=A:B:C(A+B+C=1)の酸化物のrだけ近傍であるとは、a、b、cが、(a―A)2+(b―B)2+(c―C)2≦r2を満たすことを言う。rとしては、例えば、0.05とすればよい。他の酸化物でも同様である。

【0036】

酸化物半導体は単結晶でも、非単結晶でもよい。後者の場合、アモルファスでも、多結晶でもよい。また、アモルファス中に結晶性を有する部分を含む構造でも、非アモルファスでもよい。

【0037】

アモルファス状態の酸化物半導体は、比較的容易に平坦な表面を得ることができるため、これを用いてトランジスタを作製した際の界面散乱を低減でき、比較的容易に、比較的高い移動度を得ることができる。

【0038】

また、結晶性を有する酸化物半導体では、よりバルク内欠陥を低減することができ、表面の平坦性を高めればアモルファス状態の酸化物半導体以上の移動度を得ることができる。表面の平坦性を高めるためには、平坦な表面上に酸化物半導体を形成することが好ましく、具体的には、平均面粗さ(Ra)が1nm以下、好ましくは0.3nm以下、より好ましくは0.1nm以下の表面上に形成するとよい。

【0039】

なお、Raは、JIS B0601で定義されている中心線平均粗さを面に対して適用できるよう三次元に拡張したものであり、「基準面から指定面までの偏差の絶対値を平均した値」と表現でき、以下の式にて定義される。

【0040】

【数1】

【0041】

なお、上記において、S0は、測定面(座標(x1,y1)(x1,y2)(x2,y1)(x2,y2)で表される4点によって囲まれる長方形の領域)の面積を指し、Z0は測定面の平均高さを指す。Raは原子間力顕微鏡(AFM:Atomic Force Microscope)にて評価可能である。

【0042】

半導体層108aに酸化物半導体を用いたトランジスタは、極めてオフ電流が小さい電気特性を有する。酸化物半導体は、水素などの不純物が十分に除去されることにより、または、十分な酸素が供給されることにより、高純度化されたものであることが望ましい。具体的には、例えば、酸化物半導体の水素濃度は5×1019atoms/cm3以下、望ましくは5×1018atoms/cm3以下、より望ましくは5×1017atoms/cm3以下とする。なお、上述の酸化物半導体中の水素濃度は、二次イオン質量分析法(SIMS:Secondary Ion Mass Spectrometry)で測定されるものである。このように、水素濃度が十分に低減されて高純度化され、十分な酸素の供給により酸素欠損に起因するエネルギーギャップ中の欠陥準位が低減された酸化物半導体では、水素等のドナーに起因するキャリア密度が1×1012/cm3未満、望ましくは、1×1011/cm3未満、より望ましくは1.45×1010/cm3未満となる。また、例えば、室温(25℃)でのオフ電流(ここでは、単位チャネル幅(1μm)あたりの値)は100zA(1zA(ゼプトアンペア)は1×10−21A)以下、望ましくは10zA以下となる。このように、i型化(真性化)または実質的にi型化された酸化物半導体を用いることで、極めて優れたオフ電流特性のトランジスタを得ることができる。

【0043】

従って、画素に保持された電荷の保持特性が極めて高く、容量素子が無い場合、または図1(A)、(B)に示す構成より保持容量の面積を小さくした場合においても一般的なフレーム周波数(60Hz)もしくはそれ以下のフレーム周波数においても、何ら問題なく画像を保持することができる。

【0044】

また、酸化物半導体は不純物に対して鈍感であり、膜中にはかなりの金属不純物が含まれていても問題がなく、ナトリウムのようなアルカリ金属が多量に含まれる廉価なソーダ石灰ガラスも使えると指摘されている(神谷、野村、細野、「アモルファス酸化物半導体の物性とデバイス開発の現状」、固体物理、2009年9月号、Vol.44、p.621−633)しかし、このような指摘は適切でない。酸化物半導体中のアルカリ金属は、二次イオン質量分析法による含有量の最低値で、ナトリウム(Na)が5×1016cm−3以下、好ましくは1×1016cm−3以下、さらに好ましくは1×1015cm−3以下、リチウム(Li)が5×1015cm−3以下、好ましくは1×1015cm−3以下、カリウム(K)が5×1015cm−3以下、好ましくは1×1015cm−3以下である。

【0045】

アルカリ金属、及びアルカリ土類金属は酸化物半導体にとっては悪性の不純物であり、少ないほうがよい。特にアルカリ金属のうち、Naは酸化物半導体に接する絶縁膜が酸化物であった場合、その中に拡散し、Na+となる。また、酸化物半導体内において、金属と酸素の結合を分断し、あるいは結合中に割り込む。その結果、トランジスタ特性の劣化(例えば、ノーマリオン化(しきい値の負へのシフト)、移動度の低下等)をもたらす。加えて、特性のばらつきの原因ともなる。このような問題は、特に酸化物半導体中の水素の濃度が十分に低い場合において顕著となる。したがって、酸化物半導体中の水素の濃度が5×1019cm−3以下、特に5×1018cm−3以下である場合には、アルカリ金属の濃度を上記の値にすることが強く求められる。

【0046】

また、i型化または実質的にi型化された酸化物半導体は、極めて抵抗が高く、回路を構成する上では絶縁体とみなすことができる。従って、同一島状の半導体層に複数のトランジスタが構成されていても互いに干渉することはなく、各トランジスタを動作させることができる。なお、本実施の形態では2つのトランジスタが同一島状の半導体層に形成されているが、容量素子部に半導体層を残さない構造とすれば、2つのトランジスタの半導体層を分離することもできる。

【0047】

また、図1(B)の構成においては、第1の画素電極層118が半導体層108aの側面に接して形成されている領域があるが、上記と同様にi型化または実質的にi型化された酸化物半導体は、ほぼ絶縁物とみなすことができるため、第1の画素電極層118と半導体層108aの端部が接しても、漏れ電流等の問題は生じない。

【0048】

また、半導体層108aに酸化物半導体を用いる場合は、図14(A)、(B)に示すように、画素領域全面に半導体層を残す構成としても良い。酸化物半導体層は上述のように高抵抗であることと、可視光に対して透光性を有するため、発光素子からの発光方向がトランジスタ側であっても光を透過させることができる。

【0049】

本実施の形態に示す第2のトランジスタ152は、第2のソース電極層及びドレイン電極層112dを、U字型(C字型、コの字型、または馬蹄型)の第2のソース電極層及びドレイン電極層112cで囲む形状としている。このような形状とすることで、トランジスタの面積が少なくても、十分なチャネル幅を確保することが可能となり、トランジスタの導通時に流れる電流(オン電流ともいう)の量を増やすことが可能となる。

【0050】

本発明の一態様は、保護絶縁層114と半導体膜108のエッチングを連続して行うことによりフォトリソグラフィ工程が削減できるという特徴があり、次に図4乃至7を用いて作製方法の一例の詳細を説明する。

【0051】

なお、ここではトランジスタ部250の作製方法を主として説明するが、図示してあるように容量素子部260、配線交差部270、及びFPC接続部280についても必要に応じて説明する。

【0052】

まず、絶縁表面を有する基板100上に第1の導電膜を形成した後、第1のフォトリソグラフィ工程、及びエッチング工程により第1のゲート電極層102a、第2のゲート電極層102bを形成する(図4(A)参照)。

【0053】

なお、フォトリソグラフィ工程に用いるレジストマスクはインクジェット法で形成してもよい。インクジェット法では、フォトマスクを使用しないため、更に製造コストを低減することができる。また、レジストマスクはエッチング工程の後に剥離するものとし、各フォトリソグラフィ工程における説明は省くこととする。

【0054】

ここで、基板100には、少なくとも、後の熱処理に耐えうる程度の耐熱性を有しているものを用いることができる。例えば、バリウムホウケイ酸ガラスやアルミノホウケイ酸ガラスなどのガラス基板、セラミック基板、石英基板、サファイア基板などを用いることができる。また、シリコンや炭化シリコンなどの単結晶半導体基板、多結晶半導体基板、シリコンゲルマニウムなどの化合物半導体基板、SOI基板などを用いることもできる。

【0055】

基板100と第1のゲート電極層102a、第2のゲート電極層102bとの間には、下地膜となる絶縁膜を設けてもよい。下地膜は、基板100からの不純物元素の拡散を防止する機能があり、酸化シリコン、酸窒化シリコン、窒化シリコン、酸化ハフニウム、酸化アルミニウム、酸化ガリウム、酸化ガリウムアルミニウムから選ばれた膜で形成することができる。また、該下地膜は単層に限らず、上記の複数の膜の積層であっても良い。

【0056】

第1のゲート電極層102a、第2のゲート電極層102bは、モリブデン、チタン、タンタル、タングステン、アルミニウム、銅、ネオジム、スカンジウム等の金属材料、またはこれらを主成分とする合金材料をスパッタ法等で形成することができる。また、該ゲート電極層は単層に限らず、上記複数の材料の積層であっても良い。例えば、アルミニウムとモリブデンの積層、アルミニウムとチタンの積層、銅とモリブデンの積層、または銅とタングステンの積層などがある。ここでは、銅上にモリブデンを形成した積層を用いる。

【0057】

次いで、第1のゲート電極層102a、第2のゲート電極層102b上にゲート絶縁層106をCVD法やスパッタ法等を用いて形成する。ゲート絶縁層106は、酸化シリコン、窒化シリコン、酸窒化シリコン、酸化アルミニウム、酸化タンタル、酸化ハフニウム、酸化イットリウム、酸化ガリウム、酸化ランタン、ハフニウムシリケート(HfSixOy(x>0、y>0))、窒素が添加されたハフニウムシリケート(HfSiOxNy(x>0、y>0))、窒素が添加されたハフニウムアルミネート(HfAlOxNy(x>0、y>0))、などを含むように形成するのが好適である。またはこれらの混合材料をプラズマCVD法、またはスパッタ法等により形成することもできる。また、ゲート絶縁層106は単層に限らず、上記複数の材料の積層であっても良い。また、その厚さは特に限定されないが、例えば、酸化シリコンを用いる場合には、1nm以上100nm以下、好ましくは10nm以上50nm以下とすることができる。

【0058】

なお、ゲート絶縁層106には、後に形成される半導体膜と同種の成分を含む絶縁材料を用いることが好ましい。この様な材料は、半導体膜との界面の状態を良好に保つことができる。ここで、「半導体膜と同種の成分」とは、半導体膜の構成元素から選択される一つまたは複数の元素を含むことを意味する。例えば、半導体膜がIn−Ga−Zn−O系の酸化物半導体材料によって構成される場合、同種の成分を含む絶縁材料としては酸化ガリウムなどがある。

【0059】

また、ゲート絶縁層106の形成には、緻密で絶縁耐圧の高い高品質な絶縁層を形成できるマイクロ波(例えば周波数2.45GHz)を用いた高密度プラズマCVDを用いることが好ましい。半導体層と高品質ゲート絶縁層が密接することにより、界面準位を低減することができる。

【0060】

また、成膜後の熱処理によってゲート絶縁層の膜質や、半導体層との界面特性が改質される絶縁層であっても良い。いずれにしても、ゲート絶縁層は、膜質が良好であることは勿論のこと、半導体層との界面準位密度を低減し、良好な界面を形成できるものが好ましい。

【0061】

また、ゲート絶縁層106上に形成される半導体膜(ここでは酸化物半導体膜)に水素、水酸基及び水分が極力含まれない様にするために、ゲート絶縁層106までが形成された基板100を成膜装置の予備加熱室で真空加熱し、基板100に吸着した水素、水分などの不純物を脱離させて排気することが好ましい。なお、予備加熱室に設ける排気手段には、クライオポンプを用いることが好ましい。なお、この予備加熱の処理は省略することもできる。

【0062】

次いで、ゲート絶縁層106上に、膜厚2nm以上200nm以下、好ましくは5nm以上30nm以下の半導体膜108を形成する(図4(B)参照)。

【0063】

半導体膜108には酸化物半導体を用いることが好ましい。また、用いる酸化物半導体としては、少なくともインジウム(In)あるいは亜鉛(Zn)を含むことが好ましい。特にInとZnを含むことが好ましい。また、該酸化物半導体を用いたトランジスタの電気特性のばらつきを減らすためのスタビライザーとして、それらに加えてガリウム(Ga)を有することが好ましい。また、スタビライザーとしてスズ(Sn)を有することが好ましい。また、スタビライザーとしてハフニウム(Hf)を有することが好ましい。また、スタビライザーとしてアルミニウム(Al)を有することが好ましい。

【0064】

また、他のスタビライザーとして、ランタノイドである、ランタン(La)、セリウム(Ce)、プラセオジム(Pr)、ネオジム(Nd)、サマリウム(Sm)、ユウロピウム(Eu)、ガドリニウム(Gd)、テルビウム(Tb)、ジスプロシウム(Dy)、ホルミウム(Ho)、エルビウム(Er)、ツリウム(Tm)、イッテルビウム(Yb)、ルテチウム(Lu)のいずれか一種あるいは複数種を有してもよい。

【0065】

例えば、酸化物半導体として、酸化インジウム、酸化スズ、酸化亜鉛、二元系金属の酸化物であるIn−Zn−O系酸化物、Sn−Zn−O系酸化物、Al−Zn−O系酸化物、Zn−Mg−O系酸化物、Sn−Mg−O系酸化物、In−Mg−O系酸化物、In−Ga−O系酸化物、三元系金属の酸化物であるIn−Ga−Zn−O系酸化物(IGZOとも表記する)、In−Al−Zn−O系酸化物、In−Sn−Zn−O系酸化物、Sn−Ga−Zn−O系酸化物、Al−Ga−Zn−O系酸化物、Sn−Al−Zn−O系酸化物、In−Hf−Zn−O系酸化物、In−La−Zn−O系酸化物、In−Ce−Zn−O系酸化物、In−Pr−Zn−O系酸化物、In−Nd−Zn−O系酸化物、In−Sm−Zn−O系酸化物、In−Eu−Zn−O系酸化物、In−Gd−Zn−O系酸化物、In−Tb−Zn−O系酸化物、In−Dy−Zn−O系酸化物、In−Ho−Zn−O系酸化物、In−Er−Zn−O系酸化物、In−Tm−Zn−O系酸化物、In−Yb−Zn−O系酸化物、In−Lu−Zn−O系酸化物、四元系金属の酸化物であるIn−Sn−Ga−Zn−O系酸化物、In−Hf−Ga−Zn−O系酸化物、In−Al−Ga−Zn−O系酸化物、In−Sn−Al−Zn−O系酸化物、In−Sn−Hf−Zn−O系酸化物、In−Hf−Al−Zn−O系酸化物を用いることができる。

【0066】

なお、ここで、例えば、In−Ga−Zn−O系酸化物とは、InとGaとZnを主成分として有する酸化物という意味であり、InとGaとZnの比率は問わない。また、InとGaとZn以外の金属元素が入っていてもよい。

【0067】

特にインジウムを含む酸化物半導体、インジウム及びガリウムを含む酸化物半導体などを用いると電気特性が良好なトランジスタを形成することができる。本実施の形態では、半導体膜108としてIn−Ga−Zn−O系酸化物からなる膜をスパッタ法により成膜する。

【0068】

上記スパッタ法に用いるターゲットには、例えば、組成比として、In2O3:Ga2O3:ZnO=1:1:1[mol数比]の酸化物ターゲットを用いる。また、In2O3:Ga2O3:ZnO=1:1:2[mol数比]の酸化物ターゲットを用いてもよい。

【0069】

また、酸化物半導体としてIn−Zn−O系酸化物を用いる場合、用いる酸化物ターゲットの組成比は、原子数比で、In:Zn=50:1〜1:2(mol数比に換算するとIn2O3:ZnO=25:1〜1:4)、好ましくはIn:Zn=20:1〜1:1(mol数比に換算するとIn2O3:ZnO=10:1〜1:2)、さらに好ましくはIn:Zn=15:1〜1.5:1(mol数比に換算するとIn2O3:ZnO=15:2〜3:4)とする。例えば、In−Zn−O系酸化物半導体の形成に用いる酸化物ターゲットは、原子数比がIn:Zn:O=X:Y:Zのとき、Z>1.5X+Yとする。

【0070】

また、In−Sn−Zn−O系酸化物は、ITZOと呼ぶことができ、用いるターゲットの組成比は、In:Sn:Znが原子数比で、1:2:2、2:1:3、1:1:1、または20:45:35などとなる酸化物ターゲットを用いる。

【0071】

また、ターゲットの充填率は90%以上100%以下、好ましくは95%以上100%以下である。充填率の高いターゲットを用いることにより、成膜した酸化物半導体膜は緻密な膜とすることができる。

【0072】

また、スパッタガスとしては、希ガス(代表的にはアルゴン)、酸素、または希ガスと酸素の混合ガスを用いることができる。なお、該スパッタガスには、水素、水、水酸基または水素化物などの不純物が除去された高純度ガスを用いることが好ましい。

【0073】

酸化物半導体膜の成膜は、基板を加熱しながら成膜することが好ましい。減圧状態に保持された成膜室内に基板を保持し、基板温度を200℃以上450℃以下として成膜することで、酸化物半導体膜に含まれる不純物濃度を低減することができる。ただし、ゲート電極層に用いる材料により上限の温度がことなり、本実施の形態のように融点が高い銅とモリブデンの積層と用いる場合や、銅とタングステンの積層を用いる場合は、450℃を上限とすることができるが、融点が低いアルミニウムを含む積層を用いる場合は、上限を380℃とすることが好ましい。

【0074】

また、成膜室内の残留水分を除去するためには、吸着型の真空ポンプ、例えば、クライオポンプ、イオンポンプ、チタンサブリメーションポンプを用いることが好ましい。また、排気手段としては、ターボ分子ポンプにコールドトラップを加えたものであってもよい。クライオポンプを用いて排気した成膜室は、例えば、水素原子、水など水素原子を含む化合物、及び炭素原子を含む化合物等が排気されるため、該成膜室で成膜した酸化物半導体膜に含まれる不純物の濃度を低減することができる。

【0075】

成膜条件の一例としては、基板とターゲットの間との距離を100mm、圧力0.6Pa、直流(DC)電源0.5kW、酸素(酸素流量比率100%)雰囲気下の条件が挙げられる。なお、パルス直流電源を用いると、成膜時に発生する粉状物質(パーティクル、ごみともいう)を軽減でき、膜厚分布も均一にすることができる。

【0076】

次いで、第1の熱処理による半導体膜108の脱水化または脱水素化を行う。本明細書において、脱水化または脱水素化とは、水や水素分子を脱離させていることのみを示すものではなく、水素原子や水酸基などを脱離することも含まれる。

【0077】

熱処理は、例えば、抵抗発熱体などを用いた電気炉に被処理物を導入し、窒素雰囲気下、450℃、1時間の条件で行うことができる。この間、半導体膜108は大気に触れさせず、水や水素の混入が生じないようにする。

【0078】

この熱処理によって過剰な水素(水や水酸基を含む)を除去し、酸化物半導体膜の構造を整え、エネルギーギャップ中の欠陥準位を低減することができる。熱処理の温度は、250℃以上450℃以下とする。また、熱処理時間は、上記好適な温度範囲であれば1時間程度行えば良い。ただし、低温で長時間、または高温で短時間の処理を行っても良く、実施者が適宜決定すれば良い。なお、上限の温度はゲート電極層に用いる材料に依存するため、上述したように銅を含む材料を用いる場合は、450℃を上限とすることができるが、アルミニウムを含む材料を用いる場合は、380℃が上限となる。

【0079】

熱処理装置は電気炉に限られず、加熱されたガスなどの媒体からの熱伝導、または熱輻射によって、被処理物を加熱する装置を用いても良い。例えば、GRTA(Gas Rapid Thermal Anneal)装置、LRTA(Lamp Rapid Thermal Anneal)装置等のRTA(Rapid Thermal Anneal)装置を用いることができる。LRTA装置は、ハロゲンランプ、メタルハライドランプ、キセノンアークランプ、カーボンアークランプ、高圧ナトリウムランプ、高圧水銀ランプなどのランプから発する光(電磁波)の輻射により、被処理物を加熱する装置である。GRTA装置は、高温のガスを用いて熱処理を行う装置である。ガスとしては、アルゴンなどの希ガス、または窒素のような、熱処理によって被処理物と反応しない不活性気体が用いられる。

【0080】

例えば、第1の熱処理として、熱せられた不活性ガス雰囲気中に被処理物を投入し、数分間熱した後、当該不活性ガス雰囲気から被処理物を取り出すGRTA処理を行ってもよい。GRTA処理を用いると短時間での高温熱処理が可能となる。また、被処理物の耐熱温度を超える温度条件であっても適用が可能となる。なお、処理中に、不活性ガスを、酸素を含むガスに切り替えても良い。酸素を含む雰囲気において第1の熱処理を行うことで、酸素欠損に起因するエネルギーギャップ中の欠陥準位を低減することができるためである。

【0081】

なお、不活性ガス雰囲気としては、窒素、または希ガス(ヘリウム、ネオン、アルゴン等)を主成分とする雰囲気であって、水、水素などが含まれない雰囲気を適用するのが望ましい。例えば、熱処理装置に導入する窒素や、ヘリウム、ネオン、アルゴン等の希ガスの純度を、6N(99.9999%)以上、好ましくは7N(99.99999%)以上(すなわち、不純物濃度が1ppm以下、好ましくは0.1ppm以下)とする。

【0082】

いずれにしても、第1の熱処理によって不純物を低減し、i型(真性半導体)またはi型に限りなく近い酸化物半導体膜を形成することで、極めて優れた特性のトランジスタを実現することができる。

【0083】

なお、上述の熱処理は、このタイミングに限らず、ソース電極及びドレイン電極形成後や保護絶縁膜形成後に行ってもよい。また、一回に限らず複数回行っても良い。

【0084】

次いで、第2のフォトリソグラフィ工程、及びエッチング工程により、第2のゲート電極層102b、及び第1のゲート電極層102a上の半導体膜108及びゲート絶縁層106の一部を開口した第1の開口部110a、110bを形成する。ここで、第1の開口部110aは、後に第1のトランジスタ151の第1のソース電極層及びドレイン電極層112bと第2のゲート電極102bとの接続のために用いられ、FPC接続部に形成される第1の開口部110bは、第1のゲート電極層102aを露出させるための開口である(図4(C)参照)。

【0085】

ここで、半導体膜108及びゲート絶縁層106のエッチングは、ドライエッチング、またはウェットエッチングのどちらを用いても良い。また、両方を用いてもよい。例えば、酸化物半導体である半導体膜108のエッチング液としては、燐酸、酢酸、及び硝酸を混ぜた溶液などを用いることができる。また、ITO−07N(関東化学社製)を用いてもよい。また、ゲート絶縁層106は、フッ酸系のエッチング液を用いれば良い。

【0086】

次いで、第2のゲート電極層102b、第1のゲート電極層102a、及び半導体膜108上に、トランジスタのソース電極層及びドレイン電極層(これと同じ層で形成される配線を含む)となる第2の導電膜112を形成する(図5(A)参照)。

【0087】

第2の導電膜112としては、例えば、アルミニウム、クロム、銅、タンタル、チタン、モリブデン、タングステンからから選ばれた元素を含む金属膜、または上述した元素を成分とする金属窒化物膜(窒化チタン膜、窒化モリブデン膜、窒化タングステン膜)等を用いることができる。また、アルミニウム、銅などの金属膜の一方の面または双方の面にチタン、モリブデン、タングステンなどの高融点金属膜またはそれらの窒化膜(窒化チタン膜、窒化モリブデン膜、窒化タングステン膜等)を積層させた構成としても良い。例えば、タングステンと銅の積層、タングステン、窒化タングステン、銅、タングステンの積層、モリブデン、窒化モリブデン、銅、モリブデンの積層、モリブデン、アルミニウム、モリブデンの積層などがある。本実施の形態では、タングステン上に銅を形成した積層を用いる。

【0088】

次いで、第3のフォトリソグラフィ工程により第2の導電膜112上にレジストマスクを形成し、選択的にエッチングを行って、第1のソース電極層及びドレイン電極層112a、112b、第2のソース電極層及びドレイン電極層112c、112dを形成する。また、容量素子部においては、ゲート絶縁層106及び半導体膜108を介して第2のゲート電極と重なるように電源配線(第2のソース電極層及びドレイン電極層112c)を形成する。また、FPC接続部には第1のゲート電極層102aと電気的に接続される導電層112eを形成する(図5(B)参照)。

【0089】

なお、第2の導電膜112のエッチングの際に、半導体膜108が極力エッチングされない様にすることが好ましい。しかしながら、第2の導電膜112のみをエッチングする条件を得ることは難しく、第2の導電膜112のエッチングの際に半導体膜108の一部がエッチングされ、溝部(凹部)を有する形状となることもある。

【0090】

以上の工程で第1のトランジスタ151、第2のトランジスタ152、及び容量素子153が形成される。該トランジスタは、水素、水分、水酸基または水素化物(水素化合物ともいう)などの不純物を半導体膜108より意図的に排除し、高純度化された酸化物半導体を含むトランジスタである。よって、該トランジスタは、電気的特性変動が抑制されており、電気的に安定である。

【0091】

次に、基板100上に形成した上記の構成を覆うように保護絶縁層114を形成する(図5(C)参照)。保護絶縁層114は、少なくとも1nm以上の膜厚とし、保護絶縁層114に水、水素等の不純物を極力混入させない上述した方法を適宜用いて形成することができる。本実施の形態では、スパッタ法を用いて保護絶縁層114を形成する。保護絶縁層114に水素が含まれていると、その水素が半導体膜108へ侵入する場合や、半導体膜108中の酸素を水素が引き抜く現象が生じることがある。この様な現象が起こると、半導体膜108のバックチャネル側が低抵抗化(n型化)してしまい、寄生チャネルが形成されてしまうことがある。従って、保護絶縁層114はできるだけ水素を含まない膜になる様にすることが重要である。

【0092】

保護絶縁層114は、PVD法やCVD法などを用いて形成することができる。また、酸化シリコン、酸窒化シリコン、窒化シリコン、酸化ハフニウム、酸化アルミニウム、酸化ガリウム、酸化ガリウムアルミニウム等の無機絶縁材料を含む材料を用いて、単層または積層で形成することができる。

【0093】

なお、保護絶縁層114には、ゲート絶縁層106と同様に、半導体膜108と同種の成分を含む絶縁材料を用いると好ましい。この様な材料は半導体膜108との界面の状態を良好に保つことができる。例えば、半導体膜108がIn−Ga−Zn−O系の酸化物半導体材料によって構成される場合、同種の成分でなる絶縁材料としては酸化ガリウムなどがある。

【0094】

また、保護絶縁層114を積層構造とする場合には、半導体膜108と同種の成分を含む絶縁膜(以下、膜a)と、膜aの成分材料とは異なる材料を含む膜(以下、膜b)との積層構造とするとなお良い。膜aと膜bとを半導体膜108側から順に積層した構造とすることで、電荷は膜aと膜bとの界面の電荷捕獲中心に優先的に捕獲される(半導体膜108と膜aとの界面との比較)ため、半導体膜108の界面での電荷捕獲を十分に抑制することができる様になり、トランジスタの信頼性が向上するためである。

【0095】

例えば、保護絶縁層114として半導体膜108側から酸化ガリウム膜と酸化シリコン膜との積層、または酸化ガリウム膜と窒化シリコン膜との積層などを用いることが好適である。

【0096】

本実施の形態では、保護絶縁層114に酸化シリコン膜を用いる。酸化シリコン膜は、希ガス、酸素、または希ガスと酸素の混合ガスを用いて、スパッタ法で成膜することができる。成膜時の基板温度は、室温以上300℃以下とすればよく、本実施の形態では100℃とする。また、ターゲットには、酸化シリコンターゲットまたはシリコンターゲットを用いることができる。例えば、シリコンターゲットを用いて、酸素をスパッタガスとして酸化シリコンを形成することができる。

【0097】

また、保護絶縁層114形成時においても、半導体膜108の成膜時と同様に成膜室内の残留水分を除去するため、吸着型の真空ポンプ(クライオポンプなど)を用いることが好ましい。クライオポンプを用いて排気した成膜室では、例えば、水素原子、水など水素原子を含む化合物、及び炭素原子を含む化合物等が排気されるため、成膜した保護絶縁層114に含まれる不純物の濃度を低減できる。また、成膜室内の残留水分を除去するための排気手段としては、ターボ分子ポンプにコールドトラップを加えたものであってもよい。

【0098】

保護絶縁層114を成膜する際に用いるスパッタガスには、水素、水、水酸基または水素化物などの不純物が除去された高純度ガスを用いることが好ましい。

【0099】

上述の保護絶縁層114の形成後に第2の熱処理を行っても良い。熱処理の方法や雰囲気には、前述した第1の熱処理と同様の方法を用いることができる。第1の熱処理と同様にゲート電極層、ソース電極層及びドレイン電極層に用いる材料によって熱処理の上限温度は異なり、該電極層が銅、モリブデン、タングステンなどの融点の高い金属で構成されている場合は450℃を上限温度とすることができる。一方、該電極層がアルミニウムなどの融点の低い金属が含まれて構成されている場合は、380℃を上限温度とすることができる。また、大気中、100℃以上200℃以下、1時間以上30時間以下の熱処理を行ってもよい。この熱処理は一定温度を1回で行うだけでなく、室温から100℃以上200℃以下の温度への昇温と、その温度から室温までの降温を複数回繰り返して行ってもよい。

【0100】

半導体膜108と酸素を含む保護絶縁層114を接した状態で熱処理を行うと、酸素を含む保護絶縁層114より酸素をさらに半導体膜108へ供給することができる。

【0101】

次いで、保護絶縁層114上に平坦化絶縁層116を形成する(図6(A)参照)。平坦化絶縁層116は、アクリル、ポリイミド、ポリアミドなどの有機樹脂、またはシロキサンを用いて形成することが好ましい。

【0102】

上記樹脂として、感光性樹脂を用いればフォトレジストが不要となり、露光することで所望の形状が得られるため、工程を簡略化することができる。また、露光して所望の形状に硬化させた感光性樹脂をレジストマスクとすることができる。

【0103】

本実施の形態では、平坦化絶縁層116に感光性アクリル樹脂を用い、露光(第4のフォトリソグラフィ工程)によって開口部を有する形状を得た後、該感光性アクリル樹脂をマスクとして保護絶縁層114及び半導体膜108をエッチングし、第2の開口部130a、第3の開口部130bを形成する(図6(B)参照)。

【0104】

エッチングは、ドライエッチングでもウェットエッチングでもよく、両方を用いてもよい。ドライエッチングに用いるエッチングガスとしては、塩素を含むガス(塩素系ガス、例えば塩素(Cl2)、三塩化硼素(BCl3)、四塩化珪素(SiCl4)、四塩化炭素(CCl4)など)を用いることができる。ドライエッチング法としては、平行平板型RIE(Reactive Ion Etching)法や、ICP(Inductively Coupled Plasma:誘導結合型プラズマ)エッチング法を用いることができる。

【0105】

第2の開口部130aは、保護絶縁層114及び半導体膜108をエッチングして形成される。ここで、半導体膜108の不要な領域は取り除かれ、半導体層108aが形成される。従って、半導体膜を島状に加工するような工程を省くことができる。すなわち、フォトリソグラフィ工程を削減することができる。

【0106】

第3の開口部130bは、保護絶縁層114の下部にある第2のソース電極層及びドレイン電極層112d、及び導電層112eがエッチングストッパーとなるため、保護絶縁層114のみがエッチングされて形成される。

【0107】

また、本実施の形態に示す作製工程によれば、半導体層108a上にフォトレジストが直接形成されることがなく、フォトレジストの剥離洗浄工程などにおいて半導体層108aを汚染することがないため、トランジスタの電気特性の変動を抑えることができる。

【0108】

次いで、第3の開口部130bを覆うように第3の導電膜を形成する。本実施の形態では、第1のトランジスタ151、第2のトランジスタ152は半導体層108aに酸化物半導体を用いたnチャネル型であり、第1の画素電極層118となる第3の導電膜としては発光素子の陰極となる材料を用いるのが望ましい。具体的には、陰極としては、仕事関数が小さい材料、例えば、Ca、Al、CaF、MgAg、AlLi等を用いることができる。なお、発光方向を制御するために第3の導電膜として透光性導電膜を用いても良い。この場合は、透光性導電膜上に陰極となる上記材料を形成すれば良い。なお、透光性導電膜としては、例えば酸化タングステンを含むインジウム酸化物、酸化タングステンを含むインジウム亜鉛酸化物、酸化チタンを含むインジウム酸化物、酸化チタンを含むインジウム錫酸化物、インジウム錫酸化物(以下、ITOと示す。)、インジウム亜鉛酸化物、酸化ケイ素を添加したインジウム錫酸化物などがある。また、1枚乃至10枚のグラフェンシート(グラファイトの1層分)よりなる材料を用いてもよい。

【0109】

次いで、第5のフォトリソグラフィ工程により第3の導電膜上にレジストマスクを形成し、選択的にエッチングを行って、第1の画素電極層118を形成する。このとき、第2の開口部に第1の画素電極層118が形成されても良い。なお、第3の導電膜にITO等の酸化物導電層を用いると、FPC接続部において下層の金属導電層の表面酸化によるFPC端子との接触抵抗の増加を抑えることができ、半導体装置の信頼性を向上させることができる。

【0110】

次いで、第2の開口部130a、第3の開口部130b、及び第1の画素電極層118の周囲を覆うように隔壁119を形成する(図6(C)参照)。

【0111】

次いで、図示はしないが、第1の画素電極層118上にEL層及び第2の画素電極層を選択的に形成する。

【0112】

以上の工程を含む作製方法によって発光表示装置を完成させることができる。なお、上記の方法で形成される構成とは異なり、容量素子153を形成しない構成では、図4(A)において、容量素子を形成する領域に第2のゲート電極層102bを設けない構成とすれば良い。

【0113】

また、平坦化絶縁層116を設けない構成とすることもできる。この構成の作製方法は、図5(C)までは上述の方法と同様であり、第4のフォトリソグラフィ工程によって、第2の開口部120a、第3の開口部120bを形成する(図7(A)参照)。

【0114】

次いで、少なくとも第3の開口部120bを覆うように保護絶縁層114上に第3の導電膜を形成し、第5のフォトリソグラフィ工程により第3の導電膜上にレジストマスクを形成し、選択的にエッチングを行って、第1の画素電極層118を形成する。このとき、第2の開口部120aの一部に第1の画素電極層118が形成されても良い。

【0115】

次いで、第2の開口部120a、第3の開口部120b、及び第1の画素電極層118の周囲を覆うように隔壁119を形成する(図7(B)参照)。

【0116】

以上により、保護絶縁層114に設ける開口部の開口と半導体膜108の不要な領域の除去を同時に行うことでフォトリソグラフィ工程を削減した発光表示装置の作製方法を提供することができる。

【0117】

なお、本実施の形態は他の実施の形態と自由に組み合わせることができる。

【0118】

(実施の形態2)

本実施の形態では、実施の形態1と一部異なる工程例を図8を用いて説明する。なお、図8において、図4と同一の箇所には同じ符号を用い、同じ符号の詳細な説明はここでは省略する。

【0119】

まず、実施の形態1と同様に、絶縁表面を有する基板100上に導電膜を形成した後、第1のフォトリソグラフィ工程、及びエッチング工程によりゲート電極層142を形成する。

【0120】

基板100とゲート電極層との間には、下地膜となる絶縁膜を設けてもよく、本実施の形態では下地膜101を設ける。下地膜101は、基板100からの不純物元素(Naなど)の拡散を防止する機能があり、酸化シリコン、酸窒化シリコン、窒化シリコン、酸化ハフニウム、酸化アルミニウム、酸化ガリウム、酸化ガリウムアルミニウムから選ばれた膜で形成することができる。また、該下地膜は単層に限らず、上記の複数の膜の積層であっても良い。

【0121】

本実施の形態では、後に成膜する半導体膜の成膜温度が200℃以上450℃以下、半導体膜の成膜後の加熱処理の温度が200℃以上450℃以下であるため、ゲート電極層142の材料として、銅を下層とし、モリブデンを上層とする積層、または銅を下層とし、タングステンを上層とする積層を用いる。

【0122】

次いで、実施の形態1と同様に、ゲート電極層142上にゲート絶縁層106をCVD法やスパッタ法等を用いて形成する。ここまでの工程を経た断面図を図8(A)に示す。

【0123】

次いで、ゲート絶縁層106上に、1nm以上10nm以下の第1の酸化物半導体膜を形成する。本実施の形態では、酸化物半導体用ターゲット(In−Ga−Zn−O系酸化物半導体用ターゲット(In2O3:Ga2O3:ZnO=1:1:2[mol数比])を用いて、基板とターゲットの間との距離を170mm、基板温度250℃、圧力0.4Pa、直流(DC)電源0.5kW、酸素のみ、アルゴンのみ、又はアルゴン及び酸素雰囲気下で膜厚5nmの第1の酸化物半導体膜を成膜する。

【0124】

次いで、基板を配置する雰囲気を窒素、または乾燥空気とし、第1の加熱処理を行う。第1の加熱処理の温度は、200℃以上450℃以下とする。また、第1の加熱処理の加熱時間は1時間以上24時間以下とする。第1の加熱処理によって第1の結晶性酸化物半導体層148aを形成する(図8(B)参照)。

【0125】

次いで、第1の結晶性酸化物半導体層148a上に10nmよりも厚い第2の酸化物半導体膜を形成する。本実施の形態では、In−Ga−Zn−O系酸化物ターゲット(In2O3:Ga2O3:ZnO=1:1:2[mol数比])を用いて、基板と該ターゲットの間との距離を170mm、基板温度400℃、圧力0.4Pa、直流(DC)電源0.5kW、酸素のみ、アルゴンのみ、又はアルゴン及び酸素雰囲気下で膜厚25nmの第2の酸化物半導体膜を成膜する。

【0126】

次いで、基板を配置する雰囲気を窒素、または乾燥空気とし、第2の加熱処理を行う。第2の加熱処理の温度は、200℃以上450℃以下とする。また、第2の加熱処理の加熱時間は1時間以上24時間以下とする。第2の加熱処理によって第2の結晶性酸化物半導体層148bを形成する(図8(C)参照)。

【0127】

以降の工程は、実施の形態1に従って、第2の導電膜112や保護絶縁層114などを形成し、保護絶縁層114、第1の結晶性酸化物半導体層148a、及び第2の結晶性酸化物半導体層148bを同一のレジストマスクを用いてエッチングすることによって、フォトリソグラフィ工程を削減する。

【0128】

こうして、実施の形態1に従って図6(B)に示す第1のトランジスタ151、第2のトランジスタ152を含む構成を得ることができる。ただし、本実施の形態を用いた場合、これらのトランジスタのチャネル形成領域を含む半導体層は、第1の結晶性酸化物半導体層148a、及び第2の結晶性酸化物半導体層148bの積層となる。第1の結晶性酸化物半導体層148a、及び第2の結晶性酸化物半導体層148bは、C軸配向を有する結晶性酸化物半導体である。

【0129】

該結晶性酸化物半導体は、c軸配向し、かつab面、表面または界面の方向から見て三角形状または六角形状の原子配列を有し、c軸においては金属原子が層状または金属原子と酸素原子とが層状に配列しており、ab面においてはa軸またはb軸の向きが異なる(c軸を中心に回転した)結晶(CAAC:C Axis Aligned Crystalともいう。)を含む酸化物である。

【0130】

なお、CAACは、上記の第1の結晶性酸化物半導体層148a、及び第2の結晶性酸化物半導体層148bのような積層に限らず、単層でも形成することができる。

【0131】

なお、CAACを形成するには、下地となる層の表面の平坦性をCMP等で極力向上させ、平均粗さをシリコンの熱酸化膜と同等レベルまたはそれ以下とすることが好ましい。表面の平坦性の高い層上にCAACを形成することで、CAACを構成する結晶の結晶性及び連続性を高めることができる。

【0132】

また、成膜時においては、スパッタガス中の酸素比率を高めて成膜することが好ましい。例えば、スパッタガスにアルゴンと酸素を用いる場合は、酸素の流量比率を30%以上とすることでCAACを構成する結晶の結晶性を高めることができ、かつ膜中の酸素欠損への酸素の補填を行うことができる。また、150℃以上の高温で成膜することで、CAACを構成する結晶の結晶性を更に高めることができる。

【0133】

また、膜形成後の加熱処理においては、窒素雰囲気または減圧下で加熱処理した後、酸素雰囲気または窒素と酸素の混合雰囲気で加熱処理することによりCAAC中の酸素を過剰とし、効果的に酸素欠損を補填することができる。なお、該加熱処理の温度は、450℃程度であることが好ましい。

【0134】

CAACを含む酸化物とは、広義に、非単結晶であって、そのab面に垂直な方向から見て、三角形、六角形、正三角形または正六角形の原子配列を有し、かつc軸方向に垂直な方向から見て、金属原子が層状、または金属原子と酸素原子が層状に配列した相を含む酸化物をいう。

【0135】

CAACは単結晶ではないが、非晶質のみから形成されているものでもない。また、CAACは結晶化した部分(結晶部分)を含むが、1つの結晶部分と他の結晶部分の境界を明確に判別できないこともある。

【0136】

CAACに酸素が含まれる場合、酸素の一部は窒素で置換されてもよい。また、CAACを構成する個々の結晶部分のc軸は一定の方向(例えば、CAACを支持する基板面、CAACの表面などに垂直な方向)に揃っていてもよい。または、CAACを構成する個々の結晶部分のab面の法線は一定の方向(例えば、CAACを支持する基板面、CAACの表面などに垂直な方向)を向いていてもよい。

【0137】

CAACは、その組成などに応じて、導体であったり、半導体であったり、絶縁体であったりする。また、その組成などに応じて、可視光に対して透明であったり不透明であったりする。

【0138】

このようなCAACの例として、膜状に形成され、膜表面または支持する基板面に垂直な方向から観察すると三角形または六角形の原子配列が認められ、かつその膜断面を観察すると金属原子または金属原子および酸素原子(または窒素原子)の層状配列が認められる結晶を挙げることもできる。

【0139】

CAACに含まれる結晶構造の一例について図16乃至図18を用いて詳細に説明する。なお、特に断りがない限り、図16乃至図18は縦方向をc軸方向とし、c軸方向と直交する面をab面とする。なお、単に上半分、下半分という場合、ab面を境にした場合の上半分、下半分をいう。

【0140】

図16(A)に、1個の6配位のInと、Inに近接の6個の4配位の酸素原子(以下4配位のO)と、を有する構造を示す。ここでは、金属原子が1個に対して、近接の酸素原子のみ示した構造を小グループと呼ぶ。図16(A)の構造は、八面体構造をとるが、簡単のため平面構造で示している。なお、図16(A)の上半分および下半分にはそれぞれ3個ずつ4配位のOがある。図16(A)に示す小グループは電荷が0である。

【0141】

図16(B)に、1個の5配位のGaと、Gaに近接の3個の3配位の酸素原子(以下3配位のO)と、Gaに近接の2個の4配位のOと、を有する構造を示す。3配位のOは、いずれもab面に存在する。図16(B)の上半分および下半分にはそれぞれ1個ずつ4配位のOがある。また、Inも5配位をとるため、図16(B)に示す構造をとりうる。図16(B)に示す小グループは電荷が0である。

【0142】

図16(C)に、1個の4配位のZnと、Znに近接の4個の4配位のOと、を有する構造を示す。図16(C)の上半分には1個の4配位のOがあり、下半分には3個の4配位のOがある。または、図16(C)の上半分に3個の4配位のOがあり、下半分に1個の4配位のOがあってもよい。図16(C)に示す小グループは電荷が0である。

【0143】

図16(D)に、1個の6配位のSnと、Snに近接の6個の4配位のOと、を有する構造を示す。図16(D)の上半分には3個の4配位のOがあり、下半分には3個の4配位のOがある。図16(D)に示す小グループは電荷が+1となる。

【0144】

図16(E)に、2個のZnを含む小グループを示す。図16(E)の上半分には1個の4配位のOがあり、下半分には1個の4配位のOがある。図16(E)に示す小グループは電荷が−1となる。

【0145】

ここでは、複数の小グループの集合体を中グループと呼び、複数の中グループの集合体を大グループ(ユニットセルともいう。)と呼ぶ。

【0146】

ここで、これらの小グループ同士が結合する規則について説明する。図16(A)に示す6配位のInの上半分の3個のOは下方向にそれぞれ3個の近接Inを有し、下半分の3個のOは上方向にそれぞれ3個の近接Inを有する。5配位のGaの上半分の1個のOは下方向に1個の近接Gaを有し、下半分の1個のOは上方向に1個の近接Gaを有する。4配位のZnの上半分の1個のOは下方向に1個の近接Znを有し、下半分の3個のOは上方向に3個の近接Znを有する。この様に、金属原子の上方向の4配位のOの数と、そのOの下方向にある近接金属原子の数は等しく、同様に金属原子の下方向の4配位のOの数と、そのOの上方向にある近接金属原子の数は等しい。Oは4配位なので、下方向にある近接金属原子の数と、上方向にある近接金属原子の数の和は4になる。従って、金属原子の上方向にある4配位のOの数と、別の金属原子の下方向にある4配位のOの数との和が4個のとき、金属原子を有する二種の小グループ同士は結合することができる。例えば、6配位の金属原子(InまたはSn)が下半分の4配位のOを介して結合する場合、4配位のOが3個であるため、5配位の金属原子(GaまたはIn)または4配位の金属原子(Zn)のいずれかと結合することになる。

【0147】

これらの配位数を有する金属原子は、c軸方向において、4配位のOを介して結合する。また、このほかにも、層構造の合計の電荷が0となるように複数の小グループが結合して中グループを構成する。

【0148】

図17(A)に、In−Sn−Zn−O系の層構造を構成する中グループのモデル図を示す。図17(B)に、3つの中グループで構成される大グループを示す。なお、図17(C)は、図17(B)の層構造をc軸方向から観察した場合の原子配列を示す。

【0149】

図17(A)においては、簡単のため、3配位のOは省略し、4配位のOは個数のみ示し、例えば、Snの上半分および下半分にはそれぞれ3個ずつ4配位のOがあることを丸枠の3として示している。同様に、図17(A)において、Inの上半分および下半分にはそれぞれ1個ずつ4配位のOがあり、丸枠の1として示している。また、同様に、図17(A)において、下半分には1個の4配位のOがあり、上半分には3個の4配位のOがあるZnと、上半分には1個の4配位のOがあり、下半分には3個の4配位のOがあるZnとを示している。

【0150】

図17(A)において、In−Sn−Zn−O系の層構造を構成する中グループは、上から順に4配位のOが3個ずつ上半分および下半分にあるSnが、4配位のOが1個ずつ上半分および下半分にあるInと結合し、そのInが、上半分に3個の4配位のOがあるZnと結合し、そのZnの下半分の1個の4配位のOを介して4配位のOが3個ずつ上半分および下半分にあるInと結合し、そのInが、上半分に1個の4配位のOがあるZn2個からなる小グループと結合し、この小グループの下半分の1個の4配位のOを介して4配位のOが3個ずつ上半分および下半分にあるSnと結合している構成である。この中グループが複数結合して大グループを構成する。

【0151】

ここで、3配位のOおよび4配位のOの場合、結合1本当たりの電荷はそれぞれ−0.667、−0.5と考えることができる。例えば、In(6配位または5配位)、Zn(4配位)、Sn(5配位または6配位)の電荷は、それぞれ+3、+2、+4である。従って、Snを含む小グループは電荷が+1となる。そのため、Snを含む層構造を形成するためには、電荷+1を打ち消す電荷−1が必要となる。電荷−1をとる構造として、図16(E)に示すように、2個のZnを含む小グループが挙げられる。例えば、Snを含む小グループが1個に対し、2個のZnを含む小グループが1個あれば、電荷が打ち消されるため、層構造の合計の電荷を0とすることができる。

【0152】

具体的には、図17(B)に示した大グループが繰り返されることで、In−Sn−Zn−O系の結晶(In2SnZn3O8)を得ることができる。なお、得られるIn−Sn−Zn−O系の層構造は、In2SnZn2O7(ZnO)m(mは0または自然数。)とする組成式で表すことができる。

【0153】

また、このほかにも、四元系金属の酸化物であるIn−Sn−Ga−Zn−O系酸化物や、三元系金属の酸化物であるIn−Ga−Zn−O系酸化物(IGZOとも表記する。)、In−Al−Zn−O系酸化物、Sn−Ga−Zn−O系酸化物、Al−Ga−Zn−O系酸化物、Sn−Al−Zn−O系酸化物や、In−Hf−Zn−O系酸化物、In−La−Zn−O系酸化物、In−Ce−Zn−O系酸化物、In−Pr−Zn−O系酸化物、In−Nd−Zn−O系酸化物、In−Sm−Zn−O系酸化物、In−Eu−Zn−O系酸化物、In−Gd−Zn−O系酸化物、In−Tb−Zn−O系酸化物、In−Dy−Zn−O系酸化物、In−Ho−Zn−O系酸化物、In−Er−Zn−O系酸化物、In−Tm−Zn−O系酸化物、In−Yb−Zn−O系酸化物、In−Lu−Zn−O系酸化物や、二元系金属の酸化物であるIn−Zn−O系酸化物、Sn−Zn−O系酸化物、Al−Zn−O系酸化物、Zn−Mg−O系酸化物、Sn−Mg−O系酸化物、In−Mg−O系酸化物や、In−Ga−O系酸化物などを用いた場合も同様である。

【0154】

例えば、図18(A)に、In−Ga−Zn−O系の層構造を構成する中グループのモデル図を示す。

【0155】

図18(A)において、In−Ga−Zn−O系の層構造を構成する中グループは、上から順に4配位のOが3個ずつ上半分および下半分にあるInが、4配位のOが1個上半分にあるZnと結合し、そのZnの下半分の3個の4配位のOを介して、4配位のOが1個ずつ上半分および下半分にあるGaと結合し、そのGaの下半分の1個の4配位のOを介して、4配位のOが3個ずつ上半分および下半分にあるInと結合している構成である。この中グループが複数結合して大グループを構成する。

【0156】

図18(B)に3つの中グループで構成される大グループを示す。なお、図18(C)は、図18(B)の層構造をc軸方向から観察した場合の原子配列を示している。

【0157】

ここで、In(6配位または5配位)、Zn(4配位)、Ga(5配位)の電荷は、それぞれ+3、+2、+3であるため、In、ZnおよびGaのいずれかを含む小グループは、電荷が0となる。そのため、これらの小グループの組み合わせであれば中グループの合計の電荷は常に0となる。

【0158】

また、In−Ga−Zn−O系の層構造を構成する中グループは、図18(A)に示した中グループに限定されず、In、Ga、Znの配列が異なる中グループを組み合わせた大グループも取りうる。

【0159】

具体的には、図18(B)に示した大グループが繰り返されることで、In−Ga−Zn−O系の結晶を得ることができる。なお、得られるIn−Ga−Zn−O系の層構造は、InGaO3(ZnO)n(nは自然数。)とする組成式で表すことができる。

【0160】

n=1(InGaZnO4)の場合は、例えば、図19(A)に示す結晶構造を取りうる。なお、図19(A)に示す結晶構造において、図16(B)で説明したように、Ga及びInは5配位をとるため、GaがInに置き換わった構造も取りうる。

【0161】

また、n=2(InGaZn2O5)の場合は、例えば、図19(B)に示す結晶構造を取りうる。なお、図19(B)に示す結晶構造において、図16(B)で説明したように、Ga及びInは5配位をとるため、GaがInに置き換わった構造も取りうる。

【0162】

上述したようなCAACをトランジスタに用いることで、光照射及びバイアス−熱(BT)ストレス試験におけるトランジスタのしきい値電圧の変化を小さくすることができる。

【0163】

本実施の形態は、他の実施の形態と自由に組み合わせることができる。

【0164】

(実施の形態3)

本実施の形態では、本発明の一態様における発光表示装置の例を示す。表示装置の有する表示素子としては、ここではエレクトロルミネッセンスを利用する発光素子を用いて示す。エレクトロルミネッセンスを利用する発光素子は、発光材料が有機化合物であるか、無機化合物であるかによって区別され、一般的に、前者は有機EL素子、後者は無機EL素子と呼ばれている。

【0165】

有機EL素子は、発光素子に電圧を印加することにより、一対の電極から電子および正孔がそれぞれ発光性の有機化合物を含む層に注入され、電流が流れる。そして、それらキャリア(電子および正孔)が再結合することにより、発光性の有機化合物が励起状態を形成し、その励起状態が基底状態に戻る際に発光する。このようなメカニズムから、このような発光素子は、電流励起型の発光素子と呼ばれる。

【0166】

無機EL素子は、その素子構成により、分散型無機EL素子と薄膜型無機EL素子とに分類される。分散型無機EL素子は、発光材料の粒子をバインダ中に分散させた発光層を有するものであり、発光メカニズムはドナー準位とアクセプター準位を利用するドナー−アクセプター再結合型発光である。薄膜型無機EL素子は、発光層を誘電体層で挟み込み、さらにそれを電極で挟んだ構造であり、発光メカニズムは金属イオンの内殻電子遷移を利用する局在型発光である。なお、ここでは、発光素子として有機EL素子を用いて説明する。

【0167】

本実施の形態で説明する発光表示装置は、実施の形態1で説明した画素部の構成を有するものであり、基板100、第1のトランジスタ151、第2のトランジスタ152、保護絶縁層114、平坦化絶縁層116、隔壁119、及び発光素子に用いる第1の画素電極層118を有する(図1(A)、(B)参照)。また、第1の画素電極層118上にはEL層、第2の画素電極層を有する。

【0168】

本実施の形態では画素の第1のトランジスタ151、第2のトランジスタ152がnチャネル型であるので、第1の画素電極層118として、陰極を用いるのが望ましい。具体的には、陰極としては、仕事関数が小さい材料、例えば、Ca、Al、CaF、MgAg、AlLi等を用いることができる。

【0169】

隔壁119は、有機樹脂膜、無機絶縁膜または有機ポリシロキサンを用いて形成する。特に感光性の材料を用い、第1の画素電極層118上に開口部を形成し、その開口部の側壁が連続した曲率を持って形成される傾斜面となるように形成することが好ましい。

【0170】

なお、EL層は、単数の層で構成されていても、複数の層が積層されるように構成されていてもどちらでも良い。

【0171】

陽極となる第2の画素電極層は、EL層を覆うように形成する。第2の画素電極層には、酸化タングステンを含むインジウム酸化物、酸化タングステンを含むインジウム亜鉛酸化物、酸化チタンを含むインジウム酸化物、酸化チタンを含むインジウム錫酸化物、インジウム錫酸化物(以下、ITOと示す。)、インジウム亜鉛酸化物、酸化ケイ素を添加したインジウム錫酸化物などの透光性を有する導電性材料を用いることができる。また、1枚乃至10枚のグラフェンシート(グラファイトの1層分)よりなる材料を用いてもよい。また、上記透光性導電膜の他に、窒化チタン膜またはチタン膜を用いても良い。第1の画素電極層118とEL層と第2の画素電極層とが重なり合うことで、発光素子が形成される。この後、発光素子に酸素、水素、水分、二酸化炭素等が侵入しないように、第2の電極層及び隔壁119上に保護膜を形成してもよい。保護膜としては、窒化珪素膜、窒化酸化珪素膜、DLC膜等を形成することができる。

【0172】

さらに外気に曝されないように気密性が高く、脱ガスの少ない保護フィルム(貼り合わせフィルム、紫外線硬化樹脂フィルム等)やカバー材でパッケージング(封入)することが好ましい。

【0173】

次に、発光素子の構成について、図9(A)、(B)、(C)を用いて説明する。なお、図9(A)、(B)、(C)は、図1(A)のA2−A3の断面の構成にEL層及び第2の画素電極層等を加えて図示したものである。

【0174】

発光素子は発光を取り出すために少なくとも陽極又は陰極の一方が透明であればよい。そして、基板上にトランジスタ及び発光素子を形成し、基板とは逆側の面から発光を取り出す上面射出や、基板側の面から発光を取り出す下面射出や、基板側及び基板とは反対側の面から発光を取り出す両面射出構造の発光素子があり、本発明の一態様に係る画素構成はどの射出構造の発光素子にも適用することができる。

【0175】

上面射出構造の発光素子について図9(A)を用いて説明する。

【0176】