発光装置

【課題】高繊細化に伴う画素領域の微細化、大面積化に伴う基板の大型化によって、蒸着

時に用いるマスクの精度とたわみなどによる不良が問題となっている。

【解決手段】回折格子パターン或いは半透膜からなる光強度低減機能を有する補助パター

ンを設置したフォトマスクまたはレチクルを用いることにより、工程を増やすことなく、

表示領域における画素電極(第1の電極とも呼ぶ)上、及び画素電極層周辺に膜厚が異な

る部分を有する隔壁を形成する。

時に用いるマスクの精度とたわみなどによる不良が問題となっている。

【解決手段】回折格子パターン或いは半透膜からなる光強度低減機能を有する補助パター

ンを設置したフォトマスクまたはレチクルを用いることにより、工程を増やすことなく、

表示領域における画素電極(第1の電極とも呼ぶ)上、及び画素電極層周辺に膜厚が異な

る部分を有する隔壁を形成する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、一対の電極間に有機化合物を含む膜(以下、「有機化合物層」と記す)を設

けた素子に電界を加えることで、蛍光又は燐光が得られる発光素子を用いた発光装置及び

その作製方法に関する。なお、発光装置とは、画像表示デバイス、発光デバイス、もしく

は光源(照明装置含む)を指す。

【背景技術】

【0002】

薄型軽量、高速応答性、直流低電圧駆動などの特徴を有する有機化合物を発光体として用

いた発光素子は、次世代のフラットパネルディスプレイへの応用が期待されている。特に

、発光素子をマトリクス状に配置した表示装置は、従来の液晶表示装置と比較して、視野

角が広く視認性が優れる点に優位性があると考えられている。

【0003】

発光素子の発光機構は、一対の電極間に有機化合物層を挟んで電圧を印加することにより

、陰極から注入された電子および陽極から注入された正孔が有機化合物層中の発光中心で

再結合して分子励起子を形成し、その分子励起子が基底状態に戻る際にエネルギーを放出

して発光するといわれている。励起状態には一重項励起と三重項励起が知られ、発光はど

ちらの励起状態を経ても可能であると考えられている。

【0004】

このような発光素子をマトリクス状に配置して形成された発光装置には、パッシブマトリ

クス駆動(単純マトリクス型)とアクティブマトリクス駆動(アクティブマトリクス型)

といった駆動方法を用いることが可能である。しかし、画素密度が増えた場合には、画素

(又は1ドット)毎にスイッチが設けられているアクティブマトリクス型の方が低電圧駆

動できるので有利であると考えられている。

【0005】

アクティブマトリクス型の発光装置を作製する場合、絶縁表面を有する基板上にスイッチ

ング素子としてTFTを形成し、該TFTと電気的に接続する画素電極を陽極または陰極

としたEL素子をマトリクス状に配置する。

【0006】

また、アクティブマトリクス型の発光装置やパッシブマトリクス型の発光装置を作製する

場合、隣合う画素同士を絶縁するための隔壁を画素電極の端部に設ける。

【0007】

本出願人は、特許文献1や特許文献2に記載した隔壁を提案している。

【先行技術文献】

【特許文献】

【0008】

【特許文献1】特開2002−164181

【特許文献2】特開2004−127933

【発明の概要】

【発明が解決しようとする課題】

【0009】

エレクトロルミネセンス(以下、ELとも記す)素子を備える表示装置において、フルカ

ラー表示を行うため、カラー発光するカラー発光素子を用いる。カラー発光素子を形成す

るには、各色の発光材料を微細なパターンに電極上に形成することが重要な要素の一つと

なる。

【0010】

上記目的のため、蒸着法などを用いて材料を形成する際、マスクを用いて微細パターンに

形成する方法が一般的に用いられている。

【0011】

しかし、高繊細化に伴う画素領域の微細化、大面積化に伴う基板の大型化によって、蒸着

時に用いるマスクの精度とたわみなどによる不良が問題となっている。

【0012】

本発明は、工程を増やすことなく、蒸着時に用いるマスクの精度とたわみなどによる不良

を防ぐ構造を提供する。

【0013】

また、赤、緑、青の発光色を用いるフルカラーのフラットパネルディスプレイとして、

高精細化や高開口率化や高信頼性の要求が高まっている。こうした要求は、発光装置の高

精細化(画素数の増大)及び小型化に伴う各表示画素ピッチの微細化を進める上で大きな

課題となっている。アクティブマトリクス型発光装置またはパッシブマトリクス型発光装

置を高精細化するためには隔壁の上面形状も小さくして高精細化を可能にする必要がある

。本発明は、上面形状を縮小し、さらなる高精細な表示を可能とする隔壁およびその隔壁

を備えた発光装置を提供する。

【課題を解決するための手段】

【0014】

本発明は、回折格子パターン或いは半透膜からなる光強度低減機能を有する補助パターン

を設置したフォトマスクまたはレチクルを用いることにより、工程を増やすことなく、表

示領域における画素電極(第1の電極とも呼ぶ)上、及び画素電極層周辺に膜厚が異なる

部分を有する隔壁を形成する。

【0015】

本発明の隔壁は、膜厚の厚い部分で蒸着マスクを支持し、蒸着マスクのよじれや、たわ

みなどによって蒸着マスクが画素電極表面に接してしまうことを防止する。よって、画素

電極表面にはマスクによる傷などの損傷が生じず、画素電極は形状不良とならないので、

高繊細な表示を行うことが可能であり、且つ、高信頼性な表示装置を作製することができ

る。蒸着マスクが画素電極表面に接することを防止できるのであれば、膜厚の厚い部分の

領域を選択的に形成してもよい。即ち、複数の画素が配置される領域内に膜厚の厚い部分

を一箇所形成すればよい。

【0016】

また、本発明の隔壁における膜厚の薄い部分は、有機化合物を含む層を画素電極上に形

成する際、画素電極と隔壁との境界で被覆不良が発生することを抑えることができる。従

って、本発明の隔壁は、非常に膜厚の薄い有機化合物を含む層を形成する場合に特に有効

である。隔壁における膜厚の薄い部分は、膜厚の厚い部分の少なくとも半分以下の膜厚と

する。

【0017】

回折格子パターン或いは半透膜からなる光強度低減機能を有する補助パターンを設置した

フォトマスクまたはレチクルを調節すれば、膜厚の厚い部分の幅を細くすることは可能で

あり、膜厚の薄い部分の幅を含めたトータルの隔壁幅も20μm未満とすることができる

。また、隔壁の膜厚の厚い部分の幅を5μm程度にした場合に、蒸着の際、蒸着マスクか

ら圧力がかかっても、膜厚の薄い部分が膜厚の厚い部分を両側から支える形となっている

ため、強度も確保されている。

【0018】

本明細書で開示する発明の構成は、絶縁表面を有する基板上に複数の発光素子を有する発

光装置であり、発光素子は、第1の電極と、該第1の電極の端部を覆う隔壁と、前記第1

の電極上に有機化合物を含む層と、該有機化合物を含む層上に第2の電極とを有し、前記

隔壁は、発光素子上面から基板に向かって裾広がりの断面形状を有し、隔壁の側面に段差

を有していることを特徴とする発光装置である。

【0019】

また、上記構成において、前記隔壁の上端部は、丸みを有することを特徴の一つとして

いる。隔壁の上端部に丸みを有するとは、隔壁が、基板面に垂直な面で切断した場合にお

いて、隔壁の内部に位置する曲率中心により決まる曲面を有し、その曲率半径が0.2μ

m以上3μm以下であることを指している。隔壁の上端部が丸みを有するように形成する

には、隔壁を形成する際に隔壁の材料として感光性の樹脂を用いて選択的に露光を行うこ

とが好ましい。また、ウェットエッチングにより隔壁の上端部に丸みを形成してもよい。

また、隔壁の断面形状において、上端部と下端部との2箇所に隔壁の内部に位置する曲率

中心により決まる2つの曲面を有し、その2箇所の間には隔壁の外側に位置する曲率中心

により決まる1つの曲面も有している。

【0020】

また、上記構成において、前記裾広がりの断面形状を有している隔壁は単層であること

を特徴の一つとしている。積層構造ではないため、隔壁の作製工程が簡略である。

【0021】

また、上述した課題の解決手段とは、他の解決手段として、発光素子が配置される画素

部、即ち、表示領域の周りに蒸着マスクを支持する構造物を形成してもよい。本明細書で

は、ある発光素子と、その他の発光素子の間に形成される保護層を隔壁と呼ぶ。また、本

明細書では、画素部の中心から離れて配置された発光素子の外側に位置する絶縁物であり

、且つ、その絶縁物の外側に発光素子が配置されていない絶縁物を構造物と呼ぶ。表示領

域の面積が小さい場合には、表示領域の周りに蒸着マスクを支持する構造物を形成するこ

とによって、蒸着マスクのよじれやたわみなどによって画素電極表面に接してしまうこと

を防止することができる。

【0022】

本発明の他の構成は、絶縁表面を有する基板上に複数の発光素子を有する画素部を備え

た発光装置であり、発光素子は、第1の電極と、該第1の電極の端部を覆う隔壁と、前記

第1の電極上に有機化合物を含む層と、該有機化合物を含む層上に第2の電極とを有し、

前記隔壁と同じ材料である構造物が前記画素部を囲むように配置され、前記構造物の膜厚

と前記隔壁の膜厚は異なることを特徴とする発光装置である。

【0023】

また、上述した構造物を前述した裾広がりの断面形状を有する隔壁と同一材料を用いて同

一工程で形成することもでき、上記構成において、前記隔壁は、突出した部分を有してい

ることを特徴の一つとしている。また、前記隔壁は、発光素子上面から基板に向かって裾

広がりの断面形状を有し、隔壁の側面に段差を有している。

【0024】

また、対向する基板を用いて発光素子の封止を行う場合、前記構造物が一対の基板の間隔

を保持するようにしてもよい。上記構成において、前記発光装置は、前記絶縁表面を有す

る基板に対向する基板を有し、この一対の基板の間隔を前記構造物が保持することを特徴

の一つとしている。この構成は、特に、対向する基板として透光性基板を用い、発光素子

からの発光をその透光性基板を通過させて表示を行う場合に有効である。前記構造物によ

って一対の基板間隔を均一とすることができるため、高精細な表示が実現できる。

【0025】

また、上記構成において、前記構造物と、一対の基板とで囲まれる領域は樹脂で充填され

ることを特徴の一つとしている。この構成は、特に、対向する基板として透光性基板を用

い、発光素子からの発光をその透光性基板を通過させて表示を行う場合に有効である。ま

た、透明な樹脂を一対の基板間に充填することによって、一対の基板間を空間(不活性気

体)とした場合に比べて全体の透過率を向上させることができる。

【0026】

また、上述した構造物や上述した隔壁の他にも様々な構造物、例えば、封止基板と貼り合

わせる際に密着性を上げるための凸部などを同一材料を用いて同一工程で形成することも

できる。

【0027】

また、上記構造を実現するための発明の構成は、絶縁表面を有する基板上に第1の電極

を形成し、前記第1の電極の端部上に、回折格子パターン、或いは半透部を有するフォト

マスク又はレチクルを用いて、膜厚の厚い領域と、該領域より膜厚の薄い領域を有する隔

壁を形成し、前記第1の電極上に有機化合物を含む層を形成し、前記有機化合物を含む層

上に第2の電極を形成することを特徴とする発光装置の作製方法である。

【0028】

また、上記作製工程において、前記隔壁は、回折格子パターン、或いは半透部を有する

フォトマスク又はレチクルを用いて選択的に露光現像して形成した樹脂であることを特徴

の一つとしている。

【0029】

また、上記作製工程において、前記第1の電極上に有機化合物を含む層を形成する工程

は、蒸着法、具体的には蒸着マスクを用いた抵抗加熱法を用いた場合に隔壁の膜厚の厚い

領域が蒸着マスクのたわみなどを防ぐことが可能となるため有効である。また、有機化合

物を含む層は、蒸着法に限定されず、スピンコート法、インクジェット法、ディップ法、

電解重合法等が挙げられる。

【0030】

また、他の作製方法に関する発明の構成は、絶縁表面を有する基板上に複数の薄膜トラ

ンジスタおよび複数の発光素子を有する発光装置の作製方法であり、絶縁表面を有する第

1の基板上にソース領域、ドレイン領域、およびその間のチャネル形成領域を有する半導

体層と、ゲート絶縁膜と、ゲート電極とを有する薄膜トランジスタを形成し、前記ゲート

絶縁膜上方に前記ソース領域または前記ドレイン領域と電気的に接続する第1の電極を形

成し、前記第1の電極の端部を覆う隔壁と、複数の発光素子を囲む位置に構造物とを形成

し、前記第1の電極上に有機化合物を含む層を形成し、前記有機化合物を含む層上に第2

の電極を形成し、前記構造物で基板間隔を保つように、第2の基板を樹脂材料で前記第1

の基板に貼り合せて前記発光素子を封止することを特徴とする発光装置の作製方法である

。

【0031】

また、上記作製工程において、前記隔壁および前記構造物は、同一材料であり、回折格

子パターン、或いは半透部を有するフォトマスク又はレチクルを用いて選択的に露光現像

して形成した樹脂であることを特徴の一つとしている。前記構造物は、隔壁と同一工程で

形成することができるため、工程数を増やすことなく形成することができる。

【0032】

また、本発明は、スイッチング素子を有するアクティブマトリクス型の発光装置に限定

されず、パッシブ型の発光装置にも適用することができる。

【0033】

なお、本明細書中における発光装置とは、画像表示デバイス、発光デバイス、もしくは光

源(照明装置含む)を指す。また、発光装置にコネクター、例えばFPC(Flexib

le printed circuit)もしくはTAB(Tape Automate

d Bonding)テープもしくはTCP(Tape Carrier Packag

e)が取り付けられたモジュール、TABテープやTCPの先にプリント配線板が設けら

れたモジュール、または発光素子にCOG(Chip On Glass)方式によりI

C(集積回路)が直接実装されたモジュールも全て発光装置に含むものとする。

【発明の効果】

【0034】

本発明は、工程を増やすことなく、第1の電極端部を覆う隔壁や、画素部を囲む構造物を

設けることによって、蒸着時に用いるマスクの精度とたわみなどによる不良を防ぐことが

できる。

【0035】

また、本発明は、隔壁のサイズ、特に隔壁の占める平面面積を縮小し、サイズの小さな隔

壁およびその隔壁を備えた発光装置を実現できる。特に、この隔壁を用いて蒸着マスクと

第1の電極との間隔を近づければ近づけるほど、蒸着膜の回り込みが抑えられ、蒸着膜の

塗り分け精度を上げることができる。なお、蒸着膜の回り込みとは、蒸着マスクを用いて

蒸着を行う際、蒸着マスクの開口部分の面積よりも広い領域に蒸着膜が形成されてしまう

ことを指している。本発明により、発光装置の高精細化(画素数の増大)及び小型化に伴

う各表示画素ピッチの微細化を進めることができる。本発明の隔壁は、蒸着マスクと第1

の電極との間隔を近づけ、且つ、第1の電極と蒸着マスクの接触を確実に防止することが

できる。従って、さらに厚さが薄く設計された蒸着マスクを用いることも可能となる。

【図面の簡単な説明】

【0036】

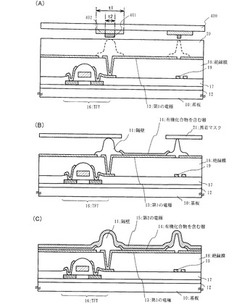

【図1】本発明の工程断面図を示す図。

【図2】蒸着装置の一例を示す図。

【図3】本発明の断面構造の一例を示す図。

【図4】本発明の断面構造の一例を示す図。

【図5】発光装置の作製工程を示す図。

【図6】発光装置の作製工程を示す図。

【図7】発光装置の作製工程を示す図。

【図8】発光装置の作製工程を示す図。

【図9】発光装置の作製工程を示す図。

【図10】アクティブマトリクス型発光装置の構成を示す図。

【図11】画素領域の上面図の一例

【図12】本発明が適用される電子機器を示す図。

【図13】本発明が適用される電子機器を示す図。

【図14】本発明が適用される電子機器を示す図。

【図15】本発明が適用される電子機器を示す図。

【図16】本発明の断面構造の一例を示す図。

【発明を実施するための形態】

【0037】

本発明の実施の形態について、図面を用いて詳細に説明する。但し、本発明は以下の説明

に限定されず、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々

に変更し得ることは当業者であれば容易に理解される。従って、本発明は以下に示す実施

の形態の記載内容に限定して解釈されるものではない。なお、以下に説明する本発明の構

成において、同一部分又は同様な機能を有する部分には同一の符号を異なる図面間で共通

して用い、その繰り返しの説明は省略する。

【0038】

(実施の形態1)

ここではアクティブマトリクス型発光装置の例を用いて本発明を説明する。

【0039】

また、図1(C)の構造を得るための作製工程の一例を以下に示す。

【0040】

まず、絶縁表面を有する基板10上にTFT16を作製する。TFT16の下地絶縁膜1

2およびゲート絶縁膜を含む絶縁膜の積層17としては、スパッタ法、またはPCVD法

により得られる無機材料(酸化シリコン、窒化シリコン、酸化窒化シリコン、SiOF膜

、SiONF膜など)を用いる。また、層間絶縁膜として機能する絶縁膜18は、スパッ

タ法、PCVD法、または塗布法により得られる無機材料(酸化シリコン、窒化シリコン

、酸化窒化シリコン、SiOF膜、SiONF膜など)、或いは塗布法により得られる感

光性または非感光性の有機材料(ポリイミド、アクリル、ポリアミド、ポリイミドアミド

、レジストまたはベンゾシクロブテン)、或いは塗布法により得られるSOG膜(シロキ

サン構造を有する絶縁膜)、またはこれらの積層などを適宜用いることができる。TFT

16は公知の方法でnチャネル型TFTまたはpチャネル型TFTを作製すればよい。

【0041】

次いで、絶縁膜18に対してエッチングを行ってTFTの電極に達する開口を形成した後

、陽極となる第1の電極13をTFTの電極と一部重なるように形成する。ここでは、第

1の電極13として、仕事関数の大きい導電膜(ITO(酸化インジウム酸化スズ合金)

、酸化インジウム酸化亜鉛合金(In2O3―ZnO)、酸化亜鉛(ZnO)等)を用い

、ウエットエッチングで形成する。第1の電極13を選択的にエッチングする際、絶縁膜

18と選択比が取れるようにエッチング条件または材料を適宜設定する。

【0042】

次いで、塗布法により絶縁膜を全面に形成した後、回折格子パターン或いは半透膜から

なる光強度低減機能を有する補助パターンを設置したフォトマスクまたはレチクルを用い

て隔壁11を形成する。隔壁11は、TFTの電極に達する開口と重なる位置に形成する

。隔壁11をTFTの電極に達する開口と重なる位置に形成すると隔壁と第1の電極との

密着性が向上するため好ましい。ここでは感光性の樹脂膜20を全面に形成した後、半透

膜からなる光強度低減機能を有する補助パターンを設置したフォトマスクを用いて露光し

た例を図1(A)に示す。

【0043】

図1(A)において、露光マスク400は、Crなどの金属膜からなる遮光部401と、

光強度低減機能を有する補助パターンとして、半透膜が設けられた部分(半透部とも呼ぶ

)402とが設置されている。露光マスクの断面図において、遮光部401の幅はt2と

示し、半透膜が設けられた部分402の幅はt1と示している。半透膜が設けられた部分

402において遮光部401と重なっている部分は、光は透過しない。ここでは露光マス

クの一部として半透膜を用いた例を示したが、回折格子パターンを用いてもよい。

【0044】

図1(A)に示す露光マスクを用いて感光性の樹脂膜20の露光を行うと、非露光領域と

露光領域が形成される。露光時には、光が遮光部401の回り込みや、半透膜が設けられ

た部分402を通過することによって図1(A)の点線に示す露光領域が形成される。そ

して、露光領域を除去すると裾広がりの断面形状を有する隔壁11が形成される。即ち、

図1(A)に示すように、隔壁11は、膜厚の厚い部分と、膜厚の薄い部分を有している

。隔壁における膜厚の薄い部分は、膜厚の厚い部分の少なくとも半分以下の膜厚とする。

ただし、膜厚の厚い部分とは、絶縁膜18の平坦な面から測定した膜厚の厚い部分を指し

ている。なお、隔壁11の高さ(即ち、膜厚の厚い部分の高さ)が2μm以上だと、カバ

レッジ不良が生じやすいので、隔壁11の高さは低い(2μm未満)ほうが好ましい。ま

た、図1(A)に示すように、TFTの電極に達する開口と重なる隔壁11とは幅の異な

る隔壁が配線19の上方に形成される。

【0045】

また、ここでは感光性の樹脂膜20を用いて形成する例を示したが、絶縁膜を全面に形

成した後、回折格子パターン或いは半透膜からなる光強度低減機能を有する補助パターン

を設置したフォトマスクまたはレチクルを用いてレジストマスクを形成し、レジストマス

クをマスクとしてエッチングを行って裾広がりの断面形状を有する隔壁11を形成しても

よい。

【0046】

次いで、有機化合物を含む層14を蒸着法で形成する。蒸着法で形成する場合には、図

1(B)に示すように蒸着マスク21を用いて選択的に有機化合物を含む層14を形成す

る。なお、図1(B)は、実際に蒸着を行う際とは上下方向を逆に示している。蒸着を行

う場合は、基板ホルダーと蒸着マスクの間に基板を挟み、基板ホルダーに設置された永久

磁石によってメタルからなる蒸着マスクを引きつけて基板を固定し、露呈している第1の

電極面の下方に蒸着源が位置するようにして蒸着が行われる。

【0047】

図1(B)では、有機化合物を含む層14は単層として示しているが、正孔注入層(また

は正孔輸送層)、発光層、電子注入層(または電子輸送層)などが積層された積層構造で

ある。なお、信頼性を向上させるため、有機化合物を含む層14の形成直前に真空加熱(

100℃〜250℃)を行って脱気を行うことが好ましい。例えば、蒸着法を用いる場合

、真空度が5×10−3Torr(0.665Pa)以下、好ましくは10−4〜10−

6Paまで真空排気された成膜室で蒸着を行う。蒸着の際、予め、抵抗加熱により有機化

合物は気化されており、蒸着時にシャッターが開くことにより基板の方向へ飛散する。気

化された有機化合物は、上方に飛散し、蒸着マスクに設けられた開口部を通って基板に蒸

着される。

【0048】

図2に蒸着装置の一例を示す。

【0049】

図2(A)に示す蒸着装置は、成膜室に蒸着材料の昇華方向を維持するために防着シール

ドが設けられており、開口部が複数設けられ、それらの開口部から蒸着材料が昇華する機

構となっている。防着シールドの下方には、基板の移動方向(搬送方向とも呼ぶ)とは垂

直な方向に移動可能な蒸着源を有している。また、防着シールドの幅Wbは、基板の幅W

aよりも広くさせて、蒸着膜の膜厚均一性を向上させている。以下に蒸着装置の機構を簡

略に示す。

【0050】

基板701は、予め蒸着マスク702と位置合わせされており、位置合わせされたまま基

板の搬送方向706a(図2(A)中の矢印の方向)に基板が搬送される。基板は搬送さ

れて、防着シールド703aの上方を通過する。防着シールド703aは開口部703b

を有しており、蒸着源704からの蒸着材料が開口部703bから昇華するようになって

いる。開口部703bから蒸着材料の昇華方向706bを維持するために防着シールド7

03aは、防着シールド自体には付着しないように加熱されている。また、蒸着シールド

に接してヒーターが設けられている。蒸着シールドの加熱温度はヒーターと接続している

コンピュータで制御しても良い。

【0051】

蒸着源704は複数のルツボが設置できるようになっており、さらに矢印の方向(蒸着源

の移動方向705)に移動することが可能である。なお、蒸着源は移動させる代わりに、

蒸着源の向きを変えて蒸着される角度を変えても良い。蒸着方法は、抵抗加熱法を用いる

。また、蒸着源が移動する範囲は基板の幅Waよりも広いことが望ましい。また、防着シ

ールドの幅Wbも基板の幅Waよりも広くすることが蒸着膜の膜厚均一性を向上させる。

【0052】

なお、図2(A)の蒸着装置において、開口部703bの形状や数は特に限定されない

。

【0053】

また、蒸着源のルツボに蒸着材料を補給するため、成膜室にゲートを介して連結する設

置室を設けてもよい。蒸着源にはルツボを加熱するヒーターが設けられている。また、一

つの成膜室に複数の蒸着源と防着シールドを設けてもよい。複数のルツボを設けた一つの

蒸着源を設け、設置室を設けた場合の蒸着装置の上面図を図2(B)に示す。蒸着源の移

動方向705に設置室707を設置し、蒸着材料を補給する際には、蒸着源を設置室まで

移動させて補給を行えばよい。蒸着源が成膜室に固定されている場合には、蒸着源に蒸着

材料を補給するためには成膜室内を大気圧としなければならず、再度蒸着するためには成

膜室内を真空にするのに時間を要してしまう。設置室707を設ければ、成膜室700の

真空度を維持したまま、設置室内のみを大気圧と真空とに切り替えればよいため、短時間

で蒸着材料の補給が可能となる。

【0054】

また、ここでは一つの成膜室に一つの蒸着源を設けた例を示したが、一つの成膜室に2以

上の数の蒸着源を設けてもよい。

【0055】

また、蒸着の際、隔壁11の膜厚の厚い部分、即ち頂部は、蒸着マスクと接して間隔を保

持する機能を有している。また、隔壁11が第1の電極を囲むように配置されている場合

、マスクの下方において開口が設けられていない領域、例えば隣の画素への蒸着を防ぐこ

とができる。なお、隔壁11は、各第1の電極の端部を覆い、絶縁膜18上に接して形成

され、且つ、第1の電極が隣り合う電極と絶縁し、短絡するのを防止している。また、隔

壁11の膜厚の厚い部分、即ち頂部は、TFTの電極に達する開口と重なる位置と重なる

。

【0056】

この隔壁11の幅が大きいと、開口率が低下するため、できるだけ隔壁の上面形状を小さ

くして開口率向上、且つ、高精細化を図ることが好ましい。また、有機化合物を含む層1

4を隔壁11における膜厚の薄い部分とも一部重ねることで、隔壁の下方に形成されてい

る第1の電極と、後に形成する第2の電極とが短絡することをより効果的に防ぐことがで

きる。即ち、有機化合物を含む層14のうち、隔壁11と重なる部分、即ち発光に寄与し

ない部分は、隔壁の一部としても機能する。

【0057】

次いで、有機化合物を含む層14上に陰極となる第2の電極15を形成する。第2の電

極15を形成する際にも蒸着マスクを用いるが、蒸着マスクの開口部分と対応する箇所が

画素部全域である場合、画素部以外に形成した構造物が蒸着マスクとの間隔を保持する。

【0058】

以上の工程で図1(C)に示す構造を得ることができる。また、有機化合物を含む層14

や第2の電極15の成膜方法は、TFT16にダメージを与えない抵抗加熱法が好ましく

、塗布法(インクジェット法やスピンコート法など)も用いることができる。また、有機

化合物を含む層14は、塗布法で形成した膜と蒸着法による膜と積層してもよく、例えば

、正孔注入層として作用するポリ(エチレンジオキシチオフェン)/ポリ(スチレンスル

ホン酸)水溶液(PEDOT/PSS)、或いはポリアニリン/ショウノウスルホン酸水

溶液(PANI/CSA)、PTPDES、Et−PTPDEK、またはPPBAなどを

スピンコート法で塗布、焼成した後、蒸着法により発光層、電子輸送層などを積層しても

よい。

【0059】

図1(C)において、10は基板、11は隔壁、12は下地絶縁膜、13は第1の電極、

14は有機化合物を含む層、15は第2の電極、16はTFT、17はゲート絶縁膜を含

む絶縁膜の積層、18は絶縁膜、19は電源供給線などの配線である。なお、図1(C)

では第1の電極13は発光素子の陽極として機能させ、第2の電極は発光素子の陰極とし

て機能させているが、特に限定されず、材料を適宜選択すれば第1の電極を陰極として機

能させ、第2の電極を陽極として機能させることも可能である。

【0060】

また、本発明は図1(A)のTFT構造に限定されず、必要があればチャネル形成領域

とドレイン領域(またはソース領域)との間にLDD領域を有する低濃度ドレイン(LD

D:Lightly Doped Drain)構造としてもよい。この構造はチャネル

形成領域と、高濃度に不純物元素を添加して形成するソース領域またはドレイン領域との

間に低濃度に不純物元素を添加した領域を設けたものであり、この領域をLDD領域と呼

んでいる。さらにゲート絶縁膜を介してLDD領域をゲート電極と重ねて配置させた、い

わゆるGOLD(Gate−drain Overlapped LDD)構造としても

よい。

【0061】

また、ここではnチャネル型TFTを用いて説明したが、n型不純物元素に代えてp型

不純物元素を用いることによってpチャネル型TFTを形成することができることは言う

までもない。

【0062】

また、ここでは、トップゲート型TFTを用いて一例を説明したが、TFT構造に関係な

く本発明を適用することが可能であり、例えばボトムゲート型(逆スタガ型)TFTや順

スタガ型TFTに適用することが可能である。

【0063】

また、本明細書において、TFTの活性層となる半導体層は、珪素を主成分とする半導

体膜、有機材料を主成分とする半導体膜、或いは金属酸化物を主成分とする半導体膜を用

いることができる。珪素を主成分とする半導体膜としては、非晶質半導体膜、結晶構造を

含む半導体膜、非晶質構造を含む化合物半導体膜などを用いることができる。具体的には

珪素を主成分とする半導体膜としてアモルファスシリコン、微結晶シリコン、多結晶シリ

コンなどを用いることができる。また、有機材料を主成分とする半導体膜としては、他の

元素と組み合わせて一定量の炭素または炭素の同素体(ダイヤモンドを除く)からなる物

質を主成分とする半導体膜を用いることができる。具体的には、ペンタセン、テトラセン

、チオフェンオリゴマ誘導体、フェニレン誘導体、フタロシアニン化合物、ポリアセチレ

ン誘導体、ポリチオフェン誘導体、シアニン色素等が挙げられる。また、金属酸化物を主

成分とする半導体膜としては、酸化亜鉛(ZnO)や亜鉛とガリウムとインジウムの酸化

物(In−Ga−Zn−O)等を用いることができる。

【0064】

(実施の形態2)

本実施の形態では、本実施の形態1とは構造が一部異なる例を図3に示す。

【0065】

ここでは、図1の層間絶縁膜を1層減らした構造、具体的には図1に示す絶縁膜18を

形成しない構造を示す。なお、図3において図1と同じ箇所には同じ符号を用いる。

【0066】

実施の形態1と同様にして絶縁表面を有する基板10上にTFT16を作製する。次い

で、ゲート絶縁膜を含む絶縁膜の積層17上に陽極となる第1の電極33を形成する。第

1の電極33は、ゲート絶縁膜を含む絶縁膜の積層17上に、TFTのソース領域または

ドレイン領域と電気的に接続する電極と一部接して重なるように形成される。

【0067】

次いで、塗布法により絶縁膜を全面に形成した後、回折格子パターン或いは半透膜から

なる光強度低減機能を有する補助パターンを設置したフォトマスクまたはレチクルを用い

て隔壁31を形成する。隔壁31は、膜厚の厚い部分と、膜厚の薄い部分を有している。

また、隔壁31は、ゲート絶縁膜を含む絶縁膜の積層17上に接して設けられ、電源供給

線などの配線19と接した状態で覆う。

【0068】

次いで、有機化合物を含む層34を蒸着法で形成する。また、図1において、有機化合

物を含む層14は、隔壁11における膜厚の薄い部分と一部重なる例を示したが、図3で

は、有機化合物を含む層34は、隔壁31における厚い部分とも重なる例を示している。

図3で示すように有機化合物を含む層34が隔壁31における厚い部分とも重なるのは、

基板面と垂直な面で切断した断面において、蒸着マスクの遮蔽部分の幅が隔壁31の膜厚

の厚い部分の幅よりも狭いものを用いているためである。本発明において蒸着マスクの遮

蔽部分の幅が隔壁の幅より狭くてもよいし、同じでもよいし、広くてもよい。また、有機

化合物を含む層34を隔壁31における膜厚の厚い部分とも一部重ねることで、隔壁の下

方に形成されているTFTと、後に形成する第2の電極とが短絡することを効果的に防ぐ

ことができる。

【0069】

次いで、有機化合物を含む層34上に陰極となる第2の電極15を形成する。

【0070】

以上の工程で図3に示す構造を得ることができる。

【0071】

このように、図3に示す構造は、図1に比べて少ない工程数で発光装置を作製することが

できる。

【0072】

本実施の形態は、実施の形態1と自由に組み合わせることができる。

【0073】

(実施の形態3)

本実施の形態では、複数の発光素子が配置された画素部(表示領域とも呼ぶ)に設ける隔

壁と、画素部の周りを囲むように配置する構造物とを設ける例を示す。

【0074】

ここでは、図4(A)及び図4(B)を用いて、パッシブマトリクス型の発光装置を作製

する例を示す。

【0075】

第1の基板301上に、第1の電極303が形成され、その端部を覆うように隔壁30

2が形成される。また、隔壁302と同一工程で構造物304が形成される。隔壁302

と構造物304は膜厚が異なる。この段階での断面図を図4(A)に示す。

【0076】

次いで、第1の電極303上に有機化合物を含む層305を形成し、その上に第2の電

極307を形成する。なお、有機化合物を含む層305を蒸着法で形成する際、構造物3

04は、蒸着マスクと第1の電極303とが接触しないように防止することができる。ま

た、蒸着マスクと隔壁302とが接触しないように防止することもできる。

【0077】

そして、第2の基板308と第1の基板301とを接着層309で貼り合わせて封止す

る。

【0078】

図4(B)に示すように、第1の基板301上に画素部306の周りを囲むように配置す

る構造物304は、第2の基板308を用いて封止する場合、一対の基板間隔を保持する

ことができる。また、構造物と一対の基板とで囲まれた領域を密閉して画素部を封止する

こともできる。即ち、構造物304は、外部からの不純物や水分の侵入を防止することが

できる。

【0079】

隔壁302と構造物304は、回折格子パターン、或いは半透部を有するフォトマスク又

はレチクルを用いて同じ工程で形成する。

【0080】

また、アクティブマトリクス型の発光装置を作製する場合には、同様に複数の発光素子が

配置された画素部(表示領域とも呼ぶ)に設ける隔壁と、画素部の周りを囲むように配置

する構造物とを形成すればよい。

【0081】

アクティブマトリクス型の発光装置を作製する場合は、画素に配置するTFTと同一工程

で駆動回路の一部をTFTで形成することもできる。その場合、画素部の周りに駆動回路

を配置することになる。また、その駆動回路と重なる位置に構造物を形成してもよい。

【0082】

本実施の形態は、実施の形態1または実施の形態2と自由に組み合わせることができる

。

【0083】

例えば、隔壁を裾状として、隔壁の一部を構造物と同じ膜厚とすることで、隔壁と構造

物との両方で一対の基板間隔を保持することができる。一つの画素を囲むような上面形状

を有する隔壁を設ける場合、第2基板と隔壁とで一つの画素を密閉して封止することがで

き、その周りを構造物でさらに密閉して封止することができる。このように二重に密閉す

ることで高信頼性を有する発光装置を実現することができる。また、発光装置が外部から

の衝撃を受けた場合、一対の基板が隔壁と構造物とで支えられているため、衝撃の力を分

散することができる。従って、丈夫な発光装置を提供することができる。

【0084】

(実施の形態4)

本実施の形態は、TFTを作製し、感光性の樹脂膜を全面に形成した後、半透膜からな

る光強度低減機能を有する補助パターンを設置したフォトマスクを用いて隔壁を形成し、

発光装置を完成させるまでの工程について以下に示す。

【0085】

まず、絶縁表面を有する基板100の上に下地膜として、スパッタリング法、PVD法

(Physical Vapor Deposition)、減圧CVD法(LPCVD

法)、またはプラズマCVD法等のCVD法(Chemical Vapor Depo

sition)などにより窒化酸化珪素膜(SiNO)を用いて下地膜101aを10〜

200nm(好ましくは50〜100nm)形成し、酸化窒化珪素膜(SiON)を用い

て下地膜101bを50〜200nm(好ましくは100〜150nm)積層する。本実

施の形態では、プラズマCVD法を用いて下地膜101a、下地膜101bを形成する。

基板100としてはガラス基板、石英基板やシリコン基板、金属基板、またはステンレス

基板の表面に絶縁膜を形成したものを用いて良い。また、本実施の形態の処理温度に耐え

うる耐熱性を有するプラスチック基板を用いてもよいし、フィルムのような可撓性基板を

用いても良い。プラスチック基板としてはPET(ポリエチレンテレフタレート)、PE

N(ポリエチレンナフタレート)、PES(ポリエーテルスルホン)からなる基板、可撓

性基板としてはアクリル等の合成樹脂を用いることができる。

【0086】

下地膜としては、酸化珪素、窒化珪素、酸化窒化珪素、窒化酸化珪素などを用いることが

でき、単層でも2層、3層といった積層構造でもよい。なお本明細書中において酸化窒化

珪素とは酸素の組成比が窒素の組成比より大きい物質であり、窒素を含む酸化珪素とも言

える。同様に、窒化酸化珪素とは、窒素の組成比が酸素の組成比より大きい物質であり、

酸素を含む窒化珪素とも言える。本実施の形態では、基板上にSiH4、NH3、N2O

、N2及びH2を反応ガスとして窒化酸化珪素膜を膜厚50nm形成し、SiH4及びN

2Oを反応ガスとして酸化窒化珪素膜を膜厚100nmで形成する。また窒化酸化珪素膜

の膜厚を140nm、積層する酸化窒化珪素膜の膜厚を100nmとしてもよい。

【0087】

次いで、下地膜上に半導体膜を形成する。半導体膜は25〜200nm(好ましくは

30〜150nm)の厚さで公知の手段(スパッタ法、LPCVD法、またはプラズマC

VD法等)により成膜すればよい。本実施の形態では、非晶質半導体膜を、レーザ結晶化

し、結晶性半導体膜とするものを用いるのが好ましい。結晶性半導体膜を用いる場合、そ

の結晶性半導体膜の作製方法は、公知の方法(レーザ結晶化法、熱結晶化法、またはニッ

ケルなどの結晶化を助長する元素を用いた熱結晶化法等)を用いれば良い。

【0088】

連続発振が可能な固体レーザを用い、基本波の第2高調波〜第4高調波のレーザ光を照射

することで、大粒径の結晶を得ることができる。例えば、代表的には、Nd:YVO4レ

ーザ(基本波1064nm)の第2高調波(532nm)や第3高調波(355nm)を

用いるのが望ましい。具体的には、連続発振のYVO4レーザから射出されたレーザ光を

非線形光学素子により高調波に変換し、出力数W以上のレーザ光を得る。そして、好まし

くは光学系により照射面にて矩形状または楕円形状のレーザ光に成形して、半導体膜に照

射する。このときのパワー密度は0.001〜100MW/cm2程度(好ましくは0.

1〜10MW/cm2)が必要である。そして、走査速度を0.5〜2000cm/se

c程度(好ましくは10〜200cm/sec)とし、照射する。

【0089】

レーザのビーム形状は、線状とすると好ましい。その結果、スループットを向上させ

ることができる。またさらにレーザは、半導体膜に対して入射角θ(0<θ<90度)を

持たせて照射させるとよい。レーザの干渉を防止することができるからである。

【0090】

このようなレーザと、半導体膜とを相対的に走査することにより、レーザ照射を行う

ことができる。またレーザ照射において、ビームを精度よく重ね合わせたり、レーザ照射

開始位置やレーザ照射終了位置を制御するため、マーカーを形成することもできる。マー

カーは非晶質半導体膜と同時に、基板上へ形成すればよい。

【0091】

なおレーザは、連続発振またはパルス発振の気体レーザ、固体レーザ、銅蒸気レーザ

または金蒸気レーザなどを用いることができる。気体レーザとして、エキシマレーザ、A

rレーザ、Krレーザ、He−Cdレーザなどがあり、固体レーザとして、YAGレーザ

、YVO4レーザ、YLFレーザ、YAlO3レーザ、Y2O3レーザ、ガラスレーザ、

ルビーレーザ、アレキサンドライトレーザ、Ti:サファイアレーザなどが挙げられる。

【0092】

半導体膜を形成する材料は、シランやゲルマンに代表される半導体材料ガスを用いて気相

成長法やスパッタリング法で作製される非晶質半導体(以下「アモルファス半導体:AS

」ともいう。)、該非晶質半導体を光エネルギーや熱エネルギーを利用して結晶化させた

多結晶半導体、或いはセミアモルファス(微結晶若しくはマイクロクリスタルとも呼ばれ

る。以下「SAS」ともいう。)半導体などを用いることができる。

【0093】

また、パルス発振のレーザ光の発振周波数を0.5MHz以上とし、通常用いられて

いる数十Hz〜数百Hzの周波数帯よりも著しく高い周波数帯を用いてレーザ結晶化を行

っても良い。パルス発振でレーザ光を半導体膜に照射してから半導体膜が完全に固化する

までの時間は数十nsec〜数百nsecと言われている。よって上記周波数帯を用いる

ことで、半導体膜がレーザ光によって溶融してから固化するまでに、次のパルスのレーザ

光を照射できる。したがって、半導体膜中において固液界面を連続的に移動させることが

できるので、走査方向に向かって連続的に成長した結晶粒を有する半導体膜が形成される

。具体的には、含まれる結晶粒の走査方向における幅が10〜30μm、走査方向に対し

て垂直な方向における幅が1〜5μm程度の結晶粒の集合を形成することができる。該走

査方向に沿って長く延びた単結晶の結晶粒を形成することで、少なくとも薄膜トランジス

タのチャネル方向には結晶粒界のほとんど存在しない半導体膜の形成が可能となる。

【0094】

また、希ガスや窒素などの不活性ガス雰囲気中でレーザ光を照射するようにしても良い。

これにより、レーザ光の照射による半導体表面の荒れを抑えることができ、界面準位密度

のばらつきによって生じるしきい値のばらつきを抑えることができる。

【0095】

非晶質半導体膜の結晶化は、熱処理とレーザ光照射による結晶化を組み合わせてもよく、

熱処理やレーザ光照射を単独で、複数回行っても良い。

【0096】

本実施の形態では、下地膜101b上に、非晶質半導体膜を形成し、非晶質半導体膜を結

晶化させることによって結晶性半導体膜を形成する。非晶質半導体膜としては、SiH4

、H2の反応ガスにより形成する非晶質珪素を用いる。本実施の形態において、下地膜1

01a、下地膜101b、非晶質半導体膜は、同チャンバー内で真空を維持したままで3

30℃の同一温度下で、反応ガスを切り変えながら連続的に形成する。次いで、非晶質半

導体膜にレーザー光を照射、具体的には、レーザの繰り返し周波数が10MHz以上のレ

ーザ発振器から射出した基本波を用いて結晶性半導体膜を形成する。この時のレーザ光の

尖頭出力の範囲は、1GW/cm2〜1TW/cm2とする。ここまでの断面図を図5(

A)に示す。

【0097】

このようにして得られた結晶性半導体膜に対して、薄膜トランジスタのしきい値電圧を制

御するために微量な不純物元素(ボロンまたはリン)のドーピングを行ってもよい。この

不純物元素のドーピングは、結晶化工程の前の非晶質半導体膜に行ってもよい。非晶質半

導体膜の状態で不純物元素をドーピングすると、その後の結晶化のための加熱処理によっ

て、不純物の活性化も行うことができる。また、ドーピングの際に生じる欠陥等も改善す

ることができる。

【0098】

次に結晶性半導体膜102をマスクを用いて選択的にエッチングする。本実施の形態では

結晶性半導体膜102上に形成された酸化膜を除去した後、新たに酸化膜を形成する。そ

して、フォトマスクを作製し、フォトリソグラフィ法を用いたパターニング処理により、

半導体層103、半導体層104、半導体層105、及び半導体層106を形成する。

【0099】

次いで、半導体層上の酸化膜を除去し、半導体層103、半導体層104、半導体層10

5、及び半導体層106を覆うゲート絶縁層107を形成する。

【0100】

ゲート絶縁層107はプラズマCVD法またはスパッタ法などを用い、厚さを10〜15

0nmとして珪素を含む絶縁膜で形成する。ゲート絶縁層107としては、窒化珪素、酸

化珪素、酸化窒化珪素、窒化酸化珪素に代表される珪素の酸化物材料又は窒化物材料等の

公知の材料で形成すればよく、積層でも単層でもよい。本実施の形態では、ゲート絶縁層

は窒化珪素膜、酸化珪素膜、窒化珪素膜の3層の積層を用いる。またそれらや、酸化窒化

珪素膜の単層、2層からなる積層でも良い。好適には、緻密な膜質を有する窒化珪素膜を

用いるとよい。さらに半導体層とゲート絶縁層の間に、膜厚1〜100nm、好ましくは

1〜10nm、さらに好ましくは2〜5nmである膜厚の薄い酸化珪素膜を形成してもよ

い。薄い酸化珪素膜の形成方法としては、GRTA法、LRTA法等を用いて半導体領域

表面を酸化し、熱酸化膜を形成することで、膜厚の薄い酸化珪素膜を形成することができ

る。

【0101】

次いで、ゲート絶縁層107上にゲート電極層として用いる膜厚20〜100nmの第1

の導電膜108と、膜厚100〜400nmの第2の導電膜109とを積層して形成する

(図5(B)参照。)。

【0102】

第1の導電膜108及び第2の導電膜109は、スパッタリング法、蒸着法、CVD法等

の公知の手法により形成することができる。第1の導電膜108及び第2の導電膜109

はタンタル(Ta)、タングステン(W)、チタン(Ti)、モリブデン(Mo)、アル

ミニウム(Al)、銅(Cu)、クロム(Cr)、ネオジウム(Nd)から選ばれた元素

、又は前記元素を主成分とする合金材料もしくは化合物材料で形成すればよい。また、第

1の導電膜108及び第2の導電膜109としてリン等の不純物元素をドーピングした多

結晶シリコン膜に代表される半導体膜や、AgPdCu合金を用いてもよい。また、2層

構造に限定されず、例えば、第1の導電膜として膜厚50nmのタングステン膜、第2の

導電膜として膜厚500nmのアルミニウムとシリコンの合金(Al−Si)膜、第3の

導電膜として膜厚30nmの窒化チタン膜を順次積層した3層構造としてもよい。また、

3層構造とする場合、第1の導電膜のタングステンに代えて窒化タングステンを用いても

よいし、第2の導電膜のアルミニウムとシリコンの合金(Al−Si)膜に代えてアルミ

ニウムとチタンの合金膜(Al−Ti)を用いてもよいし、第3の導電膜の窒化チタン膜

に代えてチタン膜を用いてもよい。また、単層構造であってもよい。本実施の形態では、

第1の導電膜108として窒化タンタル(TaN)を膜厚30nm形成し、第2の導電膜

109としてタングステン(W)を膜厚370nm形成する。

【0103】

次いで、回折格子パターン或いは半透膜からなる光強度低減機能を有する補助パターン

を設置したフォトマスクまたはレチクルを用いてレジストマスクを形成し、第1の導電膜

108及び第2の導電膜109を選択的にエッチングし、第1のゲート電極層、導電層、

及び第2のゲート電極層をテーパー形状を有する様に形成する。レジストマスクは、膜厚

の厚い部分と膜厚の薄い部分を有し、後にチャネル形成領域が形成される部分とレジスト

マスクの膜厚の厚い部分とが重なる位置になるように形成する。そして、断面形状が裾状

の電極または配線が得られた後、レジストマスクを除去する。

【0104】

以上の工程によって、周辺駆動回路領域204に第1のゲート電極層121及び第2のゲ

ート電極層131からなるゲート電極層117、第1のゲート電極層122及び第2のゲ

ート電極層132からなるゲート電極層118、画素領域206に第1のゲート電極層1

24及び第2のゲート電極層134からなるゲート電極層127、第1のゲート電極層1

25及び第2のゲート電極層135からなるゲート電極層128、第1のゲート電極層1

26及び第2のゲート電極層136からなるゲート電極層129、接続領域205に導電

層123及び導電層133からなる導電層130を形成することができる(図5(C)参

照。)。本実施の形態では、ゲート電極層の形成をドライエッチングで行うがウェットエ

ッチングでもよい。

【0105】

なお、ゲート電極層を形成する際のエッチング工程によって、ゲート絶縁層107は多少

エッチングされ、膜厚が減る(いわゆる膜減り)ことがある。

【0106】

次に、ゲート電極層117、ゲート電極層118、ゲート電極層127、ゲート電極層1

28、ゲート電極層129、導電層130をマスクとして、n型を付与する不純物元素1

51を添加し、第1のn型不純物領域140a、第1のn型不純物領域140b、第1の

n型不純物領域141a、第1のn型不純物領域141b、第1のn型不純物領域142

a、第1のn型不純物領域142b、第1のn型不純物領域142c、第1のn型不純物

領域143a、第1のn型不純物領域143bを形成する(図6(A)参照。)。ここで

は、、不純物元素を含むドーピングガスとしてホスフィン(PH3)を用いて、第1のn

型不純物領域140a、第1のn型不純物領域140b、第1のn型不純物領域141a

、第1のn型不純物領域141b、第1のn型不純物領域142a、第1のn型不純物領

域142b、第1のn型不純物領域142c、第1のn型不純物領域143a、第1のn

型不純物領域143bに、n型を付与する不純物元素が1×1017〜5×1018/c

m3程度の濃度で含まれるように添加する。

【0107】

次に半導体層103、半導体層105の一部、半導体層106を覆うマスク153a

、マスク153b、マスク153c、及びマスク153dを形成する。マスク153a、

マスク153b、マスク153c、マスク153d、第2のゲート電極層132をマスク

としてn型を付与する不純物元素152を添加し、第2のn型不純物領域144a、第2

のn型不純物領域144b、第3のn型不純物領域145a、第3のn型不純物領域14

5b、第2のn型不純物領域147a、第2のn型不純物領域147b、第2のn型不純

物領域147c、第3のn型不純物領域148a、第3のn型不純物領域148b、第3

のn型不純物領域148c、第3のn型不純物領域148dが形成される(図6(B)参

照。)。ここでは、第2のn型不純物領域144a、第2のn型不純物領域144bにn

型を付与する不純物元素が5×1019〜5×1020/cm3程度の濃度で含まれるよ

うに添加する。第3のn型不純物領域145a、第3のn型不純物領域145bは、第3

のn型不純物領域148a、第3のn型不純物領域148b、第3のn型不純物領域14

8c、第3のn型不純物領域148dと同程度、もしくは少し高めの濃度でn型を付与す

る不純物元素を含むように形成される。また、半導体層104にチャネル形成領域146

、半導体層105にチャネル形成領域149a及びチャネル形成領域149bが形成され

る。

【0108】

第2のn型不純物領域144a、第2のn型不純物領域144b、第2のn型不純物領域

147a、第2のn型不純物領域147b、第2のn型不純物領域147cは高濃度n型

不純物領域であり、ソース、ドレインとして機能する。一方、第3のn型不純物領域14

5a、第3のn型不純物領域145b、第3のn型不純物領域148a、第3のn型不純

物領域148b、第3のn型不純物領域148c、第3のn型不純物領域148dは低濃

度不純物領域であり、LDD(LightlyDoped Drain)領域となる。n

型不純物領域145a、n型不純物領域145bは、ゲート絶縁層107を介して、第1

のゲート電極層122に覆われているのでLov領域であり、ドレイン近傍の電界を緩和

し、ホットキャリアによるオン電流の劣化を抑制することが可能である。この結果、高速

動作が可能な薄膜トランジスタを形成することができる。一方、第3のn型不純物領域1

48a、第3のn型不純物領域148b、第3のn型不純物領域148c、第3のn型不

純物領域148dはゲート電極層127、ゲート電極層128に覆われていないLoff

領域に形成されるため、ドレイン近傍の電界を緩和してホットキャリア注入による劣化を

防ぐとともに、オフ電流を低減する効果がある。この結果、信頼性の高く、低消費電力の

半導体装置を作製することが可能である。

【0109】

なお、本実施の形態では、不純物領域がゲート絶縁層を介してゲート電極層と重なる領域

をLov領域と示し、不純物領域がゲート絶縁層を介してゲート電極層と重ならない領域

をLoff領域と示す。

【0110】

次に、マスク153a、マスク153b、マスク153c及びマスク153dを除去し、

半導体層104、半導体層105を覆うマスク155a、マスク155bを形成する。マ

スク155a、マスク155b、ゲート電極層117及びゲート電極層129をマスクと

してp型を付与する不純物元素154を添加し、第1のp型不純物領域160a、第1の

p型不純物領域160b、第1のp型不純物領域163a、第1のp型不純物領域163

b、第2のp型不純物領域161a、第2のp型不純物領域161b、第2のp型不純物

領域164a、第2のp型不純物領域164bが形成される(図6(C)参照。)。本実

施の形態では、不純物元素としてボロン(B)を用いる。ここでは、第1のp型不純物領

域160a、第1のp型不純物領域160b、第1のp型不純物領域163a、第1のp

型不純物領域163b、第2のp型不純物領域161a、第2のp型不純物領域161b

、第2のp型不純物領域164a、第2のp型不純物領域164bにp型を付与する不純

物元素が1×1020〜5×1021/cm3程度の濃度で含まれるように添加する。本

実施の形態では、第2のp型不純物領域161a、第2のp型不純物領域161b、第2

のp型不純物領域164a、第2のp型不純物領域164bは、ゲート電極層117及び

ゲート電極層129の形状を反映し、自己整合的に第1のp型不純物領域160a、第1

のp型不純物領域160b、第1のp型不純物領域163a、第1のp型不純物領域16

3bより低濃度となるように形成する。また、半導体層103にチャネル形成領域162

、半導体層106にチャネル形成領域165が形成される。

【0111】

次いで、マスク155a、マスク155bをO2アッシングやレジスト剥離液により除

去し、酸化膜も除去する。

【0112】

次いで、不純物元素を活性化するために加熱処理、強光の照射、又はレーザ光の照射を

行う。活性化と同時にゲート絶縁層へのプラズマダメージやゲート絶縁層と半導体層との

界面へのプラズマダメージを回復することができる。

【0113】

次いで、ゲート電極層、ゲート絶縁層を覆う層間絶縁層を形成する。本実施の形態では、

絶縁膜167と絶縁膜168との積層構造とする(図7(A)参照。)。絶縁膜167と

して窒化酸化珪素膜を膜厚200nm形成し、絶縁膜168として酸化窒化絶縁膜を膜厚

800nm形成し、積層構造とする。また、ゲート電極層、ゲート絶縁層を覆って、酸化

窒化珪素膜を膜厚30nm形成し、窒化酸化珪素膜を膜厚140nm形成し、酸化窒化珪

素膜を膜厚800nm形成し、3層の積層構造としてもよい。本実施の形態では、絶縁膜

167及び絶縁膜168を下地膜と同様にプラズマCVD法を用いて連続的に形成する。

絶縁膜167及び絶縁膜168は窒化珪素膜に限定されるものでなく、スパッタ法、また

はプラズマCVDを用いた窒化酸化珪素膜、酸化窒化珪素膜、酸化珪素膜でもよく、他の

珪素を含む絶縁膜を単層または3層以上の積層構造として用いても良い。

【0114】

次いで、窒素雰囲気中で、300〜550℃で1〜12時間の熱処理を行い、半導体

層を水素化する工程を行う。好ましくは、400〜500℃で行う。この工程は層間絶縁

層である絶縁膜167に含まれる水素により半導体層のダングリングボンドを終端する工

程である。本実施の形態では、410度(℃)で加熱処理を行う。

【0115】

次いで、レジストからなるマスクを用いて絶縁膜167、絶縁膜168、ゲート絶縁層1

07に半導体層に達するコンタクトホール(開口部)を形成する。エッチングは、用いる

材料の選択比によって、一回で行っても複数回行っても良い。

【0116】

次いで、開口部を覆うように導電膜を形成し、導電膜をエッチングして各ソース領域又は

ドレイン領域の一部とそれぞれ電気的に接続するソース電極層又はドレイン電極層169

a、ソース電極層又はドレイン電極層169b、ソース電極層又はドレイン電極層170

a、ソース電極層又はドレイン電極層170b、ソース電極層又はドレイン電極層171

a、ソース電極層又はドレイン電極層171b、ソース電極層又はドレイン電極層172

a、ソース電極層又はドレイン電極層172b、配線層156を形成する。ソース電極層

又はドレイン電極層は、PVD法、CVD法、蒸着法等により導電膜を成膜した後、所望

の形状にエッチングして形成することができる。また、液滴吐出法、印刷法、電解メッキ

法等により、所定の場所に選択的に導電層を形成することができる。更にはリフロー法、

ダマシン法を用いても良い。ソース電極層又はドレイン電極層の材料は、Ag、Au、C

u、Ni、Pt、Pd、Ir、Rh、W、Al、Ta、Mo、Cd、Zn、Fe、Ti、

Zr、Ba等の金属又はその合金、若しくはその金属窒化物を用いて形成する。また、S

i、Geを含む導電材料を用いてもよい。また、これらの積層構造としても良い。本実施

の形態では、チタン(Ti)を膜厚100nm形成し、アルミニウムとシリコンの合金(

Al−Si)を膜厚700nm形成し、チタン(Ti)を膜厚200nm形成し、選択的

にエッチングして所望な形状に形成する。

【0117】

ここまでの工程で周辺駆動回路領域204にLov領域にp型不純物領域を有するpチャ

ネル型薄膜トランジスタ173、Lov領域にn型不純物領域を有するnチャネル型薄膜

トランジスタ174を、接続領域に、導電層177を、画素領域206にLoff領域に

n型不純物領域を有するマルチチャネル型のnチャネル型薄膜トランジスタ175、Lo

v領域にp型不純物領域を有するpチャネル型薄膜トランジスタ176を有するアクティ

ブマトリクス基板を作製することができる(図7(B)参照。)。

【0118】

次に第2の層間絶縁層として絶縁膜180及び絶縁膜181を形成する(図8(A)参照

。)。図8は、表示装置の作製工程を示しており、スクライブによる切り離しのための切

り離し領域201、FPCの貼り付け部である外部端子接続領域202、周辺部の引き回

し配線領域である配線領域203、周辺駆動回路領域204、接続領域205、画素領域

206である。配線領域203には配線179a、配線179bが設けられ、外部端子接

続領域202には、外部端子と接続する端子電極層178が設けられている。

【0119】

絶縁膜180、絶縁膜181としては酸化珪素、窒化珪素、酸化窒化珪素、窒化酸化

珪素、窒化アルミニウム(AlN)、酸化窒化アルミニウム(AlON)、窒素含有量が

酸素含有量よりも多い窒化酸化アルミニウム(AlNO)または酸化アルミニウム、ダイ

アモンドライクカーボン(DLC)、窒素含有炭素膜(CN)、PSG(リンガラス)、

BPSG(リンボロンガラス)、アルミナ膜、ポリシラザン、その他の無機絶縁性材料を

含む物質から選ばれた材料で形成することができる。また、シロキサン樹脂を用いてもよ

い。なお、シロキサン樹脂とは、Si−O−Si結合を含む樹脂に相当する。シロキサン

は、シリコン(Si)と酸素(O)との結合で骨格構造が構成される。置換基として、少

なくとも水素を含む有機基(例えばアルキル基、芳香族炭化水素)が用いられる。置換基

として、フルオロ基を用いてもよい。または置換基として、少なくとも水素を含む有機基

と、フルオロ基とを用いてもよい。また、有機絶縁性材料を用いてもよく、有機材料とし

ては、感光性、非感光性どちらでも良く、ポリイミド、アクリル、ポリアミド、ポリイミ

ドアミド、レジス、ベンゾシクロブテン、低誘電率有機絶縁性材料を用いることができる

。

【0120】

次に、図8(B)に示すように、第2の層間絶縁層である絶縁膜180及び絶縁膜1

81に開口部182、183を形成する。絶縁膜180及び絶縁膜181は、接続領域2

05、配線領域203、外部端子接続領域202、切り離し領域201等では大面積にエ

ッチングする必要がある。しかし、画素領域206においては開口面積が、接続領域20

5等の開口面積と比較して非常に小さく、微細なものとなる。従って、画素領域の開口部

形成用のフォトリソグラフィ工程と、接続領域の開口部形成用のフォトリソグラフィ工程

とを別々に行う。

【0121】

その後、図8(C)に示すように、画素領域206の絶縁膜180及び絶縁膜181に微

細な開口部184、つまりコンタクトホールを形成する。

【0122】

本実施の形態では、接続領域205、配線領域203、外部端子接続領域202、切

り離し領域201、周辺駆動回路領域204を覆い、画素領域206に所定の開口部が設

けられたマスクで、絶縁膜180及び絶縁膜181をエッチングする場合を説明したが、

本発明はこれに限定されない。例えば、接続領域205の開口部は広面積であるため、エ

ッチングする量が多い。このような広面積な開口部は、複数回エッチングしてもよい。

【0123】

次に、図9(A)に示すようにソース電極層又はドレイン電極層172aと接するよ

うに、第1の電極層185(画素電極層ともいう。)を形成する。第1の電極層は陽極、

または陰極として機能し、Ti、Ni、W、Cr、Pt、Zn、Sn、In、またはMo

から選ばれた元素、TiN、TiSiXNY、WSiX、WNX、WSiXNY、NbN

、または前記元素を主成分とする合金材料もしくは化合物材料を主成分とする膜またはそ

れらの積層膜を総膜厚100nm〜800nmの範囲で用いればよい。

【0124】

本実施の形態では、表示素子として発光素子を用い、発光素子からの光を第1の電極

層185側から取り出す構造のため、第1の電極層185が透光性を有する。第1の電極

層185として、透明導電膜を形成し、所望の形状にエッチングすることで第1の電極層

185を形成する。本発明で用いる第1の電極層185として、酸化珪素を含む酸化イン

ジウムスズ(酸化珪素を含むインジウム錫酸化物ともいう、以下、「ITSO」という。

)、酸化亜鉛、酸化スズ、酸化インジウムなどを用いてもよい。この他、酸化インジウム

に2〜20wt%の酸化亜鉛(ZnO)を混合した酸化インジウム酸化亜鉛合金などの透

明導電膜を用いることができる。第1の電極層185として上記透明導電膜の他に、窒化

チタン膜またはチタン膜を用いても良い。この場合、透明導電膜を成膜した後に、窒化チ

タン膜またはチタン膜を、光が透過する程度の膜厚(好ましくは、5nm〜30nm程度

)で成膜する。本実施の形態では、第1の電極層185として、酸化インジウムスズと酸

化珪素を用いたITSOを用いる。

【0125】

第1の電極層185を形成した段階での画素領域の上面図の一例を図11に示す。図1

1において、一つの画素は、TFT501、TFT502、容量素子504、第1の電極

層185、ゲート配線層506、ソース配線層及びドレイン配線層505、電源線507

から構成されている。

【0126】

次いで、第1の電極層185を形成後、加熱処理を行ってもよい。この加熱処理により、

第1の電極層185中に含まれる水分は放出される。よって、第1の電極層185は脱ガ

スなどを生じないため、第1の電極層上に水分によって劣化しやすい発光材料を形成して

も、発光材料は劣化せず、信頼性の高い表示装置を作製することができる。本実施の形態

では、第1の電極層185にITSOを用いているので、ベークを行ってもITO(酸化

インジウム酸化スズ合金)のように結晶化せず、アモルファス状態のままである。従って

、ITSOは、ITOよりも平坦性が高く、有機化合物を含む層が薄くとも陰極とのショ

ートが生じにくい。

【0127】

次いで、第1の電極層185の端部、ソース電極層又はドレイン電極層を覆う絶縁材料

からなる隔壁186を形成する(図9(B)参照。)。回折格子パターン或いは半透膜か

らなる光強度低減機能を有する補助パターンを設置したフォトマスクまたはレチクルを用

いて隔壁186を形成する。また、隔壁186は、膜厚の厚い部分を複数箇所有した断面

形状を有し、隔壁の側面に段差を有している。この隔壁186の作製方法は、実施の形態

1に従って得ることができる。

【0128】

フルカラー表示を行うためには、第1の電極層上に電界発光層を形成する際、RGBの発

光を行う電界発光層をそれぞれ作り分けなければならない。よって、他色の電界発光層を

形成する時は、その画素電極層(第1の電極層)は蒸着マスクによって覆われている。蒸

着マスクは金属材料などからなる膜状の形態を用いることができる。このとき、蒸着マス

クは隔壁186上に設けられ、隔壁186の厚い部分で支持される。この隔壁186の厚

い部分を設けることによって、マスクによる第1の電極層への形状不良は防止され、第1

の電極層は発光不良、表示不良を引き起こすことなく、信頼性の高い高画質な表示装置と

することができる。

【0129】

また、隔壁186と同工程で外部端子接続領域202に絶縁物(絶縁層)187a、絶縁

物(絶縁層)187bを形成する。

【0130】

また、接続領域205において、隔壁186は、開口部182の側面の絶縁膜180及び

絶縁膜181の端部を覆うように形成されている。選択的にエッチングする処理によって

段差を有するように加工された絶縁膜180及び絶縁膜181の端部は、その急激な段差

のため、その上に積層する第2の電極層189の被覆性が悪い。よって本発明のように、

開口部周辺の段差を隔壁186によって覆い、段差をなだらかにすることで、積層する第

2の電極層189の被覆性を向上させることができる。接続領域205において、第2の

電極層と同工程、同材料で形成される配線層は配線層156と電気的に接続する。本実施

の形態では、第2の電極層189は配線層156と接して電気的に接続されているが、他

の配線を介して電気的に接続されてもよい。

【0131】

次いで、第1の電極層185上に電界発光層188を形成する。なお、図10では一画

素しか図示していないが、本実施の形態ではR(赤)、G(緑)、B(青)の各色に対応

した電界発光層を作り分けている。本実施の形態では電界発光層188として、赤色(R

)、緑色(G)、青色(B)の発光を示す材料を、それぞれ蒸着マスクを用いた蒸着法等

によって選択的に形成する。

【0132】

次に、電界発光層188上に導電膜からなる第2の電極層189を形成する。第2の

電極層189としては、仕事関数の小さい材料(Al、Ag、Li、Ca、またはこれら

の合金や化合物、MgAg、MgIn、AlLi、CaF2、または窒化カルシウム)を

用いればよい。こうして第1の電極層185、電界発光層188及び第2の電極層189

からなる発光素子190が形成される。

【0133】

図10に示した本実施の形態の表示装置において、発光素子190から発した光は、

第1の電極層185側から、図10中の矢印の方向に透過して射出される。

【0134】

第2の電極層189を覆うようにしてパッシベーション膜191を設けることは有効で

ある。パッシベーション膜191としては、窒化珪素、酸化珪素、酸化窒化珪素(SiO

N)、窒化酸化珪素(SiNO)、窒化アルミニウム(AlN)、酸化窒化アルミニウム

(AlON)、窒素含有量が酸素含有量よりも多い窒化酸化アルミニウム(AlNO)ま

たは酸化アルミニウム、ダイアモンドライクカーボン(DLC)、窒素含有炭素膜(CN

)を含む絶縁膜からなり、該絶縁膜を単層もしくは組み合わせた積層を用いることができ

る。また、シロキサン樹脂材料を用いてもよい。

【0135】

次いで、発光素子190が形成された基板100と、封止基板195とをシール材19

2によって固着し、発光素子を封止する(図10参照。)。

【0136】

なお、シール材で囲まれた領域には充填材や粘着テープを充填してもよく、窒素雰囲気下

で封止することによって、窒素等を封入してもよい。本実施の形態は、下面射出型のため

、充填材は透光性を有する必要はないが、充填材を透過して光を取り出す構造の場合は、

透光性を有する必要がある。代表的には可視光硬化、紫外線硬化または熱硬化のエポキシ

樹脂を用いればよい。以上の工程において、本実施の形態における、発光素子を用いた表

示機能を有する表示装置が完成する。また充填材は、液状の状態で滴下し、表示装置内に

充填することもできる。

【0137】

また、発光素子の水分による劣化を防ぐため、パネル内に乾燥剤を設置してもよい。

【0138】

次いで、外部端子接続領域202において、端子電極層178に異方性導電層196に

よってFPC194を接続し、外部と電気的に接続する。

【0139】

また、本発明の表示装置において、画面表示の駆動方法は特に限定されず、例えば、

点順次駆動方法や線順次駆動方法や面順次駆動方法などを用いればよい。代表的には、線

順次駆動方法とし、時分割階調駆動方法や面積階調駆動方法を適宜用いればよい。また、

表示装置のソース線に入力する映像信号は、アナログ信号であってもよいし、デジタル信

号であってもよく、適宜、映像信号に合わせて駆動回路などを設計すればよい。

【0140】

さらに、ビデオ信号がデジタルの表示装置において、画素に入力されるビデオ信号が

定電圧(CV)のものと、定電流(CC)のものとがある。ビデオ信号が定電圧のもの(

CV)には、発光素子に印加される電圧が一定のもの(CVCV)と、発光素子に印加さ

れる電流値が一定のもの(CVCC)とがある。また、ビデオ信号が定電流のもの(CC

)には、発光素子に印加される電圧値が一定のもの(CCCV)と、発光素子に印加され

る電流値が一定のもの(CCCC)とがある。

【0141】

本発明を用いると、信頼性の高い表示装置を簡略化した工程で作製することができる

。よって、高精細、高画質な表示装置を低いコストで歩留まり良く製造することができる

。

【0142】

本実施の形態は、実施の形態1乃至3のいずれか一と自由に組み合わせることができる

。

【0143】

(実施の形態5)

本発明によって形成される発光装置によって、テレビジョン装置を完成させることができ

る。表示パネルには、画素部のみが形成されて走査線側駆動回路と信号線側駆動回路とが

、TAB方式により実装される場合と、COG方式により実装される場合と、TFTを形

成し、画素部と走査線側駆動回路を基板上に一体形成し信号線側駆動回路を別途ドライバ

ICとして実装する場合、また画素部と信号線側駆動回路と走査線側駆動回路を基板上に

一体形成する場合などがあるが、どのような形態としても良い。

【0144】

その他の外部回路の構成として、映像信号の入力側では、チューナで受信した信号の

うち、映像信号を増幅する映像信号増幅回路と、そこから出力される信号を赤、緑、青の

各色に対応した色信号に変換する映像信号処理回路と、その映像信号をドライバICの入

力仕様に変換するためのコントロール回路などからなっている。コントロール回路は、走

査線側と信号線側にそれぞれ信号が出力する。デジタル駆動する場合には、信号線側に信

号分割回路を設け、入力デジタル信号をm個に分割して供給する構成としても良い。

【0145】

チューナで受信した信号のうち、音声信号は、音声信号増幅回路に送られ、その出力

は音声信号処理回路を経てスピーカに供給される。制御回路は受信局(受信周波数)や音

量の制御情報を入力部から受け、チューナや音声信号処理回路に信号を送出する。

【0146】

表示モジュールを、図12(A)、(B)に示すように、筐体に組みこんで、テレビ

ジョン装置を完成させることができる。FPCまで取り付けられた表示パネルのことを表

示モジュールとも呼ぶ。表示モジュールにより主画面2003が形成され、その他付属設

備としてスピーカー部2009、操作スイッチなどが備えられている。このように、本発

明によりテレビジョン装置を完成させることができる。

【0147】

また、位相差板や偏光板を用いて、外部から入射する光の反射光を遮断するようにし

てもよい。また上面放射型の表示装置ならば、隔壁となる絶縁層を着色しブラックマトリ

クスとして用いてもよい。この隔壁は液滴吐出法などによっても形成することができ、顔

料系の黒色樹脂や、ポリイミドなどの樹脂材料に、カーボンブラック等を混合させてもよ

く、その積層でもよい。液滴吐出法によって、異なった材料を同領域に複数回吐出し、隔

壁を形成してもよい。位相差板、位相差板としてはλ/4板、λ/2板を用い、光を制御

できるように設計すればよい。構成としては、順にTFT素子基板、発光素子、封止基板

(封止材)、位相差板、位相差板(λ/4板、λ/2板)、偏光板となり、発光素子から

放射された光は、これらを通過し偏光板側より外部に放射される。この位相差板や偏光板

は光が放射される側に設置すればよく、両面放射される両面放射型の表示装置であれば両

方に設置することもできる。また、偏光板の外側に反射防止膜を有していても良い。これ

により、より高繊細で精密な画像を表示することができる。

【0148】

図12(A)に示すように、筐体2001に表示素子を利用した表示用パネル200

2が組みこまれ、受信機2005により一般のテレビ放送の受信をはじめ、モデム200

4を介して有線又は無線による通信ネットワークに接続することにより一方向(送信者か

ら受信者)又は双方向(送信者と受信者間、又は受信者間同士)の情報通信をすることも

できる。テレビジョン装置の操作は、筐体に組みこまれたスイッチ又は別体のリモコン操

作機2006により行うことが可能であり、このリモコン装置にも出力する情報を表示す

る表示部2007が設けられていても良い。

【0149】

また、テレビジョン装置にも、主画面2003の他にサブ画面2008を第2の表示

用パネルで形成し、チャネルや音量などを表示する構成が付加されていても良い。この構

成において、主画面2003を視野角の優れたEL表示用パネルで形成し、サブ画面を低

消費電力で表示可能な液晶表示用パネルで形成しても良い。また、低消費電力化を優先さ

せるためには、主画面2003を液晶表示用パネルで形成し、サブ画面をEL表示用パネ

ルで形成し、サブ画面は点滅可能とする構成としても良い。本発明を用いると、このよう

な大型基板を用いて、多くのTFTや電子部品を用いても、信頼性の高い表示装置とする

ことができる。

【0150】

図12(B)は例えば20〜80インチの大型の表示部を有するテレビジョン装置で

あり、筐体2010、操作部であるキーボード部2012、表示部2011、スピーカー

部2013等を含む。本発明は、表示部2011の作製に適用される。図12(B)の表

示部は、わん曲可能な基板を用いているので、表示部がわん曲したテレビジョン装置とな

っている。このように表示部の形状を自由に設計することができるので、所望な形状のテ

レビジョン装置を作製することができる。

【0151】

本発明により、簡略な工程で表示装置を形成できるため、コストダウンも達成できる

。よって本発明を用いたテレビジョン装置では、大画面の表示部を有しても低いコストで

形成できる。よって高性能、高信頼性のテレビジョン装置を歩留まりよく作製することが

できる。

【0152】

勿論、本発明はテレビジョン装置に限定されず、パーソナルコンピュータのモニタを

はじめ、鉄道の駅や空港などにおける情報表示盤や、街頭における広告表示盤など大面積

の表示媒体としても様々な用途に適用することができる。

【0153】

本実施の形態は、実施の形態1乃至4のいずれか一と自由に組み合わせることができる

。

【0154】

(実施の形態6)

本実施の形態を図13を用いて説明する。本実施の形態は、実施の形態1乃至4で作製す

る表示装置を有するパネルを用いたモジュールの例を示す。

【0155】

図13(A)に示す情報端末のモジュールは、プリント配線基板946に、コントロ

ーラ901、中央処理装置(CPU)902、メモリ911、電源回路903、音声処理

回路929及び送受信回路904や、その他、抵抗、バッファ、容量素子等の素子が実装

されている。また、パネル900がフレキシブル配線基板(FPC)908を介してプリ

ント配線基板946に接続されている。

【0156】

パネル900には、発光素子が各画素に設けられた画素部905と、前記画素部905

が有する画素を選択する第1の走査線駆動回路906a、第2の走査線駆動回路906b

と、選択された画素にビデオ信号を供給する信号線駆動回路907とが設けられている。

【0157】

プリント配線基板946に備えられたインターフェース(I/F)部909を介して、

各種制御信号の入出力が行われる。また、アンテナとの間の信号の送受信を行なうための

アンテナ用ポート910が、プリント配線基板946に設けられている。

【0158】

なお、本実施の形態ではパネル900にプリント配線基板946がFPC908を介し

て接続されているが、必ずしもこの構成に限定されない。COG(Chip on Gl

ass)方式を用い、コントローラ901、音声処理回路929、メモリ911、CPU

902または電源回路903をパネル900に直接実装させるようにしても良い。また、

プリント配線基板946には、容量素子、バッファ等の各種素子が設けられ、電源電圧や

信号にノイズがのったり、信号の立ち上がりが鈍ったりすることを防いでいる。

【0159】

図13(B)は、図13(A)に示したモジュールのブロック図を示す。このモジュー

ル999は、メモリ911としてVRAM932、DRAM925、フラッシュメモリ9

26などが含まれている。VRAM932にはパネルに表示する画像のデータが、DRA

M925には画像データまたは音声データが、フラッシュメモリには各種プログラムが記

憶されている。

【0160】

電源回路903では、パネル900、コントローラ901、CPU902、音声処理回

路929、メモリ911、送受信回路931に与える電源電圧が生成される。またパネル

の仕様によっては、電源回路903に電流源が備えられている場合もある。

【0161】

CPU902は、制御信号生成回路920、デコーダ921、レジスタ922、演算回

路923、RAM924、CPU用のインターフェース935などを有している。インタ

ーフェース935を介してCPU902に入力された各種信号は、一旦レジスタ922に

保持された後、演算回路923、デコーダ921などに入力される。演算回路923では

、入力された信号に基づき演算を行ない、各種命令を送る場所を指定する。一方デコーダ

921に入力された信号はデコードされ、制御信号生成回路920に入力される。制御信

号生成回路920は入力された信号に基づき、各種命令を含む信号を生成し、演算回路9

23において指定された場所、具体的にはメモリ911、送受信回路931、音声処理回

路929、コントローラ901などに送る。

【0162】

メモリ911、送受信回路931、音声処理回路929、コントローラ901は、それ

ぞれ受けた命令に従って動作する。以下その動作について簡単に説明する。

【0163】

入力手段934から入力された信号は、インターフェース909を介してプリント配線

基板946に実装されたCPU902に送られる。制御信号生成回路920は、ポインテ

ィングデバイスやキーボードなどの入力手段934から送られてきた信号に従い、VRA

M932に格納してある画像データを所定のフォーマットに変換し、コントローラ901

に送付する。

【0164】

コントローラ901は、パネルの仕様に合わせてCPU902から送られてきた画像デ

ータを含む信号にデータ処理を施し、パネル900に供給する。またコントローラ901

は、電源回路903から入力された電源電圧やCPU902から入力された各種信号をも

とに、Hsync信号、Vsync信号、クロック信号CLK、交流電圧(AC Con

t)、切り替え信号L/Rを生成し、パネル900に供給する。

【0165】

送受信回路904では、アンテナ933において電波として送受信される信号が処理さ

れており、具体的にはアイソレータ、バンドパスフィルタ、VCO(Voltage C

ontrolled Oscillator)、LPF(Low Pass Filte

r)、カプラ、バランなどの高周波回路を含んでいる。送受信回路904において送受信

される信号のうち音声情報を含む信号が、CPU902からの命令に従って、音声処理回

路929に送られる。

【0166】

CPU902の命令に従って送られてきた音声情報を含む信号は、音声処理回路929

において音声信号に復調され、スピーカー928に送られる。またマイク927から送ら

れてきた音声信号は、音声処理回路929において変調され、CPU902からの命令に

従って、送受信回路904に送られる。

【0167】

コントローラ901、CPU902、電源回路903、音声処理回路929、メモリ9

11を、本実施の形態のパッケージとして実装することができる。本実施の形態は、アイ

ソレータ、バンドパスフィルタ、VCO(Voltage Controlled Os

cillator)、LPF(Low Pass Filter)、カプラ、バランなど

の高周波回路以外であれば、どのような回路にも応用することができる。

【0168】

表示パネル900は、画素電極上、又は画素電極周囲を覆う絶縁物上にスペーサを具備

している。それにより、この表示パネル900を備えるモジュールは、電界発光層を形成

時に用いるマスクが画素電極と接触しないように支持するため、画素電極の損傷が防げ、

高画質な表示と高い信頼性という効果を奏することができる。

【0169】

(実施の形態7)

本実施の形態を図14を用いて説明する。図14は、実施の形態6で作製するモジュール

を含む無線を用いた持ち運び可能な小型電話機(携帯電話)の一態様を示している。表示

パネル900はハウジング1001に脱着自在に組み込んでモジュール999と容易に固

定できるようにしている。ハウジング1001は組み入れる電子機器に合わせて、形状や

寸法を適宜変更することができる。

【0170】

表示パネル900を固定したハウジング1001はプリント配線基板946に嵌着され

モジュールとして組み立てられる。プリント配線基板946には、コントローラ、CPU

、メモリ、電源回路、その他、抵抗、バッファ、容量素子等が実装されている。さらに、

マイクロフォン994及びスピーカー995を含む音声処理回路、送受信回路などの信号

処理回路993が備えられている。パネル900はFPC908を介してプリント配線基

板946に接続される。

【0171】

このようなモジュール999、入力手段998、バッテリ997は筐体996に収納さ

れる。表示パネル900の画素部は筐体996に形成された開口窓から視認できように配

置されている。

【0172】

表示パネル900は、画素電極上、又は画素電極周囲を覆う絶縁物上にスペーサを具備

している。それにより、この表示パネル900を備えるモジュールは、電界発光層を形成

時に用いるマスクが画素電極と接触しないように支持するため、画素電極の損傷が防げ、

高画質な表示と高い信頼性という効果を奏することができる。

【0173】

図14で示す筐体996は、電話機の外観形状を一例として示している。しかしながら

、本実施の形態に係る電子機器は、その機能や用途に応じてさまざまな態様に変容し得る

。以下に示す実施の形態で、その態様の一例を説明する。

【0174】

(実施の形態8)

本発明を適用して、様々な表示装置を作製することができる。即ち、それら表示装置を表

示部に組み込んだ様々な電子機器に本発明を適用できる。

【0175】

その様な電子機器としては、ビデオカメラ、デジタルカメラ等のカメラ、プロジェク

ター、ヘッドマウントディスプレイ(ゴーグル型ディスプレイ)、カーナビゲーション、

カーステレオ、パーソナルコンピュータ、ゲーム機器、携帯情報端末(モバイルコンピュ

ータ、携帯電話または電子書籍等)、記録媒体を備えた画像再生装置(具体的にはDig

ital Versatile Disc(DVD)等の記録媒体を再生し、その画像を

表示しうるディスプレイを備えた装置)などが挙げられる。それらの例を図15に示す。

【0176】

図15(A)は、コンピュータであり、本体2101、筐体2102、表示部210

3、キーボード2104、外部接続ポート2105、ポインティングマウス2106等を

含む。本発明を用いると、小型化し、画素が微細化しても、信頼性が高く、高画質な画像

を表示するコンピュータを完成させることができる。

【0177】

図15(B)は記録媒体を備えた画像再生装置(具体的にはDVD再生装置)であり

、本体2201、筐体2202、表示部A2203、表示部B2204、記録媒体(DV

D等)読み込み部2205、操作キー2206、スピーカー部2207等を含む。表示部

A2203は主として画像情報を表示し、表示部B2204は主として文字情報を表示す

る。本発明を用いると、小型化し、画素が微細化しても、信頼性が高く、高画質な画像を

表示する画像再生装置を完成させることができる。

【0178】

図15(C)は携帯電話であり、本体2301、音声出力部2302、音声入力部2

303、表示部2304、操作スイッチ2305、アンテナ2306等を含む。本発明を

用いると、小型化し、画素が微細化しても、信頼性が高く、高画質な画像を表示する携帯

電話を完成することができる。

【0179】

図15(D)はビデオカメラであり、本体2401、表示部2402、筐体2403

、外部接続ポート2404、リモコン受信部2405、受像部2406、バッテリー24

07、音声入力部2408、接眼部2409、操作キー2410等を含む。本発明を用い

ると、小型化し、画素が微細化しても、信頼性が高く、高画質な画像を表示できるビデオ

カメラを完成することができる。

【0180】

本実施の形態は、実施の形態1乃至4のいずれか一と自由に組み合わせることができる

。

【0181】

(実施の形態9)

ここでは、発光素子と電気的に接続するTFTとして、アモルファスシリコンを活性層と

するTFTの例を図16に示す。

【0182】

図16において、1910は基板、1911は隔壁、1913は第1の電極、1914は

有機化合物を含む層、1915は第2の電極、1916はアモルファスシリコンTFT、

1917はゲート絶縁膜、1918は絶縁膜である。また、1919は電源供給線などの

配線である。

【0183】

アモルファスシリコンTFT1916の作製手順は、公知の技術を用いればよく、まず、

基板1910上にゲート電極を形成した後、ゲート絶縁膜1917を形成する。次いで、

アモルファスシリコン膜(活性層)、リンを含むアモルファスシリコン膜(n+層)、金

属膜を順次積層する。次いで、アモルファスシリコンを所望の素子形状にエッチングした

後、ゲート電極と重なる領域において、アモルファスシリコンが一部露呈するように選択

的にエッチングを行ってチャネルを形成する。次いで、全面を絶縁膜1918で覆った後

、コンタクトホールの形成、ソース配線、ドレイン配線の形成を行う。

【0184】

なお、アモルファスシリコンTFT1916はチャネルエッチ型TFTを示しているが、

チャネルストップ型TFTとしてもよい。

【0185】

アモルファスシリコンTFT作製以降の工程は、実施の形態1と同様に、第1の電極19

13の形成、断面形状が裾状の隔壁1911を形成する。

【0186】

次いで、有機化合物を含む層1914を蒸着法、インクジェット法、または塗布法によっ

て形成する。次いで、蒸着法またはスパッタ法により第2の電極1915を形成する。

【0187】

アモルファスシリコンTFTは高熱でのプロセスが少なく、量産に適したプロセスであり

、発光装置の作製におけるコスト削減することができる。

【0188】

また、本実施の形態においては、アモルファスシリコンTFTを用いる例であるので、同

一基板上に画素部と駆動回路とを作製せずに、画素部のみを基板上に形成し、駆動回路を

ICで構成する。

【0189】

本実施の形態は、実施の形態1乃至8のいずれか一と自由に組み合わせることができる。

【符号の説明】

【0190】

10 基板

11 隔壁

12 下地絶縁膜

13 第1の電極

14 有機化合物を含む層

15 第2の電極

16 TFT

17 ゲート絶縁膜を含む絶縁膜の積層

18 絶縁膜

19 配線

20 感光性の樹脂膜

21 蒸着マスク

31 隔壁

33 第1の電極

34 有機化合物を含む層

100 基板

101a 下地膜

101b 下地膜

102 結晶性半導体膜

103 半導体層

104 半導体層

105 半導体層

106 半導体層

107 ゲート絶縁層

108 導電膜

109 導電膜

117 ゲート電極層

118 ゲート電極層

121 ゲート電極層

122 ゲート電極層

123 導電層

124 ゲート電極層

125 ゲート電極層

126 ゲート電極層

127 ゲート電極層

128 ゲート電極層

129 ゲート電極層

130 導電層

131 ゲート電極層

132 ゲート電極層

133 導電層

134 ゲート電極層

135 第2のゲート電極層

136 第2のゲート電極層

140a n型不純物領域

140b n型不純物領域

141a n型不純物領域

141b n型不純物領域

142a n型不純物領域

142b n型不純物領域

142c n型不純物領域

143a n型不純物領域

143b n型不純物領域

144a n型不純物領域

144b n型不純物領域

145a n型不純物領域

145b n型不純物領域

146 チャネル形成領域

147a n型不純物領域

147b n型不純物領域

147c n型不純物領域

148a n型不純物領域

148b n型不純物領域

148c n型不純物領域

148d n型不純物領域

149a チャネル形成領域

149b チャネル形成領域

151 不純物元素

152 不純物元素

153a マスク

153b マスク

153c マスク

153d マスク

154 不純物元素

155a マスク

155b マスク

156 配線層

160a p型不純物領域

160b p型不純物領域

161a p型不純物領域

161b p型不純物領域

162 チャネル形成領域

163a p型不純物領域

163b p型不純物領域

164a p型不純物領域

164b p型不純物領域

165 チャネル形成領域

167 絶縁膜

168 絶縁膜

169a ドレイン電極層

169b ドレイン電極層

170a ドレイン電極層

170b ドレイン電極層

171a ドレイン電極層

171b ドレイン電極層

172a ドレイン電極層

172b ドレイン電極層

173 pチャネル型薄膜トランジスタ

174 nチャネル型薄膜トランジスタ

175 nチャネル型薄膜トランジスタ

176 pチャネル型薄膜トランジスタ

177 導電層

178 端子電極層

179a 配線

179b 配線

180 絶縁膜

181 絶縁膜

182 開口部

183 開口部

184 開口部

185 第1の電極層

186 隔壁

187a 絶縁物

187b 絶縁物

188 電界発光層

189 第2の電極層

190 発光素子

191 パッシベーション膜

192 シール材

194 FPC

195 封止基板

196 異方性導電層

201 領域

202 外部端子接続領域

203 配線領域

204 周辺駆動回路領域

205 接続領域

206 画素領域

301 第1の基板

302 隔壁

303 第1の電極

304 構造物

305 有機化合物を含む層

306 画素部

307 第2の電極

308 第2の基板

309 接着層

400 露光マスク

401 遮光部

402 半透部

501 TFT

502 TFT

504 容量素子

505 ドレイン配線層

506 ゲート配線層

507 電源線

700 成膜室

701 基板

702 蒸着マスク

703a 防着シールド

703b 開口部

704 蒸着源

705 蒸着源の移動方向

706a 基板の搬送方向

706b 蒸着材料の昇華方向

707 設置室

900 パネル

901 コントローラ

902 CPU

903 電源回路

904 送受信回路

905 画素部

906a 第1の走査線駆動回路

906b 第2の走査線駆動回路

907 信号線駆動回路

908 FPC

909 I/F部

910 アンテナ用ポート

911 メモリ

920 制御信号生成回路

921 デコーダ

922 レジスタ

923 演算回路

924 RAM

925 DRAM

926 フラッシュメモリ

927 マイク

928 スピーカー

929 音声処理回路

931 送受信回路

932 VRAM

933 アンテナ

934 入力手段

935 インターフェース

946 プリント配線基板

993 信号処理回路

994 マイクロフォン

995 スピーカー

996 筐体

997 バッテリ

998 入力手段

999 モジュール

1001 ハウジング

1910 基板

1911 隔壁

1913 電極

1914 有機化合物を含む層

1915 電極

1916 アモルファスシリコンTFT

1917 ゲート絶縁膜

1918 絶縁膜

1919 配線

2001 筐体

2002 表示用パネル

2003 主画面

2004 モデム

2005 受信機

2006 リモコン操作機

2007 表示部

2008 サブ画面

2009 スピーカー部

2010 筐体

2011 表示部

2012 キーボード部

2013 スピーカー部

2101 本体

2102 筐体

2103 表示部

2104 キーボード

2105 外部接続ポート

2106 ポインティングマウス

2201 本体

2202 筐体

2203 表示部A

2204 表示部B

2205 記録媒体読み込み部

2206 操作キー

2207 スピーカー部

2301 本体

2302 音声出力部

2303 音声入力部

2304 表示部

2305 操作スイッチ

2306 アンテナ

2401 本体

2402 表示部

2403 筐体

2404 外部接続ポート

2405 リモコン受信部

2406 受像部

2407 バッテリー

2408 音声入力部

2409 接眼部

2410 操作キー

【技術分野】

【0001】

本発明は、一対の電極間に有機化合物を含む膜(以下、「有機化合物層」と記す)を設

けた素子に電界を加えることで、蛍光又は燐光が得られる発光素子を用いた発光装置及び

その作製方法に関する。なお、発光装置とは、画像表示デバイス、発光デバイス、もしく

は光源(照明装置含む)を指す。

【背景技術】

【0002】

薄型軽量、高速応答性、直流低電圧駆動などの特徴を有する有機化合物を発光体として用

いた発光素子は、次世代のフラットパネルディスプレイへの応用が期待されている。特に

、発光素子をマトリクス状に配置した表示装置は、従来の液晶表示装置と比較して、視野

角が広く視認性が優れる点に優位性があると考えられている。

【0003】

発光素子の発光機構は、一対の電極間に有機化合物層を挟んで電圧を印加することにより

、陰極から注入された電子および陽極から注入された正孔が有機化合物層中の発光中心で

再結合して分子励起子を形成し、その分子励起子が基底状態に戻る際にエネルギーを放出

して発光するといわれている。励起状態には一重項励起と三重項励起が知られ、発光はど

ちらの励起状態を経ても可能であると考えられている。

【0004】

このような発光素子をマトリクス状に配置して形成された発光装置には、パッシブマトリ

クス駆動(単純マトリクス型)とアクティブマトリクス駆動(アクティブマトリクス型)

といった駆動方法を用いることが可能である。しかし、画素密度が増えた場合には、画素

(又は1ドット)毎にスイッチが設けられているアクティブマトリクス型の方が低電圧駆

動できるので有利であると考えられている。

【0005】

アクティブマトリクス型の発光装置を作製する場合、絶縁表面を有する基板上にスイッチ

ング素子としてTFTを形成し、該TFTと電気的に接続する画素電極を陽極または陰極

としたEL素子をマトリクス状に配置する。

【0006】

また、アクティブマトリクス型の発光装置やパッシブマトリクス型の発光装置を作製する

場合、隣合う画素同士を絶縁するための隔壁を画素電極の端部に設ける。

【0007】

本出願人は、特許文献1や特許文献2に記載した隔壁を提案している。

【先行技術文献】

【特許文献】

【0008】

【特許文献1】特開2002−164181

【特許文献2】特開2004−127933

【発明の概要】

【発明が解決しようとする課題】

【0009】

エレクトロルミネセンス(以下、ELとも記す)素子を備える表示装置において、フルカ

ラー表示を行うため、カラー発光するカラー発光素子を用いる。カラー発光素子を形成す

るには、各色の発光材料を微細なパターンに電極上に形成することが重要な要素の一つと

なる。

【0010】

上記目的のため、蒸着法などを用いて材料を形成する際、マスクを用いて微細パターンに

形成する方法が一般的に用いられている。

【0011】

しかし、高繊細化に伴う画素領域の微細化、大面積化に伴う基板の大型化によって、蒸着

時に用いるマスクの精度とたわみなどによる不良が問題となっている。

【0012】

本発明は、工程を増やすことなく、蒸着時に用いるマスクの精度とたわみなどによる不良

を防ぐ構造を提供する。

【0013】

また、赤、緑、青の発光色を用いるフルカラーのフラットパネルディスプレイとして、

高精細化や高開口率化や高信頼性の要求が高まっている。こうした要求は、発光装置の高

精細化(画素数の増大)及び小型化に伴う各表示画素ピッチの微細化を進める上で大きな

課題となっている。アクティブマトリクス型発光装置またはパッシブマトリクス型発光装

置を高精細化するためには隔壁の上面形状も小さくして高精細化を可能にする必要がある

。本発明は、上面形状を縮小し、さらなる高精細な表示を可能とする隔壁およびその隔壁

を備えた発光装置を提供する。

【課題を解決するための手段】

【0014】

本発明は、回折格子パターン或いは半透膜からなる光強度低減機能を有する補助パターン

を設置したフォトマスクまたはレチクルを用いることにより、工程を増やすことなく、表

示領域における画素電極(第1の電極とも呼ぶ)上、及び画素電極層周辺に膜厚が異なる

部分を有する隔壁を形成する。

【0015】

本発明の隔壁は、膜厚の厚い部分で蒸着マスクを支持し、蒸着マスクのよじれや、たわ

みなどによって蒸着マスクが画素電極表面に接してしまうことを防止する。よって、画素

電極表面にはマスクによる傷などの損傷が生じず、画素電極は形状不良とならないので、

高繊細な表示を行うことが可能であり、且つ、高信頼性な表示装置を作製することができ

る。蒸着マスクが画素電極表面に接することを防止できるのであれば、膜厚の厚い部分の

領域を選択的に形成してもよい。即ち、複数の画素が配置される領域内に膜厚の厚い部分

を一箇所形成すればよい。

【0016】

また、本発明の隔壁における膜厚の薄い部分は、有機化合物を含む層を画素電極上に形

成する際、画素電極と隔壁との境界で被覆不良が発生することを抑えることができる。従

って、本発明の隔壁は、非常に膜厚の薄い有機化合物を含む層を形成する場合に特に有効

である。隔壁における膜厚の薄い部分は、膜厚の厚い部分の少なくとも半分以下の膜厚と

する。

【0017】

回折格子パターン或いは半透膜からなる光強度低減機能を有する補助パターンを設置した

フォトマスクまたはレチクルを調節すれば、膜厚の厚い部分の幅を細くすることは可能で

あり、膜厚の薄い部分の幅を含めたトータルの隔壁幅も20μm未満とすることができる

。また、隔壁の膜厚の厚い部分の幅を5μm程度にした場合に、蒸着の際、蒸着マスクか

ら圧力がかかっても、膜厚の薄い部分が膜厚の厚い部分を両側から支える形となっている

ため、強度も確保されている。

【0018】

本明細書で開示する発明の構成は、絶縁表面を有する基板上に複数の発光素子を有する発

光装置であり、発光素子は、第1の電極と、該第1の電極の端部を覆う隔壁と、前記第1

の電極上に有機化合物を含む層と、該有機化合物を含む層上に第2の電極とを有し、前記

隔壁は、発光素子上面から基板に向かって裾広がりの断面形状を有し、隔壁の側面に段差

を有していることを特徴とする発光装置である。

【0019】

また、上記構成において、前記隔壁の上端部は、丸みを有することを特徴の一つとして

いる。隔壁の上端部に丸みを有するとは、隔壁が、基板面に垂直な面で切断した場合にお

いて、隔壁の内部に位置する曲率中心により決まる曲面を有し、その曲率半径が0.2μ

m以上3μm以下であることを指している。隔壁の上端部が丸みを有するように形成する

には、隔壁を形成する際に隔壁の材料として感光性の樹脂を用いて選択的に露光を行うこ

とが好ましい。また、ウェットエッチングにより隔壁の上端部に丸みを形成してもよい。

また、隔壁の断面形状において、上端部と下端部との2箇所に隔壁の内部に位置する曲率

中心により決まる2つの曲面を有し、その2箇所の間には隔壁の外側に位置する曲率中心

により決まる1つの曲面も有している。

【0020】

また、上記構成において、前記裾広がりの断面形状を有している隔壁は単層であること

を特徴の一つとしている。積層構造ではないため、隔壁の作製工程が簡略である。

【0021】

また、上述した課題の解決手段とは、他の解決手段として、発光素子が配置される画素

部、即ち、表示領域の周りに蒸着マスクを支持する構造物を形成してもよい。本明細書で

は、ある発光素子と、その他の発光素子の間に形成される保護層を隔壁と呼ぶ。また、本

明細書では、画素部の中心から離れて配置された発光素子の外側に位置する絶縁物であり

、且つ、その絶縁物の外側に発光素子が配置されていない絶縁物を構造物と呼ぶ。表示領

域の面積が小さい場合には、表示領域の周りに蒸着マスクを支持する構造物を形成するこ

とによって、蒸着マスクのよじれやたわみなどによって画素電極表面に接してしまうこと

を防止することができる。

【0022】

本発明の他の構成は、絶縁表面を有する基板上に複数の発光素子を有する画素部を備え

た発光装置であり、発光素子は、第1の電極と、該第1の電極の端部を覆う隔壁と、前記

第1の電極上に有機化合物を含む層と、該有機化合物を含む層上に第2の電極とを有し、

前記隔壁と同じ材料である構造物が前記画素部を囲むように配置され、前記構造物の膜厚

と前記隔壁の膜厚は異なることを特徴とする発光装置である。

【0023】

また、上述した構造物を前述した裾広がりの断面形状を有する隔壁と同一材料を用いて同

一工程で形成することもでき、上記構成において、前記隔壁は、突出した部分を有してい

ることを特徴の一つとしている。また、前記隔壁は、発光素子上面から基板に向かって裾

広がりの断面形状を有し、隔壁の側面に段差を有している。

【0024】

また、対向する基板を用いて発光素子の封止を行う場合、前記構造物が一対の基板の間隔

を保持するようにしてもよい。上記構成において、前記発光装置は、前記絶縁表面を有す

る基板に対向する基板を有し、この一対の基板の間隔を前記構造物が保持することを特徴

の一つとしている。この構成は、特に、対向する基板として透光性基板を用い、発光素子

からの発光をその透光性基板を通過させて表示を行う場合に有効である。前記構造物によ

って一対の基板間隔を均一とすることができるため、高精細な表示が実現できる。

【0025】

また、上記構成において、前記構造物と、一対の基板とで囲まれる領域は樹脂で充填され

ることを特徴の一つとしている。この構成は、特に、対向する基板として透光性基板を用

い、発光素子からの発光をその透光性基板を通過させて表示を行う場合に有効である。ま

た、透明な樹脂を一対の基板間に充填することによって、一対の基板間を空間(不活性気

体)とした場合に比べて全体の透過率を向上させることができる。

【0026】

また、上述した構造物や上述した隔壁の他にも様々な構造物、例えば、封止基板と貼り合

わせる際に密着性を上げるための凸部などを同一材料を用いて同一工程で形成することも

できる。

【0027】

また、上記構造を実現するための発明の構成は、絶縁表面を有する基板上に第1の電極

を形成し、前記第1の電極の端部上に、回折格子パターン、或いは半透部を有するフォト

マスク又はレチクルを用いて、膜厚の厚い領域と、該領域より膜厚の薄い領域を有する隔

壁を形成し、前記第1の電極上に有機化合物を含む層を形成し、前記有機化合物を含む層

上に第2の電極を形成することを特徴とする発光装置の作製方法である。

【0028】

また、上記作製工程において、前記隔壁は、回折格子パターン、或いは半透部を有する

フォトマスク又はレチクルを用いて選択的に露光現像して形成した樹脂であることを特徴

の一つとしている。

【0029】

また、上記作製工程において、前記第1の電極上に有機化合物を含む層を形成する工程

は、蒸着法、具体的には蒸着マスクを用いた抵抗加熱法を用いた場合に隔壁の膜厚の厚い

領域が蒸着マスクのたわみなどを防ぐことが可能となるため有効である。また、有機化合

物を含む層は、蒸着法に限定されず、スピンコート法、インクジェット法、ディップ法、

電解重合法等が挙げられる。

【0030】

また、他の作製方法に関する発明の構成は、絶縁表面を有する基板上に複数の薄膜トラ

ンジスタおよび複数の発光素子を有する発光装置の作製方法であり、絶縁表面を有する第

1の基板上にソース領域、ドレイン領域、およびその間のチャネル形成領域を有する半導

体層と、ゲート絶縁膜と、ゲート電極とを有する薄膜トランジスタを形成し、前記ゲート

絶縁膜上方に前記ソース領域または前記ドレイン領域と電気的に接続する第1の電極を形

成し、前記第1の電極の端部を覆う隔壁と、複数の発光素子を囲む位置に構造物とを形成

し、前記第1の電極上に有機化合物を含む層を形成し、前記有機化合物を含む層上に第2

の電極を形成し、前記構造物で基板間隔を保つように、第2の基板を樹脂材料で前記第1

の基板に貼り合せて前記発光素子を封止することを特徴とする発光装置の作製方法である

。

【0031】

また、上記作製工程において、前記隔壁および前記構造物は、同一材料であり、回折格

子パターン、或いは半透部を有するフォトマスク又はレチクルを用いて選択的に露光現像

して形成した樹脂であることを特徴の一つとしている。前記構造物は、隔壁と同一工程で

形成することができるため、工程数を増やすことなく形成することができる。

【0032】

また、本発明は、スイッチング素子を有するアクティブマトリクス型の発光装置に限定

されず、パッシブ型の発光装置にも適用することができる。

【0033】

なお、本明細書中における発光装置とは、画像表示デバイス、発光デバイス、もしくは光

源(照明装置含む)を指す。また、発光装置にコネクター、例えばFPC(Flexib

le printed circuit)もしくはTAB(Tape Automate

d Bonding)テープもしくはTCP(Tape Carrier Packag

e)が取り付けられたモジュール、TABテープやTCPの先にプリント配線板が設けら

れたモジュール、または発光素子にCOG(Chip On Glass)方式によりI

C(集積回路)が直接実装されたモジュールも全て発光装置に含むものとする。

【発明の効果】

【0034】

本発明は、工程を増やすことなく、第1の電極端部を覆う隔壁や、画素部を囲む構造物を

設けることによって、蒸着時に用いるマスクの精度とたわみなどによる不良を防ぐことが

できる。

【0035】

また、本発明は、隔壁のサイズ、特に隔壁の占める平面面積を縮小し、サイズの小さな隔

壁およびその隔壁を備えた発光装置を実現できる。特に、この隔壁を用いて蒸着マスクと

第1の電極との間隔を近づければ近づけるほど、蒸着膜の回り込みが抑えられ、蒸着膜の

塗り分け精度を上げることができる。なお、蒸着膜の回り込みとは、蒸着マスクを用いて

蒸着を行う際、蒸着マスクの開口部分の面積よりも広い領域に蒸着膜が形成されてしまう

ことを指している。本発明により、発光装置の高精細化(画素数の増大)及び小型化に伴

う各表示画素ピッチの微細化を進めることができる。本発明の隔壁は、蒸着マスクと第1

の電極との間隔を近づけ、且つ、第1の電極と蒸着マスクの接触を確実に防止することが

できる。従って、さらに厚さが薄く設計された蒸着マスクを用いることも可能となる。

【図面の簡単な説明】

【0036】

【図1】本発明の工程断面図を示す図。

【図2】蒸着装置の一例を示す図。

【図3】本発明の断面構造の一例を示す図。

【図4】本発明の断面構造の一例を示す図。

【図5】発光装置の作製工程を示す図。

【図6】発光装置の作製工程を示す図。

【図7】発光装置の作製工程を示す図。

【図8】発光装置の作製工程を示す図。

【図9】発光装置の作製工程を示す図。

【図10】アクティブマトリクス型発光装置の構成を示す図。

【図11】画素領域の上面図の一例

【図12】本発明が適用される電子機器を示す図。

【図13】本発明が適用される電子機器を示す図。

【図14】本発明が適用される電子機器を示す図。

【図15】本発明が適用される電子機器を示す図。

【図16】本発明の断面構造の一例を示す図。

【発明を実施するための形態】

【0037】

本発明の実施の形態について、図面を用いて詳細に説明する。但し、本発明は以下の説明

に限定されず、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々

に変更し得ることは当業者であれば容易に理解される。従って、本発明は以下に示す実施

の形態の記載内容に限定して解釈されるものではない。なお、以下に説明する本発明の構

成において、同一部分又は同様な機能を有する部分には同一の符号を異なる図面間で共通

して用い、その繰り返しの説明は省略する。

【0038】

(実施の形態1)

ここではアクティブマトリクス型発光装置の例を用いて本発明を説明する。

【0039】

また、図1(C)の構造を得るための作製工程の一例を以下に示す。

【0040】

まず、絶縁表面を有する基板10上にTFT16を作製する。TFT16の下地絶縁膜1

2およびゲート絶縁膜を含む絶縁膜の積層17としては、スパッタ法、またはPCVD法

により得られる無機材料(酸化シリコン、窒化シリコン、酸化窒化シリコン、SiOF膜

、SiONF膜など)を用いる。また、層間絶縁膜として機能する絶縁膜18は、スパッ

タ法、PCVD法、または塗布法により得られる無機材料(酸化シリコン、窒化シリコン

、酸化窒化シリコン、SiOF膜、SiONF膜など)、或いは塗布法により得られる感

光性または非感光性の有機材料(ポリイミド、アクリル、ポリアミド、ポリイミドアミド

、レジストまたはベンゾシクロブテン)、或いは塗布法により得られるSOG膜(シロキ

サン構造を有する絶縁膜)、またはこれらの積層などを適宜用いることができる。TFT

16は公知の方法でnチャネル型TFTまたはpチャネル型TFTを作製すればよい。

【0041】

次いで、絶縁膜18に対してエッチングを行ってTFTの電極に達する開口を形成した後

、陽極となる第1の電極13をTFTの電極と一部重なるように形成する。ここでは、第

1の電極13として、仕事関数の大きい導電膜(ITO(酸化インジウム酸化スズ合金)

、酸化インジウム酸化亜鉛合金(In2O3―ZnO)、酸化亜鉛(ZnO)等)を用い

、ウエットエッチングで形成する。第1の電極13を選択的にエッチングする際、絶縁膜

18と選択比が取れるようにエッチング条件または材料を適宜設定する。

【0042】

次いで、塗布法により絶縁膜を全面に形成した後、回折格子パターン或いは半透膜から

なる光強度低減機能を有する補助パターンを設置したフォトマスクまたはレチクルを用い

て隔壁11を形成する。隔壁11は、TFTの電極に達する開口と重なる位置に形成する

。隔壁11をTFTの電極に達する開口と重なる位置に形成すると隔壁と第1の電極との

密着性が向上するため好ましい。ここでは感光性の樹脂膜20を全面に形成した後、半透

膜からなる光強度低減機能を有する補助パターンを設置したフォトマスクを用いて露光し

た例を図1(A)に示す。

【0043】

図1(A)において、露光マスク400は、Crなどの金属膜からなる遮光部401と、

光強度低減機能を有する補助パターンとして、半透膜が設けられた部分(半透部とも呼ぶ

)402とが設置されている。露光マスクの断面図において、遮光部401の幅はt2と

示し、半透膜が設けられた部分402の幅はt1と示している。半透膜が設けられた部分

402において遮光部401と重なっている部分は、光は透過しない。ここでは露光マス

クの一部として半透膜を用いた例を示したが、回折格子パターンを用いてもよい。

【0044】

図1(A)に示す露光マスクを用いて感光性の樹脂膜20の露光を行うと、非露光領域と

露光領域が形成される。露光時には、光が遮光部401の回り込みや、半透膜が設けられ

た部分402を通過することによって図1(A)の点線に示す露光領域が形成される。そ

して、露光領域を除去すると裾広がりの断面形状を有する隔壁11が形成される。即ち、

図1(A)に示すように、隔壁11は、膜厚の厚い部分と、膜厚の薄い部分を有している

。隔壁における膜厚の薄い部分は、膜厚の厚い部分の少なくとも半分以下の膜厚とする。

ただし、膜厚の厚い部分とは、絶縁膜18の平坦な面から測定した膜厚の厚い部分を指し

ている。なお、隔壁11の高さ(即ち、膜厚の厚い部分の高さ)が2μm以上だと、カバ

レッジ不良が生じやすいので、隔壁11の高さは低い(2μm未満)ほうが好ましい。ま

た、図1(A)に示すように、TFTの電極に達する開口と重なる隔壁11とは幅の異な

る隔壁が配線19の上方に形成される。

【0045】

また、ここでは感光性の樹脂膜20を用いて形成する例を示したが、絶縁膜を全面に形

成した後、回折格子パターン或いは半透膜からなる光強度低減機能を有する補助パターン

を設置したフォトマスクまたはレチクルを用いてレジストマスクを形成し、レジストマス

クをマスクとしてエッチングを行って裾広がりの断面形状を有する隔壁11を形成しても

よい。

【0046】

次いで、有機化合物を含む層14を蒸着法で形成する。蒸着法で形成する場合には、図

1(B)に示すように蒸着マスク21を用いて選択的に有機化合物を含む層14を形成す

る。なお、図1(B)は、実際に蒸着を行う際とは上下方向を逆に示している。蒸着を行

う場合は、基板ホルダーと蒸着マスクの間に基板を挟み、基板ホルダーに設置された永久

磁石によってメタルからなる蒸着マスクを引きつけて基板を固定し、露呈している第1の

電極面の下方に蒸着源が位置するようにして蒸着が行われる。

【0047】

図1(B)では、有機化合物を含む層14は単層として示しているが、正孔注入層(また

は正孔輸送層)、発光層、電子注入層(または電子輸送層)などが積層された積層構造で

ある。なお、信頼性を向上させるため、有機化合物を含む層14の形成直前に真空加熱(

100℃〜250℃)を行って脱気を行うことが好ましい。例えば、蒸着法を用いる場合

、真空度が5×10−3Torr(0.665Pa)以下、好ましくは10−4〜10−

6Paまで真空排気された成膜室で蒸着を行う。蒸着の際、予め、抵抗加熱により有機化

合物は気化されており、蒸着時にシャッターが開くことにより基板の方向へ飛散する。気

化された有機化合物は、上方に飛散し、蒸着マスクに設けられた開口部を通って基板に蒸

着される。

【0048】

図2に蒸着装置の一例を示す。

【0049】

図2(A)に示す蒸着装置は、成膜室に蒸着材料の昇華方向を維持するために防着シール

ドが設けられており、開口部が複数設けられ、それらの開口部から蒸着材料が昇華する機

構となっている。防着シールドの下方には、基板の移動方向(搬送方向とも呼ぶ)とは垂

直な方向に移動可能な蒸着源を有している。また、防着シールドの幅Wbは、基板の幅W

aよりも広くさせて、蒸着膜の膜厚均一性を向上させている。以下に蒸着装置の機構を簡

略に示す。

【0050】

基板701は、予め蒸着マスク702と位置合わせされており、位置合わせされたまま基

板の搬送方向706a(図2(A)中の矢印の方向)に基板が搬送される。基板は搬送さ

れて、防着シールド703aの上方を通過する。防着シールド703aは開口部703b

を有しており、蒸着源704からの蒸着材料が開口部703bから昇華するようになって

いる。開口部703bから蒸着材料の昇華方向706bを維持するために防着シールド7

03aは、防着シールド自体には付着しないように加熱されている。また、蒸着シールド

に接してヒーターが設けられている。蒸着シールドの加熱温度はヒーターと接続している

コンピュータで制御しても良い。

【0051】

蒸着源704は複数のルツボが設置できるようになっており、さらに矢印の方向(蒸着源

の移動方向705)に移動することが可能である。なお、蒸着源は移動させる代わりに、

蒸着源の向きを変えて蒸着される角度を変えても良い。蒸着方法は、抵抗加熱法を用いる

。また、蒸着源が移動する範囲は基板の幅Waよりも広いことが望ましい。また、防着シ

ールドの幅Wbも基板の幅Waよりも広くすることが蒸着膜の膜厚均一性を向上させる。

【0052】

なお、図2(A)の蒸着装置において、開口部703bの形状や数は特に限定されない

。

【0053】

また、蒸着源のルツボに蒸着材料を補給するため、成膜室にゲートを介して連結する設

置室を設けてもよい。蒸着源にはルツボを加熱するヒーターが設けられている。また、一

つの成膜室に複数の蒸着源と防着シールドを設けてもよい。複数のルツボを設けた一つの

蒸着源を設け、設置室を設けた場合の蒸着装置の上面図を図2(B)に示す。蒸着源の移

動方向705に設置室707を設置し、蒸着材料を補給する際には、蒸着源を設置室まで

移動させて補給を行えばよい。蒸着源が成膜室に固定されている場合には、蒸着源に蒸着

材料を補給するためには成膜室内を大気圧としなければならず、再度蒸着するためには成

膜室内を真空にするのに時間を要してしまう。設置室707を設ければ、成膜室700の

真空度を維持したまま、設置室内のみを大気圧と真空とに切り替えればよいため、短時間

で蒸着材料の補給が可能となる。

【0054】

また、ここでは一つの成膜室に一つの蒸着源を設けた例を示したが、一つの成膜室に2以

上の数の蒸着源を設けてもよい。

【0055】

また、蒸着の際、隔壁11の膜厚の厚い部分、即ち頂部は、蒸着マスクと接して間隔を保

持する機能を有している。また、隔壁11が第1の電極を囲むように配置されている場合

、マスクの下方において開口が設けられていない領域、例えば隣の画素への蒸着を防ぐこ

とができる。なお、隔壁11は、各第1の電極の端部を覆い、絶縁膜18上に接して形成

され、且つ、第1の電極が隣り合う電極と絶縁し、短絡するのを防止している。また、隔

壁11の膜厚の厚い部分、即ち頂部は、TFTの電極に達する開口と重なる位置と重なる

。

【0056】

この隔壁11の幅が大きいと、開口率が低下するため、できるだけ隔壁の上面形状を小さ

くして開口率向上、且つ、高精細化を図ることが好ましい。また、有機化合物を含む層1

4を隔壁11における膜厚の薄い部分とも一部重ねることで、隔壁の下方に形成されてい

る第1の電極と、後に形成する第2の電極とが短絡することをより効果的に防ぐことがで

きる。即ち、有機化合物を含む層14のうち、隔壁11と重なる部分、即ち発光に寄与し

ない部分は、隔壁の一部としても機能する。

【0057】

次いで、有機化合物を含む層14上に陰極となる第2の電極15を形成する。第2の電

極15を形成する際にも蒸着マスクを用いるが、蒸着マスクの開口部分と対応する箇所が

画素部全域である場合、画素部以外に形成した構造物が蒸着マスクとの間隔を保持する。

【0058】

以上の工程で図1(C)に示す構造を得ることができる。また、有機化合物を含む層14

や第2の電極15の成膜方法は、TFT16にダメージを与えない抵抗加熱法が好ましく

、塗布法(インクジェット法やスピンコート法など)も用いることができる。また、有機

化合物を含む層14は、塗布法で形成した膜と蒸着法による膜と積層してもよく、例えば

、正孔注入層として作用するポリ(エチレンジオキシチオフェン)/ポリ(スチレンスル

ホン酸)水溶液(PEDOT/PSS)、或いはポリアニリン/ショウノウスルホン酸水

溶液(PANI/CSA)、PTPDES、Et−PTPDEK、またはPPBAなどを

スピンコート法で塗布、焼成した後、蒸着法により発光層、電子輸送層などを積層しても

よい。

【0059】

図1(C)において、10は基板、11は隔壁、12は下地絶縁膜、13は第1の電極、

14は有機化合物を含む層、15は第2の電極、16はTFT、17はゲート絶縁膜を含

む絶縁膜の積層、18は絶縁膜、19は電源供給線などの配線である。なお、図1(C)

では第1の電極13は発光素子の陽極として機能させ、第2の電極は発光素子の陰極とし

て機能させているが、特に限定されず、材料を適宜選択すれば第1の電極を陰極として機

能させ、第2の電極を陽極として機能させることも可能である。

【0060】

また、本発明は図1(A)のTFT構造に限定されず、必要があればチャネル形成領域

とドレイン領域(またはソース領域)との間にLDD領域を有する低濃度ドレイン(LD

D:Lightly Doped Drain)構造としてもよい。この構造はチャネル

形成領域と、高濃度に不純物元素を添加して形成するソース領域またはドレイン領域との

間に低濃度に不純物元素を添加した領域を設けたものであり、この領域をLDD領域と呼

んでいる。さらにゲート絶縁膜を介してLDD領域をゲート電極と重ねて配置させた、い

わゆるGOLD(Gate−drain Overlapped LDD)構造としても

よい。

【0061】

また、ここではnチャネル型TFTを用いて説明したが、n型不純物元素に代えてp型

不純物元素を用いることによってpチャネル型TFTを形成することができることは言う

までもない。

【0062】

また、ここでは、トップゲート型TFTを用いて一例を説明したが、TFT構造に関係な

く本発明を適用することが可能であり、例えばボトムゲート型(逆スタガ型)TFTや順

スタガ型TFTに適用することが可能である。

【0063】

また、本明細書において、TFTの活性層となる半導体層は、珪素を主成分とする半導

体膜、有機材料を主成分とする半導体膜、或いは金属酸化物を主成分とする半導体膜を用

いることができる。珪素を主成分とする半導体膜としては、非晶質半導体膜、結晶構造を

含む半導体膜、非晶質構造を含む化合物半導体膜などを用いることができる。具体的には

珪素を主成分とする半導体膜としてアモルファスシリコン、微結晶シリコン、多結晶シリ

コンなどを用いることができる。また、有機材料を主成分とする半導体膜としては、他の

元素と組み合わせて一定量の炭素または炭素の同素体(ダイヤモンドを除く)からなる物

質を主成分とする半導体膜を用いることができる。具体的には、ペンタセン、テトラセン

、チオフェンオリゴマ誘導体、フェニレン誘導体、フタロシアニン化合物、ポリアセチレ

ン誘導体、ポリチオフェン誘導体、シアニン色素等が挙げられる。また、金属酸化物を主

成分とする半導体膜としては、酸化亜鉛(ZnO)や亜鉛とガリウムとインジウムの酸化

物(In−Ga−Zn−O)等を用いることができる。

【0064】

(実施の形態2)

本実施の形態では、本実施の形態1とは構造が一部異なる例を図3に示す。

【0065】

ここでは、図1の層間絶縁膜を1層減らした構造、具体的には図1に示す絶縁膜18を

形成しない構造を示す。なお、図3において図1と同じ箇所には同じ符号を用いる。

【0066】

実施の形態1と同様にして絶縁表面を有する基板10上にTFT16を作製する。次い

で、ゲート絶縁膜を含む絶縁膜の積層17上に陽極となる第1の電極33を形成する。第

1の電極33は、ゲート絶縁膜を含む絶縁膜の積層17上に、TFTのソース領域または

ドレイン領域と電気的に接続する電極と一部接して重なるように形成される。

【0067】

次いで、塗布法により絶縁膜を全面に形成した後、回折格子パターン或いは半透膜から

なる光強度低減機能を有する補助パターンを設置したフォトマスクまたはレチクルを用い

て隔壁31を形成する。隔壁31は、膜厚の厚い部分と、膜厚の薄い部分を有している。

また、隔壁31は、ゲート絶縁膜を含む絶縁膜の積層17上に接して設けられ、電源供給

線などの配線19と接した状態で覆う。

【0068】

次いで、有機化合物を含む層34を蒸着法で形成する。また、図1において、有機化合

物を含む層14は、隔壁11における膜厚の薄い部分と一部重なる例を示したが、図3で

は、有機化合物を含む層34は、隔壁31における厚い部分とも重なる例を示している。

図3で示すように有機化合物を含む層34が隔壁31における厚い部分とも重なるのは、

基板面と垂直な面で切断した断面において、蒸着マスクの遮蔽部分の幅が隔壁31の膜厚

の厚い部分の幅よりも狭いものを用いているためである。本発明において蒸着マスクの遮

蔽部分の幅が隔壁の幅より狭くてもよいし、同じでもよいし、広くてもよい。また、有機

化合物を含む層34を隔壁31における膜厚の厚い部分とも一部重ねることで、隔壁の下

方に形成されているTFTと、後に形成する第2の電極とが短絡することを効果的に防ぐ

ことができる。

【0069】

次いで、有機化合物を含む層34上に陰極となる第2の電極15を形成する。

【0070】

以上の工程で図3に示す構造を得ることができる。

【0071】

このように、図3に示す構造は、図1に比べて少ない工程数で発光装置を作製することが

できる。

【0072】

本実施の形態は、実施の形態1と自由に組み合わせることができる。

【0073】

(実施の形態3)

本実施の形態では、複数の発光素子が配置された画素部(表示領域とも呼ぶ)に設ける隔

壁と、画素部の周りを囲むように配置する構造物とを設ける例を示す。

【0074】

ここでは、図4(A)及び図4(B)を用いて、パッシブマトリクス型の発光装置を作製

する例を示す。

【0075】

第1の基板301上に、第1の電極303が形成され、その端部を覆うように隔壁30

2が形成される。また、隔壁302と同一工程で構造物304が形成される。隔壁302

と構造物304は膜厚が異なる。この段階での断面図を図4(A)に示す。

【0076】

次いで、第1の電極303上に有機化合物を含む層305を形成し、その上に第2の電

極307を形成する。なお、有機化合物を含む層305を蒸着法で形成する際、構造物3

04は、蒸着マスクと第1の電極303とが接触しないように防止することができる。ま

た、蒸着マスクと隔壁302とが接触しないように防止することもできる。

【0077】

そして、第2の基板308と第1の基板301とを接着層309で貼り合わせて封止す

る。

【0078】

図4(B)に示すように、第1の基板301上に画素部306の周りを囲むように配置す

る構造物304は、第2の基板308を用いて封止する場合、一対の基板間隔を保持する

ことができる。また、構造物と一対の基板とで囲まれた領域を密閉して画素部を封止する

こともできる。即ち、構造物304は、外部からの不純物や水分の侵入を防止することが

できる。

【0079】

隔壁302と構造物304は、回折格子パターン、或いは半透部を有するフォトマスク又

はレチクルを用いて同じ工程で形成する。

【0080】

また、アクティブマトリクス型の発光装置を作製する場合には、同様に複数の発光素子が

配置された画素部(表示領域とも呼ぶ)に設ける隔壁と、画素部の周りを囲むように配置

する構造物とを形成すればよい。

【0081】

アクティブマトリクス型の発光装置を作製する場合は、画素に配置するTFTと同一工程

で駆動回路の一部をTFTで形成することもできる。その場合、画素部の周りに駆動回路

を配置することになる。また、その駆動回路と重なる位置に構造物を形成してもよい。

【0082】

本実施の形態は、実施の形態1または実施の形態2と自由に組み合わせることができる

。

【0083】

例えば、隔壁を裾状として、隔壁の一部を構造物と同じ膜厚とすることで、隔壁と構造

物との両方で一対の基板間隔を保持することができる。一つの画素を囲むような上面形状

を有する隔壁を設ける場合、第2基板と隔壁とで一つの画素を密閉して封止することがで

き、その周りを構造物でさらに密閉して封止することができる。このように二重に密閉す

ることで高信頼性を有する発光装置を実現することができる。また、発光装置が外部から

の衝撃を受けた場合、一対の基板が隔壁と構造物とで支えられているため、衝撃の力を分

散することができる。従って、丈夫な発光装置を提供することができる。

【0084】

(実施の形態4)

本実施の形態は、TFTを作製し、感光性の樹脂膜を全面に形成した後、半透膜からな

る光強度低減機能を有する補助パターンを設置したフォトマスクを用いて隔壁を形成し、

発光装置を完成させるまでの工程について以下に示す。

【0085】

まず、絶縁表面を有する基板100の上に下地膜として、スパッタリング法、PVD法

(Physical Vapor Deposition)、減圧CVD法(LPCVD

法)、またはプラズマCVD法等のCVD法(Chemical Vapor Depo

sition)などにより窒化酸化珪素膜(SiNO)を用いて下地膜101aを10〜

200nm(好ましくは50〜100nm)形成し、酸化窒化珪素膜(SiON)を用い

て下地膜101bを50〜200nm(好ましくは100〜150nm)積層する。本実

施の形態では、プラズマCVD法を用いて下地膜101a、下地膜101bを形成する。

基板100としてはガラス基板、石英基板やシリコン基板、金属基板、またはステンレス

基板の表面に絶縁膜を形成したものを用いて良い。また、本実施の形態の処理温度に耐え

うる耐熱性を有するプラスチック基板を用いてもよいし、フィルムのような可撓性基板を

用いても良い。プラスチック基板としてはPET(ポリエチレンテレフタレート)、PE

N(ポリエチレンナフタレート)、PES(ポリエーテルスルホン)からなる基板、可撓

性基板としてはアクリル等の合成樹脂を用いることができる。

【0086】

下地膜としては、酸化珪素、窒化珪素、酸化窒化珪素、窒化酸化珪素などを用いることが

でき、単層でも2層、3層といった積層構造でもよい。なお本明細書中において酸化窒化

珪素とは酸素の組成比が窒素の組成比より大きい物質であり、窒素を含む酸化珪素とも言

える。同様に、窒化酸化珪素とは、窒素の組成比が酸素の組成比より大きい物質であり、

酸素を含む窒化珪素とも言える。本実施の形態では、基板上にSiH4、NH3、N2O

、N2及びH2を反応ガスとして窒化酸化珪素膜を膜厚50nm形成し、SiH4及びN

2Oを反応ガスとして酸化窒化珪素膜を膜厚100nmで形成する。また窒化酸化珪素膜

の膜厚を140nm、積層する酸化窒化珪素膜の膜厚を100nmとしてもよい。

【0087】

次いで、下地膜上に半導体膜を形成する。半導体膜は25〜200nm(好ましくは

30〜150nm)の厚さで公知の手段(スパッタ法、LPCVD法、またはプラズマC

VD法等)により成膜すればよい。本実施の形態では、非晶質半導体膜を、レーザ結晶化

し、結晶性半導体膜とするものを用いるのが好ましい。結晶性半導体膜を用いる場合、そ

の結晶性半導体膜の作製方法は、公知の方法(レーザ結晶化法、熱結晶化法、またはニッ

ケルなどの結晶化を助長する元素を用いた熱結晶化法等)を用いれば良い。

【0088】

連続発振が可能な固体レーザを用い、基本波の第2高調波〜第4高調波のレーザ光を照射

することで、大粒径の結晶を得ることができる。例えば、代表的には、Nd:YVO4レ

ーザ(基本波1064nm)の第2高調波(532nm)や第3高調波(355nm)を

用いるのが望ましい。具体的には、連続発振のYVO4レーザから射出されたレーザ光を

非線形光学素子により高調波に変換し、出力数W以上のレーザ光を得る。そして、好まし

くは光学系により照射面にて矩形状または楕円形状のレーザ光に成形して、半導体膜に照

射する。このときのパワー密度は0.001〜100MW/cm2程度(好ましくは0.

1〜10MW/cm2)が必要である。そして、走査速度を0.5〜2000cm/se

c程度(好ましくは10〜200cm/sec)とし、照射する。

【0089】

レーザのビーム形状は、線状とすると好ましい。その結果、スループットを向上させ

ることができる。またさらにレーザは、半導体膜に対して入射角θ(0<θ<90度)を

持たせて照射させるとよい。レーザの干渉を防止することができるからである。

【0090】

このようなレーザと、半導体膜とを相対的に走査することにより、レーザ照射を行う

ことができる。またレーザ照射において、ビームを精度よく重ね合わせたり、レーザ照射

開始位置やレーザ照射終了位置を制御するため、マーカーを形成することもできる。マー

カーは非晶質半導体膜と同時に、基板上へ形成すればよい。

【0091】

なおレーザは、連続発振またはパルス発振の気体レーザ、固体レーザ、銅蒸気レーザ

または金蒸気レーザなどを用いることができる。気体レーザとして、エキシマレーザ、A

rレーザ、Krレーザ、He−Cdレーザなどがあり、固体レーザとして、YAGレーザ

、YVO4レーザ、YLFレーザ、YAlO3レーザ、Y2O3レーザ、ガラスレーザ、

ルビーレーザ、アレキサンドライトレーザ、Ti:サファイアレーザなどが挙げられる。

【0092】

半導体膜を形成する材料は、シランやゲルマンに代表される半導体材料ガスを用いて気相

成長法やスパッタリング法で作製される非晶質半導体(以下「アモルファス半導体:AS

」ともいう。)、該非晶質半導体を光エネルギーや熱エネルギーを利用して結晶化させた

多結晶半導体、或いはセミアモルファス(微結晶若しくはマイクロクリスタルとも呼ばれ

る。以下「SAS」ともいう。)半導体などを用いることができる。

【0093】

また、パルス発振のレーザ光の発振周波数を0.5MHz以上とし、通常用いられて

いる数十Hz〜数百Hzの周波数帯よりも著しく高い周波数帯を用いてレーザ結晶化を行

っても良い。パルス発振でレーザ光を半導体膜に照射してから半導体膜が完全に固化する

までの時間は数十nsec〜数百nsecと言われている。よって上記周波数帯を用いる

ことで、半導体膜がレーザ光によって溶融してから固化するまでに、次のパルスのレーザ

光を照射できる。したがって、半導体膜中において固液界面を連続的に移動させることが

できるので、走査方向に向かって連続的に成長した結晶粒を有する半導体膜が形成される

。具体的には、含まれる結晶粒の走査方向における幅が10〜30μm、走査方向に対し

て垂直な方向における幅が1〜5μm程度の結晶粒の集合を形成することができる。該走

査方向に沿って長く延びた単結晶の結晶粒を形成することで、少なくとも薄膜トランジス

タのチャネル方向には結晶粒界のほとんど存在しない半導体膜の形成が可能となる。

【0094】

また、希ガスや窒素などの不活性ガス雰囲気中でレーザ光を照射するようにしても良い。

これにより、レーザ光の照射による半導体表面の荒れを抑えることができ、界面準位密度

のばらつきによって生じるしきい値のばらつきを抑えることができる。

【0095】

非晶質半導体膜の結晶化は、熱処理とレーザ光照射による結晶化を組み合わせてもよく、

熱処理やレーザ光照射を単独で、複数回行っても良い。

【0096】

本実施の形態では、下地膜101b上に、非晶質半導体膜を形成し、非晶質半導体膜を結

晶化させることによって結晶性半導体膜を形成する。非晶質半導体膜としては、SiH4

、H2の反応ガスにより形成する非晶質珪素を用いる。本実施の形態において、下地膜1

01a、下地膜101b、非晶質半導体膜は、同チャンバー内で真空を維持したままで3

30℃の同一温度下で、反応ガスを切り変えながら連続的に形成する。次いで、非晶質半

導体膜にレーザー光を照射、具体的には、レーザの繰り返し周波数が10MHz以上のレ

ーザ発振器から射出した基本波を用いて結晶性半導体膜を形成する。この時のレーザ光の

尖頭出力の範囲は、1GW/cm2〜1TW/cm2とする。ここまでの断面図を図5(

A)に示す。

【0097】

このようにして得られた結晶性半導体膜に対して、薄膜トランジスタのしきい値電圧を制

御するために微量な不純物元素(ボロンまたはリン)のドーピングを行ってもよい。この

不純物元素のドーピングは、結晶化工程の前の非晶質半導体膜に行ってもよい。非晶質半

導体膜の状態で不純物元素をドーピングすると、その後の結晶化のための加熱処理によっ

て、不純物の活性化も行うことができる。また、ドーピングの際に生じる欠陥等も改善す

ることができる。

【0098】

次に結晶性半導体膜102をマスクを用いて選択的にエッチングする。本実施の形態では

結晶性半導体膜102上に形成された酸化膜を除去した後、新たに酸化膜を形成する。そ

して、フォトマスクを作製し、フォトリソグラフィ法を用いたパターニング処理により、

半導体層103、半導体層104、半導体層105、及び半導体層106を形成する。

【0099】

次いで、半導体層上の酸化膜を除去し、半導体層103、半導体層104、半導体層10

5、及び半導体層106を覆うゲート絶縁層107を形成する。

【0100】

ゲート絶縁層107はプラズマCVD法またはスパッタ法などを用い、厚さを10〜15

0nmとして珪素を含む絶縁膜で形成する。ゲート絶縁層107としては、窒化珪素、酸

化珪素、酸化窒化珪素、窒化酸化珪素に代表される珪素の酸化物材料又は窒化物材料等の

公知の材料で形成すればよく、積層でも単層でもよい。本実施の形態では、ゲート絶縁層

は窒化珪素膜、酸化珪素膜、窒化珪素膜の3層の積層を用いる。またそれらや、酸化窒化

珪素膜の単層、2層からなる積層でも良い。好適には、緻密な膜質を有する窒化珪素膜を

用いるとよい。さらに半導体層とゲート絶縁層の間に、膜厚1〜100nm、好ましくは

1〜10nm、さらに好ましくは2〜5nmである膜厚の薄い酸化珪素膜を形成してもよ

い。薄い酸化珪素膜の形成方法としては、GRTA法、LRTA法等を用いて半導体領域

表面を酸化し、熱酸化膜を形成することで、膜厚の薄い酸化珪素膜を形成することができ

る。

【0101】

次いで、ゲート絶縁層107上にゲート電極層として用いる膜厚20〜100nmの第1

の導電膜108と、膜厚100〜400nmの第2の導電膜109とを積層して形成する

(図5(B)参照。)。

【0102】

第1の導電膜108及び第2の導電膜109は、スパッタリング法、蒸着法、CVD法等

の公知の手法により形成することができる。第1の導電膜108及び第2の導電膜109

はタンタル(Ta)、タングステン(W)、チタン(Ti)、モリブデン(Mo)、アル

ミニウム(Al)、銅(Cu)、クロム(Cr)、ネオジウム(Nd)から選ばれた元素

、又は前記元素を主成分とする合金材料もしくは化合物材料で形成すればよい。また、第

1の導電膜108及び第2の導電膜109としてリン等の不純物元素をドーピングした多

結晶シリコン膜に代表される半導体膜や、AgPdCu合金を用いてもよい。また、2層

構造に限定されず、例えば、第1の導電膜として膜厚50nmのタングステン膜、第2の

導電膜として膜厚500nmのアルミニウムとシリコンの合金(Al−Si)膜、第3の

導電膜として膜厚30nmの窒化チタン膜を順次積層した3層構造としてもよい。また、

3層構造とする場合、第1の導電膜のタングステンに代えて窒化タングステンを用いても

よいし、第2の導電膜のアルミニウムとシリコンの合金(Al−Si)膜に代えてアルミ

ニウムとチタンの合金膜(Al−Ti)を用いてもよいし、第3の導電膜の窒化チタン膜

に代えてチタン膜を用いてもよい。また、単層構造であってもよい。本実施の形態では、

第1の導電膜108として窒化タンタル(TaN)を膜厚30nm形成し、第2の導電膜

109としてタングステン(W)を膜厚370nm形成する。

【0103】

次いで、回折格子パターン或いは半透膜からなる光強度低減機能を有する補助パターン

を設置したフォトマスクまたはレチクルを用いてレジストマスクを形成し、第1の導電膜

108及び第2の導電膜109を選択的にエッチングし、第1のゲート電極層、導電層、

及び第2のゲート電極層をテーパー形状を有する様に形成する。レジストマスクは、膜厚

の厚い部分と膜厚の薄い部分を有し、後にチャネル形成領域が形成される部分とレジスト

マスクの膜厚の厚い部分とが重なる位置になるように形成する。そして、断面形状が裾状

の電極または配線が得られた後、レジストマスクを除去する。

【0104】

以上の工程によって、周辺駆動回路領域204に第1のゲート電極層121及び第2のゲ

ート電極層131からなるゲート電極層117、第1のゲート電極層122及び第2のゲ

ート電極層132からなるゲート電極層118、画素領域206に第1のゲート電極層1

24及び第2のゲート電極層134からなるゲート電極層127、第1のゲート電極層1

25及び第2のゲート電極層135からなるゲート電極層128、第1のゲート電極層1

26及び第2のゲート電極層136からなるゲート電極層129、接続領域205に導電

層123及び導電層133からなる導電層130を形成することができる(図5(C)参

照。)。本実施の形態では、ゲート電極層の形成をドライエッチングで行うがウェットエ

ッチングでもよい。

【0105】

なお、ゲート電極層を形成する際のエッチング工程によって、ゲート絶縁層107は多少

エッチングされ、膜厚が減る(いわゆる膜減り)ことがある。

【0106】

次に、ゲート電極層117、ゲート電極層118、ゲート電極層127、ゲート電極層1

28、ゲート電極層129、導電層130をマスクとして、n型を付与する不純物元素1

51を添加し、第1のn型不純物領域140a、第1のn型不純物領域140b、第1の

n型不純物領域141a、第1のn型不純物領域141b、第1のn型不純物領域142

a、第1のn型不純物領域142b、第1のn型不純物領域142c、第1のn型不純物

領域143a、第1のn型不純物領域143bを形成する(図6(A)参照。)。ここで

は、、不純物元素を含むドーピングガスとしてホスフィン(PH3)を用いて、第1のn

型不純物領域140a、第1のn型不純物領域140b、第1のn型不純物領域141a

、第1のn型不純物領域141b、第1のn型不純物領域142a、第1のn型不純物領

域142b、第1のn型不純物領域142c、第1のn型不純物領域143a、第1のn

型不純物領域143bに、n型を付与する不純物元素が1×1017〜5×1018/c

m3程度の濃度で含まれるように添加する。

【0107】

次に半導体層103、半導体層105の一部、半導体層106を覆うマスク153a

、マスク153b、マスク153c、及びマスク153dを形成する。マスク153a、

マスク153b、マスク153c、マスク153d、第2のゲート電極層132をマスク

としてn型を付与する不純物元素152を添加し、第2のn型不純物領域144a、第2

のn型不純物領域144b、第3のn型不純物領域145a、第3のn型不純物領域14

5b、第2のn型不純物領域147a、第2のn型不純物領域147b、第2のn型不純

物領域147c、第3のn型不純物領域148a、第3のn型不純物領域148b、第3

のn型不純物領域148c、第3のn型不純物領域148dが形成される(図6(B)参

照。)。ここでは、第2のn型不純物領域144a、第2のn型不純物領域144bにn

型を付与する不純物元素が5×1019〜5×1020/cm3程度の濃度で含まれるよ

うに添加する。第3のn型不純物領域145a、第3のn型不純物領域145bは、第3

のn型不純物領域148a、第3のn型不純物領域148b、第3のn型不純物領域14

8c、第3のn型不純物領域148dと同程度、もしくは少し高めの濃度でn型を付与す

る不純物元素を含むように形成される。また、半導体層104にチャネル形成領域146

、半導体層105にチャネル形成領域149a及びチャネル形成領域149bが形成され

る。

【0108】

第2のn型不純物領域144a、第2のn型不純物領域144b、第2のn型不純物領域

147a、第2のn型不純物領域147b、第2のn型不純物領域147cは高濃度n型

不純物領域であり、ソース、ドレインとして機能する。一方、第3のn型不純物領域14

5a、第3のn型不純物領域145b、第3のn型不純物領域148a、第3のn型不純

物領域148b、第3のn型不純物領域148c、第3のn型不純物領域148dは低濃

度不純物領域であり、LDD(LightlyDoped Drain)領域となる。n

型不純物領域145a、n型不純物領域145bは、ゲート絶縁層107を介して、第1

のゲート電極層122に覆われているのでLov領域であり、ドレイン近傍の電界を緩和

し、ホットキャリアによるオン電流の劣化を抑制することが可能である。この結果、高速

動作が可能な薄膜トランジスタを形成することができる。一方、第3のn型不純物領域1

48a、第3のn型不純物領域148b、第3のn型不純物領域148c、第3のn型不

純物領域148dはゲート電極層127、ゲート電極層128に覆われていないLoff

領域に形成されるため、ドレイン近傍の電界を緩和してホットキャリア注入による劣化を

防ぐとともに、オフ電流を低減する効果がある。この結果、信頼性の高く、低消費電力の

半導体装置を作製することが可能である。

【0109】

なお、本実施の形態では、不純物領域がゲート絶縁層を介してゲート電極層と重なる領域

をLov領域と示し、不純物領域がゲート絶縁層を介してゲート電極層と重ならない領域

をLoff領域と示す。

【0110】

次に、マスク153a、マスク153b、マスク153c及びマスク153dを除去し、

半導体層104、半導体層105を覆うマスク155a、マスク155bを形成する。マ

スク155a、マスク155b、ゲート電極層117及びゲート電極層129をマスクと

してp型を付与する不純物元素154を添加し、第1のp型不純物領域160a、第1の

p型不純物領域160b、第1のp型不純物領域163a、第1のp型不純物領域163

b、第2のp型不純物領域161a、第2のp型不純物領域161b、第2のp型不純物

領域164a、第2のp型不純物領域164bが形成される(図6(C)参照。)。本実

施の形態では、不純物元素としてボロン(B)を用いる。ここでは、第1のp型不純物領

域160a、第1のp型不純物領域160b、第1のp型不純物領域163a、第1のp

型不純物領域163b、第2のp型不純物領域161a、第2のp型不純物領域161b

、第2のp型不純物領域164a、第2のp型不純物領域164bにp型を付与する不純

物元素が1×1020〜5×1021/cm3程度の濃度で含まれるように添加する。本

実施の形態では、第2のp型不純物領域161a、第2のp型不純物領域161b、第2

のp型不純物領域164a、第2のp型不純物領域164bは、ゲート電極層117及び

ゲート電極層129の形状を反映し、自己整合的に第1のp型不純物領域160a、第1

のp型不純物領域160b、第1のp型不純物領域163a、第1のp型不純物領域16

3bより低濃度となるように形成する。また、半導体層103にチャネル形成領域162

、半導体層106にチャネル形成領域165が形成される。

【0111】

次いで、マスク155a、マスク155bをO2アッシングやレジスト剥離液により除

去し、酸化膜も除去する。

【0112】

次いで、不純物元素を活性化するために加熱処理、強光の照射、又はレーザ光の照射を

行う。活性化と同時にゲート絶縁層へのプラズマダメージやゲート絶縁層と半導体層との

界面へのプラズマダメージを回復することができる。

【0113】

次いで、ゲート電極層、ゲート絶縁層を覆う層間絶縁層を形成する。本実施の形態では、

絶縁膜167と絶縁膜168との積層構造とする(図7(A)参照。)。絶縁膜167と

して窒化酸化珪素膜を膜厚200nm形成し、絶縁膜168として酸化窒化絶縁膜を膜厚

800nm形成し、積層構造とする。また、ゲート電極層、ゲート絶縁層を覆って、酸化

窒化珪素膜を膜厚30nm形成し、窒化酸化珪素膜を膜厚140nm形成し、酸化窒化珪

素膜を膜厚800nm形成し、3層の積層構造としてもよい。本実施の形態では、絶縁膜

167及び絶縁膜168を下地膜と同様にプラズマCVD法を用いて連続的に形成する。

絶縁膜167及び絶縁膜168は窒化珪素膜に限定されるものでなく、スパッタ法、また

はプラズマCVDを用いた窒化酸化珪素膜、酸化窒化珪素膜、酸化珪素膜でもよく、他の

珪素を含む絶縁膜を単層または3層以上の積層構造として用いても良い。

【0114】

次いで、窒素雰囲気中で、300〜550℃で1〜12時間の熱処理を行い、半導体

層を水素化する工程を行う。好ましくは、400〜500℃で行う。この工程は層間絶縁

層である絶縁膜167に含まれる水素により半導体層のダングリングボンドを終端する工

程である。本実施の形態では、410度(℃)で加熱処理を行う。

【0115】

次いで、レジストからなるマスクを用いて絶縁膜167、絶縁膜168、ゲート絶縁層1

07に半導体層に達するコンタクトホール(開口部)を形成する。エッチングは、用いる

材料の選択比によって、一回で行っても複数回行っても良い。

【0116】

次いで、開口部を覆うように導電膜を形成し、導電膜をエッチングして各ソース領域又は

ドレイン領域の一部とそれぞれ電気的に接続するソース電極層又はドレイン電極層169

a、ソース電極層又はドレイン電極層169b、ソース電極層又はドレイン電極層170

a、ソース電極層又はドレイン電極層170b、ソース電極層又はドレイン電極層171

a、ソース電極層又はドレイン電極層171b、ソース電極層又はドレイン電極層172

a、ソース電極層又はドレイン電極層172b、配線層156を形成する。ソース電極層

又はドレイン電極層は、PVD法、CVD法、蒸着法等により導電膜を成膜した後、所望

の形状にエッチングして形成することができる。また、液滴吐出法、印刷法、電解メッキ

法等により、所定の場所に選択的に導電層を形成することができる。更にはリフロー法、

ダマシン法を用いても良い。ソース電極層又はドレイン電極層の材料は、Ag、Au、C

u、Ni、Pt、Pd、Ir、Rh、W、Al、Ta、Mo、Cd、Zn、Fe、Ti、

Zr、Ba等の金属又はその合金、若しくはその金属窒化物を用いて形成する。また、S

i、Geを含む導電材料を用いてもよい。また、これらの積層構造としても良い。本実施