発振器およびPLL回路

【課題】半導体集積回路上に小面積で形成でき、かつ、適切な周波数の発振信号を生成できる発振器と、これを用いたPLL回路を提供する。

【解決手段】発振器は、第1のノードと第2のノードと間に並列接続される抵抗と、反転増幅器と、半導体素子とを備える。前記半導体素子は、半導体基板と、前記半導体基板に、長辺および短辺を有する形状で形成される音響波伝播層と、少なくとも前記音響波伝播層の長辺方向の両端に形成される音響波反射層と、前記音響波伝播層上に形成され、前記第1のノードと電気的に接続される第1のコンタクトと、前記音響波伝播層上に前記第1のコンタクトとは離れて形成され、前記第2のノードと電気的に接続される第2のコンタクトと、を有する。前記第1のノードまたは前記第2のノードから発振信号を出力する。

【解決手段】発振器は、第1のノードと第2のノードと間に並列接続される抵抗と、反転増幅器と、半導体素子とを備える。前記半導体素子は、半導体基板と、前記半導体基板に、長辺および短辺を有する形状で形成される音響波伝播層と、少なくとも前記音響波伝播層の長辺方向の両端に形成される音響波反射層と、前記音響波伝播層上に形成され、前記第1のノードと電気的に接続される第1のコンタクトと、前記音響波伝播層上に前記第1のコンタクトとは離れて形成され、前記第2のノードと電気的に接続される第2のコンタクトと、を有する。前記第1のノードまたは前記第2のノードから発振信号を出力する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明の実施形態は、発振器およびPLL回路に関する。

【背景技術】

【0002】

従来から多くの発振器が用いられている。例えば、水晶発振器は、水晶の圧電効果を利用したものであり、非常に高い精度の発振が得られる。しかしながら、半導体集積回路の外付け部品であるため、コストが高くなるという問題がある。一方、半導体集積回路上に形成可能な発振器としては、LC発振器やRC発振器が挙げられる。LC発振器のインダクタには、半導体集積回路の配線を利用したスパイラルインダクタが用いられる。LC発振器の発振周波数はインダクタンスに依存するため、100MHzオーダ以下の周波数で発振させるためには非常に大きなインダクタンスが必要となり、半導体集積回路上で大きな面積を占有してしまう。また、RC発振器は、数百MHz以下の比較的低い周波数での発振を実現できるが、周波数特性が劣っているという問題がある。

【先行技術文献】

【非特許文献】

【0003】

【非特許文献1】G. Weinreich, Physical Review, 104 (1956), pp. 321 - 324

【発明の概要】

【発明が解決しようとする課題】

【0004】

半導体集積回路上に小面積で形成でき、かつ、適切な周波数の発振信号を生成できる発振器と、これを用いたPLL回路を提供する。

【課題を解決するための手段】

【0005】

実施形態によれば、発振器は、第1のノードと第2のノードと間に並列接続される抵抗と、反転増幅器と、半導体素子とを備える。前記半導体素子は、半導体基板と、前記半導体基板に、長辺および短辺を有する形状で形成される音響波伝播層と、少なくとも前記音響波伝播層の長辺方向の両端に形成される音響波反射層と、前記音響波伝播層上に形成され、前記第1のノードと電気的に接続される第1のコンタクトと、前記音響波伝播層上に前記第1のコンタクトとは離れて形成され、前記第2のノードと電気的に接続される第2のコンタクトと、を有する。前記第1のノードまたは前記第2のノードから発振信号を出力する。

【図面の簡単な説明】

【0006】

【図1】半導体素子100の上面図。

【図2】半導体素子100の斜視図。

【図3】半導体素子100の断面図。

【図4】半導体素子100の変形例。

【図5】半導体素子100の等価回路。

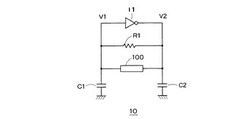

【図6】第1の実施形態に係る発振器10の回路図。

【図7】第2の実施形態に係る発振器20の回路図。

【図8】図7の発振器20をCMOS回路で構成した場合の回路図。

【図9】図7の発振器20をnMOSトランジスタを用いて構成した場合の回路図。

【図10】図7の発振器20をpMOSトランジスタを用いて構成した場合の回路図。

【図11】図9の回路のシミュレーション結果を示すグラフ。

【図12】PLL回路50の概略ブロック図。

【発明を実施するための形態】

【0007】

以下、実施形態について、図面を参照しながら具体的に説明する。まず、各実施形態の発振器で使用される半導体素子100について説明する。

【0008】

図1〜図3はそれぞれ、半導体素子100の上面図、斜視図および断面図である。半導体素子100は、シリコン基板(半導体基板)1と、nウェル2と、p型拡散層(音響波伝播層)3と、SiO2膜(音響波反射層)4と、コンタクト5a,5bと、配線6a,6bとを有する。

【0009】

シリコン基板1の表面には、例えば不純物としてリンあるいはヒ素がドーピングされたnウェル2が形成される。nウェル2の内側に、例えば不純物としてホウ素がドーピングされたp型拡散層3が形成される。p型拡散層3を上面から見た形状は、短辺および長辺を有する略長方形である。短辺および長辺の長さはそれぞれ、例えば、3μmおよび40μmであり、集積回路上に形成されるスパイラルインダクタと比べるとかなり小さくすることができる。

【0010】

nウェル2の内側で、p型拡散層3を囲うように溝7がシリコン基板1に形成され、その中にSiO2膜4が埋め込まれている。SiO2膜4は、いわゆるSTI(Shallow Trench Isolation)と呼ばれる構造であり、p型拡散層3をシリコン基板1上に形成される他の素子と電気的に分離する。コンタクト5a,5bは、p型拡散層3上に形成され、p型拡散層3と配線6a,6bとをそれぞれ電気的に接続する。コンタクト5a,5bは、互いに接触していなければp型拡散層3上のどこに形成してもよい。配線6a,6bは他の素子(不図示)と接続される。

【0011】

図1〜図3の半導体素子100は簡易な構造であるため、通常のCMOSプロセスにより形成できる。

【0012】

一般に、キャリアを有する半導体中では、電荷密度が変化すると体積が変化し、体積が変化すると電荷密度が変化すること、すなわち、電気と機械振動との相互作用が知られている。より具体的には、ρを電荷密度、Φを体積変化に比例する変数、cを半導体中の音速とすると、下記(1)式の方程式が成立する。

【数1】

【0013】

上記(1)式の左辺は音響波の伝搬を表す方程式であり、電荷密度ρの変化があると(右辺)、音速cの音響波が伝播する(左辺)ことを示している。

【0014】

このことを図1〜図3の半導体素子100に当てはめる。半導体素子100では、p型拡散層3にキャリアとしてホールが存在する。コンタクト5a,5bの一方または両方から電気入力が与えられるとp型拡散層3の電荷密度が変化し、その結果、p型拡散層3が音響波伝播層となって音響波が伝播する。一方、SiO2膜4は音響波反射層として機能する。すなわち、音響波はp型拡散層3とSiO2膜4との界面で反射し、p型拡散層3に音響定在波が生じる。この音響定在波の周波数はp型拡散層3の長辺の長さとp型拡散層3中の音速cとに応じて定まる。

【0015】

したがって、半導体素子100は特定の周波数のみで共振する共振器となる。p型拡散層3の長辺の長さが短いほど定在波の波長は短くなるため、p型拡散層3の長辺の長さに応じて、共振周波数を調整できる。一例として、長辺の長さが40μmの場合、共振周波数の実測値は94MHzである。また、シリコン基板1、nウェル2あるいはp型拡散層3にバイアスを印加することにより共振周波数を調整することもできる。

【0016】

なお、半導体素子100の構造は図1〜図3に限定されるものではない。音響波をp型拡散層3内に効率よく閉じ込めるためには、図1〜図3に示すように不純物拡散層を取り囲むように音響波反射層が設けられるのが望ましいが、少なくとも、不純物拡散領域の長辺方向の両端に音響波反射層が形成されていればよい。例えば、図4に示すように、SiO2膜4をp型拡散層3の長辺方向の両端にのみ形成し、短辺方向の側面にはnウェル2が形成されていてもよい。音響波反射層の材料は、p型拡散層が形成されるシリコン基板1の材料の音響インピーダンスとの差が大きい方が望ましく、例えばSiN等でもよい。また、図1〜図4の半導体素子100は、nウェル2およびp型拡散層3を形成しているが、導電型を逆にし、pウェル2’およびn型拡散層3’を形成してもよい。

【0017】

図5(a)は、半導体素子100の等価回路である。半導体素子100は、コンタクト5a,5b間に直列に形成される抵抗成分(第1の抵抗成分)Rs、インダクタンス成分Lsおよび容量成分Csと、これらと並列に形成される抵抗成分(第2の抵抗成分)Rpとを有する。

【0018】

抵抗成分Rpはコンタクト5a,5b間にp型拡散層3を介して電流が流れることを示している。抵抗成分Rs、インダクタンス成分Lsおよび容量成分Csは、半導体素子100の共振特性からフィッティングすることができる。

【0019】

通常、半導体集積回路上に形成されるスパイラルインダクタのインダクタンスは10nH程度であるので、これよりはるかに大きなインダクタンスを実現できる。これは、半導体中の音速cは、電気信号に比べると、非常に遅いためである。

【0020】

また、p型拡散層3の長辺方向の長さをより長く、例えば100μm以上とすると共振周波数が低くなり、インダクタンス成分Lsは数μHとなる。すなわち、p型拡散層3の長辺方向の長さを長くすればインダクタンス成分を大きくすることができる。

【0021】

このように、半導体素子100は、大きなインダクタンス成分を有し、かつ、長辺方向の長さに応じて共振周波数を調整可能な共振器として使用できる。

【0022】

したがって、圧電素子や圧電共振器に代えて、半導体集積回路上に簡易に製造可能な半導体素子100を用いることができる。

【0023】

なお、図1〜図4の半導体素子100は、2つのコンタクト5a,5bを有する例を示しているが、1つのコンタクト5aのみ有してもよい。この場合の等価回路は、図5(b)に示すようになり、コンタクト5aと接地端子との間には、抵抗成分Rpに加え容量成分Cpが形成される。

【0024】

また、上述したように半導体素子100の共振周波数は長辺の長さによって決定されるため、共振周波数のばらつきは製造上の形状ばらつきと同程度となる。半導体プロセスの加工精度は非常に高いため、半導体素子100における共振周波数のばらつきを極めて小さくできる。例えば、上記の長辺の長さが40μmの半導体素子100に対して0.01μmのプロセス誤差が生じた場合、共振周波数の誤差はわずか250ppmである。

【0025】

(第1の実施形態)

図6は、第1の実施形態に係る発振器10の回路図である。発振器10は、第1のノードV1と第2のノードV2との間に並列接続されるインバータ(反転増幅器)I1、抵抗R1および半導体素子100と、第1のノードV1と接地端子との間に接続される容量C1と、第2のノードV2と接地端子との間に接続される容量C2とを備えている。図1〜図3の半導体素子100において、コンタクト5aは第1のノードV1に接続され、コンタクト5bは第2のノードV2に接続される。

【0026】

インバータI1は、共振器としての半導体素子100の一端の電圧を反転増幅して、他端にフィードバック入力する。抵抗R1は、インバータI1の出力から入力へ電流および電圧信号をフィードバックし、半導体素子100の発振を継続させる。容量C1,C2は、負性抵抗、励振レベルおよび発振周波数を調整する。なお、半導体素子100の両端子の対地寄生容量が大きい場合は、この寄生容量で容量C1,C2を代用できるため、容量C1,C2を設けなくてもよい。

【0027】

半導体素子100の両端のインピーダンスが非常に高い共振時、両端の電圧の位相は逆位相となる。そして、インバータI1の入出力端子の位相も逆位相である。したがって、位相シフトが360度の正のフィードバックが形成され、発振する。その結果、第1のノードV1または第2のノードV2から発振信号を取り出すことができる。必要に応じて、バッファを設けて発振信号を取り出してもよい。

【0028】

このように、第1の実施形態では、水晶振動子やスパイラルインダクタを用いず、集積回路上に製造可能な簡易な構造の半導体素子100を用いて発振器10を構成する。したがって、低コストかつ低面積の発振器を実現できる。また、半導体素子100のインダクタンスはスパイラルインダクタのインダクタンスより大きいため、スパイラルインダクタを用いた発振器と比べ、発振周波数を低くすることができる。また、発振周波数は半導体素子100の長辺の長さで決定されるため、周波数精度の高い発振器が実現できる。

【0029】

(第2の実施形態)

第2の実施形態は、クロスカップリングにより発振器を構成するものである。

【0030】

図7は、第2の実施形態に係る発振器20の回路図である。発振器20は、入力端子が第1のノードV1に接続され、出力端子が第2のノードV2に接続されるインバータ(反転増幅器)Iaと、インバータIaと並列接続される抵抗Raと、第2のノードV2と第3のノードV3との間に接続される容量Caと、入力端子が第3のノードV3に接続され、出力端子が第4のノードV4に接続されるインバータ(反転増幅器)Ibと、インバータIbと並列接続される抵抗Rbと、第4のノードV4と第1のノードV1との間に接続される容量Cbと、第3のノードV3に接続される半導体素子100aと、第1のノードV1に接続される半導体素子100bとを備えている。

【0031】

半導体素子100aは、図1〜図3のコンタクト5a,5bのうちの一方のみを形成し、そのコンタクトを第3のノードV3に接続してもよい。同様に、半導体素子100bは、コンタクト5a,5bのうちの一方のみを形成し、そのコンタクトを第1のノードV1に接続してもよい。この場合、半導体素子100a,100bの等価回路は図5(b)で表される。

【0032】

あるいは、半導体素子100a,100bの少なくとも一方は、コンタクト5a,5bを形成し、その一方を接地端子に接続してもよい。また、半導体素子100a,100bを1つの半導体素子100として一体に形成し、コンタクト5aを第3のノードV3に、コンタクト5bを第1のノードV1にそれぞれ接続してもよい。

【0033】

図8は、図7の発振器20をCMOS(Complementally Metal Oxide Semiconductor)回路で構成した場合の回路図である。図7のインバータIaは、図8のpMOSトランジスタMpaおよびnMOSトランジスタMnaから構成される。同様に、図7のインバータIaは、pMOSトランジスタMpbおよびnMOSトランジスタMnbから構成される。さらに、図8の半導体素子100a,100bを一体に形成し、コンタクト5aを第1のノードV1に、コンタクト5bを第2のノードV2にそれぞれ接続している。

【0034】

図9は、図7の発振器20をnMOSトランジスタを用いて構成した場合の回路図であり、図10は、図7の発振器20をpMOSトランジスタを用いて構成した場合の回路図である。図9および図10に示すように、電流源IbiasとnMOSトランジスタMna,MnbあるいはpMOSトランジスタMpa,Mpbを用いて反転増幅器Ia,Ibを構成してもよい。

【0035】

図7の発振器20は、半導体素子100a,100bの共振時、各インバータIa,Ibの出力における位相シフトは0度である。したがって、トータルの位相シフトが360度の正のフィードバックが形成され、発振する。抵抗RaはインバータIaのフィードバック抵抗であり、容量Caと合わせてハイパスフィルタを構成する。抵抗Rbおよび容量Cbも同様である。これにより、第1〜第4のノードV1〜V4が電源電圧あるいは接地電圧に固定されるのが防止される。結果として、 第1〜第4のノードV1〜V4のいずれからも発振信号を取り出すことができる。

【0036】

図11は、図8の回路のシミュレーション結果を示すグラフである。図11(a)の横軸は時間、縦軸は周波数である。また、図11(b)の横軸は時間、縦軸は出力電圧の振幅である。これらの図に示すように、発振直後を除き、発振回路20は安定して約125MHzの発振信号を生成できる。上述したように、半導体素子100のインダクタンスを数百nHという、集積回路上のインダクタンス素子としては大きな値を実現できるために、この周波数で発振させることができる。

【0037】

このように、第2の実施形態でも、水晶振動子やスパイラルインダクタを用いず、集積回路上に製造可能な簡易な構造の半導体素子100を用いて発振器20を構成する。したがって、低コストかつ低面積の発振器を実現できる。また、半導体素子100のインダクタンスはスパイラルインダクタのインダクタンスより大きいため、スパイラルインダクタを用いた発振器と比べ、発振周波数を低くすることができる。また、発振周波数は半導体素子100の長辺の長さで決定されるため、周波数精度の高い発振器が実現できる。

【0038】

(第3の実施形態)

上述した発振器は種々の装置に用いることができるが、第3の実施形態は発振器を、クロック信号を生成するPLL(Phase Locked Loop)回路の基準信号生成器として使用するものである。

【0039】

図12は、PLL回路50の概略ブロック図である。PLL50は、基準信号生成器51と、位相比較器(PFD:Phase Frequency Detector)52と、チャージポンプ(CP:Charge Pump)53と、ループフィルタ(LF:Loop Filter)54と、電圧制御発振器(VCO:Voltage Controlled Oscillator)55と、分周器(DIV)56とを備えている。

【0040】

分周器56はPLL回路50の出力であるクロック信号CLKを分周して帰還信号FBを生成する。位相比較器52は、帰還信号FBの位相と、基準信号生成器51が生成する基準信号REFの位相とを比較し、比較結果に応じたデジタル信号を生成する。チャージポンプ53は、このデジタル信号に応じて、現在の出力電圧を高く、または、低くして新たな出力電圧を生成する。ループフィルタ54はチャージポンプ53が生成した出力電圧を平坦化し、制御電圧を生成する。電圧制御発振器55は制御信号に応じた周波数のクロック信号CLKを生成する。

【0041】

例えば、基準信号REFの位相が帰還信号FBの位相よりも進んで(遅れて)いる場合、位相比較器52はチャージポンプ53の出力電圧が高く(低く)なるよう、デジタル信号を生成する。そして、ループフィルタ54を介して、高く(低く)なった制御電圧が電圧制御発振器55に供給され、電圧制御発振器55が生成するクロック信号CLKの周波数が高く(低く)なる。これにより、クロック信号CLKの位相が基準信号REFの位相に近くなる。

【0042】

このようなフィードバックを繰り返すことにより、基準信号REFに同期したクロック信号CLKが得られる。

【0043】

図12のPLL回路において、基準信号生成器51として、第1および第2の実施形態で説明した発振器10,20を適用できる。これにより、周波数精度が高い数百MHzオーダ以下のクロック信号を生成でき、プロセッサやメモリコントローラ等のデジタル回路に使用できる。

【0044】

図6等の発振器は一例に過ぎず、種々の変形が可能である。例えば、MOSトランジスタの少なくとも一部を、バイポーラトランジスタやBi−CMOS等の他の半導体素子を用いて構成してもよい。また、トランジスタの導電型を逆にし、それに応じて電源端子と接地端子の接続位置を逆にした発振器を構成してもよい。この場合も基本的な動作原理は同じである。

【0045】

本実施形態に係る発振器は、回路全体を同一の半導体基板上に形成してもよいし、回路の一部を別の半導体基板上に形成してもよい。

【0046】

本発明のいくつかの実施形態を説明したが、これらの実施形態は、例として提示したものであり、発明の範囲を限定することは意図していない。これら実施形態は、その他の様々な形態で実施されることが可能であり、発明の要旨を逸脱しない範囲で、種々の省略、置き換え、変更を行うことができる。これら実施形態やその変形は、発明の範囲や要旨に含まれると同様に、特許請求の範囲に記載された発明とその均等の範囲に含まれるものである。

【符号の説明】

【0047】

1 シリコン基板

2 nウェル

3 p型拡散層

4 SiO2膜

5a,5b コンタクト

6a,6b 配線

7 溝

10,20 発振器

50 PLL

100 半導体素子

【技術分野】

【0001】

本発明の実施形態は、発振器およびPLL回路に関する。

【背景技術】

【0002】

従来から多くの発振器が用いられている。例えば、水晶発振器は、水晶の圧電効果を利用したものであり、非常に高い精度の発振が得られる。しかしながら、半導体集積回路の外付け部品であるため、コストが高くなるという問題がある。一方、半導体集積回路上に形成可能な発振器としては、LC発振器やRC発振器が挙げられる。LC発振器のインダクタには、半導体集積回路の配線を利用したスパイラルインダクタが用いられる。LC発振器の発振周波数はインダクタンスに依存するため、100MHzオーダ以下の周波数で発振させるためには非常に大きなインダクタンスが必要となり、半導体集積回路上で大きな面積を占有してしまう。また、RC発振器は、数百MHz以下の比較的低い周波数での発振を実現できるが、周波数特性が劣っているという問題がある。

【先行技術文献】

【非特許文献】

【0003】

【非特許文献1】G. Weinreich, Physical Review, 104 (1956), pp. 321 - 324

【発明の概要】

【発明が解決しようとする課題】

【0004】

半導体集積回路上に小面積で形成でき、かつ、適切な周波数の発振信号を生成できる発振器と、これを用いたPLL回路を提供する。

【課題を解決するための手段】

【0005】

実施形態によれば、発振器は、第1のノードと第2のノードと間に並列接続される抵抗と、反転増幅器と、半導体素子とを備える。前記半導体素子は、半導体基板と、前記半導体基板に、長辺および短辺を有する形状で形成される音響波伝播層と、少なくとも前記音響波伝播層の長辺方向の両端に形成される音響波反射層と、前記音響波伝播層上に形成され、前記第1のノードと電気的に接続される第1のコンタクトと、前記音響波伝播層上に前記第1のコンタクトとは離れて形成され、前記第2のノードと電気的に接続される第2のコンタクトと、を有する。前記第1のノードまたは前記第2のノードから発振信号を出力する。

【図面の簡単な説明】

【0006】

【図1】半導体素子100の上面図。

【図2】半導体素子100の斜視図。

【図3】半導体素子100の断面図。

【図4】半導体素子100の変形例。

【図5】半導体素子100の等価回路。

【図6】第1の実施形態に係る発振器10の回路図。

【図7】第2の実施形態に係る発振器20の回路図。

【図8】図7の発振器20をCMOS回路で構成した場合の回路図。

【図9】図7の発振器20をnMOSトランジスタを用いて構成した場合の回路図。

【図10】図7の発振器20をpMOSトランジスタを用いて構成した場合の回路図。

【図11】図9の回路のシミュレーション結果を示すグラフ。

【図12】PLL回路50の概略ブロック図。

【発明を実施するための形態】

【0007】

以下、実施形態について、図面を参照しながら具体的に説明する。まず、各実施形態の発振器で使用される半導体素子100について説明する。

【0008】

図1〜図3はそれぞれ、半導体素子100の上面図、斜視図および断面図である。半導体素子100は、シリコン基板(半導体基板)1と、nウェル2と、p型拡散層(音響波伝播層)3と、SiO2膜(音響波反射層)4と、コンタクト5a,5bと、配線6a,6bとを有する。

【0009】

シリコン基板1の表面には、例えば不純物としてリンあるいはヒ素がドーピングされたnウェル2が形成される。nウェル2の内側に、例えば不純物としてホウ素がドーピングされたp型拡散層3が形成される。p型拡散層3を上面から見た形状は、短辺および長辺を有する略長方形である。短辺および長辺の長さはそれぞれ、例えば、3μmおよび40μmであり、集積回路上に形成されるスパイラルインダクタと比べるとかなり小さくすることができる。

【0010】

nウェル2の内側で、p型拡散層3を囲うように溝7がシリコン基板1に形成され、その中にSiO2膜4が埋め込まれている。SiO2膜4は、いわゆるSTI(Shallow Trench Isolation)と呼ばれる構造であり、p型拡散層3をシリコン基板1上に形成される他の素子と電気的に分離する。コンタクト5a,5bは、p型拡散層3上に形成され、p型拡散層3と配線6a,6bとをそれぞれ電気的に接続する。コンタクト5a,5bは、互いに接触していなければp型拡散層3上のどこに形成してもよい。配線6a,6bは他の素子(不図示)と接続される。

【0011】

図1〜図3の半導体素子100は簡易な構造であるため、通常のCMOSプロセスにより形成できる。

【0012】

一般に、キャリアを有する半導体中では、電荷密度が変化すると体積が変化し、体積が変化すると電荷密度が変化すること、すなわち、電気と機械振動との相互作用が知られている。より具体的には、ρを電荷密度、Φを体積変化に比例する変数、cを半導体中の音速とすると、下記(1)式の方程式が成立する。

【数1】

【0013】

上記(1)式の左辺は音響波の伝搬を表す方程式であり、電荷密度ρの変化があると(右辺)、音速cの音響波が伝播する(左辺)ことを示している。

【0014】

このことを図1〜図3の半導体素子100に当てはめる。半導体素子100では、p型拡散層3にキャリアとしてホールが存在する。コンタクト5a,5bの一方または両方から電気入力が与えられるとp型拡散層3の電荷密度が変化し、その結果、p型拡散層3が音響波伝播層となって音響波が伝播する。一方、SiO2膜4は音響波反射層として機能する。すなわち、音響波はp型拡散層3とSiO2膜4との界面で反射し、p型拡散層3に音響定在波が生じる。この音響定在波の周波数はp型拡散層3の長辺の長さとp型拡散層3中の音速cとに応じて定まる。

【0015】

したがって、半導体素子100は特定の周波数のみで共振する共振器となる。p型拡散層3の長辺の長さが短いほど定在波の波長は短くなるため、p型拡散層3の長辺の長さに応じて、共振周波数を調整できる。一例として、長辺の長さが40μmの場合、共振周波数の実測値は94MHzである。また、シリコン基板1、nウェル2あるいはp型拡散層3にバイアスを印加することにより共振周波数を調整することもできる。

【0016】

なお、半導体素子100の構造は図1〜図3に限定されるものではない。音響波をp型拡散層3内に効率よく閉じ込めるためには、図1〜図3に示すように不純物拡散層を取り囲むように音響波反射層が設けられるのが望ましいが、少なくとも、不純物拡散領域の長辺方向の両端に音響波反射層が形成されていればよい。例えば、図4に示すように、SiO2膜4をp型拡散層3の長辺方向の両端にのみ形成し、短辺方向の側面にはnウェル2が形成されていてもよい。音響波反射層の材料は、p型拡散層が形成されるシリコン基板1の材料の音響インピーダンスとの差が大きい方が望ましく、例えばSiN等でもよい。また、図1〜図4の半導体素子100は、nウェル2およびp型拡散層3を形成しているが、導電型を逆にし、pウェル2’およびn型拡散層3’を形成してもよい。

【0017】

図5(a)は、半導体素子100の等価回路である。半導体素子100は、コンタクト5a,5b間に直列に形成される抵抗成分(第1の抵抗成分)Rs、インダクタンス成分Lsおよび容量成分Csと、これらと並列に形成される抵抗成分(第2の抵抗成分)Rpとを有する。

【0018】

抵抗成分Rpはコンタクト5a,5b間にp型拡散層3を介して電流が流れることを示している。抵抗成分Rs、インダクタンス成分Lsおよび容量成分Csは、半導体素子100の共振特性からフィッティングすることができる。

【0019】

通常、半導体集積回路上に形成されるスパイラルインダクタのインダクタンスは10nH程度であるので、これよりはるかに大きなインダクタンスを実現できる。これは、半導体中の音速cは、電気信号に比べると、非常に遅いためである。

【0020】

また、p型拡散層3の長辺方向の長さをより長く、例えば100μm以上とすると共振周波数が低くなり、インダクタンス成分Lsは数μHとなる。すなわち、p型拡散層3の長辺方向の長さを長くすればインダクタンス成分を大きくすることができる。

【0021】

このように、半導体素子100は、大きなインダクタンス成分を有し、かつ、長辺方向の長さに応じて共振周波数を調整可能な共振器として使用できる。

【0022】

したがって、圧電素子や圧電共振器に代えて、半導体集積回路上に簡易に製造可能な半導体素子100を用いることができる。

【0023】

なお、図1〜図4の半導体素子100は、2つのコンタクト5a,5bを有する例を示しているが、1つのコンタクト5aのみ有してもよい。この場合の等価回路は、図5(b)に示すようになり、コンタクト5aと接地端子との間には、抵抗成分Rpに加え容量成分Cpが形成される。

【0024】

また、上述したように半導体素子100の共振周波数は長辺の長さによって決定されるため、共振周波数のばらつきは製造上の形状ばらつきと同程度となる。半導体プロセスの加工精度は非常に高いため、半導体素子100における共振周波数のばらつきを極めて小さくできる。例えば、上記の長辺の長さが40μmの半導体素子100に対して0.01μmのプロセス誤差が生じた場合、共振周波数の誤差はわずか250ppmである。

【0025】

(第1の実施形態)

図6は、第1の実施形態に係る発振器10の回路図である。発振器10は、第1のノードV1と第2のノードV2との間に並列接続されるインバータ(反転増幅器)I1、抵抗R1および半導体素子100と、第1のノードV1と接地端子との間に接続される容量C1と、第2のノードV2と接地端子との間に接続される容量C2とを備えている。図1〜図3の半導体素子100において、コンタクト5aは第1のノードV1に接続され、コンタクト5bは第2のノードV2に接続される。

【0026】

インバータI1は、共振器としての半導体素子100の一端の電圧を反転増幅して、他端にフィードバック入力する。抵抗R1は、インバータI1の出力から入力へ電流および電圧信号をフィードバックし、半導体素子100の発振を継続させる。容量C1,C2は、負性抵抗、励振レベルおよび発振周波数を調整する。なお、半導体素子100の両端子の対地寄生容量が大きい場合は、この寄生容量で容量C1,C2を代用できるため、容量C1,C2を設けなくてもよい。

【0027】

半導体素子100の両端のインピーダンスが非常に高い共振時、両端の電圧の位相は逆位相となる。そして、インバータI1の入出力端子の位相も逆位相である。したがって、位相シフトが360度の正のフィードバックが形成され、発振する。その結果、第1のノードV1または第2のノードV2から発振信号を取り出すことができる。必要に応じて、バッファを設けて発振信号を取り出してもよい。

【0028】

このように、第1の実施形態では、水晶振動子やスパイラルインダクタを用いず、集積回路上に製造可能な簡易な構造の半導体素子100を用いて発振器10を構成する。したがって、低コストかつ低面積の発振器を実現できる。また、半導体素子100のインダクタンスはスパイラルインダクタのインダクタンスより大きいため、スパイラルインダクタを用いた発振器と比べ、発振周波数を低くすることができる。また、発振周波数は半導体素子100の長辺の長さで決定されるため、周波数精度の高い発振器が実現できる。

【0029】

(第2の実施形態)

第2の実施形態は、クロスカップリングにより発振器を構成するものである。

【0030】

図7は、第2の実施形態に係る発振器20の回路図である。発振器20は、入力端子が第1のノードV1に接続され、出力端子が第2のノードV2に接続されるインバータ(反転増幅器)Iaと、インバータIaと並列接続される抵抗Raと、第2のノードV2と第3のノードV3との間に接続される容量Caと、入力端子が第3のノードV3に接続され、出力端子が第4のノードV4に接続されるインバータ(反転増幅器)Ibと、インバータIbと並列接続される抵抗Rbと、第4のノードV4と第1のノードV1との間に接続される容量Cbと、第3のノードV3に接続される半導体素子100aと、第1のノードV1に接続される半導体素子100bとを備えている。

【0031】

半導体素子100aは、図1〜図3のコンタクト5a,5bのうちの一方のみを形成し、そのコンタクトを第3のノードV3に接続してもよい。同様に、半導体素子100bは、コンタクト5a,5bのうちの一方のみを形成し、そのコンタクトを第1のノードV1に接続してもよい。この場合、半導体素子100a,100bの等価回路は図5(b)で表される。

【0032】

あるいは、半導体素子100a,100bの少なくとも一方は、コンタクト5a,5bを形成し、その一方を接地端子に接続してもよい。また、半導体素子100a,100bを1つの半導体素子100として一体に形成し、コンタクト5aを第3のノードV3に、コンタクト5bを第1のノードV1にそれぞれ接続してもよい。

【0033】

図8は、図7の発振器20をCMOS(Complementally Metal Oxide Semiconductor)回路で構成した場合の回路図である。図7のインバータIaは、図8のpMOSトランジスタMpaおよびnMOSトランジスタMnaから構成される。同様に、図7のインバータIaは、pMOSトランジスタMpbおよびnMOSトランジスタMnbから構成される。さらに、図8の半導体素子100a,100bを一体に形成し、コンタクト5aを第1のノードV1に、コンタクト5bを第2のノードV2にそれぞれ接続している。

【0034】

図9は、図7の発振器20をnMOSトランジスタを用いて構成した場合の回路図であり、図10は、図7の発振器20をpMOSトランジスタを用いて構成した場合の回路図である。図9および図10に示すように、電流源IbiasとnMOSトランジスタMna,MnbあるいはpMOSトランジスタMpa,Mpbを用いて反転増幅器Ia,Ibを構成してもよい。

【0035】

図7の発振器20は、半導体素子100a,100bの共振時、各インバータIa,Ibの出力における位相シフトは0度である。したがって、トータルの位相シフトが360度の正のフィードバックが形成され、発振する。抵抗RaはインバータIaのフィードバック抵抗であり、容量Caと合わせてハイパスフィルタを構成する。抵抗Rbおよび容量Cbも同様である。これにより、第1〜第4のノードV1〜V4が電源電圧あるいは接地電圧に固定されるのが防止される。結果として、 第1〜第4のノードV1〜V4のいずれからも発振信号を取り出すことができる。

【0036】

図11は、図8の回路のシミュレーション結果を示すグラフである。図11(a)の横軸は時間、縦軸は周波数である。また、図11(b)の横軸は時間、縦軸は出力電圧の振幅である。これらの図に示すように、発振直後を除き、発振回路20は安定して約125MHzの発振信号を生成できる。上述したように、半導体素子100のインダクタンスを数百nHという、集積回路上のインダクタンス素子としては大きな値を実現できるために、この周波数で発振させることができる。

【0037】

このように、第2の実施形態でも、水晶振動子やスパイラルインダクタを用いず、集積回路上に製造可能な簡易な構造の半導体素子100を用いて発振器20を構成する。したがって、低コストかつ低面積の発振器を実現できる。また、半導体素子100のインダクタンスはスパイラルインダクタのインダクタンスより大きいため、スパイラルインダクタを用いた発振器と比べ、発振周波数を低くすることができる。また、発振周波数は半導体素子100の長辺の長さで決定されるため、周波数精度の高い発振器が実現できる。

【0038】

(第3の実施形態)

上述した発振器は種々の装置に用いることができるが、第3の実施形態は発振器を、クロック信号を生成するPLL(Phase Locked Loop)回路の基準信号生成器として使用するものである。

【0039】

図12は、PLL回路50の概略ブロック図である。PLL50は、基準信号生成器51と、位相比較器(PFD:Phase Frequency Detector)52と、チャージポンプ(CP:Charge Pump)53と、ループフィルタ(LF:Loop Filter)54と、電圧制御発振器(VCO:Voltage Controlled Oscillator)55と、分周器(DIV)56とを備えている。

【0040】

分周器56はPLL回路50の出力であるクロック信号CLKを分周して帰還信号FBを生成する。位相比較器52は、帰還信号FBの位相と、基準信号生成器51が生成する基準信号REFの位相とを比較し、比較結果に応じたデジタル信号を生成する。チャージポンプ53は、このデジタル信号に応じて、現在の出力電圧を高く、または、低くして新たな出力電圧を生成する。ループフィルタ54はチャージポンプ53が生成した出力電圧を平坦化し、制御電圧を生成する。電圧制御発振器55は制御信号に応じた周波数のクロック信号CLKを生成する。

【0041】

例えば、基準信号REFの位相が帰還信号FBの位相よりも進んで(遅れて)いる場合、位相比較器52はチャージポンプ53の出力電圧が高く(低く)なるよう、デジタル信号を生成する。そして、ループフィルタ54を介して、高く(低く)なった制御電圧が電圧制御発振器55に供給され、電圧制御発振器55が生成するクロック信号CLKの周波数が高く(低く)なる。これにより、クロック信号CLKの位相が基準信号REFの位相に近くなる。

【0042】

このようなフィードバックを繰り返すことにより、基準信号REFに同期したクロック信号CLKが得られる。

【0043】

図12のPLL回路において、基準信号生成器51として、第1および第2の実施形態で説明した発振器10,20を適用できる。これにより、周波数精度が高い数百MHzオーダ以下のクロック信号を生成でき、プロセッサやメモリコントローラ等のデジタル回路に使用できる。

【0044】

図6等の発振器は一例に過ぎず、種々の変形が可能である。例えば、MOSトランジスタの少なくとも一部を、バイポーラトランジスタやBi−CMOS等の他の半導体素子を用いて構成してもよい。また、トランジスタの導電型を逆にし、それに応じて電源端子と接地端子の接続位置を逆にした発振器を構成してもよい。この場合も基本的な動作原理は同じである。

【0045】

本実施形態に係る発振器は、回路全体を同一の半導体基板上に形成してもよいし、回路の一部を別の半導体基板上に形成してもよい。

【0046】

本発明のいくつかの実施形態を説明したが、これらの実施形態は、例として提示したものであり、発明の範囲を限定することは意図していない。これら実施形態は、その他の様々な形態で実施されることが可能であり、発明の要旨を逸脱しない範囲で、種々の省略、置き換え、変更を行うことができる。これら実施形態やその変形は、発明の範囲や要旨に含まれると同様に、特許請求の範囲に記載された発明とその均等の範囲に含まれるものである。

【符号の説明】

【0047】

1 シリコン基板

2 nウェル

3 p型拡散層

4 SiO2膜

5a,5b コンタクト

6a,6b 配線

7 溝

10,20 発振器

50 PLL

100 半導体素子

【特許請求の範囲】

【請求項1】

第1のノードと第2のノードと間に並列接続される抵抗と、反転増幅器と、半導体素子と、を備え、

前記半導体素子は、

半導体基板と、

前記半導体基板に、長辺および短辺を有する形状で形成される音響波伝播層と、

少なくとも前記音響波伝播層の長辺方向の両端に形成される音響波反射層と、

前記音響波伝播層上に形成され、前記第1のノードと電気的に接続される第1のコンタクトと、

前記音響波伝播層上に前記第1のコンタクトとは離れて形成され、前記第2のノードと電気的に接続される第2のコンタクトと、を有し、

前記第1のノードまたは前記第2のノードから発振信号を出力することを特徴とする発振器。

【請求項2】

前記半導体素子は、

前記第1のコンタクトおよび前記第2のコンタクトとの間に直列に形成される第1の抵抗成分、インダクタンス成分および容量成分と、

前記第1の抵抗成分、前記インダクタンス成分および前記容量成分と並列に形成される第2の抵抗成分と、を有することを特徴とする請求項1に記載の発振器。

【請求項3】

前記音響波反射層は、前記半導体基板に形成された溝に埋め込まれた絶縁体材料であることを特徴とする請求項1または2に記載の発振器。

【請求項4】

前記音響波反射層は、前記音響波伝播層を取り囲むように形成されることを特徴とする請求項1乃至3のいずれかに記載の発振器。

【請求項5】

前記音響波伝播層は、前記半導体基板に形成された不純物拡散層であることを特徴とする請求項1乃至4のいずれかに記載の発振器。

【請求項6】

前記第1のノードと接地端子との間に接続される第1の容量と、

前記第2のノードと前記接地端子との間に接続される第2の容量と、を備えることを特徴とする請求項1乃至5のいずれかに記載の発振器。

【請求項7】

入力端子が第1のノードに接続され、出力端子が第2のノードに接続される第1の反転増幅器と、

前記第1の反転増幅器と並列接続される第1の抵抗と、

前記第2のノードと第3のノードとの間に接続される第1の容量と、

入力端子が前記第3のノードに接続され、出力端子が第4のノードに接続される第2の反転増幅器と、

前記第2の反転増幅器と並列接続される第2の抵抗と、

前記第4のノードと前記第1のノードとの間に接続される第2の容量と、

前記第3のノードに接続される第1の半導体素子と、

前記第1のノードに接続される第2の半導体素子と、を備え、

前記第1および第2の半導体素子は、

半導体基板と、

前記半導体基板に、長辺および短辺を有する形状で形成される音響波伝播層と、

少なくとも前記音響波伝播層の長辺方向の両端に形成される音響波反射層と、

前記音響波伝播層上に形成され、前記第3のノードまたは前記第1のノードと電気的に接続される第1のコンタクトと、を有し、

前記第1乃至第4のノードのいずれかから発振信号を出力することを特徴とする発振器。

【請求項8】

前記第1および前記第2の半導体素子は一体に形成され、

前記第1のコンタクトが前記第3のノードに電気的に接続されるとともに、前記第1のノードと電気的に接続される第2のコンタクトが前記音響波伝播層上に前記第1のコンタクトとは離れて形成されることを特徴とする請求項7に記載の発振器。

【請求項9】

基準信号に同期したクロック信号を生成するPLL回路であって、

前記基準信号を生成する基準信号生成器と、

前記クロック信号を分周して帰還信号を生成する分周器と、

前記帰還信号の位相と前記基準信号の位相とを比較し、比較結果に応じた信号を出力する位相比較器と、

前記位相比較器が出力する信号に応じた出力電圧を生成するチャージポンプと、

前記チャージポンプの出力電圧を平坦化して制御電圧を生成するループフィルタと、

前記制御電圧に応じた周波数の前記クロック信号を生成する電圧制御発振器と、を備え、

前記基準信号生成器は、

第1のノードと第2のノードと間に並列接続される抵抗と、反転増幅器と、半導体素子と、を備え、

前記半導体素子は、

半導体基板と、

前記半導体基板に、長辺および短辺を有する形状で形成される音響波伝播層と、

少なくとも前記音響波伝播層の長辺方向の両端に形成される音響波反射層と、

前記音響波伝播層上に形成され、前記第1のノードと電気的に接続される第1のコンタクトと、

前記音響波伝播層上に前記第1のコンタクトとは離れて形成され、前記第2のノードと電気的に接続される第2のコンタクトと、を有し、

前記第1のノードまたは前記第2のノードから前記基準信号を出力することを特徴とするPLL回路。

【請求項10】

基準信号に同期したクロック信号を生成するPLL回路であって、

前記基準信号を生成する基準信号生成器と、

前記クロック信号を分周して帰還信号を生成する分周器と、

前記帰還信号の位相と前記基準信号の位相とを比較し、比較結果に応じた信号を出力する位相比較器と、

前記位相比較器が出力する信号に応じた出力電圧を生成するチャージポンプと、

前記チャージポンプの出力電圧を平坦化して制御電圧を生成するループフィルタと、

前記制御電圧に応じた周波数の前記クロック信号を生成する電圧制御発振器と、を備え、

前記基準信号生成器は、

入力端子が第1のノードに接続され、出力端子が第2のノードに接続される第1の反転増幅器と、

前記第1の反転増幅器と並列接続される第1の抵抗と、

前記第2のノードと第3のノードとの間に接続される第1の容量と、

入力端子が前記第3のノードに接続され、出力端子が第4のノードに接続される第2の反転増幅器と、

前記第2の反転増幅器と並列接続される第2の抵抗と、

前記第4のノードと前記第1のノードとの間に接続される第2の容量と、

前記第3のノードに接続される第1の半導体素子と、

前記第1のノードに接続される第2の半導体素子と、を備え、

前記第1および第2の半導体素子は、

半導体基板と、

前記半導体基板に、長辺および短辺を有する形状で形成される音響波伝播層と、

少なくとも前記音響波伝播層の長辺方向の両端に形成される音響波反射層と、

前記音響波伝播層上に形成され、前記第3のノードまたは前記第1のノードと電気的に接続される第1のコンタクトと、を有し、

前記第1乃至第4のノードのいずれかから前記基準信号を出力することを特徴とするPLL回路。

【請求項1】

第1のノードと第2のノードと間に並列接続される抵抗と、反転増幅器と、半導体素子と、を備え、

前記半導体素子は、

半導体基板と、

前記半導体基板に、長辺および短辺を有する形状で形成される音響波伝播層と、

少なくとも前記音響波伝播層の長辺方向の両端に形成される音響波反射層と、

前記音響波伝播層上に形成され、前記第1のノードと電気的に接続される第1のコンタクトと、

前記音響波伝播層上に前記第1のコンタクトとは離れて形成され、前記第2のノードと電気的に接続される第2のコンタクトと、を有し、

前記第1のノードまたは前記第2のノードから発振信号を出力することを特徴とする発振器。

【請求項2】

前記半導体素子は、

前記第1のコンタクトおよび前記第2のコンタクトとの間に直列に形成される第1の抵抗成分、インダクタンス成分および容量成分と、

前記第1の抵抗成分、前記インダクタンス成分および前記容量成分と並列に形成される第2の抵抗成分と、を有することを特徴とする請求項1に記載の発振器。

【請求項3】

前記音響波反射層は、前記半導体基板に形成された溝に埋め込まれた絶縁体材料であることを特徴とする請求項1または2に記載の発振器。

【請求項4】

前記音響波反射層は、前記音響波伝播層を取り囲むように形成されることを特徴とする請求項1乃至3のいずれかに記載の発振器。

【請求項5】

前記音響波伝播層は、前記半導体基板に形成された不純物拡散層であることを特徴とする請求項1乃至4のいずれかに記載の発振器。

【請求項6】

前記第1のノードと接地端子との間に接続される第1の容量と、

前記第2のノードと前記接地端子との間に接続される第2の容量と、を備えることを特徴とする請求項1乃至5のいずれかに記載の発振器。

【請求項7】

入力端子が第1のノードに接続され、出力端子が第2のノードに接続される第1の反転増幅器と、

前記第1の反転増幅器と並列接続される第1の抵抗と、

前記第2のノードと第3のノードとの間に接続される第1の容量と、

入力端子が前記第3のノードに接続され、出力端子が第4のノードに接続される第2の反転増幅器と、

前記第2の反転増幅器と並列接続される第2の抵抗と、

前記第4のノードと前記第1のノードとの間に接続される第2の容量と、

前記第3のノードに接続される第1の半導体素子と、

前記第1のノードに接続される第2の半導体素子と、を備え、

前記第1および第2の半導体素子は、

半導体基板と、

前記半導体基板に、長辺および短辺を有する形状で形成される音響波伝播層と、

少なくとも前記音響波伝播層の長辺方向の両端に形成される音響波反射層と、

前記音響波伝播層上に形成され、前記第3のノードまたは前記第1のノードと電気的に接続される第1のコンタクトと、を有し、

前記第1乃至第4のノードのいずれかから発振信号を出力することを特徴とする発振器。

【請求項8】

前記第1および前記第2の半導体素子は一体に形成され、

前記第1のコンタクトが前記第3のノードに電気的に接続されるとともに、前記第1のノードと電気的に接続される第2のコンタクトが前記音響波伝播層上に前記第1のコンタクトとは離れて形成されることを特徴とする請求項7に記載の発振器。

【請求項9】

基準信号に同期したクロック信号を生成するPLL回路であって、

前記基準信号を生成する基準信号生成器と、

前記クロック信号を分周して帰還信号を生成する分周器と、

前記帰還信号の位相と前記基準信号の位相とを比較し、比較結果に応じた信号を出力する位相比較器と、

前記位相比較器が出力する信号に応じた出力電圧を生成するチャージポンプと、

前記チャージポンプの出力電圧を平坦化して制御電圧を生成するループフィルタと、

前記制御電圧に応じた周波数の前記クロック信号を生成する電圧制御発振器と、を備え、

前記基準信号生成器は、

第1のノードと第2のノードと間に並列接続される抵抗と、反転増幅器と、半導体素子と、を備え、

前記半導体素子は、

半導体基板と、

前記半導体基板に、長辺および短辺を有する形状で形成される音響波伝播層と、

少なくとも前記音響波伝播層の長辺方向の両端に形成される音響波反射層と、

前記音響波伝播層上に形成され、前記第1のノードと電気的に接続される第1のコンタクトと、

前記音響波伝播層上に前記第1のコンタクトとは離れて形成され、前記第2のノードと電気的に接続される第2のコンタクトと、を有し、

前記第1のノードまたは前記第2のノードから前記基準信号を出力することを特徴とするPLL回路。

【請求項10】

基準信号に同期したクロック信号を生成するPLL回路であって、

前記基準信号を生成する基準信号生成器と、

前記クロック信号を分周して帰還信号を生成する分周器と、

前記帰還信号の位相と前記基準信号の位相とを比較し、比較結果に応じた信号を出力する位相比較器と、

前記位相比較器が出力する信号に応じた出力電圧を生成するチャージポンプと、

前記チャージポンプの出力電圧を平坦化して制御電圧を生成するループフィルタと、

前記制御電圧に応じた周波数の前記クロック信号を生成する電圧制御発振器と、を備え、

前記基準信号生成器は、

入力端子が第1のノードに接続され、出力端子が第2のノードに接続される第1の反転増幅器と、

前記第1の反転増幅器と並列接続される第1の抵抗と、

前記第2のノードと第3のノードとの間に接続される第1の容量と、

入力端子が前記第3のノードに接続され、出力端子が第4のノードに接続される第2の反転増幅器と、

前記第2の反転増幅器と並列接続される第2の抵抗と、

前記第4のノードと前記第1のノードとの間に接続される第2の容量と、

前記第3のノードに接続される第1の半導体素子と、

前記第1のノードに接続される第2の半導体素子と、を備え、

前記第1および第2の半導体素子は、

半導体基板と、

前記半導体基板に、長辺および短辺を有する形状で形成される音響波伝播層と、

少なくとも前記音響波伝播層の長辺方向の両端に形成される音響波反射層と、

前記音響波伝播層上に形成され、前記第3のノードまたは前記第1のノードと電気的に接続される第1のコンタクトと、を有し、

前記第1乃至第4のノードのいずれかから前記基準信号を出力することを特徴とするPLL回路。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【公開番号】特開2013−9152(P2013−9152A)

【公開日】平成25年1月10日(2013.1.10)

【国際特許分類】

【出願番号】特願2011−140433(P2011−140433)

【出願日】平成23年6月24日(2011.6.24)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

【公開日】平成25年1月10日(2013.1.10)

【国際特許分類】

【出願日】平成23年6月24日(2011.6.24)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

[ Back to top ]