発振器

【課題】基本波を逓倍した高次高調波を用いる発振器において、出力レベルと雑音特性を向上させることを目的としている。

【解決手段】基本波及び前記基本波の高次高調波を含む信号を生成する発振回路と、基本波の通過を阻止し、基本波の高次高調波を通過させる周波数選択回路と、を備え、周波数選択回路は、インダクタと第1キャパシタとの並列回路を含み、並列経路の共振周波数が、基本波の周波数に設定されている。

【解決手段】基本波及び前記基本波の高次高調波を含む信号を生成する発振回路と、基本波の通過を阻止し、基本波の高次高調波を通過させる周波数選択回路と、を備え、周波数選択回路は、インダクタと第1キャパシタとの並列回路を含み、並列経路の共振周波数が、基本波の周波数に設定されている。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、発振器に関する。

【背景技術】

【0002】

発振回路が生成した信号を用いる通信装置等において、基本波を用いる発振器と、基本波を逓倍した高次高調波を用いる発振器がある。基本波を逓倍した高次高調波を用いる場合、発振器は、発振回路で生成された信号の内、フィルタ回路により基本波を抑圧し、利用したい高次高周波の周波数を通過させて負荷に出力する。

【0003】

例えば、特許文献1に記載の技術では、発振回路が結合容量を介してリング共振器に接続され、発振周波数の電圧が0になるリング共振器上の一点から出力容量を介して出力を取り出すことで基本波及び奇数次高調波を抑圧し、偶数次高調波を取り出していた。このような回路構成において、一般的に、リング共振器の出力は、容量の小さいコンデンサにより疎結合されている。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開平8−107334号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

しかしながら、特許文献1に記載の技術のように、発振回路の出力にコンデンサを疎結合して高次高調波を取り出す場合、高次高調波の信号レベルは、基本波の信号レベルに対して、例えば10〜20[dB]程度低くなる。利用する高次高調波の信号レベルを上げるために、発振出力の結合を強くすると、発振回路が受ける負荷変動の影響が大きくなり、雑音特性が劣化する課題があった。

【0006】

本発明は、上記の問題点に鑑みてなされたものであって、基本波を逓倍した高次高調波を用いる発振器において、出力レベルと雑音特性を向上させることを目的としている。

【課題を解決するための手段】

【0007】

上記目的を達成するため、本発明に係る発振器は、基本波及び前記基本波の高次高調波を含む信号を生成する発振回路と、前記基本波の通過を阻止し、前記基本波の高次高調波を通過させる周波数選択回路と、を備え、前記周波数選択回路は、インダクタと第1キャパシタとの並列回路を含み、前記並列回路の共振周波数が、前記基本波の周波数に設定されていることを特徴としている。

【0008】

また、本発明の発振器において、前記第1キャパシタは、前記基本波の周波数以上の帯域において、通過損失が予め定められている値より小さくなるように容量が設定されているようにしてもよい。

【0009】

また、本発明の発振器において、前記周波数選択回路は、前記インダクタが、前記第1キャパシタに隣接して基板パターンの線路により形成され、前記第1キャパシタの容量が、前記形成されたインダクタ及び前記基本波の周波数に基づいて設定されているようにしてもよい。

【0010】

また、本発明の発振器において、前記周波数選択回路は、前記並列回路に、第2キャパシタと可変容量ダイオードとが直列に接続された回路が並列に接続され、前記第2キャパシタと前記可変容量ダイオードとの接続点に周波数選択用の制御電圧が入力され、前記入力された制御電圧に基づき、前記可変容量ダイオードの容量が可変されることで、前記インダクタ、前記第1キャパシタ、前記第2キャパシタ及び前記可変容量ダイオードによる共振周波数が前記発振回路の基本波の周波数に制御されるようにしてもよい。

【発明の効果】

【0011】

本発明の発振器は、周波数選択回路が、インダクタとコンデンサとの並列回路で構成される。この周波数選択回路の共振周波数は、発振回路における基本波の周波数に設定されている。周波数選択回路は、発振回路が生成した信号の内、基本波の信号を遮断し、高次高調波を通過するようにした。この結果、本発明の発振器は、発振回路が生成した信号の内、選択した高次高調波の信号レベルを、発振回路と負荷とをコンデンサにより疎結合させた場合より向上して通過させることができ、更に、周波数選択回路が基本波で高インピーダンスをもつため、発振回路は負荷変動の影響をほとんど受けず、出力レベルと雑音特性を向上させることができる。

【図面の簡単な説明】

【0012】

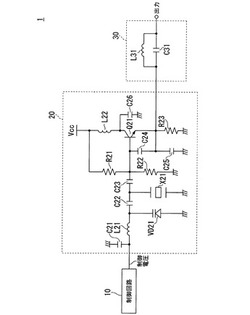

【図1】第1実施形態に係る発振器の回路図の一例である。

【図2】LC並列フィルタの伝達特性の一例である。

【図3】コンデンサの容量と通過特性の一例を説明する図である。

【図4】第2実施形態に係る発振器の回路図の一例である。

【図5】第2実施形態に係る基板上における周波数選択回路のレイアウト図である。

【図6】第3実施形態に係る発振器の回路図の一例である。

【発明を実施するための形態】

【0013】

以下、図面を用いて、本発明の実施形態について説明する。

【0014】

[第1実施形態]

図1は、本実施形態に係る発振器1の回路図の一例である。図1に示すように、発振器1は、制御回路10、発振回路20、及び周波数選択回路30を備えている。

発振回路20は、コンデンサC21〜C26、抵抗R21〜R23、インダクタL21及びL22、トランジスタQ21、可変容量ダイオードVD21、及び水晶振動子X21を備えている。周波数選択回路30は、インダクタL31及びコンデンサC31を備えている。

【0015】

発振回路20の接続構成について、さらに説明する。

コンデンサC21は、一端がインダクタL21の一端が接続され、他端が接地されている。コンデンサC21の一端とインダクタL21の一端の接続点は、制御回路10の出力と接続されている。

インダクタL21は、他端が可変容量ダイオードVD21のカソード及びコンデンサC22の一端に接続されている。可変容量ダイオードVD21は、アノードが接地されている。

コンデンサC22は、他端が水晶振動子X21の一端及びコンデンサC23の一端に接続されている。水晶振動子X21は、他端が接地されている。

コンデンサC23は、他端が抵抗R21の一端、抵抗R22の一端、コンデンサC24の一端、及びトランジスタQ21のベースに接続されている。

【0016】

抵抗R21は、他端が電源Vccに接続され、抵抗R22は、他端が接地されている。

コンデンサC24は、他端が、コンデンサC25の一端、トランジスタQ21のエミッタ、及び抵抗R23の一端に接続されている。

コンデンサC25は、他端が接地され、抵抗R23は、他端が接地されている。また、コンデンサC24の他端、コンデンサC25の一端、トランジスタQ21のエミッタ及び抵抗R23の一端の交点は、周波数選択回路30と接続されている。

トランジスタQ21は、コレクタが、インダクタL22の一端及びコンデンサC26の一端に接続されている。インダクタL22は、他端が電源Vccに接続され、コンデンサC26は、他端が接地されている。

【0017】

次に、周波数選択回路30の接続構成について説明する。

インダクタL31は、一端がコンデンサC31(第1キャパシタ)の一端と接続されている。インダクタL31の一端とコンデンサC31の一端の交点は、発振回路20の出力と接続されている。インダクタL31は、他端がコンデンサC31の他端と接続されている。インダクタL31の他端とコンデンサC31の他端との交点は、図示しない負荷に接続されている。すなわち、周波数選択回路30は、インダクタL31とコンデンサC31が並列に接続されている並列回路である。

【0018】

次に、発振器1の動作を説明する。

制御回路10は、発振周波数を制御する電圧(以下、周波数制御電圧という)を発振回路20に出力する。

発振回路20は、コルピッツ型発振回路である。発振回路20は、共振振動子X21により生成された発振信号をトランジスタQ21で増幅して周波数選択回路30に出力する。また、発振回路20は、制御回路10が出力する周波数制御電圧に基づき、可変容量ダイオードVD21への印加電圧が可変され、発振周波数が可変される。

なお、発振回路20が出力する発振信号は、共振振動子X21が生成した基本波の周波数の信号(以下、基本波信号という)と、基本波信号の高次高調波の周波数の信号(以下、高調波信号という)を含んでいる。

【0019】

周波数選択回路30は、LC並列のノッチフィルタである。周波数選択回路30の共振周波数は、発振回路20が出力する基本波信号の周波数に設定されている。例えば、基本波信号の周波数が4[GHz]の場合、コンデンサC31の容量は1[pF]、インダクタL31のインダクタンスは1.5[nH]程度である。周波数選択回路30は、発振回路20が出力する基本波信号を遮断し、高調波信号を透過し、透過した高調波信号を負荷に出力する。

また、本実施形態では、共振周波数を設定するために、コンデンサC31の容量とインダクタL31のインダクタンスを任意に設定するのではなく、以下に説明するように、共振周波数以上で通過損失が小さくなるようにコンデンサC31の容量を発振器1の設計者が設定する。

【0020】

次に、周波数選択回路30における伝達特性について、図2を用いて説明する。

図2は、LC並列フィルタの伝達特性の一例である。図2(a)は、LC並列フィルタによるインピーダンス特性の一例を示すグラフである。図2(a)において、横軸は周波数を表し、縦軸はインピーダンスの大きさを表している。曲線g101は、周波数に対するコンデンサのインピーダンスを表し、曲線g102は、周波数に対するインダクタのインピーダンスを表し、曲線g103は、周波数に対するLC並列フィルタのインピーダンスを表している。

図2に示すように、LC並列フィルタは、共振周波数fc以下において、インダクタのインピーダンスの影響を受け、共振周波数fc以上において、コンデンサのインピーダンスの影響を受ける。

図2(b)は、負荷が接続されていない場合のLC並列フィルタの伝達特性の一例を示すグラフである。図2(b)において、横軸は周波数を表し、縦軸はゲインを表している。図2(b)に示すように、負荷に接続されていないLC並列フィルタでは、共振周波数fc以上のゲインは、ほぼ0[dB]である。すなわち、共振周波数fc以上における通過による信号レベルの損失(以下、通過損失という)は、ほぼ0[dB]である。

【0021】

しかしながら、LC並列フィルタである周波数選択回路30は、出力が負荷に接続されている。このため、共振周波数fc以上において、負荷側のインピーダンスの影響を受けるため、図2(b)に示した伝達特性とは異なり、共振周波数fc以上の信号は、通過損失の影響を受ける。

このため、本実施形態では、共振周波数fc以上でインピーダンスの影響が支配的なコンデンサの容量を、共振周波数fc以上で通過損失が小さくなるように設定することで、高調波に対する通過損失を軽減する。コンデンサの容量は、例えば疎結合で用いる容量より大きな容量である。

【0022】

次に、コンデンサの容量により通過特性が異なる例を、図3を用いて説明する。

図3は、コンデンサの容量と通過特性の一例を説明する図である。図3において、横軸は周波数であり、縦軸は信号レベルである。また、曲線g201は、コンデンサの容量が2[pF]の通過特性であり、曲線g202は、コンデンサの容量が1[pF]の通過特性であり、曲線g203は、コンデンサの容量が0.5[pF]の通過特性である。なお、図3の通過特性は、インダクタのインダクタンスを共通にし、コンデンサの容量のみを変えて表している。図3に示すように、コンデンサの容量を大きくすると共振周波数が低くなり、同じ高調波帯域でみた場合に共振周波数が離れるほど通過損失は小さくなる。また、図3とは別に、同じ共振周波数になるようにインダクタンスを調整し、同じ高調波帯域でみた場合もコンデンサの容量が大きいほど通過損失は小さくなる。但し、周波数選択回路30は、インダクタンスやコンデンサ自身の自己共振周波数以下で用いる必要がある。

【0023】

以上のように、本実施形態の発振器1は、周波数選択回路30が基本波信号を遮断し、高調波信号を通過することで、発振回路20で生成された発振信号から高調波信号を選択して出力する。また、本実施形態では、コンデンサC31の容量を、共振周波数fc以上で通過損失が小さくなるように設定した。

この結果、周波数選択回路30は、疎結合時と比較して、高調波信号の通過損失を低減させることができる。このため、周波数選択回路30は、高調波信号のレベルの減少を軽減することができるので、雑音特性を向上できる。

【0024】

また、周波数選択回路30をコンデンサC31とインダクタL31により構成したため、共振周波数におけるインピーダンスが無限大であるので、基本波信号を高い通過損失によりカットできる。このように、基本波信号を発振回路20から出力しないことにより、基本波信号は、発振回路20内に留まり、発振ループ内の信号が強くなる。

この結果、発振回路20の非線形動作が促進され、高調波信号のレベルが増加し、雑音特性が改善される。

また、基本波の周波数において、周波数選択回路30は、高インピーダンスであるため、発振回路20の負荷変動による出力周波数と出力レベルの変動が少なくなる。この結果、疎結合した場合と比較して、雑音特性が改善される効果もある。

【0025】

なお、コンデンサは、高周波領域において残留インダクタンスの影響等により自己共振周波数を有している。このため、周波数選択回路30におけるコンデンサC31の自己共振周波数を、発振回路20の高周波信号の周波数と合わせるようして、コンデンサC31を選択するようにしてもよい。

【0026】

[第2実施形態]

図4は、本実施形態に係る発振器1aの回路図の一例である。

図4に示すように、発振器1aは、制御回路10、発振回路20、及び周波数選択回路30aを備えている。発振回路20の構成は、第1実施形態と同じである。周波数選択回路30aは、インダクタL31a及びコンデンサC31a(第1キャパシタ)を備えている。第1実施形態における周波数選択回路30との差異は、インダクタL31aが、図5に示すように基板上に線路により形成されている点である。

このようにインダクタL31aを基板上の線路により形成する場合、インダクタL31aのインダクタンスは、例えば、数[nH]程度までである。

【0027】

図5は、本実施形態に係る基板上における周波数選択回路のレイアウト図である。

図5に示すように、周波数選択回路30aは、基板上に、コンデンサC31aがマウントされるランド301とランド302、及び線路303を含んでいる。ランド301は、発振回路20(図4)の出力と接続され、ランド302は、発振器1aの出力に接続されている。線路303は、一端がランド301に接続され、他端がランド302に接続されている。線路303は、インダクタL31a(図4)に対応し、所望のインダクタンスが、線路長、線路幅を調整して形成されている。また、コンデンサC31aは、一端がランド301にマウントされ、他端がランド302にマウントされる。

また、図5に示すように、インダクタL31aに対応する線路303は、コンデンサ31aがマウントされるランド301及び302に隣接して形成される。

さらに、周波数選択回路30aのパターンは、高周波での寄生成分の影響で周波数選択回路の特性が劣化しないように、発振回路20の直近、例えばマイクロ波帯で1[mm]以内に配置することが望ましい。

【0028】

図4及び図5に示した例において、例えば、基板上に線路303によりインダクタL31aを形成し、形成したインダクタL31aのインダクタンスと周波数選択回路30aの共振周波数に基づき、コンデンサC31aの容量を発振器1aの設計者が設定するようにしてもよい。

この周波数選択回路30aの共振周波数は、第1実施形態と同様に、発振回路20の基本波の周波数に設定されている。また、本実施形態においても、コンデンサC31aの容量は、共振周波数以上において、通過損失が小さくなるように設定される。

【0029】

以上のように、本実施形態では、インダクタL31aを基板上に線路303により形成し、形成した線路303のインダクタンスと周波数選択回路30aの共振周波数に基づき、コンデンサC31aの容量を設定するようにした。この結果、第1実施形態の効果に加え、インダクタL31aをコンデンサC31aに隣接してマウントする場合と比較し、部品コストや基板面積を削減できる。

【0030】

なお、本実施形態では、形成した線路303のインダクタンスと周波数選択回路30aの共振周波数に基づき、コンデンサC31aの容量を設定する例を説明したが、この限りではない。コンデンサC31aのマウント後、例えば線路303の線路幅をトリミングすることでインダクタンスを調整するようにしてもよい。

【0031】

[第3実施形態]

図6は、本実施形態に係る発振器1bの回路図の一例である。

図6に示すように、発振器1bは、制御回路10b、発振回路20、及び周波数選択回路30bを備えている。図6に示すように、発振回路20の構成は、第1実施形態と同じである。

【0032】

制御回路10bは、周波数制御電圧を発振回路20に出力し、フィルタを有する周波数選択回路30bの共振周波数の制御電圧(以下、フィルタ制御電圧という)を周波数選択回路30bに出力する。

周波数選択回路30bは、インダクタL31b及びL32b、コンデンサC31b〜C33b、可変容量ダイオードVD31bを備えている。

インダクタL31bは、一端がコンデンサC31b(第1キャパシタ)の一端及びコンデンサC32b(第2キャパシタ)の一端に接続されている。また、インダクタL31bの一端、コンデンサC31bの一端及びコンデンサC32bの一端の交点は、発振回路20の出力と接続されている。

コンデンサC32bは、他端が可変容量ダイオードVD31bのカソード及びインダクタL32bの一端と接続されている。

インダクタL31bは、他端がコンデンサC31bの他端及び可変容量ダイオードVD31bのアノードに接続されている。また、インダクタL31bの他端、コンデンサC31bの他端及び可変容量ダイオードVD31bのアノードの交点は、発振器1bの出力部に接続されている。

インダクタL32bは、他端がコンデンサC33bの一端及び制御回路10bの出力と接続されている。コンデンサC33bは、他端が接地されている。

【0033】

周波数選択回路30bの共振周波数は、インダクタL31bのインダクタンス、コンデンサC31bとC32bの容量、及び可変容量ダイオードVD31bの容量により設定されている。また、制御回路10bが出力するフィルタ制御電圧により可変容量ダイオードVD31bに印加される電圧が可変されることで、この共振周波数が可変される。

例えば、発振回路20が、制御回路10bが出力する周波数制御電圧により、基本波の周波数がオクターブ変化する場合、周波数選択回路30bの共振周波数も可変する必要がある。このような場合、図6に示したように、可変容量ダイオードVD31bを有する周波数選択回路30を構成し、制御回路10bからのフィルタ制御電圧に応じて、周波数選択回路30bの共振周波数を可変する。なお、オクターブ変化とは、例えば基本波の周波数が、1GHzから2GHzへ変化することである。

【0034】

なお、図6では、制御回路10bが発振回路20に周波数制御電圧を出力し、周波数選択回路30bにフィルタ制御電圧を出力する例を説明したが、制御回路10bが出力する周波数制御と周波数選択回路30bのフィルタ制御電圧とは、同じ制御電圧を用いるようにしてもよい。

【0035】

以上のように、本実施形態では、周波数選択回路30bが可変容量ダイオードVD31bを備えるようにしたので、発振回路20の基本波の周波数が大きく変化した場合においても、周波数選択回路30bの共振周波数を可変できる。この結果、周波数選択回路30bは、発振回路20の基本波の周波数に対応して適切に基本波信号を遮断でき、高調波信号を通過させることができるため、雑音特性が向上する。

【0036】

なお、第1〜第3実施形態では、周波数選択回路30(30a、30b含む)は、発振回路20の基本波の高次高調波を全て通過させる例を説明した。発振器1(1a、1bを含む)が高次高調波の内、特定の高調波のみ負荷側が使用する場合、例えば、周波数選択回路30(30a、30b含む)と負荷との間、または周波数選択回路30(30a、30b含む)内に、所望の周波数を抽出するBPF(バンド・パス・フィルタ)回路を備えるようにしてもよい。

【符号の説明】

【0037】

1、1a、1b・・・発振器、10、10b・・・制御回路、20・・・発振回路、30、30a、30b・・・周波数選択回路、L31、L31a、L31b・・・インダクタ、C31、C31a、C31b・・・コンデンサ、303・・・線路、VD31b・・・可変容量ダイオード

【技術分野】

【0001】

本発明は、発振器に関する。

【背景技術】

【0002】

発振回路が生成した信号を用いる通信装置等において、基本波を用いる発振器と、基本波を逓倍した高次高調波を用いる発振器がある。基本波を逓倍した高次高調波を用いる場合、発振器は、発振回路で生成された信号の内、フィルタ回路により基本波を抑圧し、利用したい高次高周波の周波数を通過させて負荷に出力する。

【0003】

例えば、特許文献1に記載の技術では、発振回路が結合容量を介してリング共振器に接続され、発振周波数の電圧が0になるリング共振器上の一点から出力容量を介して出力を取り出すことで基本波及び奇数次高調波を抑圧し、偶数次高調波を取り出していた。このような回路構成において、一般的に、リング共振器の出力は、容量の小さいコンデンサにより疎結合されている。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開平8−107334号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

しかしながら、特許文献1に記載の技術のように、発振回路の出力にコンデンサを疎結合して高次高調波を取り出す場合、高次高調波の信号レベルは、基本波の信号レベルに対して、例えば10〜20[dB]程度低くなる。利用する高次高調波の信号レベルを上げるために、発振出力の結合を強くすると、発振回路が受ける負荷変動の影響が大きくなり、雑音特性が劣化する課題があった。

【0006】

本発明は、上記の問題点に鑑みてなされたものであって、基本波を逓倍した高次高調波を用いる発振器において、出力レベルと雑音特性を向上させることを目的としている。

【課題を解決するための手段】

【0007】

上記目的を達成するため、本発明に係る発振器は、基本波及び前記基本波の高次高調波を含む信号を生成する発振回路と、前記基本波の通過を阻止し、前記基本波の高次高調波を通過させる周波数選択回路と、を備え、前記周波数選択回路は、インダクタと第1キャパシタとの並列回路を含み、前記並列回路の共振周波数が、前記基本波の周波数に設定されていることを特徴としている。

【0008】

また、本発明の発振器において、前記第1キャパシタは、前記基本波の周波数以上の帯域において、通過損失が予め定められている値より小さくなるように容量が設定されているようにしてもよい。

【0009】

また、本発明の発振器において、前記周波数選択回路は、前記インダクタが、前記第1キャパシタに隣接して基板パターンの線路により形成され、前記第1キャパシタの容量が、前記形成されたインダクタ及び前記基本波の周波数に基づいて設定されているようにしてもよい。

【0010】

また、本発明の発振器において、前記周波数選択回路は、前記並列回路に、第2キャパシタと可変容量ダイオードとが直列に接続された回路が並列に接続され、前記第2キャパシタと前記可変容量ダイオードとの接続点に周波数選択用の制御電圧が入力され、前記入力された制御電圧に基づき、前記可変容量ダイオードの容量が可変されることで、前記インダクタ、前記第1キャパシタ、前記第2キャパシタ及び前記可変容量ダイオードによる共振周波数が前記発振回路の基本波の周波数に制御されるようにしてもよい。

【発明の効果】

【0011】

本発明の発振器は、周波数選択回路が、インダクタとコンデンサとの並列回路で構成される。この周波数選択回路の共振周波数は、発振回路における基本波の周波数に設定されている。周波数選択回路は、発振回路が生成した信号の内、基本波の信号を遮断し、高次高調波を通過するようにした。この結果、本発明の発振器は、発振回路が生成した信号の内、選択した高次高調波の信号レベルを、発振回路と負荷とをコンデンサにより疎結合させた場合より向上して通過させることができ、更に、周波数選択回路が基本波で高インピーダンスをもつため、発振回路は負荷変動の影響をほとんど受けず、出力レベルと雑音特性を向上させることができる。

【図面の簡単な説明】

【0012】

【図1】第1実施形態に係る発振器の回路図の一例である。

【図2】LC並列フィルタの伝達特性の一例である。

【図3】コンデンサの容量と通過特性の一例を説明する図である。

【図4】第2実施形態に係る発振器の回路図の一例である。

【図5】第2実施形態に係る基板上における周波数選択回路のレイアウト図である。

【図6】第3実施形態に係る発振器の回路図の一例である。

【発明を実施するための形態】

【0013】

以下、図面を用いて、本発明の実施形態について説明する。

【0014】

[第1実施形態]

図1は、本実施形態に係る発振器1の回路図の一例である。図1に示すように、発振器1は、制御回路10、発振回路20、及び周波数選択回路30を備えている。

発振回路20は、コンデンサC21〜C26、抵抗R21〜R23、インダクタL21及びL22、トランジスタQ21、可変容量ダイオードVD21、及び水晶振動子X21を備えている。周波数選択回路30は、インダクタL31及びコンデンサC31を備えている。

【0015】

発振回路20の接続構成について、さらに説明する。

コンデンサC21は、一端がインダクタL21の一端が接続され、他端が接地されている。コンデンサC21の一端とインダクタL21の一端の接続点は、制御回路10の出力と接続されている。

インダクタL21は、他端が可変容量ダイオードVD21のカソード及びコンデンサC22の一端に接続されている。可変容量ダイオードVD21は、アノードが接地されている。

コンデンサC22は、他端が水晶振動子X21の一端及びコンデンサC23の一端に接続されている。水晶振動子X21は、他端が接地されている。

コンデンサC23は、他端が抵抗R21の一端、抵抗R22の一端、コンデンサC24の一端、及びトランジスタQ21のベースに接続されている。

【0016】

抵抗R21は、他端が電源Vccに接続され、抵抗R22は、他端が接地されている。

コンデンサC24は、他端が、コンデンサC25の一端、トランジスタQ21のエミッタ、及び抵抗R23の一端に接続されている。

コンデンサC25は、他端が接地され、抵抗R23は、他端が接地されている。また、コンデンサC24の他端、コンデンサC25の一端、トランジスタQ21のエミッタ及び抵抗R23の一端の交点は、周波数選択回路30と接続されている。

トランジスタQ21は、コレクタが、インダクタL22の一端及びコンデンサC26の一端に接続されている。インダクタL22は、他端が電源Vccに接続され、コンデンサC26は、他端が接地されている。

【0017】

次に、周波数選択回路30の接続構成について説明する。

インダクタL31は、一端がコンデンサC31(第1キャパシタ)の一端と接続されている。インダクタL31の一端とコンデンサC31の一端の交点は、発振回路20の出力と接続されている。インダクタL31は、他端がコンデンサC31の他端と接続されている。インダクタL31の他端とコンデンサC31の他端との交点は、図示しない負荷に接続されている。すなわち、周波数選択回路30は、インダクタL31とコンデンサC31が並列に接続されている並列回路である。

【0018】

次に、発振器1の動作を説明する。

制御回路10は、発振周波数を制御する電圧(以下、周波数制御電圧という)を発振回路20に出力する。

発振回路20は、コルピッツ型発振回路である。発振回路20は、共振振動子X21により生成された発振信号をトランジスタQ21で増幅して周波数選択回路30に出力する。また、発振回路20は、制御回路10が出力する周波数制御電圧に基づき、可変容量ダイオードVD21への印加電圧が可変され、発振周波数が可変される。

なお、発振回路20が出力する発振信号は、共振振動子X21が生成した基本波の周波数の信号(以下、基本波信号という)と、基本波信号の高次高調波の周波数の信号(以下、高調波信号という)を含んでいる。

【0019】

周波数選択回路30は、LC並列のノッチフィルタである。周波数選択回路30の共振周波数は、発振回路20が出力する基本波信号の周波数に設定されている。例えば、基本波信号の周波数が4[GHz]の場合、コンデンサC31の容量は1[pF]、インダクタL31のインダクタンスは1.5[nH]程度である。周波数選択回路30は、発振回路20が出力する基本波信号を遮断し、高調波信号を透過し、透過した高調波信号を負荷に出力する。

また、本実施形態では、共振周波数を設定するために、コンデンサC31の容量とインダクタL31のインダクタンスを任意に設定するのではなく、以下に説明するように、共振周波数以上で通過損失が小さくなるようにコンデンサC31の容量を発振器1の設計者が設定する。

【0020】

次に、周波数選択回路30における伝達特性について、図2を用いて説明する。

図2は、LC並列フィルタの伝達特性の一例である。図2(a)は、LC並列フィルタによるインピーダンス特性の一例を示すグラフである。図2(a)において、横軸は周波数を表し、縦軸はインピーダンスの大きさを表している。曲線g101は、周波数に対するコンデンサのインピーダンスを表し、曲線g102は、周波数に対するインダクタのインピーダンスを表し、曲線g103は、周波数に対するLC並列フィルタのインピーダンスを表している。

図2に示すように、LC並列フィルタは、共振周波数fc以下において、インダクタのインピーダンスの影響を受け、共振周波数fc以上において、コンデンサのインピーダンスの影響を受ける。

図2(b)は、負荷が接続されていない場合のLC並列フィルタの伝達特性の一例を示すグラフである。図2(b)において、横軸は周波数を表し、縦軸はゲインを表している。図2(b)に示すように、負荷に接続されていないLC並列フィルタでは、共振周波数fc以上のゲインは、ほぼ0[dB]である。すなわち、共振周波数fc以上における通過による信号レベルの損失(以下、通過損失という)は、ほぼ0[dB]である。

【0021】

しかしながら、LC並列フィルタである周波数選択回路30は、出力が負荷に接続されている。このため、共振周波数fc以上において、負荷側のインピーダンスの影響を受けるため、図2(b)に示した伝達特性とは異なり、共振周波数fc以上の信号は、通過損失の影響を受ける。

このため、本実施形態では、共振周波数fc以上でインピーダンスの影響が支配的なコンデンサの容量を、共振周波数fc以上で通過損失が小さくなるように設定することで、高調波に対する通過損失を軽減する。コンデンサの容量は、例えば疎結合で用いる容量より大きな容量である。

【0022】

次に、コンデンサの容量により通過特性が異なる例を、図3を用いて説明する。

図3は、コンデンサの容量と通過特性の一例を説明する図である。図3において、横軸は周波数であり、縦軸は信号レベルである。また、曲線g201は、コンデンサの容量が2[pF]の通過特性であり、曲線g202は、コンデンサの容量が1[pF]の通過特性であり、曲線g203は、コンデンサの容量が0.5[pF]の通過特性である。なお、図3の通過特性は、インダクタのインダクタンスを共通にし、コンデンサの容量のみを変えて表している。図3に示すように、コンデンサの容量を大きくすると共振周波数が低くなり、同じ高調波帯域でみた場合に共振周波数が離れるほど通過損失は小さくなる。また、図3とは別に、同じ共振周波数になるようにインダクタンスを調整し、同じ高調波帯域でみた場合もコンデンサの容量が大きいほど通過損失は小さくなる。但し、周波数選択回路30は、インダクタンスやコンデンサ自身の自己共振周波数以下で用いる必要がある。

【0023】

以上のように、本実施形態の発振器1は、周波数選択回路30が基本波信号を遮断し、高調波信号を通過することで、発振回路20で生成された発振信号から高調波信号を選択して出力する。また、本実施形態では、コンデンサC31の容量を、共振周波数fc以上で通過損失が小さくなるように設定した。

この結果、周波数選択回路30は、疎結合時と比較して、高調波信号の通過損失を低減させることができる。このため、周波数選択回路30は、高調波信号のレベルの減少を軽減することができるので、雑音特性を向上できる。

【0024】

また、周波数選択回路30をコンデンサC31とインダクタL31により構成したため、共振周波数におけるインピーダンスが無限大であるので、基本波信号を高い通過損失によりカットできる。このように、基本波信号を発振回路20から出力しないことにより、基本波信号は、発振回路20内に留まり、発振ループ内の信号が強くなる。

この結果、発振回路20の非線形動作が促進され、高調波信号のレベルが増加し、雑音特性が改善される。

また、基本波の周波数において、周波数選択回路30は、高インピーダンスであるため、発振回路20の負荷変動による出力周波数と出力レベルの変動が少なくなる。この結果、疎結合した場合と比較して、雑音特性が改善される効果もある。

【0025】

なお、コンデンサは、高周波領域において残留インダクタンスの影響等により自己共振周波数を有している。このため、周波数選択回路30におけるコンデンサC31の自己共振周波数を、発振回路20の高周波信号の周波数と合わせるようして、コンデンサC31を選択するようにしてもよい。

【0026】

[第2実施形態]

図4は、本実施形態に係る発振器1aの回路図の一例である。

図4に示すように、発振器1aは、制御回路10、発振回路20、及び周波数選択回路30aを備えている。発振回路20の構成は、第1実施形態と同じである。周波数選択回路30aは、インダクタL31a及びコンデンサC31a(第1キャパシタ)を備えている。第1実施形態における周波数選択回路30との差異は、インダクタL31aが、図5に示すように基板上に線路により形成されている点である。

このようにインダクタL31aを基板上の線路により形成する場合、インダクタL31aのインダクタンスは、例えば、数[nH]程度までである。

【0027】

図5は、本実施形態に係る基板上における周波数選択回路のレイアウト図である。

図5に示すように、周波数選択回路30aは、基板上に、コンデンサC31aがマウントされるランド301とランド302、及び線路303を含んでいる。ランド301は、発振回路20(図4)の出力と接続され、ランド302は、発振器1aの出力に接続されている。線路303は、一端がランド301に接続され、他端がランド302に接続されている。線路303は、インダクタL31a(図4)に対応し、所望のインダクタンスが、線路長、線路幅を調整して形成されている。また、コンデンサC31aは、一端がランド301にマウントされ、他端がランド302にマウントされる。

また、図5に示すように、インダクタL31aに対応する線路303は、コンデンサ31aがマウントされるランド301及び302に隣接して形成される。

さらに、周波数選択回路30aのパターンは、高周波での寄生成分の影響で周波数選択回路の特性が劣化しないように、発振回路20の直近、例えばマイクロ波帯で1[mm]以内に配置することが望ましい。

【0028】

図4及び図5に示した例において、例えば、基板上に線路303によりインダクタL31aを形成し、形成したインダクタL31aのインダクタンスと周波数選択回路30aの共振周波数に基づき、コンデンサC31aの容量を発振器1aの設計者が設定するようにしてもよい。

この周波数選択回路30aの共振周波数は、第1実施形態と同様に、発振回路20の基本波の周波数に設定されている。また、本実施形態においても、コンデンサC31aの容量は、共振周波数以上において、通過損失が小さくなるように設定される。

【0029】

以上のように、本実施形態では、インダクタL31aを基板上に線路303により形成し、形成した線路303のインダクタンスと周波数選択回路30aの共振周波数に基づき、コンデンサC31aの容量を設定するようにした。この結果、第1実施形態の効果に加え、インダクタL31aをコンデンサC31aに隣接してマウントする場合と比較し、部品コストや基板面積を削減できる。

【0030】

なお、本実施形態では、形成した線路303のインダクタンスと周波数選択回路30aの共振周波数に基づき、コンデンサC31aの容量を設定する例を説明したが、この限りではない。コンデンサC31aのマウント後、例えば線路303の線路幅をトリミングすることでインダクタンスを調整するようにしてもよい。

【0031】

[第3実施形態]

図6は、本実施形態に係る発振器1bの回路図の一例である。

図6に示すように、発振器1bは、制御回路10b、発振回路20、及び周波数選択回路30bを備えている。図6に示すように、発振回路20の構成は、第1実施形態と同じである。

【0032】

制御回路10bは、周波数制御電圧を発振回路20に出力し、フィルタを有する周波数選択回路30bの共振周波数の制御電圧(以下、フィルタ制御電圧という)を周波数選択回路30bに出力する。

周波数選択回路30bは、インダクタL31b及びL32b、コンデンサC31b〜C33b、可変容量ダイオードVD31bを備えている。

インダクタL31bは、一端がコンデンサC31b(第1キャパシタ)の一端及びコンデンサC32b(第2キャパシタ)の一端に接続されている。また、インダクタL31bの一端、コンデンサC31bの一端及びコンデンサC32bの一端の交点は、発振回路20の出力と接続されている。

コンデンサC32bは、他端が可変容量ダイオードVD31bのカソード及びインダクタL32bの一端と接続されている。

インダクタL31bは、他端がコンデンサC31bの他端及び可変容量ダイオードVD31bのアノードに接続されている。また、インダクタL31bの他端、コンデンサC31bの他端及び可変容量ダイオードVD31bのアノードの交点は、発振器1bの出力部に接続されている。

インダクタL32bは、他端がコンデンサC33bの一端及び制御回路10bの出力と接続されている。コンデンサC33bは、他端が接地されている。

【0033】

周波数選択回路30bの共振周波数は、インダクタL31bのインダクタンス、コンデンサC31bとC32bの容量、及び可変容量ダイオードVD31bの容量により設定されている。また、制御回路10bが出力するフィルタ制御電圧により可変容量ダイオードVD31bに印加される電圧が可変されることで、この共振周波数が可変される。

例えば、発振回路20が、制御回路10bが出力する周波数制御電圧により、基本波の周波数がオクターブ変化する場合、周波数選択回路30bの共振周波数も可変する必要がある。このような場合、図6に示したように、可変容量ダイオードVD31bを有する周波数選択回路30を構成し、制御回路10bからのフィルタ制御電圧に応じて、周波数選択回路30bの共振周波数を可変する。なお、オクターブ変化とは、例えば基本波の周波数が、1GHzから2GHzへ変化することである。

【0034】

なお、図6では、制御回路10bが発振回路20に周波数制御電圧を出力し、周波数選択回路30bにフィルタ制御電圧を出力する例を説明したが、制御回路10bが出力する周波数制御と周波数選択回路30bのフィルタ制御電圧とは、同じ制御電圧を用いるようにしてもよい。

【0035】

以上のように、本実施形態では、周波数選択回路30bが可変容量ダイオードVD31bを備えるようにしたので、発振回路20の基本波の周波数が大きく変化した場合においても、周波数選択回路30bの共振周波数を可変できる。この結果、周波数選択回路30bは、発振回路20の基本波の周波数に対応して適切に基本波信号を遮断でき、高調波信号を通過させることができるため、雑音特性が向上する。

【0036】

なお、第1〜第3実施形態では、周波数選択回路30(30a、30b含む)は、発振回路20の基本波の高次高調波を全て通過させる例を説明した。発振器1(1a、1bを含む)が高次高調波の内、特定の高調波のみ負荷側が使用する場合、例えば、周波数選択回路30(30a、30b含む)と負荷との間、または周波数選択回路30(30a、30b含む)内に、所望の周波数を抽出するBPF(バンド・パス・フィルタ)回路を備えるようにしてもよい。

【符号の説明】

【0037】

1、1a、1b・・・発振器、10、10b・・・制御回路、20・・・発振回路、30、30a、30b・・・周波数選択回路、L31、L31a、L31b・・・インダクタ、C31、C31a、C31b・・・コンデンサ、303・・・線路、VD31b・・・可変容量ダイオード

【特許請求の範囲】

【請求項1】

基本波及び前記基本波の高次高調波を含む信号を生成する発振回路と、

前記基本波の通過を阻止し、前記基本波の高次高調波を通過させる周波数選択回路と、

を備え、

前記周波数選択回路は、

インダクタと第1キャパシタとの並列回路を含み、前記並列回路の共振周波数が、前記基本波の周波数に設定されている

ことを特徴とする発振器。

【請求項2】

前記第1キャパシタは、

前記基本波の周波数以上の帯域において、通過損失が予め定められている値より小さくなるように容量が設定されている

ことを特徴とする請求項1に記載の発振器。

【請求項3】

前記周波数選択回路は、

前記インダクタが、前記第1キャパシタに隣接して基板パターンの線路により形成され、

前記第1キャパシタの容量が、前記形成されたインダクタ及び前記基本波の周波数に基づいて設定されている

ことを特徴とする請求項1または請求項2に記載の発振器。

【請求項4】

前記周波数選択回路は、

前記並列回路に、第2キャパシタと可変容量ダイオードとが直列に接続された回路が並列に接続され、前記第2キャパシタと前記可変容量ダイオードとの接続点に周波数選択用の制御電圧が入力され、

前記入力された制御電圧に基づき、前記可変容量ダイオードの容量が可変されることで、前記インダクタ、前記第1キャパシタ、前記第2キャパシタ及び前記可変容量ダイオードによる共振周波数が前記発振回路の基本波の周波数に制御される

ことを特徴とする請求項1から請求項3のいずれか1項に記載の発振器。

【請求項1】

基本波及び前記基本波の高次高調波を含む信号を生成する発振回路と、

前記基本波の通過を阻止し、前記基本波の高次高調波を通過させる周波数選択回路と、

を備え、

前記周波数選択回路は、

インダクタと第1キャパシタとの並列回路を含み、前記並列回路の共振周波数が、前記基本波の周波数に設定されている

ことを特徴とする発振器。

【請求項2】

前記第1キャパシタは、

前記基本波の周波数以上の帯域において、通過損失が予め定められている値より小さくなるように容量が設定されている

ことを特徴とする請求項1に記載の発振器。

【請求項3】

前記周波数選択回路は、

前記インダクタが、前記第1キャパシタに隣接して基板パターンの線路により形成され、

前記第1キャパシタの容量が、前記形成されたインダクタ及び前記基本波の周波数に基づいて設定されている

ことを特徴とする請求項1または請求項2に記載の発振器。

【請求項4】

前記周波数選択回路は、

前記並列回路に、第2キャパシタと可変容量ダイオードとが直列に接続された回路が並列に接続され、前記第2キャパシタと前記可変容量ダイオードとの接続点に周波数選択用の制御電圧が入力され、

前記入力された制御電圧に基づき、前記可変容量ダイオードの容量が可変されることで、前記インダクタ、前記第1キャパシタ、前記第2キャパシタ及び前記可変容量ダイオードによる共振周波数が前記発振回路の基本波の周波数に制御される

ことを特徴とする請求項1から請求項3のいずれか1項に記載の発振器。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図2】

【図3】

【図4】

【図5】

【図6】

【公開番号】特開2013−98795(P2013−98795A)

【公開日】平成25年5月20日(2013.5.20)

【国際特許分類】

【出願番号】特願2011−240494(P2011−240494)

【出願日】平成23年11月1日(2011.11.1)

【国等の委託研究の成果に係る記載事項】(出願人による申告)平成22年度、総務省、「電波資源拡大のための研究開発」、委託研究、産業技術力強化法第19条の適用を受ける特許出願

【出願人】(000004330)日本無線株式会社 (1,186)

【Fターム(参考)】

【公開日】平成25年5月20日(2013.5.20)

【国際特許分類】

【出願日】平成23年11月1日(2011.11.1)

【国等の委託研究の成果に係る記載事項】(出願人による申告)平成22年度、総務省、「電波資源拡大のための研究開発」、委託研究、産業技術力強化法第19条の適用を受ける特許出願

【出願人】(000004330)日本無線株式会社 (1,186)

【Fターム(参考)】

[ Back to top ]