発振回路およびそれを用いた電子機器

【課題】スペクトルのピークを抑制する。

【解決手段】発振回路2は、基準クロック信号CKREFを受け、出力クロック信号CKOUTを生成する。プログラマブル分周器18は、その分周比が少なくとも2値で切りかえ可能に構成され、出力クロック信号CKOUTを設定された分周比で分周し、分周クロック信号CKDIVを生成する。位相比較器10は、基準クロック信号CKREFと分周クロック信号CKDIVの位相差に応じた位相差信号S1を生成する。ループフィルタ12は、位相差信号S1を平滑化する。VCO(電圧制御発振器)14は、ループフィルタ12から出力される位相差信号S2に応じた周波数で発振し、出力クロック信号CKOUTを生成する。制御部20は、プログラマブル分周器18の分周比を、時分割的に切りかえることにより出力クロック信号CKOUTのスペクトルを拡散させる。

【解決手段】発振回路2は、基準クロック信号CKREFを受け、出力クロック信号CKOUTを生成する。プログラマブル分周器18は、その分周比が少なくとも2値で切りかえ可能に構成され、出力クロック信号CKOUTを設定された分周比で分周し、分周クロック信号CKDIVを生成する。位相比較器10は、基準クロック信号CKREFと分周クロック信号CKDIVの位相差に応じた位相差信号S1を生成する。ループフィルタ12は、位相差信号S1を平滑化する。VCO(電圧制御発振器)14は、ループフィルタ12から出力される位相差信号S2に応じた周波数で発振し、出力クロック信号CKOUTを生成する。制御部20は、プログラマブル分周器18の分周比を、時分割的に切りかえることにより出力クロック信号CKOUTのスペクトルを拡散させる。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、発振回路に関する。

【背景技術】

【0002】

家電機器や映像機器などの電子機器に搭載されるマイクロコンピュータ、スイッチング電源、モータドライバ、液晶ドライバ等は、クロック信号と同期して動作する。一方、こうした電子機器は、十分なEMI(Electro Magnetic Interference)対策が施されていることが要求される。特に、近年の無線通信技術の進歩により、EMI対策の要求は高まっている。

【0003】

EMI対策のために、クロック信号のスペクトルを意図的に拡散する場合がある。図1は、本発明者らが検討したスペクトラム拡散が可能なPLL回路を示す回路図である。PLL回路2rは、基準クロック信号CKREFを受け、出力クロック信号CKOUTを生成する。PLL回路2rは、位相比較器10、ループフィルタ12、VCO(Voltage Controlled Oscillator)14、分周器16、変調器30を備える。

【0004】

分周器16は、周波数fOUTの出力クロック信号CKOUTを、分周比Mで分周し、周波数fDIV(=fOUT/M)の分周クロック信号CKDIVを生成する。位相比較器10は、基準クロック信号CKOUTと分周クロック信号CKDIVの位相差に応じた位相差信号S1を生成する。ループフィルタ12は、位相差信号S1を平滑化する。

【0005】

変調器30は、変調信号生成部30aと、重畳回路30bを含み、VCO14の入力電圧を変調する。変調信号生成部30aは、周期的に変化する変調信号S3を生成する。重畳回路30bは、ループフィルタ12から出力される位相差信号S2に、変調信号S3を重畳する。

【0006】

VCO14は、変調信号S3が重畳された位相差信号S4に応じた周波数で発振し、出力クロック信号CKOUTを生成する。変調信号S3として、線形的に変化する三角波信号を用いると、スペクトルのピークを抑制することができる。

【先行技術文献】

【特許文献】

【0007】

【特許文献1】特開2006−95330号公報

【発明の概要】

【発明が解決しようとする課題】

【0008】

ところが三角波信号のピークおよびボトムにおいて、VCOの入力電圧が急峻に変化するため、この急峻な変化がスペクトルに別のピークをもたらす。

【0009】

また、三角波信号のスロープの途中において、PLL回路が一瞬ロックし、ロックが外れるという動作を繰り返す。本発明者は、PLL回路がロックするときに、VCOの入力電圧が歪み、これによりスペクトルにピークが発生することを認識するに至った。

【0010】

本発明はこうした課題に鑑みてなされたものであり、そのある態様の例示的な目的のひとつは、スペクトルのピークが抑制された発振回路の提供にある。

【課題を解決するための手段】

【0011】

本発明のある態様は、基準クロック信号を受け、出力クロック信号を生成する発振回路に関する。発振回路は、分周比が少なくとも2値で切りかえ可能に構成され、出力クロック信号を設定された分周比で分周し、分周クロック信号を生成するプログラマブル分周器と、基準クロック信号と分周クロック信号の位相差に応じた位相差信号を生成する位相比較器と、位相差信号を平滑化するループフィルタと、ループフィルタから出力される位相差信号に応じた周波数で発振し、出力クロック信号を生成するVCO(電圧制御発振器)と、プログラマブル分周器の分周比を、時分割的に切りかえることにより出力クロック信号のスペクトルを拡散させる制御部と、を備える。

【0012】

この態様によると、発振回路のロック周波数が、分周比の切りかえに応じて変化する。それにより、出力クロック信号の周波数は、各分周比に応じた複数のロック周波数の間で緩やかに遷移することになり、スペクトルを拡散することができる。

【0013】

制御部は、発振回路がロックしないように、プログラマブル分周器の分周比を切りかえてもよい。

発振回路をロックさせないことにより、ロックにともなう歪みを除去できるため、スペクトルのピークを低減できる。

【0014】

制御部がプログラマブル分周器の分周比を切りかえる周期は、発振回路のロック時間より短くてもよい。制御部がプログラマブル分周器の分周比を切りかえる周期は、ループフィルタの時定数より短くてもよい。

【0015】

制御部は、VCOの入力電圧が線形的に変化するように、プログラマブル分周器の分周比を切りかえてもよい。

分周比を切りかえる周期を、ループフィルタの時定数よりも短くすることにより、VCOの入力電圧は、線形的に変化することとなり、その波形は三角波に近くなる。これにより、歪みをさらに低減することができる。

【0016】

本発明の別の態様は、電子機器に関する。この電子機器は、上述のいずれかの発振回路と、発振回路が生成する出力クロック信号を受けて動作するプロセッサと、を備える。

【0017】

なお、以上の構成要素の任意の組み合わせや本発明の構成要素や表現を、方法、装置、システムなどの間で相互に置換したものもまた、本発明の態様として有効である。

【発明の効果】

【0018】

本発明のある態様によれば、発振回路のスペクトルのピークを抑制できる。

【図面の簡単な説明】

【0019】

【図1】本発明者らが検討したスペクトラム拡散が可能なPLL回路を示す回路図である。

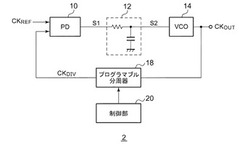

【図2】実施の形態に係る発振回路の構成を示す回路図である。

【図3】図3(a)、(b)はそれぞれ、第1、第2の制御方法の動作波形図である。

【図4】図4(a)、(b)はそれぞれ、第1、第2の制御方法における発振回路の消費電流のスペクトルの実測値を示す図である。

【図5】図2の発振回路を備える電子機器の構成を示すブロック図である。

【発明を実施するための形態】

【0020】

以下、本発明を好適な実施の形態をもとに図面を参照しながら説明する。各図面に示される同一または同等の構成要素、部材、処理には、同一の符号を付するものとし、適宜重複した説明は省略する。また、実施の形態は、発明を限定するものではなく例示であって、実施の形態に記述されるすべての特徴やその組み合わせは、必ずしも発明の本質的なものであるとは限らない。

【0021】

本明細書において、「部材Aが、部材Bと接続された状態」とは、部材Aと部材Bが物理的に直接的に接続される場合のほか、部材Aと部材Bが、それらの電気的な接続状態に実質的な影響を及ぼさない、あるいはそれらの結合により奏される機能や効果を損なわせない、その他の部材を介して間接的に接続される場合も含む。

同様に、「部材Cが、部材Aと部材Bの間に設けられた状態」とは、部材Aと部材C、あるいは部材Bと部材Cが直接的に接続される場合のほか、それらの電気的な接続状態に実質的な影響を及ぼさない、あるいはそれらの結合により奏される機能や効果を損なわせない、その他の部材を介して間接的に接続される場合も含む。

【0022】

図2は、実施の形態に係る発振回路2の構成を示す回路図である。発振回路2は、基準クロック信号CKREFを受け、出力クロック信号CKOUTを生成する。発振回路2は、位相比較器10、ループフィルタ12、VCO14、プログラマブル分周器18、制御部20を備える。

【0023】

プログラマブル分周器18は、分周比が少なくとも2値で切りかえ可能に構成される。本実施の形態では、分周比は、M1、M2の2値で切りかえられるものとする。プログラマブル分周器18は、周波数fOUTの出力クロック信号CKOUTを、分周比M1、M2のうちの設定された値で分周し、周波数fDIVの分周クロック信号CKDIVを生成する。つまり、分周比がM1のときfDIV=fOUT/M1、分周比がM2のときfDIV=fOUT/M2となる。位相比較器10は、基準クロック信号CKOUTと分周クロック信号CKDIVの位相差に応じた位相差信号S1を生成する。ループフィルタ12は、位相差信号S1を平滑化する。

【0024】

VCO14は、ループフィルタ12により平滑化された位相差信号(制御電圧ともいう)S2に応じた周波数で発振し、出力クロック信号CKOUTを生成する。

【0025】

制御部20は、プログラマブル分周器18の分周比を、時分割的に切りかえ、それにより出力クロック信号CKOUTのスペクトルを拡散させる。制御部20は、後述のように、第1の制御方法、または第2の制御方法によって、プログラマブル分周器18の分周比を切りかえる。

【0026】

以上が発振回路2の構成である。続いてその動作を説明する。

【0027】

図3(a)、(b)はそれぞれ、第1、第2の制御方法の動作波形図である。上段はプログラマブル分周器18に設定される分周比Mを、下段は、VCO14に入力される制御電圧S2を示す。図4(a)、(b)はそれぞれ、第1、第2の制御方法における発振回路2の消費電流のスペクトルの実測値を示す図である。

【0028】

はじめに、図3(a)、図4(a)を参照して、第1の制御方法について説明する。第1の制御方法では、図3(a)に示すように、分周比をある値に設定して発振回路2がロックした後に、分周比を別の値に切りかえる動作を繰り返す。すなわち、発振回路2は、ロック、アンロック状態を繰り返しており、制御部20がプログラマブル分周器16の分周比Mを切りかえる周期TSは、発振回路2のロック時間TLと実質的に同程度か、それよりも長くなっている。

【0029】

第1の制御方法では、VCO14に対する制御電圧S2は、2つの分周比M1、M2に応じた2つの電圧V1、V2の間で遷移する。そしてその電圧波形は、ループフィルタ12の時定数に応じた波形となる。

【0030】

第1の制御方法によれば、VCO14に対する制御電圧S2を時間的に変動させることができるため、図4(a)に示すように、スペクトルを拡散させることができる。

【0031】

(第2の制御方法)

多くの用途において、第1の制御方法でも十分な特性が得られるが、より好適にスペクトルを拡散させるためには、第2の制御方法を有効である。

【0032】

第1の制御方法では、発振回路2がロック、アンロックを繰り返すものであった。これに対して第2の制御方法では、制御部20は、発振回路がロックしないように、第1の制御方法よりも短い周期でプログラマブル分周器16の分周比Mを切りかえる。言い換えれば、制御部20がプログラマブル分周器16の分周比Mを切りかえる周期TSは、発振回路2のロック時間TLより短くなっている。別の観点から見ると、制御部20がプログラマブル分周器16の分周比Mを切りかえる周期TSは、ループフィルタ12の時定数より短くなっている。

【0033】

第2の制御方法によれば、第1の制御方法と同様に、VCO14の入力電圧S2を時間的に変化させることができ、スペクトルを拡散させることができる。

【0034】

また第1の制御方法では、発振回路2がロックする際の制御電圧S2の波形歪みによって、スペクトルに不要なピークが発生する。これに対して第2の制御方法では、発振回路2をロックしない状態で動作させることにより、第1の制御方法に比べて、スペクトルのピークを抑制できる。

【0035】

第2の制御方法において、制御部20は、VCO12に対する制御電圧S2が線形的に変化するような周期TSにて、プログラマブル分周器16の分周比Mを切りかえるとよい。ループフィルタ12をCRフィルタで構成する場合、制御電圧S2は図3(a)に示すように指数関数的に変化するところ、分周比Mの切りかえ直後の制御電圧S2は、線形近似できる。すなわち、分周比Mの切りかえ周期TSをCR時定数よりも十分に短く設定することにより、制御電圧S2は、図3(b)に示すように直線的に変化し、三角波に近くなる。これにより、第1の制御方法よりもさらにスペクトルのピークを抑制することができる。

【0036】

以上が発振回路2の動作である。続いて、発振回路2の好適な用途を説明する。

図5は、図2の発振回路2を備える電子機器1の構成を示すブロック図である。

電子機器1は、スピーカSPK、マイクMIC、発振回路2、フロントエンドIC(Integrated Circuit)4およびDSP(Digital Signal Processor)6を備える。

【0037】

電子機器1は、たとえば携帯電話端末やデジタルカメラ、オーディオプレイヤをはじめとするオーディオ再生、録音機能を備えるデバイスである。

【0038】

マイクMICは、入力された音響信号を、アナログの電気信号(アナログオーディオ信号)S10に変換する。フロントエンドIC4は、アナログオーディオ信号S10を受け、A/Dコンバータ42によってデジタルオーディオ信号S12に変換する。インタフェース回路44は、デジタルオーディオ信号S14を、バス5を介してDSP6に送信する。

【0039】

また、フロントエンドIC4のインタフェース回路44は、DSP6により再生されたデジタルオーディオ信号S22を受信する。D/Aコンバータ46は、受信したデジタルオーディオ信号S24をアナログオーディオ信号S26に変換する。アナログオーディオ信号S26は、図示しないアンプ等を介して、スピーカSPKへと出力される。

【0040】

DSP6は、デジタルオーディオ信号の符号化、復号化を行うCODEC(Code-DECode)−ICであり、録音機能と再生機能を備える。

DSP6のインタフェース回路62は、フロントエンドIC4からのデジタルオーディオ信号S14を受ける。CODEC回路64は、フロントエンドIC4から送信されたデジタルオーディオ信号S16(S14)を受け、それを所定のフォーマットに圧縮・符号化し、図示しないメモリへ格納する(録音機能)。

【0041】

また、CODEC回路64は、図示しないメモリに格納されたデジタルオーディオ信号を読み出し、読み出されたデータを復号化し、デジタルオーディオ信号S20に変換する。インタフェース回路62は、デジタルオーディオ信号S20を、バス5を介してフロントエンドIC4に送信する(再生機能)。

【0042】

ここで、フロントエンドIC4のA/Dコンバータ42およびD/Aコンバータ46に供給されるクロック信号CK1は、高音質な録音、再生のために、低ジッタであることが要求される。

【0043】

また、フロントエンドIC4のインタフェース回路44およびDSP6のインタフェース回路62に供給されるクロック信号CK2a、CK2bは、互いに同期がとれていることが要求される。

【0044】

一方、CODEC回路64において行われる符号化、復号化処理や、イコライジング処理、フィルタリング処理をはじめとするその他のデジタル演算処理は、他の回路との独立性が高く、したがって、それに供給されるクロック信号CK3には、ある程度のジッタが許容される。実施の形態に係る発振回路2は、CODEC回路64に対して、クロック信号CK3(CKOUT)を供給する用途に好適に利用することができる。

【0045】

なお、発振回路2は、DSP6の外部に設けられてもよいし、DSP6に内蔵されてもよい。また、フロントエンドIC4のA/Dコンバータ42、D/Aコンバータ46は、DSP6に内蔵されてもよい。この場合、インタフェース回路44、インタフェース回路62は不要である。この場合であっても、CODEC回路64のクロック信号CK2には、低ジッタ性は要求されないため、発振回路2が生成するクロック信号CKOUTを利用できる。

【0046】

実施の形態にもとづき、具体的な用語を用いて本発明を説明したが、実施の形態は、本発明の原理、応用を示しているにすぎず、実施の形態には、請求の範囲に規定された本発明の思想を逸脱しない範囲において、多くの変形例や配置の変更が認められる。

【符号の説明】

【0047】

1…電子機器、2…発振回路、10…位相比較器、12…ループフィルタ、14…VCO、16…分周器、18…プログラマブル分周器、20…制御部、30…変調器、30a…変調信号生成部、30b…重畳回路。

【技術分野】

【0001】

本発明は、発振回路に関する。

【背景技術】

【0002】

家電機器や映像機器などの電子機器に搭載されるマイクロコンピュータ、スイッチング電源、モータドライバ、液晶ドライバ等は、クロック信号と同期して動作する。一方、こうした電子機器は、十分なEMI(Electro Magnetic Interference)対策が施されていることが要求される。特に、近年の無線通信技術の進歩により、EMI対策の要求は高まっている。

【0003】

EMI対策のために、クロック信号のスペクトルを意図的に拡散する場合がある。図1は、本発明者らが検討したスペクトラム拡散が可能なPLL回路を示す回路図である。PLL回路2rは、基準クロック信号CKREFを受け、出力クロック信号CKOUTを生成する。PLL回路2rは、位相比較器10、ループフィルタ12、VCO(Voltage Controlled Oscillator)14、分周器16、変調器30を備える。

【0004】

分周器16は、周波数fOUTの出力クロック信号CKOUTを、分周比Mで分周し、周波数fDIV(=fOUT/M)の分周クロック信号CKDIVを生成する。位相比較器10は、基準クロック信号CKOUTと分周クロック信号CKDIVの位相差に応じた位相差信号S1を生成する。ループフィルタ12は、位相差信号S1を平滑化する。

【0005】

変調器30は、変調信号生成部30aと、重畳回路30bを含み、VCO14の入力電圧を変調する。変調信号生成部30aは、周期的に変化する変調信号S3を生成する。重畳回路30bは、ループフィルタ12から出力される位相差信号S2に、変調信号S3を重畳する。

【0006】

VCO14は、変調信号S3が重畳された位相差信号S4に応じた周波数で発振し、出力クロック信号CKOUTを生成する。変調信号S3として、線形的に変化する三角波信号を用いると、スペクトルのピークを抑制することができる。

【先行技術文献】

【特許文献】

【0007】

【特許文献1】特開2006−95330号公報

【発明の概要】

【発明が解決しようとする課題】

【0008】

ところが三角波信号のピークおよびボトムにおいて、VCOの入力電圧が急峻に変化するため、この急峻な変化がスペクトルに別のピークをもたらす。

【0009】

また、三角波信号のスロープの途中において、PLL回路が一瞬ロックし、ロックが外れるという動作を繰り返す。本発明者は、PLL回路がロックするときに、VCOの入力電圧が歪み、これによりスペクトルにピークが発生することを認識するに至った。

【0010】

本発明はこうした課題に鑑みてなされたものであり、そのある態様の例示的な目的のひとつは、スペクトルのピークが抑制された発振回路の提供にある。

【課題を解決するための手段】

【0011】

本発明のある態様は、基準クロック信号を受け、出力クロック信号を生成する発振回路に関する。発振回路は、分周比が少なくとも2値で切りかえ可能に構成され、出力クロック信号を設定された分周比で分周し、分周クロック信号を生成するプログラマブル分周器と、基準クロック信号と分周クロック信号の位相差に応じた位相差信号を生成する位相比較器と、位相差信号を平滑化するループフィルタと、ループフィルタから出力される位相差信号に応じた周波数で発振し、出力クロック信号を生成するVCO(電圧制御発振器)と、プログラマブル分周器の分周比を、時分割的に切りかえることにより出力クロック信号のスペクトルを拡散させる制御部と、を備える。

【0012】

この態様によると、発振回路のロック周波数が、分周比の切りかえに応じて変化する。それにより、出力クロック信号の周波数は、各分周比に応じた複数のロック周波数の間で緩やかに遷移することになり、スペクトルを拡散することができる。

【0013】

制御部は、発振回路がロックしないように、プログラマブル分周器の分周比を切りかえてもよい。

発振回路をロックさせないことにより、ロックにともなう歪みを除去できるため、スペクトルのピークを低減できる。

【0014】

制御部がプログラマブル分周器の分周比を切りかえる周期は、発振回路のロック時間より短くてもよい。制御部がプログラマブル分周器の分周比を切りかえる周期は、ループフィルタの時定数より短くてもよい。

【0015】

制御部は、VCOの入力電圧が線形的に変化するように、プログラマブル分周器の分周比を切りかえてもよい。

分周比を切りかえる周期を、ループフィルタの時定数よりも短くすることにより、VCOの入力電圧は、線形的に変化することとなり、その波形は三角波に近くなる。これにより、歪みをさらに低減することができる。

【0016】

本発明の別の態様は、電子機器に関する。この電子機器は、上述のいずれかの発振回路と、発振回路が生成する出力クロック信号を受けて動作するプロセッサと、を備える。

【0017】

なお、以上の構成要素の任意の組み合わせや本発明の構成要素や表現を、方法、装置、システムなどの間で相互に置換したものもまた、本発明の態様として有効である。

【発明の効果】

【0018】

本発明のある態様によれば、発振回路のスペクトルのピークを抑制できる。

【図面の簡単な説明】

【0019】

【図1】本発明者らが検討したスペクトラム拡散が可能なPLL回路を示す回路図である。

【図2】実施の形態に係る発振回路の構成を示す回路図である。

【図3】図3(a)、(b)はそれぞれ、第1、第2の制御方法の動作波形図である。

【図4】図4(a)、(b)はそれぞれ、第1、第2の制御方法における発振回路の消費電流のスペクトルの実測値を示す図である。

【図5】図2の発振回路を備える電子機器の構成を示すブロック図である。

【発明を実施するための形態】

【0020】

以下、本発明を好適な実施の形態をもとに図面を参照しながら説明する。各図面に示される同一または同等の構成要素、部材、処理には、同一の符号を付するものとし、適宜重複した説明は省略する。また、実施の形態は、発明を限定するものではなく例示であって、実施の形態に記述されるすべての特徴やその組み合わせは、必ずしも発明の本質的なものであるとは限らない。

【0021】

本明細書において、「部材Aが、部材Bと接続された状態」とは、部材Aと部材Bが物理的に直接的に接続される場合のほか、部材Aと部材Bが、それらの電気的な接続状態に実質的な影響を及ぼさない、あるいはそれらの結合により奏される機能や効果を損なわせない、その他の部材を介して間接的に接続される場合も含む。

同様に、「部材Cが、部材Aと部材Bの間に設けられた状態」とは、部材Aと部材C、あるいは部材Bと部材Cが直接的に接続される場合のほか、それらの電気的な接続状態に実質的な影響を及ぼさない、あるいはそれらの結合により奏される機能や効果を損なわせない、その他の部材を介して間接的に接続される場合も含む。

【0022】

図2は、実施の形態に係る発振回路2の構成を示す回路図である。発振回路2は、基準クロック信号CKREFを受け、出力クロック信号CKOUTを生成する。発振回路2は、位相比較器10、ループフィルタ12、VCO14、プログラマブル分周器18、制御部20を備える。

【0023】

プログラマブル分周器18は、分周比が少なくとも2値で切りかえ可能に構成される。本実施の形態では、分周比は、M1、M2の2値で切りかえられるものとする。プログラマブル分周器18は、周波数fOUTの出力クロック信号CKOUTを、分周比M1、M2のうちの設定された値で分周し、周波数fDIVの分周クロック信号CKDIVを生成する。つまり、分周比がM1のときfDIV=fOUT/M1、分周比がM2のときfDIV=fOUT/M2となる。位相比較器10は、基準クロック信号CKOUTと分周クロック信号CKDIVの位相差に応じた位相差信号S1を生成する。ループフィルタ12は、位相差信号S1を平滑化する。

【0024】

VCO14は、ループフィルタ12により平滑化された位相差信号(制御電圧ともいう)S2に応じた周波数で発振し、出力クロック信号CKOUTを生成する。

【0025】

制御部20は、プログラマブル分周器18の分周比を、時分割的に切りかえ、それにより出力クロック信号CKOUTのスペクトルを拡散させる。制御部20は、後述のように、第1の制御方法、または第2の制御方法によって、プログラマブル分周器18の分周比を切りかえる。

【0026】

以上が発振回路2の構成である。続いてその動作を説明する。

【0027】

図3(a)、(b)はそれぞれ、第1、第2の制御方法の動作波形図である。上段はプログラマブル分周器18に設定される分周比Mを、下段は、VCO14に入力される制御電圧S2を示す。図4(a)、(b)はそれぞれ、第1、第2の制御方法における発振回路2の消費電流のスペクトルの実測値を示す図である。

【0028】

はじめに、図3(a)、図4(a)を参照して、第1の制御方法について説明する。第1の制御方法では、図3(a)に示すように、分周比をある値に設定して発振回路2がロックした後に、分周比を別の値に切りかえる動作を繰り返す。すなわち、発振回路2は、ロック、アンロック状態を繰り返しており、制御部20がプログラマブル分周器16の分周比Mを切りかえる周期TSは、発振回路2のロック時間TLと実質的に同程度か、それよりも長くなっている。

【0029】

第1の制御方法では、VCO14に対する制御電圧S2は、2つの分周比M1、M2に応じた2つの電圧V1、V2の間で遷移する。そしてその電圧波形は、ループフィルタ12の時定数に応じた波形となる。

【0030】

第1の制御方法によれば、VCO14に対する制御電圧S2を時間的に変動させることができるため、図4(a)に示すように、スペクトルを拡散させることができる。

【0031】

(第2の制御方法)

多くの用途において、第1の制御方法でも十分な特性が得られるが、より好適にスペクトルを拡散させるためには、第2の制御方法を有効である。

【0032】

第1の制御方法では、発振回路2がロック、アンロックを繰り返すものであった。これに対して第2の制御方法では、制御部20は、発振回路がロックしないように、第1の制御方法よりも短い周期でプログラマブル分周器16の分周比Mを切りかえる。言い換えれば、制御部20がプログラマブル分周器16の分周比Mを切りかえる周期TSは、発振回路2のロック時間TLより短くなっている。別の観点から見ると、制御部20がプログラマブル分周器16の分周比Mを切りかえる周期TSは、ループフィルタ12の時定数より短くなっている。

【0033】

第2の制御方法によれば、第1の制御方法と同様に、VCO14の入力電圧S2を時間的に変化させることができ、スペクトルを拡散させることができる。

【0034】

また第1の制御方法では、発振回路2がロックする際の制御電圧S2の波形歪みによって、スペクトルに不要なピークが発生する。これに対して第2の制御方法では、発振回路2をロックしない状態で動作させることにより、第1の制御方法に比べて、スペクトルのピークを抑制できる。

【0035】

第2の制御方法において、制御部20は、VCO12に対する制御電圧S2が線形的に変化するような周期TSにて、プログラマブル分周器16の分周比Mを切りかえるとよい。ループフィルタ12をCRフィルタで構成する場合、制御電圧S2は図3(a)に示すように指数関数的に変化するところ、分周比Mの切りかえ直後の制御電圧S2は、線形近似できる。すなわち、分周比Mの切りかえ周期TSをCR時定数よりも十分に短く設定することにより、制御電圧S2は、図3(b)に示すように直線的に変化し、三角波に近くなる。これにより、第1の制御方法よりもさらにスペクトルのピークを抑制することができる。

【0036】

以上が発振回路2の動作である。続いて、発振回路2の好適な用途を説明する。

図5は、図2の発振回路2を備える電子機器1の構成を示すブロック図である。

電子機器1は、スピーカSPK、マイクMIC、発振回路2、フロントエンドIC(Integrated Circuit)4およびDSP(Digital Signal Processor)6を備える。

【0037】

電子機器1は、たとえば携帯電話端末やデジタルカメラ、オーディオプレイヤをはじめとするオーディオ再生、録音機能を備えるデバイスである。

【0038】

マイクMICは、入力された音響信号を、アナログの電気信号(アナログオーディオ信号)S10に変換する。フロントエンドIC4は、アナログオーディオ信号S10を受け、A/Dコンバータ42によってデジタルオーディオ信号S12に変換する。インタフェース回路44は、デジタルオーディオ信号S14を、バス5を介してDSP6に送信する。

【0039】

また、フロントエンドIC4のインタフェース回路44は、DSP6により再生されたデジタルオーディオ信号S22を受信する。D/Aコンバータ46は、受信したデジタルオーディオ信号S24をアナログオーディオ信号S26に変換する。アナログオーディオ信号S26は、図示しないアンプ等を介して、スピーカSPKへと出力される。

【0040】

DSP6は、デジタルオーディオ信号の符号化、復号化を行うCODEC(Code-DECode)−ICであり、録音機能と再生機能を備える。

DSP6のインタフェース回路62は、フロントエンドIC4からのデジタルオーディオ信号S14を受ける。CODEC回路64は、フロントエンドIC4から送信されたデジタルオーディオ信号S16(S14)を受け、それを所定のフォーマットに圧縮・符号化し、図示しないメモリへ格納する(録音機能)。

【0041】

また、CODEC回路64は、図示しないメモリに格納されたデジタルオーディオ信号を読み出し、読み出されたデータを復号化し、デジタルオーディオ信号S20に変換する。インタフェース回路62は、デジタルオーディオ信号S20を、バス5を介してフロントエンドIC4に送信する(再生機能)。

【0042】

ここで、フロントエンドIC4のA/Dコンバータ42およびD/Aコンバータ46に供給されるクロック信号CK1は、高音質な録音、再生のために、低ジッタであることが要求される。

【0043】

また、フロントエンドIC4のインタフェース回路44およびDSP6のインタフェース回路62に供給されるクロック信号CK2a、CK2bは、互いに同期がとれていることが要求される。

【0044】

一方、CODEC回路64において行われる符号化、復号化処理や、イコライジング処理、フィルタリング処理をはじめとするその他のデジタル演算処理は、他の回路との独立性が高く、したがって、それに供給されるクロック信号CK3には、ある程度のジッタが許容される。実施の形態に係る発振回路2は、CODEC回路64に対して、クロック信号CK3(CKOUT)を供給する用途に好適に利用することができる。

【0045】

なお、発振回路2は、DSP6の外部に設けられてもよいし、DSP6に内蔵されてもよい。また、フロントエンドIC4のA/Dコンバータ42、D/Aコンバータ46は、DSP6に内蔵されてもよい。この場合、インタフェース回路44、インタフェース回路62は不要である。この場合であっても、CODEC回路64のクロック信号CK2には、低ジッタ性は要求されないため、発振回路2が生成するクロック信号CKOUTを利用できる。

【0046】

実施の形態にもとづき、具体的な用語を用いて本発明を説明したが、実施の形態は、本発明の原理、応用を示しているにすぎず、実施の形態には、請求の範囲に規定された本発明の思想を逸脱しない範囲において、多くの変形例や配置の変更が認められる。

【符号の説明】

【0047】

1…電子機器、2…発振回路、10…位相比較器、12…ループフィルタ、14…VCO、16…分周器、18…プログラマブル分周器、20…制御部、30…変調器、30a…変調信号生成部、30b…重畳回路。

【特許請求の範囲】

【請求項1】

基準クロック信号を受け、出力クロック信号を生成する発振回路であって、

分周比が少なくとも2値で切りかえ可能に構成され、前記出力クロック信号を設定された分周比で分周し、分周クロック信号を生成するプログラマブル分周器と、

前記基準クロック信号と前記分周クロック信号の位相差に応じた位相差信号を生成する位相比較器と、

前記位相差信号を平滑化するループフィルタと、

前記ループフィルタから出力される前記位相差信号に応じた周波数で発振し、前記出力クロック信号を生成するVCO(電圧制御発振器)と、

前記プログラマブル分周器の分周比を、時分割的に切りかえることにより前記出力クロック信号のスペクトルを拡散させる制御部と、

を備えることを特徴とする発振回路。

【請求項2】

前記制御部は、前記発振回路がロックしないように、前記プログラマブル分周器の分周比を切りかえることを特徴とする請求項1に記載の発振回路。

【請求項3】

前記制御部が前記プログラマブル分周器の分周比を切りかえる周期は、前記発振回路のロック時間より短いことを特徴とする請求項1または2に記載の発振回路。

【請求項4】

前記制御部が前記プログラマブル分周器の分周比を切りかえる周期は、前記ループフィルタの時定数より短いことを特徴とする請求項1または2に記載の発振回路。

【請求項5】

前記制御部は、前記VCOの入力電圧が線形的に変化するように、前記プログラマブル分周器の分周比を切りかえることを特徴とする請求項1から4のいずれかに記載の発振回路。

【請求項6】

請求項1から5のいずれかに記載の発振回路と、

前記発振回路が生成する出力クロック信号と同期して動作するプロセッサと、

を備えることを特徴とする電子機器。

【請求項1】

基準クロック信号を受け、出力クロック信号を生成する発振回路であって、

分周比が少なくとも2値で切りかえ可能に構成され、前記出力クロック信号を設定された分周比で分周し、分周クロック信号を生成するプログラマブル分周器と、

前記基準クロック信号と前記分周クロック信号の位相差に応じた位相差信号を生成する位相比較器と、

前記位相差信号を平滑化するループフィルタと、

前記ループフィルタから出力される前記位相差信号に応じた周波数で発振し、前記出力クロック信号を生成するVCO(電圧制御発振器)と、

前記プログラマブル分周器の分周比を、時分割的に切りかえることにより前記出力クロック信号のスペクトルを拡散させる制御部と、

を備えることを特徴とする発振回路。

【請求項2】

前記制御部は、前記発振回路がロックしないように、前記プログラマブル分周器の分周比を切りかえることを特徴とする請求項1に記載の発振回路。

【請求項3】

前記制御部が前記プログラマブル分周器の分周比を切りかえる周期は、前記発振回路のロック時間より短いことを特徴とする請求項1または2に記載の発振回路。

【請求項4】

前記制御部が前記プログラマブル分周器の分周比を切りかえる周期は、前記ループフィルタの時定数より短いことを特徴とする請求項1または2に記載の発振回路。

【請求項5】

前記制御部は、前記VCOの入力電圧が線形的に変化するように、前記プログラマブル分周器の分周比を切りかえることを特徴とする請求項1から4のいずれかに記載の発振回路。

【請求項6】

請求項1から5のいずれかに記載の発振回路と、

前記発振回路が生成する出力クロック信号と同期して動作するプロセッサと、

を備えることを特徴とする電子機器。

【図1】

【図2】

【図3】

【図4】

【図5】

【図2】

【図3】

【図4】

【図5】

【公開番号】特開2013−42244(P2013−42244A)

【公開日】平成25年2月28日(2013.2.28)

【国際特許分類】

【出願番号】特願2011−176412(P2011−176412)

【出願日】平成23年8月11日(2011.8.11)

【出願人】(000116024)ローム株式会社 (3,539)

【Fターム(参考)】

【公開日】平成25年2月28日(2013.2.28)

【国際特許分類】

【出願日】平成23年8月11日(2011.8.11)

【出願人】(000116024)ローム株式会社 (3,539)

【Fターム(参考)】

[ Back to top ]