発振回路および圧電振動デバイス

【課題】部品点数を増やさず、また、電力を上げずに、複数の周波数を切り替え制御する。

【解決手段】発振回路1は、2つの水晶振動子X1,X2を接続させて2つの周波数に対応するものであり、増幅素子である発振用トランジスタQと、発振用トランジスタQに接続された容量部とが設けられている。容量部には、容量を可変させる可変容量素子であるバリキャップダイオードC12が含まれ、バリキャップダイオードC12の容量に基づいて、発振させる水晶振動子X1,X2を切替制御する。

【解決手段】発振回路1は、2つの水晶振動子X1,X2を接続させて2つの周波数に対応するものであり、増幅素子である発振用トランジスタQと、発振用トランジスタQに接続された容量部とが設けられている。容量部には、容量を可変させる可変容量素子であるバリキャップダイオードC12が含まれ、バリキャップダイオードC12の容量に基づいて、発振させる水晶振動子X1,X2を切替制御する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、発振回路および圧電振動デバイスに関する。

【背景技術】

【0002】

従来の圧電振動デバイスとして、1つの周波数に対応したものがあるが、現在、複数の周波数に対応したものが求められ、2つの周波数に対応したものがある(特許文献1参照)。

【0003】

この特許文献1に記載の水晶発振器は、2つの発振回路を用いて、それぞれの発振回路に、それぞれ異なる周波数に対応した水晶振動子が接続されている。そして、この水晶発振器では、外部からの選択信号により2つの発振回路のいずれかを選択する選択部が設けられ、選択部により選択した発振回路により所望の周波数出力を行う。

【0004】

この特許文献1の水晶発振器では、2つの周波数を選択して周波数出力を行うために、2つの周波数それぞれに対応した2つの発振回路が必要となり、1つの周波数に対応した水晶発振器に比べて、対応させる周波数の数だけ水晶発振器や発振回路の部品点数が増え、さらに、使用する発振回路を切り替える切り替え部が別途設けられている。

【0005】

また、別の従来の圧電振動デバイスとして、1つの発振回路にて2つの周波数を選択して周波数出力を行う水晶発振器がある(特許文献2参照)。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開2005−6130号公報

【特許文献2】特開2002−359521号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

しかしながら、特許文献2の水晶発振器では、2つの水晶振動子を切替するためにスイッチングダイオードが発振回路とは別個に設けられている。この水晶発振器では、2つの水晶振動子を切替するためにスイッチングダイオードに順方向電流を流す必要がある。そのため、この水晶発振器では、2つの水晶振動子を切替するために、発振回路の駆動電流とは別に大電流を必要とし、消費電力が大きくなるという問題点がある。

【0008】

そこで、上記課題を解決するために、本発明は、部品点数を増やさずに、また、電力(消費電力)を上げずに、複数の周波数を切り替え制御する発振回路および圧電振動デバイスを提供することを目的とする。

【課題を解決するための手段】

【0009】

上記の目的を達成するため、本発明にかかる発振回路は、複数の圧電振動子を接続させて複数の周波数に対応する1つの発振回路であって、増幅素子と、前記増幅素子に接続された容量部とが設けられ、前記容量部には、容量を可変させる可変容量素子が含まれ、前記可変容量素子の容量に基づいて、発振させる圧電振動子を切替制御することを特徴とする。なお、前記増幅素子として、バイポーラトランジスタやCMOSインバータが好適である。

【0010】

本発明によれば、部品点数を増やさずに、また、電力を上げずに、複数の周波数を切り替え制御することが可能となる。

【0011】

具体的には、本発明によれば、複数の周波数を選択して周波数出力を行うために複数の発振回路を必要とせずに、1つの発振回路により複数の周波数を選択して周波数出力を行うことが可能となる。その結果、本発明は、複数の周波数に対応させた発振回路(圧電振動デバイス)は、1つの周波数に対応した発振回路(圧電振動デバイス)に比べて、同等の部品点数で発振回路(圧電振動デバイス)を構成することが可能となる。

【0012】

また、本発明では、発振させる圧電振動子を前記可変容量素子を用いて切替制御するので、ダイオード電流は逆方向のみであり、その結果、消費電力が極めて小さい。そのため、本発明によれば、上記の特許文献2の水晶発振器とは異なり、2つの発振回路を切替するスイッチングダイオードを別途設けることはなく、大電力を必要しない。

【0013】

上記の目的を達成するため、本発明にかかる圧電振動デバイスは、本発明にかかる発振回路に、複数の圧電振動子が接続され、前記複数の圧電振動子のうち発振させる圧電振動子の周波数に対応させて、前記可変容量素子の容量が設定され、前記可変容量素子の容量は、発振させる圧電振動子の周波数が、周波数の増加に伴って前記発振回路の負性抵抗の絶対値が小さくなる周波数帯域内にあり、かつ、他の容量よりも前記発振回路の負性抵抗の絶対値が大きい値であるように設定されることを特徴とする。

【0014】

本発明によれば、本発明の発振回路を備えているので、本発明の発振回路と同様の効果を有する。

【0015】

前記構成において、前記複数の圧電振動子が前記発振回路に並列接続され、前記圧電振動子の並列容量(C0)と、前記発振回路の負荷容量(CL)と、の関係が、C0<CLであってもよい。また、前記構成において、前記2個の圧電振動子が前記発振回路に並列接続され、前記2個の圧電振動子のうち、前記並列容量(C0)の値が大きい方を並列容量(C01)とし、前記並列容量(C0)の値が小さい方を並列容量(C02)とした時、前記並列容量(C01)と前記並列容量(C02)と前記発振回路の負荷容量(CL)との関係が、C012/C02<CLであってもよい。

【0016】

この場合、前記圧電振動子の負荷時等価抵抗が小さくなり、その結果、発振余裕度を大きくすることが可能となる。

【0017】

前記構成において、前記2個の圧電振動子が前記発振回路に直列接続され、前記2個の圧電振動子のうち、前記並列容量(C0)の値が大きい方を並列容量(C01)とし、前記並列容量(C0)の値が小さい方を並列容量(C02)とした時、前記並列容量(C01)と前記並列容量(C02)と前記発振回路の負荷容量(CL)との関係が、C022/C01>CLであってもよい。

【0018】

この場合、前記圧電振動子の負荷時等価抵抗が小さくなり、その結果、発振余裕度を大きくすることが可能となる。

【0019】

前記構成において、前記複数の圧電振動子に、電圧制御回路が直接接続されてもよい。

【0020】

この場合、電圧制御機能による微小な周波数変動を正確に行うことが可能となる。その結果、前記可変容量素子の容量に基づいて使用する圧電振動子を切替制御しながら、前記電圧制御回路により連続した周波数範囲の調整がさらに可能となり、周波数の微調整や、周波数変調や、PLL制御を行うことが可能となる。

【発明の効果】

【0021】

本発明にかかる発振回路および圧電振動デバイスによれば、部品点数を増やさずに、また、電力を上げずに、複数の周波数を切り替え制御することが可能となる。

【図面の簡単な説明】

【0022】

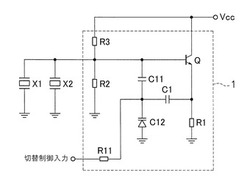

【図1】図1は、実施の形態1にかかる水晶発振器の概略回路図である。

【図2】図2は、周波数に対する負性抵抗の関係を示したグラフ図である。

【図3】図3は、実施の形態2にかかる水晶発振器の概略回路図である。

【図4】図4は、実施の形態3にかかる水晶発振器の概略回路図である。

【図5】図5は、実施の形態4にかかる水晶発振器の概略回路図である。

【図6】図6は、実施の形態5にかかる水晶発振器の概略回路図である。

【図7】図7は、実施の形態6にかかる水晶発振器の概略回路図である。

【図8】図8は、実施の形態7にかかる、発振回路に発振用トランジスタを備えた水晶発振器の概略回路図である。

【図9】図9は、実施の形態7にかかる、発振回路にCMOSインバータを備えた水晶発振器の概略回路図である。

【図10】図10は、実施の形態8にかかる、発振回路に発振用トランジスタを備えた水晶発振器の概略回路図である。

【図11】図11は、実施の形態8にかかる、発振回路にCMOSインバータを備えた水晶発振器の概略回路図である。

【発明を実施するための形態】

【0023】

以下、本発明の実施の形態について図面を参照して説明する。なお、以下に示す実施の形態では、圧電振動子として水晶振動子に本発明を適用し、圧電振動デバイスとして水晶発振器を本発明に適用した場合を示す。

【0024】

[実施の形態1]

本実施の形態1にかかる水晶発振器(図示省略)では、図1に示すように、発振回路1に、2つの水晶振動子X1,X2が並列接続され、2つの水晶振動子X1,X2を切替制御して、水晶振動子X1,X2のいずれか一方により周波数出力を行う。

【0025】

本実施の形態1で用いる2つの水晶振動子X1,X2は、約1.5倍以上の周波数の差を有する。例えば、水晶振動子X1の周波数が約100MHzであり、水晶振動子X2の周波数が約150MHzであるなど、水晶振動子X1の周波数に対して水晶振動子X2の周波数が約50%以上高い。

【0026】

発振回路1には、増幅素子である発振用トランジスタQ(バイポーラトランジスタ)と、発振用トランジスタQに接続された容量部(符号省略)と、バイアス抵抗回路などで用いる抵抗部(符号省略)と、が設けられている。このうち、容量部には、容量を形成するコンデンサC1,C11や、容量を可変させる可変容量素子であるバリキャップダイオードC12が含まれる。

【0027】

次に、発振回路1を詳説すると、図1に示すように、発振用トランジスタQのベースにコンデンサC11が接続されるとともに、抵抗R2と抵抗R3とからなるバイアス抵抗回路が接続されている。

【0028】

また、発振用トランジスタQのコレクタは、電源電圧Vccに接続されている。

【0029】

また、発振用トランジスタQのエミッタ・接地ライン間に抵抗R1が直列接続されている。また、発振用トランジスタQに、コンデンサC1が接続され、コンデンサC1がコンデンサC11とバリキャップダイオードC12(カソード端子)とに接続され、さらに抵抗R11を介して切替制御入力に接続されている。なお、バリキャップダイオードC12のアノード端子は接地されている。

【0030】

上記の概略構成からなる発振回路1では、切替制御入力から信号を入力し、この入力信号によりバリキャップダイオードC12に制御電圧を印加させて、発振回路1の負性抵抗を変化させる。そして、バリキャップダイオードC12の可変容量に基づいて変化させた負性抵抗の値により、発振させる水晶振動子X1,X2を切替制御する。なお、この時、発振させない水晶振動子を並列容量(C0)と見なすことができる。この並列容量(C0)に関して、さらに水晶振動子X1,X2を分別して水晶振動子X1の並列容量を並列容量(C01)とし、水晶振動子X2の並列容量を並列容量(C02)とすると、並列容量(C01)>並列容量(C02)の関係からなる。

【0031】

上記の発振させる水晶振動子X1,X2の切替制御に関して、水晶振動子X1,X2のうち発振させる方の周波数に対応させて、バリキャップダイオードC12の容量が設定される。ここでいうバリキャップダイオードC12の容量は、発振させる水晶振動子X1(X2)の周波数が、周波数の増加に伴って負性抵抗が大きくなる(負性抵抗の絶対値が小さくなる)周波数帯域内にあり、かつ、他の容量よりも負性抵抗が低い値(負性抵抗の絶対値が大きい値)であるように設定される。

【0032】

次に、バリキャップダイオードC12の容量可変について図2を用いて説明する。なお、図2には、発振回路1における容量部(本実施の形態1ではバリキャップダイオードC12)の容量による負性抵抗の変化を示す。

【0033】

バリキャップダイオードC12の容量は、複数の値に可変設定でき、本実施の形態1では、図2に示すように、バリキャップダイオードC12は、少なくとも容量A,Bに可変設定される。図2に示すように、2つの容量A,Bは互いに容量が異なり、容量Aが容量Bよりも小さい。

【0034】

図2を参考にして、発振させる水晶振動子を水晶振動子X1とする場合、バリキャップダイオードC12の容量が、発振させる水晶振動子X1の周波数が、周波数の増加に伴って負性抵抗が大きくなる(負性抵抗の絶対値が小さくなる)周波数帯域内にあり、かつ、他の容量(この場合、容量A)よりも負性抵抗が低い値(負性抵抗の絶対値が大きい値)となる容量Bに設定される。すなわち、水晶振動子X1は、バリキャップダイオードC12の容量を容量Bとした時に発振し、この時、水晶振動子X2は、発振しない。

【0035】

また、発振させる水晶振動子を水晶振動子X2とする場合、バリキャップダイオードC12の容量が、発振させる水晶振動子X2の周波数が、周波数の増加に伴って負性抵抗が大きくなる(負性抵抗の絶対値が小さくなる)周波数帯域内にあり、かつ、他の容量(この場合、容量B)よりも負性抵抗が低い値(負性抵抗の絶対値が大きい値)となる容量Aに設定される。すなわち、水晶振動子X2は、バリキャップダイオードC12の容量を容量Aとした時に発振し、この時、水晶振動子X1は、発振しない。

【0036】

本実施の形態1にかかる発振回路1や、発振回路1を備えた水晶発振器では、上記のようなバリキャップダイオードC12の容量可変の特性を用いて、2つの水晶振動子X1,X2を切替制御し、水晶振動子X1,X2のいずれか一方により周波数出力を行う。

【0037】

このように、本実施の形態1にかかる発振回路1や、発振回路1を備えた水晶発振器によれば、2つの水晶振動子X1,X2を接続させて2つの周波数に対応する1つの発振回路1であって、発振用トランジスタQと、発振用トランジスタQに接続された容量部とが設けられ、容量部には、容量を可変させるバリキャップダイオードC12が含まれ、バリキャップダイオードC12の容量に基づいて、発振させる水晶振動子X1,X2を切替制御するので、発振回路1や、発振回路1を備えた水晶発振器の部品点数を増やさずに、また、発振回路1や、発振回路1を備えた水晶発振器の電力を上げずに、2つの周波数を切り替え制御することができる。

【0038】

具体的には、本実施の形態1によれば、2つの周波数を選択して周波数出力を行うために複数の発振回路を必要とせずに、1つの発振回路1により2つの周波数から1つを選択して周波数出力を行うことができる。その結果、2つの周波数に対応させた発振回路1であっても、1つの周波数に対応した水晶発振器に比べて、同等の部品点数で発振回路1を構成することができる。

【0039】

また、本実施の形態1によれば、上記の特許文献1の水晶発振器とは異なり、2つの発振回路を選択する選択部を別途設けないので、選択部を動作させるための電力を必要しない。

【0040】

また、本実施の形態1では、複数の水晶振動子が並列接続され、複数の水晶振動子の並列容量(C0)と、発振回路1の負荷容量(CL)と、の関係が、C0<CLとされている。さらに詳説すると、2つの水晶振動子X1,X2は、並列接続され、水晶振動子X1の並列容量(C01)と、水晶振動子X2の並列容量(C02)と、発振回路1の負荷容量(CL)との関係が、C012/C02<CLとされている。そのため、水晶振動子X1,X2を直列に接続する形態と比較して、負荷時等価抵抗が小さくなり、発振余裕度を大きくすることができる。

【0041】

なお、本実施の形態1では、2つの水晶振動子X1,X2を用いているが、これに限定されるものではなく、出力する周波数が異なる他の水晶振動子であれば、追加してもよく、3つ以上の水晶振動子を用いてもよい。3つ以上の水晶振動子を用いた場合であっても、複数の水晶振動子の並列容量(C0)と発振回路1の負荷容量(CL)との関係(C0<CL)が成り立つ。

【0042】

なお、本実施の形態1にかかる発振回路1では、発振用トランジスタQと、コンデンサC1,C11と、バリキャップダイオードC12と、抵抗R1,R2,R3,R11とを用いているが、これに限定されるものではなく、以下の実施の形態にかかる発振回路1であってもよい。

【0043】

[実施の形態2]

本実施の形態2にかかる発振回路1、および発振回路1を備えた水晶発振器を図面を用いて説明する。なお、本実施の形態2にかかる発振回路1は、上記の実施の形態1に対して、容量部および容量部に関係する素子が異なる。そこで、本実施の形態2では、上記の実施の形態1と異なる構成について説明し、同一の構成についての説明を省略する。また、上記の実施の形態1と同一構成による作用効果及び変形例は、上記の実施の形態1と同様の作用効果及び変形例を有する。

【0044】

発振回路1の容量部には、図3に示すように、コンデンサC1,C21,C23と、バリキャップダイオードC22が含まれ、容量部に関係する素子として、抵抗R21,R22が用いられている。

【0045】

具体的には、発振用トランジスタQのベースにコンデンサC21が接続され、このコンデンサC21にバリキャップダイオードC22(アノード端子)と抵抗R21が接続され、抵抗R21が接地されている。

【0046】

また、発振用トランジスタQに、コンデンサC1が接続され、コンデンサC1がコンデンサC23とバリキャップダイオードC22(カソード端子)とに接続され、さらに抵抗R22を介して切替制御入力に接続されている。

【0047】

本実施の形態2にかかる発振回路1では、切替制御入力から信号を入力し、この入力信号によりバリキャップダイオードC22に制御電圧を印加させて、発振回路1の負性抵抗を変化させる。そして、バリキャップダイオードC22の可変容量に基づいて変化させた負性抵抗の値により、発振させる水晶振動子X1,X2を切替制御する。

【0048】

[実施の形態3]

本実施の形態3にかかる発振回路1、および発振回路1を備えた水晶発振器を図面を用いて説明する。なお、本実施の形態3にかかる発振回路1は、上記の実施の形態1に対して、容量部および容量部に関係する素子が異なる。そこで、本実施の形態3では、上記の実施の形態1と異なる構成について説明し、同一の構成についての説明を省略する。また、上記の実施の形態1と同一構成による作用効果及び変形例は、上記の実施の形態1と同様の作用効果及び変形例を有する。

【0049】

発振回路1の容量部には、図4に示すように、コンデンサC1,C31と、バリキャップダイオードC32,C33が含まれ、容量部に関係する素子として、抵抗R31,R32が用いられている。

【0050】

具体的には、発振用トランジスタQのベースにコンデンサC31が接続され、このコンデンサC31にバリキャップダイオードC32(アノード端子)と抵抗R31が接続され、抵抗R31が接地されている。

【0051】

また、発振用トランジスタQに、コンデンサC1が接続され、コンデンサC1がバリキャップダイオードC32(カソード端子)に接続され、バリキャップダイオードC33(カソード端子)に接続され、さらに抵抗R32を介して切替制御入力に接続されている。なお、バリキャップダイオードC33のアノード端子は接地されている。

【0052】

本実施の形態3にかかる発振回路1では、切替制御入力から信号を入力し、この入力信号によりバリキャップダイオードC32,C33に制御電圧を印加させて、発振回路1の負性抵抗を変化させる。そして、バリキャップダイオードC32,C33の可変容量に基づいて変化させた負性抵抗の値により、発振させる水晶振動子X1,X2を切替制御する。

【0053】

上記の実施の形態1〜3では、増幅素子として発振用トランジスタQを用いているが、これに限定されるものではなく、以下に示すCMOSインバータを用いてもよい。

【0054】

[実施の形態4]

本実施の形態4にかかる水晶発振器(図示省略)では、図5に示すように、発振回路1に、2つの水晶振動子X1,X2が並列接続され、2つの水晶振動子X1,X2を切替制御して、水晶振動子X1,X2のいずれか一方により周波数出力を行う。

【0055】

本実施の形態4で用いる2つの水晶振動子X1,X2は、上記の実施の形態1と同様に、約1.5倍以上の周波数の差を有する。例えば、水晶振動子X1の周波数が約100MHzであり、水晶振動子X2の周波数が約150MHzであるなど、水晶振動子X1の周波数に対して水晶振動子X2の周波数が約50%以上高い。

【0056】

発振回路1には、増幅素子であるCMOSインバータI(インバータ)と、CMOSインバータIに接続された容量部(符号省略)と、CMOSインバータIに並列接続されたフィードバック用抵抗R4(以下、単に抵抗R4ともいう)とが設けられている。このうち、容量部には、容量を形成するコンデンサC41,C43や、容量を可変させる可変容量素子であるバリキャップダイオードC42が含まれる。

【0057】

この発振回路1を詳説すると、図5に示すように、2つの水晶振動子X1,X2と、CMOSインバータIと、フィードバック用抵抗R4とが並列接続されている。

【0058】

そして、CMOSインバータIのゲートにコンデンサC41が接続され、コンデンサC41にバリキャップダイオードC42のカソード端子が接続され、バリキャップダイオードC42のアノード端子が接地されている。また、コンデンサC41とバリキャップダイオードC42とのライン間に、抵抗R41が接続され、抵抗R41が切替制御入力に接続されている。一方、CMOSインバータIのドレインには、コンデンサC43が接続され、コンデンサC43が接地されている。

【0059】

上記の概略構成からなる発振回路1では、切替制御入力から信号を入力し、この入力信号によりバリキャップダイオードC42に制御電圧を印加させて、発振回路1の負性抵抗を変化させる。そして、バリキャップダイオードC42の可変容量に基づいて変化させた負性抵抗の値により、発振させる水晶振動子X1,X2を切替制御する。この時、発振させない水晶振動子X1,X2を並列容量(C0)とする。なお、本実施の形態4にかかる容量部(本実施の形態ではバリキャップダイオードC42)の容量による負性抵抗の変化は、図2に示す上記の実施の形態1と同様であり、ここでの説明は省略する。

【0060】

すなわち、図2に示すように、容量部の容量が小さくなるにつれて、発振可能な周波数の値が増加しており、この特性を用いて、2つの水晶振動子X1,X2を切替制御して、水晶振動子X1,X2のいずれか一方により周波数出力を行う。

【0061】

このように、本実施の形態4にかかる発振回路1や、発振回路1を備えた水晶発振器によれば、2つの水晶振動子X1,X2を接続して2つの周波数に対応した1つの発振回路1であって、CMOSインバータIと、CMOSインバータIに接続された容量部とが設けられ、容量部には、容量を可変させるバリキャップダイオードC42が含まれ、バリキャップダイオードC42の容量に基づいて、発振させる水晶振動子X1,X2を切替制御するので、発振回路1や、発振回路1を備えた水晶発振器の部品点数を増やさずに、また、発振回路1や、発振回路1を備えた水晶発振器の電力を上げずに、2つの周波数を切り替え制御することができる。

【0062】

具体的には、本実施の形態4によれば、2つの周波数から1つを選択して周波数出力を行うために複数の発振回路を必要とせずに、1つの発振回路1により2つの周波数を選択して周波数出力を行うことができる。その結果、2つの周波数に対応させた発振回路1であっても、1つの周波数に対応した水晶発振器に比べて、同等の部品点数で発振回路1を構成することができる。

【0063】

また、本実施の形態1によれば、上記の特許文献1の水晶発振器とは異なり、2つの発振回路を選択する選択部を別途設けないので、選択部を動作させるための電力を必要しない。

【0064】

また、本実施の形態4では、2つの水晶振動子X1,X2は、並列接続され、水晶振動子X1,X2の並列容量(C0)と、発振回路1の負荷容量(CL)と、の関係が、C0<CLであるので、水晶振動子X1,X2を直列に接続する形態と比較して、負荷時等価抵抗が小さくなる。その結果、発振余裕度を大きくすることができる。

【0065】

なお、本実施の形態4では、2つの水晶振動子X1,X2を用いているが、これに限定されるものではなく、出力する周波数が異なる他の水晶振動子であれば、追加してもよく、3つ以上の水晶振動子を用いてもよい。

【0066】

なお、本実施の形態4にかかる発振回路1では、CMOSインバータIと、コンデンサC41,C43と、バリキャップダイオードC42と、抵抗R41,R42とを用いているが、これに限定されるものではなく、以下の実施の形態にかかる発振回路1であってもよい。

【0067】

[実施の形態5]

本実施の形態5にかかる発振回路1、および発振回路1を備えた水晶発振器を図面を用いて説明する。なお、本実施の形態5にかかる発振回路1は、上記の実施の形態4に対して、容量部および容量部に関係する素子が異なる。そこで、本実施の形態5では、上記の実施の形態4と異なる構成について説明し、同一の構成についての説明を省略する。また、上記の実施の形態4と同一構成による作用効果及び変形例は、上記の実施の形態4と同様の作用効果及び変形例を有する。

【0068】

発振回路1の容量部には、図6に示すように、コンデンサC51,C52と、バリキャップダイオードC53が含まれ、容量部に関係する素子として、抵抗R51が用いられている。

【0069】

具体的には、CMOSインバータIのゲートにコンデンサC51が接続され、コンデンサC51が接地されている。一方、CMOSインバータIのドレインに、コンデンサC52が接続され、コンデンサC52にバリキャップダイオードC53のカソード端子が接続され、バリキャップダイオードC53のアノード端子が接地されている。また、コンデンサC52とバリキャップダイオードC53とのライン間に、抵抗R51が接続され、抵抗R51が切替制御入力に接続されている。

【0070】

本実施の形態5にかかる発振回路1では、切替制御入力から信号を入力し、この入力信号によりバリキャップダイオードC53に制御電圧を印加させて、発振回路1の負性抵抗を変化させる。そして、バリキャップダイオードC53の可変容量に基づいて変化させた負性抵抗の値により、発振させる水晶振動子X1,X2を切替制御する。

【0071】

[実施の形態6]

本実施の形態6にかかる発振回路1、および発振回路1を備えた水晶発振器を図面を用いて説明する。なお、本実施の形態6にかかる発振回路1は、上記の実施の形態4に対して、容量部および容量部に関係する素子が異なる。そこで、本実施の形態6では、上記の実施の形態4と異なる構成について説明し、同一の構成についての説明を省略する。また、上記の実施の形態4と同一構成による作用効果及び変形例は、上記の実施の形態4と同様の作用効果及び変形例を有する。

【0072】

発振回路1の容量部には、図7に示すように、コンデンサC61,C63と、バリキャップダイオードC62,C64が含まれ、容量部に関係する素子として、抵抗R61,R62が用いられている。

【0073】

具体的には、CMOSインバータIのゲートにコンデンサC61が接続され、コンデンサC61にバリキャップダイオードC62のカソード端子が接続され、バリキャップダイオードC62のアノード端子が接地されている。また、コンデンサC61とバリキャップダイオードC62とのライン間に、抵抗R61が接続され、抵抗R61が切替制御入力に接続されている。

【0074】

一方、CMOSインバータIのドレインに、コンデンサC63が接続され、コンデンサC63にバリキャップダイオードC64のカソード端子が接続され、バリキャップダイオードC64のアノード端子が接地されている。また、コンデンサC63とバリキャップダイオードC64とのライン間に、抵抗R62が接続され、抵抗R62が切替制御入力に接続されている。

【0075】

本実施の形態6にかかる発振回路1では、切替制御入力から信号を入力し、この入力信号によりバリキャップダイオードC62,C64に制御電圧を印加させて、発振回路1の負性抵抗を変化させる。そして、バリキャップダイオードC62,C64の可変容量に基づいて変化させた負性抵抗の値により、発振させる水晶振動子X1,X2を切替制御する。

【0076】

なお、上記した実施の形態1〜6では、水晶振動子X1,X2を並列に接続しているが、これに限定されるものではなく、図8,9に示すように、水晶振動子X1,X2を直列接続してもよい(以下の実施の形態7参照)。

【0077】

[実施の形態7]

本実施の形態7にかかる発振回路1、および発振回路1を備えた水晶発振器を図面を用いて説明する。なお、本実施の形態7にかかる発振回路1は、上記の実施の形態1〜6に対して、2つの水晶振動子X1,X2の接続関係が異なる。そこで、本実施の形態7では、上記の実施の形態1〜6と異なる構成について説明し、同一の構成についての説明を省略する。また、上記の実施の形態1〜6と同一構成による作用効果及び変形例は、上記の実施の形態1〜6と同様の作用効果及び変形例を有する。

【0078】

本実施の形態7にかかる水晶発振器では、図8,9に示すように、2つの水晶振動子X1,X2は、直列接続され、水晶振動子X1の並列容量(C01)と、水晶振動子X2の並列容量(C02)と、発振回路1の負荷容量(CL)との関係が、C022/C01>CLとされている。そのため、水晶振動子X1,X2を並列に接続する形態と比較して、負荷時等価抵抗が小さくなり、発振余裕度を大きくすることができる。

【0079】

なお、本実施の形態7では、2つの水晶振動子X1,X2を用いているが、これに限定されるものではなく、出力する周波数が異なる他の水晶振動子であれば、追加してもよく、3つ以上の水晶振動子を用いてもよい。3つ以上の水晶振動子を用いた場合であっても、複数の水晶振動子の並列容量(C0)と発振回路1の負荷容量(CL)との関係(C0>CL)が成り立つ。

【0080】

また、上記した本実施の形態1〜7では、発振回路1に2つの水晶振動子X1,X2を接続しているが、さらに、電圧制御機能を有する制御入力(VCXO入力)を追加接続してもよく、電圧制御機能を有する制御入力(VCXO入力)を追加接続した形態を、以下に示す(以下の実施の形態8参照)。

【0081】

[実施の形態8]

本実施の形態8にかかる発振回路1、および発振回路1を備えた水晶発振器を図面を用いて説明する。なお、本実施の形態8にかかる発振回路1は、上記の実施の形態1〜7に対して、電圧制御機能を有する制御入力(VCXO入力)を追加接続したものである。そこで、本実施の形態8では、上記の実施の形態1,4を例にして電圧制御機能を有する制御入力(VCXO入力)を追加接続した形態とする。そこで、実施の形態1,4と異なる構成について説明し、同一の構成についての説明を省略する。また、上記の実施の形態1〜7と同一構成による作用効果及び変形例は、上記の実施の形態1〜7と同様の作用効果及び変形例を有する。

【0082】

本実施の形態8にかかる水晶発振器では、図10,11に示すように、2つの水晶振動子X1,X2に、電圧制御機能を有する制御入力(VCXO入力)を含む電圧制御回路が直接接続されている。

【0083】

詳説すると、発振回路1に発振用トランジスタQを備えた水晶発振器の場合、図10に示すように、電圧制御回路に、バリキャップダイオードC81と、抵抗R8と、VCXO入力が含まれている。

【0084】

この図10に示す電圧制御回路では、2つの水晶振動子X1,X2にバリキャップダイオードC81のカソード端子が接続され、バリキャップダイオードC81のアノード端子が接地されている。また、2つの水晶振動子X1,X2に抵抗R8が接続され、抵抗R8がVCXO入力に接続されている。

【0085】

また、発振回路1にCMOSインバータIを備えた水晶発振器の場合、図11に示すように、電圧制御回路に、コンデンサC91と,バリキャップダイオードC92と、抵抗R91,R92と、VCXO入力が含まれている。

【0086】

この図11に示す電圧制御回路では、2つの水晶振動子X1,X2と、発振回路1とのライン間にコンデンサC91とバリキャップダイオードC81のアノード端子とが直列接続され、コンデンサC91とバリキャップダイオードC81のアノード端子とのライン間に抵抗R92が接続され、抵抗R92が接地されている。また、バリキャップダイオードC81のカソード端子と2つの水晶振動子X1,X2とのライン間に抵抗R91を介したVCXO入力が接続されている。

【0087】

図10,11に示す水晶発振器によれば、電圧制御機能による微小な周波数変動を正確に行うことができる。その結果、2つの異なる周波数に対応させて周波数を切り替えることができるだけでなく、可変容量素子(図10ではバリキャップダイオードC81,図11ではバリキャップダイオードC92)の容量に基づいて使用する水晶振動子X1,X2を切替制御しながら、電圧制御回路により連続した周波数範囲の調整がさらにでき、周波数の微調整や、周波数変調や、PLL制御を行うことができる。

【0088】

なお、VCXO入力による周波数変動量に関して、圧電材料に水晶を用いた場合、基本周波数に対して約0.1%の周波数調整を行うことができ、圧電材料に圧電セラミックを用いた場合、基本周波数に対して約1%の周波数調整を行うことができる。

【0089】

本発明は、その精神や主旨または主要な特徴から逸脱することなく、他のいろいろな形で実施することができる。そのため、上述の実施例はあらゆる点で単なる例示にすぎず、限定的に解釈してはならない。本発明の範囲は特許請求の範囲によって示すものであって、明細書本文には、なんら拘束されない。さらに、特許請求の範囲の均等範囲に属する変形や変更は、全て本発明の範囲内のものである。

【産業上の利用可能性】

【0090】

本発明は、発振回路を備えた水晶発振器に有用である。

【符号の説明】

【0091】

1 発振回路

X1,X2 水晶振動子

Q 発振用トランジスタ

C1,C11,C21,C23,C31,C33,C41,C43,C51,C52,C61,C63,C91 コンデンサ

C12,C22,C32,C42,C51,C52,C61,C63,C91 バリキャップダイオード

R1,R2,R3,R4,R8,R11,R21,R22,R31,R32,R51,R61,R62,R91,R92 抵抗

Vcc 電源電圧

I CMOSインバータ

【技術分野】

【0001】

本発明は、発振回路および圧電振動デバイスに関する。

【背景技術】

【0002】

従来の圧電振動デバイスとして、1つの周波数に対応したものがあるが、現在、複数の周波数に対応したものが求められ、2つの周波数に対応したものがある(特許文献1参照)。

【0003】

この特許文献1に記載の水晶発振器は、2つの発振回路を用いて、それぞれの発振回路に、それぞれ異なる周波数に対応した水晶振動子が接続されている。そして、この水晶発振器では、外部からの選択信号により2つの発振回路のいずれかを選択する選択部が設けられ、選択部により選択した発振回路により所望の周波数出力を行う。

【0004】

この特許文献1の水晶発振器では、2つの周波数を選択して周波数出力を行うために、2つの周波数それぞれに対応した2つの発振回路が必要となり、1つの周波数に対応した水晶発振器に比べて、対応させる周波数の数だけ水晶発振器や発振回路の部品点数が増え、さらに、使用する発振回路を切り替える切り替え部が別途設けられている。

【0005】

また、別の従来の圧電振動デバイスとして、1つの発振回路にて2つの周波数を選択して周波数出力を行う水晶発振器がある(特許文献2参照)。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開2005−6130号公報

【特許文献2】特開2002−359521号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

しかしながら、特許文献2の水晶発振器では、2つの水晶振動子を切替するためにスイッチングダイオードが発振回路とは別個に設けられている。この水晶発振器では、2つの水晶振動子を切替するためにスイッチングダイオードに順方向電流を流す必要がある。そのため、この水晶発振器では、2つの水晶振動子を切替するために、発振回路の駆動電流とは別に大電流を必要とし、消費電力が大きくなるという問題点がある。

【0008】

そこで、上記課題を解決するために、本発明は、部品点数を増やさずに、また、電力(消費電力)を上げずに、複数の周波数を切り替え制御する発振回路および圧電振動デバイスを提供することを目的とする。

【課題を解決するための手段】

【0009】

上記の目的を達成するため、本発明にかかる発振回路は、複数の圧電振動子を接続させて複数の周波数に対応する1つの発振回路であって、増幅素子と、前記増幅素子に接続された容量部とが設けられ、前記容量部には、容量を可変させる可変容量素子が含まれ、前記可変容量素子の容量に基づいて、発振させる圧電振動子を切替制御することを特徴とする。なお、前記増幅素子として、バイポーラトランジスタやCMOSインバータが好適である。

【0010】

本発明によれば、部品点数を増やさずに、また、電力を上げずに、複数の周波数を切り替え制御することが可能となる。

【0011】

具体的には、本発明によれば、複数の周波数を選択して周波数出力を行うために複数の発振回路を必要とせずに、1つの発振回路により複数の周波数を選択して周波数出力を行うことが可能となる。その結果、本発明は、複数の周波数に対応させた発振回路(圧電振動デバイス)は、1つの周波数に対応した発振回路(圧電振動デバイス)に比べて、同等の部品点数で発振回路(圧電振動デバイス)を構成することが可能となる。

【0012】

また、本発明では、発振させる圧電振動子を前記可変容量素子を用いて切替制御するので、ダイオード電流は逆方向のみであり、その結果、消費電力が極めて小さい。そのため、本発明によれば、上記の特許文献2の水晶発振器とは異なり、2つの発振回路を切替するスイッチングダイオードを別途設けることはなく、大電力を必要しない。

【0013】

上記の目的を達成するため、本発明にかかる圧電振動デバイスは、本発明にかかる発振回路に、複数の圧電振動子が接続され、前記複数の圧電振動子のうち発振させる圧電振動子の周波数に対応させて、前記可変容量素子の容量が設定され、前記可変容量素子の容量は、発振させる圧電振動子の周波数が、周波数の増加に伴って前記発振回路の負性抵抗の絶対値が小さくなる周波数帯域内にあり、かつ、他の容量よりも前記発振回路の負性抵抗の絶対値が大きい値であるように設定されることを特徴とする。

【0014】

本発明によれば、本発明の発振回路を備えているので、本発明の発振回路と同様の効果を有する。

【0015】

前記構成において、前記複数の圧電振動子が前記発振回路に並列接続され、前記圧電振動子の並列容量(C0)と、前記発振回路の負荷容量(CL)と、の関係が、C0<CLであってもよい。また、前記構成において、前記2個の圧電振動子が前記発振回路に並列接続され、前記2個の圧電振動子のうち、前記並列容量(C0)の値が大きい方を並列容量(C01)とし、前記並列容量(C0)の値が小さい方を並列容量(C02)とした時、前記並列容量(C01)と前記並列容量(C02)と前記発振回路の負荷容量(CL)との関係が、C012/C02<CLであってもよい。

【0016】

この場合、前記圧電振動子の負荷時等価抵抗が小さくなり、その結果、発振余裕度を大きくすることが可能となる。

【0017】

前記構成において、前記2個の圧電振動子が前記発振回路に直列接続され、前記2個の圧電振動子のうち、前記並列容量(C0)の値が大きい方を並列容量(C01)とし、前記並列容量(C0)の値が小さい方を並列容量(C02)とした時、前記並列容量(C01)と前記並列容量(C02)と前記発振回路の負荷容量(CL)との関係が、C022/C01>CLであってもよい。

【0018】

この場合、前記圧電振動子の負荷時等価抵抗が小さくなり、その結果、発振余裕度を大きくすることが可能となる。

【0019】

前記構成において、前記複数の圧電振動子に、電圧制御回路が直接接続されてもよい。

【0020】

この場合、電圧制御機能による微小な周波数変動を正確に行うことが可能となる。その結果、前記可変容量素子の容量に基づいて使用する圧電振動子を切替制御しながら、前記電圧制御回路により連続した周波数範囲の調整がさらに可能となり、周波数の微調整や、周波数変調や、PLL制御を行うことが可能となる。

【発明の効果】

【0021】

本発明にかかる発振回路および圧電振動デバイスによれば、部品点数を増やさずに、また、電力を上げずに、複数の周波数を切り替え制御することが可能となる。

【図面の簡単な説明】

【0022】

【図1】図1は、実施の形態1にかかる水晶発振器の概略回路図である。

【図2】図2は、周波数に対する負性抵抗の関係を示したグラフ図である。

【図3】図3は、実施の形態2にかかる水晶発振器の概略回路図である。

【図4】図4は、実施の形態3にかかる水晶発振器の概略回路図である。

【図5】図5は、実施の形態4にかかる水晶発振器の概略回路図である。

【図6】図6は、実施の形態5にかかる水晶発振器の概略回路図である。

【図7】図7は、実施の形態6にかかる水晶発振器の概略回路図である。

【図8】図8は、実施の形態7にかかる、発振回路に発振用トランジスタを備えた水晶発振器の概略回路図である。

【図9】図9は、実施の形態7にかかる、発振回路にCMOSインバータを備えた水晶発振器の概略回路図である。

【図10】図10は、実施の形態8にかかる、発振回路に発振用トランジスタを備えた水晶発振器の概略回路図である。

【図11】図11は、実施の形態8にかかる、発振回路にCMOSインバータを備えた水晶発振器の概略回路図である。

【発明を実施するための形態】

【0023】

以下、本発明の実施の形態について図面を参照して説明する。なお、以下に示す実施の形態では、圧電振動子として水晶振動子に本発明を適用し、圧電振動デバイスとして水晶発振器を本発明に適用した場合を示す。

【0024】

[実施の形態1]

本実施の形態1にかかる水晶発振器(図示省略)では、図1に示すように、発振回路1に、2つの水晶振動子X1,X2が並列接続され、2つの水晶振動子X1,X2を切替制御して、水晶振動子X1,X2のいずれか一方により周波数出力を行う。

【0025】

本実施の形態1で用いる2つの水晶振動子X1,X2は、約1.5倍以上の周波数の差を有する。例えば、水晶振動子X1の周波数が約100MHzであり、水晶振動子X2の周波数が約150MHzであるなど、水晶振動子X1の周波数に対して水晶振動子X2の周波数が約50%以上高い。

【0026】

発振回路1には、増幅素子である発振用トランジスタQ(バイポーラトランジスタ)と、発振用トランジスタQに接続された容量部(符号省略)と、バイアス抵抗回路などで用いる抵抗部(符号省略)と、が設けられている。このうち、容量部には、容量を形成するコンデンサC1,C11や、容量を可変させる可変容量素子であるバリキャップダイオードC12が含まれる。

【0027】

次に、発振回路1を詳説すると、図1に示すように、発振用トランジスタQのベースにコンデンサC11が接続されるとともに、抵抗R2と抵抗R3とからなるバイアス抵抗回路が接続されている。

【0028】

また、発振用トランジスタQのコレクタは、電源電圧Vccに接続されている。

【0029】

また、発振用トランジスタQのエミッタ・接地ライン間に抵抗R1が直列接続されている。また、発振用トランジスタQに、コンデンサC1が接続され、コンデンサC1がコンデンサC11とバリキャップダイオードC12(カソード端子)とに接続され、さらに抵抗R11を介して切替制御入力に接続されている。なお、バリキャップダイオードC12のアノード端子は接地されている。

【0030】

上記の概略構成からなる発振回路1では、切替制御入力から信号を入力し、この入力信号によりバリキャップダイオードC12に制御電圧を印加させて、発振回路1の負性抵抗を変化させる。そして、バリキャップダイオードC12の可変容量に基づいて変化させた負性抵抗の値により、発振させる水晶振動子X1,X2を切替制御する。なお、この時、発振させない水晶振動子を並列容量(C0)と見なすことができる。この並列容量(C0)に関して、さらに水晶振動子X1,X2を分別して水晶振動子X1の並列容量を並列容量(C01)とし、水晶振動子X2の並列容量を並列容量(C02)とすると、並列容量(C01)>並列容量(C02)の関係からなる。

【0031】

上記の発振させる水晶振動子X1,X2の切替制御に関して、水晶振動子X1,X2のうち発振させる方の周波数に対応させて、バリキャップダイオードC12の容量が設定される。ここでいうバリキャップダイオードC12の容量は、発振させる水晶振動子X1(X2)の周波数が、周波数の増加に伴って負性抵抗が大きくなる(負性抵抗の絶対値が小さくなる)周波数帯域内にあり、かつ、他の容量よりも負性抵抗が低い値(負性抵抗の絶対値が大きい値)であるように設定される。

【0032】

次に、バリキャップダイオードC12の容量可変について図2を用いて説明する。なお、図2には、発振回路1における容量部(本実施の形態1ではバリキャップダイオードC12)の容量による負性抵抗の変化を示す。

【0033】

バリキャップダイオードC12の容量は、複数の値に可変設定でき、本実施の形態1では、図2に示すように、バリキャップダイオードC12は、少なくとも容量A,Bに可変設定される。図2に示すように、2つの容量A,Bは互いに容量が異なり、容量Aが容量Bよりも小さい。

【0034】

図2を参考にして、発振させる水晶振動子を水晶振動子X1とする場合、バリキャップダイオードC12の容量が、発振させる水晶振動子X1の周波数が、周波数の増加に伴って負性抵抗が大きくなる(負性抵抗の絶対値が小さくなる)周波数帯域内にあり、かつ、他の容量(この場合、容量A)よりも負性抵抗が低い値(負性抵抗の絶対値が大きい値)となる容量Bに設定される。すなわち、水晶振動子X1は、バリキャップダイオードC12の容量を容量Bとした時に発振し、この時、水晶振動子X2は、発振しない。

【0035】

また、発振させる水晶振動子を水晶振動子X2とする場合、バリキャップダイオードC12の容量が、発振させる水晶振動子X2の周波数が、周波数の増加に伴って負性抵抗が大きくなる(負性抵抗の絶対値が小さくなる)周波数帯域内にあり、かつ、他の容量(この場合、容量B)よりも負性抵抗が低い値(負性抵抗の絶対値が大きい値)となる容量Aに設定される。すなわち、水晶振動子X2は、バリキャップダイオードC12の容量を容量Aとした時に発振し、この時、水晶振動子X1は、発振しない。

【0036】

本実施の形態1にかかる発振回路1や、発振回路1を備えた水晶発振器では、上記のようなバリキャップダイオードC12の容量可変の特性を用いて、2つの水晶振動子X1,X2を切替制御し、水晶振動子X1,X2のいずれか一方により周波数出力を行う。

【0037】

このように、本実施の形態1にかかる発振回路1や、発振回路1を備えた水晶発振器によれば、2つの水晶振動子X1,X2を接続させて2つの周波数に対応する1つの発振回路1であって、発振用トランジスタQと、発振用トランジスタQに接続された容量部とが設けられ、容量部には、容量を可変させるバリキャップダイオードC12が含まれ、バリキャップダイオードC12の容量に基づいて、発振させる水晶振動子X1,X2を切替制御するので、発振回路1や、発振回路1を備えた水晶発振器の部品点数を増やさずに、また、発振回路1や、発振回路1を備えた水晶発振器の電力を上げずに、2つの周波数を切り替え制御することができる。

【0038】

具体的には、本実施の形態1によれば、2つの周波数を選択して周波数出力を行うために複数の発振回路を必要とせずに、1つの発振回路1により2つの周波数から1つを選択して周波数出力を行うことができる。その結果、2つの周波数に対応させた発振回路1であっても、1つの周波数に対応した水晶発振器に比べて、同等の部品点数で発振回路1を構成することができる。

【0039】

また、本実施の形態1によれば、上記の特許文献1の水晶発振器とは異なり、2つの発振回路を選択する選択部を別途設けないので、選択部を動作させるための電力を必要しない。

【0040】

また、本実施の形態1では、複数の水晶振動子が並列接続され、複数の水晶振動子の並列容量(C0)と、発振回路1の負荷容量(CL)と、の関係が、C0<CLとされている。さらに詳説すると、2つの水晶振動子X1,X2は、並列接続され、水晶振動子X1の並列容量(C01)と、水晶振動子X2の並列容量(C02)と、発振回路1の負荷容量(CL)との関係が、C012/C02<CLとされている。そのため、水晶振動子X1,X2を直列に接続する形態と比較して、負荷時等価抵抗が小さくなり、発振余裕度を大きくすることができる。

【0041】

なお、本実施の形態1では、2つの水晶振動子X1,X2を用いているが、これに限定されるものではなく、出力する周波数が異なる他の水晶振動子であれば、追加してもよく、3つ以上の水晶振動子を用いてもよい。3つ以上の水晶振動子を用いた場合であっても、複数の水晶振動子の並列容量(C0)と発振回路1の負荷容量(CL)との関係(C0<CL)が成り立つ。

【0042】

なお、本実施の形態1にかかる発振回路1では、発振用トランジスタQと、コンデンサC1,C11と、バリキャップダイオードC12と、抵抗R1,R2,R3,R11とを用いているが、これに限定されるものではなく、以下の実施の形態にかかる発振回路1であってもよい。

【0043】

[実施の形態2]

本実施の形態2にかかる発振回路1、および発振回路1を備えた水晶発振器を図面を用いて説明する。なお、本実施の形態2にかかる発振回路1は、上記の実施の形態1に対して、容量部および容量部に関係する素子が異なる。そこで、本実施の形態2では、上記の実施の形態1と異なる構成について説明し、同一の構成についての説明を省略する。また、上記の実施の形態1と同一構成による作用効果及び変形例は、上記の実施の形態1と同様の作用効果及び変形例を有する。

【0044】

発振回路1の容量部には、図3に示すように、コンデンサC1,C21,C23と、バリキャップダイオードC22が含まれ、容量部に関係する素子として、抵抗R21,R22が用いられている。

【0045】

具体的には、発振用トランジスタQのベースにコンデンサC21が接続され、このコンデンサC21にバリキャップダイオードC22(アノード端子)と抵抗R21が接続され、抵抗R21が接地されている。

【0046】

また、発振用トランジスタQに、コンデンサC1が接続され、コンデンサC1がコンデンサC23とバリキャップダイオードC22(カソード端子)とに接続され、さらに抵抗R22を介して切替制御入力に接続されている。

【0047】

本実施の形態2にかかる発振回路1では、切替制御入力から信号を入力し、この入力信号によりバリキャップダイオードC22に制御電圧を印加させて、発振回路1の負性抵抗を変化させる。そして、バリキャップダイオードC22の可変容量に基づいて変化させた負性抵抗の値により、発振させる水晶振動子X1,X2を切替制御する。

【0048】

[実施の形態3]

本実施の形態3にかかる発振回路1、および発振回路1を備えた水晶発振器を図面を用いて説明する。なお、本実施の形態3にかかる発振回路1は、上記の実施の形態1に対して、容量部および容量部に関係する素子が異なる。そこで、本実施の形態3では、上記の実施の形態1と異なる構成について説明し、同一の構成についての説明を省略する。また、上記の実施の形態1と同一構成による作用効果及び変形例は、上記の実施の形態1と同様の作用効果及び変形例を有する。

【0049】

発振回路1の容量部には、図4に示すように、コンデンサC1,C31と、バリキャップダイオードC32,C33が含まれ、容量部に関係する素子として、抵抗R31,R32が用いられている。

【0050】

具体的には、発振用トランジスタQのベースにコンデンサC31が接続され、このコンデンサC31にバリキャップダイオードC32(アノード端子)と抵抗R31が接続され、抵抗R31が接地されている。

【0051】

また、発振用トランジスタQに、コンデンサC1が接続され、コンデンサC1がバリキャップダイオードC32(カソード端子)に接続され、バリキャップダイオードC33(カソード端子)に接続され、さらに抵抗R32を介して切替制御入力に接続されている。なお、バリキャップダイオードC33のアノード端子は接地されている。

【0052】

本実施の形態3にかかる発振回路1では、切替制御入力から信号を入力し、この入力信号によりバリキャップダイオードC32,C33に制御電圧を印加させて、発振回路1の負性抵抗を変化させる。そして、バリキャップダイオードC32,C33の可変容量に基づいて変化させた負性抵抗の値により、発振させる水晶振動子X1,X2を切替制御する。

【0053】

上記の実施の形態1〜3では、増幅素子として発振用トランジスタQを用いているが、これに限定されるものではなく、以下に示すCMOSインバータを用いてもよい。

【0054】

[実施の形態4]

本実施の形態4にかかる水晶発振器(図示省略)では、図5に示すように、発振回路1に、2つの水晶振動子X1,X2が並列接続され、2つの水晶振動子X1,X2を切替制御して、水晶振動子X1,X2のいずれか一方により周波数出力を行う。

【0055】

本実施の形態4で用いる2つの水晶振動子X1,X2は、上記の実施の形態1と同様に、約1.5倍以上の周波数の差を有する。例えば、水晶振動子X1の周波数が約100MHzであり、水晶振動子X2の周波数が約150MHzであるなど、水晶振動子X1の周波数に対して水晶振動子X2の周波数が約50%以上高い。

【0056】

発振回路1には、増幅素子であるCMOSインバータI(インバータ)と、CMOSインバータIに接続された容量部(符号省略)と、CMOSインバータIに並列接続されたフィードバック用抵抗R4(以下、単に抵抗R4ともいう)とが設けられている。このうち、容量部には、容量を形成するコンデンサC41,C43や、容量を可変させる可変容量素子であるバリキャップダイオードC42が含まれる。

【0057】

この発振回路1を詳説すると、図5に示すように、2つの水晶振動子X1,X2と、CMOSインバータIと、フィードバック用抵抗R4とが並列接続されている。

【0058】

そして、CMOSインバータIのゲートにコンデンサC41が接続され、コンデンサC41にバリキャップダイオードC42のカソード端子が接続され、バリキャップダイオードC42のアノード端子が接地されている。また、コンデンサC41とバリキャップダイオードC42とのライン間に、抵抗R41が接続され、抵抗R41が切替制御入力に接続されている。一方、CMOSインバータIのドレインには、コンデンサC43が接続され、コンデンサC43が接地されている。

【0059】

上記の概略構成からなる発振回路1では、切替制御入力から信号を入力し、この入力信号によりバリキャップダイオードC42に制御電圧を印加させて、発振回路1の負性抵抗を変化させる。そして、バリキャップダイオードC42の可変容量に基づいて変化させた負性抵抗の値により、発振させる水晶振動子X1,X2を切替制御する。この時、発振させない水晶振動子X1,X2を並列容量(C0)とする。なお、本実施の形態4にかかる容量部(本実施の形態ではバリキャップダイオードC42)の容量による負性抵抗の変化は、図2に示す上記の実施の形態1と同様であり、ここでの説明は省略する。

【0060】

すなわち、図2に示すように、容量部の容量が小さくなるにつれて、発振可能な周波数の値が増加しており、この特性を用いて、2つの水晶振動子X1,X2を切替制御して、水晶振動子X1,X2のいずれか一方により周波数出力を行う。

【0061】

このように、本実施の形態4にかかる発振回路1や、発振回路1を備えた水晶発振器によれば、2つの水晶振動子X1,X2を接続して2つの周波数に対応した1つの発振回路1であって、CMOSインバータIと、CMOSインバータIに接続された容量部とが設けられ、容量部には、容量を可変させるバリキャップダイオードC42が含まれ、バリキャップダイオードC42の容量に基づいて、発振させる水晶振動子X1,X2を切替制御するので、発振回路1や、発振回路1を備えた水晶発振器の部品点数を増やさずに、また、発振回路1や、発振回路1を備えた水晶発振器の電力を上げずに、2つの周波数を切り替え制御することができる。

【0062】

具体的には、本実施の形態4によれば、2つの周波数から1つを選択して周波数出力を行うために複数の発振回路を必要とせずに、1つの発振回路1により2つの周波数を選択して周波数出力を行うことができる。その結果、2つの周波数に対応させた発振回路1であっても、1つの周波数に対応した水晶発振器に比べて、同等の部品点数で発振回路1を構成することができる。

【0063】

また、本実施の形態1によれば、上記の特許文献1の水晶発振器とは異なり、2つの発振回路を選択する選択部を別途設けないので、選択部を動作させるための電力を必要しない。

【0064】

また、本実施の形態4では、2つの水晶振動子X1,X2は、並列接続され、水晶振動子X1,X2の並列容量(C0)と、発振回路1の負荷容量(CL)と、の関係が、C0<CLであるので、水晶振動子X1,X2を直列に接続する形態と比較して、負荷時等価抵抗が小さくなる。その結果、発振余裕度を大きくすることができる。

【0065】

なお、本実施の形態4では、2つの水晶振動子X1,X2を用いているが、これに限定されるものではなく、出力する周波数が異なる他の水晶振動子であれば、追加してもよく、3つ以上の水晶振動子を用いてもよい。

【0066】

なお、本実施の形態4にかかる発振回路1では、CMOSインバータIと、コンデンサC41,C43と、バリキャップダイオードC42と、抵抗R41,R42とを用いているが、これに限定されるものではなく、以下の実施の形態にかかる発振回路1であってもよい。

【0067】

[実施の形態5]

本実施の形態5にかかる発振回路1、および発振回路1を備えた水晶発振器を図面を用いて説明する。なお、本実施の形態5にかかる発振回路1は、上記の実施の形態4に対して、容量部および容量部に関係する素子が異なる。そこで、本実施の形態5では、上記の実施の形態4と異なる構成について説明し、同一の構成についての説明を省略する。また、上記の実施の形態4と同一構成による作用効果及び変形例は、上記の実施の形態4と同様の作用効果及び変形例を有する。

【0068】

発振回路1の容量部には、図6に示すように、コンデンサC51,C52と、バリキャップダイオードC53が含まれ、容量部に関係する素子として、抵抗R51が用いられている。

【0069】

具体的には、CMOSインバータIのゲートにコンデンサC51が接続され、コンデンサC51が接地されている。一方、CMOSインバータIのドレインに、コンデンサC52が接続され、コンデンサC52にバリキャップダイオードC53のカソード端子が接続され、バリキャップダイオードC53のアノード端子が接地されている。また、コンデンサC52とバリキャップダイオードC53とのライン間に、抵抗R51が接続され、抵抗R51が切替制御入力に接続されている。

【0070】

本実施の形態5にかかる発振回路1では、切替制御入力から信号を入力し、この入力信号によりバリキャップダイオードC53に制御電圧を印加させて、発振回路1の負性抵抗を変化させる。そして、バリキャップダイオードC53の可変容量に基づいて変化させた負性抵抗の値により、発振させる水晶振動子X1,X2を切替制御する。

【0071】

[実施の形態6]

本実施の形態6にかかる発振回路1、および発振回路1を備えた水晶発振器を図面を用いて説明する。なお、本実施の形態6にかかる発振回路1は、上記の実施の形態4に対して、容量部および容量部に関係する素子が異なる。そこで、本実施の形態6では、上記の実施の形態4と異なる構成について説明し、同一の構成についての説明を省略する。また、上記の実施の形態4と同一構成による作用効果及び変形例は、上記の実施の形態4と同様の作用効果及び変形例を有する。

【0072】

発振回路1の容量部には、図7に示すように、コンデンサC61,C63と、バリキャップダイオードC62,C64が含まれ、容量部に関係する素子として、抵抗R61,R62が用いられている。

【0073】

具体的には、CMOSインバータIのゲートにコンデンサC61が接続され、コンデンサC61にバリキャップダイオードC62のカソード端子が接続され、バリキャップダイオードC62のアノード端子が接地されている。また、コンデンサC61とバリキャップダイオードC62とのライン間に、抵抗R61が接続され、抵抗R61が切替制御入力に接続されている。

【0074】

一方、CMOSインバータIのドレインに、コンデンサC63が接続され、コンデンサC63にバリキャップダイオードC64のカソード端子が接続され、バリキャップダイオードC64のアノード端子が接地されている。また、コンデンサC63とバリキャップダイオードC64とのライン間に、抵抗R62が接続され、抵抗R62が切替制御入力に接続されている。

【0075】

本実施の形態6にかかる発振回路1では、切替制御入力から信号を入力し、この入力信号によりバリキャップダイオードC62,C64に制御電圧を印加させて、発振回路1の負性抵抗を変化させる。そして、バリキャップダイオードC62,C64の可変容量に基づいて変化させた負性抵抗の値により、発振させる水晶振動子X1,X2を切替制御する。

【0076】

なお、上記した実施の形態1〜6では、水晶振動子X1,X2を並列に接続しているが、これに限定されるものではなく、図8,9に示すように、水晶振動子X1,X2を直列接続してもよい(以下の実施の形態7参照)。

【0077】

[実施の形態7]

本実施の形態7にかかる発振回路1、および発振回路1を備えた水晶発振器を図面を用いて説明する。なお、本実施の形態7にかかる発振回路1は、上記の実施の形態1〜6に対して、2つの水晶振動子X1,X2の接続関係が異なる。そこで、本実施の形態7では、上記の実施の形態1〜6と異なる構成について説明し、同一の構成についての説明を省略する。また、上記の実施の形態1〜6と同一構成による作用効果及び変形例は、上記の実施の形態1〜6と同様の作用効果及び変形例を有する。

【0078】

本実施の形態7にかかる水晶発振器では、図8,9に示すように、2つの水晶振動子X1,X2は、直列接続され、水晶振動子X1の並列容量(C01)と、水晶振動子X2の並列容量(C02)と、発振回路1の負荷容量(CL)との関係が、C022/C01>CLとされている。そのため、水晶振動子X1,X2を並列に接続する形態と比較して、負荷時等価抵抗が小さくなり、発振余裕度を大きくすることができる。

【0079】

なお、本実施の形態7では、2つの水晶振動子X1,X2を用いているが、これに限定されるものではなく、出力する周波数が異なる他の水晶振動子であれば、追加してもよく、3つ以上の水晶振動子を用いてもよい。3つ以上の水晶振動子を用いた場合であっても、複数の水晶振動子の並列容量(C0)と発振回路1の負荷容量(CL)との関係(C0>CL)が成り立つ。

【0080】

また、上記した本実施の形態1〜7では、発振回路1に2つの水晶振動子X1,X2を接続しているが、さらに、電圧制御機能を有する制御入力(VCXO入力)を追加接続してもよく、電圧制御機能を有する制御入力(VCXO入力)を追加接続した形態を、以下に示す(以下の実施の形態8参照)。

【0081】

[実施の形態8]

本実施の形態8にかかる発振回路1、および発振回路1を備えた水晶発振器を図面を用いて説明する。なお、本実施の形態8にかかる発振回路1は、上記の実施の形態1〜7に対して、電圧制御機能を有する制御入力(VCXO入力)を追加接続したものである。そこで、本実施の形態8では、上記の実施の形態1,4を例にして電圧制御機能を有する制御入力(VCXO入力)を追加接続した形態とする。そこで、実施の形態1,4と異なる構成について説明し、同一の構成についての説明を省略する。また、上記の実施の形態1〜7と同一構成による作用効果及び変形例は、上記の実施の形態1〜7と同様の作用効果及び変形例を有する。

【0082】

本実施の形態8にかかる水晶発振器では、図10,11に示すように、2つの水晶振動子X1,X2に、電圧制御機能を有する制御入力(VCXO入力)を含む電圧制御回路が直接接続されている。

【0083】

詳説すると、発振回路1に発振用トランジスタQを備えた水晶発振器の場合、図10に示すように、電圧制御回路に、バリキャップダイオードC81と、抵抗R8と、VCXO入力が含まれている。

【0084】

この図10に示す電圧制御回路では、2つの水晶振動子X1,X2にバリキャップダイオードC81のカソード端子が接続され、バリキャップダイオードC81のアノード端子が接地されている。また、2つの水晶振動子X1,X2に抵抗R8が接続され、抵抗R8がVCXO入力に接続されている。

【0085】

また、発振回路1にCMOSインバータIを備えた水晶発振器の場合、図11に示すように、電圧制御回路に、コンデンサC91と,バリキャップダイオードC92と、抵抗R91,R92と、VCXO入力が含まれている。

【0086】

この図11に示す電圧制御回路では、2つの水晶振動子X1,X2と、発振回路1とのライン間にコンデンサC91とバリキャップダイオードC81のアノード端子とが直列接続され、コンデンサC91とバリキャップダイオードC81のアノード端子とのライン間に抵抗R92が接続され、抵抗R92が接地されている。また、バリキャップダイオードC81のカソード端子と2つの水晶振動子X1,X2とのライン間に抵抗R91を介したVCXO入力が接続されている。

【0087】

図10,11に示す水晶発振器によれば、電圧制御機能による微小な周波数変動を正確に行うことができる。その結果、2つの異なる周波数に対応させて周波数を切り替えることができるだけでなく、可変容量素子(図10ではバリキャップダイオードC81,図11ではバリキャップダイオードC92)の容量に基づいて使用する水晶振動子X1,X2を切替制御しながら、電圧制御回路により連続した周波数範囲の調整がさらにでき、周波数の微調整や、周波数変調や、PLL制御を行うことができる。

【0088】

なお、VCXO入力による周波数変動量に関して、圧電材料に水晶を用いた場合、基本周波数に対して約0.1%の周波数調整を行うことができ、圧電材料に圧電セラミックを用いた場合、基本周波数に対して約1%の周波数調整を行うことができる。

【0089】

本発明は、その精神や主旨または主要な特徴から逸脱することなく、他のいろいろな形で実施することができる。そのため、上述の実施例はあらゆる点で単なる例示にすぎず、限定的に解釈してはならない。本発明の範囲は特許請求の範囲によって示すものであって、明細書本文には、なんら拘束されない。さらに、特許請求の範囲の均等範囲に属する変形や変更は、全て本発明の範囲内のものである。

【産業上の利用可能性】

【0090】

本発明は、発振回路を備えた水晶発振器に有用である。

【符号の説明】

【0091】

1 発振回路

X1,X2 水晶振動子

Q 発振用トランジスタ

C1,C11,C21,C23,C31,C33,C41,C43,C51,C52,C61,C63,C91 コンデンサ

C12,C22,C32,C42,C51,C52,C61,C63,C91 バリキャップダイオード

R1,R2,R3,R4,R8,R11,R21,R22,R31,R32,R51,R61,R62,R91,R92 抵抗

Vcc 電源電圧

I CMOSインバータ

【特許請求の範囲】

【請求項1】

複数の圧電振動子を接続させて複数の周波数に対応する1つの発振回路であって、

増幅素子と、前記増幅素子に接続された容量部とが設けられ、

前記容量部には、容量を可変させる可変容量素子が含まれ、

前記可変容量素子の容量に基づいて、発振させる圧電振動子を切替制御することを特徴とする発振回路。

【請求項2】

請求項1に記載の発振回路において、

前記増幅素子に、バイポーラトランジスタを用いたことを特徴とする発振回路。

【請求項3】

請求項1に記載の発振回路において、

前記増幅素子に、CMOSインバータを用いたことを特徴とする発振回路。

【請求項4】

圧電振動デバイスにおいて、

請求項1乃至3のうちいずれか1つに記載の発振回路に、複数の圧電振動子が接続され、

前記複数の圧電振動子のうち発振させる圧電振動子の周波数に対応させて、前記可変容量素子の容量が設定され、

前記可変容量素子の容量は、発振させる圧電振動子の周波数が、周波数の増加に伴って前記発振回路の負性抵抗の絶対値が小さくなる周波数帯域内にあり、かつ、他の容量よりも前記発振回路の負性抵抗の絶対値が大きい値であるように設定されることを特徴とする圧電振動デバイス。

【請求項5】

請求項4に記載の圧電振動デバイスにおいて、

前記複数の圧電振動子が前記発振回路に並列接続され、

前記圧電振動子の並列容量(C0)と、前記発振回路の負荷容量(CL)と、の関係が、C0<CLであることを特徴とする圧電振動デバイス。

【請求項6】

請求項5に記載の圧電振動デバイスにおいて、

前記2個の圧電振動子が前記発振回路に並列接続され、

前記2個の圧電振動子のうち、前記並列容量(C0)の値が大きい方を並列容量(C01)とし、前記並列容量(C0)の値が小さい方を並列容量(C02)とした時、前記並列容量(C01)と前記並列容量(C02)と前記発振回路の負荷容量(CL)との関係が、C012/C02<CLであることを特徴とする圧電振動デバイス。

【請求項7】

請求項4に記載の圧電振動デバイスにおいて、

前記2個の圧電振動子が前記発振回路に直列接続され、

前記2個の圧電振動子のうち、前記並列容量(C0)の値が大きい方を並列容量(C01)とし、前記並列容量(C0)の値が小さい方を並列容量(C02)とした時、前記並列容量(C01)と前記並列容量(C02)と前記発振回路の負荷容量(CL)との関係が、C022/C01>CLであることを特徴とする圧電振動デバイス。

【請求項8】

請求項5乃至7のうちいすれか1つに記載の圧電振動デバイスにおいて、

前記圧電振動子に、電圧制御回路が直接接続されたことを特徴とする圧電振動デバイス。

【請求項1】

複数の圧電振動子を接続させて複数の周波数に対応する1つの発振回路であって、

増幅素子と、前記増幅素子に接続された容量部とが設けられ、

前記容量部には、容量を可変させる可変容量素子が含まれ、

前記可変容量素子の容量に基づいて、発振させる圧電振動子を切替制御することを特徴とする発振回路。

【請求項2】

請求項1に記載の発振回路において、

前記増幅素子に、バイポーラトランジスタを用いたことを特徴とする発振回路。

【請求項3】

請求項1に記載の発振回路において、

前記増幅素子に、CMOSインバータを用いたことを特徴とする発振回路。

【請求項4】

圧電振動デバイスにおいて、

請求項1乃至3のうちいずれか1つに記載の発振回路に、複数の圧電振動子が接続され、

前記複数の圧電振動子のうち発振させる圧電振動子の周波数に対応させて、前記可変容量素子の容量が設定され、

前記可変容量素子の容量は、発振させる圧電振動子の周波数が、周波数の増加に伴って前記発振回路の負性抵抗の絶対値が小さくなる周波数帯域内にあり、かつ、他の容量よりも前記発振回路の負性抵抗の絶対値が大きい値であるように設定されることを特徴とする圧電振動デバイス。

【請求項5】

請求項4に記載の圧電振動デバイスにおいて、

前記複数の圧電振動子が前記発振回路に並列接続され、

前記圧電振動子の並列容量(C0)と、前記発振回路の負荷容量(CL)と、の関係が、C0<CLであることを特徴とする圧電振動デバイス。

【請求項6】

請求項5に記載の圧電振動デバイスにおいて、

前記2個の圧電振動子が前記発振回路に並列接続され、

前記2個の圧電振動子のうち、前記並列容量(C0)の値が大きい方を並列容量(C01)とし、前記並列容量(C0)の値が小さい方を並列容量(C02)とした時、前記並列容量(C01)と前記並列容量(C02)と前記発振回路の負荷容量(CL)との関係が、C012/C02<CLであることを特徴とする圧電振動デバイス。

【請求項7】

請求項4に記載の圧電振動デバイスにおいて、

前記2個の圧電振動子が前記発振回路に直列接続され、

前記2個の圧電振動子のうち、前記並列容量(C0)の値が大きい方を並列容量(C01)とし、前記並列容量(C0)の値が小さい方を並列容量(C02)とした時、前記並列容量(C01)と前記並列容量(C02)と前記発振回路の負荷容量(CL)との関係が、C022/C01>CLであることを特徴とする圧電振動デバイス。

【請求項8】

請求項5乃至7のうちいすれか1つに記載の圧電振動デバイスにおいて、

前記圧電振動子に、電圧制御回路が直接接続されたことを特徴とする圧電振動デバイス。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【公開番号】特開2012−50000(P2012−50000A)

【公開日】平成24年3月8日(2012.3.8)

【国際特許分類】

【出願番号】特願2010−192605(P2010−192605)

【出願日】平成22年8月30日(2010.8.30)

【出願人】(000149734)株式会社大真空 (312)

【Fターム(参考)】

【公開日】平成24年3月8日(2012.3.8)

【国際特許分類】

【出願日】平成22年8月30日(2010.8.30)

【出願人】(000149734)株式会社大真空 (312)

【Fターム(参考)】

[ Back to top ]