発振回路内で構成要素を接続するオプションコンダクタを提供する技術

【課題】発振回路内で構成要素を接続するオプションコンダクタの使用を可能とする技術の提供。

【解決手段】発振回路200は、第1の伝導層内でルーティングコンダクタを介して相互結合されるトランジスタを含む。発振回路はまた、第2の伝導層内に、バラクタ203〜206、コンデンサ221〜226、及びオプションコンダクタ207、208,212〜216も含む。オプションコンダクタは、トランジスタのうちの1つとコンデンサまたはバラクタとの間の接続の少なくとも一部を形成する。上記発振回路は、第1の伝導層内のルーティングコンダクタを介して前記複数の第1のトランジスタのうちの1つに結合されるインダクタと、該インダクタの第1の部分を形成する、前記第2の伝導層内の第2のオプションコンダクタとをさらに備え得る。

【解決手段】発振回路200は、第1の伝導層内でルーティングコンダクタを介して相互結合されるトランジスタを含む。発振回路はまた、第2の伝導層内に、バラクタ203〜206、コンデンサ221〜226、及びオプションコンダクタ207、208,212〜216も含む。オプションコンダクタは、トランジスタのうちの1つとコンデンサまたはバラクタとの間の接続の少なくとも一部を形成する。上記発振回路は、第1の伝導層内のルーティングコンダクタを介して前記複数の第1のトランジスタのうちの1つに結合されるインダクタと、該インダクタの第1の部分を形成する、前記第2の伝導層内の第2のオプションコンダクタとをさらに備え得る。

【発明の詳細な説明】

【技術分野】

【0001】

(関連出願への相互参照)

本特許出願は、2008年10月9日に出願された米国仮特許出願第61/104,230号および2008年11月25日に出願された米国特許出願第12/277,810号の利益を主張し、上記の米国特許出願は共に本明細書において参照により援用される。

【0002】

(技術分野)

本発明は電子回路に関し、より詳細には、発振回路内の構成要素へのオプションの接続を提供するための技術に関する。

【背景技術】

【0003】

(背景)

位相ロックループ回路は、典型的には、発振回路を使用し、入力クロック信号に応答して、出力クロック信号を生成する。

【発明の概要】

【課題を解決するための手段】

【0004】

(発明の簡単な概要)

本発明のいくつかの実施形態に従い、発振回路は、第1の伝導層内のルーティングコンダクタを介して相互結合されるトランジスタを含む。発振回路はさらに、第2の伝導層内に、バラクタ、コンデンサ、およびオプションコンダクタを含み得る。オプションコンダクタは、トランジスタのうちの1つとコンデンサまたはバラクタとの間の接続の少なくとも一部を形成する。本発明は、本明細書に記載される実施形態を実装するための回路および方法を含む。

【0005】

本発明の種々の目的、特徴、および利点は、以下の発明を実施するための形態および添付の図面を検討する際に、明らかになる。

例えば、本発明は以下の項目を提供する。

(項目1)

第1の伝導層内のルーティングコンダクタを介して相互結合される複数の第1のトランジスタと、

第1のバラクタと、

第1のコンデンサと、

該複数の第1のトランジスタのうちの1つと、該第1のコンデンサおよび該第1のバラクタのうちの1つとの間の接続の少なくとも一部を形成する、第2の伝導層内の第1のオプションコンダクタと

を備える、発振回路。

(項目2)

上記第1の伝導層内のルーティングコンダクタを介して上記複数の第1のトランジスタのうちの1つに結合されるインダクタと、

該インダクタの第1の部分を形成する、上記第2の伝導層内の第2のオプションコンダクタと

をさらに備え、該インダクタの第2の部分は、該第1の伝導層内に形成される、項目1に記載の発振回路。

(項目3)

上記第1の伝導層内の上記ルーティングコンダクタを介して上記第1のコンデンサに結合される第1のスイッチと、

第2のコンデンサと、

該第1の伝導層内のルーティングコンダクタを介して該第2のコンデンサに結合される第2のスイッチと、

該第2のコンデンサと該第1のコンデンサとの間の接続の少なくとも一部を形成する、上記第2の伝導層内の第2のオプションコンダクタと

をさらに備え、上記第1のオプションコンダクタは、該第1の伝導層内のルーティングコンダクタに結合される、項目1に記載の発振回路。

(項目4)

第3のコンデンサと、

上記第1の伝導層内の上記ルーティングコンダクタを介して該第3のコンデンサに結合される第3のスイッチと、

該第3のコンデンサと、上記複数の第1のトランジスタのうちの1つとの間の接続の少なくとも一部を形成する、上記第2の伝導層内の第3のオプションコンダクタと

をさらに備える、項目3に記載の発振回路。

(項目5)

第4のコンデンサと、

上記第1の伝導層内の上記ルーティングコンダクタを介して該第4のコンデンサに結合される第4のスイッチと、

該第4のコンデンサと、上記第3のコンデンサとの間の接続の少なくとも一部を形成する、上記第2の伝導層内の第4のオプションコンダクタと

をさらに備える、項目4に記載の発振回路。

(項目6)

第2のバラクタと、

該第2のバラクタと、上記複数の第1のトランジスタのうちの1つとの間の接続の少なくとも一部を形成する、上記第2の伝導層内の第2のオプションコンダクタと

をさらに備え、上記第1のオプションコンダクタは、上記第1のバラクタと、該複数の第1のトランジスタのうちの1つとの間の接続の少なくとも一部を形成する、項目1に記載の発振回路。

(項目7)

上記発振回路は、プログラマブル論理集積回路上に製造される、項目1に記載の発振回路。

(項目8)

複数の第2のトランジスタをさらに備え、該複数の第2のトランジスタは、上記第1の伝導層内の上記ルーティングコンダクタを介して、一緒に相互結合され、上記第1のバラクタに結合される、項目1に記載の発振回路。

(項目9)

複数の集積回路ダイであって、該複数の集積回路ダイは、それぞれ、

発振回路を備え、該発振回路は、

第1の伝導層内で複数の第1のルーティングコンダクタの第1のサブセットを介して相互結合される複数の第1のトランジスタと、第1のバラクタと、第1のコンデンサと、該複数の第1のルーティングコンダクタのうちの1つを介して該複数の第1のトランジスタのうちの少なくとも1つに結合されるインダクタとを備え、

第1のサブセット内の該複数の集積回路ダイは、それぞれ、該複数の第1のトランジスタのうちの少なくとも1つと、該第1のコンデンサおよび該第1のバラクタの少なくとも1つとの間の接続の少なくとも一部を形成する、第2の伝導層内の第2のルーティングコンダクタを備え、第2のサブセット内の該複数の集積回路ダイは、それぞれ、該第1のコンデンサおよび該第1のバラクタのうちの少なくとも1つを介して電流を阻止する、該第2の伝導層内の第1の開回路を備える、集積回路ダイ。

(項目10)

上記第1のサブセット内の上記複数の集積回路ダイのそれぞれは、上記インダクタの第1の部分を形成する、上記第2の伝導層内の第3のルーティングコンダクタを備え、該インダクタの第2の部分は、該第1のサブセット内の該複数の集積回路ダイのそれぞれにおける上記第1の伝導層内に形成される、項目9に記載の集積回路ダイ。

(項目11)

上記第2のルーティングコンダクタは、上記複数の第1のトランジスタのうちの少なくとも1つと上記第1のコンデンサとの間の接続の一部を形成し、上記第1のサブセット内の上記複数の集積回路ダイのそれぞれにおける上記第2の伝導層内の第3のルーティングコンダクタは、上記第1のバラクタと該複数の第1のトランジスタのうちの少なくとも1つとの間の接続の一部を形成し、上記第1の開回路は、該第1のコンデンサを通る電流を阻止し、上記第2のサブセット内の上記複数の集積回路ダイのそれぞれは、該第1のバラクタを通る電流を阻止する、該第2の伝導層内の第2の開回路を備える、項目9に記載の集積回路ダイ。

(項目12)

上記発振回路はさらに第2のコンデンサを備え、上記第2のルーティングコンダクタは、上記複数の第1のトランジスタのうちの少なくとも1つと、上記第1のコンデンサとの間の接続の一部を形成し、上記第1のサブセット内の上記複数の集積回路ダイのそれぞれにおける上記第2の伝導層内の第3のルーティングコンダクタは、該第2のコンデンサと該複数の第1のトランジスタのうちの少なくとも1つとの間の接続の一部を形成し、上記第2のサブセット内の該複数の集積回路ダイのそれぞれは、該第2のコンデンサを通る電流を阻止する、該第2の伝導層内の第2の開回路を備える、項目9に記載の集積回路ダイ。

(項目13)

上記発振回路はさらに第3のコンデンサを備え、上記第1のサブセット内の上記複数の集積回路ダイのそれぞれにおける上記第2の伝導層内の第4のルーティングコンダクタは、該第3のコンデンサと上記複数の第1のトランジスタのうちの少なくとも1つとの間の接続の一部を形成し、上記第2のサブセット内の該複数の集積回路ダイのそれぞれは、該第3のコンデンサを通る電流を阻止する、該第2の伝導層内の第3の開回路を備える、項目12に記載の集積回路ダイ。

(項目14)

上記発振回路はさらに複数の第2のトランジスタを備え、該複数の第2のトランジスタは、上記第1のルーティングコンダクタの第2のサブセットを介して相互結合され、上記複数の第1のトランジスタに結合される、項目9に記載の集積回路ダイ。

(項目15)

上記発振回路は、第2のバラクタをさらに備え、上記第2のルーティングコンダクタは、上記複数の第1のトランジスタのうちの少なくとも1つと、上記第1のバラクタとの間の接続の一部を形成し、上記第1のサブセット内の上記複数の集積回路ダイのそれぞれにおける上記第2の伝導層内の第3のルーティングコンダクタは、上記第2のバラクタと上記第1のトランジスタのうちの少なくとも1つとの間の接続の一部を形成し、上記第2のサブセット内の該複数の集積回路ダイのそれぞれは、該第2のバラクタを通る電流を阻止する、該第2の伝導層内の第2の開回路を備える、項目9に記載の集積回路ダイ。

(項目16)

上記発振回路は、第2のバラクタおよび第3のバラクタをさらに備え、該第2のバラクタおよび該第3のバラクタは、上記第1のルーティングコンダクタの第2のサブセットを介して上記複数の第1のトランジスタに結合され、上記第2のルーティングコンダクタは、該複数の第1のトランジスタのうちの少なくとも1つと、上記第1のバラクタとの間の接続の一部を形成し、上記第1の開回路は、該第2のサブセット内の上記複数の集積回路ダイのそれぞれにおける該第1のバラクタを通る電流を阻止する、項目9に記載の集積回路ダイ。

(項目17)

第1の伝導層内に形成される複数のルーティングコンダクタを介して相互結合される複数の第1のトランジスタと、

第1のコンデンサと、

該複数のルーティングコンダクタのうちの1つを介して該複数の第1のトランジスタのうちの1つに結合される、インダクタと、

該複数の第1のトランジスタのうちの1つと該第1のコンデンサとの間の接続の少なくとも一部を形成する、第1のオプションコンダクタであって、該第1のオプションコンダクタは、該第1の伝導層とは異なる第2の伝導層内にある、第1のオプションコンダクタと

を備える、発振回路。

(項目18)

第1のバラクタと、

上記複数の第1のトランジスタのうちの1つと該第1のバラクタとの間の接続の少なくとも一部を形成する、上記第2の伝導層内の第2のオプションコンダクタであって、該第2のオプションコンダクタは、上記複数のルーティングコンダクタのうちの1つに結合される、第2のオプションコンダクタと

をさらに備える、項目17に記載の発振回路。

(項目19)

第2のバラクタと、

上記複数の第1のトランジスタのうちの1つと該第2のバラクタとの間の接続の少なくとも一部を形成する、上記第2の伝導層内の第3のオプションコンダクタであって、該第3のオプションコンダクタは、上記複数のルーティングコンダクタのうちの1つに結合される、第3のオプションコンダクタと

をさらに備える、項目18に記載の発振回路。

(項目20)

第2のコンデンサと、

上記複数の第1のトランジスタのうちの1つと該第2のコンデンサとの間の接続の少なくとも一部を形成する、上記第2の伝導層内の第2のオプションコンダクタであって、該第2のオプションコンダクタは、上記複数のルーティングコンダクタのうちの1つに結合される、第2のオプションコンダクタと

をさらに備える、項目17に記載の発振回路。

(項目21)

発振器を形成するための方法であって、該方法は、

修正された伝導層にオプションコンダクタを追加することにより、複数の集積回路ダイの第1のセット内の該発振器のノードにおいてキャパシタンスを増加させることと、

該修正された伝導層から該オプションコンダクタの少なくとも一部を除去することによって、該複数の集積回路ダイの第2のセット内の該発振器の該ノードにおいて該キャパシタンスを減少させることと、

該修正された伝導層以外の1つ以上の伝導層を使用して、該発振器内の各構成要素を共に結合することと

を含む、方法。

(項目22)

上記複数の集積回路ダイの上記第1のセット内の上記発振器のノードにおいて上記キャパシタンスを増加させることは、可変キャパシタンスを該ノードに結合することによって、該ノードにおいて該キャパシタンスを増加させることをさらに含み、該複数の集積回路ダイの上記第2のセット内の上記発振器のノードにおいて該キャパシタンスを減少させることは、該可変キャパシタンスを該ノードから結合解除することによって、該ノードにおいて該キャパシタンスを減少させることをさらに含む、項目21に記載の方法。

(項目23)

上記複数の集積回路ダイの上記第1のセット内の上記発振器のノードにおいて上記キャパシタンスを増加させることは、該ノードに固定キャパシタンスを結合することによって、該ノードにおいて該キャパシタンスを増加させることをさらに含み、該複数の集積回路ダイの上記第2のセット内の上記発振器のノードにおいて該キャパシタンスを減少させることは、該固定キャパシタンスを該ノードから結合解除することによって、該ノードにおいて該キャパシタンスを減少させることをさらに含む、項目21に記載の方法。

【図面の簡単な説明】

【0006】

【図1】図1は、本発明の実施形態を含むことができる位相ロックループ(PLL)回路の例を示す。

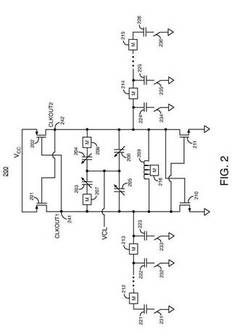

【図2】図2は、本発明の一実施形態に従う、インダクタコンデンサ(LC)電圧制御発振器(VCO)の概略図である。

【図3】図3A〜3Bは、本発明の一実施形態に従う、金属オプションの例の上面図を示すプロセスレイアウト図である。図3Cは、本発明の一実施形態に従う、インダクタの金属オプションの例の上面図を示すプロセスレイアウト図である。図3D〜3Eは、本発明の別の実施形態に従う、インダクタの金属オプションの例の上面図を示すプロセスレイアウト図である。

【図4】図4は、本発明の態様を含むことができるフィールドプログラマブルゲートアレイ(FPGA)の簡略化された部分ブロック図である。

【図5】図5は、本発明の技術を具現化し得る例示的なデジタルシステムのブロック図を示す。

【発明を実施するための形態】

【0007】

(発明の詳細な説明)

図1は、本発明の実施形態を含むことができる位相ロックループ(PLL)回路100の例を示す。PLL100は、位相周波数検知器(PFD)回路101、電荷ポンプ(CP)回路102、ループフィルタ(LF)回路103、電圧制御発振器(VCO)回路104、および周波数分割器回路105を含む。PLL100は、本発明の実施形態を含むことができるPLLの一例である。本発明の実施形態は、多数の他の構成を有するPLLと共に使用可能であることを理解すべきである。

【0008】

PLL100は、典型的には、集積回路上に製造される。PLL100は、例えば、特定用途向け集積回路(ASIC)またはフィールドプログラマブルゲートアレイ(FPGA)等のプログラマブル論理集積回路上に製造し得る。

【0009】

入力参照クロック信号RCLKは、位相周波数検知器(PFD)回路101の第1の入力端子に伝送される。PFD101は、UPおよびDNの出力位相エラー信号内のパルスを生成するために、参照クロック信号RCLKの位相および周波数を、フィードバッククロック信号FBCLKの位相および周波数と比較する。

【0010】

UPおよびDN信号は、電荷ポンプ(CP)回路102の入力端子に伝送される。電荷ポンプ(CP)102は、UPおよびDN信号に応答して、その出力制御電圧VCLを制御する。電荷ポンプ102の出力制御電圧VCLは、ループフィルタ(LF)回路103によってローパスフィルタされる。CP102は、UP信号内の論理高パルスに応答して、電荷をループフィルタ103に送信する。CP102は、DN信号内の論理高パルスに応答して、ループフィルタ103から電荷をドレインする。

【0011】

LFブロック103によってフィルタされる制御電圧VCLは、電圧制御発振器(VCO)回路104の入力端子に伝送される。VCO104は、制御電圧VCLに応答して、周期的出力クロック信号を生成する。VCO104の出力クロック信号は、周波数分割器回路105に伝送される。周波数分割器回路105は、周波数分割フィードバッククロック信号FBCLKを生成するために、周波数分割値によって、VCO104の出力クロック信号の周波数を分割する。

【0012】

PFD101は、参照クロック信号RCLKの周波数が、フィードバッククロック信号FBCLKの周波数より大きい場合に、DN信号内の論理高パルスよりも長いUP信号内の論理高パルスを生成する。UP信号内の論理高パルスがDN信号内の論理高パルスよりも長い場合、CP102は、制御電圧VCLを増加させ、それにより、VCO104の周期的出力クロック信号の周波数を増加させ、それにより、FBCLK信号の周波数を増加させる。

【0013】

PFD101は、フィードバッククロック信号FBCLKの周波数が、参照クロック信号RCLKの周波数よりも大きい場合に、UP信号内の論理高パルスよりも長いDN信号内の論理高パルスを生成する。DN信号内の論理高パルスがUP信号内の論理高パルスよりも長い場合、CP102は、制御電圧VCLを低下させ、それにより、VCO104の周期的出力クロック信号の周波数を低下させ、それにより、FBCLK信号の周波数を低下させる。

【0014】

VCO104は、参照クロック信号RCLKおよびフィードバッククロック信号FBCLKが周波数および位相整列されるまで、制御電圧VCL内の変化に応答して、その出力クロック信号の周波数を変化させる。参照クロック信号RCLKおよびフィードバッククロック信号FBCLKが同一の周波数および位相を有する場合、PLL100は、ロックモードである。

【0015】

図2は、本発明の一実施形態に従う、インダクタコンデンサ(LC)電圧制御発振器(VCO)200の概略図である。LC VCO200(本明細書においてVCO200とも称される)は、図1内のVCO104を実装するために使用可能なアーキテクチャの例である。VCO200は、p−チャネルフィールドエフェクトトランジスタ(FET)201〜202、n−チャネルFET210〜211、インダクタ209、バラクタ203〜206、コンデンサ221〜226、スイッチ231〜236、および金属オプション207〜208および212〜216を含む。VCO200内のトランジスタは、例えば、酸化金属半導体FET(つまり、MOSFET)にし得る。トランジスタは、スイッチ231〜236を実装し得る。

【0016】

バラクタ203、204、205、および206は、可変キャパシタンスを有するコンデンサである。各バラクタ203〜206のキャパシタンスは、バラクタにおける電圧に依存する。バラクタ203〜206は、例えば、逆バイアスダイオードまたはMOSバラクタにし得る。MOSバラクタは、バルク領域がp型ではないn−チャネルMOSFETである。MOSバラクタ内のバルク領域は、p型の基板の代わりに、N型のウェル(well)内にある。

【0017】

電荷ポンプ102は、図2に示されるように、バラクタ203〜206のそれぞれの端子に伝送される制御電圧VCLを生成する。各バラクタ203〜206のキャパシタンスは、バラクタにおける電圧内の変化に応答して変動する。バラクタ203〜206における電圧は、制御電圧VCLおよびノード241〜242における電圧内の変化に応答して、変動する。

【0018】

P−チャネルトランジスタ201〜202は、相互結合される。p−チャネルトランジスタ201のゲートは、p−チャネルトランジスタ202のドレインに結合される。p−チャネルトランジスタ202のゲートは、p−チャネルトランジスタ201のドレインに結合される。トランジスタ201〜202のソースは、電圧VCCを受信するために結合される。トランジスタ201のドレインは、金属オプション207、バラクタ205、インダクタ209、トランジスタ210のドレイン、コンデンサ223、および金属オプション213に結合される。トランジスタ202のドレインは、金属オプション208、バラクタ206、インダクタ209、トランジスタ211のドレイン、コンデンサ224、および金属オプション214に結合される。

【0019】

N−チャネルトランジスタ210〜211は、相互結合される。n−チャネルトランジスタ210のゲートは、n−チャネルトランジスタ211のドレインに結合される。n−チャネルトランジスタ211のゲートは、n−チャネルトランジスタ210のドレインに結合される。トランジスタ210〜211のソースは、同相対地電圧を受信するために結合される。

【0020】

VCO200は、出力ノード241において、0°の位相を有する第1のデジタル出力クロック信号CLKOUT1を生成する。VCO200は、出力ノード242において、第2のデジタル出力クロック信号CLKOUT2を生成する。第2の出力クロック信号CLKOUT2は、第1の出力クロック信号CLKOUT1の位相に対して、180°オフセットである位相を有する。トランジスタ201〜202および210〜211は、出力クロック信号CLKOUT1およびCLKOUT2内の論理高および論理低状態の間の移行を生成するために、オンおよびオフになる。トランジスタ201および211がオンである場合、トランジスタ202および210はオフである。トランジスタ202および210がオンである場合、トランジスタ201および211はオフである。CLKOUT1またはCLKOUT2のいずれかを、フィードバッククロック信号FBCLKを生成するために、周波数分割器105に伝送することができる。

【0021】

VCO200内のインダクタ209およびバラクタ203〜206は、並列共振LCタンクを形成する。バラクタのキャパシタンス203〜206は、電荷ポンプ102によって生じる制御電圧VCL内の変化に応答して変動する。LCタンクは、制御電圧VCLがバラクタ203〜206のキャパシタンスを調整すると、その発振周波数を特定する(locates)。VCO200の出力クロック信号CLKOUT1およびCLKOUT2の周波数調整範囲Foscを、式(1)に示す。

【0022】

【数1】

式(1)において、LTANKは、インダクタ209のインダクタンスと等しく、CTANKは、電流がその中を流れることができるように、VCO200内に接続されるコンデンサ221〜226およびバラクタ203〜206の合計のキャパシタンスと等しい。

【0023】

VCO200は、ノード241において並列に結合される任意の適した数のコンデンサを有することができ、VCO200は、ノード242において並列に結合される任意の適した数のコンデンサを有し得る。3つのコンデンサ221〜223が図2の左側に示されるが、これは例示にすぎない。さらに、3つのコンデンサ224〜226が図2の右側に示されるが、これは例示にすぎない。

【0024】

コンデンサ221〜226のそれぞれは、図2に示されるように、スイッチ231〜236のうちの対応する1つと、直列に結合される。スイッチ231〜236は、同相対地電圧を受信するために結合される。コンデンサ221〜226のそれぞれは、固定キャパシタンスを有する。スイッチ231〜233のうちの1つ以上の伝導状態の変化によって、ノード241における全キャパシタンスを変化させることができる。例えば、スイッチ233の伝導状態は、コンデンサ223を対地端子に結合させるために、開から閉へ変更し得る。コンデンサ223の対地端子への結合により、コンデンサ223のキャパシタンスがノード241に追加される。別の例として、コンデンサ223を対地端子から結合解除させるために、スイッチ233の伝導状態を、閉から開へと変更させることができる。対地端子からのコンデンサ223の結合解除により、コンデンサ223のキャパシタンスが、ノード241から除かれる。

【0025】

スイッチ234〜236のうちの1つ以上の伝導状態の変化によって、ノード242における全キャパシタンスを変化させることができる。例えば、スイッチの伝導状態234は、コンデンサ224を対地端子に結合させるために、開から閉へ変更し得る。コンデンサ224の対地端子への結合により、コンデンサ224のキャパシタンスがノード242に追加される。別の例として、対地端子からコンデンサ224を結合解除させるために、スイッチの伝導状態234を、閉から開へ変更し得る。対地端子からのコンデンサ224の結合解除により、コンデンサ224のキャパシタンスが、ノード242から除かれる。

【0026】

ノード241〜242においてキャパシタンスを増加させるために、さらなるスイッチ231〜236を閉じることができ、ノード241〜242におけるキャパシタンスを減少させるために、さらなるスイッチ231〜236を開くことができる。さらなるスイッチ231〜236が開いている場合、最大周波数、最小周波数、中心周波数、およびクロック信号CLKOUT1およびCLKOUT2のためにVCO200が生成可能な他の周波数は増加する。さらなるスイッチ231〜236が閉じている場合、最大周波数、最小周波数、中心周波数、およびクロック信号CLKOUT1およびCLKOUT2のためにVCO200が生成可能な他の周波数は低下する。ノード241におけるキャパシタンスは、好適には、VCO200がその中心を通る垂直軸に対して対称となるように、ノード242におけるキャパシタンスと等しい。

【0027】

ノード241および対地端子の間で結合されるコンデンサ221〜223ならびにノード242および対地端子の間で結合されるコンデンサ224〜226は、VCO200の周波数調整範囲を決定する。スイッチ231〜236および金属オプション207〜208および212〜216の伝導状態の任意の特定のセットにおいて、VCO200の周波数調整範囲は、VCO200によって生成されたクロック信号CLKOUT1およびCLKOUT2の最大および最小周波数の間の差と等しい。特定の周波数調整範囲内のクロック信号CLKOUT1およびCLKOUT2の最大周波数は、バラクタ203〜206がそれらの最小キャパシタンス値である場合に生じる。特定の周波数調整範囲内のクロック信号CLKOUT1およびCLKOUT2の最小周波数は、バラクタ203〜206がそれらの最大キャパシタンス値である場合に生じる。各バラクタ203〜206のキャパシタンスは、バラクタにおいて印加された電圧と反比例する。

【0028】

ノード241〜242における固定キャパシタンスは、出力クロック信号CLKOUT1およびCLKOUT2のためにVCO200が生成する、最小周波数、最大周波数、中心周波数および周波数調整範囲を変化させるために、変更し得る。スイッチ231〜233のうちの1つ以上およびスイッチ234〜236のうちの1つ以上を閉じた後で、ノード241および242におけるキャパシタンスを増加させることにより、VCO200の最小周波数、最大周波数、中心周波数、および周波数調整範囲を縮小させる。ノード241〜242において切り替えられるコンデンサ221〜226は、調整可能なキャパシタンスを有しないため、VCO200の周波数調整範囲は、金属オプション212〜215が伝導性である場合に縮小する。コンデンサ221〜226は、固定荷重として作用する。金属オプション212〜215が全て伝導性である場合、VCO200が、CLKOUT1およびCLKOUT2のために生成する周波数調整範囲は、より多くの固定コンデンサ221〜226等がノード241〜242において切り替えられるため、より多くの量、縮小する。

【0029】

VCO200において、コンデンサ221〜226の上部プレートおよびスイッチ231〜236は、ノード241および242のそれぞれにおける全キャパシタンスを増加し得る寄生キャパシタンスを有する。これらの寄生キャパシタンスは、VCO200が、スイッチ231〜236および金属オプション207〜208および212〜216の伝導状態の任意の特定のセットにおいて、CLKOUT1およびCLKOUT2のために生成可能な最大周波数を制限する。例えば、コンデンサ221〜226の寄生キャパシタンスは、スイッチ231〜236の全てが開であり、かつ、金属オプションの全てが伝導性である場合に、CLKOUT1およびCLKOUT2の最大周波数を制限し得る。

【0030】

バラクタ203〜206のキャパシタンスは、出力クロック信号CLKOUT1およびCLKOUT2の周波数の微調整を生成するために、制御電圧VCLに応答して変動する。コンデンサ221〜226は、出力クロック信号CLKOUT1およびCLKOUT2の周波数の粗調整を生成させるために(つまり、バラクタによって生じるよりも大きい周波数の変化を生じさせるために)、スイッチ231〜236を使用して、ノード241〜242において、入および切に切り替えられる。

【0031】

VCO200は、金属オプション207〜208および212〜216を含む。金属オプション207〜208および212〜216は、VCO200内のコンダクタのほとんどを形成するために使用される伝導層とは異なる1つ以上のさらなる伝導層内に形成されるコンダクタを含む。金属オプションを形成するコンダクタは、1つ以上のさらなる伝導層内の集積回路ダイに任意で追加され得る。金属オプションは、金属または別の適した伝導材料を用いて、1つ以上のさらなる伝導層内に形成し得る。金属オプション207〜208および212〜216を形成するコンダクタのいずれかを、対応する金属オプション接続を作成または結合解除するために、さらなる伝導層のためのマスクへ追加、またはマスクから除去し得る。

【0032】

金属オプションを含むさらなる伝導層のマスクを、VCO200において他のコンダクタを含む1つ以上の伝導層のために各マスクを修正する必要なく、修正できる。この特徴により、VCO200内の伝導層を形成するために使用されるマスク層に作成する必要がある、修正の量および複雑さが低減される。そのため、金属オプション207〜208および212〜216は、露光プロセス中の集積回路ダイの作成に使用されるマスク層の修正コストを削減する。金属オプションは、さらに、他のマスクを再生成するためにさらに時間がかからないため、集積回路製品が市場に出るまでの時間を短縮する。マスクを利用して、ほぼ同一の発振回路アーキテクチャを有する、複数の集積回路ダイを作成し得る。発振回路アーキテクチャは、1つ以上のさらなる伝導層における金属オプション207〜208および212〜216の伝導性に関し、集積回路ダイの間に限って異なる。

【0033】

図3A〜3Bは、本発明の一実施形態に従う、金属オプションの例の上面図を示すプロセスレイアウト図である。図3A〜3Bに示される金属オプションは、図2に示される金属オプション207〜208および212〜215のそれぞれを実装するように使用可能な一実施形態である。図3A〜3Bに示される金属オプションは、一例にすぎず、本発明の範囲を制限することは意図されていない。図2に示される金属オプションを実装するために、他の種類の構成を使用することもできる。

【0034】

ある特定の実施例に従い、回路要素201〜211、221〜226、および231〜236を接続するルーティングコンダクタの大部分が、VCO200を含む集積回路ダイ上の第1の金属層に形成される。これらのルーティングコンダクタは、図2内の回路要素を接続する実線として示される。この例に従い、金属オプション207〜208および212〜216が、集積回路ダイの上の第2の金属層内に形成される。第1および第2の金属層は、異なる金属層である。集積回路ダイは、2つの金属層よりも多く(例:11の金属層)有し得る。本明細書に記載される第1および第2の金属層は、ダイ上の金属層のうちの任意の2つにし得る。

【0035】

図3Aは、第2の金属層内に形成されるルーティングコンダクタ303Aを示す。ルーティングコンダクタ303Aは、金属オプション207〜208および212〜215のうちの1つの例である。ルーティングコンダクタ304〜305は、第1の金属層内に形成される。第1の金属層は、VCO200内にルーティングコンダクタの大部分を含む。金属オプションは、ルーティングコンダクタ303Aを第2の金属層に追加することにより、ルーティングコンダクタ304および305を接続できる。ルーティングコンダクタ303Aは、ビア301を介して、ルーティングコンダクタ304に、およびビア302を介して、ルーティングコンダクタ305に結合される。

【0036】

金属オプションは、図3Bに示されるように、第2の金属層からルーティングコンクタ303Aの一部を除去することにより、ルーティングコンダクタ304および305を結合解除できる。図3Bは、第2の金属層内のコンダクタ303Aの一部である、コンダクタ303Bおよびコンダクタ303Cを示す。コンダクタ303Bおよび303Cは、コンダクタ303Bおよび303Cの間に結合解除部分があるため、コンダクタ304および305は共に結合しない。図3Bに示されるように、第2の金属層内のコンダクタ303Bおよび303Cがコンダクタ304および305を共に接続させない場合、金属オプション(例:207〜208および212〜215)は、開回路となる。

【0037】

図3A〜3Bの設定の間で、ルーティングコンダクタ303の形状を変更するために、第2の金属層を形成するために使用される露光マスクを修正し得る。第1の金属層のマスクまたは露光中に集積回路ダイ上にVCO200を形成するために使用される他の層のいずれかのためのマスクを変更せずに、第2の金属層のマスクを修正し得る。

【0038】

金属オプション216は、インダクタ209のコイルへ1つ以上の一巻きを追加する、またはインダクタ209のコイルから1つ以上の一巻きを除去できる。金属オプション216は、インダクタ209のコイル内の一巻きの数の変更に加えて、または、その代わりに、インダクタ209のコイルの1つ以上の一巻きの直径を大きくする、または、インダクタ209のコイルの1つ以上の一巻きの直径を小さくすることもできる。

【0039】

図3Cは、本発明の一実施形態に従う、インダクタ209の金属オプションの例の上面図を示す、プロセスレイアウト図である。図3Cは、外側の一巻きおよび内側の一巻きを有するインダクタ209のコイルを示す。コンダクタ311は、インダクタ209の外側の一巻きであり、コンダクタ312は、インダクタ209の内側の一巻きである。コンダクタ311〜312は、金属、または、代替的に、別の種類の伝導性材料で形成される。コンダクタ311は、第1の金属層内に形成され、コンダクタ312は、第2の金属層内に形成される。コンダクタ311および312は、交差313において互いに交差する。コンダクタ311は、入力ノード1および2に結合される。

【0040】

コンダクタ312は、金属オプション216の例である。コンダクタ312は、ビア314および315を介して、コンダクタ311に接続可能である。コンダクタ312は、内側の一巻きをインダクタ209の外側の一巻きへ接続するために、第2の金属層のためのマスクに追加できる。あるいは、コンダクタ312の一部または全てを、インダクタ209から内側の一巻きを除去する、または単に外側の一巻きから内側の一巻きを結合解除するために、第2の金属層のマスクから除去できる。インダクタ209のインダクタンスを増加させるために、内側の一巻き312を第2の金属層に追加し、また、外側の一巻き311に接続し得る。内側の一巻き312を、インダクタ209のインダクタンスを低下させるために、第2の金属層から除去する、または外側の一巻き311から結合解除できる。

【0041】

図3D〜3Eは、本発明の別の実施形態に従う、インダクタ209の金属オプションの例の上面図を示すプロセスレイアウト図である。コンダクタ321は、インダクタ209のコイルの一巻きにし得る。コンダクタ322は、インダクタ209のコイルの一巻きにすることもできる。VCO200のルーティングコンダクタは、第1の金属層に形成される。コンダクタ321〜322は、第2の金属層に形成される。VCO200のルーティングコンダクタのいくつかを、第3、第4等の金属層において形成し得る。

【0042】

コンダクタ321〜322は、金属オプション216の例である。コンダクタ321は、インダクタ209のコイルのより大きな直径の一巻きを形成するために、ダイの第2の金属層内に形成される。コンダクタ322が、インダクタ209のコイルのより小さい直径の一巻きを生成するために、ダイの第2の金属層内に形成される。コイルの1つ以上の一巻きの直径の変化は、インダクタ209のインダクタンスに影響する。コンダクタ321またはコンダクタ322のいずれかは、ノード1および2において第1の金属層内のインダクタ209(例:さらなるコイルの一巻き)のコンダクタに接続される。第2の金属層を作成するために使用されるマスクは、図3D〜3Eに示されるコイルの一巻きの直径の変化に影響するように修正される。

【0043】

インダクタ209は、そのコイル内に複数の一巻きを有し得る。しかしながら、図面の簡略化のために、図3D〜3Eのそれぞれでは、1つのみの一巻きが示されている。一実施形態に従い、インダクタ209のコイルの複数の一巻きの直径を、第2の伝導層内の対応するコンダクタの直径を変化させることにより、修正し得る。

【0044】

再び図2を参照すると、金属オプション207は、バラクタ203をノード241に接続する、またはノード241からバラクタ203を結合解除させることができる。金属オプション208は、バラクタ204をノード242に接続する、またはノード242からバラクタ204を結合解除させることができる。金属オプション207〜208は、VCO200の周波数調整範囲を増加させるために、それぞれ、ノード241〜242に、バラクタ203〜204を接続し得る。金属オプション207〜208は、VCO200の周波数調整範囲を縮小させるために、それぞれ、ノード241〜242からバラクタ203〜204を結合解除させることができる。上記のように、さらなる伝導層へ、ルーティングコンダクタの一部を追加するまたは追加しないことにより、金属オプション207〜208を実装し得る。バラクタ203および204がそれぞれ、ノード241〜242から結合解除される場合、ルーティングコンダクタは、ノード241〜242において、バラクタ203〜204によって導入される寄生キャパシタンスを減少させるために、金属オプション207〜208から除去される。

【0045】

金属オプション213は、コンデンサ222をノード241に接続させる、またはノード241からコンデンサ222を結合解除させることができる。金属オプション213が伝導性である場合、金属オプション212は、コンデンサ221をノード241に接続する、またはノード241からコンデンサ221を結合解除させることができる。金属オプション214は、コンデンサ225をノード242に接続する、またはコンデンサ225をノード242から結合解除し得る。金属オプション214が伝導性である場合、金属オプション215は、コンデンサ226をノード242に接続する、またはコンデンサ226をノード242から結合解除し得る。上記のように、金属オプション212〜215を、さらなる伝導層へ、ルーティングコンダクタの一部を追加する、または追加しないことにより、実装し得る。

【0046】

スイッチ231〜232および235〜236の伝導状態を変化させることによってダイを形成後、ダイがノード241〜242における固定キャパシタンスを調整するための柔軟性を有することが意図されている場合、金属オプション212〜215を伝導性にすることにより、特定の集積回路ダイ内において、ノード241〜242に余剰の固定コンデンサ221〜222および225〜226を結合し得る。例えば、金属オプション212〜215は、高いまたは低い周波数において機能するように意図されている発振器内で伝導性であり得る。

【0047】

高い周波数においてのみ機能するように意図されている発振器において、金属オプション212〜215は、ノード241〜242から使用されていない回路要素(例:コンデンサ221〜222、コンデンサ225〜226、スイッチ231〜232、およびスイッチ235〜236)を結合解除するために、第2の伝導層内における開回路にすることができ、それにより、ノード241および242における寄生キャパシタンスを減少させる。ノード241〜242における寄生キャパシタンスの減少により、VCO200によって、できるだけ大きなCLKOUT1およびCLKOUT2のための最大周波数、最小周波数、中心周波数、および周波数調整範囲を生成させる。例えば、コンデンサ221〜222および225〜226が集積回路ダイで使用することを意図されていない場合、ノード241および242における寄生キャパシタンスを減少させる開回路を作成するために、ダイから金属オプション213および214内のルーティングコンダクタを削除できる。

【0048】

別の例として、集積回路ダイにおいてコンデンサ222および225を使用し得るが、コンデンサ221および226がそのダイで使用されることを意図されていない場合、金属オプション213および214内のルーティングコンダクタは、コンデンサ222および225を、それぞれ、ノード241および242に接続させるために、ダイに追加され、金属オプション212および215内のルーティングコンダクタは、ノード241および242における寄生キャパシタンスを減少する開回路を作成するために、ダイから削除される。

【0049】

金属オプション216は、インダクタ209におけるコイルの不要な一巻きを除去することにより、ノード241および242における寄生キャパシタンスを減少できる。金属オプション216は、さらに、インダクタ209のインダクタンス値を変更するために使用し得る。上記の式(1)に基づき、インダクタ209のためのより小さなインダクタンス値は、VCO200の出力クロック信号CLKOUT1およびCLKOUT2の周波数が増加することを可能にする。VCO200の出力クロック信号の周波数における増加の大部分は、インダクタ209のインダクタンス値の変化の結果である。

【0050】

CLKOUT1およびCLKOUT2の周波数は、ノード241および242における寄生キャパシタンスの減少に応答して増加する。特に、CLKOUT1およびCLKOUT2の最大周波数、最小周波数、中心周波数、および周波数調整範囲は、全て、ノード241〜242における寄生キャパシタンスの減少に応答して、増加する。一例として、VCO200は、最高で秒あたり10〜11ギガバイト(Gbps)のCLKOUT1およびCLKOUT2のデータレートを生成し得る。この例は、本発明の範囲を制限することを意図するものではない。

【0051】

上述のように、VCO200は、CLKOUT1およびCLKOUT2のための複数の異なる周波数調整範囲を生成できる。金属オプション207〜208および212〜216が、使用されていない回路要素によって生じるノード241〜242における寄生キャパシタンスを減少させる場合に、VCO200内の寄生キャパシタンスは、CLKOUT1およびCLKOUT2の周波数調整範囲の縮小を生じさせる。従って、VCO200は、CLKOUT1およびCLKOUT2の小さいおよび大きい中心周波数において、幅広い周波数調整範囲をサポートできる。

【0052】

本発明の範囲を制限することが意図されていない特定の例を挙げると、VCO200は、VCO200によってサポートされる最小中心周波数の二倍であるCLKOUT1およびCLKOUT2の最大中心周波数をサポートできる。ノード241〜242において固定キャパシタンスを減少させるための金属オプション、バラクタの数、およびインダクタ209のサイズおよびインダクタンスを使用することにより、VCO200は、CLKOUT1およびCLKOUT2のためのより大きな周波数を生成できる。より高いデータレートにおいて、金属オプションは、より低いデータレート(つまり、5〜6Gbps)で必要な余剰のキャパシタンスおよび伝導電荷を除去するために使用される。

【0053】

本明細書に記載される金属オプションは、それぞれ、発振回路を有する複数の集積回路ダイを作成するために使用できる。集積回路ダイ内の発振回路は、上記のように、および、図に示されるように、1つ以上のさらなる伝導層内における金属オプションコンダクタ207〜208および212〜216の伝導性に関してのみ、互いに、アーキテクチャが異なる。各ダイ内の発振回路の間の差を作成するために、さらなる伝導層のみ(例:第2の金属層)が修正される。

【0054】

図4は、本発明の態様を含むことができるフィールドプログラマブルゲートアレイ(FPGA)400の略部分ブロック図である。FPGA400は、本発明の特徴を含むことができる集積回路の一例にすぎない。本発明の実施形態は、フィールドプログラマブルゲートアレイ(FPGA)、プログラマブル論理デバイス(PLD)、複雑なプログラマブル論理デバイス(CPLD)、プログラマブル論理アレイ(PLA)、および特定用途向け集積回路(ASIC)等の数多くの種類の集積回路で使用可能であることを理解されたい。

【0055】

FPGA400は、多様な長さおよび速度の、行および列の相互接続コンダクタのネットワークで相互接続される、プログラマブル論理アレイブロック(またはLAB)402の2次元アレイを含む。LAB402は、複数の(例えば、10の)論理要素(またはLE)を含む。

【0056】

LEは、ユーザ定義された論理機能の効率的な実装を行うプログラマブル論理回路ブロックである。FPGAは、種々の組み合わせおよびシーケンスの機能を実装するように構成可能な、多くの論理要素を有する。論理要素は、プログラマブル相互接続構造にアクセスできる。プログラマブル相互接続構造は、ほぼ任意の所望の構成における論理要素と相互接続するようにプログラムすることが可能である。

【0057】

FPGA400は、さらに、アレイ全体に提供される多様なサイズのランダムアクセスメモリ(RAM)ブロックを含む分散メモリ構造を含む。RAMブロックは、例えば、ブロック404、ブロック406、およびブロック408を含む。これらのメモリブロックは、さらに、シフトレジスタおよび先入れ先出し(FIFO)バッファを含むことができる。

【0058】

FPGA400は、さらに、例えば、加算または減算機能を有する乗算器を実装可能なデジタル信号処理(DSP)ブロック410を含む。この実施例において、チップの周辺に配置される入力/出力要素(IOE)412は、多数のシングルエンドおよび差分入力/出力基準(differential input/output standards)をサポートする。IOE412は、集積回路のパッドに連結される入力および出力バッファを含む。パッドは、例えば、FPGAおよび1つ以上の外部デバイスの間で入力信号、出力信号、および供給電圧を経路指定するように使用可能なFPGAダイの外部端子である。FPGA400は、例示の目的のために、本明細書に記載されているにすぎず、本発明は、多くの異なる種類のPLD、FPGA、およびASICで実装可能であることを理解されたい。

【0059】

本発明は、いくつかの構成要素のうちの1つとしてFPGAを有するシステムで実装することもできる。図5は、本発明の技術を具現化可能な例示的なデジタルシステム500のブロック図を示す。システム500は、プログラムされたデジタルコンピュータシステム、デジタル信号処理システム、専用のデジタル切り替えネットワーク、または他の処理システムにし得る。さらに、かかるシステムは、電気通信システム、自動車システム、制御システム、家庭用電化製品、パーソナルコンピュータ、インターネット通信およびネットワーキング等の幅広い種類の応用のために設計し得る。さらに、システム500は、単一ボード上、複数ボード上、または複数の筐体内に提供可能である。

【0060】

システム500は、1つ以上のバスで相互結合される処理装置502、メモリ装置504、および入力/出力(I/O)装置506を含む。この例示的な実施形態に従い、FPGA508は、処理装置502に埋め込まれる。FPGA508は、図5のシステム内の多くの異なる目的に役立つことができる。FPGA508は、例えば、その内部および外部動作をサポートする、処理装置502の論理ビルディングブロックにし得る。FPGA508は、システム動作におけるその特定の役割を実行するために必要な論理機能を実装するようにプログラムされる。FPGA508は、特に、接続510によってメモリ504へ、また、接続512によって、I/O装置506へ連結可能である。

【0061】

処理装置502は、処理または格納のために、適切なシステム構成要素にデータを送信し、メモリ504に格納されたプログラムを実行し、I/O装置506、または他の同様の機能を介して、データを送受信できる。処理装置502は、コントローラ、ネットワークコントローラ、または任意の種類のプロセッサまたはコントローラとして使用されるようにプログラムされた、中央処理装置(CPU)、マイクロプロセッサ、浮動小数点コプロセッサ、グラフィックコプロセッサ、ハードウェアコントローラ、マイクロコントローラ、フィールドプログラマブルゲートアレイにし得る。さらに、多くの実施形態において、多くの場合、CPUは不要である。

【0062】

例えば、CPUの代わりに、1つ以上のFPGA508が、システムの論理動作を制御可能である。別の例として、FPGA508は、特定のコンピューティングタスクを取り扱うために必要なように再プログラム可能な、再構成可能なプロセッサとして機能する。あるいは、FPGA508は、それ自体に、埋め込みマイクロプロセッサを含むことができる。メモリ装置504は、ランダムアクセスメモリ(RAM)、読み込み専用メモリ(ROM)、固定またはフレキシブルディスク媒体、フラッシュメモリ、テープ、または任意の他の格納手段、あるいはこれらの格納手段の任意の組み合わせにし得る。

【0063】

本発明の例示的な実施形態の上記の記載は、例示および説明の目的で示されている。上記の記載は、包括的、または、本発明を本明細書に開示された実施例に制限することを意図していない。いくつかの例において、本発明の特徴は、記載されているように、他の特徴の対応する利用なしに利用し得る。本発明の範囲から逸脱せずに、上記の教示に照らして、多くの修正、置換、および変形が可能である。

【技術分野】

【0001】

(関連出願への相互参照)

本特許出願は、2008年10月9日に出願された米国仮特許出願第61/104,230号および2008年11月25日に出願された米国特許出願第12/277,810号の利益を主張し、上記の米国特許出願は共に本明細書において参照により援用される。

【0002】

(技術分野)

本発明は電子回路に関し、より詳細には、発振回路内の構成要素へのオプションの接続を提供するための技術に関する。

【背景技術】

【0003】

(背景)

位相ロックループ回路は、典型的には、発振回路を使用し、入力クロック信号に応答して、出力クロック信号を生成する。

【発明の概要】

【課題を解決するための手段】

【0004】

(発明の簡単な概要)

本発明のいくつかの実施形態に従い、発振回路は、第1の伝導層内のルーティングコンダクタを介して相互結合されるトランジスタを含む。発振回路はさらに、第2の伝導層内に、バラクタ、コンデンサ、およびオプションコンダクタを含み得る。オプションコンダクタは、トランジスタのうちの1つとコンデンサまたはバラクタとの間の接続の少なくとも一部を形成する。本発明は、本明細書に記載される実施形態を実装するための回路および方法を含む。

【0005】

本発明の種々の目的、特徴、および利点は、以下の発明を実施するための形態および添付の図面を検討する際に、明らかになる。

例えば、本発明は以下の項目を提供する。

(項目1)

第1の伝導層内のルーティングコンダクタを介して相互結合される複数の第1のトランジスタと、

第1のバラクタと、

第1のコンデンサと、

該複数の第1のトランジスタのうちの1つと、該第1のコンデンサおよび該第1のバラクタのうちの1つとの間の接続の少なくとも一部を形成する、第2の伝導層内の第1のオプションコンダクタと

を備える、発振回路。

(項目2)

上記第1の伝導層内のルーティングコンダクタを介して上記複数の第1のトランジスタのうちの1つに結合されるインダクタと、

該インダクタの第1の部分を形成する、上記第2の伝導層内の第2のオプションコンダクタと

をさらに備え、該インダクタの第2の部分は、該第1の伝導層内に形成される、項目1に記載の発振回路。

(項目3)

上記第1の伝導層内の上記ルーティングコンダクタを介して上記第1のコンデンサに結合される第1のスイッチと、

第2のコンデンサと、

該第1の伝導層内のルーティングコンダクタを介して該第2のコンデンサに結合される第2のスイッチと、

該第2のコンデンサと該第1のコンデンサとの間の接続の少なくとも一部を形成する、上記第2の伝導層内の第2のオプションコンダクタと

をさらに備え、上記第1のオプションコンダクタは、該第1の伝導層内のルーティングコンダクタに結合される、項目1に記載の発振回路。

(項目4)

第3のコンデンサと、

上記第1の伝導層内の上記ルーティングコンダクタを介して該第3のコンデンサに結合される第3のスイッチと、

該第3のコンデンサと、上記複数の第1のトランジスタのうちの1つとの間の接続の少なくとも一部を形成する、上記第2の伝導層内の第3のオプションコンダクタと

をさらに備える、項目3に記載の発振回路。

(項目5)

第4のコンデンサと、

上記第1の伝導層内の上記ルーティングコンダクタを介して該第4のコンデンサに結合される第4のスイッチと、

該第4のコンデンサと、上記第3のコンデンサとの間の接続の少なくとも一部を形成する、上記第2の伝導層内の第4のオプションコンダクタと

をさらに備える、項目4に記載の発振回路。

(項目6)

第2のバラクタと、

該第2のバラクタと、上記複数の第1のトランジスタのうちの1つとの間の接続の少なくとも一部を形成する、上記第2の伝導層内の第2のオプションコンダクタと

をさらに備え、上記第1のオプションコンダクタは、上記第1のバラクタと、該複数の第1のトランジスタのうちの1つとの間の接続の少なくとも一部を形成する、項目1に記載の発振回路。

(項目7)

上記発振回路は、プログラマブル論理集積回路上に製造される、項目1に記載の発振回路。

(項目8)

複数の第2のトランジスタをさらに備え、該複数の第2のトランジスタは、上記第1の伝導層内の上記ルーティングコンダクタを介して、一緒に相互結合され、上記第1のバラクタに結合される、項目1に記載の発振回路。

(項目9)

複数の集積回路ダイであって、該複数の集積回路ダイは、それぞれ、

発振回路を備え、該発振回路は、

第1の伝導層内で複数の第1のルーティングコンダクタの第1のサブセットを介して相互結合される複数の第1のトランジスタと、第1のバラクタと、第1のコンデンサと、該複数の第1のルーティングコンダクタのうちの1つを介して該複数の第1のトランジスタのうちの少なくとも1つに結合されるインダクタとを備え、

第1のサブセット内の該複数の集積回路ダイは、それぞれ、該複数の第1のトランジスタのうちの少なくとも1つと、該第1のコンデンサおよび該第1のバラクタの少なくとも1つとの間の接続の少なくとも一部を形成する、第2の伝導層内の第2のルーティングコンダクタを備え、第2のサブセット内の該複数の集積回路ダイは、それぞれ、該第1のコンデンサおよび該第1のバラクタのうちの少なくとも1つを介して電流を阻止する、該第2の伝導層内の第1の開回路を備える、集積回路ダイ。

(項目10)

上記第1のサブセット内の上記複数の集積回路ダイのそれぞれは、上記インダクタの第1の部分を形成する、上記第2の伝導層内の第3のルーティングコンダクタを備え、該インダクタの第2の部分は、該第1のサブセット内の該複数の集積回路ダイのそれぞれにおける上記第1の伝導層内に形成される、項目9に記載の集積回路ダイ。

(項目11)

上記第2のルーティングコンダクタは、上記複数の第1のトランジスタのうちの少なくとも1つと上記第1のコンデンサとの間の接続の一部を形成し、上記第1のサブセット内の上記複数の集積回路ダイのそれぞれにおける上記第2の伝導層内の第3のルーティングコンダクタは、上記第1のバラクタと該複数の第1のトランジスタのうちの少なくとも1つとの間の接続の一部を形成し、上記第1の開回路は、該第1のコンデンサを通る電流を阻止し、上記第2のサブセット内の上記複数の集積回路ダイのそれぞれは、該第1のバラクタを通る電流を阻止する、該第2の伝導層内の第2の開回路を備える、項目9に記載の集積回路ダイ。

(項目12)

上記発振回路はさらに第2のコンデンサを備え、上記第2のルーティングコンダクタは、上記複数の第1のトランジスタのうちの少なくとも1つと、上記第1のコンデンサとの間の接続の一部を形成し、上記第1のサブセット内の上記複数の集積回路ダイのそれぞれにおける上記第2の伝導層内の第3のルーティングコンダクタは、該第2のコンデンサと該複数の第1のトランジスタのうちの少なくとも1つとの間の接続の一部を形成し、上記第2のサブセット内の該複数の集積回路ダイのそれぞれは、該第2のコンデンサを通る電流を阻止する、該第2の伝導層内の第2の開回路を備える、項目9に記載の集積回路ダイ。

(項目13)

上記発振回路はさらに第3のコンデンサを備え、上記第1のサブセット内の上記複数の集積回路ダイのそれぞれにおける上記第2の伝導層内の第4のルーティングコンダクタは、該第3のコンデンサと上記複数の第1のトランジスタのうちの少なくとも1つとの間の接続の一部を形成し、上記第2のサブセット内の該複数の集積回路ダイのそれぞれは、該第3のコンデンサを通る電流を阻止する、該第2の伝導層内の第3の開回路を備える、項目12に記載の集積回路ダイ。

(項目14)

上記発振回路はさらに複数の第2のトランジスタを備え、該複数の第2のトランジスタは、上記第1のルーティングコンダクタの第2のサブセットを介して相互結合され、上記複数の第1のトランジスタに結合される、項目9に記載の集積回路ダイ。

(項目15)

上記発振回路は、第2のバラクタをさらに備え、上記第2のルーティングコンダクタは、上記複数の第1のトランジスタのうちの少なくとも1つと、上記第1のバラクタとの間の接続の一部を形成し、上記第1のサブセット内の上記複数の集積回路ダイのそれぞれにおける上記第2の伝導層内の第3のルーティングコンダクタは、上記第2のバラクタと上記第1のトランジスタのうちの少なくとも1つとの間の接続の一部を形成し、上記第2のサブセット内の該複数の集積回路ダイのそれぞれは、該第2のバラクタを通る電流を阻止する、該第2の伝導層内の第2の開回路を備える、項目9に記載の集積回路ダイ。

(項目16)

上記発振回路は、第2のバラクタおよび第3のバラクタをさらに備え、該第2のバラクタおよび該第3のバラクタは、上記第1のルーティングコンダクタの第2のサブセットを介して上記複数の第1のトランジスタに結合され、上記第2のルーティングコンダクタは、該複数の第1のトランジスタのうちの少なくとも1つと、上記第1のバラクタとの間の接続の一部を形成し、上記第1の開回路は、該第2のサブセット内の上記複数の集積回路ダイのそれぞれにおける該第1のバラクタを通る電流を阻止する、項目9に記載の集積回路ダイ。

(項目17)

第1の伝導層内に形成される複数のルーティングコンダクタを介して相互結合される複数の第1のトランジスタと、

第1のコンデンサと、

該複数のルーティングコンダクタのうちの1つを介して該複数の第1のトランジスタのうちの1つに結合される、インダクタと、

該複数の第1のトランジスタのうちの1つと該第1のコンデンサとの間の接続の少なくとも一部を形成する、第1のオプションコンダクタであって、該第1のオプションコンダクタは、該第1の伝導層とは異なる第2の伝導層内にある、第1のオプションコンダクタと

を備える、発振回路。

(項目18)

第1のバラクタと、

上記複数の第1のトランジスタのうちの1つと該第1のバラクタとの間の接続の少なくとも一部を形成する、上記第2の伝導層内の第2のオプションコンダクタであって、該第2のオプションコンダクタは、上記複数のルーティングコンダクタのうちの1つに結合される、第2のオプションコンダクタと

をさらに備える、項目17に記載の発振回路。

(項目19)

第2のバラクタと、

上記複数の第1のトランジスタのうちの1つと該第2のバラクタとの間の接続の少なくとも一部を形成する、上記第2の伝導層内の第3のオプションコンダクタであって、該第3のオプションコンダクタは、上記複数のルーティングコンダクタのうちの1つに結合される、第3のオプションコンダクタと

をさらに備える、項目18に記載の発振回路。

(項目20)

第2のコンデンサと、

上記複数の第1のトランジスタのうちの1つと該第2のコンデンサとの間の接続の少なくとも一部を形成する、上記第2の伝導層内の第2のオプションコンダクタであって、該第2のオプションコンダクタは、上記複数のルーティングコンダクタのうちの1つに結合される、第2のオプションコンダクタと

をさらに備える、項目17に記載の発振回路。

(項目21)

発振器を形成するための方法であって、該方法は、

修正された伝導層にオプションコンダクタを追加することにより、複数の集積回路ダイの第1のセット内の該発振器のノードにおいてキャパシタンスを増加させることと、

該修正された伝導層から該オプションコンダクタの少なくとも一部を除去することによって、該複数の集積回路ダイの第2のセット内の該発振器の該ノードにおいて該キャパシタンスを減少させることと、

該修正された伝導層以外の1つ以上の伝導層を使用して、該発振器内の各構成要素を共に結合することと

を含む、方法。

(項目22)

上記複数の集積回路ダイの上記第1のセット内の上記発振器のノードにおいて上記キャパシタンスを増加させることは、可変キャパシタンスを該ノードに結合することによって、該ノードにおいて該キャパシタンスを増加させることをさらに含み、該複数の集積回路ダイの上記第2のセット内の上記発振器のノードにおいて該キャパシタンスを減少させることは、該可変キャパシタンスを該ノードから結合解除することによって、該ノードにおいて該キャパシタンスを減少させることをさらに含む、項目21に記載の方法。

(項目23)

上記複数の集積回路ダイの上記第1のセット内の上記発振器のノードにおいて上記キャパシタンスを増加させることは、該ノードに固定キャパシタンスを結合することによって、該ノードにおいて該キャパシタンスを増加させることをさらに含み、該複数の集積回路ダイの上記第2のセット内の上記発振器のノードにおいて該キャパシタンスを減少させることは、該固定キャパシタンスを該ノードから結合解除することによって、該ノードにおいて該キャパシタンスを減少させることをさらに含む、項目21に記載の方法。

【図面の簡単な説明】

【0006】

【図1】図1は、本発明の実施形態を含むことができる位相ロックループ(PLL)回路の例を示す。

【図2】図2は、本発明の一実施形態に従う、インダクタコンデンサ(LC)電圧制御発振器(VCO)の概略図である。

【図3】図3A〜3Bは、本発明の一実施形態に従う、金属オプションの例の上面図を示すプロセスレイアウト図である。図3Cは、本発明の一実施形態に従う、インダクタの金属オプションの例の上面図を示すプロセスレイアウト図である。図3D〜3Eは、本発明の別の実施形態に従う、インダクタの金属オプションの例の上面図を示すプロセスレイアウト図である。

【図4】図4は、本発明の態様を含むことができるフィールドプログラマブルゲートアレイ(FPGA)の簡略化された部分ブロック図である。

【図5】図5は、本発明の技術を具現化し得る例示的なデジタルシステムのブロック図を示す。

【発明を実施するための形態】

【0007】

(発明の詳細な説明)

図1は、本発明の実施形態を含むことができる位相ロックループ(PLL)回路100の例を示す。PLL100は、位相周波数検知器(PFD)回路101、電荷ポンプ(CP)回路102、ループフィルタ(LF)回路103、電圧制御発振器(VCO)回路104、および周波数分割器回路105を含む。PLL100は、本発明の実施形態を含むことができるPLLの一例である。本発明の実施形態は、多数の他の構成を有するPLLと共に使用可能であることを理解すべきである。

【0008】

PLL100は、典型的には、集積回路上に製造される。PLL100は、例えば、特定用途向け集積回路(ASIC)またはフィールドプログラマブルゲートアレイ(FPGA)等のプログラマブル論理集積回路上に製造し得る。

【0009】

入力参照クロック信号RCLKは、位相周波数検知器(PFD)回路101の第1の入力端子に伝送される。PFD101は、UPおよびDNの出力位相エラー信号内のパルスを生成するために、参照クロック信号RCLKの位相および周波数を、フィードバッククロック信号FBCLKの位相および周波数と比較する。

【0010】

UPおよびDN信号は、電荷ポンプ(CP)回路102の入力端子に伝送される。電荷ポンプ(CP)102は、UPおよびDN信号に応答して、その出力制御電圧VCLを制御する。電荷ポンプ102の出力制御電圧VCLは、ループフィルタ(LF)回路103によってローパスフィルタされる。CP102は、UP信号内の論理高パルスに応答して、電荷をループフィルタ103に送信する。CP102は、DN信号内の論理高パルスに応答して、ループフィルタ103から電荷をドレインする。

【0011】

LFブロック103によってフィルタされる制御電圧VCLは、電圧制御発振器(VCO)回路104の入力端子に伝送される。VCO104は、制御電圧VCLに応答して、周期的出力クロック信号を生成する。VCO104の出力クロック信号は、周波数分割器回路105に伝送される。周波数分割器回路105は、周波数分割フィードバッククロック信号FBCLKを生成するために、周波数分割値によって、VCO104の出力クロック信号の周波数を分割する。

【0012】

PFD101は、参照クロック信号RCLKの周波数が、フィードバッククロック信号FBCLKの周波数より大きい場合に、DN信号内の論理高パルスよりも長いUP信号内の論理高パルスを生成する。UP信号内の論理高パルスがDN信号内の論理高パルスよりも長い場合、CP102は、制御電圧VCLを増加させ、それにより、VCO104の周期的出力クロック信号の周波数を増加させ、それにより、FBCLK信号の周波数を増加させる。

【0013】

PFD101は、フィードバッククロック信号FBCLKの周波数が、参照クロック信号RCLKの周波数よりも大きい場合に、UP信号内の論理高パルスよりも長いDN信号内の論理高パルスを生成する。DN信号内の論理高パルスがUP信号内の論理高パルスよりも長い場合、CP102は、制御電圧VCLを低下させ、それにより、VCO104の周期的出力クロック信号の周波数を低下させ、それにより、FBCLK信号の周波数を低下させる。

【0014】

VCO104は、参照クロック信号RCLKおよびフィードバッククロック信号FBCLKが周波数および位相整列されるまで、制御電圧VCL内の変化に応答して、その出力クロック信号の周波数を変化させる。参照クロック信号RCLKおよびフィードバッククロック信号FBCLKが同一の周波数および位相を有する場合、PLL100は、ロックモードである。

【0015】

図2は、本発明の一実施形態に従う、インダクタコンデンサ(LC)電圧制御発振器(VCO)200の概略図である。LC VCO200(本明細書においてVCO200とも称される)は、図1内のVCO104を実装するために使用可能なアーキテクチャの例である。VCO200は、p−チャネルフィールドエフェクトトランジスタ(FET)201〜202、n−チャネルFET210〜211、インダクタ209、バラクタ203〜206、コンデンサ221〜226、スイッチ231〜236、および金属オプション207〜208および212〜216を含む。VCO200内のトランジスタは、例えば、酸化金属半導体FET(つまり、MOSFET)にし得る。トランジスタは、スイッチ231〜236を実装し得る。

【0016】

バラクタ203、204、205、および206は、可変キャパシタンスを有するコンデンサである。各バラクタ203〜206のキャパシタンスは、バラクタにおける電圧に依存する。バラクタ203〜206は、例えば、逆バイアスダイオードまたはMOSバラクタにし得る。MOSバラクタは、バルク領域がp型ではないn−チャネルMOSFETである。MOSバラクタ内のバルク領域は、p型の基板の代わりに、N型のウェル(well)内にある。

【0017】

電荷ポンプ102は、図2に示されるように、バラクタ203〜206のそれぞれの端子に伝送される制御電圧VCLを生成する。各バラクタ203〜206のキャパシタンスは、バラクタにおける電圧内の変化に応答して変動する。バラクタ203〜206における電圧は、制御電圧VCLおよびノード241〜242における電圧内の変化に応答して、変動する。

【0018】

P−チャネルトランジスタ201〜202は、相互結合される。p−チャネルトランジスタ201のゲートは、p−チャネルトランジスタ202のドレインに結合される。p−チャネルトランジスタ202のゲートは、p−チャネルトランジスタ201のドレインに結合される。トランジスタ201〜202のソースは、電圧VCCを受信するために結合される。トランジスタ201のドレインは、金属オプション207、バラクタ205、インダクタ209、トランジスタ210のドレイン、コンデンサ223、および金属オプション213に結合される。トランジスタ202のドレインは、金属オプション208、バラクタ206、インダクタ209、トランジスタ211のドレイン、コンデンサ224、および金属オプション214に結合される。

【0019】

N−チャネルトランジスタ210〜211は、相互結合される。n−チャネルトランジスタ210のゲートは、n−チャネルトランジスタ211のドレインに結合される。n−チャネルトランジスタ211のゲートは、n−チャネルトランジスタ210のドレインに結合される。トランジスタ210〜211のソースは、同相対地電圧を受信するために結合される。

【0020】

VCO200は、出力ノード241において、0°の位相を有する第1のデジタル出力クロック信号CLKOUT1を生成する。VCO200は、出力ノード242において、第2のデジタル出力クロック信号CLKOUT2を生成する。第2の出力クロック信号CLKOUT2は、第1の出力クロック信号CLKOUT1の位相に対して、180°オフセットである位相を有する。トランジスタ201〜202および210〜211は、出力クロック信号CLKOUT1およびCLKOUT2内の論理高および論理低状態の間の移行を生成するために、オンおよびオフになる。トランジスタ201および211がオンである場合、トランジスタ202および210はオフである。トランジスタ202および210がオンである場合、トランジスタ201および211はオフである。CLKOUT1またはCLKOUT2のいずれかを、フィードバッククロック信号FBCLKを生成するために、周波数分割器105に伝送することができる。

【0021】

VCO200内のインダクタ209およびバラクタ203〜206は、並列共振LCタンクを形成する。バラクタのキャパシタンス203〜206は、電荷ポンプ102によって生じる制御電圧VCL内の変化に応答して変動する。LCタンクは、制御電圧VCLがバラクタ203〜206のキャパシタンスを調整すると、その発振周波数を特定する(locates)。VCO200の出力クロック信号CLKOUT1およびCLKOUT2の周波数調整範囲Foscを、式(1)に示す。

【0022】

【数1】

式(1)において、LTANKは、インダクタ209のインダクタンスと等しく、CTANKは、電流がその中を流れることができるように、VCO200内に接続されるコンデンサ221〜226およびバラクタ203〜206の合計のキャパシタンスと等しい。

【0023】

VCO200は、ノード241において並列に結合される任意の適した数のコンデンサを有することができ、VCO200は、ノード242において並列に結合される任意の適した数のコンデンサを有し得る。3つのコンデンサ221〜223が図2の左側に示されるが、これは例示にすぎない。さらに、3つのコンデンサ224〜226が図2の右側に示されるが、これは例示にすぎない。

【0024】

コンデンサ221〜226のそれぞれは、図2に示されるように、スイッチ231〜236のうちの対応する1つと、直列に結合される。スイッチ231〜236は、同相対地電圧を受信するために結合される。コンデンサ221〜226のそれぞれは、固定キャパシタンスを有する。スイッチ231〜233のうちの1つ以上の伝導状態の変化によって、ノード241における全キャパシタンスを変化させることができる。例えば、スイッチ233の伝導状態は、コンデンサ223を対地端子に結合させるために、開から閉へ変更し得る。コンデンサ223の対地端子への結合により、コンデンサ223のキャパシタンスがノード241に追加される。別の例として、コンデンサ223を対地端子から結合解除させるために、スイッチ233の伝導状態を、閉から開へと変更させることができる。対地端子からのコンデンサ223の結合解除により、コンデンサ223のキャパシタンスが、ノード241から除かれる。

【0025】

スイッチ234〜236のうちの1つ以上の伝導状態の変化によって、ノード242における全キャパシタンスを変化させることができる。例えば、スイッチの伝導状態234は、コンデンサ224を対地端子に結合させるために、開から閉へ変更し得る。コンデンサ224の対地端子への結合により、コンデンサ224のキャパシタンスがノード242に追加される。別の例として、対地端子からコンデンサ224を結合解除させるために、スイッチの伝導状態234を、閉から開へ変更し得る。対地端子からのコンデンサ224の結合解除により、コンデンサ224のキャパシタンスが、ノード242から除かれる。

【0026】

ノード241〜242においてキャパシタンスを増加させるために、さらなるスイッチ231〜236を閉じることができ、ノード241〜242におけるキャパシタンスを減少させるために、さらなるスイッチ231〜236を開くことができる。さらなるスイッチ231〜236が開いている場合、最大周波数、最小周波数、中心周波数、およびクロック信号CLKOUT1およびCLKOUT2のためにVCO200が生成可能な他の周波数は増加する。さらなるスイッチ231〜236が閉じている場合、最大周波数、最小周波数、中心周波数、およびクロック信号CLKOUT1およびCLKOUT2のためにVCO200が生成可能な他の周波数は低下する。ノード241におけるキャパシタンスは、好適には、VCO200がその中心を通る垂直軸に対して対称となるように、ノード242におけるキャパシタンスと等しい。

【0027】

ノード241および対地端子の間で結合されるコンデンサ221〜223ならびにノード242および対地端子の間で結合されるコンデンサ224〜226は、VCO200の周波数調整範囲を決定する。スイッチ231〜236および金属オプション207〜208および212〜216の伝導状態の任意の特定のセットにおいて、VCO200の周波数調整範囲は、VCO200によって生成されたクロック信号CLKOUT1およびCLKOUT2の最大および最小周波数の間の差と等しい。特定の周波数調整範囲内のクロック信号CLKOUT1およびCLKOUT2の最大周波数は、バラクタ203〜206がそれらの最小キャパシタンス値である場合に生じる。特定の周波数調整範囲内のクロック信号CLKOUT1およびCLKOUT2の最小周波数は、バラクタ203〜206がそれらの最大キャパシタンス値である場合に生じる。各バラクタ203〜206のキャパシタンスは、バラクタにおいて印加された電圧と反比例する。

【0028】

ノード241〜242における固定キャパシタンスは、出力クロック信号CLKOUT1およびCLKOUT2のためにVCO200が生成する、最小周波数、最大周波数、中心周波数および周波数調整範囲を変化させるために、変更し得る。スイッチ231〜233のうちの1つ以上およびスイッチ234〜236のうちの1つ以上を閉じた後で、ノード241および242におけるキャパシタンスを増加させることにより、VCO200の最小周波数、最大周波数、中心周波数、および周波数調整範囲を縮小させる。ノード241〜242において切り替えられるコンデンサ221〜226は、調整可能なキャパシタンスを有しないため、VCO200の周波数調整範囲は、金属オプション212〜215が伝導性である場合に縮小する。コンデンサ221〜226は、固定荷重として作用する。金属オプション212〜215が全て伝導性である場合、VCO200が、CLKOUT1およびCLKOUT2のために生成する周波数調整範囲は、より多くの固定コンデンサ221〜226等がノード241〜242において切り替えられるため、より多くの量、縮小する。

【0029】

VCO200において、コンデンサ221〜226の上部プレートおよびスイッチ231〜236は、ノード241および242のそれぞれにおける全キャパシタンスを増加し得る寄生キャパシタンスを有する。これらの寄生キャパシタンスは、VCO200が、スイッチ231〜236および金属オプション207〜208および212〜216の伝導状態の任意の特定のセットにおいて、CLKOUT1およびCLKOUT2のために生成可能な最大周波数を制限する。例えば、コンデンサ221〜226の寄生キャパシタンスは、スイッチ231〜236の全てが開であり、かつ、金属オプションの全てが伝導性である場合に、CLKOUT1およびCLKOUT2の最大周波数を制限し得る。

【0030】

バラクタ203〜206のキャパシタンスは、出力クロック信号CLKOUT1およびCLKOUT2の周波数の微調整を生成するために、制御電圧VCLに応答して変動する。コンデンサ221〜226は、出力クロック信号CLKOUT1およびCLKOUT2の周波数の粗調整を生成させるために(つまり、バラクタによって生じるよりも大きい周波数の変化を生じさせるために)、スイッチ231〜236を使用して、ノード241〜242において、入および切に切り替えられる。

【0031】

VCO200は、金属オプション207〜208および212〜216を含む。金属オプション207〜208および212〜216は、VCO200内のコンダクタのほとんどを形成するために使用される伝導層とは異なる1つ以上のさらなる伝導層内に形成されるコンダクタを含む。金属オプションを形成するコンダクタは、1つ以上のさらなる伝導層内の集積回路ダイに任意で追加され得る。金属オプションは、金属または別の適した伝導材料を用いて、1つ以上のさらなる伝導層内に形成し得る。金属オプション207〜208および212〜216を形成するコンダクタのいずれかを、対応する金属オプション接続を作成または結合解除するために、さらなる伝導層のためのマスクへ追加、またはマスクから除去し得る。

【0032】

金属オプションを含むさらなる伝導層のマスクを、VCO200において他のコンダクタを含む1つ以上の伝導層のために各マスクを修正する必要なく、修正できる。この特徴により、VCO200内の伝導層を形成するために使用されるマスク層に作成する必要がある、修正の量および複雑さが低減される。そのため、金属オプション207〜208および212〜216は、露光プロセス中の集積回路ダイの作成に使用されるマスク層の修正コストを削減する。金属オプションは、さらに、他のマスクを再生成するためにさらに時間がかからないため、集積回路製品が市場に出るまでの時間を短縮する。マスクを利用して、ほぼ同一の発振回路アーキテクチャを有する、複数の集積回路ダイを作成し得る。発振回路アーキテクチャは、1つ以上のさらなる伝導層における金属オプション207〜208および212〜216の伝導性に関し、集積回路ダイの間に限って異なる。

【0033】

図3A〜3Bは、本発明の一実施形態に従う、金属オプションの例の上面図を示すプロセスレイアウト図である。図3A〜3Bに示される金属オプションは、図2に示される金属オプション207〜208および212〜215のそれぞれを実装するように使用可能な一実施形態である。図3A〜3Bに示される金属オプションは、一例にすぎず、本発明の範囲を制限することは意図されていない。図2に示される金属オプションを実装するために、他の種類の構成を使用することもできる。

【0034】

ある特定の実施例に従い、回路要素201〜211、221〜226、および231〜236を接続するルーティングコンダクタの大部分が、VCO200を含む集積回路ダイ上の第1の金属層に形成される。これらのルーティングコンダクタは、図2内の回路要素を接続する実線として示される。この例に従い、金属オプション207〜208および212〜216が、集積回路ダイの上の第2の金属層内に形成される。第1および第2の金属層は、異なる金属層である。集積回路ダイは、2つの金属層よりも多く(例:11の金属層)有し得る。本明細書に記載される第1および第2の金属層は、ダイ上の金属層のうちの任意の2つにし得る。

【0035】

図3Aは、第2の金属層内に形成されるルーティングコンダクタ303Aを示す。ルーティングコンダクタ303Aは、金属オプション207〜208および212〜215のうちの1つの例である。ルーティングコンダクタ304〜305は、第1の金属層内に形成される。第1の金属層は、VCO200内にルーティングコンダクタの大部分を含む。金属オプションは、ルーティングコンダクタ303Aを第2の金属層に追加することにより、ルーティングコンダクタ304および305を接続できる。ルーティングコンダクタ303Aは、ビア301を介して、ルーティングコンダクタ304に、およびビア302を介して、ルーティングコンダクタ305に結合される。

【0036】

金属オプションは、図3Bに示されるように、第2の金属層からルーティングコンクタ303Aの一部を除去することにより、ルーティングコンダクタ304および305を結合解除できる。図3Bは、第2の金属層内のコンダクタ303Aの一部である、コンダクタ303Bおよびコンダクタ303Cを示す。コンダクタ303Bおよび303Cは、コンダクタ303Bおよび303Cの間に結合解除部分があるため、コンダクタ304および305は共に結合しない。図3Bに示されるように、第2の金属層内のコンダクタ303Bおよび303Cがコンダクタ304および305を共に接続させない場合、金属オプション(例:207〜208および212〜215)は、開回路となる。

【0037】

図3A〜3Bの設定の間で、ルーティングコンダクタ303の形状を変更するために、第2の金属層を形成するために使用される露光マスクを修正し得る。第1の金属層のマスクまたは露光中に集積回路ダイ上にVCO200を形成するために使用される他の層のいずれかのためのマスクを変更せずに、第2の金属層のマスクを修正し得る。

【0038】

金属オプション216は、インダクタ209のコイルへ1つ以上の一巻きを追加する、またはインダクタ209のコイルから1つ以上の一巻きを除去できる。金属オプション216は、インダクタ209のコイル内の一巻きの数の変更に加えて、または、その代わりに、インダクタ209のコイルの1つ以上の一巻きの直径を大きくする、または、インダクタ209のコイルの1つ以上の一巻きの直径を小さくすることもできる。

【0039】

図3Cは、本発明の一実施形態に従う、インダクタ209の金属オプションの例の上面図を示す、プロセスレイアウト図である。図3Cは、外側の一巻きおよび内側の一巻きを有するインダクタ209のコイルを示す。コンダクタ311は、インダクタ209の外側の一巻きであり、コンダクタ312は、インダクタ209の内側の一巻きである。コンダクタ311〜312は、金属、または、代替的に、別の種類の伝導性材料で形成される。コンダクタ311は、第1の金属層内に形成され、コンダクタ312は、第2の金属層内に形成される。コンダクタ311および312は、交差313において互いに交差する。コンダクタ311は、入力ノード1および2に結合される。

【0040】

コンダクタ312は、金属オプション216の例である。コンダクタ312は、ビア314および315を介して、コンダクタ311に接続可能である。コンダクタ312は、内側の一巻きをインダクタ209の外側の一巻きへ接続するために、第2の金属層のためのマスクに追加できる。あるいは、コンダクタ312の一部または全てを、インダクタ209から内側の一巻きを除去する、または単に外側の一巻きから内側の一巻きを結合解除するために、第2の金属層のマスクから除去できる。インダクタ209のインダクタンスを増加させるために、内側の一巻き312を第2の金属層に追加し、また、外側の一巻き311に接続し得る。内側の一巻き312を、インダクタ209のインダクタンスを低下させるために、第2の金属層から除去する、または外側の一巻き311から結合解除できる。

【0041】

図3D〜3Eは、本発明の別の実施形態に従う、インダクタ209の金属オプションの例の上面図を示すプロセスレイアウト図である。コンダクタ321は、インダクタ209のコイルの一巻きにし得る。コンダクタ322は、インダクタ209のコイルの一巻きにすることもできる。VCO200のルーティングコンダクタは、第1の金属層に形成される。コンダクタ321〜322は、第2の金属層に形成される。VCO200のルーティングコンダクタのいくつかを、第3、第4等の金属層において形成し得る。

【0042】

コンダクタ321〜322は、金属オプション216の例である。コンダクタ321は、インダクタ209のコイルのより大きな直径の一巻きを形成するために、ダイの第2の金属層内に形成される。コンダクタ322が、インダクタ209のコイルのより小さい直径の一巻きを生成するために、ダイの第2の金属層内に形成される。コイルの1つ以上の一巻きの直径の変化は、インダクタ209のインダクタンスに影響する。コンダクタ321またはコンダクタ322のいずれかは、ノード1および2において第1の金属層内のインダクタ209(例:さらなるコイルの一巻き)のコンダクタに接続される。第2の金属層を作成するために使用されるマスクは、図3D〜3Eに示されるコイルの一巻きの直径の変化に影響するように修正される。

【0043】

インダクタ209は、そのコイル内に複数の一巻きを有し得る。しかしながら、図面の簡略化のために、図3D〜3Eのそれぞれでは、1つのみの一巻きが示されている。一実施形態に従い、インダクタ209のコイルの複数の一巻きの直径を、第2の伝導層内の対応するコンダクタの直径を変化させることにより、修正し得る。

【0044】

再び図2を参照すると、金属オプション207は、バラクタ203をノード241に接続する、またはノード241からバラクタ203を結合解除させることができる。金属オプション208は、バラクタ204をノード242に接続する、またはノード242からバラクタ204を結合解除させることができる。金属オプション207〜208は、VCO200の周波数調整範囲を増加させるために、それぞれ、ノード241〜242に、バラクタ203〜204を接続し得る。金属オプション207〜208は、VCO200の周波数調整範囲を縮小させるために、それぞれ、ノード241〜242からバラクタ203〜204を結合解除させることができる。上記のように、さらなる伝導層へ、ルーティングコンダクタの一部を追加するまたは追加しないことにより、金属オプション207〜208を実装し得る。バラクタ203および204がそれぞれ、ノード241〜242から結合解除される場合、ルーティングコンダクタは、ノード241〜242において、バラクタ203〜204によって導入される寄生キャパシタンスを減少させるために、金属オプション207〜208から除去される。

【0045】

金属オプション213は、コンデンサ222をノード241に接続させる、またはノード241からコンデンサ222を結合解除させることができる。金属オプション213が伝導性である場合、金属オプション212は、コンデンサ221をノード241に接続する、またはノード241からコンデンサ221を結合解除させることができる。金属オプション214は、コンデンサ225をノード242に接続する、またはコンデンサ225をノード242から結合解除し得る。金属オプション214が伝導性である場合、金属オプション215は、コンデンサ226をノード242に接続する、またはコンデンサ226をノード242から結合解除し得る。上記のように、金属オプション212〜215を、さらなる伝導層へ、ルーティングコンダクタの一部を追加する、または追加しないことにより、実装し得る。

【0046】

スイッチ231〜232および235〜236の伝導状態を変化させることによってダイを形成後、ダイがノード241〜242における固定キャパシタンスを調整するための柔軟性を有することが意図されている場合、金属オプション212〜215を伝導性にすることにより、特定の集積回路ダイ内において、ノード241〜242に余剰の固定コンデンサ221〜222および225〜226を結合し得る。例えば、金属オプション212〜215は、高いまたは低い周波数において機能するように意図されている発振器内で伝導性であり得る。

【0047】

高い周波数においてのみ機能するように意図されている発振器において、金属オプション212〜215は、ノード241〜242から使用されていない回路要素(例:コンデンサ221〜222、コンデンサ225〜226、スイッチ231〜232、およびスイッチ235〜236)を結合解除するために、第2の伝導層内における開回路にすることができ、それにより、ノード241および242における寄生キャパシタンスを減少させる。ノード241〜242における寄生キャパシタンスの減少により、VCO200によって、できるだけ大きなCLKOUT1およびCLKOUT2のための最大周波数、最小周波数、中心周波数、および周波数調整範囲を生成させる。例えば、コンデンサ221〜222および225〜226が集積回路ダイで使用することを意図されていない場合、ノード241および242における寄生キャパシタンスを減少させる開回路を作成するために、ダイから金属オプション213および214内のルーティングコンダクタを削除できる。

【0048】

別の例として、集積回路ダイにおいてコンデンサ222および225を使用し得るが、コンデンサ221および226がそのダイで使用されることを意図されていない場合、金属オプション213および214内のルーティングコンダクタは、コンデンサ222および225を、それぞれ、ノード241および242に接続させるために、ダイに追加され、金属オプション212および215内のルーティングコンダクタは、ノード241および242における寄生キャパシタンスを減少する開回路を作成するために、ダイから削除される。

【0049】

金属オプション216は、インダクタ209におけるコイルの不要な一巻きを除去することにより、ノード241および242における寄生キャパシタンスを減少できる。金属オプション216は、さらに、インダクタ209のインダクタンス値を変更するために使用し得る。上記の式(1)に基づき、インダクタ209のためのより小さなインダクタンス値は、VCO200の出力クロック信号CLKOUT1およびCLKOUT2の周波数が増加することを可能にする。VCO200の出力クロック信号の周波数における増加の大部分は、インダクタ209のインダクタンス値の変化の結果である。

【0050】

CLKOUT1およびCLKOUT2の周波数は、ノード241および242における寄生キャパシタンスの減少に応答して増加する。特に、CLKOUT1およびCLKOUT2の最大周波数、最小周波数、中心周波数、および周波数調整範囲は、全て、ノード241〜242における寄生キャパシタンスの減少に応答して、増加する。一例として、VCO200は、最高で秒あたり10〜11ギガバイト(Gbps)のCLKOUT1およびCLKOUT2のデータレートを生成し得る。この例は、本発明の範囲を制限することを意図するものではない。

【0051】

上述のように、VCO200は、CLKOUT1およびCLKOUT2のための複数の異なる周波数調整範囲を生成できる。金属オプション207〜208および212〜216が、使用されていない回路要素によって生じるノード241〜242における寄生キャパシタンスを減少させる場合に、VCO200内の寄生キャパシタンスは、CLKOUT1およびCLKOUT2の周波数調整範囲の縮小を生じさせる。従って、VCO200は、CLKOUT1およびCLKOUT2の小さいおよび大きい中心周波数において、幅広い周波数調整範囲をサポートできる。

【0052】

本発明の範囲を制限することが意図されていない特定の例を挙げると、VCO200は、VCO200によってサポートされる最小中心周波数の二倍であるCLKOUT1およびCLKOUT2の最大中心周波数をサポートできる。ノード241〜242において固定キャパシタンスを減少させるための金属オプション、バラクタの数、およびインダクタ209のサイズおよびインダクタンスを使用することにより、VCO200は、CLKOUT1およびCLKOUT2のためのより大きな周波数を生成できる。より高いデータレートにおいて、金属オプションは、より低いデータレート(つまり、5〜6Gbps)で必要な余剰のキャパシタンスおよび伝導電荷を除去するために使用される。

【0053】

本明細書に記載される金属オプションは、それぞれ、発振回路を有する複数の集積回路ダイを作成するために使用できる。集積回路ダイ内の発振回路は、上記のように、および、図に示されるように、1つ以上のさらなる伝導層内における金属オプションコンダクタ207〜208および212〜216の伝導性に関してのみ、互いに、アーキテクチャが異なる。各ダイ内の発振回路の間の差を作成するために、さらなる伝導層のみ(例:第2の金属層)が修正される。

【0054】

図4は、本発明の態様を含むことができるフィールドプログラマブルゲートアレイ(FPGA)400の略部分ブロック図である。FPGA400は、本発明の特徴を含むことができる集積回路の一例にすぎない。本発明の実施形態は、フィールドプログラマブルゲートアレイ(FPGA)、プログラマブル論理デバイス(PLD)、複雑なプログラマブル論理デバイス(CPLD)、プログラマブル論理アレイ(PLA)、および特定用途向け集積回路(ASIC)等の数多くの種類の集積回路で使用可能であることを理解されたい。

【0055】

FPGA400は、多様な長さおよび速度の、行および列の相互接続コンダクタのネットワークで相互接続される、プログラマブル論理アレイブロック(またはLAB)402の2次元アレイを含む。LAB402は、複数の(例えば、10の)論理要素(またはLE)を含む。

【0056】

LEは、ユーザ定義された論理機能の効率的な実装を行うプログラマブル論理回路ブロックである。FPGAは、種々の組み合わせおよびシーケンスの機能を実装するように構成可能な、多くの論理要素を有する。論理要素は、プログラマブル相互接続構造にアクセスできる。プログラマブル相互接続構造は、ほぼ任意の所望の構成における論理要素と相互接続するようにプログラムすることが可能である。

【0057】

FPGA400は、さらに、アレイ全体に提供される多様なサイズのランダムアクセスメモリ(RAM)ブロックを含む分散メモリ構造を含む。RAMブロックは、例えば、ブロック404、ブロック406、およびブロック408を含む。これらのメモリブロックは、さらに、シフトレジスタおよび先入れ先出し(FIFO)バッファを含むことができる。

【0058】

FPGA400は、さらに、例えば、加算または減算機能を有する乗算器を実装可能なデジタル信号処理(DSP)ブロック410を含む。この実施例において、チップの周辺に配置される入力/出力要素(IOE)412は、多数のシングルエンドおよび差分入力/出力基準(differential input/output standards)をサポートする。IOE412は、集積回路のパッドに連結される入力および出力バッファを含む。パッドは、例えば、FPGAおよび1つ以上の外部デバイスの間で入力信号、出力信号、および供給電圧を経路指定するように使用可能なFPGAダイの外部端子である。FPGA400は、例示の目的のために、本明細書に記載されているにすぎず、本発明は、多くの異なる種類のPLD、FPGA、およびASICで実装可能であることを理解されたい。

【0059】

本発明は、いくつかの構成要素のうちの1つとしてFPGAを有するシステムで実装することもできる。図5は、本発明の技術を具現化可能な例示的なデジタルシステム500のブロック図を示す。システム500は、プログラムされたデジタルコンピュータシステム、デジタル信号処理システム、専用のデジタル切り替えネットワーク、または他の処理システムにし得る。さらに、かかるシステムは、電気通信システム、自動車システム、制御システム、家庭用電化製品、パーソナルコンピュータ、インターネット通信およびネットワーキング等の幅広い種類の応用のために設計し得る。さらに、システム500は、単一ボード上、複数ボード上、または複数の筐体内に提供可能である。

【0060】

システム500は、1つ以上のバスで相互結合される処理装置502、メモリ装置504、および入力/出力(I/O)装置506を含む。この例示的な実施形態に従い、FPGA508は、処理装置502に埋め込まれる。FPGA508は、図5のシステム内の多くの異なる目的に役立つことができる。FPGA508は、例えば、その内部および外部動作をサポートする、処理装置502の論理ビルディングブロックにし得る。FPGA508は、システム動作におけるその特定の役割を実行するために必要な論理機能を実装するようにプログラムされる。FPGA508は、特に、接続510によってメモリ504へ、また、接続512によって、I/O装置506へ連結可能である。

【0061】

処理装置502は、処理または格納のために、適切なシステム構成要素にデータを送信し、メモリ504に格納されたプログラムを実行し、I/O装置506、または他の同様の機能を介して、データを送受信できる。処理装置502は、コントローラ、ネットワークコントローラ、または任意の種類のプロセッサまたはコントローラとして使用されるようにプログラムされた、中央処理装置(CPU)、マイクロプロセッサ、浮動小数点コプロセッサ、グラフィックコプロセッサ、ハードウェアコントローラ、マイクロコントローラ、フィールドプログラマブルゲートアレイにし得る。さらに、多くの実施形態において、多くの場合、CPUは不要である。

【0062】

例えば、CPUの代わりに、1つ以上のFPGA508が、システムの論理動作を制御可能である。別の例として、FPGA508は、特定のコンピューティングタスクを取り扱うために必要なように再プログラム可能な、再構成可能なプロセッサとして機能する。あるいは、FPGA508は、それ自体に、埋め込みマイクロプロセッサを含むことができる。メモリ装置504は、ランダムアクセスメモリ(RAM)、読み込み専用メモリ(ROM)、固定またはフレキシブルディスク媒体、フラッシュメモリ、テープ、または任意の他の格納手段、あるいはこれらの格納手段の任意の組み合わせにし得る。

【0063】

本発明の例示的な実施形態の上記の記載は、例示および説明の目的で示されている。上記の記載は、包括的、または、本発明を本明細書に開示された実施例に制限することを意図していない。いくつかの例において、本発明の特徴は、記載されているように、他の特徴の対応する利用なしに利用し得る。本発明の範囲から逸脱せずに、上記の教示に照らして、多くの修正、置換、および変形が可能である。

【特許請求の範囲】

【請求項1】

第1の伝導層内の複数のルーティングコンダクタを介してクロス結合された複数の第1のトランジスタと、

第1のバラクタと、

第1のコンデンサと、

第2の伝導層内の第1のオプションコンダクタであって、前記第1のオプションコンダクタは、前記発振回路内のノードにおける寄生キャパシタンスを低減するために、前記発振回路内の前記ノードから、前記第1のコンデンサおよび前記第1のバラクタのうちの一方を結合解除することをオプションとして行う、第1のオプションコンダクタと、

前記第1の伝導層内の複数のルーティングコンダクタを介して前記複数の第1のトランジスタに結合されたインダクタと

を含む発振回路であって、

前記第2の伝導層内の第2のオプションコンダクタは、前記インダクタの第1の一巻きを形成し、前記インダクタの第2の一巻きは、前記第1の伝導層内に形成され、前記第2のオプションコンダクタは、前記インダクタのインダクタンスを変更するために用いられる、発振回路。

【請求項2】

前記第1の伝導層内の複数のルーティングコンダクタを介して前記第1のコンデンサに結合された第1のスイッチと、

第2のコンデンサと、

前記第1の伝導層内の複数のルーティングコンダクタを介して前記第2のコンデンサに結合された第2のスイッチと、

前記第2のコンデンサと前記第1のコンデンサとの間の接続の少なくとも一部を形成する前記第2の伝導層内の第3のオプションコンダクタと

をさらに含む、請求項1に記載の発振回路。

【請求項3】

第3のコンデンサと、

前記第1の伝導層内の複数のルーティングコンダクタを介して前記第3のコンデンサに結合された第3のスイッチと、

前記第3のコンデンサと前記複数の第1のトランジスタとの間の接続の少なくとも一部を形成する前記第2の伝導層内の第4のオプションコンダクタと

をさらに含む、請求項2に記載の発振回路。

【請求項4】

第4のコンデンサと、

前記第1の伝導層内の複数のルーティングコンダクタを介して前記第4のコンデンサに結合された第4のスイッチと、

前記第4のコンデンサと前記第3のコンデンサとの間の接続の少なくとも一部を形成する前記第2の伝導層内の第5のオプションコンダクタと

をさらに含む、請求項3に記載の発振回路。

【請求項5】

第2のバラクタと、

前記第2のバラクタと前記複数の第1のトランジスタとの間の接続の少なとも一部を形成する前記第2の伝導層内の第3のオプションコンダクタと

をさらに含む、請求項1に記載の発振回路。

【請求項6】

前記発振回路は、プログラマブル論理集積回路上に製造される、請求項1に記載の発振回路。

【請求項7】

複数の第2のトランジスタをさらに含み、前記複数の第2のトランジスタは、互いにクロス結合されており、前記第1の伝導層内の複数のルーティングコンダクタを介して、第2のバラクタに結合されている、請求項1に記載の発振回路。

【請求項8】

発振回路を含む集積回路であって、前記発振回路は、

第1の伝導層内で複数の第1のルーティングコンダクタの第1のサブセットを介してクロス結合された複数の第1のトランジスタと、第1のバラクタと、第1のコンデンサと、前記複数の第1のルーティングコンダクタのうちの1つを介して前記複数の第1のトランジスタに結合されたインダクタとを含み、

第2の伝導層内の第2のルーティングコンダクタは、前記インダクタの第1の一巻きを形成し、前記インダクタの第2の一巻きは、前記第1の伝導層内に形成され、前記インダクタの前記第1の一巻きは、前記インダクタのインダクタンスを変更するために用いられるオプションコンダクタである、集積回路。

【請求項9】

前記第2の伝導層内の第1の開回路は、前記第1のコンデンサを通る電流を阻止し、前記第2の伝導層内の第2の開回路は、前記第1のバラクタを通る電流を阻止する、請求項8に記載の集積回路。

【請求項10】

前記発振回路は、第2のコンデンサをさらに含み、前記第2の伝導層内の第3のルーティングコンダクタは、前記複数の第1のトランジスタと前記第1のコンデンサとの間の接続の一部を形成し、前記第2の伝導層内の第1の開回路は、前記第2のコンデンサを通る電流を阻止する、請求項8に記載の集積回路。

【請求項11】

前記発振回路は、第3のコンデンサをさらに含み、前記第2の伝導層内の第2の開回路は、前記第3のコンデンサを通る電流を阻止する、請求項10に記載の集積回路。

【請求項12】

前記発振回路は、複数の第2のトランジスタをさらに含み、前記複数の第2のトランジスタは、クロス結合され、前記複数の第1のルーティングコンダクタの第2のサブセットを介して前記複数の第1のトランジスタに結合されている、請求項8に記載の集積回路。

【請求項13】

前記発振回路は、第2のバラクタをさらに含み、第3のルーティングコンダクタは、前記複数の第1のトランジスタと前記第1のバラクタとの間の接続の一部を形成し、前記第2の伝導層内の第1の開回路は、前記第2のバラクタを通る電流を阻止する、請求項8に記載の集積回路。

【請求項14】

前記発振回路は、第2のバラクタおよび第3のバラクタをさらに含み、前記第2のバラクタおよび前記第3のバラクタは、前記複数の第1のルーティングコンダクタの第2のサブセットを介して前記複数の第1のトランジスタに結合され、第1の開回路は、前記第1のバラクタを通る電流を阻止する、請求項8に記載の集積回路。

【請求項15】

発振回路であって、前記発振回路は、

第1の伝導層内に形成された複数のルーティングコンダクタを介してクロス結合された複数の第1のトランジスタと、

前記複数の第1のトランジスタに結合された第1のコンデンサと、

前記複数のルーティングコンダクタのうちの1つを介して前記複数の第1のトランジスタに結合されたインダクタと、

前記インダクタの第1の一巻きを形成する第1のオプションコンダクタと

を含み、

前記インダクタの第2の一巻きは、前記第1の伝導層内に形成され、前記第1のオプションコンダクタは、前記第1の伝導層とは異なる第2の伝導層内にあり、前記第1のオプションコンダクタは、前記インダクタのインダクタンスを変更するために用いられる、発振回路。

【請求項16】

第1のバラクタと、

前記複数の第1のトランジスタと前記第1のバラクタとの間の接続の少なくとも一部を形成する、前記第2の伝導層内の第2のオプションコンダクタであって、前記第2のオプションコンダクタは、前記複数のルーティングコンダクタのうちの1つに結合されている、第2のオプションコンダクタと

をさらに含む、請求項15に記載の集積回路。

【請求項17】

第2のバラクタと、

前記複数の第1のトランジスタと前記第2のバラクタとの間の接続の少なくとも一部を形成する、前記第2の伝導層内の第3のオプションコンダクタであって、前記第3のオプションコンダクタは、前記複数のルーティングコンダクタのうちの1つに結合されている、第3のオプションコンダクタと

をさらに含む、請求項16に記載の発振回路。

【請求項18】

第2のコンデンサと、

前記複数の第1のトランジスタと前記第2のコンデンサとの間の接続の少なくとも一部を形成する、前記第2の伝導層内の第2のオプションコンダクタであって、前記第2のプションコンダクタは、前記複数のルーティングコンダクタのうちの1つに結合されている、第2のオプションコンダクタと

をさらに含む、請求項15に記載の発振回路。

【請求項19】

発振器を形成するための方法であって、前記方法は、

第1のスイッチを第1の伝導層内の複数のルーティングコンダクタを介して第1のコンデンサに結合することと、

第2のスイッチを前記第1の伝導層内の複数のルーティングコンダクタを介して第2のコンデンサに結合することと、

前記第1の伝導層内の複数のルーティングコンダクタを介して複数の第1のトランジスタにインダクタを結合することと、

前記インダクタの第1の一巻きを形成する第2の伝導層内のオプションコンダクタを用いて、前記インダクタのインダクタンスを変更することであって、前記インダクタの第2の一巻きは、前記第1の伝導層内に形成される、ことと

を含む、方法。

【請求項20】

前記第1の伝導層内の複数のルーティングコンダクタを介して第3のコンデンサに第3のスイッチを結合すること

をさらに含む、請求項19に記載の方法。

【請求項1】

第1の伝導層内の複数のルーティングコンダクタを介してクロス結合された複数の第1のトランジスタと、

第1のバラクタと、

第1のコンデンサと、

第2の伝導層内の第1のオプションコンダクタであって、前記第1のオプションコンダクタは、前記発振回路内のノードにおける寄生キャパシタンスを低減するために、前記発振回路内の前記ノードから、前記第1のコンデンサおよび前記第1のバラクタのうちの一方を結合解除することをオプションとして行う、第1のオプションコンダクタと、

前記第1の伝導層内の複数のルーティングコンダクタを介して前記複数の第1のトランジスタに結合されたインダクタと

を含む発振回路であって、

前記第2の伝導層内の第2のオプションコンダクタは、前記インダクタの第1の一巻きを形成し、前記インダクタの第2の一巻きは、前記第1の伝導層内に形成され、前記第2のオプションコンダクタは、前記インダクタのインダクタンスを変更するために用いられる、発振回路。

【請求項2】

前記第1の伝導層内の複数のルーティングコンダクタを介して前記第1のコンデンサに結合された第1のスイッチと、

第2のコンデンサと、

前記第1の伝導層内の複数のルーティングコンダクタを介して前記第2のコンデンサに結合された第2のスイッチと、

前記第2のコンデンサと前記第1のコンデンサとの間の接続の少なくとも一部を形成する前記第2の伝導層内の第3のオプションコンダクタと

をさらに含む、請求項1に記載の発振回路。

【請求項3】

第3のコンデンサと、

前記第1の伝導層内の複数のルーティングコンダクタを介して前記第3のコンデンサに結合された第3のスイッチと、

前記第3のコンデンサと前記複数の第1のトランジスタとの間の接続の少なくとも一部を形成する前記第2の伝導層内の第4のオプションコンダクタと

をさらに含む、請求項2に記載の発振回路。

【請求項4】

第4のコンデンサと、

前記第1の伝導層内の複数のルーティングコンダクタを介して前記第4のコンデンサに結合された第4のスイッチと、

前記第4のコンデンサと前記第3のコンデンサとの間の接続の少なくとも一部を形成する前記第2の伝導層内の第5のオプションコンダクタと

をさらに含む、請求項3に記載の発振回路。

【請求項5】

第2のバラクタと、

前記第2のバラクタと前記複数の第1のトランジスタとの間の接続の少なとも一部を形成する前記第2の伝導層内の第3のオプションコンダクタと

をさらに含む、請求項1に記載の発振回路。

【請求項6】

前記発振回路は、プログラマブル論理集積回路上に製造される、請求項1に記載の発振回路。

【請求項7】

複数の第2のトランジスタをさらに含み、前記複数の第2のトランジスタは、互いにクロス結合されており、前記第1の伝導層内の複数のルーティングコンダクタを介して、第2のバラクタに結合されている、請求項1に記載の発振回路。

【請求項8】

発振回路を含む集積回路であって、前記発振回路は、

第1の伝導層内で複数の第1のルーティングコンダクタの第1のサブセットを介してクロス結合された複数の第1のトランジスタと、第1のバラクタと、第1のコンデンサと、前記複数の第1のルーティングコンダクタのうちの1つを介して前記複数の第1のトランジスタに結合されたインダクタとを含み、

第2の伝導層内の第2のルーティングコンダクタは、前記インダクタの第1の一巻きを形成し、前記インダクタの第2の一巻きは、前記第1の伝導層内に形成され、前記インダクタの前記第1の一巻きは、前記インダクタのインダクタンスを変更するために用いられるオプションコンダクタである、集積回路。

【請求項9】

前記第2の伝導層内の第1の開回路は、前記第1のコンデンサを通る電流を阻止し、前記第2の伝導層内の第2の開回路は、前記第1のバラクタを通る電流を阻止する、請求項8に記載の集積回路。

【請求項10】

前記発振回路は、第2のコンデンサをさらに含み、前記第2の伝導層内の第3のルーティングコンダクタは、前記複数の第1のトランジスタと前記第1のコンデンサとの間の接続の一部を形成し、前記第2の伝導層内の第1の開回路は、前記第2のコンデンサを通る電流を阻止する、請求項8に記載の集積回路。

【請求項11】

前記発振回路は、第3のコンデンサをさらに含み、前記第2の伝導層内の第2の開回路は、前記第3のコンデンサを通る電流を阻止する、請求項10に記載の集積回路。

【請求項12】

前記発振回路は、複数の第2のトランジスタをさらに含み、前記複数の第2のトランジスタは、クロス結合され、前記複数の第1のルーティングコンダクタの第2のサブセットを介して前記複数の第1のトランジスタに結合されている、請求項8に記載の集積回路。

【請求項13】

前記発振回路は、第2のバラクタをさらに含み、第3のルーティングコンダクタは、前記複数の第1のトランジスタと前記第1のバラクタとの間の接続の一部を形成し、前記第2の伝導層内の第1の開回路は、前記第2のバラクタを通る電流を阻止する、請求項8に記載の集積回路。

【請求項14】

前記発振回路は、第2のバラクタおよび第3のバラクタをさらに含み、前記第2のバラクタおよび前記第3のバラクタは、前記複数の第1のルーティングコンダクタの第2のサブセットを介して前記複数の第1のトランジスタに結合され、第1の開回路は、前記第1のバラクタを通る電流を阻止する、請求項8に記載の集積回路。

【請求項15】

発振回路であって、前記発振回路は、

第1の伝導層内に形成された複数のルーティングコンダクタを介してクロス結合された複数の第1のトランジスタと、

前記複数の第1のトランジスタに結合された第1のコンデンサと、

前記複数のルーティングコンダクタのうちの1つを介して前記複数の第1のトランジスタに結合されたインダクタと、

前記インダクタの第1の一巻きを形成する第1のオプションコンダクタと

を含み、

前記インダクタの第2の一巻きは、前記第1の伝導層内に形成され、前記第1のオプションコンダクタは、前記第1の伝導層とは異なる第2の伝導層内にあり、前記第1のオプションコンダクタは、前記インダクタのインダクタンスを変更するために用いられる、発振回路。

【請求項16】

第1のバラクタと、

前記複数の第1のトランジスタと前記第1のバラクタとの間の接続の少なくとも一部を形成する、前記第2の伝導層内の第2のオプションコンダクタであって、前記第2のオプションコンダクタは、前記複数のルーティングコンダクタのうちの1つに結合されている、第2のオプションコンダクタと

をさらに含む、請求項15に記載の集積回路。

【請求項17】

第2のバラクタと、

前記複数の第1のトランジスタと前記第2のバラクタとの間の接続の少なくとも一部を形成する、前記第2の伝導層内の第3のオプションコンダクタであって、前記第3のオプションコンダクタは、前記複数のルーティングコンダクタのうちの1つに結合されている、第3のオプションコンダクタと

をさらに含む、請求項16に記載の発振回路。

【請求項18】

第2のコンデンサと、

前記複数の第1のトランジスタと前記第2のコンデンサとの間の接続の少なくとも一部を形成する、前記第2の伝導層内の第2のオプションコンダクタであって、前記第2のプションコンダクタは、前記複数のルーティングコンダクタのうちの1つに結合されている、第2のオプションコンダクタと

をさらに含む、請求項15に記載の発振回路。

【請求項19】

発振器を形成するための方法であって、前記方法は、

第1のスイッチを第1の伝導層内の複数のルーティングコンダクタを介して第1のコンデンサに結合することと、

第2のスイッチを前記第1の伝導層内の複数のルーティングコンダクタを介して第2のコンデンサに結合することと、

前記第1の伝導層内の複数のルーティングコンダクタを介して複数の第1のトランジスタにインダクタを結合することと、

前記インダクタの第1の一巻きを形成する第2の伝導層内のオプションコンダクタを用いて、前記インダクタのインダクタンスを変更することであって、前記インダクタの第2の一巻きは、前記第1の伝導層内に形成される、ことと

を含む、方法。

【請求項20】

前記第1の伝導層内の複数のルーティングコンダクタを介して第3のコンデンサに第3のスイッチを結合すること

をさらに含む、請求項19に記載の方法。

【図1】

【図3】

【図4】

【図5】

【図2】

【図3】

【図4】

【図5】

【図2】

【公開番号】特開2013−102456(P2013−102456A)

【公開日】平成25年5月23日(2013.5.23)

【国際特許分類】

【出願番号】特願2012−275471(P2012−275471)

【出願日】平成24年12月18日(2012.12.18)

【分割の表示】特願2011−531098(P2011−531098)の分割

【原出願日】平成21年10月5日(2009.10.5)

【出願人】(597154922)アルテラ コーポレイション (163)

【氏名又は名称原語表記】Altera Corporation

【Fターム(参考)】

【公開日】平成25年5月23日(2013.5.23)

【国際特許分類】

【出願日】平成24年12月18日(2012.12.18)

【分割の表示】特願2011−531098(P2011−531098)の分割

【原出願日】平成21年10月5日(2009.10.5)

【出願人】(597154922)アルテラ コーポレイション (163)

【氏名又は名称原語表記】Altera Corporation

【Fターム(参考)】

[ Back to top ]