発振回路及び発振器

【課題】発振子と発振回路とのインピーダンス整合を容易にとることができる発振回路及び発振器を提供する。

【解決手段】発振回路100が、第1の入力端子4と、第1の出力端子5と、第1の入力端子4に接続される信号調整部10と、第1の入力端子4及び第1の出力端子5に接続される信号形成部20と、を含み、該信号調整部は、第1の素子13、第1の抵抗11、第2の抵抗12及び第1のコンデンサー14を有し、第1の素子13は、一方端が第1の入力端子4に接続され、他の一方端が第1の抵抗11の一方端、第2の抵抗の一方端及び第1のコンデンサーの一方端に接続され、第1の抵抗は、他の一方端が第1の電源2に接続され、第2の抵抗は、他の一方端が第2の電源3に接続され、第1のコンデンサーは、他の一方端が第2の電源に接続され、該信号形成部において、第1の出力端子から出力される信号は、第1の入力端子から入力された信号を基に形成される。

【解決手段】発振回路100が、第1の入力端子4と、第1の出力端子5と、第1の入力端子4に接続される信号調整部10と、第1の入力端子4及び第1の出力端子5に接続される信号形成部20と、を含み、該信号調整部は、第1の素子13、第1の抵抗11、第2の抵抗12及び第1のコンデンサー14を有し、第1の素子13は、一方端が第1の入力端子4に接続され、他の一方端が第1の抵抗11の一方端、第2の抵抗の一方端及び第1のコンデンサーの一方端に接続され、第1の抵抗は、他の一方端が第1の電源2に接続され、第2の抵抗は、他の一方端が第2の電源3に接続され、第1のコンデンサーは、他の一方端が第2の電源に接続され、該信号形成部において、第1の出力端子から出力される信号は、第1の入力端子から入力された信号を基に形成される。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、水晶振動子、SAW共振子及びセラミック発振子などの発振子に用いられる発振回路、及び、発振子と発振回路とを有する発振器に関する。

【背景技術】

【0002】

従来、発振器は、水晶振動子、SAW共振子及びセラミック振動子などの発振子と発振回路とが組み合わされたもので、機器の制御に用いるためのタイミング信号(クロック信号)を生成する用途などに使用される。発振回路は、発振子から発振される信号の変化の中から所定の周波数の信号を増幅すると共に発振子に対して適切な信号の帰還を行い、発振子の恒常的な発振の制御を行うものである。

【0003】

発振子は所定の周波数による主振動以外にも副振動(以降、発生する要因に関わらず主振動以外のものを総じて副振動と呼ぶことにする)を生じる場合があり、発振回路から出力されるクロック信号が主振動の周波数成分と副振動の周波数成分とが合成されたものとなる場合がある。副振動は、例えば水晶発振子はそのカットの仕方によって発生するもの、発振子の出力インピーダンスと発振回路の入力インピーダンスの整合が取られていないことによる信号の反射などにより生じる場合がある。

【0004】

図8に、発振回路の一例として発振回路Aを示し、発振回路Aの発振用トランジスターTrのベース振幅波形と出力Voutの振幅波形を図9−(a)に示す。発振回路Aには、発振子XTALが接続されている。図9−(b)は、発振用トランジスターTrのベース振幅波形及び出力Voutの振幅波形の高速フーリエ変換(Fast Fourier Transform)結果である。図9−(b)の結果により、図9−(a)の信号に見られる周期の乱れは、主振動による245MHzの周波数成分と副振動の142MHzの周波数成分が合成されたことによることが分かる。機器の制御を行うためには副振動による周波数の成分の影響が極力出力Voutに出ないことが好ましい。

【0005】

発振子のカット状態が要因の副振動における周波数成分を抑制するために、特許文献1には、発振用トランジスターのエミッタ・コレクタ間又はエミッタ・ベース間に、コンデンサー、インダクター及びコンデンサーからなるリアクタンス回路を設けることが記載されている。エミッタ・ベース間にリアクタンス回路Cを配置した発振回路Bを図10に示す。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開2010−41346号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

しかしながら、特許文献1における方法では、発振子と発振回路との間のインピーダンスの不整合が原因となって発生する副振動の低減をすることが難しいという問題がある。

【課題を解決するための手段】

【0008】

本発明は、上述した問題若しくは課題の少なくともひとつを解決するためになされたものであり、以下の適用例若しくは実施形態として実現することが可能である。

【0009】

[適用例1]

本適用例にかかる発振回路は、第1の入力端子と、第1の出力端子と、前記第1の入力端子に接続される信号調整部と、前記第1の入力端子及び前記第1の出力端子に接続される信号形成部と、を含み、前記信号調整部は、第1の素子、第1の抵抗、第2の抵抗及び第1のコンデンサーを有し、前記第1の素子は、一方端が前記第1の入力端子に接続され、他の一方端が前記第1の抵抗の一方端、前記第2の抵抗の一方端及び前記第1のコンデンサーの一方端に接続され、前記第1の抵抗は、他の一方端が第1の電源に接続され、前記第2の抵抗は、他の一方端が第2の電源に接続され、前記第1のコンデンサーは、他の一方端が前記第2の電源に接続され、前記信号形成部において、前記第1の出力端子から出力される信号は、前記第1の入力端子から入力された信号を基に形成されることを特徴とする。

【0010】

この構成によれば、信号調整部が第1の入力端子に接続され、信号形成部が第1の入力端子及び第1の出力端子に接続されていることで、外部から第1の入力端子に接続される装置(以降第1の装置と記載する)とのインピーダンス整合を信号形成部の回路変更をすることなく、信号調整部において行うことができる。これにより、インピーダンスの不整合が原因となって発生する副振動の低減を図ることができる。

【0011】

上記の第1の電源は例えばVCC電源でよく、上記の第2の電源は例えばGNDでよい。上記したが、信号調整部は、第1の素子、第1の抵抗、第2の抵抗及び第1のコンデンサーを有し、第1の素子は、一方端が第1の入力端子に接続され、他の一方端が第1の抵抗の一方端、第2の抵抗の一方端及び第1のコンデンサーの一方端に接続され、第1の抵抗は、他の一方端が第1の電源に接続され、第2の抵抗は、他の一方端が第2の電源に接続され、第1のコンデンサーは、他の一方端が第2の電源に接続されている。この構成により、信号調整部は信号形成部に対するバイアス電圧を設定する機能を有するが、第1の抵抗と第2の抵抗とにより分圧されたポイントに第1の素子を介して第1の入力端子が接続されているため、第1の素子におけるインピーダンスを調整することで、容易に第1の装置とのインピーダンスの整合を取ることができる。また、第1のコンデンサーは、第1の電源及び第2の電源のノイズを原因とする変動による信号形成部に対する影響を軽減する効果を有する。第1の装置は、例えば、水晶発振子であり、SAW共振子であり、セラミック振動子である。

【0012】

[適用例2]

上記適用例にかかる発振回路のひとつは、前記第1の素子は、抵抗であることが好ましい。

【0013】

この構成によれば、第1の素子として抵抗を用いることができる。適切なインピーダンスを有する抵抗を用いることで、信号形成部に対する適切なバイアス電圧を維持しながら第1の装置とのインピーダンス整合を容易にとることができる。

【0014】

[適用例3]

上記適用例にかかる発振回路のひとつは、前記第1の素子は、インダクターであることが好ましい。

【0015】

この構成によれば、第1の素子としてインダクターを用いることができる。適切なインピーダンスを有するインダクターを用いることで、信号形成部に対する適切なバイアス電圧を維持しながら第1の装置とのインピーダンス整合を容易にとることができる。

【0016】

[適用例4]

上記適用例にかかる発振回路のひとつは、前記第1の素子は、抵抗とインダクターとを直列に接続したものであることが好ましい。

【0017】

この構成によれば、第1の素子に抵抗とインダクターとを直列に接続したものをもちいることができる。適切なインピーダンスを有する抵抗及び適切なインピーダンスを有するインダクターを用いることで、信号形成部に対する適切なバイアス電圧を維持しながら第1の装置とのインピーダンス整合を容易にとることができる。

【0018】

[適用例5]

上記適用例にかかる発振回路のひとつは、前記第1の素子は、抵抗とインダクターとを並列に接続したものであることが好ましい。

【0019】

この構成によれば、第1の素子は、抵抗とインダクターとを並列に接続したものであることが好ましい。適切なインピーダンスを有する抵抗及び適切なインピーダンスを有するインダクターを用いることで、信号形成部に対する適切なバイアス電圧を維持しながら第1の装置とのインピーダンス整合を容易にとることができる。

【0020】

[適用例6]

本適用例にかかる発振器は、第1の入力端子と、第1の出力端子と、第1の入力端子に接続される信号発振部と、前記信号発振部から出力される第1の発振信号が伝搬される第1の信号線に接続される信号調整部と、前記第1の信号線及び前記第1の出力端子に接続される信号形成部と、を含み、前記信号発振部は、第1の発振子を有し、前記第1の発振子の発振周波数を制御するための所定の電圧が前記第1の入力端子に印加され、前記信号調整部は、第1の素子、第1の抵抗、第2の抵抗及び第1のコンデンサーを有し、前記第1の素子は、一方端が前記第1の信号線に接続され、他の一方端が前記第1の抵抗の一方端、前記第2の抵抗の一方端及び前記第1のコンデンサーの一方端に接続され、前記第1の抵抗は、他の一方端が第1の電源に接続され、前記第2の抵抗は、他の一方端が第2の電源に接続され、前記第1のコンデンサーは、他の一方端が前記第2の電源に接続され、前記信号形成部において、前記第1の出力端子から出力される信号は、前記第1の信号線により伝搬された信号を基に形成されることを特徴とする。

【0021】

この構成によれば、発振器に信号発振部、信号調整部及び信号形成部が含まれ、信号調整部が、第1の素子、第1の抵抗、第2の抵抗及び第1のコンデンサーを有し、第1の素子は、一方端が第1の信号線に接続され、他の一方端が第1の抵抗の一方端、第2の抵抗の一方端及び第1のコンデンサーの一方端に接続され、第1の抵抗は、他の一方端が第1の電源に接続され、第2の抵抗は、他の一方端が第2の電源に接続され、第1のコンデンサーは、他の一方端が第2の電源に接続されていることで、信号発振部の出力インピーダンスと信号調整部及び信号形成部との入力インピーダンスとの整合を信号調整部においてとることができる。第1の電源は例えばVCC電源でよく、第2の電源は例えばGNDでよい。この構成により、信号調整部は信号形成部に対するバイアス電圧を設定する機能を有するが、第1の抵抗と第2の抵抗とにより分圧されたポイントに第1の素子を介して第1の信号線が接続されているため、第1の素子の特性を調整することにより、容易に信号発振部とのインピーダンスの整合を取ることができる。

【0022】

[適用例7]

上記適用例にかかる発振器のひとつは、前記第1の素子は、抵抗であることを特徴とする。

【0023】

この構成によれば、第1の素子として抵抗を用いることができる。適切なインピーダンスを有する抵抗を用いることで、信号形成部に対する適切なバイアス電圧を維持しながら第1の装置とのインピーダンス整合を容易にとることができる。

【0024】

[適用例8]

上記適用例にかかる発振器のひとつは、前記第1の素子は、インダクターであることを特徴とする。

【0025】

この構成によれば、第1の素子としてインダクターを用いることができる。適切なインピーダンスを有するインダクターを用いることで、信号形成部に対する適切なバイアス電圧を維持しながら第1の装置とのインピーダンス整合を容易にとることができる。

【0026】

[適用例9]

上記適用例にかかる発振器のひとつは、前記第1の素子は、抵抗とインダクターとを直列に接続したものであることを特徴とする。

【0027】

この構成によれば、第1の素子に抵抗とインダクターとを直列に接続したものをもちいることができる。適切なインピーダンスを有する抵抗及び適切なインピーダンスを有するインダクターを用いることで、信号形成部に対する適切なバイアス電圧を維持しながら第1の装置とのインピーダンス整合を容易にとることができる。

【0028】

[適用例10]

上記適用例にかかる発振器のひとつは、前記第1の素子は、抵抗とインダクターとを並列に接続したものであることを特徴とする。

【0029】

この構成によれば、第1の素子は、抵抗とインダクターとを並列に接続したものであることが好ましい。適切なインピーダンスを有する抵抗及び適切なインピーダンスを有するインダクターを用いることで、信号形成部に対する適切なバイアス電圧を維持しながら第1の装置とのインピーダンス整合を容易にとることができる。

【図面の簡単な説明】

【0030】

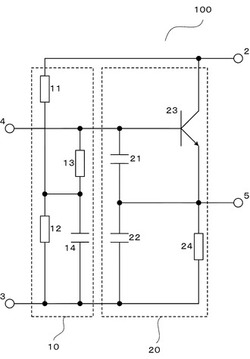

【図1】発振回路(第1実施形態)の回路ブロック図。

【図2】発振回路(第1実施形態)の使用例と振幅波形。

【図3】発振回路(第1実施形態)の変形使用例。

【図4】発振回路(第1実施形態)の変形例。

【図5】発振回路(第1実施形態)の変形例。

【図6】発振回路(第1実施形態)の変形例。

【図7】発振回路(第2実施形態)の回路ブロック図。

【図8】従来技術における発振回路の回路ブロック図。

【図9】従来技術における発振回路の振幅波形。

【図10】従来技術における発振回路の回路ブロック図。

【発明を実施するための形態】

【0031】

以下、図を用いて本発明の実施形態について説明する。

【0032】

(第1実施形態)

図1に、本発明を適用した発振回路100を示す、発振回路100は、信号調整部10及び信号形成部20を含む。また、発振回路100は、第1の入力端子4、第1の出力端子5、第1の電源端子2及び第2の電源端子3を有する。第1の電源端子2は正電源電圧(Vcc)が供給され、第2の電源端子3はGndに接続される。発振子は、第1の入力端子4と第2の電源端子3の間に接続される。発振子50を接続した状態の模式図を図2−(a)に示す。

【0033】

信号調整部10は、第1の素子13、第1の抵抗11、第2の抵抗12及び第1のコンデンサー14を有する。図1から分かるように、本実施形態における第1の素子13は抵抗素子である。第1の素子13の一方端は第1の入力端子4に接続されている。第1の素子13の他の一方端は第1の抵抗11の一方端、第2の抵抗12の一方端及び第1のコンデンサー14の一方端に接続されている。第1の抵抗11の他の一方端はVccに接続されている。第2の抵抗12の他の一方端及び第1のコンデンサー14の他の一方端はいずれもGndに接続されている。第1のコンデンサー14は、第1の抵抗11と第2の抵抗12とによる分圧点のAC成分による変動を押さえ、Vccにのったノイズ等による影響を軽減する役割を有する。

【0034】

信号形成部20は、第2のコンデンサー21、第3のコンデンサー22、第1のトランジスター23及び第3の抵抗24を有し、第1のトランジスター23のエミッターが第1の出力端子5に接続されており、いわゆるコルビッツ型発振回路の構成を有する。第1のトランジスター23のベースには第1の入力端子4が接続されている。

【0035】

信号調整部10は、第1のトランジスター23のベースのバイアス点を供給する機能を有する。Vccが第1の抵抗11と第2の抵抗12とで分圧され、分圧された電圧の第1の素子13の抵抗値で決まる電圧降下分下がった電圧がバイアス点となる。図8で示した発振回路Aに比べてバイアス点を決めるための構成要素として直列に第1の素子13が接続されていることから、第1の素子13のインピーダンスを調整することにより第1の入力端子4に接続される発振子の出力インピーダンスとの整合を容易に取ることができる。

【0036】

図2−(b)に、信号調整部10におけるインピーダンスを調整し、発振回路100の第1の入力端子4における入力インピーダンスと発振子50の出力インピーダンスとの整合をとったときの第1のトランジスター23のベース振幅波形と第1の出力端子5における出力振幅波形とを示す。図2−(b)に示した波形と図9−(a)に示した波形とを比較すると、図2−(b)に示した波形では副振動が除去されていることがわかる。

【0037】

図3に示したのは、図2−(a)の発振子50に換えて、発振子51、インダクター52、バリキャップ53及び外部抵抗54により構成される回路を接続したものである。この回路構成により発振回路100を用いてVCO(Voltage Controled Oscillator)を構成することができる。端子VCには、発振子51の発振周波数を調整するための所定の電圧が供給される。

【0038】

図4に示した発振回路200、図5に示した発振回路300及び図6に示した発振回路400は、本実施形態における変形例である。発振回路200の第1の素子16は、インダクターである。発振回路300の第1の素子33は、インダクターと抵抗とを直列に接続して構成したものである。また、発振回路400の第1の素子43は、インダクターと抵抗とを並列に接続して構成したものである。発振回路100、発振回路200、発振回路300及び発振回路400のいずれを用いるかは発振子の特性や主振動の周波数などにより決定されるものであり、どの発振回路が好ましいかどうかは、発振子の特性、要求される発振回路の出力周波数などの条件により選択されるものである。

【0039】

(第2実施形態)

図7に本発明を適用した発振器500の回路ブロック図を示す。発振器500は、信号発振部60、信号調整部10及び信号形成部20を含む。尚、本実施形態においては、第1実施形態と同様の構成については同じ符号を付し、その説明を省略する。

【0040】

本実施形態は、図3に示した発振回路100の外付けとした回路をひとつのパッケージ若しくはモジュールとして収めたものである。第1の入力端子6には、発振子51の発振周波数を調整するための所定の電圧が印加される。信号調整部10は、該所定の電圧が第1の入力端子6に印加されたときの信号発振部60の出力インピーダンスとインピーダンス整合が取れるように調整されている。尚、第1実施形態と同様に、第1の素子13は、抵抗、インダクター、抵抗とインダクターとを直列に接続したもの、及び、抵抗とインダクターとを並列に接続したもの、のいずれか適切なものが用いられる。

【0041】

以上、本発明の適用例及び実施形態を記載したが、本発明は上記の実施形態に限定されるものでなく、本発明の主旨を逸脱しない範囲で広く適用可能である。たとえば、発振回路はいわゆるコルビッツ型でなく、他のタイプの発振回路を用いてもかまわない。

【符号の説明】

【0042】

2…第1の電源端子、3…第2の電源端子、4…第1の入力端子、5…第1の出力端子、6…第1の入力端子、10…信号調整部、11…第1の抵抗、12…第2の抵抗、13…第1の素子、14…第1のコンデンサー、16…第1の素子、20…信号形成部、21…第2のコンデンサー、22…第3のコンデンサー、23…第1のトランジスター、24…第3の抵抗、33…第1の素子、43…第1の素子、50…発振子、51…発振子、52…インダクター、53…バリキャップ、54…外部抵抗、60…信号発振部、100…発振回路、200…発振回路、300…発振回路、400…発振回路、500…発振器。

【技術分野】

【0001】

本発明は、水晶振動子、SAW共振子及びセラミック発振子などの発振子に用いられる発振回路、及び、発振子と発振回路とを有する発振器に関する。

【背景技術】

【0002】

従来、発振器は、水晶振動子、SAW共振子及びセラミック振動子などの発振子と発振回路とが組み合わされたもので、機器の制御に用いるためのタイミング信号(クロック信号)を生成する用途などに使用される。発振回路は、発振子から発振される信号の変化の中から所定の周波数の信号を増幅すると共に発振子に対して適切な信号の帰還を行い、発振子の恒常的な発振の制御を行うものである。

【0003】

発振子は所定の周波数による主振動以外にも副振動(以降、発生する要因に関わらず主振動以外のものを総じて副振動と呼ぶことにする)を生じる場合があり、発振回路から出力されるクロック信号が主振動の周波数成分と副振動の周波数成分とが合成されたものとなる場合がある。副振動は、例えば水晶発振子はそのカットの仕方によって発生するもの、発振子の出力インピーダンスと発振回路の入力インピーダンスの整合が取られていないことによる信号の反射などにより生じる場合がある。

【0004】

図8に、発振回路の一例として発振回路Aを示し、発振回路Aの発振用トランジスターTrのベース振幅波形と出力Voutの振幅波形を図9−(a)に示す。発振回路Aには、発振子XTALが接続されている。図9−(b)は、発振用トランジスターTrのベース振幅波形及び出力Voutの振幅波形の高速フーリエ変換(Fast Fourier Transform)結果である。図9−(b)の結果により、図9−(a)の信号に見られる周期の乱れは、主振動による245MHzの周波数成分と副振動の142MHzの周波数成分が合成されたことによることが分かる。機器の制御を行うためには副振動による周波数の成分の影響が極力出力Voutに出ないことが好ましい。

【0005】

発振子のカット状態が要因の副振動における周波数成分を抑制するために、特許文献1には、発振用トランジスターのエミッタ・コレクタ間又はエミッタ・ベース間に、コンデンサー、インダクター及びコンデンサーからなるリアクタンス回路を設けることが記載されている。エミッタ・ベース間にリアクタンス回路Cを配置した発振回路Bを図10に示す。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開2010−41346号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

しかしながら、特許文献1における方法では、発振子と発振回路との間のインピーダンスの不整合が原因となって発生する副振動の低減をすることが難しいという問題がある。

【課題を解決するための手段】

【0008】

本発明は、上述した問題若しくは課題の少なくともひとつを解決するためになされたものであり、以下の適用例若しくは実施形態として実現することが可能である。

【0009】

[適用例1]

本適用例にかかる発振回路は、第1の入力端子と、第1の出力端子と、前記第1の入力端子に接続される信号調整部と、前記第1の入力端子及び前記第1の出力端子に接続される信号形成部と、を含み、前記信号調整部は、第1の素子、第1の抵抗、第2の抵抗及び第1のコンデンサーを有し、前記第1の素子は、一方端が前記第1の入力端子に接続され、他の一方端が前記第1の抵抗の一方端、前記第2の抵抗の一方端及び前記第1のコンデンサーの一方端に接続され、前記第1の抵抗は、他の一方端が第1の電源に接続され、前記第2の抵抗は、他の一方端が第2の電源に接続され、前記第1のコンデンサーは、他の一方端が前記第2の電源に接続され、前記信号形成部において、前記第1の出力端子から出力される信号は、前記第1の入力端子から入力された信号を基に形成されることを特徴とする。

【0010】

この構成によれば、信号調整部が第1の入力端子に接続され、信号形成部が第1の入力端子及び第1の出力端子に接続されていることで、外部から第1の入力端子に接続される装置(以降第1の装置と記載する)とのインピーダンス整合を信号形成部の回路変更をすることなく、信号調整部において行うことができる。これにより、インピーダンスの不整合が原因となって発生する副振動の低減を図ることができる。

【0011】

上記の第1の電源は例えばVCC電源でよく、上記の第2の電源は例えばGNDでよい。上記したが、信号調整部は、第1の素子、第1の抵抗、第2の抵抗及び第1のコンデンサーを有し、第1の素子は、一方端が第1の入力端子に接続され、他の一方端が第1の抵抗の一方端、第2の抵抗の一方端及び第1のコンデンサーの一方端に接続され、第1の抵抗は、他の一方端が第1の電源に接続され、第2の抵抗は、他の一方端が第2の電源に接続され、第1のコンデンサーは、他の一方端が第2の電源に接続されている。この構成により、信号調整部は信号形成部に対するバイアス電圧を設定する機能を有するが、第1の抵抗と第2の抵抗とにより分圧されたポイントに第1の素子を介して第1の入力端子が接続されているため、第1の素子におけるインピーダンスを調整することで、容易に第1の装置とのインピーダンスの整合を取ることができる。また、第1のコンデンサーは、第1の電源及び第2の電源のノイズを原因とする変動による信号形成部に対する影響を軽減する効果を有する。第1の装置は、例えば、水晶発振子であり、SAW共振子であり、セラミック振動子である。

【0012】

[適用例2]

上記適用例にかかる発振回路のひとつは、前記第1の素子は、抵抗であることが好ましい。

【0013】

この構成によれば、第1の素子として抵抗を用いることができる。適切なインピーダンスを有する抵抗を用いることで、信号形成部に対する適切なバイアス電圧を維持しながら第1の装置とのインピーダンス整合を容易にとることができる。

【0014】

[適用例3]

上記適用例にかかる発振回路のひとつは、前記第1の素子は、インダクターであることが好ましい。

【0015】

この構成によれば、第1の素子としてインダクターを用いることができる。適切なインピーダンスを有するインダクターを用いることで、信号形成部に対する適切なバイアス電圧を維持しながら第1の装置とのインピーダンス整合を容易にとることができる。

【0016】

[適用例4]

上記適用例にかかる発振回路のひとつは、前記第1の素子は、抵抗とインダクターとを直列に接続したものであることが好ましい。

【0017】

この構成によれば、第1の素子に抵抗とインダクターとを直列に接続したものをもちいることができる。適切なインピーダンスを有する抵抗及び適切なインピーダンスを有するインダクターを用いることで、信号形成部に対する適切なバイアス電圧を維持しながら第1の装置とのインピーダンス整合を容易にとることができる。

【0018】

[適用例5]

上記適用例にかかる発振回路のひとつは、前記第1の素子は、抵抗とインダクターとを並列に接続したものであることが好ましい。

【0019】

この構成によれば、第1の素子は、抵抗とインダクターとを並列に接続したものであることが好ましい。適切なインピーダンスを有する抵抗及び適切なインピーダンスを有するインダクターを用いることで、信号形成部に対する適切なバイアス電圧を維持しながら第1の装置とのインピーダンス整合を容易にとることができる。

【0020】

[適用例6]

本適用例にかかる発振器は、第1の入力端子と、第1の出力端子と、第1の入力端子に接続される信号発振部と、前記信号発振部から出力される第1の発振信号が伝搬される第1の信号線に接続される信号調整部と、前記第1の信号線及び前記第1の出力端子に接続される信号形成部と、を含み、前記信号発振部は、第1の発振子を有し、前記第1の発振子の発振周波数を制御するための所定の電圧が前記第1の入力端子に印加され、前記信号調整部は、第1の素子、第1の抵抗、第2の抵抗及び第1のコンデンサーを有し、前記第1の素子は、一方端が前記第1の信号線に接続され、他の一方端が前記第1の抵抗の一方端、前記第2の抵抗の一方端及び前記第1のコンデンサーの一方端に接続され、前記第1の抵抗は、他の一方端が第1の電源に接続され、前記第2の抵抗は、他の一方端が第2の電源に接続され、前記第1のコンデンサーは、他の一方端が前記第2の電源に接続され、前記信号形成部において、前記第1の出力端子から出力される信号は、前記第1の信号線により伝搬された信号を基に形成されることを特徴とする。

【0021】

この構成によれば、発振器に信号発振部、信号調整部及び信号形成部が含まれ、信号調整部が、第1の素子、第1の抵抗、第2の抵抗及び第1のコンデンサーを有し、第1の素子は、一方端が第1の信号線に接続され、他の一方端が第1の抵抗の一方端、第2の抵抗の一方端及び第1のコンデンサーの一方端に接続され、第1の抵抗は、他の一方端が第1の電源に接続され、第2の抵抗は、他の一方端が第2の電源に接続され、第1のコンデンサーは、他の一方端が第2の電源に接続されていることで、信号発振部の出力インピーダンスと信号調整部及び信号形成部との入力インピーダンスとの整合を信号調整部においてとることができる。第1の電源は例えばVCC電源でよく、第2の電源は例えばGNDでよい。この構成により、信号調整部は信号形成部に対するバイアス電圧を設定する機能を有するが、第1の抵抗と第2の抵抗とにより分圧されたポイントに第1の素子を介して第1の信号線が接続されているため、第1の素子の特性を調整することにより、容易に信号発振部とのインピーダンスの整合を取ることができる。

【0022】

[適用例7]

上記適用例にかかる発振器のひとつは、前記第1の素子は、抵抗であることを特徴とする。

【0023】

この構成によれば、第1の素子として抵抗を用いることができる。適切なインピーダンスを有する抵抗を用いることで、信号形成部に対する適切なバイアス電圧を維持しながら第1の装置とのインピーダンス整合を容易にとることができる。

【0024】

[適用例8]

上記適用例にかかる発振器のひとつは、前記第1の素子は、インダクターであることを特徴とする。

【0025】

この構成によれば、第1の素子としてインダクターを用いることができる。適切なインピーダンスを有するインダクターを用いることで、信号形成部に対する適切なバイアス電圧を維持しながら第1の装置とのインピーダンス整合を容易にとることができる。

【0026】

[適用例9]

上記適用例にかかる発振器のひとつは、前記第1の素子は、抵抗とインダクターとを直列に接続したものであることを特徴とする。

【0027】

この構成によれば、第1の素子に抵抗とインダクターとを直列に接続したものをもちいることができる。適切なインピーダンスを有する抵抗及び適切なインピーダンスを有するインダクターを用いることで、信号形成部に対する適切なバイアス電圧を維持しながら第1の装置とのインピーダンス整合を容易にとることができる。

【0028】

[適用例10]

上記適用例にかかる発振器のひとつは、前記第1の素子は、抵抗とインダクターとを並列に接続したものであることを特徴とする。

【0029】

この構成によれば、第1の素子は、抵抗とインダクターとを並列に接続したものであることが好ましい。適切なインピーダンスを有する抵抗及び適切なインピーダンスを有するインダクターを用いることで、信号形成部に対する適切なバイアス電圧を維持しながら第1の装置とのインピーダンス整合を容易にとることができる。

【図面の簡単な説明】

【0030】

【図1】発振回路(第1実施形態)の回路ブロック図。

【図2】発振回路(第1実施形態)の使用例と振幅波形。

【図3】発振回路(第1実施形態)の変形使用例。

【図4】発振回路(第1実施形態)の変形例。

【図5】発振回路(第1実施形態)の変形例。

【図6】発振回路(第1実施形態)の変形例。

【図7】発振回路(第2実施形態)の回路ブロック図。

【図8】従来技術における発振回路の回路ブロック図。

【図9】従来技術における発振回路の振幅波形。

【図10】従来技術における発振回路の回路ブロック図。

【発明を実施するための形態】

【0031】

以下、図を用いて本発明の実施形態について説明する。

【0032】

(第1実施形態)

図1に、本発明を適用した発振回路100を示す、発振回路100は、信号調整部10及び信号形成部20を含む。また、発振回路100は、第1の入力端子4、第1の出力端子5、第1の電源端子2及び第2の電源端子3を有する。第1の電源端子2は正電源電圧(Vcc)が供給され、第2の電源端子3はGndに接続される。発振子は、第1の入力端子4と第2の電源端子3の間に接続される。発振子50を接続した状態の模式図を図2−(a)に示す。

【0033】

信号調整部10は、第1の素子13、第1の抵抗11、第2の抵抗12及び第1のコンデンサー14を有する。図1から分かるように、本実施形態における第1の素子13は抵抗素子である。第1の素子13の一方端は第1の入力端子4に接続されている。第1の素子13の他の一方端は第1の抵抗11の一方端、第2の抵抗12の一方端及び第1のコンデンサー14の一方端に接続されている。第1の抵抗11の他の一方端はVccに接続されている。第2の抵抗12の他の一方端及び第1のコンデンサー14の他の一方端はいずれもGndに接続されている。第1のコンデンサー14は、第1の抵抗11と第2の抵抗12とによる分圧点のAC成分による変動を押さえ、Vccにのったノイズ等による影響を軽減する役割を有する。

【0034】

信号形成部20は、第2のコンデンサー21、第3のコンデンサー22、第1のトランジスター23及び第3の抵抗24を有し、第1のトランジスター23のエミッターが第1の出力端子5に接続されており、いわゆるコルビッツ型発振回路の構成を有する。第1のトランジスター23のベースには第1の入力端子4が接続されている。

【0035】

信号調整部10は、第1のトランジスター23のベースのバイアス点を供給する機能を有する。Vccが第1の抵抗11と第2の抵抗12とで分圧され、分圧された電圧の第1の素子13の抵抗値で決まる電圧降下分下がった電圧がバイアス点となる。図8で示した発振回路Aに比べてバイアス点を決めるための構成要素として直列に第1の素子13が接続されていることから、第1の素子13のインピーダンスを調整することにより第1の入力端子4に接続される発振子の出力インピーダンスとの整合を容易に取ることができる。

【0036】

図2−(b)に、信号調整部10におけるインピーダンスを調整し、発振回路100の第1の入力端子4における入力インピーダンスと発振子50の出力インピーダンスとの整合をとったときの第1のトランジスター23のベース振幅波形と第1の出力端子5における出力振幅波形とを示す。図2−(b)に示した波形と図9−(a)に示した波形とを比較すると、図2−(b)に示した波形では副振動が除去されていることがわかる。

【0037】

図3に示したのは、図2−(a)の発振子50に換えて、発振子51、インダクター52、バリキャップ53及び外部抵抗54により構成される回路を接続したものである。この回路構成により発振回路100を用いてVCO(Voltage Controled Oscillator)を構成することができる。端子VCには、発振子51の発振周波数を調整するための所定の電圧が供給される。

【0038】

図4に示した発振回路200、図5に示した発振回路300及び図6に示した発振回路400は、本実施形態における変形例である。発振回路200の第1の素子16は、インダクターである。発振回路300の第1の素子33は、インダクターと抵抗とを直列に接続して構成したものである。また、発振回路400の第1の素子43は、インダクターと抵抗とを並列に接続して構成したものである。発振回路100、発振回路200、発振回路300及び発振回路400のいずれを用いるかは発振子の特性や主振動の周波数などにより決定されるものであり、どの発振回路が好ましいかどうかは、発振子の特性、要求される発振回路の出力周波数などの条件により選択されるものである。

【0039】

(第2実施形態)

図7に本発明を適用した発振器500の回路ブロック図を示す。発振器500は、信号発振部60、信号調整部10及び信号形成部20を含む。尚、本実施形態においては、第1実施形態と同様の構成については同じ符号を付し、その説明を省略する。

【0040】

本実施形態は、図3に示した発振回路100の外付けとした回路をひとつのパッケージ若しくはモジュールとして収めたものである。第1の入力端子6には、発振子51の発振周波数を調整するための所定の電圧が印加される。信号調整部10は、該所定の電圧が第1の入力端子6に印加されたときの信号発振部60の出力インピーダンスとインピーダンス整合が取れるように調整されている。尚、第1実施形態と同様に、第1の素子13は、抵抗、インダクター、抵抗とインダクターとを直列に接続したもの、及び、抵抗とインダクターとを並列に接続したもの、のいずれか適切なものが用いられる。

【0041】

以上、本発明の適用例及び実施形態を記載したが、本発明は上記の実施形態に限定されるものでなく、本発明の主旨を逸脱しない範囲で広く適用可能である。たとえば、発振回路はいわゆるコルビッツ型でなく、他のタイプの発振回路を用いてもかまわない。

【符号の説明】

【0042】

2…第1の電源端子、3…第2の電源端子、4…第1の入力端子、5…第1の出力端子、6…第1の入力端子、10…信号調整部、11…第1の抵抗、12…第2の抵抗、13…第1の素子、14…第1のコンデンサー、16…第1の素子、20…信号形成部、21…第2のコンデンサー、22…第3のコンデンサー、23…第1のトランジスター、24…第3の抵抗、33…第1の素子、43…第1の素子、50…発振子、51…発振子、52…インダクター、53…バリキャップ、54…外部抵抗、60…信号発振部、100…発振回路、200…発振回路、300…発振回路、400…発振回路、500…発振器。

【特許請求の範囲】

【請求項1】

第1の入力端子と、

第1の出力端子と、

前記第1の入力端子に接続される信号調整部と、

前記第1の入力端子及び前記第1の出力端子に接続される信号形成部と、を含み、

前記信号調整部は、第1の素子、第1の抵抗、第2の抵抗及び第1のコンデンサーを有し、

前記第1の素子は、一方端が前記第1の入力端子に接続され、他の一方端が前記第1の抵抗の一方端、前記第2の抵抗の一方端及び前記第1のコンデンサーの一方端に接続され、

前記第1の抵抗は、他の一方端が第1の電源に接続され、

前記第2の抵抗は、他の一方端が第2の電源に接続され、

前記第1のコンデンサーは、他の一方端が前記第2の電源に接続され、

前記信号形成部において、前記第1の出力端子から出力される信号は、前記第1の入力端子から入力された信号を基に形成されることを特徴とする発振回路。

【請求項2】

前記第1の素子は、抵抗であることを特徴とする請求項1に記載の発振回路。

【請求項3】

前記第1の素子は、インダクターであることを特徴とする請求項1に記載の発振回路。

【請求項4】

前記第1の素子は、抵抗とインダクターとを直列に接続したものであることを特徴とする請求項1に記載の発振回路。

【請求項5】

前記第1の素子は、抵抗とインダクターとを並列に接続したものであることを特徴とする請求項1に記載の発振回路。

【請求項6】

第1の入力端子と、

第1の出力端子と、

第1の入力端子に接続される信号発振部と、

前記信号発振部から出力される第1の発振信号が伝搬される第1の信号線に接続される信号調整部と、

前記第1の信号線及び前記第1の出力端子に接続される信号形成部と、を含み、

前記信号発振部は、第1の発振子を有し、前記第1の発振子の発振周波数を制御するための所定の電圧が前記第1の入力端子に印加され、

前記信号調整部は、第1の素子、第1の抵抗、第2の抵抗及び第1のコンデンサーを有し、

前記第1の素子は、一方端が前記第1の信号線に接続され、他の一方端が前記第1の抵抗の一方端、前記第2の抵抗の一方端及び前記第1のコンデンサーの一方端に接続され、

前記第1の抵抗は、他の一方端が第1の電源に接続され、

前記第2の抵抗は、他の一方端が第2の電源に接続され、

前記第1のコンデンサーは、他の一方端が前記第2の電源に接続され、

前記信号形成部において、前記第1の出力端子から出力される信号は、前記第1の信号線により伝搬された信号を基に形成されることを特徴とする発振器。

【請求項7】

前記第1の素子は、抵抗であることを特徴とする請求項6に記載の発振器。

【請求項8】

前記第1の素子は、インダクターであることを特徴とする請求項6に記載の発振器。

【請求項9】

前記第1の素子は、抵抗とインダクターとを直列に接続したものであることを特徴とする請求項6に記載の発振器。

【請求項10】

前記第1の素子は、抵抗とインダクターとを並列に接続したものであることを特徴とする請求項6に記載の発振器。

【請求項1】

第1の入力端子と、

第1の出力端子と、

前記第1の入力端子に接続される信号調整部と、

前記第1の入力端子及び前記第1の出力端子に接続される信号形成部と、を含み、

前記信号調整部は、第1の素子、第1の抵抗、第2の抵抗及び第1のコンデンサーを有し、

前記第1の素子は、一方端が前記第1の入力端子に接続され、他の一方端が前記第1の抵抗の一方端、前記第2の抵抗の一方端及び前記第1のコンデンサーの一方端に接続され、

前記第1の抵抗は、他の一方端が第1の電源に接続され、

前記第2の抵抗は、他の一方端が第2の電源に接続され、

前記第1のコンデンサーは、他の一方端が前記第2の電源に接続され、

前記信号形成部において、前記第1の出力端子から出力される信号は、前記第1の入力端子から入力された信号を基に形成されることを特徴とする発振回路。

【請求項2】

前記第1の素子は、抵抗であることを特徴とする請求項1に記載の発振回路。

【請求項3】

前記第1の素子は、インダクターであることを特徴とする請求項1に記載の発振回路。

【請求項4】

前記第1の素子は、抵抗とインダクターとを直列に接続したものであることを特徴とする請求項1に記載の発振回路。

【請求項5】

前記第1の素子は、抵抗とインダクターとを並列に接続したものであることを特徴とする請求項1に記載の発振回路。

【請求項6】

第1の入力端子と、

第1の出力端子と、

第1の入力端子に接続される信号発振部と、

前記信号発振部から出力される第1の発振信号が伝搬される第1の信号線に接続される信号調整部と、

前記第1の信号線及び前記第1の出力端子に接続される信号形成部と、を含み、

前記信号発振部は、第1の発振子を有し、前記第1の発振子の発振周波数を制御するための所定の電圧が前記第1の入力端子に印加され、

前記信号調整部は、第1の素子、第1の抵抗、第2の抵抗及び第1のコンデンサーを有し、

前記第1の素子は、一方端が前記第1の信号線に接続され、他の一方端が前記第1の抵抗の一方端、前記第2の抵抗の一方端及び前記第1のコンデンサーの一方端に接続され、

前記第1の抵抗は、他の一方端が第1の電源に接続され、

前記第2の抵抗は、他の一方端が第2の電源に接続され、

前記第1のコンデンサーは、他の一方端が前記第2の電源に接続され、

前記信号形成部において、前記第1の出力端子から出力される信号は、前記第1の信号線により伝搬された信号を基に形成されることを特徴とする発振器。

【請求項7】

前記第1の素子は、抵抗であることを特徴とする請求項6に記載の発振器。

【請求項8】

前記第1の素子は、インダクターであることを特徴とする請求項6に記載の発振器。

【請求項9】

前記第1の素子は、抵抗とインダクターとを直列に接続したものであることを特徴とする請求項6に記載の発振器。

【請求項10】

前記第1の素子は、抵抗とインダクターとを並列に接続したものであることを特徴とする請求項6に記載の発振器。

【図1】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図10】

【図2】

【図9】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図10】

【図2】

【図9】

【公開番号】特開2013−5007(P2013−5007A)

【公開日】平成25年1月7日(2013.1.7)

【国際特許分類】

【出願番号】特願2011−130992(P2011−130992)

【出願日】平成23年6月13日(2011.6.13)

【出願人】(000002369)セイコーエプソン株式会社 (51,324)

【Fターム(参考)】

【公開日】平成25年1月7日(2013.1.7)

【国際特許分類】

【出願日】平成23年6月13日(2011.6.13)

【出願人】(000002369)セイコーエプソン株式会社 (51,324)

【Fターム(参考)】

[ Back to top ]