発振回路

【課題】MOSトランジスタの閾値電圧の製造ばらつきについて、発振周波数の補正をかけることができる発振回路を提供する。

【解決手段】リングオシレータOSCを構成するインバータ回路の入力反転用トランジスタと同じ導電型のp型トランジスタP4をダイオード接続すると共に第1抵抗R1を介して接地し、これに定電流源I1からの定電流を流すことで、製造ばらつきによる閾値電圧変動に追随したターンオン電圧を得て、この電圧を演算増幅器A1を介してp型トランジスタP6のゲートに供給し、n型トランジスタN0とインバータ回路の各n型トランジスタN1、N2、N3によるカレントミラーを通じてリングオシレータOSCに流す電流の制御に利用する構成とした。

【解決手段】リングオシレータOSCを構成するインバータ回路の入力反転用トランジスタと同じ導電型のp型トランジスタP4をダイオード接続すると共に第1抵抗R1を介して接地し、これに定電流源I1からの定電流を流すことで、製造ばらつきによる閾値電圧変動に追随したターンオン電圧を得て、この電圧を演算増幅器A1を介してp型トランジスタP6のゲートに供給し、n型トランジスタN0とインバータ回路の各n型トランジスタN1、N2、N3によるカレントミラーを通じてリングオシレータOSCに流す電流の制御に利用する構成とした。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、一定の周波数を出力する発振回路に関し、特にその発振周波数を決定するMOSトランジスタの閾値電圧の製造ばらつきを補償する発振回路に関する。

【背景技術】

【0002】

従来、各種電子機器等に用いられる発振回路では、種々の物理的な条件の変化に対して、所望の発振周波数の信号を安定して発生させるために種々の工夫が施されている。その理由は、所望の周波数にて設計していた電子機器が動作しなくなったり、他の電子機器に悪影響を及ぼしたりするからである。

【0003】

以下、従来の発振回路200について、図2を参照して説明する。図2において、CI2は温度に依存しない定電流回路、OSCは奇数段のインバータ回路をリング状に接続したリングオシレータである。定電流回路CI2を構成するn型トランジスタN7のソースは接地され、ドレインはゲートと共通接続されると共に定電流源I2を介して電源VDDに接続されている。

【0004】

3段の各インバータ回路の負荷用MOSトランジスタとしてのn型トランジスタN1、N2、N3の各ソースは接地され、各ゲートはn型トランジスタN7のゲートに共通接続されている。また、各インバータ回路の入力反転用トランジスタとしてのp型トランジスタP1、P2、P3の各ソースは電源VDDに接続され、各ドレインはそれぞれn型トランジスタN1、N2、N3の各ドレインに接続されている。そして、p型トランジスタP1とn型トランジスタN1の各ドレイン接続点が、次段のp型トランジスタP2のゲートに接続され、同じくp型トランジスタP2とn型トランジスタN2の各ドレイン接続点が、次段のp型トランジスタP3のゲートに接続され、最終段のp型トランジスタP3とn型トランジスタN3の各ドレイン接続点が、初段のp型トランジスタP1のゲートに接続されている。

【0005】

尚、各p型トランジスタP1、P2、P3は同一形状、同一特性のトランジスタであり、各n型トランジスタN1、N2、N3も同一形状、同一特性のトランジスタとされることが多いが、形状は違っていてもよい。また、n型トランジスタN7は各n型トランジスタN1、N2、N3とゲート長が同じでゲート幅が異なるトランジスタとされることが多い。

【0006】

上記構成の発振回路200の動作を説明する。n型トランジスタN7とインバータ回路の各n型トランジスタN1、N2、N3はカレントミラーを構成しているので、インバータ回路の各n型トランジスタには、n型トランジスタN7とのミラー比に応じた電流が流れる。そして、温度の影響を受けにくい定電流源I2を用い、温度依存のない常に安定した定電流をリングオシレータOSCに供給している。

【0007】

したがって、温度依存のない定電流がリングオシレータOSCの各インバータ回路に供給されるので、リングオシレータOSCでも温度に依存されず、精度のよい安定した発振周波数を出力することができる。また、I2を調整することにより周波数を調整することができる(例えば、特許文献1参照。)。尚、発振回路200は、特許文献1の電源とグラウンド及び各トランジスタのn型とp型の極性を反転させた例を示している。

【特許文献1】特開2003−283305号公報 (第3、4頁、第1図)

【発明の開示】

【発明が解決しようとする課題】

【0008】

ところが、各インバータ回路を構成するp型トランジスタP1、P2、P3の閾値電圧が拡散工程等の製造ばらつきにより変動すると、発振周波数も変動するという問題点がある。これは、発振回路の周波数が、各インバータ回路に流れる電流と、p型トランジスタP1、P2、P3の各入力容量(サイズで決まる為ほぼ一定)と、各段の入力反転用トランジスタであるp型トランジスタP1、P2、P3の閾値電圧でほぼ決まるからである。

【課題を解決するための手段】

【0009】

請求項1記載の発明は、入力反転用MOSトランジスタと負荷用MOSトランジスタとからなるインバータがリング状に奇数段接続されたリングオシレータと、負荷用MOSトランジスタに定電流を供給する定電流回路とを具備した発振回路において、定電流回路は、入力反転用MOSトランジスタの閾値電圧に追随した定電圧を発生させる定電圧発生手段と、定電圧を定電流に変換する電圧電流変換手段とを有することを特徴とする発振回路である。

【0010】

本発明では、製造ばらつきにより、リングオシレータの各インバータ回路を構成する入力反転用MOSトランジスタの閾値電圧が高くなると、リングオシレータの周波数が、各インバータ回路の入力反転用MOSトランジスタに流れる電流、サイズで決まる入力容量及び閾値電圧でほぼ決まるため、リングオシレータ自体の発振周波数は低くなる。

【0011】

しかし、入力反転用MOSトランジスタの閾値電圧に追随した定電圧を発生させる定電圧発生手段と、この定電圧を定電流に変換する電圧電流変換手段とにより、リングオシレータの各インバータ回路を構成する負荷用MOSトランジスタに流れる電流が大きくなる。この結果、リングオシレータの発振周波数が上がるように補正がかかる。

【0012】

逆に、入力反転用MOSトランジスタの閾値電圧が低くなると、リングオシレータの発振周波数は高くなるが、負荷用MOSトランジスタに流れる電流が小さくなり、リングオシレータの発振周波数が下がるように補正がかかる。こうして発振周波数の変化の割合と、入力反転用MOSトランジスタの閾値電圧変化に追随した負荷用MOSトランジスタに流れる電流変化の割合を定電圧発生手段と電圧電流変換手段とにより合わせることで、製造ばらつきについての補正をかけている。

【発明の効果】

【0013】

本発明の発振回路によれば、閾値電圧の製造ばらつきについて発振周波数の補正をかけることができる。

【発明を実施するための最良の形態】

【0014】

発振周波数のばらつきを、リングオシレータを構成するインバータ回路の入力反転用トランジスタと同じ導電型のトランジスタをダイオード接続すると共に抵抗を介して接地し、これに定電流を流すことで、製造ばらつきによる閾値電圧変動に追随したターンオン電圧を得て、この電圧をリングオシレータに流れる電流の制御に利用することで実現した。

【実施例1】

【0015】

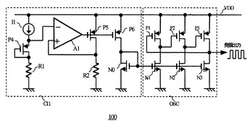

以下、本発明の実施例1の発振回路100について、図1を参照して説明する。尚、図2と同一のものについては同一符号を付してその説明を省略する。図1において、CI1は温度に依存しない定電流回路、OSCは奇数段のインバータ回路をリング状に接続したリングオシレータであり、リングオシレータOSCは図1のものと同一である。

【0016】

P4はリングオシレータOSCを構成するインバータ回路の入力反転用トランジスタと同じ導電型の定電圧出力用MOSトランジスタとしてのp型トランジスタで、ゲートとドレインが接続されてダイオード接続されると共に第1抵抗R1を介して接地されている。第1抵抗R1は、正の温度係数を持った拡散抵抗である。そして、p型トランジスタP4のソースが、定電流源I1を介して電源VDDに接続されている。

【0017】

A1は演算増幅器で、反転入力端にはp型トランジスタP4のソースと定電流源I1との接続点の電圧が入力されている。P5はp型トランジスタで、ソースが電源VDDに、ゲートが演算増幅器A1の出力端にそれぞれ接続され、ドレインが演算増幅器A1の非反転入力端に接続されると共に第2抵抗R2を介して接地されている。

【0018】

P6はソースが電源VDDに、ゲートが演算増幅器A1の出力端にそれぞれ接続されたp型トランジスタである。N0はソースが接地され、ドレインがゲートと共通接続されると共にp型トランジスタP6のドレインに接続されたn型トランジスタである。

【0019】

こうして定電流回路CI1が構成され、n型トランジスタN0のゲートが3段の各インバータ回路を構成する負荷用MOSトランジスタとしてのn型トランジスタN1、N2、N3の各ゲートに接続されている。

【0020】

尚、p型トランジスタP4は各インバータ回路の入力反転用トランジスタを構成する各p型トランジスタP1、P2、P3とゲート長が同じでゲート幅が異なるトランジスタであり、p型トランジスタP5はp型トランジスタP6とゲート長が同じでゲート幅が異なるトランジスタであることが好ましい。また、n型トランジスタN0は各n型トランジスタN1、N2、N3とゲート長が同じでゲート幅が異なるトランジスタであることが好ましい。回路設計が容易となり補償精度も向上するからである。

【0021】

上記構成の発振回路100の動作を説明する。ダイオード接続されたp型トランジスタP4及び第1抵抗R1の直列回路には定電流源I1による温度に依存しない一定の電流が流れる。そして、例えば回路の温度が上昇した場合、p型トランジスタP4のソースとドレイン間の電圧は下がるが、拡散抵抗である第1抵抗R1の抵抗値は上がる。したがって、p型トランジスタP4及び第1抵抗R1の素子の両端電圧に関する温度特性を好適に選定することで両者の電圧変動は打ち消され、p型トランジスタP4と定電流源I1との接続点の電圧は温度に依存しない一定値となる。

【0022】

この電圧は、演算増幅器A1の反転入力端に入力されており、演算増幅器A1のイマジナリショートのはたらきにより非反転入力端すなわちp型トランジスタP5と第2抵抗R2との接続点の電圧も温度に依存しない一定値となる。そして、p型トランジスタP5と第2抵抗R2を流れる電流を一定にする電圧が、演算増幅器A1の出力端に現れることとなる。

【0023】

この演算増幅器A1の温度に依存しない出力電圧は、p型トランジスタP6にも与えられているため、これに接続されているn型トランジスタN0には温度に依存しない一定の電流が流れる。n型トランジスタN0を基準トランジスタとし、インバータ回路の各n型トランジスタN1、N2、N3をミラートランジスタとするカレントミラーを構成しているので、インバータ回路の各n型トランジスタには、n型トランジスタN0とのミラー比に応じた電流が流れる。

【0024】

したがって、温度依存のない定電流がリングオシレータOSCの各インバータ回路に供給されるので、リングオシレータOSCでも温度に依存されず、精度のよい安定した発振周波数を出力することができる。

【0025】

次に、製造ばらつきにより、各インバータ回路を構成するp型トランジスタP1、P2、P3の閾値電圧が高くなると、リングオシレータOSC自体の発振周波数は低くなるが、p型トランジスタP4のターンオン電圧も高くなり、演算増幅器A1の反転入力端の電圧は上昇し、出力端の電圧は下降する。したがって、各p型トランジスタP5、P6に流れる電流が大きくなり、リングオシレータOSCの各n型トランジスタN1、N2、N3に流れる電流も大きくなる。この結果、リングオシレータOSCの発振周波数が上がるように補正がかかる。

【0026】

逆に、p型トランジスタP1、P2、P3の閾値電圧が低くなると、リングオシレータOSC自体の発振周波数は高くなるが、p型トランジスタP4のターンオン電圧も低くなり、演算増幅器A1の反転入力端の電圧は下がり、出力端の電圧は上昇する。したがって、各p型トランジスタP5、P6に流れる電流が小さくなり、リングオシレータOSCの各n型トランジスタN1、N2、N3に流れる電流も小さくなる。この結果、リングオシレータOSCの発振周波数が下がるように補正がかかる。こうして発振周波数の変化の割合と、p型トランジスタP1、P2、P3の閾値電圧変化に追随したn型トランジスタN1、N2、N3に流れる電流変化の割合を合わせることで、製造ばらつきについての補正をかけている。

【0027】

以上説明したように、リングオシレータOSCを構成するインバータ回路の入力反転用トランジスタと同じ導電型のp型トランジスタP4をダイオード接続すると共に第1抵抗R1を介して接地し、これに定電流を流すことで、製造ばらつきによる閾値電圧変動に追随したターンオン電圧を得て、この電圧をリングオシレータOSCに流す電流の制御に利用する構成としたので、発振周波数の閾値電圧の製造ばらつきについて補正をかけることができる。なお、発振回路100の第2抵抗R2を半導体集積回路に組み込まずに外部接続し、この第2抵抗R2を調整することにより周波数を容易に調整することもできる。

【0028】

尚、本発明の第1実施例の発振回路100では、回路の温度が上昇した場合、p型トランジスタP4のソースとドレイン間の電圧が下がる場合で説明したが、これとは逆の温度特性となる場合には、第1抵抗R1を負の抵抗値温度特性を持つ例えばポリシリ抵抗とすればよい。また、本発明の第1実施例の発振回路100とは逆に、電源とグラウンド及び各トランジスタのn型とp型の極性を反転させた回路構成としてもよい。

【産業上の利用可能性】

【0029】

本発明の発振回路は、MOSトランジスタの閾値電圧の製造ばらつきを補償する必要のある発振回路に広く適用できる。例えば、近年のDVDやMDなどの光ディスクの情報を読みとるための光ピックアップ用レーザーダイオード駆動回路で使用されている高周波重畳モジュール内の発振回路である。高周波重畳モジュールは、種々のレーザーノイズを低減するために、レーザーダイオード駆動電流に数百MHzの高周波電流を重畳する役割をしており、発振周波数の安定性が求められている。

【図面の簡単な説明】

【0030】

【図1】本発明の第1実施例の発振回路図。

【図2】従来例の発振回路図。

【符号の説明】

【0031】

CI1、CI2 定電流回路

I1、I2 定電流源

N0、N7 n型トランジスタ

N1、N2、N3 n型トランジスタ

OSC リングオシレータ

P1、P2、P3 p型トランジスタ

P4、P5、P6 p型トランジスタ

R1、R2 抵抗

VDD 電源

100、200 発振回路

【技術分野】

【0001】

本発明は、一定の周波数を出力する発振回路に関し、特にその発振周波数を決定するMOSトランジスタの閾値電圧の製造ばらつきを補償する発振回路に関する。

【背景技術】

【0002】

従来、各種電子機器等に用いられる発振回路では、種々の物理的な条件の変化に対して、所望の発振周波数の信号を安定して発生させるために種々の工夫が施されている。その理由は、所望の周波数にて設計していた電子機器が動作しなくなったり、他の電子機器に悪影響を及ぼしたりするからである。

【0003】

以下、従来の発振回路200について、図2を参照して説明する。図2において、CI2は温度に依存しない定電流回路、OSCは奇数段のインバータ回路をリング状に接続したリングオシレータである。定電流回路CI2を構成するn型トランジスタN7のソースは接地され、ドレインはゲートと共通接続されると共に定電流源I2を介して電源VDDに接続されている。

【0004】

3段の各インバータ回路の負荷用MOSトランジスタとしてのn型トランジスタN1、N2、N3の各ソースは接地され、各ゲートはn型トランジスタN7のゲートに共通接続されている。また、各インバータ回路の入力反転用トランジスタとしてのp型トランジスタP1、P2、P3の各ソースは電源VDDに接続され、各ドレインはそれぞれn型トランジスタN1、N2、N3の各ドレインに接続されている。そして、p型トランジスタP1とn型トランジスタN1の各ドレイン接続点が、次段のp型トランジスタP2のゲートに接続され、同じくp型トランジスタP2とn型トランジスタN2の各ドレイン接続点が、次段のp型トランジスタP3のゲートに接続され、最終段のp型トランジスタP3とn型トランジスタN3の各ドレイン接続点が、初段のp型トランジスタP1のゲートに接続されている。

【0005】

尚、各p型トランジスタP1、P2、P3は同一形状、同一特性のトランジスタであり、各n型トランジスタN1、N2、N3も同一形状、同一特性のトランジスタとされることが多いが、形状は違っていてもよい。また、n型トランジスタN7は各n型トランジスタN1、N2、N3とゲート長が同じでゲート幅が異なるトランジスタとされることが多い。

【0006】

上記構成の発振回路200の動作を説明する。n型トランジスタN7とインバータ回路の各n型トランジスタN1、N2、N3はカレントミラーを構成しているので、インバータ回路の各n型トランジスタには、n型トランジスタN7とのミラー比に応じた電流が流れる。そして、温度の影響を受けにくい定電流源I2を用い、温度依存のない常に安定した定電流をリングオシレータOSCに供給している。

【0007】

したがって、温度依存のない定電流がリングオシレータOSCの各インバータ回路に供給されるので、リングオシレータOSCでも温度に依存されず、精度のよい安定した発振周波数を出力することができる。また、I2を調整することにより周波数を調整することができる(例えば、特許文献1参照。)。尚、発振回路200は、特許文献1の電源とグラウンド及び各トランジスタのn型とp型の極性を反転させた例を示している。

【特許文献1】特開2003−283305号公報 (第3、4頁、第1図)

【発明の開示】

【発明が解決しようとする課題】

【0008】

ところが、各インバータ回路を構成するp型トランジスタP1、P2、P3の閾値電圧が拡散工程等の製造ばらつきにより変動すると、発振周波数も変動するという問題点がある。これは、発振回路の周波数が、各インバータ回路に流れる電流と、p型トランジスタP1、P2、P3の各入力容量(サイズで決まる為ほぼ一定)と、各段の入力反転用トランジスタであるp型トランジスタP1、P2、P3の閾値電圧でほぼ決まるからである。

【課題を解決するための手段】

【0009】

請求項1記載の発明は、入力反転用MOSトランジスタと負荷用MOSトランジスタとからなるインバータがリング状に奇数段接続されたリングオシレータと、負荷用MOSトランジスタに定電流を供給する定電流回路とを具備した発振回路において、定電流回路は、入力反転用MOSトランジスタの閾値電圧に追随した定電圧を発生させる定電圧発生手段と、定電圧を定電流に変換する電圧電流変換手段とを有することを特徴とする発振回路である。

【0010】

本発明では、製造ばらつきにより、リングオシレータの各インバータ回路を構成する入力反転用MOSトランジスタの閾値電圧が高くなると、リングオシレータの周波数が、各インバータ回路の入力反転用MOSトランジスタに流れる電流、サイズで決まる入力容量及び閾値電圧でほぼ決まるため、リングオシレータ自体の発振周波数は低くなる。

【0011】

しかし、入力反転用MOSトランジスタの閾値電圧に追随した定電圧を発生させる定電圧発生手段と、この定電圧を定電流に変換する電圧電流変換手段とにより、リングオシレータの各インバータ回路を構成する負荷用MOSトランジスタに流れる電流が大きくなる。この結果、リングオシレータの発振周波数が上がるように補正がかかる。

【0012】

逆に、入力反転用MOSトランジスタの閾値電圧が低くなると、リングオシレータの発振周波数は高くなるが、負荷用MOSトランジスタに流れる電流が小さくなり、リングオシレータの発振周波数が下がるように補正がかかる。こうして発振周波数の変化の割合と、入力反転用MOSトランジスタの閾値電圧変化に追随した負荷用MOSトランジスタに流れる電流変化の割合を定電圧発生手段と電圧電流変換手段とにより合わせることで、製造ばらつきについての補正をかけている。

【発明の効果】

【0013】

本発明の発振回路によれば、閾値電圧の製造ばらつきについて発振周波数の補正をかけることができる。

【発明を実施するための最良の形態】

【0014】

発振周波数のばらつきを、リングオシレータを構成するインバータ回路の入力反転用トランジスタと同じ導電型のトランジスタをダイオード接続すると共に抵抗を介して接地し、これに定電流を流すことで、製造ばらつきによる閾値電圧変動に追随したターンオン電圧を得て、この電圧をリングオシレータに流れる電流の制御に利用することで実現した。

【実施例1】

【0015】

以下、本発明の実施例1の発振回路100について、図1を参照して説明する。尚、図2と同一のものについては同一符号を付してその説明を省略する。図1において、CI1は温度に依存しない定電流回路、OSCは奇数段のインバータ回路をリング状に接続したリングオシレータであり、リングオシレータOSCは図1のものと同一である。

【0016】

P4はリングオシレータOSCを構成するインバータ回路の入力反転用トランジスタと同じ導電型の定電圧出力用MOSトランジスタとしてのp型トランジスタで、ゲートとドレインが接続されてダイオード接続されると共に第1抵抗R1を介して接地されている。第1抵抗R1は、正の温度係数を持った拡散抵抗である。そして、p型トランジスタP4のソースが、定電流源I1を介して電源VDDに接続されている。

【0017】

A1は演算増幅器で、反転入力端にはp型トランジスタP4のソースと定電流源I1との接続点の電圧が入力されている。P5はp型トランジスタで、ソースが電源VDDに、ゲートが演算増幅器A1の出力端にそれぞれ接続され、ドレインが演算増幅器A1の非反転入力端に接続されると共に第2抵抗R2を介して接地されている。

【0018】

P6はソースが電源VDDに、ゲートが演算増幅器A1の出力端にそれぞれ接続されたp型トランジスタである。N0はソースが接地され、ドレインがゲートと共通接続されると共にp型トランジスタP6のドレインに接続されたn型トランジスタである。

【0019】

こうして定電流回路CI1が構成され、n型トランジスタN0のゲートが3段の各インバータ回路を構成する負荷用MOSトランジスタとしてのn型トランジスタN1、N2、N3の各ゲートに接続されている。

【0020】

尚、p型トランジスタP4は各インバータ回路の入力反転用トランジスタを構成する各p型トランジスタP1、P2、P3とゲート長が同じでゲート幅が異なるトランジスタであり、p型トランジスタP5はp型トランジスタP6とゲート長が同じでゲート幅が異なるトランジスタであることが好ましい。また、n型トランジスタN0は各n型トランジスタN1、N2、N3とゲート長が同じでゲート幅が異なるトランジスタであることが好ましい。回路設計が容易となり補償精度も向上するからである。

【0021】

上記構成の発振回路100の動作を説明する。ダイオード接続されたp型トランジスタP4及び第1抵抗R1の直列回路には定電流源I1による温度に依存しない一定の電流が流れる。そして、例えば回路の温度が上昇した場合、p型トランジスタP4のソースとドレイン間の電圧は下がるが、拡散抵抗である第1抵抗R1の抵抗値は上がる。したがって、p型トランジスタP4及び第1抵抗R1の素子の両端電圧に関する温度特性を好適に選定することで両者の電圧変動は打ち消され、p型トランジスタP4と定電流源I1との接続点の電圧は温度に依存しない一定値となる。

【0022】

この電圧は、演算増幅器A1の反転入力端に入力されており、演算増幅器A1のイマジナリショートのはたらきにより非反転入力端すなわちp型トランジスタP5と第2抵抗R2との接続点の電圧も温度に依存しない一定値となる。そして、p型トランジスタP5と第2抵抗R2を流れる電流を一定にする電圧が、演算増幅器A1の出力端に現れることとなる。

【0023】

この演算増幅器A1の温度に依存しない出力電圧は、p型トランジスタP6にも与えられているため、これに接続されているn型トランジスタN0には温度に依存しない一定の電流が流れる。n型トランジスタN0を基準トランジスタとし、インバータ回路の各n型トランジスタN1、N2、N3をミラートランジスタとするカレントミラーを構成しているので、インバータ回路の各n型トランジスタには、n型トランジスタN0とのミラー比に応じた電流が流れる。

【0024】

したがって、温度依存のない定電流がリングオシレータOSCの各インバータ回路に供給されるので、リングオシレータOSCでも温度に依存されず、精度のよい安定した発振周波数を出力することができる。

【0025】

次に、製造ばらつきにより、各インバータ回路を構成するp型トランジスタP1、P2、P3の閾値電圧が高くなると、リングオシレータOSC自体の発振周波数は低くなるが、p型トランジスタP4のターンオン電圧も高くなり、演算増幅器A1の反転入力端の電圧は上昇し、出力端の電圧は下降する。したがって、各p型トランジスタP5、P6に流れる電流が大きくなり、リングオシレータOSCの各n型トランジスタN1、N2、N3に流れる電流も大きくなる。この結果、リングオシレータOSCの発振周波数が上がるように補正がかかる。

【0026】

逆に、p型トランジスタP1、P2、P3の閾値電圧が低くなると、リングオシレータOSC自体の発振周波数は高くなるが、p型トランジスタP4のターンオン電圧も低くなり、演算増幅器A1の反転入力端の電圧は下がり、出力端の電圧は上昇する。したがって、各p型トランジスタP5、P6に流れる電流が小さくなり、リングオシレータOSCの各n型トランジスタN1、N2、N3に流れる電流も小さくなる。この結果、リングオシレータOSCの発振周波数が下がるように補正がかかる。こうして発振周波数の変化の割合と、p型トランジスタP1、P2、P3の閾値電圧変化に追随したn型トランジスタN1、N2、N3に流れる電流変化の割合を合わせることで、製造ばらつきについての補正をかけている。

【0027】

以上説明したように、リングオシレータOSCを構成するインバータ回路の入力反転用トランジスタと同じ導電型のp型トランジスタP4をダイオード接続すると共に第1抵抗R1を介して接地し、これに定電流を流すことで、製造ばらつきによる閾値電圧変動に追随したターンオン電圧を得て、この電圧をリングオシレータOSCに流す電流の制御に利用する構成としたので、発振周波数の閾値電圧の製造ばらつきについて補正をかけることができる。なお、発振回路100の第2抵抗R2を半導体集積回路に組み込まずに外部接続し、この第2抵抗R2を調整することにより周波数を容易に調整することもできる。

【0028】

尚、本発明の第1実施例の発振回路100では、回路の温度が上昇した場合、p型トランジスタP4のソースとドレイン間の電圧が下がる場合で説明したが、これとは逆の温度特性となる場合には、第1抵抗R1を負の抵抗値温度特性を持つ例えばポリシリ抵抗とすればよい。また、本発明の第1実施例の発振回路100とは逆に、電源とグラウンド及び各トランジスタのn型とp型の極性を反転させた回路構成としてもよい。

【産業上の利用可能性】

【0029】

本発明の発振回路は、MOSトランジスタの閾値電圧の製造ばらつきを補償する必要のある発振回路に広く適用できる。例えば、近年のDVDやMDなどの光ディスクの情報を読みとるための光ピックアップ用レーザーダイオード駆動回路で使用されている高周波重畳モジュール内の発振回路である。高周波重畳モジュールは、種々のレーザーノイズを低減するために、レーザーダイオード駆動電流に数百MHzの高周波電流を重畳する役割をしており、発振周波数の安定性が求められている。

【図面の簡単な説明】

【0030】

【図1】本発明の第1実施例の発振回路図。

【図2】従来例の発振回路図。

【符号の説明】

【0031】

CI1、CI2 定電流回路

I1、I2 定電流源

N0、N7 n型トランジスタ

N1、N2、N3 n型トランジスタ

OSC リングオシレータ

P1、P2、P3 p型トランジスタ

P4、P5、P6 p型トランジスタ

R1、R2 抵抗

VDD 電源

100、200 発振回路

【特許請求の範囲】

【請求項1】

入力反転用MOSトランジスタと負荷用MOSトランジスタとからなるインバータがリング状に奇数段接続されたリングオシレータと、負荷用MOSトランジスタに定電流を供給する定電流回路とを具備した発振回路において、

前記定電流回路は、前記入力反転用MOSトランジスタの閾値電圧に追随した定電圧を発生させる定電圧発生手段と、前記定電圧を前記定電流に変換する電圧電流変換手段とを有することを特徴とする発振回路。

【請求項2】

前記定電圧発生手段は、定電流源と、定電流源からの定電流により前記入力反転用MOSトランジスタの閾値電圧に追随した定電圧を出力する定電圧出力用MOSトランジスタとを有し、

前記電圧電流変換手段は、前記定電圧を反転増幅する反転増幅器と、反転増幅器の出力を定電流に変換して前記負荷用MOSトランジスタに供給する電圧電流変換回路とを有することを特徴とする請求項1記載の発振回路。

【請求項1】

入力反転用MOSトランジスタと負荷用MOSトランジスタとからなるインバータがリング状に奇数段接続されたリングオシレータと、負荷用MOSトランジスタに定電流を供給する定電流回路とを具備した発振回路において、

前記定電流回路は、前記入力反転用MOSトランジスタの閾値電圧に追随した定電圧を発生させる定電圧発生手段と、前記定電圧を前記定電流に変換する電圧電流変換手段とを有することを特徴とする発振回路。

【請求項2】

前記定電圧発生手段は、定電流源と、定電流源からの定電流により前記入力反転用MOSトランジスタの閾値電圧に追随した定電圧を出力する定電圧出力用MOSトランジスタとを有し、

前記電圧電流変換手段は、前記定電圧を反転増幅する反転増幅器と、反転増幅器の出力を定電流に変換して前記負荷用MOSトランジスタに供給する電圧電流変換回路とを有することを特徴とする請求項1記載の発振回路。

【図1】

【図2】

【図2】

【公開番号】特開2006−121250(P2006−121250A)

【公開日】平成18年5月11日(2006.5.11)

【国際特許分類】

【出願番号】特願2004−305107(P2004−305107)

【出願日】平成16年10月20日(2004.10.20)

【出願人】(000156950)関西日本電気株式会社 (26)

【公開日】平成18年5月11日(2006.5.11)

【国際特許分類】

【出願日】平成16年10月20日(2004.10.20)

【出願人】(000156950)関西日本電気株式会社 (26)

[ Back to top ]