直流電流電圧源および半導体試験装置

【課題】直流の電流および電圧を発生するときに、過剰な消費電力が出力アンプに作用しないように制御することを目的とする。

【解決手段】本発明の直流電流電圧源3は、出力設定部11により設定された設定電圧Vsetを出力する出力アンプ12と、出力アンプ12が出力する出力電圧V1と出力アンプ12に帰還されて入力される入力電圧V2とを入力して、出力アンプ12の消費電力Pampを演算する演算部19と、演算部19により演算された消費電力Pampが予め設定された設定電力Plimを超過しているか否かを比較する比較部20と、消費電力Pampが設定電力Plimを超過しているときには、出力設定部11の設定値を低下させる制御を行う制御部21と、を備えている。

【解決手段】本発明の直流電流電圧源3は、出力設定部11により設定された設定電圧Vsetを出力する出力アンプ12と、出力アンプ12が出力する出力電圧V1と出力アンプ12に帰還されて入力される入力電圧V2とを入力して、出力アンプ12の消費電力Pampを演算する演算部19と、演算部19により演算された消費電力Pampが予め設定された設定電力Plimを超過しているか否かを比較する比較部20と、消費電力Pampが設定電力Plimを超過しているときには、出力設定部11の設定値を低下させる制御を行う制御部21と、を備えている。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は直流の電流または電圧を出力する直流電流電圧源およびこの直流電流電圧源を適用した半導体試験装置に関するものである。

【背景技術】

【0002】

被試験デバイス(DUT:Device Under Test)に直流の電流または電圧を印加して、DUTの良否判定を行う半導体試験装置が用いられている。このために、半導体試験装置に直流電流および直流電圧を出力する直流電流電圧源を設けて、直流電流および直流電圧をDUTに出力する。この種の直流電流電圧源を用いた半導体試験装置としては例えば特許文献1に開示されている技術がある。

【0003】

従来の直流電流電圧源の一例を図3に示す。同図に示すように、直流電流電圧源101はDUT102と直流電流電圧ユニット103とを有して構成している。DUT102は被試験デバイスであり、所定の内部抵抗(DUT抵抗Rdut)と所定の内部電圧(DUT電圧vdut)とを有している。

【0004】

直流電流電圧ユニット103は出力設定部111と出力アンプ112と抵抗113と第1バッファアンプ114と第2バッファアンプ115と第3バッファアンプ116と電流検出アンプ117とスイッチ118とを備えている。出力設定部111は設定電圧Vsetを出力アンプ112に設定するデジタルアナログコンバータである。

【0005】

出力アンプ112は設定された設定電圧Vsetに基づいて、出力電圧V1を出力する。DUT102への印加電圧をvdとすると、出力アンプ112の出力側に接続された抵抗113(抵抗値R1)に出力電圧V1が出力されることで、印加電流id(=(V1―vd)/R1)が流れる。また、DUT102には印加電圧vdが印加される。

【0006】

第1バッファアンプ114および第2バッファアンプ115は抵抗113の両端に接続されるバッファアンプであり、電流検出アンプ117に抵抗113の両端の電圧を出力している。第3バッファアンプ116は印加電圧vdを出力アンプ112に負帰還させるためのアンプであり、出力アンプ112の反転入力端子に入力電圧V2として入力される。

【0007】

電流検出アンプ117は抵抗113の両端の電圧を検出しており、検出した電圧を検出電圧id×R1として出力アンプ112に負帰還させている。この検出電圧id×R1は出力アンプ112の反転入力端子に入力電圧V2として入力される。抵抗値R1は既知であるため、電流検出アンプ117が検出電圧id×R1(=入力電圧V2)を検出することで、抵抗113を流れる印加電流idを検出している。

【0008】

スイッチ118はa側に接続したときには電圧源モードになっており、印加電圧vdが出力アンプ112に負帰還される。出力アンプ112の非反転入力端子には設定電圧Vsetが入力されており、反転入力端子に入力された印加電圧vdを設定電圧Vsetに近づけようとする。これにより、「Vset≒V2=vd」となる。つまり、印加電圧vdを設定電圧Vsetとなるように制御している。

【0009】

スイッチ118はb側に接続したときには電流源モードになっており、検出電圧id×R1が入力電圧V2として負帰還される。この場合も同様に、検出電圧id×R1を設定電圧Vsetに近づけようとする。これにより、「Vset≒V2=id×R1」となる。抵抗値R1は既知であるため、これにより印加電流idを設定電圧Vsetと抵抗値R1とに基づく値となるように制御している。

【0010】

従って、出力アンプ112により印加電圧vdおよび印加電流idの制御を行っている。このとき、出力アンプ112には消費電力Pampを生じる。この消費電力Pampは印加電流idの正負によって以下のようになる。

id≧0:Pamp=(vdd−V1)×id

id<0:Pamp=(Vss−V1)×id

【先行技術文献】

【特許文献】

【0011】

【特許文献1】特開2010−127820号公報

【発明の概要】

【発明が解決しようとする課題】

【0012】

近年の半導体試験装置は、多品種のDUT102の試験を行うために、多様な試験が要求されている。従って、DUT102に対して印加される印加電圧vdおよび印加電流idも広範囲な値が使用される。このとき、印加電圧vdおよび印加電流idの値に応じて出力アンプ112の消費電力Pampの値が大きくなる。

【0013】

前述した式における、出力電圧V1は「V1=vd+R1×id」となる。従って、消費電力Pampは印加電圧vdと印加電流idとによって規定される。前述した式から、印加電流idが正の場合には、印加電圧vdが低く且つ印加電流idが高くなるほど消費電力Pampが大きくなる。一方、印加電流idが負の場合には、印加電圧vdが高く且つ電流が低くなるほど消費電力Pampが大きくなる。

【0014】

出力アンプ112には設計や実装面積、或いは冷却構成の関係から、消費電力Pampには所定の上限値が存在する。この上限値を超過した消費電力Pampが出力アンプ112に作用すると、出力アンプ112が故障する。図4は印加電圧vdと印加電流idとの積の領域を示している。

【0015】

この図に示されるZ1は安全領域であり、消費電力Pampが上限値を超過していない領域を示している。Z2は危険領域であり、消費電力Pampが上限値を超過している領域を示している。前述したように、印加電流idが正の場合には、印加電圧vdが低く且つ印加電流idが高くなると消費電力Pampは大きくなり、危険領域Z2の範囲内になる。一方、印加電流idが負の場合には、印加電圧vdが高く且つ印加電流idが低くなると消費電力Pampは大きくなり、危険領域Z2の範囲内になる。この危険領域Z2の範囲内にあるときには出力アンプ112が故障する。

【0016】

印加電圧vdと印加電流idとは共に出力アンプ112の設定を行う設定電圧Vsetをコントロールすることにより制御される。従って、印加電圧vdと印加電流idとに基づく図4の値が危険領域Z2に位置しないように、設定電圧Vsetを制御する。この制御はユーザ等が設定電圧Vsetの値に基づいて推測することにより行われる。

【0017】

従って、設定電圧Vsetに基づいて推測により出力アンプ112の消費電力Pampが制御されていることになる。このため、実際には出力アンプ112の消費電力Pampが上限値を超過しているにもかかわらず、そのことがユーザ等に認識されない場合がある。

【0018】

例えば、DUT102は所定のDUT電圧vdutを持つ。このとき、DUT102のDUT抵抗Rdutがゼロの場合、DUT102から直接的にvdutが直流電流電圧ユニット103に入力される。このときのvdutが図4で示す電圧範囲の最小値VLLであるとする。

【0019】

一方、直流電源ユニット103が電流源モードで動作していた場合、出力アンプ112から出力された出力電圧V1により抵抗113に印加電流idが流れ、電流検出アンプ117で印加電流idが検出される。そして、検出電圧id×R1が入力電圧V2として出力アンプ112に入力されることで、電流は制御される。

【0020】

このとき、出力設定部111は印加電流idが電流範囲の最大値IHLとなるように設定していたとする。これにより、印加電圧vdは「vd=VLL」となり、印加電流idは「id≧IHL」となる。従って、出力アンプ112の消費電力Pampは図4で示した危険領域D2に位置することになる。これにより、出力アンプ112に故障を生じることになる。

【0021】

そこで、本発明は、直流の電流および電圧を発生するときに、過剰な消費電力が出力アンプに作用しないように制御することを目的とする。

【課題を解決するための手段】

【0022】

以上の課題を解決するため、本発明の直流電流電圧源は、出力設定部により設定された電圧を出力する出力アンプと、この出力アンプが出力する出力電圧と前記出力アンプに帰還されて入力される入力電圧とを入力して、前記出力アンプの消費電力を演算する演算部と、この演算部により演算された前記消費電力が予め設定された設定電力を超過しているか否かを比較する比較部と、前記消費電力が前記設定電力を超過しているときには、前記出力設定部の設定値を低下させる制御を行う制御部と、を備えたことを特徴とする。

【0023】

この直流電流電圧源によれば、出力アンプの出力電圧と入力電圧とに基づいて演算および比較を行って、出力設定部の設定値を低下させる制御を行っている。これにより、リアルタイムに消費電力の状況を監視することができ、過剰な消費電力が出力アンプに作用することがなくなる。

【0024】

また、前記出力アンプの消費電力をPamp、出力側に接続される抵抗をR1、正電源をvdd、負電源をVss、前記出力電圧をV1、前記入力電圧をV2、前記設定電力をPlimとしたときに、前記演算部は、V2≧0のときに「Pamp×R1=(vdd−V1)×V2」、V2<0のときに「Pamp×R1=(Vss−V1)×V2」、を演算し、前記比較部は、「Pamp×R1」と「Plim×R1」とを比較し、前記制御部は、「Pamp×R1>Plim×R1」のときには、「Pamp=Plim」となるように前記出力設定部を制御し、「Pamp×R1≦Plim×R1」のときには、前記出力設定部の値を維持させることを特徴とする。

【0025】

演算部は前記の式を用いて演算を行って、比較部が比較を行うことができる。比較の対象を消費電力Pampと抵抗値R1との積にしていることにより、出力電圧V1と入力電圧V2という2つの電圧の積を用いることができる。これにより、単純な回路を用いた比較を行うことができる。

【0026】

また、前記出力アンプと前記演算部と前記比較部と前記制御部とを備えた直流電流電圧ユニットを複数備え、各直流電流電圧ユニットの前記演算部から前記消費電力Pampを取得して合計して合計消費電力Ptampとし、この合計消費電力Ptampが予め設定され合計設定電力Ptlimより大きいときには、前記合計消費電力Ptampが前記合計設定電力Ptlim以下となるように各直流電流電圧ユニットの前記制御部に対して前記出力設定部の設定値を低下させる制御を行わせる合計比較部を備えたことを特徴とする。

【0027】

1つの直流電流電圧ユニットに過剰な消費電力が生じていない場合でも、複数の直流電流電圧ユニットが熱的に干渉して、出力アンプに過剰な熱が作用することがある。このために、合計比較部が合計消費電力を比較して、各直流電流電圧ユニットを制御することで、出力アンプの故障を生じないようにしている。

【0028】

また、前記比較部により前記消費電力が前記設定電力を超過していると判定されたときは、警報を鳴動するアラームを備えたことを特徴とする。

【0029】

消費電力が設定電力を超過したときに、アラームが警報を鳴動することで、消費電力の異常をユーザ等に認識させることができるようになる。

【0030】

また、本発明の半導体試験装置は、前述の何れかの直流電流電圧源を備えたことを特徴とする。直流電流電圧源は半導体試験装置が試験を行うときに被試験デバイスに印加する電流または電圧を発生させるための装置として用いることができる。

【発明の効果】

【0031】

本発明は、出力アンプの出力電圧と入力電圧とに基づいて出力アンプの消費電力を演算し、消費電力が設定電力以下となるように出力設定部を制御していることから、リアルタイムに出力アンプの消費電力の管理を行うことができる。これにより、出力アンプに過剰な消費電力が作用しなくなり、アンプの故障を生じることがなくなる。

【図面の簡単な説明】

【0032】

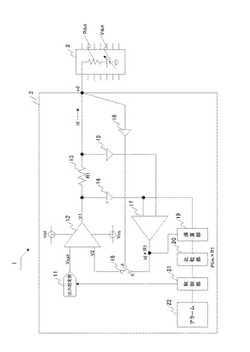

【図1】実施形態の半導体試験装置の構成図である。

【図2】複数の直流電流電圧ユニットを設けた変形例の説明図である。

【図3】従来の半導体試験装置の構成図である。

【図4】安全領域と危険領域とを説明するための図である。

【発明を実施するための形態】

【0033】

以下、本発明の実施形態について図面を参照して説明する。本実施形態では、被試験デバイス(DUT:Device Under Test)の試験を行うための半導体試験装置に直流電流電圧源を用いているが、直流の電流および電圧を印加させる装置であれば、任意の装置に本実施形態の直流電流電圧源を用いることができる。

【0034】

図1において、半導体試験装置1はDUT2に直流電流電圧源3が接続されている。DUT2は直流電流電圧源3から電流または電圧が印加されて試験が行われる被試験デバイスである。このDUT2の内部には所定の内部抵抗(DUT抵抗Rdut)および所定の内部電圧(DUT電圧vdut)が存在している。

【0035】

直流電流電圧源3は出力設定部11と出力アンプ12と抵抗13と第1バッファアンプ14と第2バッファアンプ15と第3バッファアンプ16と電流検出アンプ17とスイッチ18と演算部19と比較部20と制御部21とアラーム22とを備えて構成している。

【0036】

出力設定部11は出力アンプ12が出力する電圧を制御するデジタルアナログコンバータである。従って、出力設定部11にはデジタル値としての電圧が設定されて、設定された電圧をアナログの設定電圧Vsetとして出力する。この設定電圧Vsetが出力アンプ12に設定される。

【0037】

出力アンプ12は2つの入力端子(非反転入力端子および反転入力端子)と1つの出力端子を有しており、正電源vddと負電源Vssとに接続されている。非反転入力端子には出力設定部11が設定する設定電圧Vsetが入力される。反転入力端子には入力電圧V2が入力されている。そして、出力アンプ12からは出力電圧V1が出力される。

【0038】

抵抗13は抵抗値R1の抵抗であり、出力アンプ12に接続されている。出力アンプ12が出力する出力電圧V1により抵抗13には印加電流id(=V1/R1)が流れる。この印加電流idがDUT2に対して印加される。また、出力アンプ12からは印加電圧vdがDUT2に対して印加される。

【0039】

第1バッファアンプ14および第2バッファアンプ15は抵抗13の両端に接続されており、抵抗13の両端の電位差(電圧)を電流検出アンプ17に出力している。このうち、抵抗13の出力アンプ12の側の電位、つまり出力アンプ12の出力電圧V1が演算部19に対して出力される。第3バッファアンプ16は印加電圧vdを入力電圧V2として出力アンプ12に入力させる。

【0040】

電流検出アンプ17は抵抗13の両端の電圧を検出電圧id×R1として検出している。抵抗13の抵抗値R1は既知であるため、電流検出アンプ17は印加電流idを検出していることになる。この検出電圧id×R1を入力電圧V2として出力アンプ12に入力させる。

【0041】

スイッチ18は電流源モードと電圧源モードとを切り替えるスイッチであり、a側とb側とに切り替えることで、第3バッファアンプ16と電流検出アンプ17とのうち何れかを出力アンプ12の反転入力端子に接続する。電圧モードのときにはa側にスイッチを切り替え、印加電圧vdを入力電圧V2として入力させる。電流モードのときにはb側にスイッチを切り替え、検出電圧id×R1を入力電圧V2として入力させる。

【0042】

従って、電圧モードのときには印加電圧vdが出力アンプ12に負帰還され、電流モードのときには印加電流id×R1が出力アンプ12に負帰還される。つまり、電圧および電流の不帰還の回路が構成される。

【0043】

演算部19は出力アンプ12の出力電圧V1および電流検出アンプ17の検出電圧id×R1(つまり、入力電圧V2)を入力する。そして、出力アンプ12の消費電力をPampとしたときに、以下の式1の演算を行う。

式1:

V2≧0:Pamp×R1=(vdd−V1)×V2

V2<0:Pamp×R1=(Vss−V1)×V2

従って、演算部19が行う演算は乗算および減算になる。よって、演算部19は乗算回路と減算回路を有して構成する。例えば、これらの回路はオペアンプとトランジスタとにより構成される簡単な回路になる。

【0044】

比較部20は演算部19が演算したPamp×R1の比較を行う。比較部20には予め消費電力Pampの上限値が設定電力Plimとして設定されており、Plim×R1として記憶している。この設定電力Plim×R1とPamp×R1との比較を行う。比較の結果は制御部21に出力される。比較部20は簡単なコンパレータ回路により構成される。

【0045】

制御部21は比較部20の比較結果に基づいて、所定の制御を行う。比較部20の比較結果が「Pamp×R1>Plim×R1」であるときには、出力設定部11の設定電圧Vsetの値を低下させる制御を行う。これは、「Pamp×R1=Plim×R1」となるまで設定電圧Vsetの値が低下するまで行われる。且つ、このときには、その旨をアラーム22に通知する。一方、「Pamp×R1≦Plim×R1」のときには、格別の制御は行わない。

【0046】

制御部21としては一般的なアナログコントローラとして使用されるFPGA(Field Programmable Gate Array)により構成される。アラーム22は警報を鳴動し、制御部21から「Pamp×R1>Plim×R1」であることが通知されたときには、警報を鳴動する。

【0047】

次に、動作について説明する。出力設定部11が設定電圧Vsetを設定する。これにより、出力アンプ12から出力電圧V1が出力されて、抵抗13に印加電流idが流れて、DUT2に印加される。また、出力アンプ12が出力した出力電圧V1に基づいて、印加電圧vdがDUT2に印加される。これにより、DUT2の電流印加試験または電圧印加試験が行われる。

【0048】

電圧モードのときには、スイッチ18はa側に切り替えられる。これにより、印加電圧vdが入力電圧V2として出力アンプ12に負帰還される。出力アンプ12では入力電圧V2が設定電圧Vsetに近づくように作用する。これにより、印加電圧vdが制御される(Vset≒V2=vd)。

【0049】

一方、電流モードのときには、スイッチ18はb側に切り替えられる。これにより、印加電流idが電流検出アンプ17により検出電圧id×R1として検出され、入力電圧V2として出力アンプ12に負帰還される。出力アンプ12では入力電圧V2が設定電圧Vsetに近づくように作用するため、印加電流idが制御される(Vset≒V2=id×R1)。

【0050】

演算部19はリアルタイムに出力電圧V1と検出電圧id×R1(V2)とを入力している。そして、前述した式1の演算を常に行っている。式1のうち、正電源vdd、負電源Vss、抵抗値R1は既知であり、演算部19には出力電圧V1と入力電圧V2(=id×R1)が入力される。従って、消費電力Pampを演算することができる。

【0051】

ただし、演算部19は消費電力Pampを演算するのではなく、消費電力Pampに抵抗値R1を乗じたPamp×R1の形で演算して比較部20に出力する。この点、抵抗値R1は既知の値であり、演算部19は実質的に消費電力Pampを演算していることになる。

【0052】

演算部19は常にPamp×R1を演算しており、これに伴い比較部20も常に前述した比較を行っている。出力電圧V1および入力電圧V2はその値が変動することがあり、よって消費電力Pampも変動する。比較部20には消費電力Pampの上限値が設定電力Plimとして設定されている。ただし、Plim×R1の形で設定されている。

【0053】

比較部20は、設定されているPlim×R1と演算部19が演算したPamp×R1との比較を行う。そして、比較の結果を制御部21に出力する。式1で示したように、消費電力Pampを演算するために、出力電圧V1と入力電圧V2との2つの電圧の積を用いている。

【0054】

消費電力Pampと電圧の2乗との単位とは異なるが、消費電力Pampに抵抗値R1を乗じることにより、比較の単位を統一することができる。これにより、比較部20は単純な比較回路で構成することができる。

【0055】

制御部21は、比較部20の比較の結果が「Pamp×R1>Plim×R1」のときには、過剰な消費電力Pampが作用していることを認識する。これにより、出力設定部11を制御して、idの極性によっては低下させると消費電力が増える。出力アンプ12は設定電圧Vsetが低下することで、消費電力Pampが低下する。従って、過剰な消費電力Pampが作用することに起因する出力アンプ12の故障を回避することができる。

【0056】

これと共に、制御部21は過剰な消費電力Pampが作用したことをユーザ等に了知させるために、アラーム22を鳴動させる。これにより、ユーザ等は消費電力Pampの異常を迅速に把握することができる。

【0057】

演算部19と比較部20と制御部21とは常に動作を行っており、出力アンプ12の消費電力Pampをリアルタイムに監視している。これにより、印加電流idと印加電圧vdとに基づく値が安全領域Z1から危険領域Z2に入ったときに設定電圧Vsetを制御する。従って、迅速且つ自動的に安全領域Z1に戻すことができるようになる。

【0058】

一方、制御部21は、比較部20の比較の結果が「Pamp×R1≦Plim×R1」のときには、過剰な消費電力Pampは作用していないことを認識する。このときには、格別に出力アンプ12の消費電力Pampを低下させる必要はないため、出力設定部11の設定電圧Vsetはそのままの値を維持させる。つまり、格別な制御は行わない。

【0059】

ところで、DUT2は内部電圧(DUT電圧vdut)を有しており、内部抵抗(DUT抵抗Rdut)がゼロの場合には、DUT電圧vdutが直流電流電圧源3に作用する。このときに、DUT電圧vdutが図4に示した電圧範囲の最小値のVLLであるとする。

【0060】

このDUT電圧vdutは印加電圧vdと一致する。そして、この印加電圧vdが直接的或いは間接的に出力アンプ12に作用するため、出力アンプ12の消費電力Pampに影響を及ぼす。ただし、DUT電圧vdutが作用したとしても、演算部19と比較部20と制御部21とは出力アンプ12の出力電圧V1と入力電圧V2とをリアルタイムに監視して設定電圧Vsetの制御を行っているため、出力アンプ12に過剰な消費電力Pampが作用することはない。

【0061】

例えば、電流源モードにて、設定電圧Vset=R1×IHL(IHLは図4の電流範囲の最大値)となるように設定していたとする。つまり、高い電流値を印加するように設定していたとする。また、DUT電圧vdutは図4の電圧範囲の最小値VLLと等しい場合を想定すると(vdut=VLL)、印加電圧vdはVLLと等しくなる(vd=VLL)。

【0062】

このとき、従来の場合には、「vd=VLL」、「id≧IHL」となり、危険領域Z2に位置することになる。これにより、過剰な消費電力Pampが出力アンプ12に作用し、出力アンプ12が故障する。

【0063】

一方、本実施形態では、演算部19が消費電力Pamp×R1を演算して、比較部20が比較を行い、制御部21が「Pamp×R1=Plim×R1」となるように、つまり「Pamp=Plim」となるように出力設定部11の制御を行っている。従って、過剰な消費電力Pampが出力アンプ12に作用することなく、出力アンプ12が故障することはない。このときの印加電圧vdは「vd=VLL」となり、印加電流idは「id≦Plim/(vdd−VLL)」となる。

【0064】

次に、図2を用いて、変形例について説明する。この変形例では、直流電流電圧源3はN(Nは2以上の整数)個を備えており、それぞれ直流電流電圧ユニット3−1〜3−Nとする。各直流電流電圧ユニット3−1〜3−Nには前述した構成が備えられている。図2では、そのうち演算部19と制御部21とを示している。

【0065】

各直流電流電圧ユニット3−1〜3−Nの演算部19は合計比較部30に接続されている。つまり、各演算部19は式1で演算したPamp×R1を合計比較部30に出力している。合計比較部30は各演算部19から入力したPamp×R1を合計して、合計消費電力Ptampを演算する。

【0066】

合計比較部30には合計消費電力Ptampと比較するための合計設定電力Ptlimが設定されている。そして、合計したPtampとPtlimとの比較を行って、「Ptamp>Ptlim」となっているときには、各直流電流電圧ユニット3−1〜3−Nの全て或いは一部の制御部21にその旨を通知する。

【0067】

この旨の通知を受領した制御部21は出力設定部11を制御して、設定電圧Vsetを低下させる制御を行う。これにより、N個の直流電流電圧ユニット3−1〜3−Nの合計消費電力Ptampも低下する。この作業を「Patmp≦Ptlim」となるまで行う。

【0068】

半導体試験装置1にN個の直流電流電圧ユニット3−1〜3―Nを備えるようにした場合には、各直流電流電圧ユニット3−1〜3−Nが熱的に相互に干渉し、出力アンプ12に過剰な熱量が与えられることになる。各直流電流電圧ユニット3の個々の出力アンプ12の消費電力Pampが適正であるとしても、全体としての合計消費電力Ptampが過剰になると、やはり出力アンプ12に熱作用による故障を生じる。

【0069】

そこで、個々の出力アンプ12の消費電力Pampが適正である場合でも、全体の合計消費電力Ptampが上限値である合計設定電力Ptlimを超過したときには、直流電流電圧ユニット3−1〜3−Nの設定電圧Vsetを低下させる。これにより、全体の消費電力としても適正なコントロールを行うことが可能になる。

【0070】

このとき、合計比較部30は各直流電流電圧ユニット3−1〜3−Nのうち、一部の熱に弱い直流電流電圧ユニット3−1〜3−Nの設定電圧Vsetを優先的に下げるように制御してもよい。また、全ての直流電流電圧ユニット3−1〜3−Nの設定電圧Vsetを均等に低下させると、簡単な制御が実現できる。

【符号の説明】

【0071】

1 半導体試験装置

3 直流電流電圧源(直流電流電圧ユニット)

11 出力設定部

12 出力アンプ

13 抵抗

17 電流検出アンプ

18 スイッチ

19 演算部

20 比較部

21 制御部

22 アラーム

30 合計比較部

【技術分野】

【0001】

本発明は直流の電流または電圧を出力する直流電流電圧源およびこの直流電流電圧源を適用した半導体試験装置に関するものである。

【背景技術】

【0002】

被試験デバイス(DUT:Device Under Test)に直流の電流または電圧を印加して、DUTの良否判定を行う半導体試験装置が用いられている。このために、半導体試験装置に直流電流および直流電圧を出力する直流電流電圧源を設けて、直流電流および直流電圧をDUTに出力する。この種の直流電流電圧源を用いた半導体試験装置としては例えば特許文献1に開示されている技術がある。

【0003】

従来の直流電流電圧源の一例を図3に示す。同図に示すように、直流電流電圧源101はDUT102と直流電流電圧ユニット103とを有して構成している。DUT102は被試験デバイスであり、所定の内部抵抗(DUT抵抗Rdut)と所定の内部電圧(DUT電圧vdut)とを有している。

【0004】

直流電流電圧ユニット103は出力設定部111と出力アンプ112と抵抗113と第1バッファアンプ114と第2バッファアンプ115と第3バッファアンプ116と電流検出アンプ117とスイッチ118とを備えている。出力設定部111は設定電圧Vsetを出力アンプ112に設定するデジタルアナログコンバータである。

【0005】

出力アンプ112は設定された設定電圧Vsetに基づいて、出力電圧V1を出力する。DUT102への印加電圧をvdとすると、出力アンプ112の出力側に接続された抵抗113(抵抗値R1)に出力電圧V1が出力されることで、印加電流id(=(V1―vd)/R1)が流れる。また、DUT102には印加電圧vdが印加される。

【0006】

第1バッファアンプ114および第2バッファアンプ115は抵抗113の両端に接続されるバッファアンプであり、電流検出アンプ117に抵抗113の両端の電圧を出力している。第3バッファアンプ116は印加電圧vdを出力アンプ112に負帰還させるためのアンプであり、出力アンプ112の反転入力端子に入力電圧V2として入力される。

【0007】

電流検出アンプ117は抵抗113の両端の電圧を検出しており、検出した電圧を検出電圧id×R1として出力アンプ112に負帰還させている。この検出電圧id×R1は出力アンプ112の反転入力端子に入力電圧V2として入力される。抵抗値R1は既知であるため、電流検出アンプ117が検出電圧id×R1(=入力電圧V2)を検出することで、抵抗113を流れる印加電流idを検出している。

【0008】

スイッチ118はa側に接続したときには電圧源モードになっており、印加電圧vdが出力アンプ112に負帰還される。出力アンプ112の非反転入力端子には設定電圧Vsetが入力されており、反転入力端子に入力された印加電圧vdを設定電圧Vsetに近づけようとする。これにより、「Vset≒V2=vd」となる。つまり、印加電圧vdを設定電圧Vsetとなるように制御している。

【0009】

スイッチ118はb側に接続したときには電流源モードになっており、検出電圧id×R1が入力電圧V2として負帰還される。この場合も同様に、検出電圧id×R1を設定電圧Vsetに近づけようとする。これにより、「Vset≒V2=id×R1」となる。抵抗値R1は既知であるため、これにより印加電流idを設定電圧Vsetと抵抗値R1とに基づく値となるように制御している。

【0010】

従って、出力アンプ112により印加電圧vdおよび印加電流idの制御を行っている。このとき、出力アンプ112には消費電力Pampを生じる。この消費電力Pampは印加電流idの正負によって以下のようになる。

id≧0:Pamp=(vdd−V1)×id

id<0:Pamp=(Vss−V1)×id

【先行技術文献】

【特許文献】

【0011】

【特許文献1】特開2010−127820号公報

【発明の概要】

【発明が解決しようとする課題】

【0012】

近年の半導体試験装置は、多品種のDUT102の試験を行うために、多様な試験が要求されている。従って、DUT102に対して印加される印加電圧vdおよび印加電流idも広範囲な値が使用される。このとき、印加電圧vdおよび印加電流idの値に応じて出力アンプ112の消費電力Pampの値が大きくなる。

【0013】

前述した式における、出力電圧V1は「V1=vd+R1×id」となる。従って、消費電力Pampは印加電圧vdと印加電流idとによって規定される。前述した式から、印加電流idが正の場合には、印加電圧vdが低く且つ印加電流idが高くなるほど消費電力Pampが大きくなる。一方、印加電流idが負の場合には、印加電圧vdが高く且つ電流が低くなるほど消費電力Pampが大きくなる。

【0014】

出力アンプ112には設計や実装面積、或いは冷却構成の関係から、消費電力Pampには所定の上限値が存在する。この上限値を超過した消費電力Pampが出力アンプ112に作用すると、出力アンプ112が故障する。図4は印加電圧vdと印加電流idとの積の領域を示している。

【0015】

この図に示されるZ1は安全領域であり、消費電力Pampが上限値を超過していない領域を示している。Z2は危険領域であり、消費電力Pampが上限値を超過している領域を示している。前述したように、印加電流idが正の場合には、印加電圧vdが低く且つ印加電流idが高くなると消費電力Pampは大きくなり、危険領域Z2の範囲内になる。一方、印加電流idが負の場合には、印加電圧vdが高く且つ印加電流idが低くなると消費電力Pampは大きくなり、危険領域Z2の範囲内になる。この危険領域Z2の範囲内にあるときには出力アンプ112が故障する。

【0016】

印加電圧vdと印加電流idとは共に出力アンプ112の設定を行う設定電圧Vsetをコントロールすることにより制御される。従って、印加電圧vdと印加電流idとに基づく図4の値が危険領域Z2に位置しないように、設定電圧Vsetを制御する。この制御はユーザ等が設定電圧Vsetの値に基づいて推測することにより行われる。

【0017】

従って、設定電圧Vsetに基づいて推測により出力アンプ112の消費電力Pampが制御されていることになる。このため、実際には出力アンプ112の消費電力Pampが上限値を超過しているにもかかわらず、そのことがユーザ等に認識されない場合がある。

【0018】

例えば、DUT102は所定のDUT電圧vdutを持つ。このとき、DUT102のDUT抵抗Rdutがゼロの場合、DUT102から直接的にvdutが直流電流電圧ユニット103に入力される。このときのvdutが図4で示す電圧範囲の最小値VLLであるとする。

【0019】

一方、直流電源ユニット103が電流源モードで動作していた場合、出力アンプ112から出力された出力電圧V1により抵抗113に印加電流idが流れ、電流検出アンプ117で印加電流idが検出される。そして、検出電圧id×R1が入力電圧V2として出力アンプ112に入力されることで、電流は制御される。

【0020】

このとき、出力設定部111は印加電流idが電流範囲の最大値IHLとなるように設定していたとする。これにより、印加電圧vdは「vd=VLL」となり、印加電流idは「id≧IHL」となる。従って、出力アンプ112の消費電力Pampは図4で示した危険領域D2に位置することになる。これにより、出力アンプ112に故障を生じることになる。

【0021】

そこで、本発明は、直流の電流および電圧を発生するときに、過剰な消費電力が出力アンプに作用しないように制御することを目的とする。

【課題を解決するための手段】

【0022】

以上の課題を解決するため、本発明の直流電流電圧源は、出力設定部により設定された電圧を出力する出力アンプと、この出力アンプが出力する出力電圧と前記出力アンプに帰還されて入力される入力電圧とを入力して、前記出力アンプの消費電力を演算する演算部と、この演算部により演算された前記消費電力が予め設定された設定電力を超過しているか否かを比較する比較部と、前記消費電力が前記設定電力を超過しているときには、前記出力設定部の設定値を低下させる制御を行う制御部と、を備えたことを特徴とする。

【0023】

この直流電流電圧源によれば、出力アンプの出力電圧と入力電圧とに基づいて演算および比較を行って、出力設定部の設定値を低下させる制御を行っている。これにより、リアルタイムに消費電力の状況を監視することができ、過剰な消費電力が出力アンプに作用することがなくなる。

【0024】

また、前記出力アンプの消費電力をPamp、出力側に接続される抵抗をR1、正電源をvdd、負電源をVss、前記出力電圧をV1、前記入力電圧をV2、前記設定電力をPlimとしたときに、前記演算部は、V2≧0のときに「Pamp×R1=(vdd−V1)×V2」、V2<0のときに「Pamp×R1=(Vss−V1)×V2」、を演算し、前記比較部は、「Pamp×R1」と「Plim×R1」とを比較し、前記制御部は、「Pamp×R1>Plim×R1」のときには、「Pamp=Plim」となるように前記出力設定部を制御し、「Pamp×R1≦Plim×R1」のときには、前記出力設定部の値を維持させることを特徴とする。

【0025】

演算部は前記の式を用いて演算を行って、比較部が比較を行うことができる。比較の対象を消費電力Pampと抵抗値R1との積にしていることにより、出力電圧V1と入力電圧V2という2つの電圧の積を用いることができる。これにより、単純な回路を用いた比較を行うことができる。

【0026】

また、前記出力アンプと前記演算部と前記比較部と前記制御部とを備えた直流電流電圧ユニットを複数備え、各直流電流電圧ユニットの前記演算部から前記消費電力Pampを取得して合計して合計消費電力Ptampとし、この合計消費電力Ptampが予め設定され合計設定電力Ptlimより大きいときには、前記合計消費電力Ptampが前記合計設定電力Ptlim以下となるように各直流電流電圧ユニットの前記制御部に対して前記出力設定部の設定値を低下させる制御を行わせる合計比較部を備えたことを特徴とする。

【0027】

1つの直流電流電圧ユニットに過剰な消費電力が生じていない場合でも、複数の直流電流電圧ユニットが熱的に干渉して、出力アンプに過剰な熱が作用することがある。このために、合計比較部が合計消費電力を比較して、各直流電流電圧ユニットを制御することで、出力アンプの故障を生じないようにしている。

【0028】

また、前記比較部により前記消費電力が前記設定電力を超過していると判定されたときは、警報を鳴動するアラームを備えたことを特徴とする。

【0029】

消費電力が設定電力を超過したときに、アラームが警報を鳴動することで、消費電力の異常をユーザ等に認識させることができるようになる。

【0030】

また、本発明の半導体試験装置は、前述の何れかの直流電流電圧源を備えたことを特徴とする。直流電流電圧源は半導体試験装置が試験を行うときに被試験デバイスに印加する電流または電圧を発生させるための装置として用いることができる。

【発明の効果】

【0031】

本発明は、出力アンプの出力電圧と入力電圧とに基づいて出力アンプの消費電力を演算し、消費電力が設定電力以下となるように出力設定部を制御していることから、リアルタイムに出力アンプの消費電力の管理を行うことができる。これにより、出力アンプに過剰な消費電力が作用しなくなり、アンプの故障を生じることがなくなる。

【図面の簡単な説明】

【0032】

【図1】実施形態の半導体試験装置の構成図である。

【図2】複数の直流電流電圧ユニットを設けた変形例の説明図である。

【図3】従来の半導体試験装置の構成図である。

【図4】安全領域と危険領域とを説明するための図である。

【発明を実施するための形態】

【0033】

以下、本発明の実施形態について図面を参照して説明する。本実施形態では、被試験デバイス(DUT:Device Under Test)の試験を行うための半導体試験装置に直流電流電圧源を用いているが、直流の電流および電圧を印加させる装置であれば、任意の装置に本実施形態の直流電流電圧源を用いることができる。

【0034】

図1において、半導体試験装置1はDUT2に直流電流電圧源3が接続されている。DUT2は直流電流電圧源3から電流または電圧が印加されて試験が行われる被試験デバイスである。このDUT2の内部には所定の内部抵抗(DUT抵抗Rdut)および所定の内部電圧(DUT電圧vdut)が存在している。

【0035】

直流電流電圧源3は出力設定部11と出力アンプ12と抵抗13と第1バッファアンプ14と第2バッファアンプ15と第3バッファアンプ16と電流検出アンプ17とスイッチ18と演算部19と比較部20と制御部21とアラーム22とを備えて構成している。

【0036】

出力設定部11は出力アンプ12が出力する電圧を制御するデジタルアナログコンバータである。従って、出力設定部11にはデジタル値としての電圧が設定されて、設定された電圧をアナログの設定電圧Vsetとして出力する。この設定電圧Vsetが出力アンプ12に設定される。

【0037】

出力アンプ12は2つの入力端子(非反転入力端子および反転入力端子)と1つの出力端子を有しており、正電源vddと負電源Vssとに接続されている。非反転入力端子には出力設定部11が設定する設定電圧Vsetが入力される。反転入力端子には入力電圧V2が入力されている。そして、出力アンプ12からは出力電圧V1が出力される。

【0038】

抵抗13は抵抗値R1の抵抗であり、出力アンプ12に接続されている。出力アンプ12が出力する出力電圧V1により抵抗13には印加電流id(=V1/R1)が流れる。この印加電流idがDUT2に対して印加される。また、出力アンプ12からは印加電圧vdがDUT2に対して印加される。

【0039】

第1バッファアンプ14および第2バッファアンプ15は抵抗13の両端に接続されており、抵抗13の両端の電位差(電圧)を電流検出アンプ17に出力している。このうち、抵抗13の出力アンプ12の側の電位、つまり出力アンプ12の出力電圧V1が演算部19に対して出力される。第3バッファアンプ16は印加電圧vdを入力電圧V2として出力アンプ12に入力させる。

【0040】

電流検出アンプ17は抵抗13の両端の電圧を検出電圧id×R1として検出している。抵抗13の抵抗値R1は既知であるため、電流検出アンプ17は印加電流idを検出していることになる。この検出電圧id×R1を入力電圧V2として出力アンプ12に入力させる。

【0041】

スイッチ18は電流源モードと電圧源モードとを切り替えるスイッチであり、a側とb側とに切り替えることで、第3バッファアンプ16と電流検出アンプ17とのうち何れかを出力アンプ12の反転入力端子に接続する。電圧モードのときにはa側にスイッチを切り替え、印加電圧vdを入力電圧V2として入力させる。電流モードのときにはb側にスイッチを切り替え、検出電圧id×R1を入力電圧V2として入力させる。

【0042】

従って、電圧モードのときには印加電圧vdが出力アンプ12に負帰還され、電流モードのときには印加電流id×R1が出力アンプ12に負帰還される。つまり、電圧および電流の不帰還の回路が構成される。

【0043】

演算部19は出力アンプ12の出力電圧V1および電流検出アンプ17の検出電圧id×R1(つまり、入力電圧V2)を入力する。そして、出力アンプ12の消費電力をPampとしたときに、以下の式1の演算を行う。

式1:

V2≧0:Pamp×R1=(vdd−V1)×V2

V2<0:Pamp×R1=(Vss−V1)×V2

従って、演算部19が行う演算は乗算および減算になる。よって、演算部19は乗算回路と減算回路を有して構成する。例えば、これらの回路はオペアンプとトランジスタとにより構成される簡単な回路になる。

【0044】

比較部20は演算部19が演算したPamp×R1の比較を行う。比較部20には予め消費電力Pampの上限値が設定電力Plimとして設定されており、Plim×R1として記憶している。この設定電力Plim×R1とPamp×R1との比較を行う。比較の結果は制御部21に出力される。比較部20は簡単なコンパレータ回路により構成される。

【0045】

制御部21は比較部20の比較結果に基づいて、所定の制御を行う。比較部20の比較結果が「Pamp×R1>Plim×R1」であるときには、出力設定部11の設定電圧Vsetの値を低下させる制御を行う。これは、「Pamp×R1=Plim×R1」となるまで設定電圧Vsetの値が低下するまで行われる。且つ、このときには、その旨をアラーム22に通知する。一方、「Pamp×R1≦Plim×R1」のときには、格別の制御は行わない。

【0046】

制御部21としては一般的なアナログコントローラとして使用されるFPGA(Field Programmable Gate Array)により構成される。アラーム22は警報を鳴動し、制御部21から「Pamp×R1>Plim×R1」であることが通知されたときには、警報を鳴動する。

【0047】

次に、動作について説明する。出力設定部11が設定電圧Vsetを設定する。これにより、出力アンプ12から出力電圧V1が出力されて、抵抗13に印加電流idが流れて、DUT2に印加される。また、出力アンプ12が出力した出力電圧V1に基づいて、印加電圧vdがDUT2に印加される。これにより、DUT2の電流印加試験または電圧印加試験が行われる。

【0048】

電圧モードのときには、スイッチ18はa側に切り替えられる。これにより、印加電圧vdが入力電圧V2として出力アンプ12に負帰還される。出力アンプ12では入力電圧V2が設定電圧Vsetに近づくように作用する。これにより、印加電圧vdが制御される(Vset≒V2=vd)。

【0049】

一方、電流モードのときには、スイッチ18はb側に切り替えられる。これにより、印加電流idが電流検出アンプ17により検出電圧id×R1として検出され、入力電圧V2として出力アンプ12に負帰還される。出力アンプ12では入力電圧V2が設定電圧Vsetに近づくように作用するため、印加電流idが制御される(Vset≒V2=id×R1)。

【0050】

演算部19はリアルタイムに出力電圧V1と検出電圧id×R1(V2)とを入力している。そして、前述した式1の演算を常に行っている。式1のうち、正電源vdd、負電源Vss、抵抗値R1は既知であり、演算部19には出力電圧V1と入力電圧V2(=id×R1)が入力される。従って、消費電力Pampを演算することができる。

【0051】

ただし、演算部19は消費電力Pampを演算するのではなく、消費電力Pampに抵抗値R1を乗じたPamp×R1の形で演算して比較部20に出力する。この点、抵抗値R1は既知の値であり、演算部19は実質的に消費電力Pampを演算していることになる。

【0052】

演算部19は常にPamp×R1を演算しており、これに伴い比較部20も常に前述した比較を行っている。出力電圧V1および入力電圧V2はその値が変動することがあり、よって消費電力Pampも変動する。比較部20には消費電力Pampの上限値が設定電力Plimとして設定されている。ただし、Plim×R1の形で設定されている。

【0053】

比較部20は、設定されているPlim×R1と演算部19が演算したPamp×R1との比較を行う。そして、比較の結果を制御部21に出力する。式1で示したように、消費電力Pampを演算するために、出力電圧V1と入力電圧V2との2つの電圧の積を用いている。

【0054】

消費電力Pampと電圧の2乗との単位とは異なるが、消費電力Pampに抵抗値R1を乗じることにより、比較の単位を統一することができる。これにより、比較部20は単純な比較回路で構成することができる。

【0055】

制御部21は、比較部20の比較の結果が「Pamp×R1>Plim×R1」のときには、過剰な消費電力Pampが作用していることを認識する。これにより、出力設定部11を制御して、idの極性によっては低下させると消費電力が増える。出力アンプ12は設定電圧Vsetが低下することで、消費電力Pampが低下する。従って、過剰な消費電力Pampが作用することに起因する出力アンプ12の故障を回避することができる。

【0056】

これと共に、制御部21は過剰な消費電力Pampが作用したことをユーザ等に了知させるために、アラーム22を鳴動させる。これにより、ユーザ等は消費電力Pampの異常を迅速に把握することができる。

【0057】

演算部19と比較部20と制御部21とは常に動作を行っており、出力アンプ12の消費電力Pampをリアルタイムに監視している。これにより、印加電流idと印加電圧vdとに基づく値が安全領域Z1から危険領域Z2に入ったときに設定電圧Vsetを制御する。従って、迅速且つ自動的に安全領域Z1に戻すことができるようになる。

【0058】

一方、制御部21は、比較部20の比較の結果が「Pamp×R1≦Plim×R1」のときには、過剰な消費電力Pampは作用していないことを認識する。このときには、格別に出力アンプ12の消費電力Pampを低下させる必要はないため、出力設定部11の設定電圧Vsetはそのままの値を維持させる。つまり、格別な制御は行わない。

【0059】

ところで、DUT2は内部電圧(DUT電圧vdut)を有しており、内部抵抗(DUT抵抗Rdut)がゼロの場合には、DUT電圧vdutが直流電流電圧源3に作用する。このときに、DUT電圧vdutが図4に示した電圧範囲の最小値のVLLであるとする。

【0060】

このDUT電圧vdutは印加電圧vdと一致する。そして、この印加電圧vdが直接的或いは間接的に出力アンプ12に作用するため、出力アンプ12の消費電力Pampに影響を及ぼす。ただし、DUT電圧vdutが作用したとしても、演算部19と比較部20と制御部21とは出力アンプ12の出力電圧V1と入力電圧V2とをリアルタイムに監視して設定電圧Vsetの制御を行っているため、出力アンプ12に過剰な消費電力Pampが作用することはない。

【0061】

例えば、電流源モードにて、設定電圧Vset=R1×IHL(IHLは図4の電流範囲の最大値)となるように設定していたとする。つまり、高い電流値を印加するように設定していたとする。また、DUT電圧vdutは図4の電圧範囲の最小値VLLと等しい場合を想定すると(vdut=VLL)、印加電圧vdはVLLと等しくなる(vd=VLL)。

【0062】

このとき、従来の場合には、「vd=VLL」、「id≧IHL」となり、危険領域Z2に位置することになる。これにより、過剰な消費電力Pampが出力アンプ12に作用し、出力アンプ12が故障する。

【0063】

一方、本実施形態では、演算部19が消費電力Pamp×R1を演算して、比較部20が比較を行い、制御部21が「Pamp×R1=Plim×R1」となるように、つまり「Pamp=Plim」となるように出力設定部11の制御を行っている。従って、過剰な消費電力Pampが出力アンプ12に作用することなく、出力アンプ12が故障することはない。このときの印加電圧vdは「vd=VLL」となり、印加電流idは「id≦Plim/(vdd−VLL)」となる。

【0064】

次に、図2を用いて、変形例について説明する。この変形例では、直流電流電圧源3はN(Nは2以上の整数)個を備えており、それぞれ直流電流電圧ユニット3−1〜3−Nとする。各直流電流電圧ユニット3−1〜3−Nには前述した構成が備えられている。図2では、そのうち演算部19と制御部21とを示している。

【0065】

各直流電流電圧ユニット3−1〜3−Nの演算部19は合計比較部30に接続されている。つまり、各演算部19は式1で演算したPamp×R1を合計比較部30に出力している。合計比較部30は各演算部19から入力したPamp×R1を合計して、合計消費電力Ptampを演算する。

【0066】

合計比較部30には合計消費電力Ptampと比較するための合計設定電力Ptlimが設定されている。そして、合計したPtampとPtlimとの比較を行って、「Ptamp>Ptlim」となっているときには、各直流電流電圧ユニット3−1〜3−Nの全て或いは一部の制御部21にその旨を通知する。

【0067】

この旨の通知を受領した制御部21は出力設定部11を制御して、設定電圧Vsetを低下させる制御を行う。これにより、N個の直流電流電圧ユニット3−1〜3−Nの合計消費電力Ptampも低下する。この作業を「Patmp≦Ptlim」となるまで行う。

【0068】

半導体試験装置1にN個の直流電流電圧ユニット3−1〜3―Nを備えるようにした場合には、各直流電流電圧ユニット3−1〜3−Nが熱的に相互に干渉し、出力アンプ12に過剰な熱量が与えられることになる。各直流電流電圧ユニット3の個々の出力アンプ12の消費電力Pampが適正であるとしても、全体としての合計消費電力Ptampが過剰になると、やはり出力アンプ12に熱作用による故障を生じる。

【0069】

そこで、個々の出力アンプ12の消費電力Pampが適正である場合でも、全体の合計消費電力Ptampが上限値である合計設定電力Ptlimを超過したときには、直流電流電圧ユニット3−1〜3−Nの設定電圧Vsetを低下させる。これにより、全体の消費電力としても適正なコントロールを行うことが可能になる。

【0070】

このとき、合計比較部30は各直流電流電圧ユニット3−1〜3−Nのうち、一部の熱に弱い直流電流電圧ユニット3−1〜3−Nの設定電圧Vsetを優先的に下げるように制御してもよい。また、全ての直流電流電圧ユニット3−1〜3−Nの設定電圧Vsetを均等に低下させると、簡単な制御が実現できる。

【符号の説明】

【0071】

1 半導体試験装置

3 直流電流電圧源(直流電流電圧ユニット)

11 出力設定部

12 出力アンプ

13 抵抗

17 電流検出アンプ

18 スイッチ

19 演算部

20 比較部

21 制御部

22 アラーム

30 合計比較部

【特許請求の範囲】

【請求項1】

出力設定部により設定された電圧を出力する出力アンプと、

この出力アンプが出力する出力電圧と前記出力アンプに帰還されて入力される入力電圧とを入力して、前記出力アンプの消費電力を演算する演算部と、

この演算部により演算された前記消費電力が予め設定された設定電力を超過しているか否かを比較する比較部と、

前記消費電力が前記設定電力を超過しているときには、前記出力設定部の設定値を低下させる制御を行う制御部と、

を備えたことを特徴とする直流電流電圧源。

【請求項2】

前記出力アンプの消費電力をPamp、出力側に接続される抵抗をR1、正電源をvdd、負電源をVss、前記出力電圧をV1、前記入力電圧をV2、前記設定電力をPlimとしたときに、

前記演算部は、

V2≧0のときに「Pamp×R1=(vdd−V1)×V2」、

V2<0のときに「Pamp×R1=(Vss−V1)×V2」、を演算し、

前記比較部は、「Pamp×R1」と「Plim×R1」とを比較し、

前記制御部は、

「Pamp×R1>Plim×R1」のときには、「Pamp=Plim」となるように前記出力設定部を制御し、

「Pamp×R1≦Plim×R1」のときには、前記出力設定部の値を維持させること

を特徴とする請求項1記載の直流電流電圧源。

【請求項3】

前記出力アンプと前記演算部と前記比較部と前記制御部とを備えた直流電流電圧ユニットを複数備え、

各直流電流電圧ユニットの前記演算部から前記消費電力Pampを取得して合計して合計消費電力Ptampとし、この合計消費電力Ptampが予め設定され合計設定電力Ptlimより大きいときには、前記合計消費電力Ptampが前記合計設定電力Ptlim以下となるように各直流電流電圧ユニットの前記制御部に対して前記出力設定部の設定値を低下させる制御を行わせる合計比較部を備えたこと

を特徴とする請求項2記載の直流電流電圧源。

【請求項4】

前記比較部により前記消費電力が前記設定電力を超過していると判定されたときは、警報を鳴動するアラームを備えたこと

を特徴とする請求項1記載の直流電流電圧源。

【請求項5】

請求項1乃至4の何れか1項に記載の直流電流電圧源を備えたことを特徴とする半導体試験装置。

【請求項1】

出力設定部により設定された電圧を出力する出力アンプと、

この出力アンプが出力する出力電圧と前記出力アンプに帰還されて入力される入力電圧とを入力して、前記出力アンプの消費電力を演算する演算部と、

この演算部により演算された前記消費電力が予め設定された設定電力を超過しているか否かを比較する比較部と、

前記消費電力が前記設定電力を超過しているときには、前記出力設定部の設定値を低下させる制御を行う制御部と、

を備えたことを特徴とする直流電流電圧源。

【請求項2】

前記出力アンプの消費電力をPamp、出力側に接続される抵抗をR1、正電源をvdd、負電源をVss、前記出力電圧をV1、前記入力電圧をV2、前記設定電力をPlimとしたときに、

前記演算部は、

V2≧0のときに「Pamp×R1=(vdd−V1)×V2」、

V2<0のときに「Pamp×R1=(Vss−V1)×V2」、を演算し、

前記比較部は、「Pamp×R1」と「Plim×R1」とを比較し、

前記制御部は、

「Pamp×R1>Plim×R1」のときには、「Pamp=Plim」となるように前記出力設定部を制御し、

「Pamp×R1≦Plim×R1」のときには、前記出力設定部の値を維持させること

を特徴とする請求項1記載の直流電流電圧源。

【請求項3】

前記出力アンプと前記演算部と前記比較部と前記制御部とを備えた直流電流電圧ユニットを複数備え、

各直流電流電圧ユニットの前記演算部から前記消費電力Pampを取得して合計して合計消費電力Ptampとし、この合計消費電力Ptampが予め設定され合計設定電力Ptlimより大きいときには、前記合計消費電力Ptampが前記合計設定電力Ptlim以下となるように各直流電流電圧ユニットの前記制御部に対して前記出力設定部の設定値を低下させる制御を行わせる合計比較部を備えたこと

を特徴とする請求項2記載の直流電流電圧源。

【請求項4】

前記比較部により前記消費電力が前記設定電力を超過していると判定されたときは、警報を鳴動するアラームを備えたこと

を特徴とする請求項1記載の直流電流電圧源。

【請求項5】

請求項1乃至4の何れか1項に記載の直流電流電圧源を備えたことを特徴とする半導体試験装置。

【図1】

【図2】

【図3】

【図4】

【図2】

【図3】

【図4】

【公開番号】特開2013−29409(P2013−29409A)

【公開日】平成25年2月7日(2013.2.7)

【国際特許分類】

【出願番号】特願2011−165404(P2011−165404)

【出願日】平成23年7月28日(2011.7.28)

【出願人】(000006507)横河電機株式会社 (4,443)

【Fターム(参考)】

【公開日】平成25年2月7日(2013.2.7)

【国際特許分類】

【出願日】平成23年7月28日(2011.7.28)

【出願人】(000006507)横河電機株式会社 (4,443)

【Fターム(参考)】

[ Back to top ]