相互接続構造の珪化物層およびロープロファイルバンプを有するパワーMOSFETを形成する半導体デバイスおよび方法

【課題】相互接続構造の珪化物層と、ロープロファイルバンプを含む、バンプ間ショートを防止したパワーMOSFETからなる半導体デバイスおよび製造方法を提供する。

【解決手段】基板上にソース領域160およびドレイン領域170を有し、珪化物層174が、ソース領域およびドレイン領域の上に配置されている。第1の相互接続層194が、珪化物層上に形成されており、ソース領域に接続される第1のランナー196と、ドレイン領域に接続される第2のランナー198とが配置される。第2の相互接続層214が、第1の相互接続層上に形成されており、第1のランナーに接続される第3のランナー216と、第2のランナーに接続される第4のランナー218とを含む。第3の相互接続層234が形成され、ソースパッド236、ソースバンプ240が電気的に接続される。

【解決手段】基板上にソース領域160およびドレイン領域170を有し、珪化物層174が、ソース領域およびドレイン領域の上に配置されている。第1の相互接続層194が、珪化物層上に形成されており、ソース領域に接続される第1のランナー196と、ドレイン領域に接続される第2のランナー198とが配置される。第2の相互接続層214が、第1の相互接続層上に形成されており、第1のランナーに接続される第3のランナー216と、第2のランナーに接続される第4のランナー218とを含む。第3の相互接続層234が形成され、ソースパッド236、ソースバンプ240が電気的に接続される。

【発明の詳細な説明】

【技術分野】

【0001】

(本発明の分野)

本発明は、概して、電子回路および半導体デバイスに関し、より具体的に、密集したトランジスターの上に形成された相互接続構造の珪化物層を有し、さらにロープロファイルバンプを含むパワーMOSFETを形成する半導体デバイスおよび方法に関する。

【背景技術】

【0002】

(本発明の背景)

半導体デバイスが、現代の電子製品において一般的に見つけられる。半導体デバイスは、電気部品の数および密度が変化する。離散的半導体デバイスは、概して、1つのタイプの電気部品、例えば、発光ダイオード(LED)、微小信号トランジスター、抵抗器、キャパシター、インダクター、パワー酸化金属半導体電界効果トランジスター(MOSFET)を含む。集積半導体デバイスは、典型的に、数百個から数百万個の電気部品を含む。集積半導体デバイスの例は、マイクロコントローラ、マイクロプロセッサ、電荷結合デバイス(CCD)、太陽電池、およびデジタルマイクロミラーデバイス(DMD)を含む。

【0003】

半導体デバイスは、広範囲の機能、例えば、信号処理、高速計算、電磁気信号を送受信すること、電子デバイスを制御すること、太陽光から電気へ変換すること、およびテレビジョンディスプレイのための視覚投影を生成することを行う。半導体デバイスは、エンターテイメント、通信、電力変換、ネットワーク、コンピュータ、および消費者製品の分野において見つけられる。半導体デバイスは、軍事用途、航空、自動車、工業用コントローラ、およびオフィス機器においても見つけられる。

【0004】

半導体デバイスは、半導体材料の電気的性質を活用する。半導体材料の原子構造は、半導体の材料の導電率が、電界またはベース電流の適用によって、またはドーピングの処理を介して操作されることを可能にする。ドーピングは、半導体材料内に不純物を導入し、半導体デバイスの導電率を操作し、かつ制御する。

【0005】

半導体デバイスは、能動電気構造および受動電気構造を含む。双極性電界効果トランジスターを含む能動構造は、電流の流れを制御する。ドーピングのレベル、および電界またはベース電流の適用のレベルを変化させることによって、トランジスターは、電流を促進するかまたは制限する。抵抗器、キャパシター、およびインダクターを含む受動構造は、さまざまな電気的機能を行うために必要な電圧と電流との間の関係を生成する。行う。受動構造および能動構造は、回路を形成するように電気的に接続されており、回路は、半導体デバイスが、高速計算および他の有用な機能を行うことを可能にする。

【0006】

半導体デバイスは、概して、2つの複雑な製造プロセス、すなわち、フロントエンド製造およびバックエンド製造を用いて製造され、各プロセスは、潜在的に数百個のステップを必要とする。フロントエンド製造は、半導体ウェーハの表面上に複数のダイの形成を必要とする。各ダイは、典型的に同様であり、能動部品と受動部品を電気的に接続することによって形成された回路を含む。バックエンド製造は、完成したウェーハから個々のダイを単一化することと、構造的支持および環境的分離を提供するようにダイをパッケージする。

【0007】

半導体製造の1つの目標は、より小さな半導体デバイスを生産することである。より小さなデバイスは、典型的に、より少ない電力を消費し、より低い電圧で動作し、より高い性能を有し、そしてより効率的に生産され得る。加えて、より小さな半導体デバイスは、より小さなエンド製品にとって望ましい、より小さなフットプリントを有する。より小さなダイのサイズは、フロントエンドプロセスの向上によって達成され得、より小さく、より高密度の能動部品および受動部品を有するダイをもたらす。バックエンドプロセスは、電気的相互接続およびパッケージング材料の改良によってより小さなフットプリントを有する半導体デバイスパッケージをもたらし得る。

【0008】

パワーMOSFETは、電子回路、例えば、通信システムおよび電源に一般的に使用される半導体デバイスの1つの例である。特に、パワーMOSFETは、電子スイッチとして使用される場合に、比較的に大きな電流の伝導を有効にし、無効にするのに有用である。パワーMOSFETのオン/オフ状態は、ゲート電圧にトリガー信号を印加し、除去することによって制御される。オンにされると、MOSFETにおける電流は、ドレインとソースとの間に流れる。オフにされると、電流が、MOSFETによってブロックされる。

【0009】

パワーMOSFETの小型化は、半導体のダイの全表面にわたって分布されている小さなMOSFETセルまたはトランジスターを含むデバイスを産み出す。MOSFETセルは、ソース領域およびドレイン領域を含み、ソース領域およびドレイン領域は、後の電気的相互接続のために、例えば、ソースパッドおよびドレインパッド上に形成されたバンプ、または端子の大きさのような電気的相互接続に形成される。従って、複数のソース領域およびドレイン領域は、しばしば、単一のソースパッドまたはドレインパッドの下に設置される。密集したトランジスターを有するパワーMOSFET内の厳しい垂直の相互接続の使用は、対応する水平にずれたソースパッドおよびドレインパッドと接続するために、単一のソースパッドまたはドレインパッドの下に設置されたトランジスターのソース領域およびドレイン領域の両方を接続することを提供しない。従って、水平のずれを考慮する相互接続構造は、単一のソースパッドまたはドレインパッドの下に設置されたトランジスターのソース領域およびドレイン領域を、水平オフセットのソースパッドおよびドレインパッドに接続する必要がある。

【0010】

さらに、他の半導体デバイスと同様に、パワーMOSFETは、半導体デバイスを、基板、回路基板、および他の半導体デバイスに電気的に接続するための相互接続構造を含む。半導体ダイをプリント回路基板(PCB)または他のデバイスと相互接続する1つの一般的な技術は、はんだバンプの使用を必要とする。図1aは、従来のUBMはんだバンプ構造10を示す。はんだバンプ構造10は、ベースシリコンの半導体ウェーハ12を含む半導体ダイ11を含み、能動エリア14が、半導体ウェーハ12上に形成されている。能動エリア14は、半導体ダイ11内に形成された能動デバイス、受動デバイス、導電層、および誘電層として実装され、かつ半導体ダイの電気的設計および機能に従って電気的に相互接続されたアナログまたはデジタル回路を含む。電気伝導層16は、半導体ダイ11の能動エリア14上に形成され、接触パッドとして動作する。絶縁またはパシベーション層18は、半導体ダイ11および導電層16上に形成される。絶縁層18の一部分は、導電層16の一部分を露出させる絶縁層の開口部20を形成するために、エッチングプロセスによって除去される。1つの実施形態において、開口部20は、270マイクロメートル(μm)の幅を有する。電気伝導またはUBM層22が、開口部20内の、絶縁層18の一部分の上の導電層16上に順応的に形成される。1つの実施形態において、導電層22は、アルミニウム(Al)を含む接着層、ニッケルバナジウム(NiV)を含むバリア層、および銅(Cu)を含む溶接層を含む。ベンゾシクロブテン(BCB)のような絶縁またはパシベーション層24が、導電層22および絶縁層18の上に形成される。絶縁層24の開口部26は、UBM22上に形成され、UBM22の一部分を露出させる。1つの実施形態において、開口部26は、280μmの幅を有する。導電性バンプ28は、従来のUBMはんだバンプ構造10を完成させるために、導電層16および22の上に、開口部20および26内に配置される。1つの実施形態において、導電性バンプ28は、ボールドロッププロセスで導電層22に取り付けられ、かつ350μmの所定の直径30を有する、事前成形されたはんだ球を含む。

【0011】

図1bは、パッケージ(SiP)32の中のオーバー成形のシステムの一部分として、パッケージングされている図1aからの、従来のUBMはんだバンプ構造10を有する半導体ダイ11を示す。半導体ダイ11は、導電性接触36をさらに含む基板または多層化されたPCB34に取り付けられている。アンダーフィル38は、半導体ダイ11と基板34との間の接続を向上させるために、バンプ28の周り、かつ基板34と半導体ダイ11の能動エリア14との間に蒸着される。バンプ28は、電気的、かつ機械的接続を向上させるために、複数回のリフローを受ける。バンプ28の複数回のリフローは、バンプを半導体ダイ11に接続するために、バンプ28をリフローすること、半導体ダイ11およびバンプ28を基板34に接続するために、半導体ダイ11に接続されるバンプ28をリフローすること、基板または多層化されたPCBにSiP32を取り付けるときに、バンプ28をリフローすること、および追加の基板または多層化されたPCBに追加の部品を取り付け、または追加の基板または多層化されたPCBの再処理のために、バンプ28をリフローすることを含む。しかしながら、いくつかの場合においてバンプ28をリフローすることは、バンプ28の間のはんだブリッジングおよび電気的ショートの原因となり、それによって、半導体ダイ11の故障を引き起こす。バンプ28の間のはんだブリッジングおよび電気的ショートは、バンプが微細ピッチを有する場合に、より発生する可能性が高い。アンダーフィル材料38は、バンプ28の間にアンダーフィルが欠けることを防止し、かつリフローの間、バンプ材料を局在化した状態に保つことによるはんだブリッジングおよび電気的ショートを防止することを助けるために最適化される。しかしながら、アンダーフィル38の配置を制御することは、難しく、不均一な厚さを有するアンダーフィルの配置を生じ得る。不均一な厚さのアンダーフィル材料38は、一般的であり、例えば、半導体ダイの第1の面上の、半導体ダイ11と基板34との間のギャップの一部分のみが充填されるが、半導体ダイの第2の面上のギャップの全体が充填される構成を含む。不均一に分布されたアンダーフィル38は、半導体ダイ11上にストレスの非平衡を引き起こし、ストレスの非平衡は、半導体ダイのクラッキングおよび故障を引き起こし得る。さらに、カプセルの材料または成形化合物40が、半導体ダイ11上、および周りに置かれる。カプセルの材料40と不均一に分布されたアンダーフィル38との組み合わせはさらに、半導体ダイ11上にストレスの非平衡を引き起こし、ストレスの非平衡はさらに、ダイのクラッキングおよび故障を引き起こす。従って、アンダーフィル38を有するSiP32の従来の組立体は、SiP組立体の生産高および信頼性を減少させる欠点になりやすい。

【発明の概要】

【課題を解決するための手段】

【0012】

(本発明の要約)

ロープロファイルバンプと、密集したトランジスター上に形成される相互接続構造とを有するパワーMOSFETを提供するニーズが存在する。従って、1つの実施形態において、本発明は、半導体デバイスを作る方法であり、方法は、基板を提供することと、基板の第1の表面上にソース領域を形成することと、ソース領域に隣接して、基板の第1の表面上にドレイン領域を形成することと、ソース領域およびドレイン領域の上に珪化物層を蒸着することと、珪化物層上に第1の相互接続層を形成することと、第1の相互接続層上に第2の相互接続層を形成することと、第2の相互接続層の上、かつ第2の相互接続層に電気的に接続されるUBMを形成することとを含む。第1の相互接続層は、ソース領域に接続される第1のランナーと、ドレイン領域に接続される第2のランナーとを含む。第2の相互接続層は、第1のランナーに接続される第3のランナーと、第2のランナーに接続される第4のランナーとを含む。方法は、マスクの開口部がUBM上に整列されるように、基板上にマスクを配置するステップと、開口部内に導電性バンプ材料を蒸着するステップと、マスクを除去するステップと、バンプを形成するために、導電性バンプ材料をリフローするステップとをさらに含む。

【0013】

別の実施形態において、本発明は、半導体デバイスを作る方法であり、方法は、ソース領域と、隣接するドレイン領域とを含む基板を提供することと、ソース領域およびドレイン領域の上に珪化物層を蒸着することと、珪化物層上に第1の相互接続層を形成することとを含む。第1の相互接続層は、ソース領域に接続される第1のランナーと、ドレイン領域に接続される第2のランナーとを含む。方法は、第1の相互接続層の上、かつ第1の相互接続層に電気的に接続されるUBMを形成するステップと、マスクの開口部がUBM上に整列されるように、基板上にマスクを配置するステップと、開口部内に導電性バンプ材料を蒸着するステップと、マスクを除去するステップと、バンプを形成するために、導電性バンプ材料をリフローするステップとをさらに含む。

【0014】

別の実施形態において、本発明は、半導体デバイスを作る方法であり、方法は、基板を提供することと、基板上に珪化物層を有するトランジスターを形成することと、トランジスターの上、かつトランジスターに接続される第1の相互接続層を形成することと、第1の相互接続層の上、かつ第1の相互接続層に接続されるUBMを形成することと、マスクの開口部がUBM上に整列されるように、基板上にマスクを配置することと、バンプを形成するために、開口部内に導電性材料を蒸着することとを含む。

【0015】

別の実施形態において、本発明は、半導体デバイスであり、半導体デバイスは、ソース領域と、隣接するドレイン領域とを含む基板を含む。珪化物層が、ソース領域およびドレイン領域の上に配置されている。第1の相互接続層が、珪化物層上に形成されている。第1の相互接続層は、ソース領域に接続される第1のランナーと、ドレイン領域に接続される第2のランナーとを含む。UBMが、第1の相互接続層上に形成されており、かつ第1の相互接続層に電気的に接続される。バンプが、UBMに電気的に接続される。バンプは、マスク開口部の体積によって決定される導電性バンプ材料の体積を有する。

【0016】

本発明は、例えば、以下の項目を提供する。

(項目1)

半導体デバイスを作る方法であって、該方法は、

ソース領域と、隣接するドレイン領域とを含む基板を提供することと、

該ソース領域および該ドレイン領域の上に珪化物層を形成することと、

該珪化物層上に第1の相互接続層を形成することであって、該第1の相互接続層は、該ソース領域に接続される第1のランナーと、該ドレイン領域に接続される第2のランナーとを含む、ことと、

該第1の相互接続層の上、かつ該第1の相互接続層に電気的に接続される導電層を形成することと、

該基板上にマスクを配置することであって、該マスクの開口部が該導電層上に整列されられている、ことと、

相互接続を形成するために、該開口部内に導電性材料を蒸着することと

を含む、方法。

(項目2)

上記第1の相互接続層上に第2の相互接続層を形成することをさらに含み、該第2の相互接続層は、第3のランナーおよび第4のランナーを有し、該第3のランナーおよび該第4のランナーは、互いに対して平行であり、かつ上記第1のランナーおよび上記第2のランナーと直交している、上記項目のいずれかに記載の方法。

(項目3)

上記基板にわたって延在するストライプのように、上記ソース領域を形成することと、

該基板にわたって延在し、かつ該ソース領域に対して平行であるストライプのように、上記ドレイン領域を形成することと

さらに含む、上記項目のいずれかに記載の方法。

(項目4)

上記第1のランナーおよび上記第2のランナーは、長方形、十字の形状(+)、L形(L)、またはT形(T)である、上記項目のいずれかに記載の方法。

(項目5)

半導体デバイスを作る方法であって、該方法は、

基板を提供することと、

該基板上に珪化物層を有するトランジスターを形成することと、

該トランジスターの上、かつ該トランジスターに接続される第1の相互接続層を形成することと、

該第1の相互接続層の上、かつ該第1の相互接続層に接続される導電層を形成することと、

該基板上にマスクを配置することであって、該マスクの開口部が該導電層上に整列されられている、ことと、

相互接続を形成するために、該開口部内に導電性材料を蒸着することと

を含む、方法。

(項目6)

ソース領域と、隣接するドレイン領域とを有する上記トランジスターを形成することと、

該ソース領域および該ドレイン領域の上に上記珪化物層を形成することと

をさらに含む、上記項目のいずれかに記載の方法。

(項目7)

互いに対して平行である第1のランナーおよび第2のランナーを有する上記第1の相互接続層を形成することをさらに含む、上記項目のいずれかに記載の方法。

(項目8)

上記第1の相互接続層上に第2の相互接続層を形成することをさらに含み、該第2の相互接続層は、第3のランナーおよび第4のランナーを有し、該第3のランナーおよび該第4のランナーは、互いに対して平行であり、かつ上記第1のランナーおよび上記第2のランナーと直交している、上記項目のいずれかに記載の方法。

(項目9)

上記基板にわたって延在するストライプのように、上記ソース領域を形成することと、

該基板にわたって延在し、かつ該ソース領域に対して平行であるストライプのように、上記ドレイン領域を形成することと

さらに含む、上記項目のいずれかに記載の方法。

(項目10)

上記第1の相互接続層は、長方形、十字の形状(+)、L形(L)、またはT形(T)である、上記項目のいずれかに記載の方法。

(項目11)

半導体デバイスであって、該半導体デバイスは、

ソース領域と、隣接するドレイン領域とを含む基板と、

該ソース領域および該ドレイン領域の上に配置されている珪化物層と、

該珪化物層上に形成されている第1の相互接続層であって、該第1の相互接続層は、該ソース領域に接続される第1のランナーと、該ドレイン領域に接続される第2のランナーとを含む、第1の相互接続層と、

該第1の相互接続層上に形成され、かつ該第1の相互接続層に電気的に接続される導電層と、

該導電層に電気的に接続される相互接続であって、該相互接続は、マスク開口部の体積によって決定される導電性材料の体積を有する、相互接続と

を含む、半導体デバイス。

(項目12)

上記第1のランナーおよび上記第2のランナーは、互いに対して平行であり、上記ソース領域および上記ドレイン領域と直交している、上記項目のいずれかに記載の半導体デバイス。

(項目13)

第2の相互接続層が、上記第1の相互接続層上に形成され、該第2の相互接続層は、第3のランナーおよび第4のランナーを有し、該第3のランナーおよび該第4のランナーは、互いに対して平行であり、かつ上記第1のランナーおよび上記第2のランナーと直交している、上記項目のいずれかに記載の半導体デバイス。

(項目14)

上記ソース領域は、上記基板にわたって延在するストライプのように形成され、

上記ドレイン領域は、該基板にわたって延在し、かつ該ソース領域に対して平行であるストライプのように形成される、上記項目のいずれかに記載の半導体デバイス。

(項目15)

上記第1のランナーおよび上記第2のランナーは、長方形、十字の形状(+)、L形(L)、またはT形(T)である、上記項目のいずれかに記載の半導体デバイス。

(項目1a)

半導体デバイスを作る方法であって、該方法は、

基板を提供することと、

該基板の第1の表面上にソース領域を形成することと、

該ソース領域に隣接して、該基板の該第1の表面上にドレイン領域を形成することと、

該ソース領域および該ドレイン領域の上に珪化物層を形成することと、

該珪化物層上に第1の相互接続層を形成することであって、該第1の相互接続層は、該ソース領域に接続される第1のランナーと、該ドレイン領域に接続される第2のランナーとを含む、ことと、

該第1の相互接続層上に第2の相互接続層を形成することであって、該第2の相互接続層は、該第1のランナーに接続される第3のランナーと、該第2のランナーに接続される第4のランナーとを含む、ことと、

該第2の相互接続層の上、かつ該第2の相互接続層に電気的に接続されるアンダーバンプ金属化(UBM)を形成することと、

マスクの開口部が該UBM上に整列されるように、該基板上に該マスクを配置することと、

該開口部内に導電性バンプ材料を蒸着することと、

該マスクを除去することと、

バンプを形成するために、該導電性バンプ材料をリフローすることと

を含む、方法。

(項目2a)

互いに対して平行であり、かつ上記ソース領域およびドレイン領域と直交している上記第1のランナーおよび上記第2のランナーを形成することをさらに含む、上記項目のいずれかに記載の方法。

(項目3a)

互いに対して平行であり、かつ上記第1のランナーおよび上記第2のランナーと直交している上記第3のランナーおよび上記第4のランナーを形成することをさらに含む、上記項目のいずれかに記載の方法。

(項目4a)

上記基板の上記第1の表面にわたって延在するストライプのように、上記ソース領域を形成することと、

該基板の上記第1の表面にわたって延在し、かつ該ソース領域に対して平行であるストライプのように、上記ドレイン領域を形成することと

さらに含む、上記項目のいずれかに記載の方法。

(項目5a)

電流が、最小の抵抗を有する電気的パスに沿って上記ソース領域および上記ドレイン領域の各々へ流れるように、該ソース領域および該ドレイン領域を複数の電気的パスに接続することをさらに含む、上記項目のいずれかに記載の方法。

(項目6a)

上記第1のランナー、上記第2のランナー、上記第3のランナー、および上記第4のランナーは、長方形、十字の形状(+)、L形(L)、またはT形(T)である、上記項目のいずれかに記載の方法。

(項目7a)

互いに対して平行であり、かつ上記ソース領域およびドレイン領域と直交している上記第1のランナーおよび上記第2のランナーを形成することをさらに含む、上記項目のいずれかに記載の方法。

(項目8a)

電流が、最小の抵抗を有する電気的パスに沿って上記ソース領域および上記ドレイン領域の各々へ流れるように、該ソース領域および該ドレイン領域を複数の電気的パスに接続することをさらに含む、上記項目のいずれかに記載の方法。

(項目9a)

電流が、最小の抵抗を有する電気的パスに沿って流れるように、上記トランジスターを複数の電気的パスに接続することをさらに含む、上記項目のいずれかに記載の方法。

(項目10a)

電流が、最小の抵抗を有する電気的パスに沿って上記ソース領域および上記ドレイン領域の各々へ流れるように、該ソース領域および該ドレイン領域は、複数の電気的パスに接続される、上記項目のいずれかに記載の半導体デバイス。

【0017】

(摘要)

半導体デバイスは、基板を有し、基板は、基板上に形成されるソース領域およびドレイン領域を有する。珪化物層が、ソース領域およびドレイン領域の上に配置されている。第1の相互接続層が、珪化物層上に形成されており、ソース領域に接続される第1のランナーと、ドレイン領域に接続される第2のランナーとを含む。第2の相互接続層が、第1の相互接続層上に形成されており、第1のランナーに接続される第3のランナーと、第2のランナーに接続される第4のランナーとを含む。アンダーバンプ金属化(UBM)が、第2の相互接続層上に形成されており、かつ第2の相互接続層に電気的に接続される。マスクの開口部がUBM上に整列されるように、マスクが、基板上に配置される。導電性バンプ材料が、マスクの開口部内に蒸着される。マスクが除去され、導電性バンプ材料が、バンプを形成するためにリフローされる。

【図面の簡単な説明】

【0018】

【図1a】図1aは、従来のUBMはんだバンプ構造を例示する。

【図1b】図1bは、従来のUBMはんだバンプ構造を例示する。

【図2】図2は、その表面に取り付けられた異なるタイプのパッケージを有するPCBを例示する。

【図3a】図3aは、PCBに取り付けられた代表的な半導体パッケージのさらなる詳細を例示する。

【図3b】図3bは、PCBに取り付けられた代表的な半導体パッケージのさらなる詳細を例示する。

【図3c】図3cは、PCBに取り付けられた代表的な半導体パッケージのさらなる詳細を例示する。

【図4a】図4aは、珪化物層および相互接続構造を有するパワーMOSFETを形成する方法を例示する。

【図4b】図4bは、珪化物層および相互接続構造を有するパワーMOSFETを形成する方法を例示する。

【図4c】図4cは、珪化物層および相互接続構造を有するパワーMOSFETを形成する方法を例示する。

【図4d】図4dは、珪化物層および相互接続構造を有するパワーMOSFETを形成する方法を例示する。

【図4e】図4eは、珪化物層および相互接続構造を有するパワーMOSFETを形成する方法を例示する。

【図4f】図4fは、珪化物層および相互接続構造を有するパワーMOSFETを形成する方法を例示する。

【図4g】図4gは、珪化物層および相互接続構造を有するパワーMOSFETを形成する方法を例示する。

【図4h】図4hは、珪化物層および相互接続構造を有するパワーMOSFETを形成する方法を例示する。

【図4i】図4iは、珪化物層および相互接続構造を有するパワーMOSFETを形成する方法を例示する。

【図4j】図4jは、珪化物層および相互接続構造を有するパワーMOSFETを形成する方法を例示する。

【図4k】図4kは、珪化物層および相互接続構造を有するパワーMOSFETを形成する方法を例示する。

【図4l】図4lは、珪化物層および相互接続構造を有するパワーMOSFETを形成する方法を例示する。

【図4m】図4mは、珪化物層および相互接続構造を有するパワーMOSFETを形成する方法を例示する。

【図4n】図4nは、珪化物層および相互接続構造を有するパワーMOSFETを形成する方法を例示する。

【図4o】図4oは、珪化物層および相互接続構造を有するパワーMOSFETを形成する方法を例示する。

【図4p】図4pは、珪化物層および相互接続構造を有するパワーMOSFETを形成する方法を例示する。

【図4q】図4qは、珪化物層および相互接続構造を有するパワーMOSFETを形成する方法を例示する。

【図4r】図4rは、珪化物層および相互接続構造を有するパワーMOSFETを形成する方法を例示する。

【図4s】図4sは、珪化物層および相互接続構造を有するパワーMOSFETを形成する方法を例示する。

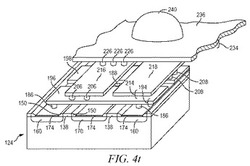

【図4t】図4tは、珪化物層および相互接続構造を有するパワーMOSFETを形成する方法を例示する。

【図5a】図5aは、パワーMOSFETのさらなる詳細を例示する。

【図5b】図5bは、パワーMOSFETのさらなる詳細を例示する。

【図5c】図5cは、パワーMOSFETのさらなる詳細を例示する。

【図6a】図6aは、短いUBM構造を形成する方法を例示する。

【図6b】図6bは、短いUBM構造を形成する方法を例示する。

【図6c】図6cは、短いUBM構造を形成する方法を例示する。

【図6d】図6dは、短いUBM構造を形成する方法を例示する。

【図6e】図6eは、短いUBM構造を形成する方法を例示する。

【図6f】図6fは、短いUBM構造を形成する方法を例示する。

【図6g】図6gは、短いUBM構造を形成する方法を例示する。

【図6h】図6hは、短いUBM構造を形成する方法を例示する。

【図6i】図6iは、短いUBM構造を形成する方法を例示する。

【図7a】図7aは、相互接続構造を有するパワーMOSFETのさらなる詳細を例示する。

【図7b】図7bは、相互接続構造を有するパワーMOSFETのさらなる詳細を例示する。

【図7c】図7cは、相互接続構造を有するパワーMOSFETのさらなる詳細を例示する。

【図8】図8は、パワーMOSFETの相互接続構造のさらなる詳細を例示する。

【図9】図9は、相互接続構造を有するパワーMOSFETのさらなる詳細を例示する。

【図10a】図10aは、アンダーフィル材料を有しない基板に取り付けられた短いUBM構造を有するパワーMOSFETを例示する。

【図10b】図10bは、アンダーフィル材料を有しない基板に取り付けられた短いUBM構造を有するパワーMOSFETを例示する。

【発明を実施するための形態】

【0019】

(図面の詳細な説明)

本発明は、図面を参照して以下の説明における1つ以上の実施形態において説明される。同様の数字は、同じまたは類似な構成要素を表す。本発明が、本発明の目標を達成するための最もよいモードに関連して説明されるが、当業者によって、本発明が、添付した請求範囲によって規定されるような本発明の精神および範囲内に含まれ得るような代替物、変更、および同等物、並びに以下の開示および図面によって支持されるようなそれらの同等物をカバーするように意図されることが認識される。

【0020】

半導体デバイスは、概して、2つの複合の製造プロセス、すなわち、フロントエンド製造およびバックエンド製造を用いて製造される。フロントエンド製造は、半導体ウェーハの表面上に複数のダイの形成を必要とする。ウェーハ上の各ダイは、機能的電気回路を形成するために、電気的に接続されている能動電気部品および受動電気部品を含む。能動電気部品、例えば、トランジスターおよびダイオードは、電流の流れを制御する能力を有する。受動電気部品、例えば、キャパシター、インダクター、抵抗器、および変圧器は、電流の機能を行うために必要な電圧と電流との間の関係を生成する。

【0021】

受動部品および能動部品は、ドーピング、蒸着、フォトリソグラフィー、エッチング、および平坦化を含む一連のプロセスによって半導体ウェーハの表面上に形成される。ドーピングは、イオン注入または熱拡散のような技術によって半導体材料内に不純物を導入する。ドーピングプロセスは、能動デバイスにおける半導体材料の導電率を変更させ、半導体材料を絶縁体、導体に変換させ、または電場またはベース電流に応じて半導体材料の導電率を動的に変化させる。トランジスターは、電場またはベース電流を印加すると、トランジスターが電流の流れを促進、または制限することを可能にするのに必要であるように配列される、ドーピングのタイプおよび濃度が変化する領域を含む。

【0022】

能動部品および受動部品が、異なる電気性質を有する材料の層によって形成され得る。層は、蒸着される材料のタイプによって部分的に決定されるさまざまな蒸着技術によって形成され得る。例えば、薄膜蒸着は、化学蒸着法(CVD)、物理蒸着法(PVD)、電解めっき、および無電解めっきを含み得る。各層は、概して、能動部品、受動部品、または部品の間の電気的接続の一部分を形成するようにパターンをつけられる。

【0023】

層は、パターンをつけられるべきである層の上に感光性材料、例えば、フォトレジストの蒸着を含むフォトリソグラフィーを用いてパターンをつけられ得る。パターンは、光照射を用いて、フォトマスクからフォトレジストに転送される。光に露出されたフォトレジストパターンの一部分が、溶剤を用いて除去され、パターンをつけられるように、下にある層の一部分を露出させる。フォトレジストの残りが除去され、パターンをつけられた層を残しておく。代替的には、いくつかのタイプの材料は、無電解めっきおよび電解めっきのような技術を用いる事前の蒸着/エッチプロセスによって形成されたエリアまたは隙間内に材料を直接に蒸着することによってパターンをつけられる。

【0024】

存在するパターンの上に薄膜の材料を蒸着することは、下にあるパターンを誇張し、不均一なフラット表面を生成し得る。均一なフラット表面は、より小さく、より低密度に詰められた能動部品および受動部品を生成することを要求される。平坦化は、ウェーハの表面から材料を除去し、かつ均一なフラット表面を生成するために使用され得る。平坦化は、磨きパッドを用いて、ウェーハの表面を磨くことを必要とする。研磨材料および腐食性化学薬品が、磨く際にウェーハの表面に加えられる。研磨剤の機械的作用と、化学薬品の腐食性作用との組み合わせは、不規則な形態を除去し、均一なフラット表面をもたらす。

【0025】

バックエンド製造は、完成したウェーハを個々のダイに切断し、または単一化し、次に構造的支持および環境的分離のためにダイをパッケージすることを指す。ダイを単一化するために、ウェーハは、ソーストリートまたはスクライブと呼ばれる、ウェーハの機能しない領域に沿って刻み目をつけられ、そして割られる。ウェーハは、レーザー切断ツールまたはソースクライブを用いて単一化される。単一化の後に、個々のダイは、他のシステム部品との相互接続のためのピンまたは接触パッドを含むパッケージ基板に取り付けられる。次に、半導体ダイの上に形成された接触パッドが、パッケージ内の接触パッドに接続される。電気的接続は、はんだバンプ、スタッドバンプ、導電性ペーストまたはワイヤボンドを用いて作られ得る。カプセルの材料または他の成形する材料は、物理的支持および電気的分離を提供するためにパッケージの上に蒸着される。次に、完成したパッケージは、電気的システム内に挿入され、半導体デバイスの機能が、他のシステム部品に利用可能にされる。

【0026】

図2は、チップキャリア基板またはPCB52を有する電子デバイス50を例示し、チップキャリア基板またはPCB52は、その表面上に取り付けられた複数の半導体パッケージを有する。電子デバイス50は、用途に依存して、1つのタイプの半導体パッケージ、または複数のタイプの半導体パッケージを有し得る。異なるタイプの半導体パッケージが、例示の目的のために、図2に示される。

【0027】

電子デバイス50は、1つ以上の電気的機能を行うために、半導体パッケージを使用するスタンドアロンシステムであり得る。代替的には、電子デバイス50は、より大きなシステムのサブ部品であり得る。例えば、電子デバイス50は、セルラー電話、パーソナルデジタルアシスタント(PDA)、デジタルビデオカメラ(DVC)、または他の電子通信デバイスの一部分であり得る。代替的には、電子デバイス50は、グラフィックカード、ネットワークインターフェースカード、またはコンピュータ内に挿入され得る他の信号処理カードであり得る。半導体パッケージは、マイクロプロセッサ、メモリ、特定用途の集積回路(ASIC)、論理回路、アナログ回路、RF回路、離散型デバイス、または他の半導体ダイまたは電子部品を含み得る。小型化および重量軽減は、市場によって受け入れられるために、これらの製品にとって必須である。半導体デバイス間の距離は、より高密度を達成するために減少されなければならない。

【0028】

図2において、PCB52は、PCB上に取り付けられる半導体パッケージの構造的支持および電気的相互接続のための一般的基板を提供する。導電性信号トレース54は、蒸着、電解めっき、無電解めっき、スクリーンプリント、または他の適切な金属蒸着プロセスを用いてPCB52の層の表面上、または層内に形成される。信号トレース54は、半導体パッケージ、取り付けられた部品、および他の外部システム部品の各々の間に、電気的連絡を提供する。トレース54はまた、半導体パッケージの各々への電力接続およびグラウンド接続を提供する。

【0029】

いくつかの実施形態において、半導体デバイスは、2つのパッケージングレベルを有する。第1のレベルのパッケージングは、中間キャリアに半導体ダイを機械的、かつ電気的に張りつけるための技術である。第2のレベルのパッケージングは、PCBに中間キャリアを機械的、かつ電気的に張りつけることを含む。他の実施形態において、半導体デバイスは、ダイがPCBに直接に機械的、かつ電気的に取り付けられる第1のレベルのパッケージングのみを有し得る。

【0030】

例示の目的のために、ワイヤボンド56およびフリップチップ58を含むいくつかのタイプの第1のレベルのパッケージングが、PCB52上に示される。さらに、ボールグリッドアレイ(BGA)60、バンプチップキャリア(BCC)62、デュアルインラインパッケージ(DIP)64、ランドグリッドアレイ(LGA)66、マルチチップモジュール(MCM)68、カッドフラット無鉛パッケージ(QFN)70、およびカッドフラットパッケージ72を含むいくつかの第2のレベルのパッケージングが、PCB52上に取り付けられる。システムの要求に依存して、第1および第2のレベルのパッケージング型の任意の組み合わせを用いて構成される半導体パッケージの任意の組み合わせだけではなく、他の電子部品もPCB52に接続され得る。いくつかの実施形態において、電子デバイス50は、単一の張りつけられた半導体パッケージを含み、その一方で、他の実施形態は、複数の相互接続されたパッケージを必要とする。単一の基板にわたって1つ以上の半導体パッケージを組み合わせることによって、製造者は、電子デバイスおよびシステムに事前に作られた部品を組み込み得る。半導体パッケージが、高性能の機能を含むので、電子デバイスは、より安価な部品および流線型製造プロセスを用いて製造され得る。結果のデバイスは、故障がより少なく、製造もより安価であり、結果として消費者にとってより低いコストをもたらす。

【0031】

図3a〜3cは、代表的な半導体パッケージを示す。図3aは、PCB52上に取り付けられたDIP64のさらなる詳細を例示する。半導体ダイ74は、能動領域を含み、能動領域は、ダイ内に形成され、かつダイの電気的設計に従って電気的に相互接続される能動デバイス、受動デバイス、導電層、および誘電層として実装されるアナログまたはデジタル回路を含む。例えば、回路は、1つ以上のトランジスター、ダイオード、インダクター、キャパシター、レジスター、および半導体ダイ74の能動領域内に形成された他の回路要素を含み得る。接触パッド76は、導電性材料、例えば、Al、Cu、tin(Sn)、ニッケル(Ni)、金(Au)、または銀(Ag)の1つ以上の層であり、半導体ダイ74内に形成された回路要素に電気的に接続される。DIP64の組立の間に、半導体ダイ74は、金−シリコン共晶層、または熱エポキシまたはエポキシ樹脂等のような接着材料を用いて、中間キャリア78に取り付けられる。パッケージ本体は、絶縁パッケージング材料、例えば、ポリマーまたはセラミックを含む。導体リード80およびボンドワイヤ82は、半導体ダイ74とPCB52との間に電気的相互接続を提供する。カプセルの材料84は、水分および粒子がパッケージに浸入し、ダイ74またはボンドワイヤ82を汚染することを防止することによる環境的保護のために、パッケージの上に蒸着される。

【0032】

図3bは、PCB52上に取り付けられたBCC62のさらなる詳細を例示する。半導体ダイ88は、アンダーフィルまたはエポキシ樹脂の接着材料92を用いてキャリア90上に取り付けられる。ボンドワイヤ94は、接触パッド96と98との間の第1のレベルのパッケージング相互接続を提供する。成形する化合物またはカプセルの材料100は、デバイスに対して物理的支持および電気的分離を提供するために、半導体ダイ88およびボンドワイヤ94上に蒸着される。接触パッド102は、酸化を防止するために、適切な金属蒸着プロセス、例えば、電解めっきまたは無電解めっきを用いてPCB52の表面上に形成される。接触パッド102は、PCB52の1つ以上の導電性信号トレース54に電気的に接続される。バンプ104は、BCC62の接触パッド98と、PCB52の接触パッド102との間に形成される。

【0033】

図3cにおいて、半導体ダイ58は、フリップチップ型の第1のレベルのパッケージングを有する中間キャリア106にうつ伏せ状態で取り付けられている。半導体ダイ58の能動領域108は、ダイの電気的設計に従って形成される能動デバイス、受動デバイス、導電層、および誘電層として実装されるアナログまたはデジタル回路を含む。例えば、回路は、1つ以上のトランジスター、ダイオード、インダクター、キャパシター、レジスター、および能動領域108内の他の回路要素を含み得る。半導体ダイ58は、バンプ110を介してキャリア106に電気的、かつ機械的に接続される。

【0034】

BGA60は、バンプ112を用いて、BGA型の第2のレベルのパッケージングを有するPCB52に電気的、かつ機械的に接続される。半導体ダイ58は、バンプ110、信号ライン114、およびバンプ112を介してPCB52の導電性信号トレース54に電気的に接続される。成形する化合物またはカプセルの材料116は、デバイスに対して物理的支持および電気的分離を提供するために、半導体ダイ58およびキャリア106の上に蒸着される。フリップチップ半導体デバイスは、信号伝搬距離を減少させ、キャパシタンスを低下させ、全体の回路性能を向上させるために、半導体ダイ58上の能動デバイスからPCB52上の導電性トレースまでに短い電気的伝導パスを提供する。別の実施形態において、半導体ダイ58は、中間キャリア106を有しないフリップチップ型の第1のレベルのパッケージングを用いてPCB52に直接に機械的、かつ電気的に接続され得る。

【0035】

図4a〜4tは、図2および3a〜3cに関連して、密集したトランジスターの上に形成された相互接続構造および珪化物層を有し、さらにロープロファイルのバンプを含むパワーMOSFETを形成するプロセスにおけるステップを例示する。図4aは、構造的支持のためのベース基板材料122、例えば、シリコン、ゲルマニウム、ガリウムヒ素、リン化インジウム、または炭化珪素を有する半導体ウェーハ120を示す。

【0036】

図4bは、MOSFETセル124を形成するための、ベース基板材料122から作られた基板または半導体ウェーハ120の一部分の断面図を示す。半導体ウェーハ120は、上部表面130と、上部表面130の反対側にある底部表面132とを含む。

【0037】

MOSFETセル124は、nチャンネルデバイス(N−MOS)またはpチャンネルデバイス(P−MOS)であり得、「p」が、正のキャリアタイプ(正孔)を示し、「n」が、負のキャリアタイプ(電子)を示す。MOSFETセル124の本実施形態が、p型基板120上に形成されるN−MOSデバイスに関して説明されるが、反対のタイプの半導体材料は、P−MOSデバイスを形成するために使用され得る。例えば、n型基板は、n型井戸領域を形成するために、最初に、n型半導体材料、例えば、リン、アンチモン、または砒素の不純物を用いてドープされ得る。p型基板120を含む本発明の実施形態はさらに、pマイナス型基板の最上部上に蒸着され得る。

【0038】

図4cにおいて、絶縁層または誘電層134は、ゲート酸化層として、基板120の表面130上に形成される。絶縁層134は、二酸化珪素(SiO2)、窒化珪素(Si3N4)、酸窒化珪素(SiON)、五酸化タンタル(Ta2O5)、酸化アルミニウム(Al2O3)、ポリイミド、BCB、ポリベンゾオキサゾール(PBO)、または他の適切な誘電材料の1つ以上の層を含む。絶縁層134は、PVD、CVD、スクリーンプリント、スピンコーティング、スプレーコーティング、焼結、または熱酸化を用いて形成される。

【0039】

図4dにおいて、ポリシリコン138が、絶縁層134上に形成される。図4eにおいて、フォトレジスト層140が、ポリシリコン層138上に形成される。フォトレジスト層に開口部142を形成し、かつポリシリコン層138の一部分を露出させるために、フォトレジスト層140の一部分が、エッチングプロセスによって除去される。エッチングプロセスにおいて除去されていないフォトレジスト140の残り部分は、MOSFETセル124内の、ゲートバターンに対応する。

【0040】

図4fにおいて、開口部142のフットプリント内、かつフォトレジスト140の外側に設置されているポリシリコン138の一部分が、エッチングプロセスによって除去される。ポリシリコン層138の残り部分は、後に形成されるMOSFETセル124内のトランジスターのためのゲートとして役に立つ。

【0041】

図4gにおいて、フォトレジスト層140の残りは、ポリシリコン層138のエッチングの後に除去される。図4gは、低濃度ドープされたドレイン(LDD)領域144および146を形成するために、基板120が、n型半導体材料、例えば、砒素を用いてドープされることをさらに示す。n型ドーパントが、イオン注入によって蒸着される。イオン注入によって導入されるドーパントの量は、LDD領域144および146が、nマイナスLDDおよびn型領域を含むように変化し得る。

【0042】

図4hにおいて、絶縁層150が、ポリシリコン層138の周り、かつ絶縁層134の上に形成される。絶縁層150はまた、LDD領域144および146の一部分の上に延在する。絶縁層150は、SiO2、Si3N4、SiON、Ta2O5、Al2O3、ポリイミド、BCB、PBO、または他の適切な誘電材料の1つ以上の層を含む。絶縁層150は、PVD、CVD、スクリーンプリント、スピンコーティング、スプレーコーティング、焼結、または熱酸化を用いて形成される。LDD領域144および146上の絶縁層134の一部分が、マスクとしてポリシリコン層138および絶縁層150を用いるエッチングプロセスによって除去される。絶縁層134の残り部分は、ポリシリコン層138を超えて、LDD領域144および146の上、かつ絶縁層150の下に延在する。絶縁層150はまた、後のドレインおよびソースイオン注入をマスクするための側壁スペーサーとして動作する。絶縁層150の配置は、開口部142によって露出される絶縁層134のエリアを減少させ、それによって、開口部142のエリアより小さいエリアを有する開口部152を形成させる。

【0043】

図4iにおいて、ポリシリコン層138および絶縁層150によって形成されたマスクの外側(すなわち、開口部152内)のLDD領域144および146の一部分は、ソース領域160およびドレイン領域170を形成するために、高濃度ドープされる。図4iが、単一のソース領域160および単一のドレイン領域170を示すが、MOSFETセル124は、後の図に示されるような複数のソース領域160およびドレイン領域170を含む。ソース領域160およびドレイン領域170は、それぞれ、事前に形成されたLDD144および146より深くウェーハ120内に延在する。従って、LDD領域144および146のエリアが、ソース領域160およびドレイン領域170の形成によって減少され、その結果、LDD領域144および146は、絶縁層150の下に設置される、減少されたエリアを占め、開口部152内のエリアを占めない。1つの実施形態において、LDD領域144および146を形成するために使用される、変化する注入の量は、nマイナス型LDD144およびn型領域146をもたらす。

【0044】

図4iは、ソース領域160が領域162、164および166を含むことをさらに示す。領域162、164および166が、さまざまな構成に従ってドープされ得る。第1の構成において、領域162が、nプラス型領域としてドープされ、領域164が、pプラス型領域としてドープされ、領域166が、n型領域としてドープされる。第2の構成において、領域164が、pプラス型領域としてドープされ、領域162および166が、pプラス型領域164の両側に隣接するnプラス型領域としてドープされる。さらに、ソース領域160の領域162および164は、LDD144を含み得る。これに反して、LDD144が、ソース領域160に完全にない場合もある。また図4iに形成されたドレイン領域170が、nプラス型領域としてドープされる。ドレイン領域170が、n型領域146の間に配置されている。

【0045】

図4jにおいて、珪化物層174が、ソース領域160およびドレイン領域170の上、並びにパシベーション層134の開口部152内の薄層として形成される。珪化物層174は、WSi2、TiSi2、MoSi2、TaSi2、または他の適切な珪化物を含み、PVD、CVD、共蒸着、スパッタリング、または他の適切なプロセスを使用することによって形成される。珪化物層174が、PVDによって形成されるが、珪化物層174は、半導体ウェーハ120上に耐熱性金属を蒸着させ、耐熱性金属が半導体ウェーハと接触する場所に珪化物層が形成されるように半導体ウェーハおよび耐熱性金属を加熱することによって自己整列される。珪化物層の一部分を形成するために、反応しない余分の耐熱性金属が除去される。珪化物層174が、ソース領域160の上部表面、およびドレイン領域170の上部表面に形成される。1つの実施形態において、珪化物層174は、100〜3000オングストロームの範囲の厚さを有する。珪化物層174は、ソース領域160およびドレイン領域170の上部表面にわたる金属導体として役に立つ。珪化物層174の存在は、MOSFETセル124の全体コストを減少させ、後に形成されるバンプから、ソース領域160およびドレイン領域170までの低抵抗電気的パスの一部分をそれぞれに形成することによって電流伝導を増大させる金属化パスとして役に立つ。

【0046】

図4kにおいて、絶縁層または中間層誘電体(ILD)180が、半導体ウェーハ120の上、すなわち、ポリシリコン層138、絶縁層150、および珪化物層174の上に形成されている。ILD180は、SiO2、Si3N4、SiON、Ta2O5、Al2O3、ポリイミド、BCB、PBO、または他の適切な誘電材料の1つ以上の層を含む。ILD180は、PVD、CVD、スクリーンプリント、スピンコーティング、スプレーコーティング、焼結、または熱酸化を用いて形成される。ILD180の一部分は、ビア182を形成するために、エッチングプロセスによって除去される。ビア182は、ILD180の上部表面から、ILDを通って、珪化物層174まで延在し、ソース領域160およびドレイン領域170への後の電気的接続を提供する。電気的接続はまた、ポリシリコン層138における、MOSFETセル124のためのゲート電極によって作られ、電気的接続は、ビア182による接続を含み得る。導電性材料184は、導電性ビアを形成するように、ビア182内、かつ珪化物層174の露出された部分上に形成される。導電性材料184は、タングステン(W)を含み、Al、Cu、Sn、Ni、Au、Ag、チタン(Ti)、ポリシリコン、または他の適切な電気伝導材料も含み得、PVD、CVD、電解めっき、無電解めっき、または他の適切な金属蒸着プロセスを用いて形成される。

【0047】

図4lは、図4kからのMOSFETセル124の上面図を示す。MOSFETセル124のソース領域160およびドレイン領域170は、基板120にわたって延在する交互配置ストライプのように、基板120に形成されている。ソース領域160およびドレイン領域170は、固定の距離の間隔で交互に空けられ、ポリシリコンゲート138によって分離される。

【0048】

導電性材料184が、ソース領域160上の導電性ビア186と、ドレイン領域170上の導電性ビア188とを形成するために、ビア182上に蒸着される。導電性ビア186および188は、ソース領域160およびドレイン領域170から、それぞれ、第1の相互接続層194への電気的接続を提供する。

【0049】

第1の相互接続層194は、ILD180の上、導電柱186および188の上、並びにソース領域160およびドレイン領域170の上に形成される。第1の相互接続層194は、ソースランナーまたは導電層196と、ドレインランナーまたは導電層198とを含む。ソースランナー196およびドレインランナー198は、1つ以上の層であり得、Cu、Sn、Ni、NiV、Au、Ag、Alまたは他の適切な導電性材料であり得る。ソースランナー196およびドレインランナー198は、電解めっき、無電解めっき、スパッタリング、PVD、CVD、または他の適切な金属蒸着プロセスを用いてパターンをつけられ、蒸着される。図4lに示されるソースランナー196とドレインランナー198とは、長方形、かつ実質的に等しい幅であるが、ランナーは、任意の形状であり得る。例として、ソースランナー196とドレインランナー198とは、等しくない幅であり得、ランナーは、変化する狭い部分およびより広い部分、並びに丸い角を有し得る。1つの実施形態において、第1の、ソースランナー196およびドレインランナー198は、従来のデバイスに対して短く、かつ広い寸法を含む。ソースランナー196およびドレインランナー198は、交互に配置され、固定の距離で交互に間隔を空けられ、互いに対して実質的に平行に配向される。ソースランナー196およびドレインランナー198は、ソース領域160およびドレイン領域170に対して、実質的に垂直または直交して配向される。代替的には、他の垂直でない向き(例えば、角度のある向きまたは平行の向き)が使用され得る。ソースランナー196およびドレインランナー198が配向されている反復する交互配置の、または交互に生じる間隔は、半導体ウェーハ120の表面にわたって分布されたユニット構造を生成する。

【0050】

ソースランナー196およびドレインランナー198は、それぞれ、導電性ビア186および188を介して、ソース領域160およびドレイン領域170に電気的に接続される。図4lは、2つのビア186が、ソース領域とソースランナーとが重なる場所において、ソース領域160とソースランナー196との間に電気的接続を形成するために使用されることを示す。同様に、図4lは、2つのビア188が、ドレイン領域とドレインランナーとが重なる場所において、ドレイン領域170とドレインランナー198との間に電気的接続を形成するために使用されることをさらに示す。代替的には、1つの導電性ビア、または3つ以上の導電性ビアは、それぞれ、ソース領域160およびドレイン領域170をソースランナー196およびドレインランナー198に接続するために使用され得る。

【0051】

図4kから続く図4mにおいて、MOSFETセル124およびソースランナー196の断面図を示す。図4lから、ソースランナー196は、導電性ビア186上に形成され、かつ導電性ビア186に電気的に接続される。

【0052】

図4nにおいて、絶縁層またはILD200が、第1の相互接続層194およびILD180の上に形成される。ILD200は、SiO2、Si3N4、SiON、Ta2O5、Al2O3、ポリイミド、BCB、PBO、または他の適切な誘電材料の1つ以上の層を含む。ILD200は、PVD、CVD、スクリーンプリント、スピンコーティング、スプレーコーティング、焼結、または熱酸化を用いて形成される。ILD200の一部分は、ビア202を形成するために、エッチングプロセスによって除去される。ビア202は、ILD200の上部表面から、ILDを通して、第1の相互接続層194まで延在する。導電性材料204が、導電性ビアを形成するために、ビア202内、かつ第1の相互接続層194の露出された部分の上に形成される。導電性材料204は、Wを含み、Al、Cu、Sn、Ni、Au、Ag、Ti、ポリシリコン、または他の適切な電気伝導材料も含み得、PVD、CVD、電解めっき、無電解めっき、または他の適切な金属蒸着プロセスを用いて形成される。

【0053】

図4oは、図4nからの部分的に形成された半導体デバイスの上面図を示す。ビア202内に形成された導電性材料204は、ソースランナー196上に形成された導電性ビア206と、ドレインランナー198上に形成された導電性ビア208とをもたらす。導電性ビア206および208は、それぞれ、ソースランナー196およびドレインランナー198から第2の相互接続層214への電気的接続を提供する。

【0054】

第2の相互接続層214は、ILD200上、導電柱206および208の上、並びに第1の相互接続層194上に形成される。第2の相互接続層214は、ソースランナーまたは導電層216と、ドレインランナーまたは導電層218とを含む。ソースランナー216およびドレインランナー218は、1つ以上の層であり得、Cu、Sn、Ni、NiV、Au、Ag、Alまたは他の適切な導電性材料であり得る。ソースランナー216およびドレインランナー218は、電解めっき、無電解めっき、スパッタリング、PVD、CVD、または他の適切な金属蒸着プロセスを用いてパターンをつけられ、蒸着される。図4oに示されるソースランナー216とドレインランナー218とは、実質的に等しい幅、かつ長方形であるが、ランナーは、任意の形状であり得る。例として、ソースランナー216とドレインランナー218とは、等しくない幅であり得、ランナーは、変化する細い部分およびより広い部分、並びに丸い角を有し得る。1つの実施形態において、第2の、ソースランナー216およびドレインランナー218は、従来のデバイスに対して短く、かつ広い寸法を含む。ソースランナー216およびドレインランナー218は、交互に配置され、固定の距離で交互に間隔を空けられ、互いに対して実質的に平行に配向される。ソースランナー216およびドレインランナー218は、ソースランナー196およびドレインランナー198に対して、実質的に垂直または直交して配向される。代替的には、他の垂直でない向き(例えば、角度のある向きまたは平行の向き)が使用され得る。ソースランナー216およびドレインランナー218が配向されている反復する交互配置の、または交互に生じる間隔は、ソースランナー196およびドレインランナー198だけではなく、半導体ウェーハ120の表面にもわたって分布されたユニット構造を生成する。

【0055】

ソースランナー216およびドレインランナー218は、それぞれ、導電性ビア206および208を介して、ソースランナー196およびドレインランナー198に電気的に接続される。図4oは、2つのビア206が、ソースランナー196と216が重なる場所において、ソースランナー196とソースランナー216との間に電気的接続を形成するために使用されることを示す。同様に、図4oは、2つのビア208が、ドレインランナーが重なる場所において、ドレインランナー198とドレインランナー218との間に電気的接続を形成するために使用されることをさらに示す。代替的には、1つの導電性ビア、または3つ以上の導電性ビアが、それぞれ、ソース領域160およびドレイン領域170をソースランナー196およびドレインランナー198に接続するために使用され得る。

【0056】

図4nから続く図4pにおいて、MOSFETセル124、並びにソースランナー216およびドレインランナー218の断面図を示す。図4oから、ソースランナー216は、導電性ビア206上に形成され、かつ導電性ビア206に電気的に接続される。

【0057】

図4qにおいて、絶縁層またはILD220が、第2の相互接続層214およびILD200の上に形成される。ILD220は、SiO2、Si3N4、SiON、Ta2O5、Al2O3、ポリイミド、BCB、PBO、または他の適切な誘電材料の1つ以上の層を含む。ILD220は、PVD、CVD、スクリーンプリント、スピンコーティング、スプレーコーティング、焼結、または熱酸化を用いて形成される。ILD220の一部分は、ビア222を形成するために、エッチングプロセスによって除去される。ビア222は、ILD220の上部表面から、ILDを通って、第2の相互接続層214まで延在する。導電性材料224が、導電性ビアを形成するために、ビア222内、かつ第2の相互接続層214の露出された部分の上に形成される。導電性材料224は、Wを含み、アルミニウムAl、Cu、Sn、Ni、Au、Ag、Ti、ポリシリコン、または他の適切な電気伝導材料も含み得、PVD、CVD、スッパタリング、電解めっき、無電解めっき、または他の適切な金属蒸着プロセスを用いて形成される。

【0058】

図4rは、図4qからの部分的に形成された半導体デバイスの上面図を示す。ビア222内に形成された導電性材料224は、ソースランナー216上に形成された導電性ビア226をもたらす。導電性ビア226は、それぞれ、ソースランナー216から第3の相互接続レベル234への電気的接続を提供する。ソースパッド236は、ILD220上、導電柱226上、および第2の相互接続層214上の第3の相互接続レベル234に形成される。ソースパッド236は、Cu、Sn、Ni、NiV、Au、Ag、Alまたは他の適切な導電性材料の1つ以上の層であり得る。ソースパッド236は、電解めっき、無電解めっき、スパッタリング、PVD、CVD、または他の適切な金属蒸着プロセスを用いてパターンをつけられ、蒸着される。

【0059】

ソースパッド236は、ソース領域160とMOSFETセル124に対する外部のデバイスとの間に電気的接続を提供する、後に形成されるソースバンプに接続されるように構成されている。同様に、ビア222内、かつドレインランナー218上に形成された導電性材料224は、ドレインランナー218からドレインパッドへの電気的接続を提供する。ドレインパッドは、ドレイン領域170からMOSFETセル124に対する外部のデバイスへの電気的接続を提供する、後に形成されるドレインバンプに接続されるように構成されている。

【0060】

図4qから続く図4sは、MOSFETセル124およびソースパッド236の断面図を示す。図4rから、ソースパッド236は、導電性ビア226上に形成され、かつ導電性ビア226に電気的に接続される。電気伝導バンプ材料は、図6a〜6iにさらに詳細に説明されるように、ソースバンプまたは相互接続240を形成するために、ソースパッド236上に蒸着される。ソースバンプ240は、ソース領域160からMOSFETセル124に対する外部のデバイスへの電気的接続を提供する。ソースバンプ240は、ソースパッド236上に形成され得る1つのタイプの相互接続構造を表す。ソースバンプまたは相互接続240はまた、ボンドワイヤ、導電性ペースト、スタッドバンプ、マイクロバンプ、または他の電気的相互接続を使用し得る。

【0061】

図4tは、MOSFETセル124の等角の3次元図を示す。第1の相互接続層194、第2の接続層214、および導電性ビアは、ソース領域160およびドレイン領域170から、第3の相互接続レベル234でのソースパッドおよびドレインパッドへの電気的接続を提供する。従って、単一のソースパッドおよびドレインパッドの下に設置されたソース接続およびドレイン接続の両方を有する、半導体ダイの全表面にわたって形成される、密接に整列されたトランジスターを接続する問題が解決される。トランジスターのソース領域およびドレイン領域を単一のソースパッドまたはドレインパッドに接続し得る厳密に垂直方向の相互接続を使用するのではなく、むしろ導電性ランナーは、単一のパッドの下のトランジスターのソース領域およびドレイン領域を複数の対応するパッドに接続するように構成されている。このようにして、トランジスターのドレイン領域が、ドレインパッドに接続され、トランジスターのソース領域が、ソースパッドに接続される。具体的には、ソース領域160は、ソースパッド236、導電性ビア186、ソースランナー196、導電性ビア206、ソースランナー216、および導電性ビア226によってソースバンプ240に電気的に接続される。同様に、ドレイン領域170は、導電性ビア188、ドレインランナー198、導電性ビア208、ドレインランナー218、およびドレインランナー218からドレインパッドに延在する追加の導電性ビアによってドレインパッドに電気的に接続される。

【0062】

珪化物層174が、ソース領域160およびドレイン領域170の上に形成される。珪化物層174は、ソース領域160およびドレイン領域170の上部表面上に形成される。珪化物層174は、ソース領域160およびドレイン領域170の上部表面にわたる金属導体として役に立つ。珪化物層174は、MOSFET124の全体コストを減少させるように、ソース領域160およびドレイン領域170の上部表面にわたる金属導体として役に立ち、ソース領域160およびドレイン領域170から後に形成されるバンプへの低抵抗電気的パスの一部分として電流伝導を増大させるための金属化パスとしてそれぞれに役に立つ。

【0063】

図5aは、複数のMOSFETセル、例えば、図4tからのMOSFETセル124を含むパワーMOSFET258の等角の3次元図を示す。パワーMOSFET258は、数百個または数千個のMOSFETセル124を含む。図5aにおいて、MOSFETセルの詳細、例えば、ソース領域160、ドレイン領域170、およびポリシリコンゲート138だけではなく、第1の相互接続層194、第2の相互接続層214、並びに導電性ビア186、188、206、208、および226を含む導電性ビアも含む、図4tに示されるMOSFETセル124の詳細が、明示的には示されていないが、パワーMOSFET258内、かつソースバンプ240、ドレインバンプ246、およびゲートバンプ250の下に含まれている。図5aは、ソースパッド236上に形成されたソースバンプ240、ドレインパッド244上に形成されたドレインバンプ246、およびゲートパッド248上に形成されたゲートバンプ250をさらに示している。図5aに示される実施形態において、ソースパッド236およびドレインパッド244は、パワーMOSFET258の上部表面にわたってチェッカーボード構成で配列されている。複数のMOSFETセル124のための電気的接続は、複数のソースパッド236、ドレインパッド244、およびゲートパッド248を通してルートが定められる。パワーMOSFET258は、各パワーMOSFET258内のダイまたはパッケージエリアの大部分を覆う、相互接続されたMOSFETセルのアレイを含む。各パワーMOSFET258は、電流の多くのアンペアを処理することが可能な単一のモノリシックスイッチングデバイスとして動作する。

【0064】

図5bは、図5aに示されるパワーMOSFET258に類似するパワーMOSFET259の代替の、等角の3次元図を示す。「ストライプ」状の形状のソースパッド237およびドレインパッド245が、交互に配置され、固定の距離で交互に間隔を空けられ、互いに対して実質的に平行に配向される。ゲートパッド249は、パワーMOSFETの構成および設計に従って、短縮されたソースパッド237または短縮されたドレインパッド245と直列に、パワーMOSFET259の上部表面上に形成される。図5bは、ソースパッド237上に形成されたソースバンプ241、ドレインパッド245上に形成されたドレインバンプ247、およびゲートパッド249上に形成されたゲートバンプ251をさらに示す。

【0065】

図5cは、複数のパワーMOSFET258をさらに含む、図4aからの半導体ウェーハ120の上面図を示す。パワーMOSFET258は、前述のように、ベース基板材料122上に形成され、かつソーストリート260によって分離される。

【0066】

図6a〜6iは、図4a〜4tおよび5a〜5cに関連して、それぞれ、パッド236、244、および248上にバンプ240、246、および250を形成するプロセスに関するさらなる詳細を例示する。

【0067】

図6aは、ソーストリート260によって分離された別個のパワーMOSFET258に属する複数のMOSFETセル124の一部分を含む、半導体ウェーハ120の一部分の断面図を示す。ソース接触パッド236およびドレイン接触パッド244の両方は、MOSFETセル124上に第3の相互接続レベル234にあると示される。ソース領域160、ドレイン領域170、およびポリシリコンゲート138だけではなく、第1の相互接続層194、第2の相互接続層214、並びに導電性ビア186、188、206、208、および226を含む導電性ビアも含む、図4tに示されるMOSFETセル124の詳細が、明示的には示されていないが、ソースパッド236およびドレインパッド244の下に含まれている。ソースバンプがソースパッド236上に形成される前、およびドレインバンプがドレインパッド244上に形成される前に、いくつかの介在する層が、ソースパッドおよびドレインパッドの上に形成される。具体的には、絶縁またはパシベーション層270は、MOSFETセル124の上部表面、ソース接触パッド236、ドレイン接触パッド244、およびソーストリート260の上の第3の相互接続レベル234において、半導体デバイスに順応的に適用される。絶縁層270の底部表面は、第3の相互接続レベル、ソース接触パッド236、およびドレイン接触パッド244の底部表面の輪郭に順応的に適用され、かつそれに追従する。絶縁層270の上部表面は、絶縁層が、ソースパッド236およびドレインパッド244のフットプリントの外側の、半導体ウェーハ120上の第1の厚さと、ソースパッド236およびドレインパッド244のフットプリント内の、半導体ウェーハ120上の第2の厚さとを有するように、実質的に平面である。第1の厚さは、第2の厚さより厚い。絶縁層270は、SiO2、Si3N4、SiON、Ta2O5、ジルコン(ZrO2)、Al2O3、ポリイミド、BCB、PBO、または適切な電気絶縁の性質を有する他の材料の1つ以上の層であり得る。絶縁層270は、PVD、CVD、プリント、スピンコーティング、スプレーコーティング、硬化焼結、または熱酸化を用いてパターンをつけられ、層状に蒸着される。絶縁層270の一部分は、ソースパッド236およびドレインパッド244の一部分を露出させる、絶縁層270における開口部272を生成するために、エッチングプロセスによって除去される。開口部272は、絶縁層270の上部表面から、絶縁層270の下部表面まで延在する。1つの実施形態において、開口部272は、図1aからの開口部20の幅に類似する270μmの幅を有する。ソースパッド236およびドレインパッド244の別の部分は、絶縁層270によって覆われた状態のままである。

【0068】

図6bにおいて、電気伝導層278は、パターニングおよび金属蒸着プロセス、例えば、プリント、PVD、CVD、スパッタリング、電解めっき、および無電解めっきを使用することによって、ソースパッド236およびドレインパッド244の上、かつ絶縁層270の一部分の上に形成され、ソースパッド236およびドレインパッド244に順応的に適用される。1つの実施形態において、ウェーハ120は、無電解ニッケルめっき溶液内に浸され、ニッケルが、ソースパッド236およびドレインパッド244上に3μmの厚さまでめっきされる。代替的には、導電層278は、Al、Cu、Sn、Au、Ag、または他の適切な電気伝導材料の1つ以上の層であり得る。導電層278は、絶縁層270の上部表面にわたって延在し、開口部272の周囲における絶縁層270の側壁に沿って、開口部272内のソースパッド236およびドレインパッド244の上部表面にわたって、絶縁層270の上部表面の輪郭に追従する。導電層278は、開口部272のフットプリント内、かつソースパッド236およびドレインパッド244の上にあるエリア280を含む。エリア280は、実質的に平坦であり、ソースパッド236およびドレインパッド244のそれぞれの全エリアより小さい。導電層278は、後に形成されるバンプのための第1のUBM層として動作する。

【0069】

図6cにおいて、電気伝導層284は、蒸着プロセス、例えば、無電解めっき、またはパターニングおよび金属蒸着プロセス、例えば、プリント、PVD、CVD、スパッタリング、および電解めっきを用いて、導電層278上に形成され、かつ導電層278に順応的に適用される。1つの実施形態において、ウェーハ120が、無電解金めっき溶液内に浸され、約100オングストロームの厚さを有する金の層が、無電解めっきプロセスを用いて導電層278の露出された金属領域上にめっきされる。別の実施形態において、金の層は、約10〜300オングストロームの厚さでめっきされる。代替的には、導電層284は、Al、Cu、Sn、Ni、Ag、または他の適切な電気伝導材料の1つ以上の層であり得る。導電層284は、絶縁層270から露出された導電層278、ソースパッド236、およびドレインパッド244の表面にわたって導電層278の輪郭に追従する。導電層284は、導電層278の側壁にわたって、絶縁層270から、絶縁層270の上部表面へ、かつ絶縁層270の上部表面にわたって、そして導電層278のエリア280内へ、かつ導電層278のエリア280にわたって延在する。導電層284の上部表面は、エリア286を含み、エリア286は、ソースパッド236およびドレインパッド244の上に形成され、実質的に平坦であり、両方のエリア280より小さく、エリア280のフットプリント内に含まれている。導電層284は、導電層278、ソースパッド236、およびドレインパッド244への導電性バンプの後の張りつけを支援するための接着層として役に立つ第2のUBM層として働く。導電層278および284の使用が、UBMを形成する低コストの方法であるが、他の方法が、導電性バンプの後の張りつけを支援するように、ソースパッド236およびドレインパッド244の上にUBMを形成するためにも使用され得る。

【0070】

図6dにおいて、開口部290を有するステンシルまたはマスキング層288は、開口部290が、エリア286の露出された中心部分と整列されているようにウェーハ120上に配置される。ステンシル288は、固体表面を有する剛性本体を含み、金属または他の適切な材料で作られる。ステンシル288は、ウェーハ120の全体上に配置されており、後に形成されるバンプを受け取るように構成されるUBM部位と整列するために、所望の場所にレーザーまたは切断ツールによって形成される開口部290を含む。開口部290は、ステンシル288の一部分が、開口部290をパシベーション層270から分離するために、導電層278および284の周囲部分の上に配置されるようにエリア286の中心部分上に整列させられる。開口部290とパシベーション層270とを分離することによって、後に形成される導電性材料が、パシベーション層270下へ拡散し、または流れることが防止される。開口部290は、半導体パッケージの設計および機能に従って、後に蒸着される導電性ペーストの所定の体積を含むように形成された高さおよび幅を有する。従って、エリア286上に後に蒸着される導電性材料の体積は、ステンシルの厚さ、および開口部290の断面積またはアパーチャサイズによって決定される。1つの実施形態において、開口部290は、短い高さおよび円形断面を含む円筒の形状を有する導電性バンプを形成するように構成された円形の断面エリアを有する。別の実施形態において、開口部290は、270μmより狭い幅を有し、絶縁層270における開口部272の幅より狭い。

【0071】

図6eにおいて、電気伝導バンプ材料294が、開口部290内、かつエリア286の中心部分の上に蒸着される。導電性バンプ材料294は、Al、Sn、Ni、Au、Ag、Pb、ビスマス(Bi)、Cu、インジウム(In)、はんだ、および任意のフラックス溶液を用いるそれらの組み合わせであり得る。例えば、バンプ材料は、共晶Sn/Pb、高鉛はんだ、または無鉛はんだであり得る。導電性バンプ材料294は、バンプ材料を開口部290内の導電層284上にステンシリングによって蒸着される。ステンシリングは、対象物がステンシル288の上部表面を横断するときに、開口部290内に多量のバンプ材料294を押し付けるように、スクイジーのような対象物を使用することによって達成される。ステンシリングはまた、ステンシル288内の開口部290内に導電性バンプ材料294をスプレーし、プリントし、またはブラシすることによって達成される。代替的には、導電性バンプ材料294は、開口部290内に噴射され得る。ウェーハ120上、かつMOSFETセル124上に導電性バンプ材料294をステンシリングすることによって、回路ボード上に導電性ペーストをステンシリングすること以外、半導体ダイの上に導電性バンプを形成するためのバンプ材料が、単一のステップにおいて全半導体ウェーハ120に対して蒸着され得るように、導電性バンプ材料294の正確な場所が提供される。さらに、導電層284上に蒸着された導電性バンプ材料294の体積が、ステンシル288の厚さ、および開口部290の断面積またはアパーチャサイズによって制御され、それによって後に形成される導電性バンプの最終的サイズを制御する。

【0072】

図6fにおいて、ステンシル288は、エリア286の中心部分上の導電性バンプ材料294を残して、ウェーハ120上、かつ、導電層278および284、ソースパッド236、並びにドレインパッド244上から除去される。導電層278および284、ソースパッド236、並びにドレインパッド244上に残るはんだ材料の結果的体積は、ソースパッド236およびドレインパッド244の幅に対応する所定の直径を有し、かつボールドロッププロセスに使用される、事前成形されたはんだボールからの導電性材料の体積より少ない。

【0073】

図6gにおいて、導電性バンプ材料294は、短い導電性バンプ298を形成するために、その融点以上に材料を加熱することによってリフローされる。いくつかの応用において、バンプ298は、導電層278および284との接触を含む電気的、かつ機械的接続を向上させるために、数回にリフローされる。バンプ298のその後のリフローは、MOSFETセル124およびバンプ298を後に提供される基板に接続するために、MOSFETセル124に接続される間に、バンプ298をリフローすること、追加の後に提供される基板または多層化されたPCBにMOSFETセル124を取り付けるときにバンプ298をリフローすること、および追加の後に提供される基板または多層化されたPCBに追加の部品の取り付けまたはそれらの再処理のために、バンプ298をリフローすることをさらに含む。導電性ペースト294をリフローする場合に、導電性ペーストは、エリア286の中心部分から外向きに移動し、導電層の周囲において導電層284の側壁と接触し、導電層284の周囲に隣接する絶縁層270の一部分と接触する。開口部290の幅に実質的に等しい第1の幅から、導電層284の幅に実質的に等しい第2の幅までの導電性ペースト294の広がりは、短い導電性バンプ298をもたらす。バンプ298は、導電性ペースト294の幅より広い幅を有する円形プロファイルと、開口部290に蒸着された導電性ペーストの高さより低い高さとを有する。1つの実施形態において、導電性バンプ298は、約300μmの幅300、約200μmのバンプ間の間隔、および約500μmのピッチを有する。しかしながら、開口部290のピッチおよびバンプ298の対応するピッチは、さらにより小さく作られ得る。さらに、バンプ298は、約70μmの高さ302を有する。生じる短いバンプ298は、実質的に等しい高さの事前成形された球形はんだボールの接触エリアより広い、ソースパッド236およびドレインパッド244の接触エリアを有する。同様に、短いバンプ298は、同様な幅(例えば、300μm)を有する、事前成形された球形バールより実質的に短い高さ(例えば、70μm)を有する、従って、バンプ298の構成は、実質的に同様な高さの事前成形された球形はんだボールに対して、電流の向上された流れを提供する。

【0074】

図6hは、ソースパッド236およびドレインパッド244に形成された短いバンプ298、絶縁層270、導電層278、および導電層284の平面図または上面図を示す。前述のように、1つ実施形態において、ソースパッド236、ドレインパッド244、導電層278、および導電層284は、リフローされた298が、短い高さと円形の断面とを有する円筒の形状を含むように、円形の断面を有する。

【0075】

図6iにおいて、半導体ウェーハ120は、複数の短いバンプ298を有する個々のパワーMOSFET258を形成するために、ソーまたはレーザー切断ツール306を用いて、ソーストリート260を通って単一化される。

【0076】

図7aは、図4a〜4tに示される実施形態に類似する本発明の別の実施形態を示す。図7aは、MOSFETセル310の等角の3次元図を示す。MOSFETセル310は、図4tに示されるソース領域160およびドレイン領域170に類似する、ソース領域314およびドレイン領域316を含む。しかしながら、ソース領域314およびドレイン領域316は、図4tに示されるような「ストライプ」より、むしろMOSFETセル310にわたる「チェッカーボード」パターンで形成されるように示される。

【0077】

導電性ビア320は、PVD、CVD、電解めっき、無電解めっきプロセス、または他の適切な金属蒸着プロセスを用いてソース領域314上に形成され、W、Al、Cu、Sn、Ni、Au、Ag、Ti、ポリシリコン、または他の適切な電気伝導材料を含む。導電性ビア320は、ソース領域314から第1の相互接続層322への電気的接続を提供する。

【0078】

第1の相互接続層322は、MOSFETセル310上、導電性ビア320上、およびドレイン領域316上に形成される。第1の相互接続層322は、導電平面324を含み、導電平面324は、開口部またはカットアウト328と、接続330とをさらに含む。導電平面324は、Cu、Sn、Ni、NiV、Au、Ag、Alまたは他の適切な導電性材料の1つ以上の層である。導電平面324は、電解めっき、無電解めっき、スパッタリング、PVD、CVD、または他の適切な金属蒸着プロセスを用いてパターンをつけられ、蒸着される。導電平面324は、導電性ビア320を介してソース領域314に電気的に接続し、ソース接続層として動作する。導電平面324における開口部328が、導電平面の一部分の除去によって形成される。接続300の周囲における導電平面324の一部分を除去することによって、接続300は、導電平面324に対して電気的に隔離され、導電平面324と接触せず、第1の相互接続層322の上から第1の相互接続層の下へ通過する後の垂直方向の電気的接続のために構成される。

【0079】

導電性ビア334は、PVD、CVD、電解めっき、無電解めっきプロセス、または他の適切な金属蒸着プロセスを用いてドレイン領域316上に形成され、W、Al、Cu、Sn、Ni、Au、Ag、Ti、ポリシリコン、または他の適切な電気伝導材料を含む。導電性ビア334は、ドレイン領域316から接続330への電気的接続を提供する。同様に、導電性ビア336は、PVD、CVD、電解めっき、無電解めっきプロセス、または他の適切な金属蒸着プロセスを用いて接続330上に形成され、W、Al、Cu、Sn、Ni、Au、Ag、Ti、ポリシリコン、または他の適切な電気伝導材料を含む。導電性ビア336は、接続330から第2の相互接続層338への電気的接続を提供する。

【0080】

第2の相互接続層328は、MOSFETセル310上、ソース領域314およびドレイン領域316上、導電性ビア320、334、および336、並びに接続330上に形成される。第2の相互接続層338は、導電平面340を含み、導電平面は、開口部342と、接続344とをさらに含む。導電平面340は、Cu、Sn、Ni、NiV、Au、Ag、Alまたは他の適切な導電性材料の1つ以上の層である。導電平面340は、電解めっき、無電解めっき、スパッタリング、PVD、CVD、または他の適切な金属蒸着プロセスを用いてパターンをつけられ、蒸着される。導電平面340は、導電性ビア334、接続330、および導電性ビア336を介してドレイン領域316に電気的に接続し、ドレイン接続層として動作する。導電平面340における開口部342が、導電平面の一部分の除去によって形成される。接続344の周囲における導電平面340の一部分を除去することによって、接続344は、導電平面340に対して電気的に隔離され、導電平面340と接触せず、第2の相互接続層340の上から第2の相互接続層の下へ通過する後の垂直の電気的接続のために構成される。

【0081】

導電性ビア346は、PVD、CVD、電解めっき、無電解めっきプロセス、または他の適切な金属蒸着プロセスを用いて第1の相互接続層322上に形成され、W、Al、Cu、Sn、Ni、Au、Ag、Ti、ポリシリコン、または他の適切な電気伝導材料を含む。導電性ビア346は、接続344に、かつ導電性ビア320および導電平面324を介してソース領域314に電気的に接続される。接続344は、第3の相互接続層にさらに電気的に接続される。

【0082】

図4rおよび4sにおいて第3の相互接続層として示されるソースパッド236に類似して、第3の相互接続層は、MOSFETセル310上、ソース領域314およびドレイン領域316上、導電性ビア320、334、336、および346、接続330および344、並びに第1の相互接続層322および第2の相互接続層338上に形成される。第3の相互接続層は、Cu、Sn、Ni、NiV、Au、Ag、Alまたは他の適切な導電性材料の1つ以上の層であるソースパッドを含む。ソースパッドは、電解めっき、無電解めっき、スパッタリング、PVD、CVD、または他の適切な金属蒸着プロセスを用いてパターンをつけられ、蒸着される。ソースパッドは、ドレイン領域316とMOSFETセル310に対する外部のデバイスとの間に電気的接続を提供する、後に形成されるソースバンプに接続されるように構成されている。

【0083】

電気伝導バンプ材料は、図6a〜6iに説明されるように、ソースバンプまたは相互接続を形成するために、ソースパッド上に蒸着される。ドレインバンプは、ドレイン領域316からMOSFETセル310に対する外部のデバイスへの電気的接続を提供する。ソースバンプは、ソースパッド上に形成され得る1つのタイプの相互接続構造を表す。ソースバンプまたは相互接続はまた、ボンドワイヤ、導電性ペースト、スタッドバンプ、マイクロバンプ、または他の電気的相互接続を使用し得る。

【0084】

図7bは、ドレイン領域316を、導電性ビア334、接続330、導電性ビア336、および導電平面340に電気的に接続するための、開口部328を有する導電平面324の上面図を示す。

【0085】

図7cは、ソース領域314を、導電性ビア320、導電平面324、導電性ビア346、および接続344に電気的に接続するための、開口部342を有する導電平面340の上面図を示す。

【0086】

図8は、図4a〜4tおよび図7a〜7cに示される実施形態に類似する本発明の別の実施形態を示す。図8は、図4l〜4tの相互接続レベル194、214、および234、並びに図7a〜7cの相互接続層322および338に配置された相互接続層に類似する相互接続層350の上面図を示す。各相互接続層350は、ソースランナーまたは導電層354と、ドレインランナーまたは導電層356とを含む。ソースランナー354およびドレインランナー356は、1つ以上の層であり得、Cu、Sn、Ni、NiV、Au、Ag、Alまたは他の適切な導電性材料であり得る。ソースランナー354およびドレインランナー356は、電解めっき、無電解めっき、スパッタリング、PVD、CVD、または他の適切な金属蒸着プロセスを用いてパターンをつけられ、蒸着される。ソースランナー354およびドレインランナー356は、十字の形状(+)であり、隣接するソース領域およびドレイン領域、または隣接する相互接続層との電気的接続を確立する。ソースランナー354およびドレインランナー356は、十字の形状(+)以外の形状、例えば、L形(L)およびT形(T)であり得る。

【0087】

ソースランナー354およびドレインランナー356は、隣接するランナーの中心ポイントの間に一定のピッチまたは距離を有する、反復するパターンで配列される。同様に、ソースランナー354およびドレインランナー356に接続される追加の構造、例えば、伝導性ビアおよびソースバンプ、または他の相互接続層はまた、中心ポイントの間に一定のピッチを有する、反復するパターンで配列される。ソースランナー354およびドレインランナー356が配向されている、反復する交互配置の、または交互する間隔は、ソースランナーおよびドレインランナーが形成される半導体ウェーハの表面上に分布させられたユニット構造を生成する。

【0088】

各相互接続層350は、第1、第2、第3、または他の相互接続レベルとして使用され得る。3つ以上、または4つ以上の相互接続層が使用され得、中間接続層が、第1の相互接続層と第2の相互接続層との間、または第2の相互接続層と第3の相互接続層との間に形成され得る。追加の中間接続層は、電気信号のルーティングを支援し、ソースバンプおよびドレイバンプまたは相互接続のピッチを減少させる。第1の相互接続レベルとして、相互接続レベル350は、導電性ビア、ソース領域およびドレイン領域に電気的に接続される。ソースランナー354およびドレインランナー356は、任意の所望の数のチップ面導電性要素を電気的に接続する。1つの実施形態において、十字のランナーは、5つのソース領域またはドレイン領域のグループと接触する導電性ビアに電気的に接続される。1つのビアは、十字の2つの直交部分が重なる十字のランナーの中心に設置され、4つのビアは、十字のランナーの4つの遠位端部に設置される。ソースランナー354およびドレインランナー356は、それぞれ、ソース領域およびドレイン領域に電気的に接続する。代替的には、ソースランナー354およびドレインランナー356は、集積デバイスのソース領域およびドレイン領域に接続する必要がないが、別の実施形態において、さまざまな別々の部品に電気的に接続し得る。第2の相互接続レベルとして、相互接続レベル350は、ソース領域およびドレイン領域の上、導電柱上、並びに第1の接続層上に形成される。第2の相互接続レベルとして、相互接続レベル350はまた、導電性ビアの下、第3の相互接続レベルの下、MOSFETセルに対する外部のデバイスへの電気的接続を提供する導電性ビアの下に配置され得る。第3の相互接続レベルとして、相互接続レベル350は、例えば、図6a〜6iに示されるように、後に形成されるソースバンプおよびドレインバンプまたは相互接続に接続されるように構成されており、ソースバンプおよびドレインバンプまたは相互接続は、第2の相互接続層とMOSFETセルに対する外部のデバイスとの間に電気的接続を提供する。1つの実施形態において、図6a〜6iからのソースバンプおよびドレインバンプは、十字の形状(+)のソースランナー354およびドレインランナー356の中心に張りつけられる。ソースバンプおよびドレインバンプまたは相互接続はまた、ボンドワイヤ、導電性ペースト、スタッドバンプ、マイクロバンプ、または他の電気的相互接続を含む。

【0089】

図9は、図4a〜4t、図7a〜7c、および図8に示される実施形態に類似する本発明の別の実施形態を示す。図9は、MOSFETセル360の等角の3次元図を示す。MOSFETセル360は、例えば、図4tに示されるソース領域160およびドレイン領域170に類似する、ソース領域372およびドレイン領域374を含む。図4dからのポリシリコン層138に類似するポリシリコン層364が、半導体ダイ362上に形成される。ポリシリコン層364の一部分が、エッチングプロセスによって除去され、図9に示されるポリシリコン層364の残り部分は、MOSFETセル360内のトランジスターのためのゲートとして役に立つ。図4hからの絶縁層150に類似する絶縁層366が、ポリシリコン層364の周りに形成され、ソース領域372およびドレイン領域374の一部分上に延在する。図4jの珪化物層174に類似する珪化物層368が、ソース領域372およびドレイン領域374の上に薄層として形成される。

【0090】

導電性ビア378が、ソース領域372上に形成され、導電性ビア380が、ドレイン領域374上に形成される。導電性ビア378および380は、W、Al、Cu、Sn、Ni、Au、Ag、Ti、ポリシリコン、または他の適切な電気伝導材料を含み、PVD、CVD、電解めっき、無電解めっきプロセス、または他の適切な金属蒸着プロセスを用いて形成される。導電性ビア378および380は、それぞれ、ソース領域372およびドレイン領域374から第1の相互接続層382への電気的接続を提供する。

【0091】

第1の相互接続層382は、MOSFETセル360上、導電性ビア378および380の上、並びにソース領域372およびドレイン領域374上に形成される。第1の相互接続層382は、図4lからのソースランナー196およびドレインランナー198に類似し、かつ図4oからのソースランナー216およびドレインランナー218に類似するソースランナーまたは導電層384およびドレインランナーまたは導電層386を含む。ソースランナー384は、ソース領域372上に形成され、導電性ビア378を用いてソース領域372に電気的に接続される。ドレインランナー386は、ドレイン領域374上に形成され、導電性ビア380を用いてドレイン領域374に電気的に接続される。ソースランナー384はまた、図4rに示される導電性ビア226に類似するソースランナー384上に形成された導電性ビアに電気的に接続される。ドレインランナー386はまた、ドレインランナー386上に形成された導電性ビア390に電気的に接続され、かつ第2の相互接続層394に電気的に接続される。

【0092】

図4rおよび4sにおいて第3の相互接続層として示されるソースパッド236に類似して、第2の相互接続層394が、MOSFETセル360上に形成される。第2の相互接続層394はまた、ソース領域372およびドレイン領域374上、導電性ビア378、380、および390、並びにソースランナー384およびドレインランナー386を含む第1の相互接続層382上に形成される。図9は、ドレインパッド396として形成された第2の相互接続層394を示し、ドレインパッド396は、ドレイン領域374と、MOSFETセル360に対する外部のデバイスとの間に電気的接続を提供するために、ドレインバンプ398に接続される。ドレインバンプ398は、図6a〜6iに描かれているように、ドレインパッド396上に形成される。ドレインバンプは、ドレイン領域374からMOSFETセル360に対する外部のデバイスへの電気的接続を提供する。ドレインバンプは、ドレインパッド396上に形成され得る1つのタイプの相互接続構造を表す。ソースバンプまたは相互接続398はまた、ボンドワイヤ、導電性ペースト、スタッドバンプ、マイクロバンプ、または他の電気的相互接続を含む。

【0093】

図10aは、図5aおよび6iからのパワーMOSFET258、または図5bからのパワーMOSFET259に類似して、短い導電性バンプ401を有する単一化されたパワーMOSFETセル400を示し、パワーMOSFETセル400が、基板に向かって配向されたバンプ401を用いて基板または多層化されたPCB402に取り付けられる。基板402は、パワーMOSFETが基板に取り付けられると、パワーMOSFET400に対して一般的に構造的支持および電気的相互接続を提供する。基板402は、導電性接触404をさらに含む。

【0094】

図10bにおいて、パワーMOSFET400が、基板402に取り付けられている。バンプ401の周り、または基板402とパワーMOSFET400との間には蒸着されるアンダーフィル材料が存在しない。バンプ401は、電気的、および機械的接続を向上させるために、複数回のリフローを受ける。バンプ401の複数回のリフローは、バンプをパワーMOSFET400に接続するために、バンプ401をリフローすること、パワーMOSFET400およびバンプ401を基板402に接続するために、パワーMOSFET400に接続される間にバンプ401をリフローすること、追加の基板または多層化されたPCBに基板402を取り付けるときにバンプ401をリフローすること、および追加の基板または多層化されたPCBの追加の部品の取り付けまたはそれらの再処理のために、バンプ401をリフローすることを含む。重要なことには、アンダーフィル材料がなくても、図1bに示されるバンプ28のような従来の球形バンプに対して、バンプ401の高さが減少されるために、バンプ401のブリッジングおよび電気的ショートのリスクが減少される。バンプ401に存在するバンプ材料の減少された体積は、他のバンプと接触するように広がり、かつ電気的ショートを引き起こすことなしに、リフローの間にUBM層の上の適所にとどまる傾向がある。それゆえに、アンダーフィル材料に対する必要性が減少され、半導体ダイのクラッキングおよび故障を引き起こすアンダーフィル材料の問題点が軽減される。

【0095】

カプセルの材料408は、ペーストプリント、圧縮成形、トランスファー成形、液体カプセル成形、真空積層、または他の適切な塗布具を用いて、基板402の上、およびパワーMOSFET400の上および周りに形成される。カプセルの材料408は、ポリマー合成材料、例えば、充填剤を有するエポキシ樹脂、充填剤を有するエポキシアクリラート、または適切な充填剤を有するポリマーであり得る。カプセルの材料408は、導電性ではなく、物理的支持を提供し、外部の要素および汚染からパワーMOSFET400を環境的に保護する。カプセルの材料408の一部分は、パワーMOSFET400と基板402との間に少なくとも部分的に延在し、特にパワーMOSFET400の周辺付近に延在する。カプセルの材料408はまた、パワーMOSFET400と基板402との間の隙間を完全に充填するために、パワーMOSFET400の下まで完全に延在する。バンプ401の減少された高さおよびロープロファイルのために、カプセルの材料408の配置に起因してパワーMOSFET400のシフトのリスクが減少される。さらに、不均一なアンダーフィル材料によって引き起こされた機械的、熱的、および化学的ストレスの問題は、均一に蒸着されたカプセルの材料で存在しない。短い導電性バンプ401を用いて基板402に取り付けられるパワーMOSFET400を含むパッケージ410の構成は、パワーMOSFET400のトランジスターと基板402の間に、従来の球形バンプを用いる場合より短い電気的パスを生成する。より短い電気的パスは、特に高周波数応用に関して、より低い抵抗およびより低いインダクタンスをもたらす。熱がパワーMOSFETから基板へより容易に転送されることを可能にする、パワーMOSFETと基板402との間の減少されたスタンドオフ高さのために、より短い電気的パスはまた、パワーMOSFET400の増大された熱性能をもたらす。それゆえに、アンダーフィル成形なしに、短い導電性バンプを用いる基板へのパワーMOSFETの張りつけを含むパッケージ410の構成は、バンプの間のはんだブリッジングおよびショートの問題を減少させると同時に、ロバストの電気的接続を維持し、それによって生産高および信頼性を増大させる。

【0096】

本発明の1つ以上の実施形態が、詳細に例示されたが、当業者は、それらの実施形態への変更および適応が、以下の請求範囲において説明されるような本発明の範囲から逸脱することなしに加えられ得ることを認識する。

【技術分野】

【0001】

(本発明の分野)

本発明は、概して、電子回路および半導体デバイスに関し、より具体的に、密集したトランジスターの上に形成された相互接続構造の珪化物層を有し、さらにロープロファイルバンプを含むパワーMOSFETを形成する半導体デバイスおよび方法に関する。

【背景技術】

【0002】

(本発明の背景)

半導体デバイスが、現代の電子製品において一般的に見つけられる。半導体デバイスは、電気部品の数および密度が変化する。離散的半導体デバイスは、概して、1つのタイプの電気部品、例えば、発光ダイオード(LED)、微小信号トランジスター、抵抗器、キャパシター、インダクター、パワー酸化金属半導体電界効果トランジスター(MOSFET)を含む。集積半導体デバイスは、典型的に、数百個から数百万個の電気部品を含む。集積半導体デバイスの例は、マイクロコントローラ、マイクロプロセッサ、電荷結合デバイス(CCD)、太陽電池、およびデジタルマイクロミラーデバイス(DMD)を含む。

【0003】

半導体デバイスは、広範囲の機能、例えば、信号処理、高速計算、電磁気信号を送受信すること、電子デバイスを制御すること、太陽光から電気へ変換すること、およびテレビジョンディスプレイのための視覚投影を生成することを行う。半導体デバイスは、エンターテイメント、通信、電力変換、ネットワーク、コンピュータ、および消費者製品の分野において見つけられる。半導体デバイスは、軍事用途、航空、自動車、工業用コントローラ、およびオフィス機器においても見つけられる。

【0004】

半導体デバイスは、半導体材料の電気的性質を活用する。半導体材料の原子構造は、半導体の材料の導電率が、電界またはベース電流の適用によって、またはドーピングの処理を介して操作されることを可能にする。ドーピングは、半導体材料内に不純物を導入し、半導体デバイスの導電率を操作し、かつ制御する。

【0005】

半導体デバイスは、能動電気構造および受動電気構造を含む。双極性電界効果トランジスターを含む能動構造は、電流の流れを制御する。ドーピングのレベル、および電界またはベース電流の適用のレベルを変化させることによって、トランジスターは、電流を促進するかまたは制限する。抵抗器、キャパシター、およびインダクターを含む受動構造は、さまざまな電気的機能を行うために必要な電圧と電流との間の関係を生成する。行う。受動構造および能動構造は、回路を形成するように電気的に接続されており、回路は、半導体デバイスが、高速計算および他の有用な機能を行うことを可能にする。

【0006】

半導体デバイスは、概して、2つの複雑な製造プロセス、すなわち、フロントエンド製造およびバックエンド製造を用いて製造され、各プロセスは、潜在的に数百個のステップを必要とする。フロントエンド製造は、半導体ウェーハの表面上に複数のダイの形成を必要とする。各ダイは、典型的に同様であり、能動部品と受動部品を電気的に接続することによって形成された回路を含む。バックエンド製造は、完成したウェーハから個々のダイを単一化することと、構造的支持および環境的分離を提供するようにダイをパッケージする。

【0007】

半導体製造の1つの目標は、より小さな半導体デバイスを生産することである。より小さなデバイスは、典型的に、より少ない電力を消費し、より低い電圧で動作し、より高い性能を有し、そしてより効率的に生産され得る。加えて、より小さな半導体デバイスは、より小さなエンド製品にとって望ましい、より小さなフットプリントを有する。より小さなダイのサイズは、フロントエンドプロセスの向上によって達成され得、より小さく、より高密度の能動部品および受動部品を有するダイをもたらす。バックエンドプロセスは、電気的相互接続およびパッケージング材料の改良によってより小さなフットプリントを有する半導体デバイスパッケージをもたらし得る。

【0008】

パワーMOSFETは、電子回路、例えば、通信システムおよび電源に一般的に使用される半導体デバイスの1つの例である。特に、パワーMOSFETは、電子スイッチとして使用される場合に、比較的に大きな電流の伝導を有効にし、無効にするのに有用である。パワーMOSFETのオン/オフ状態は、ゲート電圧にトリガー信号を印加し、除去することによって制御される。オンにされると、MOSFETにおける電流は、ドレインとソースとの間に流れる。オフにされると、電流が、MOSFETによってブロックされる。

【0009】

パワーMOSFETの小型化は、半導体のダイの全表面にわたって分布されている小さなMOSFETセルまたはトランジスターを含むデバイスを産み出す。MOSFETセルは、ソース領域およびドレイン領域を含み、ソース領域およびドレイン領域は、後の電気的相互接続のために、例えば、ソースパッドおよびドレインパッド上に形成されたバンプ、または端子の大きさのような電気的相互接続に形成される。従って、複数のソース領域およびドレイン領域は、しばしば、単一のソースパッドまたはドレインパッドの下に設置される。密集したトランジスターを有するパワーMOSFET内の厳しい垂直の相互接続の使用は、対応する水平にずれたソースパッドおよびドレインパッドと接続するために、単一のソースパッドまたはドレインパッドの下に設置されたトランジスターのソース領域およびドレイン領域の両方を接続することを提供しない。従って、水平のずれを考慮する相互接続構造は、単一のソースパッドまたはドレインパッドの下に設置されたトランジスターのソース領域およびドレイン領域を、水平オフセットのソースパッドおよびドレインパッドに接続する必要がある。

【0010】

さらに、他の半導体デバイスと同様に、パワーMOSFETは、半導体デバイスを、基板、回路基板、および他の半導体デバイスに電気的に接続するための相互接続構造を含む。半導体ダイをプリント回路基板(PCB)または他のデバイスと相互接続する1つの一般的な技術は、はんだバンプの使用を必要とする。図1aは、従来のUBMはんだバンプ構造10を示す。はんだバンプ構造10は、ベースシリコンの半導体ウェーハ12を含む半導体ダイ11を含み、能動エリア14が、半導体ウェーハ12上に形成されている。能動エリア14は、半導体ダイ11内に形成された能動デバイス、受動デバイス、導電層、および誘電層として実装され、かつ半導体ダイの電気的設計および機能に従って電気的に相互接続されたアナログまたはデジタル回路を含む。電気伝導層16は、半導体ダイ11の能動エリア14上に形成され、接触パッドとして動作する。絶縁またはパシベーション層18は、半導体ダイ11および導電層16上に形成される。絶縁層18の一部分は、導電層16の一部分を露出させる絶縁層の開口部20を形成するために、エッチングプロセスによって除去される。1つの実施形態において、開口部20は、270マイクロメートル(μm)の幅を有する。電気伝導またはUBM層22が、開口部20内の、絶縁層18の一部分の上の導電層16上に順応的に形成される。1つの実施形態において、導電層22は、アルミニウム(Al)を含む接着層、ニッケルバナジウム(NiV)を含むバリア層、および銅(Cu)を含む溶接層を含む。ベンゾシクロブテン(BCB)のような絶縁またはパシベーション層24が、導電層22および絶縁層18の上に形成される。絶縁層24の開口部26は、UBM22上に形成され、UBM22の一部分を露出させる。1つの実施形態において、開口部26は、280μmの幅を有する。導電性バンプ28は、従来のUBMはんだバンプ構造10を完成させるために、導電層16および22の上に、開口部20および26内に配置される。1つの実施形態において、導電性バンプ28は、ボールドロッププロセスで導電層22に取り付けられ、かつ350μmの所定の直径30を有する、事前成形されたはんだ球を含む。

【0011】

図1bは、パッケージ(SiP)32の中のオーバー成形のシステムの一部分として、パッケージングされている図1aからの、従来のUBMはんだバンプ構造10を有する半導体ダイ11を示す。半導体ダイ11は、導電性接触36をさらに含む基板または多層化されたPCB34に取り付けられている。アンダーフィル38は、半導体ダイ11と基板34との間の接続を向上させるために、バンプ28の周り、かつ基板34と半導体ダイ11の能動エリア14との間に蒸着される。バンプ28は、電気的、かつ機械的接続を向上させるために、複数回のリフローを受ける。バンプ28の複数回のリフローは、バンプを半導体ダイ11に接続するために、バンプ28をリフローすること、半導体ダイ11およびバンプ28を基板34に接続するために、半導体ダイ11に接続されるバンプ28をリフローすること、基板または多層化されたPCBにSiP32を取り付けるときに、バンプ28をリフローすること、および追加の基板または多層化されたPCBに追加の部品を取り付け、または追加の基板または多層化されたPCBの再処理のために、バンプ28をリフローすることを含む。しかしながら、いくつかの場合においてバンプ28をリフローすることは、バンプ28の間のはんだブリッジングおよび電気的ショートの原因となり、それによって、半導体ダイ11の故障を引き起こす。バンプ28の間のはんだブリッジングおよび電気的ショートは、バンプが微細ピッチを有する場合に、より発生する可能性が高い。アンダーフィル材料38は、バンプ28の間にアンダーフィルが欠けることを防止し、かつリフローの間、バンプ材料を局在化した状態に保つことによるはんだブリッジングおよび電気的ショートを防止することを助けるために最適化される。しかしながら、アンダーフィル38の配置を制御することは、難しく、不均一な厚さを有するアンダーフィルの配置を生じ得る。不均一な厚さのアンダーフィル材料38は、一般的であり、例えば、半導体ダイの第1の面上の、半導体ダイ11と基板34との間のギャップの一部分のみが充填されるが、半導体ダイの第2の面上のギャップの全体が充填される構成を含む。不均一に分布されたアンダーフィル38は、半導体ダイ11上にストレスの非平衡を引き起こし、ストレスの非平衡は、半導体ダイのクラッキングおよび故障を引き起こし得る。さらに、カプセルの材料または成形化合物40が、半導体ダイ11上、および周りに置かれる。カプセルの材料40と不均一に分布されたアンダーフィル38との組み合わせはさらに、半導体ダイ11上にストレスの非平衡を引き起こし、ストレスの非平衡はさらに、ダイのクラッキングおよび故障を引き起こす。従って、アンダーフィル38を有するSiP32の従来の組立体は、SiP組立体の生産高および信頼性を減少させる欠点になりやすい。

【発明の概要】

【課題を解決するための手段】

【0012】

(本発明の要約)

ロープロファイルバンプと、密集したトランジスター上に形成される相互接続構造とを有するパワーMOSFETを提供するニーズが存在する。従って、1つの実施形態において、本発明は、半導体デバイスを作る方法であり、方法は、基板を提供することと、基板の第1の表面上にソース領域を形成することと、ソース領域に隣接して、基板の第1の表面上にドレイン領域を形成することと、ソース領域およびドレイン領域の上に珪化物層を蒸着することと、珪化物層上に第1の相互接続層を形成することと、第1の相互接続層上に第2の相互接続層を形成することと、第2の相互接続層の上、かつ第2の相互接続層に電気的に接続されるUBMを形成することとを含む。第1の相互接続層は、ソース領域に接続される第1のランナーと、ドレイン領域に接続される第2のランナーとを含む。第2の相互接続層は、第1のランナーに接続される第3のランナーと、第2のランナーに接続される第4のランナーとを含む。方法は、マスクの開口部がUBM上に整列されるように、基板上にマスクを配置するステップと、開口部内に導電性バンプ材料を蒸着するステップと、マスクを除去するステップと、バンプを形成するために、導電性バンプ材料をリフローするステップとをさらに含む。

【0013】

別の実施形態において、本発明は、半導体デバイスを作る方法であり、方法は、ソース領域と、隣接するドレイン領域とを含む基板を提供することと、ソース領域およびドレイン領域の上に珪化物層を蒸着することと、珪化物層上に第1の相互接続層を形成することとを含む。第1の相互接続層は、ソース領域に接続される第1のランナーと、ドレイン領域に接続される第2のランナーとを含む。方法は、第1の相互接続層の上、かつ第1の相互接続層に電気的に接続されるUBMを形成するステップと、マスクの開口部がUBM上に整列されるように、基板上にマスクを配置するステップと、開口部内に導電性バンプ材料を蒸着するステップと、マスクを除去するステップと、バンプを形成するために、導電性バンプ材料をリフローするステップとをさらに含む。

【0014】

別の実施形態において、本発明は、半導体デバイスを作る方法であり、方法は、基板を提供することと、基板上に珪化物層を有するトランジスターを形成することと、トランジスターの上、かつトランジスターに接続される第1の相互接続層を形成することと、第1の相互接続層の上、かつ第1の相互接続層に接続されるUBMを形成することと、マスクの開口部がUBM上に整列されるように、基板上にマスクを配置することと、バンプを形成するために、開口部内に導電性材料を蒸着することとを含む。

【0015】

別の実施形態において、本発明は、半導体デバイスであり、半導体デバイスは、ソース領域と、隣接するドレイン領域とを含む基板を含む。珪化物層が、ソース領域およびドレイン領域の上に配置されている。第1の相互接続層が、珪化物層上に形成されている。第1の相互接続層は、ソース領域に接続される第1のランナーと、ドレイン領域に接続される第2のランナーとを含む。UBMが、第1の相互接続層上に形成されており、かつ第1の相互接続層に電気的に接続される。バンプが、UBMに電気的に接続される。バンプは、マスク開口部の体積によって決定される導電性バンプ材料の体積を有する。

【0016】

本発明は、例えば、以下の項目を提供する。

(項目1)

半導体デバイスを作る方法であって、該方法は、

ソース領域と、隣接するドレイン領域とを含む基板を提供することと、

該ソース領域および該ドレイン領域の上に珪化物層を形成することと、

該珪化物層上に第1の相互接続層を形成することであって、該第1の相互接続層は、該ソース領域に接続される第1のランナーと、該ドレイン領域に接続される第2のランナーとを含む、ことと、

該第1の相互接続層の上、かつ該第1の相互接続層に電気的に接続される導電層を形成することと、

該基板上にマスクを配置することであって、該マスクの開口部が該導電層上に整列されられている、ことと、

相互接続を形成するために、該開口部内に導電性材料を蒸着することと

を含む、方法。

(項目2)

上記第1の相互接続層上に第2の相互接続層を形成することをさらに含み、該第2の相互接続層は、第3のランナーおよび第4のランナーを有し、該第3のランナーおよび該第4のランナーは、互いに対して平行であり、かつ上記第1のランナーおよび上記第2のランナーと直交している、上記項目のいずれかに記載の方法。

(項目3)

上記基板にわたって延在するストライプのように、上記ソース領域を形成することと、

該基板にわたって延在し、かつ該ソース領域に対して平行であるストライプのように、上記ドレイン領域を形成することと

さらに含む、上記項目のいずれかに記載の方法。

(項目4)

上記第1のランナーおよび上記第2のランナーは、長方形、十字の形状(+)、L形(L)、またはT形(T)である、上記項目のいずれかに記載の方法。

(項目5)

半導体デバイスを作る方法であって、該方法は、

基板を提供することと、

該基板上に珪化物層を有するトランジスターを形成することと、

該トランジスターの上、かつ該トランジスターに接続される第1の相互接続層を形成することと、

該第1の相互接続層の上、かつ該第1の相互接続層に接続される導電層を形成することと、

該基板上にマスクを配置することであって、該マスクの開口部が該導電層上に整列されられている、ことと、

相互接続を形成するために、該開口部内に導電性材料を蒸着することと

を含む、方法。

(項目6)

ソース領域と、隣接するドレイン領域とを有する上記トランジスターを形成することと、

該ソース領域および該ドレイン領域の上に上記珪化物層を形成することと

をさらに含む、上記項目のいずれかに記載の方法。

(項目7)

互いに対して平行である第1のランナーおよび第2のランナーを有する上記第1の相互接続層を形成することをさらに含む、上記項目のいずれかに記載の方法。

(項目8)

上記第1の相互接続層上に第2の相互接続層を形成することをさらに含み、該第2の相互接続層は、第3のランナーおよび第4のランナーを有し、該第3のランナーおよび該第4のランナーは、互いに対して平行であり、かつ上記第1のランナーおよび上記第2のランナーと直交している、上記項目のいずれかに記載の方法。

(項目9)

上記基板にわたって延在するストライプのように、上記ソース領域を形成することと、

該基板にわたって延在し、かつ該ソース領域に対して平行であるストライプのように、上記ドレイン領域を形成することと

さらに含む、上記項目のいずれかに記載の方法。

(項目10)

上記第1の相互接続層は、長方形、十字の形状(+)、L形(L)、またはT形(T)である、上記項目のいずれかに記載の方法。

(項目11)

半導体デバイスであって、該半導体デバイスは、

ソース領域と、隣接するドレイン領域とを含む基板と、

該ソース領域および該ドレイン領域の上に配置されている珪化物層と、

該珪化物層上に形成されている第1の相互接続層であって、該第1の相互接続層は、該ソース領域に接続される第1のランナーと、該ドレイン領域に接続される第2のランナーとを含む、第1の相互接続層と、

該第1の相互接続層上に形成され、かつ該第1の相互接続層に電気的に接続される導電層と、

該導電層に電気的に接続される相互接続であって、該相互接続は、マスク開口部の体積によって決定される導電性材料の体積を有する、相互接続と

を含む、半導体デバイス。

(項目12)

上記第1のランナーおよび上記第2のランナーは、互いに対して平行であり、上記ソース領域および上記ドレイン領域と直交している、上記項目のいずれかに記載の半導体デバイス。

(項目13)

第2の相互接続層が、上記第1の相互接続層上に形成され、該第2の相互接続層は、第3のランナーおよび第4のランナーを有し、該第3のランナーおよび該第4のランナーは、互いに対して平行であり、かつ上記第1のランナーおよび上記第2のランナーと直交している、上記項目のいずれかに記載の半導体デバイス。

(項目14)

上記ソース領域は、上記基板にわたって延在するストライプのように形成され、

上記ドレイン領域は、該基板にわたって延在し、かつ該ソース領域に対して平行であるストライプのように形成される、上記項目のいずれかに記載の半導体デバイス。

(項目15)

上記第1のランナーおよび上記第2のランナーは、長方形、十字の形状(+)、L形(L)、またはT形(T)である、上記項目のいずれかに記載の半導体デバイス。

(項目1a)

半導体デバイスを作る方法であって、該方法は、

基板を提供することと、

該基板の第1の表面上にソース領域を形成することと、

該ソース領域に隣接して、該基板の該第1の表面上にドレイン領域を形成することと、

該ソース領域および該ドレイン領域の上に珪化物層を形成することと、

該珪化物層上に第1の相互接続層を形成することであって、該第1の相互接続層は、該ソース領域に接続される第1のランナーと、該ドレイン領域に接続される第2のランナーとを含む、ことと、

該第1の相互接続層上に第2の相互接続層を形成することであって、該第2の相互接続層は、該第1のランナーに接続される第3のランナーと、該第2のランナーに接続される第4のランナーとを含む、ことと、

該第2の相互接続層の上、かつ該第2の相互接続層に電気的に接続されるアンダーバンプ金属化(UBM)を形成することと、

マスクの開口部が該UBM上に整列されるように、該基板上に該マスクを配置することと、

該開口部内に導電性バンプ材料を蒸着することと、

該マスクを除去することと、

バンプを形成するために、該導電性バンプ材料をリフローすることと

を含む、方法。

(項目2a)

互いに対して平行であり、かつ上記ソース領域およびドレイン領域と直交している上記第1のランナーおよび上記第2のランナーを形成することをさらに含む、上記項目のいずれかに記載の方法。

(項目3a)

互いに対して平行であり、かつ上記第1のランナーおよび上記第2のランナーと直交している上記第3のランナーおよび上記第4のランナーを形成することをさらに含む、上記項目のいずれかに記載の方法。

(項目4a)

上記基板の上記第1の表面にわたって延在するストライプのように、上記ソース領域を形成することと、

該基板の上記第1の表面にわたって延在し、かつ該ソース領域に対して平行であるストライプのように、上記ドレイン領域を形成することと

さらに含む、上記項目のいずれかに記載の方法。

(項目5a)

電流が、最小の抵抗を有する電気的パスに沿って上記ソース領域および上記ドレイン領域の各々へ流れるように、該ソース領域および該ドレイン領域を複数の電気的パスに接続することをさらに含む、上記項目のいずれかに記載の方法。

(項目6a)

上記第1のランナー、上記第2のランナー、上記第3のランナー、および上記第4のランナーは、長方形、十字の形状(+)、L形(L)、またはT形(T)である、上記項目のいずれかに記載の方法。

(項目7a)

互いに対して平行であり、かつ上記ソース領域およびドレイン領域と直交している上記第1のランナーおよび上記第2のランナーを形成することをさらに含む、上記項目のいずれかに記載の方法。

(項目8a)

電流が、最小の抵抗を有する電気的パスに沿って上記ソース領域および上記ドレイン領域の各々へ流れるように、該ソース領域および該ドレイン領域を複数の電気的パスに接続することをさらに含む、上記項目のいずれかに記載の方法。

(項目9a)

電流が、最小の抵抗を有する電気的パスに沿って流れるように、上記トランジスターを複数の電気的パスに接続することをさらに含む、上記項目のいずれかに記載の方法。

(項目10a)

電流が、最小の抵抗を有する電気的パスに沿って上記ソース領域および上記ドレイン領域の各々へ流れるように、該ソース領域および該ドレイン領域は、複数の電気的パスに接続される、上記項目のいずれかに記載の半導体デバイス。

【0017】

(摘要)

半導体デバイスは、基板を有し、基板は、基板上に形成されるソース領域およびドレイン領域を有する。珪化物層が、ソース領域およびドレイン領域の上に配置されている。第1の相互接続層が、珪化物層上に形成されており、ソース領域に接続される第1のランナーと、ドレイン領域に接続される第2のランナーとを含む。第2の相互接続層が、第1の相互接続層上に形成されており、第1のランナーに接続される第3のランナーと、第2のランナーに接続される第4のランナーとを含む。アンダーバンプ金属化(UBM)が、第2の相互接続層上に形成されており、かつ第2の相互接続層に電気的に接続される。マスクの開口部がUBM上に整列されるように、マスクが、基板上に配置される。導電性バンプ材料が、マスクの開口部内に蒸着される。マスクが除去され、導電性バンプ材料が、バンプを形成するためにリフローされる。

【図面の簡単な説明】

【0018】

【図1a】図1aは、従来のUBMはんだバンプ構造を例示する。

【図1b】図1bは、従来のUBMはんだバンプ構造を例示する。

【図2】図2は、その表面に取り付けられた異なるタイプのパッケージを有するPCBを例示する。

【図3a】図3aは、PCBに取り付けられた代表的な半導体パッケージのさらなる詳細を例示する。

【図3b】図3bは、PCBに取り付けられた代表的な半導体パッケージのさらなる詳細を例示する。

【図3c】図3cは、PCBに取り付けられた代表的な半導体パッケージのさらなる詳細を例示する。

【図4a】図4aは、珪化物層および相互接続構造を有するパワーMOSFETを形成する方法を例示する。

【図4b】図4bは、珪化物層および相互接続構造を有するパワーMOSFETを形成する方法を例示する。

【図4c】図4cは、珪化物層および相互接続構造を有するパワーMOSFETを形成する方法を例示する。

【図4d】図4dは、珪化物層および相互接続構造を有するパワーMOSFETを形成する方法を例示する。

【図4e】図4eは、珪化物層および相互接続構造を有するパワーMOSFETを形成する方法を例示する。

【図4f】図4fは、珪化物層および相互接続構造を有するパワーMOSFETを形成する方法を例示する。

【図4g】図4gは、珪化物層および相互接続構造を有するパワーMOSFETを形成する方法を例示する。

【図4h】図4hは、珪化物層および相互接続構造を有するパワーMOSFETを形成する方法を例示する。

【図4i】図4iは、珪化物層および相互接続構造を有するパワーMOSFETを形成する方法を例示する。

【図4j】図4jは、珪化物層および相互接続構造を有するパワーMOSFETを形成する方法を例示する。

【図4k】図4kは、珪化物層および相互接続構造を有するパワーMOSFETを形成する方法を例示する。

【図4l】図4lは、珪化物層および相互接続構造を有するパワーMOSFETを形成する方法を例示する。

【図4m】図4mは、珪化物層および相互接続構造を有するパワーMOSFETを形成する方法を例示する。

【図4n】図4nは、珪化物層および相互接続構造を有するパワーMOSFETを形成する方法を例示する。

【図4o】図4oは、珪化物層および相互接続構造を有するパワーMOSFETを形成する方法を例示する。

【図4p】図4pは、珪化物層および相互接続構造を有するパワーMOSFETを形成する方法を例示する。

【図4q】図4qは、珪化物層および相互接続構造を有するパワーMOSFETを形成する方法を例示する。

【図4r】図4rは、珪化物層および相互接続構造を有するパワーMOSFETを形成する方法を例示する。

【図4s】図4sは、珪化物層および相互接続構造を有するパワーMOSFETを形成する方法を例示する。

【図4t】図4tは、珪化物層および相互接続構造を有するパワーMOSFETを形成する方法を例示する。

【図5a】図5aは、パワーMOSFETのさらなる詳細を例示する。

【図5b】図5bは、パワーMOSFETのさらなる詳細を例示する。

【図5c】図5cは、パワーMOSFETのさらなる詳細を例示する。

【図6a】図6aは、短いUBM構造を形成する方法を例示する。

【図6b】図6bは、短いUBM構造を形成する方法を例示する。

【図6c】図6cは、短いUBM構造を形成する方法を例示する。

【図6d】図6dは、短いUBM構造を形成する方法を例示する。

【図6e】図6eは、短いUBM構造を形成する方法を例示する。

【図6f】図6fは、短いUBM構造を形成する方法を例示する。

【図6g】図6gは、短いUBM構造を形成する方法を例示する。

【図6h】図6hは、短いUBM構造を形成する方法を例示する。

【図6i】図6iは、短いUBM構造を形成する方法を例示する。

【図7a】図7aは、相互接続構造を有するパワーMOSFETのさらなる詳細を例示する。

【図7b】図7bは、相互接続構造を有するパワーMOSFETのさらなる詳細を例示する。

【図7c】図7cは、相互接続構造を有するパワーMOSFETのさらなる詳細を例示する。

【図8】図8は、パワーMOSFETの相互接続構造のさらなる詳細を例示する。

【図9】図9は、相互接続構造を有するパワーMOSFETのさらなる詳細を例示する。

【図10a】図10aは、アンダーフィル材料を有しない基板に取り付けられた短いUBM構造を有するパワーMOSFETを例示する。

【図10b】図10bは、アンダーフィル材料を有しない基板に取り付けられた短いUBM構造を有するパワーMOSFETを例示する。

【発明を実施するための形態】

【0019】

(図面の詳細な説明)

本発明は、図面を参照して以下の説明における1つ以上の実施形態において説明される。同様の数字は、同じまたは類似な構成要素を表す。本発明が、本発明の目標を達成するための最もよいモードに関連して説明されるが、当業者によって、本発明が、添付した請求範囲によって規定されるような本発明の精神および範囲内に含まれ得るような代替物、変更、および同等物、並びに以下の開示および図面によって支持されるようなそれらの同等物をカバーするように意図されることが認識される。

【0020】

半導体デバイスは、概して、2つの複合の製造プロセス、すなわち、フロントエンド製造およびバックエンド製造を用いて製造される。フロントエンド製造は、半導体ウェーハの表面上に複数のダイの形成を必要とする。ウェーハ上の各ダイは、機能的電気回路を形成するために、電気的に接続されている能動電気部品および受動電気部品を含む。能動電気部品、例えば、トランジスターおよびダイオードは、電流の流れを制御する能力を有する。受動電気部品、例えば、キャパシター、インダクター、抵抗器、および変圧器は、電流の機能を行うために必要な電圧と電流との間の関係を生成する。

【0021】

受動部品および能動部品は、ドーピング、蒸着、フォトリソグラフィー、エッチング、および平坦化を含む一連のプロセスによって半導体ウェーハの表面上に形成される。ドーピングは、イオン注入または熱拡散のような技術によって半導体材料内に不純物を導入する。ドーピングプロセスは、能動デバイスにおける半導体材料の導電率を変更させ、半導体材料を絶縁体、導体に変換させ、または電場またはベース電流に応じて半導体材料の導電率を動的に変化させる。トランジスターは、電場またはベース電流を印加すると、トランジスターが電流の流れを促進、または制限することを可能にするのに必要であるように配列される、ドーピングのタイプおよび濃度が変化する領域を含む。

【0022】

能動部品および受動部品が、異なる電気性質を有する材料の層によって形成され得る。層は、蒸着される材料のタイプによって部分的に決定されるさまざまな蒸着技術によって形成され得る。例えば、薄膜蒸着は、化学蒸着法(CVD)、物理蒸着法(PVD)、電解めっき、および無電解めっきを含み得る。各層は、概して、能動部品、受動部品、または部品の間の電気的接続の一部分を形成するようにパターンをつけられる。

【0023】

層は、パターンをつけられるべきである層の上に感光性材料、例えば、フォトレジストの蒸着を含むフォトリソグラフィーを用いてパターンをつけられ得る。パターンは、光照射を用いて、フォトマスクからフォトレジストに転送される。光に露出されたフォトレジストパターンの一部分が、溶剤を用いて除去され、パターンをつけられるように、下にある層の一部分を露出させる。フォトレジストの残りが除去され、パターンをつけられた層を残しておく。代替的には、いくつかのタイプの材料は、無電解めっきおよび電解めっきのような技術を用いる事前の蒸着/エッチプロセスによって形成されたエリアまたは隙間内に材料を直接に蒸着することによってパターンをつけられる。

【0024】

存在するパターンの上に薄膜の材料を蒸着することは、下にあるパターンを誇張し、不均一なフラット表面を生成し得る。均一なフラット表面は、より小さく、より低密度に詰められた能動部品および受動部品を生成することを要求される。平坦化は、ウェーハの表面から材料を除去し、かつ均一なフラット表面を生成するために使用され得る。平坦化は、磨きパッドを用いて、ウェーハの表面を磨くことを必要とする。研磨材料および腐食性化学薬品が、磨く際にウェーハの表面に加えられる。研磨剤の機械的作用と、化学薬品の腐食性作用との組み合わせは、不規則な形態を除去し、均一なフラット表面をもたらす。

【0025】

バックエンド製造は、完成したウェーハを個々のダイに切断し、または単一化し、次に構造的支持および環境的分離のためにダイをパッケージすることを指す。ダイを単一化するために、ウェーハは、ソーストリートまたはスクライブと呼ばれる、ウェーハの機能しない領域に沿って刻み目をつけられ、そして割られる。ウェーハは、レーザー切断ツールまたはソースクライブを用いて単一化される。単一化の後に、個々のダイは、他のシステム部品との相互接続のためのピンまたは接触パッドを含むパッケージ基板に取り付けられる。次に、半導体ダイの上に形成された接触パッドが、パッケージ内の接触パッドに接続される。電気的接続は、はんだバンプ、スタッドバンプ、導電性ペーストまたはワイヤボンドを用いて作られ得る。カプセルの材料または他の成形する材料は、物理的支持および電気的分離を提供するためにパッケージの上に蒸着される。次に、完成したパッケージは、電気的システム内に挿入され、半導体デバイスの機能が、他のシステム部品に利用可能にされる。

【0026】

図2は、チップキャリア基板またはPCB52を有する電子デバイス50を例示し、チップキャリア基板またはPCB52は、その表面上に取り付けられた複数の半導体パッケージを有する。電子デバイス50は、用途に依存して、1つのタイプの半導体パッケージ、または複数のタイプの半導体パッケージを有し得る。異なるタイプの半導体パッケージが、例示の目的のために、図2に示される。

【0027】

電子デバイス50は、1つ以上の電気的機能を行うために、半導体パッケージを使用するスタンドアロンシステムであり得る。代替的には、電子デバイス50は、より大きなシステムのサブ部品であり得る。例えば、電子デバイス50は、セルラー電話、パーソナルデジタルアシスタント(PDA)、デジタルビデオカメラ(DVC)、または他の電子通信デバイスの一部分であり得る。代替的には、電子デバイス50は、グラフィックカード、ネットワークインターフェースカード、またはコンピュータ内に挿入され得る他の信号処理カードであり得る。半導体パッケージは、マイクロプロセッサ、メモリ、特定用途の集積回路(ASIC)、論理回路、アナログ回路、RF回路、離散型デバイス、または他の半導体ダイまたは電子部品を含み得る。小型化および重量軽減は、市場によって受け入れられるために、これらの製品にとって必須である。半導体デバイス間の距離は、より高密度を達成するために減少されなければならない。

【0028】

図2において、PCB52は、PCB上に取り付けられる半導体パッケージの構造的支持および電気的相互接続のための一般的基板を提供する。導電性信号トレース54は、蒸着、電解めっき、無電解めっき、スクリーンプリント、または他の適切な金属蒸着プロセスを用いてPCB52の層の表面上、または層内に形成される。信号トレース54は、半導体パッケージ、取り付けられた部品、および他の外部システム部品の各々の間に、電気的連絡を提供する。トレース54はまた、半導体パッケージの各々への電力接続およびグラウンド接続を提供する。

【0029】

いくつかの実施形態において、半導体デバイスは、2つのパッケージングレベルを有する。第1のレベルのパッケージングは、中間キャリアに半導体ダイを機械的、かつ電気的に張りつけるための技術である。第2のレベルのパッケージングは、PCBに中間キャリアを機械的、かつ電気的に張りつけることを含む。他の実施形態において、半導体デバイスは、ダイがPCBに直接に機械的、かつ電気的に取り付けられる第1のレベルのパッケージングのみを有し得る。

【0030】

例示の目的のために、ワイヤボンド56およびフリップチップ58を含むいくつかのタイプの第1のレベルのパッケージングが、PCB52上に示される。さらに、ボールグリッドアレイ(BGA)60、バンプチップキャリア(BCC)62、デュアルインラインパッケージ(DIP)64、ランドグリッドアレイ(LGA)66、マルチチップモジュール(MCM)68、カッドフラット無鉛パッケージ(QFN)70、およびカッドフラットパッケージ72を含むいくつかの第2のレベルのパッケージングが、PCB52上に取り付けられる。システムの要求に依存して、第1および第2のレベルのパッケージング型の任意の組み合わせを用いて構成される半導体パッケージの任意の組み合わせだけではなく、他の電子部品もPCB52に接続され得る。いくつかの実施形態において、電子デバイス50は、単一の張りつけられた半導体パッケージを含み、その一方で、他の実施形態は、複数の相互接続されたパッケージを必要とする。単一の基板にわたって1つ以上の半導体パッケージを組み合わせることによって、製造者は、電子デバイスおよびシステムに事前に作られた部品を組み込み得る。半導体パッケージが、高性能の機能を含むので、電子デバイスは、より安価な部品および流線型製造プロセスを用いて製造され得る。結果のデバイスは、故障がより少なく、製造もより安価であり、結果として消費者にとってより低いコストをもたらす。

【0031】

図3a〜3cは、代表的な半導体パッケージを示す。図3aは、PCB52上に取り付けられたDIP64のさらなる詳細を例示する。半導体ダイ74は、能動領域を含み、能動領域は、ダイ内に形成され、かつダイの電気的設計に従って電気的に相互接続される能動デバイス、受動デバイス、導電層、および誘電層として実装されるアナログまたはデジタル回路を含む。例えば、回路は、1つ以上のトランジスター、ダイオード、インダクター、キャパシター、レジスター、および半導体ダイ74の能動領域内に形成された他の回路要素を含み得る。接触パッド76は、導電性材料、例えば、Al、Cu、tin(Sn)、ニッケル(Ni)、金(Au)、または銀(Ag)の1つ以上の層であり、半導体ダイ74内に形成された回路要素に電気的に接続される。DIP64の組立の間に、半導体ダイ74は、金−シリコン共晶層、または熱エポキシまたはエポキシ樹脂等のような接着材料を用いて、中間キャリア78に取り付けられる。パッケージ本体は、絶縁パッケージング材料、例えば、ポリマーまたはセラミックを含む。導体リード80およびボンドワイヤ82は、半導体ダイ74とPCB52との間に電気的相互接続を提供する。カプセルの材料84は、水分および粒子がパッケージに浸入し、ダイ74またはボンドワイヤ82を汚染することを防止することによる環境的保護のために、パッケージの上に蒸着される。

【0032】

図3bは、PCB52上に取り付けられたBCC62のさらなる詳細を例示する。半導体ダイ88は、アンダーフィルまたはエポキシ樹脂の接着材料92を用いてキャリア90上に取り付けられる。ボンドワイヤ94は、接触パッド96と98との間の第1のレベルのパッケージング相互接続を提供する。成形する化合物またはカプセルの材料100は、デバイスに対して物理的支持および電気的分離を提供するために、半導体ダイ88およびボンドワイヤ94上に蒸着される。接触パッド102は、酸化を防止するために、適切な金属蒸着プロセス、例えば、電解めっきまたは無電解めっきを用いてPCB52の表面上に形成される。接触パッド102は、PCB52の1つ以上の導電性信号トレース54に電気的に接続される。バンプ104は、BCC62の接触パッド98と、PCB52の接触パッド102との間に形成される。

【0033】

図3cにおいて、半導体ダイ58は、フリップチップ型の第1のレベルのパッケージングを有する中間キャリア106にうつ伏せ状態で取り付けられている。半導体ダイ58の能動領域108は、ダイの電気的設計に従って形成される能動デバイス、受動デバイス、導電層、および誘電層として実装されるアナログまたはデジタル回路を含む。例えば、回路は、1つ以上のトランジスター、ダイオード、インダクター、キャパシター、レジスター、および能動領域108内の他の回路要素を含み得る。半導体ダイ58は、バンプ110を介してキャリア106に電気的、かつ機械的に接続される。

【0034】

BGA60は、バンプ112を用いて、BGA型の第2のレベルのパッケージングを有するPCB52に電気的、かつ機械的に接続される。半導体ダイ58は、バンプ110、信号ライン114、およびバンプ112を介してPCB52の導電性信号トレース54に電気的に接続される。成形する化合物またはカプセルの材料116は、デバイスに対して物理的支持および電気的分離を提供するために、半導体ダイ58およびキャリア106の上に蒸着される。フリップチップ半導体デバイスは、信号伝搬距離を減少させ、キャパシタンスを低下させ、全体の回路性能を向上させるために、半導体ダイ58上の能動デバイスからPCB52上の導電性トレースまでに短い電気的伝導パスを提供する。別の実施形態において、半導体ダイ58は、中間キャリア106を有しないフリップチップ型の第1のレベルのパッケージングを用いてPCB52に直接に機械的、かつ電気的に接続され得る。

【0035】

図4a〜4tは、図2および3a〜3cに関連して、密集したトランジスターの上に形成された相互接続構造および珪化物層を有し、さらにロープロファイルのバンプを含むパワーMOSFETを形成するプロセスにおけるステップを例示する。図4aは、構造的支持のためのベース基板材料122、例えば、シリコン、ゲルマニウム、ガリウムヒ素、リン化インジウム、または炭化珪素を有する半導体ウェーハ120を示す。

【0036】

図4bは、MOSFETセル124を形成するための、ベース基板材料122から作られた基板または半導体ウェーハ120の一部分の断面図を示す。半導体ウェーハ120は、上部表面130と、上部表面130の反対側にある底部表面132とを含む。

【0037】

MOSFETセル124は、nチャンネルデバイス(N−MOS)またはpチャンネルデバイス(P−MOS)であり得、「p」が、正のキャリアタイプ(正孔)を示し、「n」が、負のキャリアタイプ(電子)を示す。MOSFETセル124の本実施形態が、p型基板120上に形成されるN−MOSデバイスに関して説明されるが、反対のタイプの半導体材料は、P−MOSデバイスを形成するために使用され得る。例えば、n型基板は、n型井戸領域を形成するために、最初に、n型半導体材料、例えば、リン、アンチモン、または砒素の不純物を用いてドープされ得る。p型基板120を含む本発明の実施形態はさらに、pマイナス型基板の最上部上に蒸着され得る。

【0038】

図4cにおいて、絶縁層または誘電層134は、ゲート酸化層として、基板120の表面130上に形成される。絶縁層134は、二酸化珪素(SiO2)、窒化珪素(Si3N4)、酸窒化珪素(SiON)、五酸化タンタル(Ta2O5)、酸化アルミニウム(Al2O3)、ポリイミド、BCB、ポリベンゾオキサゾール(PBO)、または他の適切な誘電材料の1つ以上の層を含む。絶縁層134は、PVD、CVD、スクリーンプリント、スピンコーティング、スプレーコーティング、焼結、または熱酸化を用いて形成される。

【0039】

図4dにおいて、ポリシリコン138が、絶縁層134上に形成される。図4eにおいて、フォトレジスト層140が、ポリシリコン層138上に形成される。フォトレジスト層に開口部142を形成し、かつポリシリコン層138の一部分を露出させるために、フォトレジスト層140の一部分が、エッチングプロセスによって除去される。エッチングプロセスにおいて除去されていないフォトレジスト140の残り部分は、MOSFETセル124内の、ゲートバターンに対応する。

【0040】

図4fにおいて、開口部142のフットプリント内、かつフォトレジスト140の外側に設置されているポリシリコン138の一部分が、エッチングプロセスによって除去される。ポリシリコン層138の残り部分は、後に形成されるMOSFETセル124内のトランジスターのためのゲートとして役に立つ。

【0041】

図4gにおいて、フォトレジスト層140の残りは、ポリシリコン層138のエッチングの後に除去される。図4gは、低濃度ドープされたドレイン(LDD)領域144および146を形成するために、基板120が、n型半導体材料、例えば、砒素を用いてドープされることをさらに示す。n型ドーパントが、イオン注入によって蒸着される。イオン注入によって導入されるドーパントの量は、LDD領域144および146が、nマイナスLDDおよびn型領域を含むように変化し得る。

【0042】

図4hにおいて、絶縁層150が、ポリシリコン層138の周り、かつ絶縁層134の上に形成される。絶縁層150はまた、LDD領域144および146の一部分の上に延在する。絶縁層150は、SiO2、Si3N4、SiON、Ta2O5、Al2O3、ポリイミド、BCB、PBO、または他の適切な誘電材料の1つ以上の層を含む。絶縁層150は、PVD、CVD、スクリーンプリント、スピンコーティング、スプレーコーティング、焼結、または熱酸化を用いて形成される。LDD領域144および146上の絶縁層134の一部分が、マスクとしてポリシリコン層138および絶縁層150を用いるエッチングプロセスによって除去される。絶縁層134の残り部分は、ポリシリコン層138を超えて、LDD領域144および146の上、かつ絶縁層150の下に延在する。絶縁層150はまた、後のドレインおよびソースイオン注入をマスクするための側壁スペーサーとして動作する。絶縁層150の配置は、開口部142によって露出される絶縁層134のエリアを減少させ、それによって、開口部142のエリアより小さいエリアを有する開口部152を形成させる。

【0043】

図4iにおいて、ポリシリコン層138および絶縁層150によって形成されたマスクの外側(すなわち、開口部152内)のLDD領域144および146の一部分は、ソース領域160およびドレイン領域170を形成するために、高濃度ドープされる。図4iが、単一のソース領域160および単一のドレイン領域170を示すが、MOSFETセル124は、後の図に示されるような複数のソース領域160およびドレイン領域170を含む。ソース領域160およびドレイン領域170は、それぞれ、事前に形成されたLDD144および146より深くウェーハ120内に延在する。従って、LDD領域144および146のエリアが、ソース領域160およびドレイン領域170の形成によって減少され、その結果、LDD領域144および146は、絶縁層150の下に設置される、減少されたエリアを占め、開口部152内のエリアを占めない。1つの実施形態において、LDD領域144および146を形成するために使用される、変化する注入の量は、nマイナス型LDD144およびn型領域146をもたらす。

【0044】

図4iは、ソース領域160が領域162、164および166を含むことをさらに示す。領域162、164および166が、さまざまな構成に従ってドープされ得る。第1の構成において、領域162が、nプラス型領域としてドープされ、領域164が、pプラス型領域としてドープされ、領域166が、n型領域としてドープされる。第2の構成において、領域164が、pプラス型領域としてドープされ、領域162および166が、pプラス型領域164の両側に隣接するnプラス型領域としてドープされる。さらに、ソース領域160の領域162および164は、LDD144を含み得る。これに反して、LDD144が、ソース領域160に完全にない場合もある。また図4iに形成されたドレイン領域170が、nプラス型領域としてドープされる。ドレイン領域170が、n型領域146の間に配置されている。

【0045】

図4jにおいて、珪化物層174が、ソース領域160およびドレイン領域170の上、並びにパシベーション層134の開口部152内の薄層として形成される。珪化物層174は、WSi2、TiSi2、MoSi2、TaSi2、または他の適切な珪化物を含み、PVD、CVD、共蒸着、スパッタリング、または他の適切なプロセスを使用することによって形成される。珪化物層174が、PVDによって形成されるが、珪化物層174は、半導体ウェーハ120上に耐熱性金属を蒸着させ、耐熱性金属が半導体ウェーハと接触する場所に珪化物層が形成されるように半導体ウェーハおよび耐熱性金属を加熱することによって自己整列される。珪化物層の一部分を形成するために、反応しない余分の耐熱性金属が除去される。珪化物層174が、ソース領域160の上部表面、およびドレイン領域170の上部表面に形成される。1つの実施形態において、珪化物層174は、100〜3000オングストロームの範囲の厚さを有する。珪化物層174は、ソース領域160およびドレイン領域170の上部表面にわたる金属導体として役に立つ。珪化物層174の存在は、MOSFETセル124の全体コストを減少させ、後に形成されるバンプから、ソース領域160およびドレイン領域170までの低抵抗電気的パスの一部分をそれぞれに形成することによって電流伝導を増大させる金属化パスとして役に立つ。

【0046】

図4kにおいて、絶縁層または中間層誘電体(ILD)180が、半導体ウェーハ120の上、すなわち、ポリシリコン層138、絶縁層150、および珪化物層174の上に形成されている。ILD180は、SiO2、Si3N4、SiON、Ta2O5、Al2O3、ポリイミド、BCB、PBO、または他の適切な誘電材料の1つ以上の層を含む。ILD180は、PVD、CVD、スクリーンプリント、スピンコーティング、スプレーコーティング、焼結、または熱酸化を用いて形成される。ILD180の一部分は、ビア182を形成するために、エッチングプロセスによって除去される。ビア182は、ILD180の上部表面から、ILDを通って、珪化物層174まで延在し、ソース領域160およびドレイン領域170への後の電気的接続を提供する。電気的接続はまた、ポリシリコン層138における、MOSFETセル124のためのゲート電極によって作られ、電気的接続は、ビア182による接続を含み得る。導電性材料184は、導電性ビアを形成するように、ビア182内、かつ珪化物層174の露出された部分上に形成される。導電性材料184は、タングステン(W)を含み、Al、Cu、Sn、Ni、Au、Ag、チタン(Ti)、ポリシリコン、または他の適切な電気伝導材料も含み得、PVD、CVD、電解めっき、無電解めっき、または他の適切な金属蒸着プロセスを用いて形成される。

【0047】

図4lは、図4kからのMOSFETセル124の上面図を示す。MOSFETセル124のソース領域160およびドレイン領域170は、基板120にわたって延在する交互配置ストライプのように、基板120に形成されている。ソース領域160およびドレイン領域170は、固定の距離の間隔で交互に空けられ、ポリシリコンゲート138によって分離される。

【0048】

導電性材料184が、ソース領域160上の導電性ビア186と、ドレイン領域170上の導電性ビア188とを形成するために、ビア182上に蒸着される。導電性ビア186および188は、ソース領域160およびドレイン領域170から、それぞれ、第1の相互接続層194への電気的接続を提供する。

【0049】

第1の相互接続層194は、ILD180の上、導電柱186および188の上、並びにソース領域160およびドレイン領域170の上に形成される。第1の相互接続層194は、ソースランナーまたは導電層196と、ドレインランナーまたは導電層198とを含む。ソースランナー196およびドレインランナー198は、1つ以上の層であり得、Cu、Sn、Ni、NiV、Au、Ag、Alまたは他の適切な導電性材料であり得る。ソースランナー196およびドレインランナー198は、電解めっき、無電解めっき、スパッタリング、PVD、CVD、または他の適切な金属蒸着プロセスを用いてパターンをつけられ、蒸着される。図4lに示されるソースランナー196とドレインランナー198とは、長方形、かつ実質的に等しい幅であるが、ランナーは、任意の形状であり得る。例として、ソースランナー196とドレインランナー198とは、等しくない幅であり得、ランナーは、変化する狭い部分およびより広い部分、並びに丸い角を有し得る。1つの実施形態において、第1の、ソースランナー196およびドレインランナー198は、従来のデバイスに対して短く、かつ広い寸法を含む。ソースランナー196およびドレインランナー198は、交互に配置され、固定の距離で交互に間隔を空けられ、互いに対して実質的に平行に配向される。ソースランナー196およびドレインランナー198は、ソース領域160およびドレイン領域170に対して、実質的に垂直または直交して配向される。代替的には、他の垂直でない向き(例えば、角度のある向きまたは平行の向き)が使用され得る。ソースランナー196およびドレインランナー198が配向されている反復する交互配置の、または交互に生じる間隔は、半導体ウェーハ120の表面にわたって分布されたユニット構造を生成する。

【0050】

ソースランナー196およびドレインランナー198は、それぞれ、導電性ビア186および188を介して、ソース領域160およびドレイン領域170に電気的に接続される。図4lは、2つのビア186が、ソース領域とソースランナーとが重なる場所において、ソース領域160とソースランナー196との間に電気的接続を形成するために使用されることを示す。同様に、図4lは、2つのビア188が、ドレイン領域とドレインランナーとが重なる場所において、ドレイン領域170とドレインランナー198との間に電気的接続を形成するために使用されることをさらに示す。代替的には、1つの導電性ビア、または3つ以上の導電性ビアは、それぞれ、ソース領域160およびドレイン領域170をソースランナー196およびドレインランナー198に接続するために使用され得る。

【0051】

図4kから続く図4mにおいて、MOSFETセル124およびソースランナー196の断面図を示す。図4lから、ソースランナー196は、導電性ビア186上に形成され、かつ導電性ビア186に電気的に接続される。

【0052】

図4nにおいて、絶縁層またはILD200が、第1の相互接続層194およびILD180の上に形成される。ILD200は、SiO2、Si3N4、SiON、Ta2O5、Al2O3、ポリイミド、BCB、PBO、または他の適切な誘電材料の1つ以上の層を含む。ILD200は、PVD、CVD、スクリーンプリント、スピンコーティング、スプレーコーティング、焼結、または熱酸化を用いて形成される。ILD200の一部分は、ビア202を形成するために、エッチングプロセスによって除去される。ビア202は、ILD200の上部表面から、ILDを通して、第1の相互接続層194まで延在する。導電性材料204が、導電性ビアを形成するために、ビア202内、かつ第1の相互接続層194の露出された部分の上に形成される。導電性材料204は、Wを含み、Al、Cu、Sn、Ni、Au、Ag、Ti、ポリシリコン、または他の適切な電気伝導材料も含み得、PVD、CVD、電解めっき、無電解めっき、または他の適切な金属蒸着プロセスを用いて形成される。

【0053】

図4oは、図4nからの部分的に形成された半導体デバイスの上面図を示す。ビア202内に形成された導電性材料204は、ソースランナー196上に形成された導電性ビア206と、ドレインランナー198上に形成された導電性ビア208とをもたらす。導電性ビア206および208は、それぞれ、ソースランナー196およびドレインランナー198から第2の相互接続層214への電気的接続を提供する。

【0054】

第2の相互接続層214は、ILD200上、導電柱206および208の上、並びに第1の相互接続層194上に形成される。第2の相互接続層214は、ソースランナーまたは導電層216と、ドレインランナーまたは導電層218とを含む。ソースランナー216およびドレインランナー218は、1つ以上の層であり得、Cu、Sn、Ni、NiV、Au、Ag、Alまたは他の適切な導電性材料であり得る。ソースランナー216およびドレインランナー218は、電解めっき、無電解めっき、スパッタリング、PVD、CVD、または他の適切な金属蒸着プロセスを用いてパターンをつけられ、蒸着される。図4oに示されるソースランナー216とドレインランナー218とは、実質的に等しい幅、かつ長方形であるが、ランナーは、任意の形状であり得る。例として、ソースランナー216とドレインランナー218とは、等しくない幅であり得、ランナーは、変化する細い部分およびより広い部分、並びに丸い角を有し得る。1つの実施形態において、第2の、ソースランナー216およびドレインランナー218は、従来のデバイスに対して短く、かつ広い寸法を含む。ソースランナー216およびドレインランナー218は、交互に配置され、固定の距離で交互に間隔を空けられ、互いに対して実質的に平行に配向される。ソースランナー216およびドレインランナー218は、ソースランナー196およびドレインランナー198に対して、実質的に垂直または直交して配向される。代替的には、他の垂直でない向き(例えば、角度のある向きまたは平行の向き)が使用され得る。ソースランナー216およびドレインランナー218が配向されている反復する交互配置の、または交互に生じる間隔は、ソースランナー196およびドレインランナー198だけではなく、半導体ウェーハ120の表面にもわたって分布されたユニット構造を生成する。

【0055】

ソースランナー216およびドレインランナー218は、それぞれ、導電性ビア206および208を介して、ソースランナー196およびドレインランナー198に電気的に接続される。図4oは、2つのビア206が、ソースランナー196と216が重なる場所において、ソースランナー196とソースランナー216との間に電気的接続を形成するために使用されることを示す。同様に、図4oは、2つのビア208が、ドレインランナーが重なる場所において、ドレインランナー198とドレインランナー218との間に電気的接続を形成するために使用されることをさらに示す。代替的には、1つの導電性ビア、または3つ以上の導電性ビアが、それぞれ、ソース領域160およびドレイン領域170をソースランナー196およびドレインランナー198に接続するために使用され得る。

【0056】

図4nから続く図4pにおいて、MOSFETセル124、並びにソースランナー216およびドレインランナー218の断面図を示す。図4oから、ソースランナー216は、導電性ビア206上に形成され、かつ導電性ビア206に電気的に接続される。

【0057】

図4qにおいて、絶縁層またはILD220が、第2の相互接続層214およびILD200の上に形成される。ILD220は、SiO2、Si3N4、SiON、Ta2O5、Al2O3、ポリイミド、BCB、PBO、または他の適切な誘電材料の1つ以上の層を含む。ILD220は、PVD、CVD、スクリーンプリント、スピンコーティング、スプレーコーティング、焼結、または熱酸化を用いて形成される。ILD220の一部分は、ビア222を形成するために、エッチングプロセスによって除去される。ビア222は、ILD220の上部表面から、ILDを通って、第2の相互接続層214まで延在する。導電性材料224が、導電性ビアを形成するために、ビア222内、かつ第2の相互接続層214の露出された部分の上に形成される。導電性材料224は、Wを含み、アルミニウムAl、Cu、Sn、Ni、Au、Ag、Ti、ポリシリコン、または他の適切な電気伝導材料も含み得、PVD、CVD、スッパタリング、電解めっき、無電解めっき、または他の適切な金属蒸着プロセスを用いて形成される。

【0058】

図4rは、図4qからの部分的に形成された半導体デバイスの上面図を示す。ビア222内に形成された導電性材料224は、ソースランナー216上に形成された導電性ビア226をもたらす。導電性ビア226は、それぞれ、ソースランナー216から第3の相互接続レベル234への電気的接続を提供する。ソースパッド236は、ILD220上、導電柱226上、および第2の相互接続層214上の第3の相互接続レベル234に形成される。ソースパッド236は、Cu、Sn、Ni、NiV、Au、Ag、Alまたは他の適切な導電性材料の1つ以上の層であり得る。ソースパッド236は、電解めっき、無電解めっき、スパッタリング、PVD、CVD、または他の適切な金属蒸着プロセスを用いてパターンをつけられ、蒸着される。

【0059】

ソースパッド236は、ソース領域160とMOSFETセル124に対する外部のデバイスとの間に電気的接続を提供する、後に形成されるソースバンプに接続されるように構成されている。同様に、ビア222内、かつドレインランナー218上に形成された導電性材料224は、ドレインランナー218からドレインパッドへの電気的接続を提供する。ドレインパッドは、ドレイン領域170からMOSFETセル124に対する外部のデバイスへの電気的接続を提供する、後に形成されるドレインバンプに接続されるように構成されている。

【0060】

図4qから続く図4sは、MOSFETセル124およびソースパッド236の断面図を示す。図4rから、ソースパッド236は、導電性ビア226上に形成され、かつ導電性ビア226に電気的に接続される。電気伝導バンプ材料は、図6a〜6iにさらに詳細に説明されるように、ソースバンプまたは相互接続240を形成するために、ソースパッド236上に蒸着される。ソースバンプ240は、ソース領域160からMOSFETセル124に対する外部のデバイスへの電気的接続を提供する。ソースバンプ240は、ソースパッド236上に形成され得る1つのタイプの相互接続構造を表す。ソースバンプまたは相互接続240はまた、ボンドワイヤ、導電性ペースト、スタッドバンプ、マイクロバンプ、または他の電気的相互接続を使用し得る。

【0061】

図4tは、MOSFETセル124の等角の3次元図を示す。第1の相互接続層194、第2の接続層214、および導電性ビアは、ソース領域160およびドレイン領域170から、第3の相互接続レベル234でのソースパッドおよびドレインパッドへの電気的接続を提供する。従って、単一のソースパッドおよびドレインパッドの下に設置されたソース接続およびドレイン接続の両方を有する、半導体ダイの全表面にわたって形成される、密接に整列されたトランジスターを接続する問題が解決される。トランジスターのソース領域およびドレイン領域を単一のソースパッドまたはドレインパッドに接続し得る厳密に垂直方向の相互接続を使用するのではなく、むしろ導電性ランナーは、単一のパッドの下のトランジスターのソース領域およびドレイン領域を複数の対応するパッドに接続するように構成されている。このようにして、トランジスターのドレイン領域が、ドレインパッドに接続され、トランジスターのソース領域が、ソースパッドに接続される。具体的には、ソース領域160は、ソースパッド236、導電性ビア186、ソースランナー196、導電性ビア206、ソースランナー216、および導電性ビア226によってソースバンプ240に電気的に接続される。同様に、ドレイン領域170は、導電性ビア188、ドレインランナー198、導電性ビア208、ドレインランナー218、およびドレインランナー218からドレインパッドに延在する追加の導電性ビアによってドレインパッドに電気的に接続される。

【0062】

珪化物層174が、ソース領域160およびドレイン領域170の上に形成される。珪化物層174は、ソース領域160およびドレイン領域170の上部表面上に形成される。珪化物層174は、ソース領域160およびドレイン領域170の上部表面にわたる金属導体として役に立つ。珪化物層174は、MOSFET124の全体コストを減少させるように、ソース領域160およびドレイン領域170の上部表面にわたる金属導体として役に立ち、ソース領域160およびドレイン領域170から後に形成されるバンプへの低抵抗電気的パスの一部分として電流伝導を増大させるための金属化パスとしてそれぞれに役に立つ。

【0063】

図5aは、複数のMOSFETセル、例えば、図4tからのMOSFETセル124を含むパワーMOSFET258の等角の3次元図を示す。パワーMOSFET258は、数百個または数千個のMOSFETセル124を含む。図5aにおいて、MOSFETセルの詳細、例えば、ソース領域160、ドレイン領域170、およびポリシリコンゲート138だけではなく、第1の相互接続層194、第2の相互接続層214、並びに導電性ビア186、188、206、208、および226を含む導電性ビアも含む、図4tに示されるMOSFETセル124の詳細が、明示的には示されていないが、パワーMOSFET258内、かつソースバンプ240、ドレインバンプ246、およびゲートバンプ250の下に含まれている。図5aは、ソースパッド236上に形成されたソースバンプ240、ドレインパッド244上に形成されたドレインバンプ246、およびゲートパッド248上に形成されたゲートバンプ250をさらに示している。図5aに示される実施形態において、ソースパッド236およびドレインパッド244は、パワーMOSFET258の上部表面にわたってチェッカーボード構成で配列されている。複数のMOSFETセル124のための電気的接続は、複数のソースパッド236、ドレインパッド244、およびゲートパッド248を通してルートが定められる。パワーMOSFET258は、各パワーMOSFET258内のダイまたはパッケージエリアの大部分を覆う、相互接続されたMOSFETセルのアレイを含む。各パワーMOSFET258は、電流の多くのアンペアを処理することが可能な単一のモノリシックスイッチングデバイスとして動作する。

【0064】

図5bは、図5aに示されるパワーMOSFET258に類似するパワーMOSFET259の代替の、等角の3次元図を示す。「ストライプ」状の形状のソースパッド237およびドレインパッド245が、交互に配置され、固定の距離で交互に間隔を空けられ、互いに対して実質的に平行に配向される。ゲートパッド249は、パワーMOSFETの構成および設計に従って、短縮されたソースパッド237または短縮されたドレインパッド245と直列に、パワーMOSFET259の上部表面上に形成される。図5bは、ソースパッド237上に形成されたソースバンプ241、ドレインパッド245上に形成されたドレインバンプ247、およびゲートパッド249上に形成されたゲートバンプ251をさらに示す。

【0065】

図5cは、複数のパワーMOSFET258をさらに含む、図4aからの半導体ウェーハ120の上面図を示す。パワーMOSFET258は、前述のように、ベース基板材料122上に形成され、かつソーストリート260によって分離される。

【0066】

図6a〜6iは、図4a〜4tおよび5a〜5cに関連して、それぞれ、パッド236、244、および248上にバンプ240、246、および250を形成するプロセスに関するさらなる詳細を例示する。

【0067】

図6aは、ソーストリート260によって分離された別個のパワーMOSFET258に属する複数のMOSFETセル124の一部分を含む、半導体ウェーハ120の一部分の断面図を示す。ソース接触パッド236およびドレイン接触パッド244の両方は、MOSFETセル124上に第3の相互接続レベル234にあると示される。ソース領域160、ドレイン領域170、およびポリシリコンゲート138だけではなく、第1の相互接続層194、第2の相互接続層214、並びに導電性ビア186、188、206、208、および226を含む導電性ビアも含む、図4tに示されるMOSFETセル124の詳細が、明示的には示されていないが、ソースパッド236およびドレインパッド244の下に含まれている。ソースバンプがソースパッド236上に形成される前、およびドレインバンプがドレインパッド244上に形成される前に、いくつかの介在する層が、ソースパッドおよびドレインパッドの上に形成される。具体的には、絶縁またはパシベーション層270は、MOSFETセル124の上部表面、ソース接触パッド236、ドレイン接触パッド244、およびソーストリート260の上の第3の相互接続レベル234において、半導体デバイスに順応的に適用される。絶縁層270の底部表面は、第3の相互接続レベル、ソース接触パッド236、およびドレイン接触パッド244の底部表面の輪郭に順応的に適用され、かつそれに追従する。絶縁層270の上部表面は、絶縁層が、ソースパッド236およびドレインパッド244のフットプリントの外側の、半導体ウェーハ120上の第1の厚さと、ソースパッド236およびドレインパッド244のフットプリント内の、半導体ウェーハ120上の第2の厚さとを有するように、実質的に平面である。第1の厚さは、第2の厚さより厚い。絶縁層270は、SiO2、Si3N4、SiON、Ta2O5、ジルコン(ZrO2)、Al2O3、ポリイミド、BCB、PBO、または適切な電気絶縁の性質を有する他の材料の1つ以上の層であり得る。絶縁層270は、PVD、CVD、プリント、スピンコーティング、スプレーコーティング、硬化焼結、または熱酸化を用いてパターンをつけられ、層状に蒸着される。絶縁層270の一部分は、ソースパッド236およびドレインパッド244の一部分を露出させる、絶縁層270における開口部272を生成するために、エッチングプロセスによって除去される。開口部272は、絶縁層270の上部表面から、絶縁層270の下部表面まで延在する。1つの実施形態において、開口部272は、図1aからの開口部20の幅に類似する270μmの幅を有する。ソースパッド236およびドレインパッド244の別の部分は、絶縁層270によって覆われた状態のままである。

【0068】

図6bにおいて、電気伝導層278は、パターニングおよび金属蒸着プロセス、例えば、プリント、PVD、CVD、スパッタリング、電解めっき、および無電解めっきを使用することによって、ソースパッド236およびドレインパッド244の上、かつ絶縁層270の一部分の上に形成され、ソースパッド236およびドレインパッド244に順応的に適用される。1つの実施形態において、ウェーハ120は、無電解ニッケルめっき溶液内に浸され、ニッケルが、ソースパッド236およびドレインパッド244上に3μmの厚さまでめっきされる。代替的には、導電層278は、Al、Cu、Sn、Au、Ag、または他の適切な電気伝導材料の1つ以上の層であり得る。導電層278は、絶縁層270の上部表面にわたって延在し、開口部272の周囲における絶縁層270の側壁に沿って、開口部272内のソースパッド236およびドレインパッド244の上部表面にわたって、絶縁層270の上部表面の輪郭に追従する。導電層278は、開口部272のフットプリント内、かつソースパッド236およびドレインパッド244の上にあるエリア280を含む。エリア280は、実質的に平坦であり、ソースパッド236およびドレインパッド244のそれぞれの全エリアより小さい。導電層278は、後に形成されるバンプのための第1のUBM層として動作する。

【0069】

図6cにおいて、電気伝導層284は、蒸着プロセス、例えば、無電解めっき、またはパターニングおよび金属蒸着プロセス、例えば、プリント、PVD、CVD、スパッタリング、および電解めっきを用いて、導電層278上に形成され、かつ導電層278に順応的に適用される。1つの実施形態において、ウェーハ120が、無電解金めっき溶液内に浸され、約100オングストロームの厚さを有する金の層が、無電解めっきプロセスを用いて導電層278の露出された金属領域上にめっきされる。別の実施形態において、金の層は、約10〜300オングストロームの厚さでめっきされる。代替的には、導電層284は、Al、Cu、Sn、Ni、Ag、または他の適切な電気伝導材料の1つ以上の層であり得る。導電層284は、絶縁層270から露出された導電層278、ソースパッド236、およびドレインパッド244の表面にわたって導電層278の輪郭に追従する。導電層284は、導電層278の側壁にわたって、絶縁層270から、絶縁層270の上部表面へ、かつ絶縁層270の上部表面にわたって、そして導電層278のエリア280内へ、かつ導電層278のエリア280にわたって延在する。導電層284の上部表面は、エリア286を含み、エリア286は、ソースパッド236およびドレインパッド244の上に形成され、実質的に平坦であり、両方のエリア280より小さく、エリア280のフットプリント内に含まれている。導電層284は、導電層278、ソースパッド236、およびドレインパッド244への導電性バンプの後の張りつけを支援するための接着層として役に立つ第2のUBM層として働く。導電層278および284の使用が、UBMを形成する低コストの方法であるが、他の方法が、導電性バンプの後の張りつけを支援するように、ソースパッド236およびドレインパッド244の上にUBMを形成するためにも使用され得る。

【0070】

図6dにおいて、開口部290を有するステンシルまたはマスキング層288は、開口部290が、エリア286の露出された中心部分と整列されているようにウェーハ120上に配置される。ステンシル288は、固体表面を有する剛性本体を含み、金属または他の適切な材料で作られる。ステンシル288は、ウェーハ120の全体上に配置されており、後に形成されるバンプを受け取るように構成されるUBM部位と整列するために、所望の場所にレーザーまたは切断ツールによって形成される開口部290を含む。開口部290は、ステンシル288の一部分が、開口部290をパシベーション層270から分離するために、導電層278および284の周囲部分の上に配置されるようにエリア286の中心部分上に整列させられる。開口部290とパシベーション層270とを分離することによって、後に形成される導電性材料が、パシベーション層270下へ拡散し、または流れることが防止される。開口部290は、半導体パッケージの設計および機能に従って、後に蒸着される導電性ペーストの所定の体積を含むように形成された高さおよび幅を有する。従って、エリア286上に後に蒸着される導電性材料の体積は、ステンシルの厚さ、および開口部290の断面積またはアパーチャサイズによって決定される。1つの実施形態において、開口部290は、短い高さおよび円形断面を含む円筒の形状を有する導電性バンプを形成するように構成された円形の断面エリアを有する。別の実施形態において、開口部290は、270μmより狭い幅を有し、絶縁層270における開口部272の幅より狭い。

【0071】

図6eにおいて、電気伝導バンプ材料294が、開口部290内、かつエリア286の中心部分の上に蒸着される。導電性バンプ材料294は、Al、Sn、Ni、Au、Ag、Pb、ビスマス(Bi)、Cu、インジウム(In)、はんだ、および任意のフラックス溶液を用いるそれらの組み合わせであり得る。例えば、バンプ材料は、共晶Sn/Pb、高鉛はんだ、または無鉛はんだであり得る。導電性バンプ材料294は、バンプ材料を開口部290内の導電層284上にステンシリングによって蒸着される。ステンシリングは、対象物がステンシル288の上部表面を横断するときに、開口部290内に多量のバンプ材料294を押し付けるように、スクイジーのような対象物を使用することによって達成される。ステンシリングはまた、ステンシル288内の開口部290内に導電性バンプ材料294をスプレーし、プリントし、またはブラシすることによって達成される。代替的には、導電性バンプ材料294は、開口部290内に噴射され得る。ウェーハ120上、かつMOSFETセル124上に導電性バンプ材料294をステンシリングすることによって、回路ボード上に導電性ペーストをステンシリングすること以外、半導体ダイの上に導電性バンプを形成するためのバンプ材料が、単一のステップにおいて全半導体ウェーハ120に対して蒸着され得るように、導電性バンプ材料294の正確な場所が提供される。さらに、導電層284上に蒸着された導電性バンプ材料294の体積が、ステンシル288の厚さ、および開口部290の断面積またはアパーチャサイズによって制御され、それによって後に形成される導電性バンプの最終的サイズを制御する。

【0072】