省面積及び省電力のスタンダードセル方法

【課題】省面積及び省電力のための半導体集積回路の設計方法を提供する。

【解決手段】主回路217と適応電圧用調整回路を含む半導体集積回路であって、適応電圧調整用回路は、クロック信号を受け取るように構成された整合回路211と、整合回路211の出力を受け取り、また、クロック信号を受け取るように構成された位相検出器213と、電源電圧を増加又は減少させるように構成された電圧レギュレータ215とを含み、主回路217は電圧レギュレータ215から電源電圧を受け取るように構成され、整合回路211は電源電圧を受け取って、電源電圧における増加又は減少に基づいて、信号伝搬における遅延を調整するように構成される。

【解決手段】主回路217と適応電圧用調整回路を含む半導体集積回路であって、適応電圧調整用回路は、クロック信号を受け取るように構成された整合回路211と、整合回路211の出力を受け取り、また、クロック信号を受け取るように構成された位相検出器213と、電源電圧を増加又は減少させるように構成された電圧レギュレータ215とを含み、主回路217は電圧レギュレータ215から電源電圧を受け取るように構成され、整合回路211は電源電圧を受け取って、電源電圧における増加又は減少に基づいて、信号伝搬における遅延を調整するように構成される。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は一般的に半導体集積回路に関し、特にスタンダードセル方式を用いた半導体集積回路の設計に関する。

【背景技術】

【0002】

半導体集積回路は、大抵は非常に複雑である。回路は、多様な機能を実行する様々なグループ内の数千又は何百万個ものゲートを含むことができる。ゲートは、1以上のクロック信号により同期されるゲートの動作により、製造プロセス変動、電源電圧変動及び温度変動にしばしば依存的なゲートの動作速度により、時間順に沿って動作するように大抵設計されている。

【0003】

これらの複雑性を考慮して、自動化ツールが半導体集積回路の設計にしばしば用いられる。自動化ツールは様々な機能を提供するものであるが、そのようなツールは、高いレベルの記述を低いレベルの実装に分解し、チップ内の低いレベルの実装要素の配置を決定し、チップ内のルーティング(経路探索)を決定するツールにより、設計者に対して、比較的高いレベルで回路機能を特定する可能性をしばしば提供するものである。

【0004】

高いレベルの記述を低いレベルの実装に分解する際に、自動化ツールは、標準要素のライブラリからの標準要素を非常に頻繁に用いる。各標準要素は、複数の考えられるバリエーション、例えば、駆動トランジスタ、バッファ、トランジスタの長さ/幅の比、或いは他の事項に関する複数のバリエーションを含み得る。特定のゲートの速度を早めるため、或いはタイミング目標に到達するホールドタイムを増加させるため、或いはその他の理由により、別の標準要素がそのツールにより用いられてもよい。

【0005】

半導体集積回路の適正なタイミング操作は非常に重要であり、その回路要素及びその回路の全体のタイミング目標が適合しない場合、回路の所望の機能は適正に実行され得ない。不運なことに、集積回路の特性は、実装変動、材料不純物又はその他の要因に基づいて、チップ毎、より一般的にはロット毎に異なっており、動作中は動作電圧又は温度変動に基づいて変動する。

【0006】

よって、自動化ツールは、プロセス、電圧及び温度変動の予想される曲線上の異なるポイントに関して、予想される回路タイミングをしばしばチェックする。多くの例では、その曲線の「スロー(遅い)」ポイントとその曲線の「ファスト(速い)」ポイントに対するタイミングがチェックされるが、あるツールではその曲線上の様々なポイント、或いは各変数に関する複数の曲線に対するタイミングをチェックする場合もある。

【0007】

一般的には、自動ツールは、ライブラリからの異なる要素を用いることにより、或いは更なる動作を実行するための追加的なライブラリ要素を並列に挿入することによって、タイミング変動を計算する。そのツールは、ホールドタイムを増加させるために、一連の要素の中に追加的なライブラリ要素を配置することができる。その変化は、より高電力な要素又は追加的な電力を必要とする要素をしばしばもたらし、そして、その追加的な電力への要求はしばしば、スイッチング速度又は信号上昇時間(signal rise times)の増加を必要とすることにより動作する。しかしながら、要素の数及び要素のサイズの増加は、しばしばチップサイズ条件及び電力条件を増加させる結果となり、それらは大抵望ましくない。

【発明の概要】

【0008】

本発明は、省面積及び省電力のための半導体集積回路の設計方法を提供する。

【0009】

本発明は一側面において、集積回路の電源線の動作特性に影響を及ぼすために使用される速度比較機能を提供する信号パスを含む、集積回路の条件を特定し、自動ツールにより使用されるスローコーナー用の電圧を、標準よりも高いレベルに設定し、高いレベルを使用して、自動ツールにより生成される回路設計が、集積回路のタイミング条件と適合し得るかどうかを決定することを含む集積回路の設計に用いられる方法を提供する。

【0010】

本発明は他の一側面において、動的電圧制御を含む集積回路の条件を特定し、条件をレジスタ転送レベル(RTL)記述に翻訳し、RTL記述を合成することであって、スローコーナーを特徴化するために標準電圧よりも高い電圧を使用することを含むことを含む集積回路の設計方法を提供する。

【0011】

本発明は他の一側面において、回路の転送レジスタレベル(RTL)記述を受け取り、RTL記述と一致する機能を実装するために、スタンダードセルライブラリの中から、RTL記述により表されたタイミング条件の一部に基づくセルを選択することにより、RTL記述を合成し、選択されたセルが、スローコーナー及びファストコーナーの双方に対するRTL記述により表されるタイミング条件に適合するか否かを決定することであって、スローコーナーは、スロープロセスパラメータ、スロー電圧パラメータ及びスロー温度パラメータの少なくとも一部により決定され、ファストコーナーは、ファストプロセスパラメータ、ファスト電圧パラメータ及びファスト温度パラメータの少なくとも一部により決定され、スロー電圧パラメータがファスト電圧パラメータと近似することを含む集積回路の設計方法を提供する。

【0012】

本発明は他の一側面において、適応電圧調整用回路を含む半導体集積回路であって、半導体集積回路は、スローコーナーのタイミング分析を実行する場合に、標準電圧よりも高い電圧を使用するプロセスにより選択されたスタンダードセル内のゲートを含む半導体集積回路を提供する。

【0013】

本発明のこれら又は他の側面は、本開示を考慮に入れることによって更に完全に理解される。

【図面の簡単な説明】

【0014】

【図1】本発明の一側面に係る集積回路を設計するためのプロセスのフロー図である。

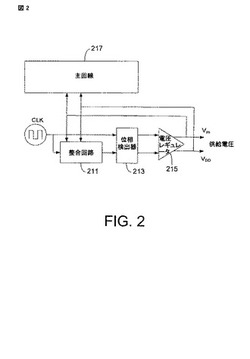

【図2】本発明の一側面に係る動的電圧制御回路の例を含む集積回路のブロック図である。

【図3】本発明の一側面に係るプロセスの更なるフロー図である。

【図4】本発明の一側面に係る集積回路のセミブロック図構成を示す説明図である。

【図5】本発明の一側面に係る設計操作を実行するためのコンピュータシステムを表すブロック図である。

【発明を実施するための形態】

【0015】

図1は、半導体集積回路を設計するためのプロセスのフロー図である。ブロック111においては仕様が決定される。一般的には、仕様は、集積回路の条件を特定する。仕様は、多くの形式をとることができ、例えば、VHDL又はベリログ(Verilog)コードの形式で与えられるが、このVHDL又はベリログコードは、仕様に基づいていても、或いは他の形式に基づいていても構わない。ブロック113において、仕様は、レジスタ転送レベル(RTL)記述に翻訳される。本発明の一側面においては、仕様は、予め定義された時間の信号遅延を与える回路を含んでいる。また、図示はしていないが、仕様とRTL記述との間の一致性を保証するための検証プロセスが含まれていてもよい。

【0016】

ブロック115において、RTL記述が、RTL記述を合成する合成ツールに与えられる。市場における様々な合成ツールが利用可能である。合成ツールは、半導体集積回路の論理ゲートレベルの実装を形成するために、スクリプト及び物理ゲート記述のライブラリを利用する。多くの場合、合成ツールは、スタンダードセル実装を使用し、各スタンダードセルは一般的には予め定められたサイズ及び異なる論理機能を実行する。各スタンダードセルは、一般的には、任意の製造プロセスに対してトランジスタレベルで特徴化されたゲートレベル回路で構成され、そのゲートレベル回路の特徴化により、電位が異なるどのスタンダードセルを使用すべきか、いくつ使用すべきか、及び実装設計の他の実装詳細を決定するに際して、合成ツールが、設計全体の動作の異なる側面を見積もることが可能となる。

【0017】

合成操作を実行する際、合成ツールは一般的には、結果として得られるチップがタイミング条件を含む操作条件に適合した方式となるように、スタンダードセルを提供しようと試みるであろう。チップは、標準の製造プロセス変動の観点から異なる特徴を有しているであろうし、また異なる供給電圧又は温度等の異なる条件下で操作され得るため、合成ツールは、一般的には、プロセス、電圧及び温度変動の予想範囲を超えるタイミング条件に適合するチップのゲートレベル記述を与えようと試みるであろう。したがって、合成ツールは、静的タイミング解析特性をしばしば含むであろう(しかし静的タイミング解析は別個のツールにより実行されるかもしれないが)。図1は、静的タイミング解析特性が合成ツールによって与えられることを想定している。しかし他の実施形態においては、この特徴は、合成ツールを用いて繰り返して操作される可能性のある別個のツールとして与えられることができることを理解すべきである。

【0018】

本発明の一側面においては、電圧変動の予想範囲における最も低い電圧値が増加され、電圧変動の予想範囲における最も高い電圧値が減少されるが、種々の実施形態においては、それらの1のみ又は他が行われても構わない。例えば、合成ツールは、電圧が一般的にレール・ツー・レール電圧で接続されるときに、低電圧で0.9ボルトから高電圧で1.2ボルトまでの範囲の公称供給電圧を予想し得る。本発明の一側面においては、例えば、合成ツールは、公称供給電圧が、低電圧では1.0ボルトから高電圧では1.1ボルトまでの範囲にあるという情報を持っていてもよい。本発明のある側面においては、合成ツールは、公称低電圧条件が、公称高電圧条件と同等又は実質的に同等であり、例えば双方が1.1ボルトであり得るという情報を持っていてもよい。代替的には、合成ツールは、公称供給電圧が低電圧で1.1ボルトから高電圧で1.2ボルトまでの範囲にあるという情報を持っていてもよいし、或いは、合成ツールが公称供給電圧が低電圧で0.9ボルトから高電圧で1.0ボルトまでの範囲にあるという情報を持っていてもよい。

【0019】

多くの場合、合成ツールにより提供されるゲートレベルネットリストがRTL記述及び/又は仕様と一致(整合)することを保証するために、合成の後に検証が行われる。様々な検証ツールが利用可能であり、バイナリ・ディシジョン・ダイアグラム(BDD)ベースのツール、自動テストパターン生成(ATPG)ツール、或いは他のツール又はツールの組み合わせであっても構わない。

【0020】

ブロック117において、ゲートレベル合成が配置配線ツールにより受け取られる。配置配線ツールは、半導体集積回路のセル配置及びセル間の信号配線を決定する。説明上、配置配線ツールは、ツールの配置配線特徴と共に繰り返し操作され得る静的及び動的タイミング分析特性を含むことを想定している。繰り返すが、配置配線ツールは低電圧から高電圧の範囲の公称供給電圧の情報を持っており、本発明の一側面においては、低電圧が低電圧として標準的に予想される値よりも高く特定されるか、高電圧が高電圧として標準的に予想される値よりも低く特定されるか、或いは、低電圧及び高電圧の一方又は他方がそのように特定される。

ある実施形態においては、プロセスは、設計を含むチップの製造を更に含む。ある実施形態においては、図1に示すように、配置配線ツールがセルを配置して設計基準を満たすことを想定して、プロセスがその後に戻される(リターン)。配置配線ツールがそのようなことができない場合には、プロセスが、設計を再合成して更に操作を行うための合成ブロックに戻される。

【0021】

本発明の一側面において、図1のプロセスでは、適応電源電圧調整(アダプティブ・パワーサプライ・レギュレーション)用の回路が、半導体集積回路の特定要素として含まれる。ある実施形態においては、回路に適応電源電圧調整が備わっており、ある実施形態においては回路が適応電源電圧調整を提供する。

【0022】

一実施形態においては、適応電源電圧調整用回路は、プロセス、電圧及び温度変動によって変化する予め定められた公称信号遅延を有するオンチップ(チップ上の)回路を備える。回路は、例えば、リング発振器として、数多くのバッファ及び/又はゲートで形成される(タップされた又はアンタップされた)遅延線として、或いは他の回路要素を用いた、多くの異なる方法によって実装され得る。電圧レベルの調整により、回路及びオンチップ集積回路の残りに対して電力として供給するオフチップ回路により実行される他の実施形態では、好ましい動作制限内の遅れで操作することが可能となる。

【0023】

図2に適応電源電圧調整用回路のブロック図の一例を提供する。図2の回路例は、レール電圧を半導体集積回路上の主回路に与える。しかしながら、種々の実施形態においては、適応電源電圧調整用回路は、レール電圧を設定する際に電源供給回路により使用される制御信号を提供してもよい。

【0024】

図2の回路は、便宜上整合回路と呼ばれる回路211を備えており、例えば、リング発信器、タップされた遅延線、又は信号伝搬に遅延を生じさせる他の回路構造等を含む。遅延は一般に、プロセス変動、即ち集積回路の製造プロセスにおける変動、電圧変動、即ち回路に与えられる供給電圧変動、及び温度変動、即ち回路の動作温度変動に基づく。

【0025】

整合回路に対して、クロック信号が与えられる。クロック信号は、オフチップ(チップ外)のクロックソース(クロック源)から供給され得る。しかしながら、多くの実施形態においては、クロック信号が、オフチップ(チップ外の)の低周波域クロックソースに基づく、PLL又はDLL等のオンチップ(チップ上の)要素によって生成される。整合回路は入力クロック信号を受け取り、入力クロック信号の遅延バージョンである出力信号を与える。整合回路により提供されるクロック信号の遅れの一部は、電力を整合回路に与える電源供給レールの電圧レベルによるものである。整合回路の出力は、位相検出器213によって受け取られ、位相検出器213はクロック信号をも受け取る。位相検出器は、整合回路により与えられた遅れを示す位相差で、整合回路の出力とクロック信号の間の位相差を決定する。位相検出器は、アップ(UP)及びダウン(DOWN)信号を電圧レギュレータ215に与える。アップ・ダウン信号に基づく電圧レギュレータは、電源電圧を増加させ、又は減少させる。電源電圧は、整合回路の遅れを減少させると予測されるような増大した電源電圧で、整合回路に与えられる。したがって、電圧レギュレータは、位相検出器の入力に基づいて、クロック信号に対して望ましい整合回路処理速度を持つように、電源レール電圧を駆動する。

【0026】

電源電圧は主回路217にも提供される。主回路は、仕様に特定された回路構造を含み、例えば、図1のプロセスを用いることによって実装される。このため、主回路の動作速度は、印加する電源電圧の変化を通じて、プロセス変動及び温度変動を計算するように調整され得る。

【0027】

設計において適応電源電圧調整回路を包含させることには多くの利益がある。そのような利益の1つとしては、例えば、スローコーナー電圧条件を増加させること及び/又はファストコーナー電圧条件を低減すること考慮に入れた設計プロセスの利用を通じて、より小さな集積回路を設計することができ、これはまた、一般的には回路に必要な電力を削減することを表す。更には、適応電源電圧調整回路は、より高電力なレベルでの回路動作期間を短くする。回路に必要とされる全体電力の削減及び高電力レベルでの動作期間の減縮の双方は、信頼性の増加及びチップの動作耐用年数の増加に繋がるであろう。更に、多くの場合において、配置配線操作により、タイミング仕様に適合する回路が得られ、設計の再合成を通して甚大な再作業をする必要を避けることができるため、設計クロージャを容易に達成することができる。

【0028】

図3は、回路設計を改善するためのプロセスのフロー図を更に示すものである。ブロック311において、適応電源電圧調整回路が半導体集積回路のための仕様に含まれる。代替的には、適応電源電圧調整に用いられる回路と一致する電源電圧調整に用いられることが予想されるオフチップ回路(外部チップ回路)により、適応電源電圧調整用回路が含まれる。ブロック313において、合成ツールにより使用されるコーナー電圧条件が修正される。一般的には、合成ツールは、回路の「スロー(遅い)」動作を決定するための(一般的には適正なプロセス及び温度パラメータ条件下での)低電源電圧条件と、回路の「ファスト(速い)」動作条件を決定するための(繰り返すが、一般的には適正なプロセス及び温度パラメータ条件下での)高電源電圧条件とを、遅い条件及び速い条件の双方下での正確な回路動作目標とともに使用する。多くの実施形態において、スローコーナー電圧条件及びファストコーナー電圧条件が修正される。即ち一般的にはスローコーナー電圧はデフォルトよりも増大するか、そうでなければ予想されたスローコーナー電圧とされ、ファストコーナー電圧はデフォルトより小さくされるか、そうでなければ予想されたファストコーナー電圧とされる状態となるように修正される。そのような実施形態において、スローコーナー電圧及びファストコーナー電圧は、同一電圧又は実質に同一な電圧に設定される。しかしながら、ある実施形態においては、スローコーナー電圧条件のみが修正されるか、一方他の実施形態では、ファストコーナー電源条件のみが修正される。例えば、ある実施形態においては、合成ツールが、スローコーナーの回路速度を決定する場合に増大電圧が用いられる。

【0029】

ブロック315において、合成ツールは、スローコーナー電圧条件を用いて回路を合成する。このスローコーナー電圧条件が標準よりも高いため、合成ツールは、使用するセル及びセルの特徴を決定する場合に、より小さなトランジスタを用いることができ、そうでなければセルの総数を減らすことができる。小さなトランジスタを使用し、セル総数の総数を少なくすることにより、省電力な半導体回路が提供される。

【0030】

図4は、本発明の一側面に係る半導体集積回路を含むチップのセミブロック図である。半導体集積回路は、大抵よくあるように、チップの周辺付近に表されるI/Oリング411を含む。チップの内部付近には、論理処理ブロック413、415が配置される。集積回路のコーナー(角部)には、電源調整ブロック417が位置する。電源調整ブロックは、しばしばレールと呼ばれる電源線のパワーレベルを設定する。遅延線及び比較ブロック419は、遅延線の動作速度が、望ましい動作速度の範囲内にある回路動作速度を示しているかどうかを決定(判断)する。遅延線及び比較ブロックは、回路動作速度が遅すぎるために電源調整ブロックがパワーレベルを増加させる必要があるかどうか、及び回路動作速度が速すぎるため電源調整ブロックがパワーレベルを小さくする必要があるかどうか、又は適正な範囲内にあるかどうかを指し示す1以上の信号を電源調整ブロックに対して供給する。

【0031】

図5は、本発明の一側面に係る操作の実行に利用されるコンピュータシステムのブロック図である。コンピュータシステムはプロセッサ502を備える。便宜上、単一のプロセッサが示されているが、複数のプロセッサをシステム内に用いてもよい。プロセッサはシステムバス503を介してメインメモリ504及びI/Oインターフェース制御ユニット506に動作可能に接続されている。I/Oインターフェース制御ユニットはI/Oローカルバス508を介して記憶装置コントローラ510に動作可能に接続されている。システムは、入力装置コントローラ520を介してI/Oローカルバスに接続されたユーザ入力装置522に更に接続されている。

【0032】

プロセッサは、I/Oインターフェース制御ユニット、I/Oローカルバス及び入力装置コントローラを介して記憶装置512に接続されている。本明細書で説明した設計ツール等を実装したコンピュータプログラム命令513が、プロセッサがコンピュータプログラム命令を検索してこれらをメインメモリに格納するまで、記憶装置に格納される。プロセッサは、本明細書で説明したプロセスを実行するために、メインメモリ内に格納されたコンピュータプログラム命令を実行する。例えば、プロセッサは、ユーザから、例えばユーザ入力装置、又は追加的には記憶装置を介して設計情報を受け付け、その設計情報のプログラム命令に基づいて、例えば合成及び/又は配線操作等の操作を実行し、例えばネットリスト又は最終設計などの設計結果情報を、メモリ又は記憶装置に格納する。

【0033】

データ処理システムは、ディスプレイコントローラ516を介してI/Oローカルバスに接続されたディスプレイ装置又はスクリーン518を更に備える。データ処理システムは、ディスプレイ情報、例えば設計情報や設計結果情報を表示させるために、ディスプレイコントローラ及びディスプレイ装置を使用する。

【0034】

本発明は特定の実施形態を用いて説明したが、本発明はここに明示的に説明した以外により実行され得ることを認識すべきである。したがって、本発明は、特許請求の範囲及びこの開示によりサポートされる非本質的な変形例により考察されるであろう。

【技術分野】

【0001】

本発明は一般的に半導体集積回路に関し、特にスタンダードセル方式を用いた半導体集積回路の設計に関する。

【背景技術】

【0002】

半導体集積回路は、大抵は非常に複雑である。回路は、多様な機能を実行する様々なグループ内の数千又は何百万個ものゲートを含むことができる。ゲートは、1以上のクロック信号により同期されるゲートの動作により、製造プロセス変動、電源電圧変動及び温度変動にしばしば依存的なゲートの動作速度により、時間順に沿って動作するように大抵設計されている。

【0003】

これらの複雑性を考慮して、自動化ツールが半導体集積回路の設計にしばしば用いられる。自動化ツールは様々な機能を提供するものであるが、そのようなツールは、高いレベルの記述を低いレベルの実装に分解し、チップ内の低いレベルの実装要素の配置を決定し、チップ内のルーティング(経路探索)を決定するツールにより、設計者に対して、比較的高いレベルで回路機能を特定する可能性をしばしば提供するものである。

【0004】

高いレベルの記述を低いレベルの実装に分解する際に、自動化ツールは、標準要素のライブラリからの標準要素を非常に頻繁に用いる。各標準要素は、複数の考えられるバリエーション、例えば、駆動トランジスタ、バッファ、トランジスタの長さ/幅の比、或いは他の事項に関する複数のバリエーションを含み得る。特定のゲートの速度を早めるため、或いはタイミング目標に到達するホールドタイムを増加させるため、或いはその他の理由により、別の標準要素がそのツールにより用いられてもよい。

【0005】

半導体集積回路の適正なタイミング操作は非常に重要であり、その回路要素及びその回路の全体のタイミング目標が適合しない場合、回路の所望の機能は適正に実行され得ない。不運なことに、集積回路の特性は、実装変動、材料不純物又はその他の要因に基づいて、チップ毎、より一般的にはロット毎に異なっており、動作中は動作電圧又は温度変動に基づいて変動する。

【0006】

よって、自動化ツールは、プロセス、電圧及び温度変動の予想される曲線上の異なるポイントに関して、予想される回路タイミングをしばしばチェックする。多くの例では、その曲線の「スロー(遅い)」ポイントとその曲線の「ファスト(速い)」ポイントに対するタイミングがチェックされるが、あるツールではその曲線上の様々なポイント、或いは各変数に関する複数の曲線に対するタイミングをチェックする場合もある。

【0007】

一般的には、自動ツールは、ライブラリからの異なる要素を用いることにより、或いは更なる動作を実行するための追加的なライブラリ要素を並列に挿入することによって、タイミング変動を計算する。そのツールは、ホールドタイムを増加させるために、一連の要素の中に追加的なライブラリ要素を配置することができる。その変化は、より高電力な要素又は追加的な電力を必要とする要素をしばしばもたらし、そして、その追加的な電力への要求はしばしば、スイッチング速度又は信号上昇時間(signal rise times)の増加を必要とすることにより動作する。しかしながら、要素の数及び要素のサイズの増加は、しばしばチップサイズ条件及び電力条件を増加させる結果となり、それらは大抵望ましくない。

【発明の概要】

【0008】

本発明は、省面積及び省電力のための半導体集積回路の設計方法を提供する。

【0009】

本発明は一側面において、集積回路の電源線の動作特性に影響を及ぼすために使用される速度比較機能を提供する信号パスを含む、集積回路の条件を特定し、自動ツールにより使用されるスローコーナー用の電圧を、標準よりも高いレベルに設定し、高いレベルを使用して、自動ツールにより生成される回路設計が、集積回路のタイミング条件と適合し得るかどうかを決定することを含む集積回路の設計に用いられる方法を提供する。

【0010】

本発明は他の一側面において、動的電圧制御を含む集積回路の条件を特定し、条件をレジスタ転送レベル(RTL)記述に翻訳し、RTL記述を合成することであって、スローコーナーを特徴化するために標準電圧よりも高い電圧を使用することを含むことを含む集積回路の設計方法を提供する。

【0011】

本発明は他の一側面において、回路の転送レジスタレベル(RTL)記述を受け取り、RTL記述と一致する機能を実装するために、スタンダードセルライブラリの中から、RTL記述により表されたタイミング条件の一部に基づくセルを選択することにより、RTL記述を合成し、選択されたセルが、スローコーナー及びファストコーナーの双方に対するRTL記述により表されるタイミング条件に適合するか否かを決定することであって、スローコーナーは、スロープロセスパラメータ、スロー電圧パラメータ及びスロー温度パラメータの少なくとも一部により決定され、ファストコーナーは、ファストプロセスパラメータ、ファスト電圧パラメータ及びファスト温度パラメータの少なくとも一部により決定され、スロー電圧パラメータがファスト電圧パラメータと近似することを含む集積回路の設計方法を提供する。

【0012】

本発明は他の一側面において、適応電圧調整用回路を含む半導体集積回路であって、半導体集積回路は、スローコーナーのタイミング分析を実行する場合に、標準電圧よりも高い電圧を使用するプロセスにより選択されたスタンダードセル内のゲートを含む半導体集積回路を提供する。

【0013】

本発明のこれら又は他の側面は、本開示を考慮に入れることによって更に完全に理解される。

【図面の簡単な説明】

【0014】

【図1】本発明の一側面に係る集積回路を設計するためのプロセスのフロー図である。

【図2】本発明の一側面に係る動的電圧制御回路の例を含む集積回路のブロック図である。

【図3】本発明の一側面に係るプロセスの更なるフロー図である。

【図4】本発明の一側面に係る集積回路のセミブロック図構成を示す説明図である。

【図5】本発明の一側面に係る設計操作を実行するためのコンピュータシステムを表すブロック図である。

【発明を実施するための形態】

【0015】

図1は、半導体集積回路を設計するためのプロセスのフロー図である。ブロック111においては仕様が決定される。一般的には、仕様は、集積回路の条件を特定する。仕様は、多くの形式をとることができ、例えば、VHDL又はベリログ(Verilog)コードの形式で与えられるが、このVHDL又はベリログコードは、仕様に基づいていても、或いは他の形式に基づいていても構わない。ブロック113において、仕様は、レジスタ転送レベル(RTL)記述に翻訳される。本発明の一側面においては、仕様は、予め定義された時間の信号遅延を与える回路を含んでいる。また、図示はしていないが、仕様とRTL記述との間の一致性を保証するための検証プロセスが含まれていてもよい。

【0016】

ブロック115において、RTL記述が、RTL記述を合成する合成ツールに与えられる。市場における様々な合成ツールが利用可能である。合成ツールは、半導体集積回路の論理ゲートレベルの実装を形成するために、スクリプト及び物理ゲート記述のライブラリを利用する。多くの場合、合成ツールは、スタンダードセル実装を使用し、各スタンダードセルは一般的には予め定められたサイズ及び異なる論理機能を実行する。各スタンダードセルは、一般的には、任意の製造プロセスに対してトランジスタレベルで特徴化されたゲートレベル回路で構成され、そのゲートレベル回路の特徴化により、電位が異なるどのスタンダードセルを使用すべきか、いくつ使用すべきか、及び実装設計の他の実装詳細を決定するに際して、合成ツールが、設計全体の動作の異なる側面を見積もることが可能となる。

【0017】

合成操作を実行する際、合成ツールは一般的には、結果として得られるチップがタイミング条件を含む操作条件に適合した方式となるように、スタンダードセルを提供しようと試みるであろう。チップは、標準の製造プロセス変動の観点から異なる特徴を有しているであろうし、また異なる供給電圧又は温度等の異なる条件下で操作され得るため、合成ツールは、一般的には、プロセス、電圧及び温度変動の予想範囲を超えるタイミング条件に適合するチップのゲートレベル記述を与えようと試みるであろう。したがって、合成ツールは、静的タイミング解析特性をしばしば含むであろう(しかし静的タイミング解析は別個のツールにより実行されるかもしれないが)。図1は、静的タイミング解析特性が合成ツールによって与えられることを想定している。しかし他の実施形態においては、この特徴は、合成ツールを用いて繰り返して操作される可能性のある別個のツールとして与えられることができることを理解すべきである。

【0018】

本発明の一側面においては、電圧変動の予想範囲における最も低い電圧値が増加され、電圧変動の予想範囲における最も高い電圧値が減少されるが、種々の実施形態においては、それらの1のみ又は他が行われても構わない。例えば、合成ツールは、電圧が一般的にレール・ツー・レール電圧で接続されるときに、低電圧で0.9ボルトから高電圧で1.2ボルトまでの範囲の公称供給電圧を予想し得る。本発明の一側面においては、例えば、合成ツールは、公称供給電圧が、低電圧では1.0ボルトから高電圧では1.1ボルトまでの範囲にあるという情報を持っていてもよい。本発明のある側面においては、合成ツールは、公称低電圧条件が、公称高電圧条件と同等又は実質的に同等であり、例えば双方が1.1ボルトであり得るという情報を持っていてもよい。代替的には、合成ツールは、公称供給電圧が低電圧で1.1ボルトから高電圧で1.2ボルトまでの範囲にあるという情報を持っていてもよいし、或いは、合成ツールが公称供給電圧が低電圧で0.9ボルトから高電圧で1.0ボルトまでの範囲にあるという情報を持っていてもよい。

【0019】

多くの場合、合成ツールにより提供されるゲートレベルネットリストがRTL記述及び/又は仕様と一致(整合)することを保証するために、合成の後に検証が行われる。様々な検証ツールが利用可能であり、バイナリ・ディシジョン・ダイアグラム(BDD)ベースのツール、自動テストパターン生成(ATPG)ツール、或いは他のツール又はツールの組み合わせであっても構わない。

【0020】

ブロック117において、ゲートレベル合成が配置配線ツールにより受け取られる。配置配線ツールは、半導体集積回路のセル配置及びセル間の信号配線を決定する。説明上、配置配線ツールは、ツールの配置配線特徴と共に繰り返し操作され得る静的及び動的タイミング分析特性を含むことを想定している。繰り返すが、配置配線ツールは低電圧から高電圧の範囲の公称供給電圧の情報を持っており、本発明の一側面においては、低電圧が低電圧として標準的に予想される値よりも高く特定されるか、高電圧が高電圧として標準的に予想される値よりも低く特定されるか、或いは、低電圧及び高電圧の一方又は他方がそのように特定される。

ある実施形態においては、プロセスは、設計を含むチップの製造を更に含む。ある実施形態においては、図1に示すように、配置配線ツールがセルを配置して設計基準を満たすことを想定して、プロセスがその後に戻される(リターン)。配置配線ツールがそのようなことができない場合には、プロセスが、設計を再合成して更に操作を行うための合成ブロックに戻される。

【0021】

本発明の一側面において、図1のプロセスでは、適応電源電圧調整(アダプティブ・パワーサプライ・レギュレーション)用の回路が、半導体集積回路の特定要素として含まれる。ある実施形態においては、回路に適応電源電圧調整が備わっており、ある実施形態においては回路が適応電源電圧調整を提供する。

【0022】

一実施形態においては、適応電源電圧調整用回路は、プロセス、電圧及び温度変動によって変化する予め定められた公称信号遅延を有するオンチップ(チップ上の)回路を備える。回路は、例えば、リング発振器として、数多くのバッファ及び/又はゲートで形成される(タップされた又はアンタップされた)遅延線として、或いは他の回路要素を用いた、多くの異なる方法によって実装され得る。電圧レベルの調整により、回路及びオンチップ集積回路の残りに対して電力として供給するオフチップ回路により実行される他の実施形態では、好ましい動作制限内の遅れで操作することが可能となる。

【0023】

図2に適応電源電圧調整用回路のブロック図の一例を提供する。図2の回路例は、レール電圧を半導体集積回路上の主回路に与える。しかしながら、種々の実施形態においては、適応電源電圧調整用回路は、レール電圧を設定する際に電源供給回路により使用される制御信号を提供してもよい。

【0024】

図2の回路は、便宜上整合回路と呼ばれる回路211を備えており、例えば、リング発信器、タップされた遅延線、又は信号伝搬に遅延を生じさせる他の回路構造等を含む。遅延は一般に、プロセス変動、即ち集積回路の製造プロセスにおける変動、電圧変動、即ち回路に与えられる供給電圧変動、及び温度変動、即ち回路の動作温度変動に基づく。

【0025】

整合回路に対して、クロック信号が与えられる。クロック信号は、オフチップ(チップ外)のクロックソース(クロック源)から供給され得る。しかしながら、多くの実施形態においては、クロック信号が、オフチップ(チップ外の)の低周波域クロックソースに基づく、PLL又はDLL等のオンチップ(チップ上の)要素によって生成される。整合回路は入力クロック信号を受け取り、入力クロック信号の遅延バージョンである出力信号を与える。整合回路により提供されるクロック信号の遅れの一部は、電力を整合回路に与える電源供給レールの電圧レベルによるものである。整合回路の出力は、位相検出器213によって受け取られ、位相検出器213はクロック信号をも受け取る。位相検出器は、整合回路により与えられた遅れを示す位相差で、整合回路の出力とクロック信号の間の位相差を決定する。位相検出器は、アップ(UP)及びダウン(DOWN)信号を電圧レギュレータ215に与える。アップ・ダウン信号に基づく電圧レギュレータは、電源電圧を増加させ、又は減少させる。電源電圧は、整合回路の遅れを減少させると予測されるような増大した電源電圧で、整合回路に与えられる。したがって、電圧レギュレータは、位相検出器の入力に基づいて、クロック信号に対して望ましい整合回路処理速度を持つように、電源レール電圧を駆動する。

【0026】

電源電圧は主回路217にも提供される。主回路は、仕様に特定された回路構造を含み、例えば、図1のプロセスを用いることによって実装される。このため、主回路の動作速度は、印加する電源電圧の変化を通じて、プロセス変動及び温度変動を計算するように調整され得る。

【0027】

設計において適応電源電圧調整回路を包含させることには多くの利益がある。そのような利益の1つとしては、例えば、スローコーナー電圧条件を増加させること及び/又はファストコーナー電圧条件を低減すること考慮に入れた設計プロセスの利用を通じて、より小さな集積回路を設計することができ、これはまた、一般的には回路に必要な電力を削減することを表す。更には、適応電源電圧調整回路は、より高電力なレベルでの回路動作期間を短くする。回路に必要とされる全体電力の削減及び高電力レベルでの動作期間の減縮の双方は、信頼性の増加及びチップの動作耐用年数の増加に繋がるであろう。更に、多くの場合において、配置配線操作により、タイミング仕様に適合する回路が得られ、設計の再合成を通して甚大な再作業をする必要を避けることができるため、設計クロージャを容易に達成することができる。

【0028】

図3は、回路設計を改善するためのプロセスのフロー図を更に示すものである。ブロック311において、適応電源電圧調整回路が半導体集積回路のための仕様に含まれる。代替的には、適応電源電圧調整に用いられる回路と一致する電源電圧調整に用いられることが予想されるオフチップ回路(外部チップ回路)により、適応電源電圧調整用回路が含まれる。ブロック313において、合成ツールにより使用されるコーナー電圧条件が修正される。一般的には、合成ツールは、回路の「スロー(遅い)」動作を決定するための(一般的には適正なプロセス及び温度パラメータ条件下での)低電源電圧条件と、回路の「ファスト(速い)」動作条件を決定するための(繰り返すが、一般的には適正なプロセス及び温度パラメータ条件下での)高電源電圧条件とを、遅い条件及び速い条件の双方下での正確な回路動作目標とともに使用する。多くの実施形態において、スローコーナー電圧条件及びファストコーナー電圧条件が修正される。即ち一般的にはスローコーナー電圧はデフォルトよりも増大するか、そうでなければ予想されたスローコーナー電圧とされ、ファストコーナー電圧はデフォルトより小さくされるか、そうでなければ予想されたファストコーナー電圧とされる状態となるように修正される。そのような実施形態において、スローコーナー電圧及びファストコーナー電圧は、同一電圧又は実質に同一な電圧に設定される。しかしながら、ある実施形態においては、スローコーナー電圧条件のみが修正されるか、一方他の実施形態では、ファストコーナー電源条件のみが修正される。例えば、ある実施形態においては、合成ツールが、スローコーナーの回路速度を決定する場合に増大電圧が用いられる。

【0029】

ブロック315において、合成ツールは、スローコーナー電圧条件を用いて回路を合成する。このスローコーナー電圧条件が標準よりも高いため、合成ツールは、使用するセル及びセルの特徴を決定する場合に、より小さなトランジスタを用いることができ、そうでなければセルの総数を減らすことができる。小さなトランジスタを使用し、セル総数の総数を少なくすることにより、省電力な半導体回路が提供される。

【0030】

図4は、本発明の一側面に係る半導体集積回路を含むチップのセミブロック図である。半導体集積回路は、大抵よくあるように、チップの周辺付近に表されるI/Oリング411を含む。チップの内部付近には、論理処理ブロック413、415が配置される。集積回路のコーナー(角部)には、電源調整ブロック417が位置する。電源調整ブロックは、しばしばレールと呼ばれる電源線のパワーレベルを設定する。遅延線及び比較ブロック419は、遅延線の動作速度が、望ましい動作速度の範囲内にある回路動作速度を示しているかどうかを決定(判断)する。遅延線及び比較ブロックは、回路動作速度が遅すぎるために電源調整ブロックがパワーレベルを増加させる必要があるかどうか、及び回路動作速度が速すぎるため電源調整ブロックがパワーレベルを小さくする必要があるかどうか、又は適正な範囲内にあるかどうかを指し示す1以上の信号を電源調整ブロックに対して供給する。

【0031】

図5は、本発明の一側面に係る操作の実行に利用されるコンピュータシステムのブロック図である。コンピュータシステムはプロセッサ502を備える。便宜上、単一のプロセッサが示されているが、複数のプロセッサをシステム内に用いてもよい。プロセッサはシステムバス503を介してメインメモリ504及びI/Oインターフェース制御ユニット506に動作可能に接続されている。I/Oインターフェース制御ユニットはI/Oローカルバス508を介して記憶装置コントローラ510に動作可能に接続されている。システムは、入力装置コントローラ520を介してI/Oローカルバスに接続されたユーザ入力装置522に更に接続されている。

【0032】

プロセッサは、I/Oインターフェース制御ユニット、I/Oローカルバス及び入力装置コントローラを介して記憶装置512に接続されている。本明細書で説明した設計ツール等を実装したコンピュータプログラム命令513が、プロセッサがコンピュータプログラム命令を検索してこれらをメインメモリに格納するまで、記憶装置に格納される。プロセッサは、本明細書で説明したプロセスを実行するために、メインメモリ内に格納されたコンピュータプログラム命令を実行する。例えば、プロセッサは、ユーザから、例えばユーザ入力装置、又は追加的には記憶装置を介して設計情報を受け付け、その設計情報のプログラム命令に基づいて、例えば合成及び/又は配線操作等の操作を実行し、例えばネットリスト又は最終設計などの設計結果情報を、メモリ又は記憶装置に格納する。

【0033】

データ処理システムは、ディスプレイコントローラ516を介してI/Oローカルバスに接続されたディスプレイ装置又はスクリーン518を更に備える。データ処理システムは、ディスプレイ情報、例えば設計情報や設計結果情報を表示させるために、ディスプレイコントローラ及びディスプレイ装置を使用する。

【0034】

本発明は特定の実施形態を用いて説明したが、本発明はここに明示的に説明した以外により実行され得ることを認識すべきである。したがって、本発明は、特許請求の範囲及びこの開示によりサポートされる非本質的な変形例により考察されるであろう。

【特許請求の範囲】

【請求項1】

集積回路の電源線の動作特性に影響を及ぼすために使用される速度比較機能を提供する信号パスを含む、前記集積回路の条件を特定し、

自動ツールにより使用されるスローコーナー用の電圧を、標準よりも高いレベルに設定し、

前記高いレベルを使用して、前記自動ツールにより生成される回路設計が、前記集積回路のタイミング条件と適合し得るかどうかを決定すること

を含む集積回路の設計に用いられる方法。

【請求項2】

前記自動ツールに使用されるファストコーナー用の電圧を、標準よりも低いレベルに設定し、

前記低いレベルを使用して、前記自動ツールにより生成される回路設計が、前記集積回路のタイミング条件と適合し得るかどうかを決定すること

を更に含む請求項1に記載の方法。

【請求項3】

前記低いレベル及び前記高いレベルは、実質的に同じレベルである請求項2に記載の方法。

【請求項4】

前記低いレベル及び前記高いレベルが、異なるレベルである請求項2に記載の方法。

【請求項5】

集積回路の電源線の動作特性に影響を及ぼすために使用される速度比較機能を提供する信号パスを含む、前記集積回路の条件を特定し、

自動ツールにより使用されるファストコーナー用の電圧を、標準よりも低いレベルに設定し、

前記低いレベルを使用して、前記自動ツールにより生成される回路設計が、前記集積回路のタイミング条件と適合し得るかどうかを決定すること

を含む集積回路の設計に用いられる方法。

【請求項6】

動的電圧制御を含む集積回路の条件を特定し、

前記条件をレジスタ転送レベル(RTL)記述に翻訳し、

前記RTL記述を合成することであって、スローコーナーを特徴化するために標準電圧よりも高い電圧を使用することを含むこと

を含む集積回路の設計方法。

【請求項7】

前記RTL記述を合成することが、

ファストコーナーを特徴化するために標準電圧よりも低い電圧を使用することを更に含む請求項6に記載の方法。

【請求項8】

前記スローコーナーを特徴化するための標準電圧よりも高い電圧と、前記ファストコーナーを特徴化するための標準電圧よりも低い電圧とが、実質的に同一電圧である請求項7に記載の方法。

【請求項9】

前記スローコーナーを特徴化するための標準電圧よりも高い電圧と、前記ファストコーナーを特徴化するための標準電圧よりも低い電圧とが、異なる電圧である請求項7に記載の方法。

【請求項10】

前記RTL記述を合成することにより提供されるゲートレベル表現に対して配置配線操作を実行し、前記標準電圧よりも高い電圧を用いて、前記配置配線操作により提供された回路表現がタイミング条件に適合するか否かを決定することを更に含む請求項6に記載の方法。

【請求項11】

前記RTL記述を合成することにより提供されるゲートレベル表現に対して配置配線操作を実行し、前記標準電圧よりも高い電圧及び前記標準電圧よりも低い電圧を用いて、前記配置配線操作がタイミング条件に適合するか否かを決定することを更に含む請求項7に記載の方法。

【請求項12】

回路の転送レジスタレベル(RTL)記述を受け取り、

前記RTL記述と一致する機能を実装するために、スタンダードセルライブラリの中から、前記RTL記述により表されたタイミング条件の一部に基づくセルを選択することにより、前記RTL記述を合成し、

前記選択されたセルが、スローコーナー及びファストコーナーの双方に対する前記RTL記述により表されるタイミング条件に適合するか否かを決定することであって、

前記スローコーナーは、スロープロセスパラメータ、スロー電圧パラメータ及びスロー温度パラメータの少なくとも一部により決定され、

前記ファストコーナーは、ファストプロセスパラメータ、ファスト電圧パラメータ及びファスト温度パラメータの少なくとも一部により決定され、

前記スロー電圧パラメータが前記ファスト電圧パラメータと近似することを含む集積回路の設計方法。

【請求項13】

適応電圧調整用回路を含む半導体集積回路であって、前記半導体集積回路は、スローコーナーのタイミング分析を実行する場合に、標準電圧よりも高い電圧を使用するプロセスにより選択されたスタンダードセル内のゲートを含む半導体集積回路。

【請求項14】

前記プロセスが、ファストコーナーのタイミング分析を実行する場合に標準電圧よりも低い電圧を使用する請求項13に記載の半導体集積回路。

【請求項15】

前記適応電圧調整用回路が、適応電源電圧調整回路を含む請求項13に記載の半導体集積回路。

【請求項1】

集積回路の電源線の動作特性に影響を及ぼすために使用される速度比較機能を提供する信号パスを含む、前記集積回路の条件を特定し、

自動ツールにより使用されるスローコーナー用の電圧を、標準よりも高いレベルに設定し、

前記高いレベルを使用して、前記自動ツールにより生成される回路設計が、前記集積回路のタイミング条件と適合し得るかどうかを決定すること

を含む集積回路の設計に用いられる方法。

【請求項2】

前記自動ツールに使用されるファストコーナー用の電圧を、標準よりも低いレベルに設定し、

前記低いレベルを使用して、前記自動ツールにより生成される回路設計が、前記集積回路のタイミング条件と適合し得るかどうかを決定すること

を更に含む請求項1に記載の方法。

【請求項3】

前記低いレベル及び前記高いレベルは、実質的に同じレベルである請求項2に記載の方法。

【請求項4】

前記低いレベル及び前記高いレベルが、異なるレベルである請求項2に記載の方法。

【請求項5】

集積回路の電源線の動作特性に影響を及ぼすために使用される速度比較機能を提供する信号パスを含む、前記集積回路の条件を特定し、

自動ツールにより使用されるファストコーナー用の電圧を、標準よりも低いレベルに設定し、

前記低いレベルを使用して、前記自動ツールにより生成される回路設計が、前記集積回路のタイミング条件と適合し得るかどうかを決定すること

を含む集積回路の設計に用いられる方法。

【請求項6】

動的電圧制御を含む集積回路の条件を特定し、

前記条件をレジスタ転送レベル(RTL)記述に翻訳し、

前記RTL記述を合成することであって、スローコーナーを特徴化するために標準電圧よりも高い電圧を使用することを含むこと

を含む集積回路の設計方法。

【請求項7】

前記RTL記述を合成することが、

ファストコーナーを特徴化するために標準電圧よりも低い電圧を使用することを更に含む請求項6に記載の方法。

【請求項8】

前記スローコーナーを特徴化するための標準電圧よりも高い電圧と、前記ファストコーナーを特徴化するための標準電圧よりも低い電圧とが、実質的に同一電圧である請求項7に記載の方法。

【請求項9】

前記スローコーナーを特徴化するための標準電圧よりも高い電圧と、前記ファストコーナーを特徴化するための標準電圧よりも低い電圧とが、異なる電圧である請求項7に記載の方法。

【請求項10】

前記RTL記述を合成することにより提供されるゲートレベル表現に対して配置配線操作を実行し、前記標準電圧よりも高い電圧を用いて、前記配置配線操作により提供された回路表現がタイミング条件に適合するか否かを決定することを更に含む請求項6に記載の方法。

【請求項11】

前記RTL記述を合成することにより提供されるゲートレベル表現に対して配置配線操作を実行し、前記標準電圧よりも高い電圧及び前記標準電圧よりも低い電圧を用いて、前記配置配線操作がタイミング条件に適合するか否かを決定することを更に含む請求項7に記載の方法。

【請求項12】

回路の転送レジスタレベル(RTL)記述を受け取り、

前記RTL記述と一致する機能を実装するために、スタンダードセルライブラリの中から、前記RTL記述により表されたタイミング条件の一部に基づくセルを選択することにより、前記RTL記述を合成し、

前記選択されたセルが、スローコーナー及びファストコーナーの双方に対する前記RTL記述により表されるタイミング条件に適合するか否かを決定することであって、

前記スローコーナーは、スロープロセスパラメータ、スロー電圧パラメータ及びスロー温度パラメータの少なくとも一部により決定され、

前記ファストコーナーは、ファストプロセスパラメータ、ファスト電圧パラメータ及びファスト温度パラメータの少なくとも一部により決定され、

前記スロー電圧パラメータが前記ファスト電圧パラメータと近似することを含む集積回路の設計方法。

【請求項13】

適応電圧調整用回路を含む半導体集積回路であって、前記半導体集積回路は、スローコーナーのタイミング分析を実行する場合に、標準電圧よりも高い電圧を使用するプロセスにより選択されたスタンダードセル内のゲートを含む半導体集積回路。

【請求項14】

前記プロセスが、ファストコーナーのタイミング分析を実行する場合に標準電圧よりも低い電圧を使用する請求項13に記載の半導体集積回路。

【請求項15】

前記適応電圧調整用回路が、適応電源電圧調整回路を含む請求項13に記載の半導体集積回路。

【図1】

【図2】

【図3】

【図4】

【図5】

【図2】

【図3】

【図4】

【図5】

【公開番号】特開2013−102443(P2013−102443A)

【公開日】平成25年5月23日(2013.5.23)

【国際特許分類】

【外国語出願】

【出願番号】特願2012−265258(P2012−265258)

【出願日】平成24年12月4日(2012.12.4)

【分割の表示】特願2010−524938(P2010−524938)の分割

【原出願日】平成20年9月8日(2008.9.8)

【出願人】(595020643)クゥアルコム・インコーポレイテッド (7,166)

【氏名又は名称原語表記】QUALCOMM INCORPORATED

【Fターム(参考)】

【公開日】平成25年5月23日(2013.5.23)

【国際特許分類】

【出願番号】特願2012−265258(P2012−265258)

【出願日】平成24年12月4日(2012.12.4)

【分割の表示】特願2010−524938(P2010−524938)の分割

【原出願日】平成20年9月8日(2008.9.8)

【出願人】(595020643)クゥアルコム・インコーポレイテッド (7,166)

【氏名又は名称原語表記】QUALCOMM INCORPORATED

【Fターム(参考)】

[ Back to top ]