真空装置および成膜方法

【課題】樹脂基板等の耐熱温度の低い基板でもイオンアシスト成膜を可能とする。

【解決手段】真空槽30と、基板ドーム21との間に高周波電源41から高周波電圧を印加し、真空槽30内のガスをプラズマ化し、陽イオンにより、蒸着分子の成膜基板22への堆積をアシストする。高周波電圧の印加により発生する基板ドーム21のセルフバイアス電圧を検出し、セルフバイアス電圧が減少すると、これを補償するように高周波電源41の出力電力を増加する。

【解決手段】真空槽30と、基板ドーム21との間に高周波電源41から高周波電圧を印加し、真空槽30内のガスをプラズマ化し、陽イオンにより、蒸着分子の成膜基板22への堆積をアシストする。高周波電圧の印加により発生する基板ドーム21のセルフバイアス電圧を検出し、セルフバイアス電圧が減少すると、これを補償するように高周波電源41の出力電力を増加する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は真空装置及び成膜方法に関し、特に成膜基板を搭載する基板ドームに高周波電力を供給して真空装置内のガスをイオン化する真空装置及びイオンにより成膜をアシストする成膜方法に関する。

【背景技術】

【0002】

真空蒸着法等において、真空槽内部へ導入したガスを電離させ、発生した陽イオンによって蒸着分子を基板へ押し付けることにより密着力が強く充填密度の高い薄膜を形成する手法は、一般的にIon Assisted Depositionと呼ばれる(以下「IAD」という)。この成膜方法は、例えば特許文献1などに開示されている。

【特許文献1】特開2001‐73136号公報

【発明の開示】

【発明が解決しようとする課題】

【0003】

IADには、イオンガンなどを利用してガスイオンを基板に照射するイオンビームアシスト蒸着や、何らかのイオン化手段により真空槽内にプラズマを生成してイオンを基板に衝突させるイオンプレーティング等がある。

ここでは、成膜基板が搭載された基板ドームと真空槽の間に高周波電圧を印加して真空槽内のガスをプラズマ化し、陽イオンを生成して基板に衝突させる真空蒸着装置について説明する。

【0004】

基板ドームと真空槽の間に高周波電圧を印加し続けると、基板ドームと真空槽の面積の差、イオンと電子の単位時間当たりの移動距離の差等により、真空槽よりも基板ドームの方が電位が低くなる現象が発生する。この現象により発生する電圧は、セルフバイアス電圧又はセルフ直流バイアス電圧(以下、VDC)と呼ばれる。

【0005】

このVDCが小さいと、アシスト効果が減殺されて、密着力が弱く、充填密度の低い薄膜が形成されてしまうという課題が生ずる。一方で、VDCが大きすぎると、基板が昇温してしまうと共に膜応力が大きくなってしまうという課題が生ずる。従って、適切なVDCを選択し、維持する必要がある。

【0006】

しかし、従来のIADでは、時間の経過(処理の進行)に伴ってVDCが変化してしまう。これは、基板ドームの電極としての能力が、プロセスの生成物が付着することにより処理回数に応じて劣化すること等による。

【0007】

前述のように、VDCが低下すると、イオンアシスト効果が低減し、形成された膜の充填密度(屈折率)が低下してしまう。特に、バッチ処理をくり返すと、その影響が大きくなる。

【0008】

また、1回のバッチ処理(真空槽内に基板を搬入してから搬出するまで)間に、複数回成膜する場合も同様の問題が発生する。さらに、1回のバッチ処理で、異なる材質の膜を蒸着形成する場合には、同じ電力を供給しても蒸着材料毎にVDCが異なるため、例えば、図3(a)に示すように、前層の蒸着材料のVDCから成膜中の蒸着材料のVDCまで、変化してしまう。

【0009】

例えば、供給電力一定でNb2O5膜とSiO2膜とを積層した際のVDCの変化を、図2を参照に説明する。図2(a)と(b)は1バッチ目における1層目と2層目のVDCの値を示し、図2(c)と(d)は10バッチ目における1層目と2層目のVDCの値を示す。

図2(b)と(d)に示すように、2層目を形成する際には、1層目のVDCの影響を受けて、VDCが1層目の蒸着材料のVDCから2層目の蒸着材料のVDCに変化するという現象が起きる。1層の形成中にVDCの値が変化すると、形成膜の厚み方向の屈折率が変化してしまう。また、1バッチで複数層の蒸着を繰り返す場合には、図示はしないが、1バッチ内の各層の形成中にVDCが減少する現象が起きる。さらに、バッチ処理を繰り返すうちに、図2(a)、(b)と(c)、(d)に示すように、VDCが全体として低下してしまう。

【0010】

VDCの低下に備えて、従来は、高めの高周波電力を基板ドームに供給するようにしていた。しかし、この場合、真空槽の清掃直後などにおいては、イオンアシスト効果が高いため、基板温度が高くなってしまう。

【0011】

基板がガラスなどの耐熱温度の高いものであればこの手法も有効であるが、基板として樹脂・プラスチック基板、アクリル基板などの耐熱温度の低い基板を使用する場合には、この手法を使用することができない。

このため、高周波電力を基板ドームに供給する成膜方法では、比較的熱に弱いタイプの基板上に成膜することが困難であった。

【0012】

また、VDCの値は、形成される膜の膜質、例えば、その屈折率や密着力に影響を与える。従って、成膜中にVDCの値が変化すると、屈折率が変化し、屈折率が変化すると所望の光学特性が得られなくなる。このため、所望の膜質の膜を形成するためには、VDCの値を制御する必要がある。

【0013】

この発明は上記実情に鑑みてなされたものであり、セルフバイアス電圧を適切な値に維持可能とすることを目的とする。

また、この発明は上記実情に鑑みてなされたものであり、耐熱温度の低い基板でも成膜が可能な真空装置及びイオンアシスト成膜方法を提供することを他の目的とする。

【課題を解決するための手段】

【0014】

上記目的を達成するため、この発明の第1の観点に係る真空装置は、

真空槽と、該真空槽内に配置される電極と、該電極と真空槽との間に高周波電力を供給し、真空槽内のガスをイオン化するための給電手段と、高周波電力の印加により前記電極に発生するセルフバイアス電圧を検出し、検出したセルフバイアス電圧に基づいて前記給電手段の出力する高周波電力を制御する制御手段と、から構成される。

【0015】

前記制御手段は、例えば、前記セルフバイアス電圧が一定になるように、前記給電手段の出力する高周波電力を制御する。

【0016】

成膜対象の基板を搭載する手段と、蒸発源と、を配置し、前記蒸発源からの蒸発分子の前記基板への付着をイオンによりアシストする。

【0017】

上記目的を達成するため、この発明の第2の観点に係る成膜方法は、

真空槽と該真空槽内に配置される電極との間に高周波電圧を印加して、真空槽内に供給されたガスをイオン化し、該イオンにより蒸発源からの蒸着粒子の基板への付着をアシストして成膜し、

高周波電力の印加により前記真空槽と前記電極との間に発生するセルフバイアス電圧を検出し、

検出したセルフバイアス電圧が一定となるように、高周波電力を制御する、

ことを特徴とする。

【発明の効果】

【0018】

本発明によれば、セルフバイアス電圧を検出し、セルフバイアス電圧が所望の値となるように高周波電力を制御することにより、成膜の再現性を向上させ、所望の特性を有する素子を精度よく作製することが可能となる。

【発明を実施するための最良の形態】

【0019】

以下、この発明の実施の形態に係るIAD(Ion Assisted Deposition)法を用いた高周波電圧直接印加方式の光学薄膜用真空蒸着装置について説明する。

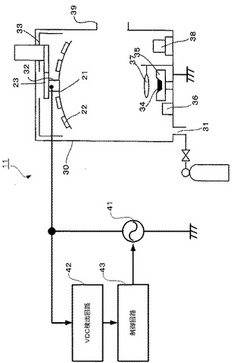

本実施の形態の光学薄膜用真空蒸着装置11は、図1に示すように、基板ドーム21と、基板ドーム回転機構23と、真空槽30と、ガス導入口31と、給電部32と、基板加熱用ヒーター33と、蒸着材料34を充填する坩堝35と、電子銃36と、シャッター37と、ニュートラライザ38と、排気口39と、を備える。

【0020】

また、給電部32と真空槽30との間には、高周波電源41とVDC測定回路42とが接続され、高周波電源41とVDC測定回路42とに制御回路43が接続されている。

【0021】

真空槽(真空チャンバ)30は、導体から構成され、接地された密閉容器から構成され、基板ドーム21と、基板ドーム回転機構23と、給電部32と、基板加熱用ヒーター33と、坩堝35と、電子銃36と、シャッター37と、ニュートラライザ38と、等を収容し、ガス導入口31と排気口39とを備える。

【0022】

基板ドーム21は、ドーム状の形状を有し、高周波電極として機能し、真空槽30内に高周波電圧を印加する。また、基板ドーム21上には、成膜対象の成膜基板22が載置される。なお、基板22を、基板ドーム21近傍に保持する構成でもよい。

【0023】

基板ドーム回転機構23は、均一な成膜を可能とするため、成膜処理の間、基板ドーム21を回転する。

ガス導入口31は、真空槽30内部にアルゴン(Ar)、酸素(O2)等の放電ガス、プロセスガス、等、任意のガスを導入する。

給電部32は、回転する基板ドーム21に高周波電圧を印加する。

基板加熱用ヒーター33は、成膜基板22を加熱する。

蒸着材料34は、例えば、シリコン(Si)やニオブ(Nb)の酸化物等である。

坩堝35には、プロセスに応じた種類の蒸着材料が充填されている。

電子銃36は、坩堝35内の蒸着材料34に電子を衝突させ、蒸発温度まで加熱する。

【0024】

シャッター37は、開閉可能に構成され、蒸着完了時に閉じ蒸着材料を遮蔽する。

ニュートラライザ38は、放電の着火と基板のチャージアップを防止するために電子を放出する。

排気口39は、真空ポンプなどの排気装置に接続され、真空槽30内のガスを排気する。

【0025】

高周波電源41は、可変電力型の高周波電源装置であり、制御回路43からの制御信号が指示する電力で、給電部32と真空槽30との間に、高周波電圧を印加する。高周波電圧の周波数と電圧はプロセスに応じて適宜選択されるが、例えば、M(メガ)帯域やG(ギガ)帯域の周波数を有する。

【0026】

VDC検出回路42は、基板ドーム21の電圧の直流成分、即ち、セルフバイアス電圧(VDC)を検出するものであり、サンプル・ホールド回路と、A/D(アナログ・ディジタル)変換器を備える。サンプル・ホールド回路は、基板ドーム22の電圧を一定時間サンプリングし、A/D変換器は、サンプル・ホールド回路がサンプリングした電圧をディジタル信号に変換する。

【0027】

制御回路43は、マイクロプロセッサなどから構成され、VDC測定回路42が出力するデジタル信号、即ち、VDCの値に従って、高周波電源41の出力電力(Pf)を制御する。

【0028】

VDC検出回路42と制御回路43とは、負の帰還ループ(ネガティブフィードバック)を形成し、VDCが所望の一定値を維持するように、VDCが大きくなるに従って、高周波電源41の電力を小さくし、VDCが小さくなるに従って高周波電源41の電力を大きくするように制御する。なお、制御手法自体は、P(比例)制御でも、PI(比例・積分)制御でも、PID(比例・積分・微分)制御でも、任意である。

【0029】

制御対象であるVDCの目標値は任意であるが、VDCにより生成された熱により成膜基板22が昇温したときの温度がその耐熱温度以下で、高周波電圧の振幅よりも大きい値に設定される。

制御対象であるVDCの目標値は必要に応じて適宜設定すればよい。例えば、予め実験などによりVDCの値と、その条件で形成される膜の屈折率及び密着力との相関を求めておき、所望の屈折率、所望の密着力を得るために必要なVDCの目標値を適宜選択して設定するようにすればよい。なお、VDCの目標値は、成膜期間中、一定値である必要はなく、適宜変動させてもよい。

【0030】

次に、真空蒸着装置11により基板上に蒸着を行なう動作を、SiO2膜とNb2O5膜の積層膜を形成する場合を例に説明する。

まず、基板ドーム21に成膜基板22を設置する。続いて、蒸発源には形成する膜に応じた蒸着材料34であるNb2O5を充填した坩堝35aとSiO2を充填した坩堝35bを配置しておく。

【0031】

次に、真空槽30内を図示しない排気系によって10−4Pa程度の高真空領域まで排気する。基板ドーム回転機構23により基板ドーム21を回転させる。また、必要に応じて基板加熱用ヒーター33を用いて成膜基板22を加熱する。

続いて、また、ガス導入口31から真空槽30内にAr,O2等のガスを導入する。ガス流量を安定させ、例えば真空槽30内の圧力を10−2Pa程度の真空状態に維持する。

また、電子銃36から電子ビームを坩堝35a内のNb2O5蒸着材料34へ照射し、蒸着材料34を蒸発温度まで昇温させる。

【0032】

一方、制御回路43は、高周波電源41を起動して、給電部32を介して基板ドーム21に高周波電圧を印加すると共にニュートラライザ38から電子を放出し、プラズマを着火する。また、VDCをNb2O5用の目標値に維持するためのネガティブフィードバックを開始する。

【0033】

基板ドーム21と真空槽30との間に印加された高周波電圧は、ガス導入口31から導入したガスをイオン化し、真空槽30内にプラズマを発生させる。

【0034】

VDC検出回路42のサンプル・ホールド回路は、基板ドーム21の電圧をサンプリングし、A/D変換器により、サンプル値をデジタル化して、制御回路43に供給する。サンプル・ホールド回路のサンプリング期間は、高周波の影響を受けずにVDCを安定して検出できるように、高周波電圧の周期の数倍以上の期間を有することが望ましい。

【0035】

シャッター37を開くと蒸着材料34であるNb2O5は真空槽30内を飛散し、VDCに吸引されたイオンにアシストされて、成膜基板22上に堆積することで緻密なNb2O5薄膜を形成する。

【0036】

この間、制御回路43は、VDC検出回路42の出力データに基づいて、VDCの実測値と基準値との偏差を求め、この偏差を小さくするように、高周波電源41の出力電力を制御し続ける。

【0037】

成膜されたNb2O5膜の膜厚が目標値に到達したらシャッター37を一旦閉じる。

【0038】

続いて、電子銃36から電子ビームを坩堝35b内のSiO2蒸着材料34へ照射し、蒸着材料34を蒸発温度まで昇温させる。また、VDCの目標値をSiO2用の値に切り替える。

【0039】

シャッター37を開くと蒸着材料34であるSiO2は真空槽30内を飛散し、VDCに吸引されたイオンにアシストされて、成膜基板22上に堆積することで緻密な薄膜を形成する。

【0040】

以後、同様の動作を繰り返し、所望の膜厚のNb2O5膜とSiO2膜とを、必要な層数だけ積層する。

成膜処理が終了すると、シャッター37を閉じると共に電子銃36、基板加熱用ヒーター33、高周波電源41、ガスの導入、およびニュートラライザ38などを停止させる。冷却後、真空槽30内に大気を導入した後、薄膜が形成された成膜基板22を取り出す。

【0041】

このような構成によれば、成膜処理中は、フィードバック制御により、図3(b)に示すように、基板ドーム21のVDCが最適な一定レベルに維持される。従って、イオンアシスト効果が1回の処理(1層形成中)中ほぼ一定であり、また、複数回の処理間でもほぼ一定であり、安定して高品質の成膜が可能である。即ち、1バッチ内及びバッチ間で均質な成膜が可能となる。

【0042】

また、従来と異なり、VDCの低下に備えて高周波電源41の出力電力を予め大きくしておく必要が無い。従って、エネルギーロスを抑え、不必要な熱の発生を抑えて、樹脂・アクリルなどの比較的耐熱温度の低い成膜基材22上にも成膜が可能となる。

【0043】

なお、以上の説明においては、制御ループをVDC検出回路42と制御回路43とから構成したが、VDC検出回路42の入力段にローパスフィルタなどを配置してもよい。また、単純な構成により、基板ドーム21の電圧を積分回路(ローパスフィルタ)等を介して電源回路41の電力制御端に供給することにより、電源回路41の電力を制御する等してもよい。

【0044】

その他、この発明は上記実施の形態に限定されず、種々の変形及び応用が可能である。例えば、上記実施の形態においては、理解を容易にするため、高周波電源及びその制御回路を真空槽30の外部に配置したが、一般的に行われているように、基板ドーム22の上部に高周波電源部を収納する等しても良い。

【0045】

また、蒸着材料、ガス種、圧力、温度などは、上記実施の形態で例示したものに限定されず、任意に変更可能である。

【図面の簡単な説明】

【0046】

【図1】本発明の実施の形態に係る真空装置の全体構成図である。

【図2】1バッチで異なる材質の膜を形成する処理を複数バッチ繰り返した場合の、VDCの変化を例示する図である。

【図3】異なる材質の膜を積層する処理を複数バッチ繰り返した場合の、VDCの変化を、従来と本願発明の実施形態とを対比して例示する図である。

【符号の説明】

【0047】

21 基板ドーム

22 成膜基板

23 基板ドーム回転機構

30 真空槽

31 ガス導入口

32 給電部

33 基板加熱用ヒーター

34 蒸着材料

35 坩堝

36 電子銃

37 シャッター

38 ニュートラライザ

39 排気口

41 高周波電源

42 VDC検出回路

43 制御回路

【技術分野】

【0001】

本発明は真空装置及び成膜方法に関し、特に成膜基板を搭載する基板ドームに高周波電力を供給して真空装置内のガスをイオン化する真空装置及びイオンにより成膜をアシストする成膜方法に関する。

【背景技術】

【0002】

真空蒸着法等において、真空槽内部へ導入したガスを電離させ、発生した陽イオンによって蒸着分子を基板へ押し付けることにより密着力が強く充填密度の高い薄膜を形成する手法は、一般的にIon Assisted Depositionと呼ばれる(以下「IAD」という)。この成膜方法は、例えば特許文献1などに開示されている。

【特許文献1】特開2001‐73136号公報

【発明の開示】

【発明が解決しようとする課題】

【0003】

IADには、イオンガンなどを利用してガスイオンを基板に照射するイオンビームアシスト蒸着や、何らかのイオン化手段により真空槽内にプラズマを生成してイオンを基板に衝突させるイオンプレーティング等がある。

ここでは、成膜基板が搭載された基板ドームと真空槽の間に高周波電圧を印加して真空槽内のガスをプラズマ化し、陽イオンを生成して基板に衝突させる真空蒸着装置について説明する。

【0004】

基板ドームと真空槽の間に高周波電圧を印加し続けると、基板ドームと真空槽の面積の差、イオンと電子の単位時間当たりの移動距離の差等により、真空槽よりも基板ドームの方が電位が低くなる現象が発生する。この現象により発生する電圧は、セルフバイアス電圧又はセルフ直流バイアス電圧(以下、VDC)と呼ばれる。

【0005】

このVDCが小さいと、アシスト効果が減殺されて、密着力が弱く、充填密度の低い薄膜が形成されてしまうという課題が生ずる。一方で、VDCが大きすぎると、基板が昇温してしまうと共に膜応力が大きくなってしまうという課題が生ずる。従って、適切なVDCを選択し、維持する必要がある。

【0006】

しかし、従来のIADでは、時間の経過(処理の進行)に伴ってVDCが変化してしまう。これは、基板ドームの電極としての能力が、プロセスの生成物が付着することにより処理回数に応じて劣化すること等による。

【0007】

前述のように、VDCが低下すると、イオンアシスト効果が低減し、形成された膜の充填密度(屈折率)が低下してしまう。特に、バッチ処理をくり返すと、その影響が大きくなる。

【0008】

また、1回のバッチ処理(真空槽内に基板を搬入してから搬出するまで)間に、複数回成膜する場合も同様の問題が発生する。さらに、1回のバッチ処理で、異なる材質の膜を蒸着形成する場合には、同じ電力を供給しても蒸着材料毎にVDCが異なるため、例えば、図3(a)に示すように、前層の蒸着材料のVDCから成膜中の蒸着材料のVDCまで、変化してしまう。

【0009】

例えば、供給電力一定でNb2O5膜とSiO2膜とを積層した際のVDCの変化を、図2を参照に説明する。図2(a)と(b)は1バッチ目における1層目と2層目のVDCの値を示し、図2(c)と(d)は10バッチ目における1層目と2層目のVDCの値を示す。

図2(b)と(d)に示すように、2層目を形成する際には、1層目のVDCの影響を受けて、VDCが1層目の蒸着材料のVDCから2層目の蒸着材料のVDCに変化するという現象が起きる。1層の形成中にVDCの値が変化すると、形成膜の厚み方向の屈折率が変化してしまう。また、1バッチで複数層の蒸着を繰り返す場合には、図示はしないが、1バッチ内の各層の形成中にVDCが減少する現象が起きる。さらに、バッチ処理を繰り返すうちに、図2(a)、(b)と(c)、(d)に示すように、VDCが全体として低下してしまう。

【0010】

VDCの低下に備えて、従来は、高めの高周波電力を基板ドームに供給するようにしていた。しかし、この場合、真空槽の清掃直後などにおいては、イオンアシスト効果が高いため、基板温度が高くなってしまう。

【0011】

基板がガラスなどの耐熱温度の高いものであればこの手法も有効であるが、基板として樹脂・プラスチック基板、アクリル基板などの耐熱温度の低い基板を使用する場合には、この手法を使用することができない。

このため、高周波電力を基板ドームに供給する成膜方法では、比較的熱に弱いタイプの基板上に成膜することが困難であった。

【0012】

また、VDCの値は、形成される膜の膜質、例えば、その屈折率や密着力に影響を与える。従って、成膜中にVDCの値が変化すると、屈折率が変化し、屈折率が変化すると所望の光学特性が得られなくなる。このため、所望の膜質の膜を形成するためには、VDCの値を制御する必要がある。

【0013】

この発明は上記実情に鑑みてなされたものであり、セルフバイアス電圧を適切な値に維持可能とすることを目的とする。

また、この発明は上記実情に鑑みてなされたものであり、耐熱温度の低い基板でも成膜が可能な真空装置及びイオンアシスト成膜方法を提供することを他の目的とする。

【課題を解決するための手段】

【0014】

上記目的を達成するため、この発明の第1の観点に係る真空装置は、

真空槽と、該真空槽内に配置される電極と、該電極と真空槽との間に高周波電力を供給し、真空槽内のガスをイオン化するための給電手段と、高周波電力の印加により前記電極に発生するセルフバイアス電圧を検出し、検出したセルフバイアス電圧に基づいて前記給電手段の出力する高周波電力を制御する制御手段と、から構成される。

【0015】

前記制御手段は、例えば、前記セルフバイアス電圧が一定になるように、前記給電手段の出力する高周波電力を制御する。

【0016】

成膜対象の基板を搭載する手段と、蒸発源と、を配置し、前記蒸発源からの蒸発分子の前記基板への付着をイオンによりアシストする。

【0017】

上記目的を達成するため、この発明の第2の観点に係る成膜方法は、

真空槽と該真空槽内に配置される電極との間に高周波電圧を印加して、真空槽内に供給されたガスをイオン化し、該イオンにより蒸発源からの蒸着粒子の基板への付着をアシストして成膜し、

高周波電力の印加により前記真空槽と前記電極との間に発生するセルフバイアス電圧を検出し、

検出したセルフバイアス電圧が一定となるように、高周波電力を制御する、

ことを特徴とする。

【発明の効果】

【0018】

本発明によれば、セルフバイアス電圧を検出し、セルフバイアス電圧が所望の値となるように高周波電力を制御することにより、成膜の再現性を向上させ、所望の特性を有する素子を精度よく作製することが可能となる。

【発明を実施するための最良の形態】

【0019】

以下、この発明の実施の形態に係るIAD(Ion Assisted Deposition)法を用いた高周波電圧直接印加方式の光学薄膜用真空蒸着装置について説明する。

本実施の形態の光学薄膜用真空蒸着装置11は、図1に示すように、基板ドーム21と、基板ドーム回転機構23と、真空槽30と、ガス導入口31と、給電部32と、基板加熱用ヒーター33と、蒸着材料34を充填する坩堝35と、電子銃36と、シャッター37と、ニュートラライザ38と、排気口39と、を備える。

【0020】

また、給電部32と真空槽30との間には、高周波電源41とVDC測定回路42とが接続され、高周波電源41とVDC測定回路42とに制御回路43が接続されている。

【0021】

真空槽(真空チャンバ)30は、導体から構成され、接地された密閉容器から構成され、基板ドーム21と、基板ドーム回転機構23と、給電部32と、基板加熱用ヒーター33と、坩堝35と、電子銃36と、シャッター37と、ニュートラライザ38と、等を収容し、ガス導入口31と排気口39とを備える。

【0022】

基板ドーム21は、ドーム状の形状を有し、高周波電極として機能し、真空槽30内に高周波電圧を印加する。また、基板ドーム21上には、成膜対象の成膜基板22が載置される。なお、基板22を、基板ドーム21近傍に保持する構成でもよい。

【0023】

基板ドーム回転機構23は、均一な成膜を可能とするため、成膜処理の間、基板ドーム21を回転する。

ガス導入口31は、真空槽30内部にアルゴン(Ar)、酸素(O2)等の放電ガス、プロセスガス、等、任意のガスを導入する。

給電部32は、回転する基板ドーム21に高周波電圧を印加する。

基板加熱用ヒーター33は、成膜基板22を加熱する。

蒸着材料34は、例えば、シリコン(Si)やニオブ(Nb)の酸化物等である。

坩堝35には、プロセスに応じた種類の蒸着材料が充填されている。

電子銃36は、坩堝35内の蒸着材料34に電子を衝突させ、蒸発温度まで加熱する。

【0024】

シャッター37は、開閉可能に構成され、蒸着完了時に閉じ蒸着材料を遮蔽する。

ニュートラライザ38は、放電の着火と基板のチャージアップを防止するために電子を放出する。

排気口39は、真空ポンプなどの排気装置に接続され、真空槽30内のガスを排気する。

【0025】

高周波電源41は、可変電力型の高周波電源装置であり、制御回路43からの制御信号が指示する電力で、給電部32と真空槽30との間に、高周波電圧を印加する。高周波電圧の周波数と電圧はプロセスに応じて適宜選択されるが、例えば、M(メガ)帯域やG(ギガ)帯域の周波数を有する。

【0026】

VDC検出回路42は、基板ドーム21の電圧の直流成分、即ち、セルフバイアス電圧(VDC)を検出するものであり、サンプル・ホールド回路と、A/D(アナログ・ディジタル)変換器を備える。サンプル・ホールド回路は、基板ドーム22の電圧を一定時間サンプリングし、A/D変換器は、サンプル・ホールド回路がサンプリングした電圧をディジタル信号に変換する。

【0027】

制御回路43は、マイクロプロセッサなどから構成され、VDC測定回路42が出力するデジタル信号、即ち、VDCの値に従って、高周波電源41の出力電力(Pf)を制御する。

【0028】

VDC検出回路42と制御回路43とは、負の帰還ループ(ネガティブフィードバック)を形成し、VDCが所望の一定値を維持するように、VDCが大きくなるに従って、高周波電源41の電力を小さくし、VDCが小さくなるに従って高周波電源41の電力を大きくするように制御する。なお、制御手法自体は、P(比例)制御でも、PI(比例・積分)制御でも、PID(比例・積分・微分)制御でも、任意である。

【0029】

制御対象であるVDCの目標値は任意であるが、VDCにより生成された熱により成膜基板22が昇温したときの温度がその耐熱温度以下で、高周波電圧の振幅よりも大きい値に設定される。

制御対象であるVDCの目標値は必要に応じて適宜設定すればよい。例えば、予め実験などによりVDCの値と、その条件で形成される膜の屈折率及び密着力との相関を求めておき、所望の屈折率、所望の密着力を得るために必要なVDCの目標値を適宜選択して設定するようにすればよい。なお、VDCの目標値は、成膜期間中、一定値である必要はなく、適宜変動させてもよい。

【0030】

次に、真空蒸着装置11により基板上に蒸着を行なう動作を、SiO2膜とNb2O5膜の積層膜を形成する場合を例に説明する。

まず、基板ドーム21に成膜基板22を設置する。続いて、蒸発源には形成する膜に応じた蒸着材料34であるNb2O5を充填した坩堝35aとSiO2を充填した坩堝35bを配置しておく。

【0031】

次に、真空槽30内を図示しない排気系によって10−4Pa程度の高真空領域まで排気する。基板ドーム回転機構23により基板ドーム21を回転させる。また、必要に応じて基板加熱用ヒーター33を用いて成膜基板22を加熱する。

続いて、また、ガス導入口31から真空槽30内にAr,O2等のガスを導入する。ガス流量を安定させ、例えば真空槽30内の圧力を10−2Pa程度の真空状態に維持する。

また、電子銃36から電子ビームを坩堝35a内のNb2O5蒸着材料34へ照射し、蒸着材料34を蒸発温度まで昇温させる。

【0032】

一方、制御回路43は、高周波電源41を起動して、給電部32を介して基板ドーム21に高周波電圧を印加すると共にニュートラライザ38から電子を放出し、プラズマを着火する。また、VDCをNb2O5用の目標値に維持するためのネガティブフィードバックを開始する。

【0033】

基板ドーム21と真空槽30との間に印加された高周波電圧は、ガス導入口31から導入したガスをイオン化し、真空槽30内にプラズマを発生させる。

【0034】

VDC検出回路42のサンプル・ホールド回路は、基板ドーム21の電圧をサンプリングし、A/D変換器により、サンプル値をデジタル化して、制御回路43に供給する。サンプル・ホールド回路のサンプリング期間は、高周波の影響を受けずにVDCを安定して検出できるように、高周波電圧の周期の数倍以上の期間を有することが望ましい。

【0035】

シャッター37を開くと蒸着材料34であるNb2O5は真空槽30内を飛散し、VDCに吸引されたイオンにアシストされて、成膜基板22上に堆積することで緻密なNb2O5薄膜を形成する。

【0036】

この間、制御回路43は、VDC検出回路42の出力データに基づいて、VDCの実測値と基準値との偏差を求め、この偏差を小さくするように、高周波電源41の出力電力を制御し続ける。

【0037】

成膜されたNb2O5膜の膜厚が目標値に到達したらシャッター37を一旦閉じる。

【0038】

続いて、電子銃36から電子ビームを坩堝35b内のSiO2蒸着材料34へ照射し、蒸着材料34を蒸発温度まで昇温させる。また、VDCの目標値をSiO2用の値に切り替える。

【0039】

シャッター37を開くと蒸着材料34であるSiO2は真空槽30内を飛散し、VDCに吸引されたイオンにアシストされて、成膜基板22上に堆積することで緻密な薄膜を形成する。

【0040】

以後、同様の動作を繰り返し、所望の膜厚のNb2O5膜とSiO2膜とを、必要な層数だけ積層する。

成膜処理が終了すると、シャッター37を閉じると共に電子銃36、基板加熱用ヒーター33、高周波電源41、ガスの導入、およびニュートラライザ38などを停止させる。冷却後、真空槽30内に大気を導入した後、薄膜が形成された成膜基板22を取り出す。

【0041】

このような構成によれば、成膜処理中は、フィードバック制御により、図3(b)に示すように、基板ドーム21のVDCが最適な一定レベルに維持される。従って、イオンアシスト効果が1回の処理(1層形成中)中ほぼ一定であり、また、複数回の処理間でもほぼ一定であり、安定して高品質の成膜が可能である。即ち、1バッチ内及びバッチ間で均質な成膜が可能となる。

【0042】

また、従来と異なり、VDCの低下に備えて高周波電源41の出力電力を予め大きくしておく必要が無い。従って、エネルギーロスを抑え、不必要な熱の発生を抑えて、樹脂・アクリルなどの比較的耐熱温度の低い成膜基材22上にも成膜が可能となる。

【0043】

なお、以上の説明においては、制御ループをVDC検出回路42と制御回路43とから構成したが、VDC検出回路42の入力段にローパスフィルタなどを配置してもよい。また、単純な構成により、基板ドーム21の電圧を積分回路(ローパスフィルタ)等を介して電源回路41の電力制御端に供給することにより、電源回路41の電力を制御する等してもよい。

【0044】

その他、この発明は上記実施の形態に限定されず、種々の変形及び応用が可能である。例えば、上記実施の形態においては、理解を容易にするため、高周波電源及びその制御回路を真空槽30の外部に配置したが、一般的に行われているように、基板ドーム22の上部に高周波電源部を収納する等しても良い。

【0045】

また、蒸着材料、ガス種、圧力、温度などは、上記実施の形態で例示したものに限定されず、任意に変更可能である。

【図面の簡単な説明】

【0046】

【図1】本発明の実施の形態に係る真空装置の全体構成図である。

【図2】1バッチで異なる材質の膜を形成する処理を複数バッチ繰り返した場合の、VDCの変化を例示する図である。

【図3】異なる材質の膜を積層する処理を複数バッチ繰り返した場合の、VDCの変化を、従来と本願発明の実施形態とを対比して例示する図である。

【符号の説明】

【0047】

21 基板ドーム

22 成膜基板

23 基板ドーム回転機構

30 真空槽

31 ガス導入口

32 給電部

33 基板加熱用ヒーター

34 蒸着材料

35 坩堝

36 電子銃

37 シャッター

38 ニュートラライザ

39 排気口

41 高周波電源

42 VDC検出回路

43 制御回路

【特許請求の範囲】

【請求項1】

真空槽と、

該真空槽内に配置される電極と、

該電極と真空槽との間に高周波電力を供給し、真空槽内のガスをイオン化するための給電手段と、

高周波電力の印加により前記電極に発生するセルフバイアス電圧を検出し、検出したセルフバイアス電圧に基づいて前記給電手段の出力する高周波電力を制御する制御手段と、

から構成されることを特徴とする真空装置。

【請求項2】

前記制御手段は、前記セルフバイアス電圧が一定になるように、前記給電手段の出力する高周波電力を制御する、

ことを特徴とする請求項1に記載の真空装置。

【請求項3】

成膜対象の基板を搭載する手段と、蒸発源と、を備え、

前記蒸発源からの蒸発粒子の前記基板への付着をイオンによりアシストする、

ことを特徴とする請求項1又は2に記載の真空装置。

【請求項4】

真空槽と該真空槽内に配置される電極との間に高周波電圧を印加して、真空槽内に供給されたガスをイオン化し、該イオンにより蒸発源からの蒸着粒子の基板への付着をアシストして成膜し、

高周波電力の印加により前記真空槽と前記電極との間に発生するセルフバイアス電圧を検出し、

検出したセルフバイアス電圧が一定となるように、高周波電力を制御する、

ことを特徴とする成膜方法。

【請求項1】

真空槽と、

該真空槽内に配置される電極と、

該電極と真空槽との間に高周波電力を供給し、真空槽内のガスをイオン化するための給電手段と、

高周波電力の印加により前記電極に発生するセルフバイアス電圧を検出し、検出したセルフバイアス電圧に基づいて前記給電手段の出力する高周波電力を制御する制御手段と、

から構成されることを特徴とする真空装置。

【請求項2】

前記制御手段は、前記セルフバイアス電圧が一定になるように、前記給電手段の出力する高周波電力を制御する、

ことを特徴とする請求項1に記載の真空装置。

【請求項3】

成膜対象の基板を搭載する手段と、蒸発源と、を備え、

前記蒸発源からの蒸発粒子の前記基板への付着をイオンによりアシストする、

ことを特徴とする請求項1又は2に記載の真空装置。

【請求項4】

真空槽と該真空槽内に配置される電極との間に高周波電圧を印加して、真空槽内に供給されたガスをイオン化し、該イオンにより蒸発源からの蒸着粒子の基板への付着をアシストして成膜し、

高周波電力の印加により前記真空槽と前記電極との間に発生するセルフバイアス電圧を検出し、

検出したセルフバイアス電圧が一定となるように、高周波電力を制御する、

ことを特徴とする成膜方法。

【図1】

【図2】

【図3】

【図2】

【図3】

【公開番号】特開2007−204799(P2007−204799A)

【公開日】平成19年8月16日(2007.8.16)

【国際特許分類】

【出願番号】特願2006−23397(P2006−23397)

【出願日】平成18年1月31日(2006.1.31)

【出願人】(000146009)株式会社昭和真空 (72)

【Fターム(参考)】

【公開日】平成19年8月16日(2007.8.16)

【国際特許分類】

【出願日】平成18年1月31日(2006.1.31)

【出願人】(000146009)株式会社昭和真空 (72)

【Fターム(参考)】

[ Back to top ]