瞬時に同期を確立しかつ保持できる同期発振器

【課題】瞬時に同期を確立し、比較的に長時間、同期状態を高精度で保持することができる同期発振器を安価に実現する。

【解決手段】少なくとも、セットもしくはリセット付きカウンタ22と同期検出手段24とから構成され、前記同期検出手段24において、同期入力信号の立上り点、立下り点、もしくはゼロ交差点のタイミングを検出し、前記タイミングにおいて、前記カウンタ22をセットしあるいはリセットすることで、同期入力信号と瞬時に同期を確立し、前記同期入力信号が休止しあるいは停止した場合、あるいは取去られた後にも、比較的に長時間、同期状態を高精度で保持することができる。

【解決手段】少なくとも、セットもしくはリセット付きカウンタ22と同期検出手段24とから構成され、前記同期検出手段24において、同期入力信号の立上り点、立下り点、もしくはゼロ交差点のタイミングを検出し、前記タイミングにおいて、前記カウンタ22をセットしあるいはリセットすることで、同期入力信号と瞬時に同期を確立し、前記同期入力信号が休止しあるいは停止した場合、あるいは取去られた後にも、比較的に長時間、同期状態を高精度で保持することができる。

【発明の詳細な説明】

【技術分野】

【0001】

この発明は、瞬時に同期を確立し、かつ比較的に長時間同期を保持しあるいは維持できる同期発振器に関するものである。

【背景技術】

【0002】

従来から、同期を確立しかつ保持できる同期発振器が提案されている。(例えば、特許文献1から3参照)

【特許文献1】特開2008−278479号

【特許文献2】特開2009−100061号

【特許文献3】特開2009−210372号

【0003】

図7は、特許文献1に示す、従来の「デジタルシンセサイザ」の実施例である。図7において、10はデジタルシンセサイザ、11はデジタル位相比較器、12は数値制御発振器(NCO)、13は分周器、14は入力端子、15は出力端子である。

数値制御発振器12はデジタル位相比較器11から出力される制御信号に応じて発振周波数が変化し、その同期出力信号が分周器13によってN分周され、位相比較器11の一方の端子に入力される。

【0004】

外部からの同期入力信号が入力端子14に加えられると、前記位相比較器11によって分周器13の出力信号と位相が比較され、両者間の位相差に応じて制御信号が変化し、前記制御信号に応じて、前記数値制御発振器12の発振周波数を制御する。

【0005】

前記数値制御発振器12の発振周波数が前記同期入力信号の周波数より高い場合には、前記数値制御発振器12の発振周波数を下げるように働き、逆の場合には発振周波数を高めるように働き、前記数値制御発振器12の発振周波数が前記同期入力信号の周波数が等しい場合に同期を確立し、前記制御信号をホールドして同期を維持して、前記数値制御発振器12から出力される同期出力信号が、接続端子14を介して外部に出力される。

【0006】

前記の従来の技術では、前記位相比較器11によって位相を比較しているため、同期の確立までに時間を要し、同期を確立した時点での前記数値制御発振器12から出力される同期出力信号と前記同期入力信号との間の残留位相誤差もしくは同期確立誤差が存在し、前記残留位相誤差が不安定となるなどの問題点がある。

【0007】

特許文献2に記載されている従来の「相対距離測定機能を有するユビキタスモバイルネットワーク」では、(請求項1)において「同期発振器」を設けることが述べられているが、具体的な構成についての記述がされていない問題点がある。

【0008】

特許文献3に記載されている従来の「距離測定装置」では、前記の特許文献1に記載されている「デジタルシンセサイザ」が適用されており、特許文献1と同様な問題点がある。

【発明の開示】

【発明が解決しようとする課題】

【0009】

この発明は、従来の位相同期発振器(PLL)、もしくは注入同期発振器では、同期入力信号の入力が休止しあるいは停止している期間が存在すると、同期を保持できない問題点を解決するためになされたものであり、同期入力信号と瞬時に同期を確立し、同期入力信号が休止しあるいは停止した場合でも、高精度で安定に同期を保持できる同期発振器を提供することを目的とする。

【課題を解決するための手段】

【0010】

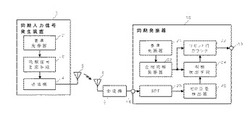

この発明に係わる「瞬時に同期を確立しかつ保持できる同期発振器」では、図1に示すように、受信機7によって同期入力信号が復調され、帯域通過フイルタ25によって不要な雑音が除去された後、ゼロ交差検出器26によってデジタル信号に変換される。一方、周波数安定度の高い基準発振器21によって生成されるクロック信号を、直接サンプリング信号とし、あるいは位相同期発振器23によって周波数の高いサンプリング信号に変換し、前記サンプリング信号を用いて、前記デジタル信号をサンプリングし、前記同期入力信号の立上り点、立下り点、もしくはゼロ交差点のタイミングを検出する。

【0011】

前記検出したタイミングで、前記基準発振器21の出力信号を直接もしくは周波数を変換してクロック信号とし、あるいは位相同期発振器もしくは逓倍器によって高い周波数に変換してクロック信号とし、前記クロック信号によって駆動されるセットもしくはリセット付きのカウンタ22を、セットしあるいはリセットすることで、前記セットもしくはリセット付きのカウンタが、前記同期入力信号と瞬時に同期を確立し、前記同期入力信号が休止しあるいは停止した後も比較的に長時間、高精度な同期を保持しあるいは維持できることによって、前記同期発振器を安価に実現できる。なお、図1に示すように無線回線によって接続することは必須条件ではなく、有線回線によって接続しても同様な効果が得られる。

【発明の効果】

【0012】

従来の同期が保持できる同期発振器では、デジタル化された位相比較器が採用されているが、その出力信号はアナログ信号であり、前記アナログ信号をアナログデジタル変換器でデジタル信号に変換して制御信号とし、前記制御信号によって数値制御発振器(NCO)のレジスタの設定値を、加算もしくは減算して周波数を制御しているため、短時間に同期を確立することが難しく、しかも同期確立精度も低いことから、同期入力信号が休止しあるいは停止した場合に、同期状態を安定にかつ高精度で保持することが難しい問題点があった。

【0013】

これに対して本発明の同期発振器では、同期入力信号の立上り点、立下り点、もしくはゼロ交差点のタイミングで、セットもしくはリセット付きのカウンタをセットしあるいはリセットすることで、前記セットもしくはリセット付きのカウンタが、瞬時に同期を確立でき、しかも同期入力信号が休止しあるいは停止した場合にも、同期状態を安定にかつ高精度で保持できる他、回路を集積回路内に、安価に構成できるメリットが得られる。

【発明を実施するための最良の形態】

【0014】

この発明に係わる同期発振器は、図1および請求項1に本発明の第1の実施の形態を示すように、無線回線もしくは有線回線を通じて伝送される同期入力信号と瞬時に同期を確立し、かつ比較的に長時間同期を保持するための同期発振器10において、前記同期発振器10が、少なくとも、発振周波数が高安定である基準発振器21と、前記基準発振器21の出力信号を直接もしくは周波数を変換してサンプリング信号とし、同期入力信号の立上り点、立下り点、もしくはゼロ交差点のタイミングを検出するための同期検出手段24と、前記基準発振器21の出力信号を直接もしくは周波数を変換してクロック信号とし、前記クロック信号によって駆動されるセットもしくはリセット付きのカウンタもしくは数値制御発振器22とから構成され、

【0015】

前記同期検出手段24が、検出したタイミングにおいて、前記カウンタもしくは数値制御発振器をセットしあるいはリセットして瞬時に同期を確立し、前記セットもしくはリセット付きのカウンタもしくは数値制御発振器が、前記同期入力信号が休止しあるいは停止している間も、高精度で比較的に長時間同期を保持しあるいは維持できる。

【0016】

また、図3および請求項2に示すように、前記同期入力信号に同期確立誤差関数を付与するために、前記同期入力信号の立上り点、立下り点、もしくはゼロ交差点のタイミングを検出するために用いるサンプリング信号の位相を、複数組の移相手段52a〜52nを設けて異なった位相にシフトさせ、前記位相をシフトさせた複数組のサンプリング信号を、切替制御手段53によって順次にあるいは周期的に切替えて出力する。

【0017】

また、請求項3に示すように、前記同期入力信号に同期確立誤差関数を付与するために、前記同期入力信号の位相を、複数組の移相手段52a〜52nを設けて異なった位相にシフトさせ、前記位相をシフトさせた複数組の同期入力信号を、切替制御手段53によって順次にあるいは周期的に切替えて出力する。

【0018】

また、図4および請求項4に示すように、前記同期入力信号に同期確立誤差関数を付与するために、同期入力信号発生装置1側と同期発振器10側とを無線回線で接続し、前記同期入力信号発生装置1側、同期発振器10側、もしくはこれらの両方に、複数のアンテナ又は送受波器6a、6bを設け、アンテナ切替器61によって、順次にあるいは周期的に切替えて出力する。

【0019】

また、図5および請求項5に示すように、前記同期確立誤差関数を付与するのに対応して、複数組のセットもしくはリセット付きカウンタもしくは数値制御発振器72a〜72nを設け、前記同期入力信号が入力される間は、前記同期確立誤差関数を付与する側の切替制御手段53もしくはアンテナ切替器61を切替えるタイミングに合わせて、前記複数組のカウンタもしくは数値制御発振器72a〜72nを切替え、前記複数組のカウンタもしくは数値制御発振器を順次にあるいは周期的にセットしあるいはリセットして瞬時に同期を確立し、前記同期入力信号が休止しあるいは停止している間は、前記複数組のカウンタもしくは数値制御発振器72a〜72nの動作を継続して比較的に長時間同期を保持しあるいは維持し、前記複数組のカウンタ72a〜72nの出力信号を順次にあるいは周期的に切替えて出力する。

【0020】

また、請求項6に示すように、前記位相シフトの合計が、前記サンプリング信号の1周期の長さ以上であるものとする。

また、請求項7に示すように、前記同期発振器10に入力される同期入力信号、前記同期発振器10から出力される同期出力信号、あるいはこれらの両方を、伝達位相誤差、中心周波数偏差、群遅延歪み、もしくはこれらの組合せが少ないかあるいは少なく微調整が可能な帯域通過フイルタに通し、前記同期出力信号に含まれるジッタ雑音を軽減する。

【0021】

また、請求項8に示すように、前記同期入力信号が間欠発信でなく連続して発信される場合でも、同期入力信号に、直接もしくは間接に、同期確立誤差関数を付与することによって、瞬断もしくは多重伝搬が発生する有線回線もしくは無線回線にも適用できる。

また、請求項9に示すように、前記基準発振器の出力信号を、位相同期発振器もしくは逓倍器を用いて、前記同期入力信号の10倍以上の周波数に変換し、前記クロック信号、サンプリング信号、もしくはこれらの両方として用いる。

【0022】

(実施の形態1)

図1は本発明の第1の実施の形態による同期発振器の構成図である。図1において、1は同期入力信号発生装置、2は基準発振器、3は同期入力信号生成手段、4は送信機、5、6はアンテナ又は送受波器、7は受信機、10は同期発振器、14は同期入力端子、15は同期出力端子、21は基準発振器、22はセットもしくはリセット付きのカウンタ、23は位相同期発振器、24は同期検出手段、25は帯域通過フイルタ、26はゼロ交差検出器もしくはコンパレータである。

【0023】

送信機4に接続されたアンテナ又は送受波器5と、受信機7に接続されたアンテナ又は送受波器6とは、お互いに離れた場所に設置されており、無線回線によって接続されている。前記同期入力信号生成手段3では、基準発振器2から供給されるクロック信号と同期しもしくは直交した同期入力信号を生成し、送信機4によって変調して増幅し、アンテナ又は送受波器5を介し、バースト状の無線信号として、空間へ間欠発信される。

【0024】

前記空間へ間欠発信された無線信号がアンテナ又は送受波器6で受信され、受信機7によって復調された同期入力信号は、同期入力端子14を介して、帯域通過フイルタ25によって不要な高調波と雑音が除去された後、ゼロ交差検出器26によってデジタル信号に変換され、一方、基準発振器21によって生成されるクロック信号を、直接もしくは位相同期発振器もしくは逓倍器23によって高い周波数のサンプリング信号に変換し、前記サンプリング信号を同期検出器24に供給して、ゼロ交差検出器26の出力信号をサンプリングし、前記同期入力信号の立上り点、立下り点、もしくはゼロ交差点のタイミングを検出する。

【0025】

前記検出されたタイミングにおいて、前記セットもしくはリセット付きカウンタ22を複数回、例えば3回程度、セットしあるいはリセットすることで、瞬時に、例えば3マイクロ秒で、同期を確立し、同期入力信号が休止しあるいは停止した場合、あるいは取去られた場合にも、比較的に長時間、同期状態を高精度でしかも高安定に保持しあるいは維持できる。

なお、前記セットもしくはリセット付きカウンタ22は、前記基準発振器21の出力信号を、直接、あるいは位相同期発振器もしくは逓倍器23を用いて高い周波数に変換してクロック信号とし、前記クロック信号によって駆動されているものとする。

【0026】

また、前記基準発振器21の発振周波数は、前記同期入力信号の周波数に比較して、整数倍であることが必須であり、両者間の周波数偏差は±1ppm程度以内であり、可能な限り少ないことが望ましい。

また、前記同期入力信号の周波数が1MHzの場合、セットもしくはリセットを3回継続することで、3マイクロ秒以内に、確実に同期を確立させることができる。

【0027】

図2は本発明の第1の実施の形態による同期発振器の動作説明図である。図2において、31は同期入力信号、32は同期入力信号のゼロ交差信号、33はサンプリング信号、34a、34bはセットもしくはリセット信号、35a〜35dは同期発振器から出力される同期出力信号、36a、36bは同期確立誤差、37は同期入力信号の時間軸、38はゼロ交差信号の時間軸、39はサンプリング信号の時間軸、40はセットもしくはリセット信号の時間軸、41は同期出力信号の時間軸である。

前記セットもしくはリセット信号34a、34bは数ビットが割付けられるので、同期確立に要する時間は前記ビット数に比例することとなる。

【0028】

ここで、同期確立以前には、ゼロ交差信号32の位相とサンプリング信号33の位相との間には同期誤差36aが存在するのに対して、前記同期入力信号31の立上り点、立下り点、もしくはゼロ交差点のタイミングを検出し、前記検出したタイミングでカウンタをリセットすると、最大で前記サンプリング信号33のパルス間隔分の同期検出誤差36bを生じ、従って、前記サンプリング信号33のパルス間隔分の同期確立誤差36bが発生する。前記サンプリング信号33のパルス間隔をΔtとすると、同期確立誤差の変動幅は±Δt/2で表わされる。

【0029】

高精度でしかも短時間で同期を確立し、かつ比較的に長時間同期を保持しあるいは維持する技術を確立するためには、(1)同期入力信号31の立上り点、立下り点、もしくはゼロ交差点を高精度で検出できること、(2)前記検出したタイミングで同期発振器と瞬時に同期を確立できること、(3)前記同期入力信号31が休止しあるいは停止した後も、前記同期発振器が安定に同期を保持しあるいは維持できること、などが必須の条件となる。

【0030】

(1)のためには、同期入力信号31の立ち上り、立下り、もしくはゼロ交差点を検出するために、サンプリング信号33の周波数を、同期入力信号31の周波数の10倍以上の高い周波数に設定する必要がある。例えば、サンプリング信号の周波数が256MHzの場合、同期入力信号の立ち上りもしくは立下りの検出誤差の変動幅は±2ナノ秒となる。

【0031】

(2)のためには、同期入力信号31の立ち上り点、立下り点、もしくはゼロ交差点を検出したタイミングで、セットもしくはリセット付きのカウンタを、複数回セットしあるいはリセットすることで実現できる。前記セットもしくはリセット付きのカウンタは、高安定水晶発振器21の出力信号を、直接、あるいは位相同期発振器もしくは逓倍器23の出力信号をクロック信号とし、前記クロック信号33をカウントダウンして、同期入力信号31と同期しあるいは直交する同期出力信号35a〜35dを生成する。

【0032】

(3)のためには、セットもしくはリセット付きのカウンタを採用すると、リセット信号が休止しあるいは停止した後も引続き同期発振が継続し、前記同期入力信号31の周波数と、前記基準発振器21の発振周波数との間の周波数偏差内で同期を保持しあるいは維持できる。

【0033】

なお、同期入力信号31に同期確立誤差関数を付与するために、前記同期入力信号、前記同期入力信号の立上り点、立下り点、あるいはゼロ交差点を検出するためのサンプリング信号、もしくはこれらの両方の信号の位相を複数組の移相手段を設け、切替制御手段によって順次選択して出力することで、前記同期確立誤差を軽減することができる。

また、前記同期入力信号が、間欠発信でなく連続して発信される場合でも、同期入力信号に、直接もしくは間接に、同期確立誤差関数を付与することによって、瞬断もしくは多重伝搬が発生する有線回線もしくは無線回線にも、安価なコストで適用できる。

【0034】

(実施の形態2)

図6は、本発明の第2の実施の形態による同期発振器の構成図である。図6において、22はセットもしくはリセット付きの数値制御発振器、81は加算器、82はルックアップテーブル、83はデジタルアナログ変換器、84は帯域通過フイルタ、85はゼロ交差検出器、74はクロック信号の入力端子、76はセットもしくはリセット端子、75は出力端子である。

【0035】

前記数値制御発振器22は、前記同期発振器10のセットもしくはリセット付きのカウンタ22の代替えとなるものであり、加算器81のレジスタは、前記同期入力信号と同期しあるいは直交する同期出力信号の周波数を生成するようにプログラムされており、入力端子74に入力されるクロック信号によって順次加算が繰返され、ルックアップテーブル82によって振幅の変化もしくは位相の変換に置換えられ、デジタルアナログ変換器83によってアナログ信号に変換され、帯域通過フイルタ84によって不要な周波数成分が除去され、コンパレータ85によってデジタル信号に変換されて、出力端子75からデジタル信号として出力される。

【0036】

セットもしくはリセット端子76に、セットもしくはリセット信号が入力されると、前記数値制御発振器22は中性点(ゼロ交差点)を出力するものとすると、前記セットもしくはリセット信号が取り除かれると、前記同期入力信号の立上り、立下り、もしくはゼロ交差点に同期した同期出力信号が、出力端子75から出力される。

【0037】

図3は、本発明の同期確立誤差関数生成手段の構成図である。図3において、21は基準発振器、23は位相同期発振器、27は同期確立誤差関数生成手段、51は複数段の移相手段、52a〜52nは移相手段51の切替タップ、53は切替制御手段、54はサンプリング信号の入力端子、55はクロック信号入力端子、56はサンプリング信号出力端子である。

同期確立誤差関数生成手段27は、少なくとも、移相相手段51と、切替タッブ52a〜52nと、切替制御手段53とから構成される。

【0038】

前記位相同期発振器23から出力されるサンプリング信号は、周波数が同期入力信号の周波数の10倍以上の十分に高い周波数であり、例えば256MHzもしくはそれ以上の周波数であり、移相手段51に接続される。前記移相手段51は、複数段のシフトレジスタ、複数段の遅延素子、もしくは複数段の遅延回路などによって構成され、各段の信号出力は切替タップ52a〜52nによって引き出され、切替制御手段53によって順次選択され、サンプリング信号出力端子56から外部に出力される。

【0039】

前記移相手段51の各段の移相量は極力小さいことが望ましく、かつ移相量の合計は、前記サンプリング信号のパルス間隔Δt以上であることが必要である。例えば、前記サンプリング信号の周波数が256MHzであるとすると、前記移相手段51の各段の移相量は4ナノ秒以下であり、かつ移相量の合計は4ナノ秒以上とする必要がある。ここで、前記切替タップの数を16とし、前記バースト信号の長さを0.5msとすると、前記切替制御手段53は、1ステップ当り32μsの速さでタップを切替えることになる。

【0040】

従って、前記1ステップ当りの切替時間32μsの10分の1、すなわち3μs程度で同期を確立する必要がある。

なお、前記同期確立誤差関数生成手段27は、ある種のシステムに適用する場合には、前記同期入力信号生成手段3の出力端子、あるいは前記ゼロ交差検出器26の出力端子に接続しても同様な効果が得られる。

【0041】

また、前記移相手段51の複数段のタップ52a〜52n毎に生じる同期確立誤差の合計を、同期確立誤差関数として表現すれば、同期確立誤差関数は多項式によって表現でき、前記多項式は、0もしくは一定値に収斂することが望ましい。

【0042】

図4は、本発明の同期確立誤差関数生成手段の他の構成図である。図4において、27は同期確立誤差関数生成手段、25は受信機、6a、6bは複数のアンテナ又は送受波器、61はアンテナ切替器、14は受信機の出力端子である。

複数のアンテナ又は送受波器6aと6bとはお互いに4分1波長以上離れて設置されており、両者をアンテナ切替器61を用いて順次にあるいは周期的に切替えながら無線信号を受信し、受信機25によって同期入力信号を復調すると、無線区間で生じる伝搬経路長の差もしくは多重伝搬等の影響で、両者の間で復調した同期入力信号の位相が異なり、両者間の相関性も小さいことが分かっている。

【0043】

そこで、前記アンテナ切替器61を、前記バースト信号として受信する間に、順次にあるいは周期的に切替えることで、図3に示す同期確立誤差関数生成手段27と同様な効果が得られることになる。

なお、前記アンテナ又は送受波器の数は、2基以上であれば多いほど、無線区間で生じる多重伝搬による同期誤差関数の付与効果が大きくなる。

【0044】

図5は、本明の同期確立誤差関数生成手段の他の構成図である。図5において、22はリセット付きカウンタ、71、73は切替制御手段、72a〜72nは複数組のカウンタもしくは数値制御発振器、74はセットもしくはリセット信号接続端子、75は出力端子、76はクロック信号入力端子である。

カウンタもしくは数値制御発振器22のセットもしくはリセット信号の入力端子74には、前記同期入力信号がバースト信号として受信される間、前記同期検出手段24によって、同期入力信号の立ち上り、立下り、もしくはゼロ交差点のタイミングが検出されて、タイミング信号として入力される。

【0045】

そこで、図3、図4における前記同期確立誤差関数を付与する側の切替制御手段53もしくはアンテナスイッチ61を切替えるタイミングに同期して、図5の切替制御手段71を順次にあるいは周期的に切替え、前記同期入力信号が休止しあるいは停止している期間中、あるいは必要な期間中には、前記切替制御手段71を開放して同期を保持しあるいは維持し、前記切替制御手段73によって順次にあるいは周期的に切替え、出力端子75から同期出力信号を出力する。

【0046】

一方、前記カウンタもしくは数値制御発振器22のクロック信号入力端子76には、前記基準発振器21からクロック信号が直接もしくは周波数変換されて供給されているので、前記セットもしくはリセット信号のタイミングに同期して、通常、低い周波数へカウントダウンが開始され、同期が確立する。

また、前記切替制御手段73もしくはアンテナ切替器61の切替えは、順序を決めて順番に行なうか、周期的に行なうか、ランダムに行なうか、あるいは任意の方法かのいずれかを選択する。

【0047】

ここで、前記同期入力発生装置1の基準発振器2と、前記同期発振器10の基準発振器21とは、発振周波数偏差が±1ppm以内に保たれていると、両者の位相関係は前記バースト信号の期間中ほぼ一定に保たれ、従って、前記同期検出手段24によって検出されるセットもしくはリセット信号のタイミングも一定に保たれ、従って、同期確立誤差も一定に保たれてしまう問題点がある。

【0048】

そこで、前記同期確立誤差関数を付与すると、前記同期確立誤差がジッタ雑音に変換されるので、何らかの方法で平準化することで、同期確立誤差を軽減できることになる。平準化する方法として、前記同期発振器10に入力される同期入力信号、前記同期発振器10から出力される同期出力信号、あるいはこれらの両方を、伝達位相誤差、中心周波数偏差、群遅延歪み、もしくはこれらの組合せが少ないかあるいは少なく微調整が可能な帯域通過フイルタを通して平準化すれば、前記ジッタ雑音が軽減されるので、従って同期確立誤差を軽減することができる。なお、平準化された同期出力信号はアナログ信号なので、ゼロ交差検出器を用いてデジタル信号に変換できる。

【0049】

以上の説明では、セットもしくはリセット付きのカウンタもしくは数値制御発振器を用いる場合について述べたが、同様な機能を有する発振器を用いることでも、前記同期発振器を容易に構成することができる。

また、前記同期入力信号には、有線回線で伝送された信号、無線信号を復調した信号、連続的な信号、あるいは単一周波数であるいかなる種類の同期入力信号をも含めることができる。

また、前記同期発振器の用途によっては、同期入力信号を生成する側に、前記移相手段を設け、複数組の位相シフトを付与することでも同様な効果が得られる。

【0050】

また、同期確立誤差関数を付与する他の方法として、前記同期入力信号発生装置と同期発振器側との間を無線回線で接続している場合、前記同期入力信号発生装置側、同期発振器側、もしくはこれらの両方に、複数のアンテナ又は送受波器、およびアンテナ切替器を設け、前記同期発振器のカウンタに設けた切替制御手段の切替えタイミングに合わせて、前記複数のアンテナ又は送受波器を周期的に切替えることが有効である。

また、無線信号として、超音波信号、高周波信号、もしくは光信号が用いられ、超音波信号と光信号とは、送受波器を用いて発受信されるものとする。

【産業上の利用可能性】

【0051】

本発明は、上記のように構成されているため、通信システムにおいて同じ周波数であり、同じ位相であり、あるいはこれらの両方が必須である、同期入力信号と同期出力信号との間の同期を、数マイクロ秒以内の瞬時にしかも高い精度で確立し、前記同期入力信号が休止し、停止し、消滅し、あるいは取去られた場合にも、同期出力信号が同期状態を高い精度で保持しあるいは維持する必要がある分野において、広く利用できる基盤技術に関するものである。

【0052】

具体的には、時分割同時送受話方式の無線装置間で相互間の距離を測定する分野において、距離を測定する側の装置、距離を測定される側の装置、前記2つの装置以外で無線信号を中継する装置、あるいはこれらの組み合わせから、無線信号に含まれて発信されあるいは受信される同期入力信号と、同期して出力される同期出力信号とを、高い精度で瞬時に同期を確立させかつ比較的に長時間同期を保持させるために用いることができる。

また、複数の無線装置の間でアドホックネットワークを瞬時に構成する必要がある場合に、相互間の距離を瞬時に測定するために用いることができる。

【図面の簡単な説明】

【0053】

【図1】本発明の第1の実施の形態による同期発振器の構成図

【図2】本発明の第1の実施の形態による同期発振器の動作説明図

【図3】本発明の同期確立誤差関数生成手段の構成図

【図4】本発明の同期確立誤差関数生成手段の他の構成図

【図5】本発明の同期確立誤差関数生成手段の他の構成図

【図6】本発明の第2の実施の形態による同期発振器の構成図

【図7】従来の実施例を示す構成図

【符号の説明】

【0054】

1 同期入力信号発生装置

2 基準発振器

3 同期入力信号生成手段

4 送信機

5、6、6a、6b アンテナ又は送受波器

7 受信機

10 同期発振器

21 基準発振器

22 セットもしくはリセット付きカウンタ

23 位相同期発振器

24 位相同期検出手段

25 帯域通過フイルタ

26 ゼロ交差検出器もしくはコンパレータ

27 同期確立誤差関数生成手段

【技術分野】

【0001】

この発明は、瞬時に同期を確立し、かつ比較的に長時間同期を保持しあるいは維持できる同期発振器に関するものである。

【背景技術】

【0002】

従来から、同期を確立しかつ保持できる同期発振器が提案されている。(例えば、特許文献1から3参照)

【特許文献1】特開2008−278479号

【特許文献2】特開2009−100061号

【特許文献3】特開2009−210372号

【0003】

図7は、特許文献1に示す、従来の「デジタルシンセサイザ」の実施例である。図7において、10はデジタルシンセサイザ、11はデジタル位相比較器、12は数値制御発振器(NCO)、13は分周器、14は入力端子、15は出力端子である。

数値制御発振器12はデジタル位相比較器11から出力される制御信号に応じて発振周波数が変化し、その同期出力信号が分周器13によってN分周され、位相比較器11の一方の端子に入力される。

【0004】

外部からの同期入力信号が入力端子14に加えられると、前記位相比較器11によって分周器13の出力信号と位相が比較され、両者間の位相差に応じて制御信号が変化し、前記制御信号に応じて、前記数値制御発振器12の発振周波数を制御する。

【0005】

前記数値制御発振器12の発振周波数が前記同期入力信号の周波数より高い場合には、前記数値制御発振器12の発振周波数を下げるように働き、逆の場合には発振周波数を高めるように働き、前記数値制御発振器12の発振周波数が前記同期入力信号の周波数が等しい場合に同期を確立し、前記制御信号をホールドして同期を維持して、前記数値制御発振器12から出力される同期出力信号が、接続端子14を介して外部に出力される。

【0006】

前記の従来の技術では、前記位相比較器11によって位相を比較しているため、同期の確立までに時間を要し、同期を確立した時点での前記数値制御発振器12から出力される同期出力信号と前記同期入力信号との間の残留位相誤差もしくは同期確立誤差が存在し、前記残留位相誤差が不安定となるなどの問題点がある。

【0007】

特許文献2に記載されている従来の「相対距離測定機能を有するユビキタスモバイルネットワーク」では、(請求項1)において「同期発振器」を設けることが述べられているが、具体的な構成についての記述がされていない問題点がある。

【0008】

特許文献3に記載されている従来の「距離測定装置」では、前記の特許文献1に記載されている「デジタルシンセサイザ」が適用されており、特許文献1と同様な問題点がある。

【発明の開示】

【発明が解決しようとする課題】

【0009】

この発明は、従来の位相同期発振器(PLL)、もしくは注入同期発振器では、同期入力信号の入力が休止しあるいは停止している期間が存在すると、同期を保持できない問題点を解決するためになされたものであり、同期入力信号と瞬時に同期を確立し、同期入力信号が休止しあるいは停止した場合でも、高精度で安定に同期を保持できる同期発振器を提供することを目的とする。

【課題を解決するための手段】

【0010】

この発明に係わる「瞬時に同期を確立しかつ保持できる同期発振器」では、図1に示すように、受信機7によって同期入力信号が復調され、帯域通過フイルタ25によって不要な雑音が除去された後、ゼロ交差検出器26によってデジタル信号に変換される。一方、周波数安定度の高い基準発振器21によって生成されるクロック信号を、直接サンプリング信号とし、あるいは位相同期発振器23によって周波数の高いサンプリング信号に変換し、前記サンプリング信号を用いて、前記デジタル信号をサンプリングし、前記同期入力信号の立上り点、立下り点、もしくはゼロ交差点のタイミングを検出する。

【0011】

前記検出したタイミングで、前記基準発振器21の出力信号を直接もしくは周波数を変換してクロック信号とし、あるいは位相同期発振器もしくは逓倍器によって高い周波数に変換してクロック信号とし、前記クロック信号によって駆動されるセットもしくはリセット付きのカウンタ22を、セットしあるいはリセットすることで、前記セットもしくはリセット付きのカウンタが、前記同期入力信号と瞬時に同期を確立し、前記同期入力信号が休止しあるいは停止した後も比較的に長時間、高精度な同期を保持しあるいは維持できることによって、前記同期発振器を安価に実現できる。なお、図1に示すように無線回線によって接続することは必須条件ではなく、有線回線によって接続しても同様な効果が得られる。

【発明の効果】

【0012】

従来の同期が保持できる同期発振器では、デジタル化された位相比較器が採用されているが、その出力信号はアナログ信号であり、前記アナログ信号をアナログデジタル変換器でデジタル信号に変換して制御信号とし、前記制御信号によって数値制御発振器(NCO)のレジスタの設定値を、加算もしくは減算して周波数を制御しているため、短時間に同期を確立することが難しく、しかも同期確立精度も低いことから、同期入力信号が休止しあるいは停止した場合に、同期状態を安定にかつ高精度で保持することが難しい問題点があった。

【0013】

これに対して本発明の同期発振器では、同期入力信号の立上り点、立下り点、もしくはゼロ交差点のタイミングで、セットもしくはリセット付きのカウンタをセットしあるいはリセットすることで、前記セットもしくはリセット付きのカウンタが、瞬時に同期を確立でき、しかも同期入力信号が休止しあるいは停止した場合にも、同期状態を安定にかつ高精度で保持できる他、回路を集積回路内に、安価に構成できるメリットが得られる。

【発明を実施するための最良の形態】

【0014】

この発明に係わる同期発振器は、図1および請求項1に本発明の第1の実施の形態を示すように、無線回線もしくは有線回線を通じて伝送される同期入力信号と瞬時に同期を確立し、かつ比較的に長時間同期を保持するための同期発振器10において、前記同期発振器10が、少なくとも、発振周波数が高安定である基準発振器21と、前記基準発振器21の出力信号を直接もしくは周波数を変換してサンプリング信号とし、同期入力信号の立上り点、立下り点、もしくはゼロ交差点のタイミングを検出するための同期検出手段24と、前記基準発振器21の出力信号を直接もしくは周波数を変換してクロック信号とし、前記クロック信号によって駆動されるセットもしくはリセット付きのカウンタもしくは数値制御発振器22とから構成され、

【0015】

前記同期検出手段24が、検出したタイミングにおいて、前記カウンタもしくは数値制御発振器をセットしあるいはリセットして瞬時に同期を確立し、前記セットもしくはリセット付きのカウンタもしくは数値制御発振器が、前記同期入力信号が休止しあるいは停止している間も、高精度で比較的に長時間同期を保持しあるいは維持できる。

【0016】

また、図3および請求項2に示すように、前記同期入力信号に同期確立誤差関数を付与するために、前記同期入力信号の立上り点、立下り点、もしくはゼロ交差点のタイミングを検出するために用いるサンプリング信号の位相を、複数組の移相手段52a〜52nを設けて異なった位相にシフトさせ、前記位相をシフトさせた複数組のサンプリング信号を、切替制御手段53によって順次にあるいは周期的に切替えて出力する。

【0017】

また、請求項3に示すように、前記同期入力信号に同期確立誤差関数を付与するために、前記同期入力信号の位相を、複数組の移相手段52a〜52nを設けて異なった位相にシフトさせ、前記位相をシフトさせた複数組の同期入力信号を、切替制御手段53によって順次にあるいは周期的に切替えて出力する。

【0018】

また、図4および請求項4に示すように、前記同期入力信号に同期確立誤差関数を付与するために、同期入力信号発生装置1側と同期発振器10側とを無線回線で接続し、前記同期入力信号発生装置1側、同期発振器10側、もしくはこれらの両方に、複数のアンテナ又は送受波器6a、6bを設け、アンテナ切替器61によって、順次にあるいは周期的に切替えて出力する。

【0019】

また、図5および請求項5に示すように、前記同期確立誤差関数を付与するのに対応して、複数組のセットもしくはリセット付きカウンタもしくは数値制御発振器72a〜72nを設け、前記同期入力信号が入力される間は、前記同期確立誤差関数を付与する側の切替制御手段53もしくはアンテナ切替器61を切替えるタイミングに合わせて、前記複数組のカウンタもしくは数値制御発振器72a〜72nを切替え、前記複数組のカウンタもしくは数値制御発振器を順次にあるいは周期的にセットしあるいはリセットして瞬時に同期を確立し、前記同期入力信号が休止しあるいは停止している間は、前記複数組のカウンタもしくは数値制御発振器72a〜72nの動作を継続して比較的に長時間同期を保持しあるいは維持し、前記複数組のカウンタ72a〜72nの出力信号を順次にあるいは周期的に切替えて出力する。

【0020】

また、請求項6に示すように、前記位相シフトの合計が、前記サンプリング信号の1周期の長さ以上であるものとする。

また、請求項7に示すように、前記同期発振器10に入力される同期入力信号、前記同期発振器10から出力される同期出力信号、あるいはこれらの両方を、伝達位相誤差、中心周波数偏差、群遅延歪み、もしくはこれらの組合せが少ないかあるいは少なく微調整が可能な帯域通過フイルタに通し、前記同期出力信号に含まれるジッタ雑音を軽減する。

【0021】

また、請求項8に示すように、前記同期入力信号が間欠発信でなく連続して発信される場合でも、同期入力信号に、直接もしくは間接に、同期確立誤差関数を付与することによって、瞬断もしくは多重伝搬が発生する有線回線もしくは無線回線にも適用できる。

また、請求項9に示すように、前記基準発振器の出力信号を、位相同期発振器もしくは逓倍器を用いて、前記同期入力信号の10倍以上の周波数に変換し、前記クロック信号、サンプリング信号、もしくはこれらの両方として用いる。

【0022】

(実施の形態1)

図1は本発明の第1の実施の形態による同期発振器の構成図である。図1において、1は同期入力信号発生装置、2は基準発振器、3は同期入力信号生成手段、4は送信機、5、6はアンテナ又は送受波器、7は受信機、10は同期発振器、14は同期入力端子、15は同期出力端子、21は基準発振器、22はセットもしくはリセット付きのカウンタ、23は位相同期発振器、24は同期検出手段、25は帯域通過フイルタ、26はゼロ交差検出器もしくはコンパレータである。

【0023】

送信機4に接続されたアンテナ又は送受波器5と、受信機7に接続されたアンテナ又は送受波器6とは、お互いに離れた場所に設置されており、無線回線によって接続されている。前記同期入力信号生成手段3では、基準発振器2から供給されるクロック信号と同期しもしくは直交した同期入力信号を生成し、送信機4によって変調して増幅し、アンテナ又は送受波器5を介し、バースト状の無線信号として、空間へ間欠発信される。

【0024】

前記空間へ間欠発信された無線信号がアンテナ又は送受波器6で受信され、受信機7によって復調された同期入力信号は、同期入力端子14を介して、帯域通過フイルタ25によって不要な高調波と雑音が除去された後、ゼロ交差検出器26によってデジタル信号に変換され、一方、基準発振器21によって生成されるクロック信号を、直接もしくは位相同期発振器もしくは逓倍器23によって高い周波数のサンプリング信号に変換し、前記サンプリング信号を同期検出器24に供給して、ゼロ交差検出器26の出力信号をサンプリングし、前記同期入力信号の立上り点、立下り点、もしくはゼロ交差点のタイミングを検出する。

【0025】

前記検出されたタイミングにおいて、前記セットもしくはリセット付きカウンタ22を複数回、例えば3回程度、セットしあるいはリセットすることで、瞬時に、例えば3マイクロ秒で、同期を確立し、同期入力信号が休止しあるいは停止した場合、あるいは取去られた場合にも、比較的に長時間、同期状態を高精度でしかも高安定に保持しあるいは維持できる。

なお、前記セットもしくはリセット付きカウンタ22は、前記基準発振器21の出力信号を、直接、あるいは位相同期発振器もしくは逓倍器23を用いて高い周波数に変換してクロック信号とし、前記クロック信号によって駆動されているものとする。

【0026】

また、前記基準発振器21の発振周波数は、前記同期入力信号の周波数に比較して、整数倍であることが必須であり、両者間の周波数偏差は±1ppm程度以内であり、可能な限り少ないことが望ましい。

また、前記同期入力信号の周波数が1MHzの場合、セットもしくはリセットを3回継続することで、3マイクロ秒以内に、確実に同期を確立させることができる。

【0027】

図2は本発明の第1の実施の形態による同期発振器の動作説明図である。図2において、31は同期入力信号、32は同期入力信号のゼロ交差信号、33はサンプリング信号、34a、34bはセットもしくはリセット信号、35a〜35dは同期発振器から出力される同期出力信号、36a、36bは同期確立誤差、37は同期入力信号の時間軸、38はゼロ交差信号の時間軸、39はサンプリング信号の時間軸、40はセットもしくはリセット信号の時間軸、41は同期出力信号の時間軸である。

前記セットもしくはリセット信号34a、34bは数ビットが割付けられるので、同期確立に要する時間は前記ビット数に比例することとなる。

【0028】

ここで、同期確立以前には、ゼロ交差信号32の位相とサンプリング信号33の位相との間には同期誤差36aが存在するのに対して、前記同期入力信号31の立上り点、立下り点、もしくはゼロ交差点のタイミングを検出し、前記検出したタイミングでカウンタをリセットすると、最大で前記サンプリング信号33のパルス間隔分の同期検出誤差36bを生じ、従って、前記サンプリング信号33のパルス間隔分の同期確立誤差36bが発生する。前記サンプリング信号33のパルス間隔をΔtとすると、同期確立誤差の変動幅は±Δt/2で表わされる。

【0029】

高精度でしかも短時間で同期を確立し、かつ比較的に長時間同期を保持しあるいは維持する技術を確立するためには、(1)同期入力信号31の立上り点、立下り点、もしくはゼロ交差点を高精度で検出できること、(2)前記検出したタイミングで同期発振器と瞬時に同期を確立できること、(3)前記同期入力信号31が休止しあるいは停止した後も、前記同期発振器が安定に同期を保持しあるいは維持できること、などが必須の条件となる。

【0030】

(1)のためには、同期入力信号31の立ち上り、立下り、もしくはゼロ交差点を検出するために、サンプリング信号33の周波数を、同期入力信号31の周波数の10倍以上の高い周波数に設定する必要がある。例えば、サンプリング信号の周波数が256MHzの場合、同期入力信号の立ち上りもしくは立下りの検出誤差の変動幅は±2ナノ秒となる。

【0031】

(2)のためには、同期入力信号31の立ち上り点、立下り点、もしくはゼロ交差点を検出したタイミングで、セットもしくはリセット付きのカウンタを、複数回セットしあるいはリセットすることで実現できる。前記セットもしくはリセット付きのカウンタは、高安定水晶発振器21の出力信号を、直接、あるいは位相同期発振器もしくは逓倍器23の出力信号をクロック信号とし、前記クロック信号33をカウントダウンして、同期入力信号31と同期しあるいは直交する同期出力信号35a〜35dを生成する。

【0032】

(3)のためには、セットもしくはリセット付きのカウンタを採用すると、リセット信号が休止しあるいは停止した後も引続き同期発振が継続し、前記同期入力信号31の周波数と、前記基準発振器21の発振周波数との間の周波数偏差内で同期を保持しあるいは維持できる。

【0033】

なお、同期入力信号31に同期確立誤差関数を付与するために、前記同期入力信号、前記同期入力信号の立上り点、立下り点、あるいはゼロ交差点を検出するためのサンプリング信号、もしくはこれらの両方の信号の位相を複数組の移相手段を設け、切替制御手段によって順次選択して出力することで、前記同期確立誤差を軽減することができる。

また、前記同期入力信号が、間欠発信でなく連続して発信される場合でも、同期入力信号に、直接もしくは間接に、同期確立誤差関数を付与することによって、瞬断もしくは多重伝搬が発生する有線回線もしくは無線回線にも、安価なコストで適用できる。

【0034】

(実施の形態2)

図6は、本発明の第2の実施の形態による同期発振器の構成図である。図6において、22はセットもしくはリセット付きの数値制御発振器、81は加算器、82はルックアップテーブル、83はデジタルアナログ変換器、84は帯域通過フイルタ、85はゼロ交差検出器、74はクロック信号の入力端子、76はセットもしくはリセット端子、75は出力端子である。

【0035】

前記数値制御発振器22は、前記同期発振器10のセットもしくはリセット付きのカウンタ22の代替えとなるものであり、加算器81のレジスタは、前記同期入力信号と同期しあるいは直交する同期出力信号の周波数を生成するようにプログラムされており、入力端子74に入力されるクロック信号によって順次加算が繰返され、ルックアップテーブル82によって振幅の変化もしくは位相の変換に置換えられ、デジタルアナログ変換器83によってアナログ信号に変換され、帯域通過フイルタ84によって不要な周波数成分が除去され、コンパレータ85によってデジタル信号に変換されて、出力端子75からデジタル信号として出力される。

【0036】

セットもしくはリセット端子76に、セットもしくはリセット信号が入力されると、前記数値制御発振器22は中性点(ゼロ交差点)を出力するものとすると、前記セットもしくはリセット信号が取り除かれると、前記同期入力信号の立上り、立下り、もしくはゼロ交差点に同期した同期出力信号が、出力端子75から出力される。

【0037】

図3は、本発明の同期確立誤差関数生成手段の構成図である。図3において、21は基準発振器、23は位相同期発振器、27は同期確立誤差関数生成手段、51は複数段の移相手段、52a〜52nは移相手段51の切替タップ、53は切替制御手段、54はサンプリング信号の入力端子、55はクロック信号入力端子、56はサンプリング信号出力端子である。

同期確立誤差関数生成手段27は、少なくとも、移相相手段51と、切替タッブ52a〜52nと、切替制御手段53とから構成される。

【0038】

前記位相同期発振器23から出力されるサンプリング信号は、周波数が同期入力信号の周波数の10倍以上の十分に高い周波数であり、例えば256MHzもしくはそれ以上の周波数であり、移相手段51に接続される。前記移相手段51は、複数段のシフトレジスタ、複数段の遅延素子、もしくは複数段の遅延回路などによって構成され、各段の信号出力は切替タップ52a〜52nによって引き出され、切替制御手段53によって順次選択され、サンプリング信号出力端子56から外部に出力される。

【0039】

前記移相手段51の各段の移相量は極力小さいことが望ましく、かつ移相量の合計は、前記サンプリング信号のパルス間隔Δt以上であることが必要である。例えば、前記サンプリング信号の周波数が256MHzであるとすると、前記移相手段51の各段の移相量は4ナノ秒以下であり、かつ移相量の合計は4ナノ秒以上とする必要がある。ここで、前記切替タップの数を16とし、前記バースト信号の長さを0.5msとすると、前記切替制御手段53は、1ステップ当り32μsの速さでタップを切替えることになる。

【0040】

従って、前記1ステップ当りの切替時間32μsの10分の1、すなわち3μs程度で同期を確立する必要がある。

なお、前記同期確立誤差関数生成手段27は、ある種のシステムに適用する場合には、前記同期入力信号生成手段3の出力端子、あるいは前記ゼロ交差検出器26の出力端子に接続しても同様な効果が得られる。

【0041】

また、前記移相手段51の複数段のタップ52a〜52n毎に生じる同期確立誤差の合計を、同期確立誤差関数として表現すれば、同期確立誤差関数は多項式によって表現でき、前記多項式は、0もしくは一定値に収斂することが望ましい。

【0042】

図4は、本発明の同期確立誤差関数生成手段の他の構成図である。図4において、27は同期確立誤差関数生成手段、25は受信機、6a、6bは複数のアンテナ又は送受波器、61はアンテナ切替器、14は受信機の出力端子である。

複数のアンテナ又は送受波器6aと6bとはお互いに4分1波長以上離れて設置されており、両者をアンテナ切替器61を用いて順次にあるいは周期的に切替えながら無線信号を受信し、受信機25によって同期入力信号を復調すると、無線区間で生じる伝搬経路長の差もしくは多重伝搬等の影響で、両者の間で復調した同期入力信号の位相が異なり、両者間の相関性も小さいことが分かっている。

【0043】

そこで、前記アンテナ切替器61を、前記バースト信号として受信する間に、順次にあるいは周期的に切替えることで、図3に示す同期確立誤差関数生成手段27と同様な効果が得られることになる。

なお、前記アンテナ又は送受波器の数は、2基以上であれば多いほど、無線区間で生じる多重伝搬による同期誤差関数の付与効果が大きくなる。

【0044】

図5は、本明の同期確立誤差関数生成手段の他の構成図である。図5において、22はリセット付きカウンタ、71、73は切替制御手段、72a〜72nは複数組のカウンタもしくは数値制御発振器、74はセットもしくはリセット信号接続端子、75は出力端子、76はクロック信号入力端子である。

カウンタもしくは数値制御発振器22のセットもしくはリセット信号の入力端子74には、前記同期入力信号がバースト信号として受信される間、前記同期検出手段24によって、同期入力信号の立ち上り、立下り、もしくはゼロ交差点のタイミングが検出されて、タイミング信号として入力される。

【0045】

そこで、図3、図4における前記同期確立誤差関数を付与する側の切替制御手段53もしくはアンテナスイッチ61を切替えるタイミングに同期して、図5の切替制御手段71を順次にあるいは周期的に切替え、前記同期入力信号が休止しあるいは停止している期間中、あるいは必要な期間中には、前記切替制御手段71を開放して同期を保持しあるいは維持し、前記切替制御手段73によって順次にあるいは周期的に切替え、出力端子75から同期出力信号を出力する。

【0046】

一方、前記カウンタもしくは数値制御発振器22のクロック信号入力端子76には、前記基準発振器21からクロック信号が直接もしくは周波数変換されて供給されているので、前記セットもしくはリセット信号のタイミングに同期して、通常、低い周波数へカウントダウンが開始され、同期が確立する。

また、前記切替制御手段73もしくはアンテナ切替器61の切替えは、順序を決めて順番に行なうか、周期的に行なうか、ランダムに行なうか、あるいは任意の方法かのいずれかを選択する。

【0047】

ここで、前記同期入力発生装置1の基準発振器2と、前記同期発振器10の基準発振器21とは、発振周波数偏差が±1ppm以内に保たれていると、両者の位相関係は前記バースト信号の期間中ほぼ一定に保たれ、従って、前記同期検出手段24によって検出されるセットもしくはリセット信号のタイミングも一定に保たれ、従って、同期確立誤差も一定に保たれてしまう問題点がある。

【0048】

そこで、前記同期確立誤差関数を付与すると、前記同期確立誤差がジッタ雑音に変換されるので、何らかの方法で平準化することで、同期確立誤差を軽減できることになる。平準化する方法として、前記同期発振器10に入力される同期入力信号、前記同期発振器10から出力される同期出力信号、あるいはこれらの両方を、伝達位相誤差、中心周波数偏差、群遅延歪み、もしくはこれらの組合せが少ないかあるいは少なく微調整が可能な帯域通過フイルタを通して平準化すれば、前記ジッタ雑音が軽減されるので、従って同期確立誤差を軽減することができる。なお、平準化された同期出力信号はアナログ信号なので、ゼロ交差検出器を用いてデジタル信号に変換できる。

【0049】

以上の説明では、セットもしくはリセット付きのカウンタもしくは数値制御発振器を用いる場合について述べたが、同様な機能を有する発振器を用いることでも、前記同期発振器を容易に構成することができる。

また、前記同期入力信号には、有線回線で伝送された信号、無線信号を復調した信号、連続的な信号、あるいは単一周波数であるいかなる種類の同期入力信号をも含めることができる。

また、前記同期発振器の用途によっては、同期入力信号を生成する側に、前記移相手段を設け、複数組の位相シフトを付与することでも同様な効果が得られる。

【0050】

また、同期確立誤差関数を付与する他の方法として、前記同期入力信号発生装置と同期発振器側との間を無線回線で接続している場合、前記同期入力信号発生装置側、同期発振器側、もしくはこれらの両方に、複数のアンテナ又は送受波器、およびアンテナ切替器を設け、前記同期発振器のカウンタに設けた切替制御手段の切替えタイミングに合わせて、前記複数のアンテナ又は送受波器を周期的に切替えることが有効である。

また、無線信号として、超音波信号、高周波信号、もしくは光信号が用いられ、超音波信号と光信号とは、送受波器を用いて発受信されるものとする。

【産業上の利用可能性】

【0051】

本発明は、上記のように構成されているため、通信システムにおいて同じ周波数であり、同じ位相であり、あるいはこれらの両方が必須である、同期入力信号と同期出力信号との間の同期を、数マイクロ秒以内の瞬時にしかも高い精度で確立し、前記同期入力信号が休止し、停止し、消滅し、あるいは取去られた場合にも、同期出力信号が同期状態を高い精度で保持しあるいは維持する必要がある分野において、広く利用できる基盤技術に関するものである。

【0052】

具体的には、時分割同時送受話方式の無線装置間で相互間の距離を測定する分野において、距離を測定する側の装置、距離を測定される側の装置、前記2つの装置以外で無線信号を中継する装置、あるいはこれらの組み合わせから、無線信号に含まれて発信されあるいは受信される同期入力信号と、同期して出力される同期出力信号とを、高い精度で瞬時に同期を確立させかつ比較的に長時間同期を保持させるために用いることができる。

また、複数の無線装置の間でアドホックネットワークを瞬時に構成する必要がある場合に、相互間の距離を瞬時に測定するために用いることができる。

【図面の簡単な説明】

【0053】

【図1】本発明の第1の実施の形態による同期発振器の構成図

【図2】本発明の第1の実施の形態による同期発振器の動作説明図

【図3】本発明の同期確立誤差関数生成手段の構成図

【図4】本発明の同期確立誤差関数生成手段の他の構成図

【図5】本発明の同期確立誤差関数生成手段の他の構成図

【図6】本発明の第2の実施の形態による同期発振器の構成図

【図7】従来の実施例を示す構成図

【符号の説明】

【0054】

1 同期入力信号発生装置

2 基準発振器

3 同期入力信号生成手段

4 送信機

5、6、6a、6b アンテナ又は送受波器

7 受信機

10 同期発振器

21 基準発振器

22 セットもしくはリセット付きカウンタ

23 位相同期発振器

24 位相同期検出手段

25 帯域通過フイルタ

26 ゼロ交差検出器もしくはコンパレータ

27 同期確立誤差関数生成手段

【特許請求の範囲】

【請求項1】

無線回線もしくは有線回線を通じて伝送される同期入力信号と瞬時に同期を確立し、かつ比較的に長時間同期を保持するための同期発振器において、前記同期発振器が、少なくとも、発振周波数が高安定である基準発振器と、前記基準発振器の出力信号を直接もしくは周波数を変換してサンプリング信号とし、同期入力信号の立上り点、立下り点、もしくはゼロ交差点のタイミングを検出するための同期検出手段と、前記基準発振器の出力信号を直接もしくは周波数を変換してクロック信号とし、前記クロック信号によって駆動されるセットもしくはリセット付きのカウンタもしくは数値制御発振器とから構成され、

前記同期検出手段が、前記検出したタイミングにおいて、前記カウンタもしくは数値制御発振器をセットしあるいはリセットして瞬時に同期を確立し、前記セットもしくはリセット付きのカウンタもしくは数値制御発振器が、前記同期入力信号が休止しあるいは停止している間も、高精度で比較的に長時間同期を保持しあるいは維持できる

ことを特徴とする瞬時に同期を確立しかつ保持できる同期発振器。

【請求項2】

前記同期入力信号に同期確立誤差関数を付与するために、前記同期入力信号の立上り点、立下り点、もしくはゼロ交差点のタイミングを検出するために用いるサンプリング信号の位相を、複数組の移相手段を設けて異なった位相にシフトさせ、前記位相をシフトさせた複数組のサンプリング信号を、切替制御手段によって、順次にあるいは周期的に切替えることを特徴とする請求項第1項に記載の瞬時に同期を確立しかつ保持できる同期発振器。

【請求項3】

前記同期入力信号に同期確立誤差関数を付与するために、前記同期入力信号の位相を、複数組の移相手段を設けて異なった位相にシフトさせ、前記位相をシフトさせた複数組の同期入力信号を、切替制御手段によって、順次にあるいは周期的に切替えることを特徴とする請求項第1項に記載の瞬時に同期を確立しかつ保持できる同期発振器。

【請求項4】

前記同期入力信号に同期確立誤差関数を付与するために、同期入力信号発生装置側と同期発振器側とを無線回線で接続し、前記同期入力信号発生装置側、同期発振器側、もしくはこれらの両方に、複数のアンテナを設け、アンテナ切替器によって、順次にあるいは周期的に切替えることを特徴とする請求項第1項に記載の瞬時に同期を確立しかつ保持できる同期発振器。

【請求項5】

前記同期確立誤差関数を付与するのに対応して、複数組のセットもしくはリセット付きのカウンタもしくは数値制御発振器を設け、前記同期入力信号が入力される間は、前記同期確立誤差関数を付与する側の切替制御手段もしくはアンテナ切替器を切替えるタイミングに合わせて、前記複数組のカウンタもしくは数値制御発振器を切替え、前記複数組のカウンタもしくは数値制御発振器を、順次にあるいは周期的に、セットしもしくはリセットして瞬時に同期を確立し、前記同期入力信号が休止しあるいは停止している間は、前記複数組のカウンタの動作を継続して同期を比較的に長時間保持しあるいは維持し、前記複数組のカウンタもしくは数値制御発振器の出力信号を順次にあるいは周期的に切替えて出力することを特徴とする請求項第2項から第4項までの何れかに該当する瞬時に同期を確立しかつ保持できる同期発振器。

【請求項6】

前記位相シフトの合計が、前記サンプリング信号の1周期の長さ以上であることを特徴とする請求項第2項もしくは第3項に記載の瞬時に同期を確立しかつ保持できる同期発振器。

【請求項7】

前記同期発振器に入力される同期入力信号、前記同期発振器から出力される同期出力信号、あるいはこれらの両方を、伝達位相誤差、中心周波数偏差、遅延歪み、もしくはこれらの組合せが少ないかあるいは少なく微調整が可能な帯域通過フイルタに通し、前記同期出力信号に含まれる雑音を軽減し、必要に応じてゼロ交差検出器によってデジタル信号に変換することを特徴とする請求項第5項に記載の瞬時に同期を確立しかつ保持できる同期発振器。

【請求項8】

前記同期入力信号が間欠発信でなく連続して発信される場合でも、同期入力信号に、直接もしくは間接に、同期確立誤差関数を付与することによって、瞬断もしくは多重伝搬が発生する有線回線もしくは無線回線にも適用できることを特徴とする請求項第1項から第7項のいずれかに該当する瞬時に同期を確立しかつ保持できる同期発振器。

【請求項9】

前記基準発振器の出力信号を、位相同期発振器もしくは逓倍器を用いて、前記同期入力信号の10倍以上の周波数に変換し、前記クロック信号、サンプリング信号、もしくはこれらの両方として用いることを特徴とする請求項第1項に記載の瞬時に同期を確立しかつ保持できる同期発振器。

【請求項1】

無線回線もしくは有線回線を通じて伝送される同期入力信号と瞬時に同期を確立し、かつ比較的に長時間同期を保持するための同期発振器において、前記同期発振器が、少なくとも、発振周波数が高安定である基準発振器と、前記基準発振器の出力信号を直接もしくは周波数を変換してサンプリング信号とし、同期入力信号の立上り点、立下り点、もしくはゼロ交差点のタイミングを検出するための同期検出手段と、前記基準発振器の出力信号を直接もしくは周波数を変換してクロック信号とし、前記クロック信号によって駆動されるセットもしくはリセット付きのカウンタもしくは数値制御発振器とから構成され、

前記同期検出手段が、前記検出したタイミングにおいて、前記カウンタもしくは数値制御発振器をセットしあるいはリセットして瞬時に同期を確立し、前記セットもしくはリセット付きのカウンタもしくは数値制御発振器が、前記同期入力信号が休止しあるいは停止している間も、高精度で比較的に長時間同期を保持しあるいは維持できる

ことを特徴とする瞬時に同期を確立しかつ保持できる同期発振器。

【請求項2】

前記同期入力信号に同期確立誤差関数を付与するために、前記同期入力信号の立上り点、立下り点、もしくはゼロ交差点のタイミングを検出するために用いるサンプリング信号の位相を、複数組の移相手段を設けて異なった位相にシフトさせ、前記位相をシフトさせた複数組のサンプリング信号を、切替制御手段によって、順次にあるいは周期的に切替えることを特徴とする請求項第1項に記載の瞬時に同期を確立しかつ保持できる同期発振器。

【請求項3】

前記同期入力信号に同期確立誤差関数を付与するために、前記同期入力信号の位相を、複数組の移相手段を設けて異なった位相にシフトさせ、前記位相をシフトさせた複数組の同期入力信号を、切替制御手段によって、順次にあるいは周期的に切替えることを特徴とする請求項第1項に記載の瞬時に同期を確立しかつ保持できる同期発振器。

【請求項4】

前記同期入力信号に同期確立誤差関数を付与するために、同期入力信号発生装置側と同期発振器側とを無線回線で接続し、前記同期入力信号発生装置側、同期発振器側、もしくはこれらの両方に、複数のアンテナを設け、アンテナ切替器によって、順次にあるいは周期的に切替えることを特徴とする請求項第1項に記載の瞬時に同期を確立しかつ保持できる同期発振器。

【請求項5】

前記同期確立誤差関数を付与するのに対応して、複数組のセットもしくはリセット付きのカウンタもしくは数値制御発振器を設け、前記同期入力信号が入力される間は、前記同期確立誤差関数を付与する側の切替制御手段もしくはアンテナ切替器を切替えるタイミングに合わせて、前記複数組のカウンタもしくは数値制御発振器を切替え、前記複数組のカウンタもしくは数値制御発振器を、順次にあるいは周期的に、セットしもしくはリセットして瞬時に同期を確立し、前記同期入力信号が休止しあるいは停止している間は、前記複数組のカウンタの動作を継続して同期を比較的に長時間保持しあるいは維持し、前記複数組のカウンタもしくは数値制御発振器の出力信号を順次にあるいは周期的に切替えて出力することを特徴とする請求項第2項から第4項までの何れかに該当する瞬時に同期を確立しかつ保持できる同期発振器。

【請求項6】

前記位相シフトの合計が、前記サンプリング信号の1周期の長さ以上であることを特徴とする請求項第2項もしくは第3項に記載の瞬時に同期を確立しかつ保持できる同期発振器。

【請求項7】

前記同期発振器に入力される同期入力信号、前記同期発振器から出力される同期出力信号、あるいはこれらの両方を、伝達位相誤差、中心周波数偏差、遅延歪み、もしくはこれらの組合せが少ないかあるいは少なく微調整が可能な帯域通過フイルタに通し、前記同期出力信号に含まれる雑音を軽減し、必要に応じてゼロ交差検出器によってデジタル信号に変換することを特徴とする請求項第5項に記載の瞬時に同期を確立しかつ保持できる同期発振器。

【請求項8】

前記同期入力信号が間欠発信でなく連続して発信される場合でも、同期入力信号に、直接もしくは間接に、同期確立誤差関数を付与することによって、瞬断もしくは多重伝搬が発生する有線回線もしくは無線回線にも適用できることを特徴とする請求項第1項から第7項のいずれかに該当する瞬時に同期を確立しかつ保持できる同期発振器。

【請求項9】

前記基準発振器の出力信号を、位相同期発振器もしくは逓倍器を用いて、前記同期入力信号の10倍以上の周波数に変換し、前記クロック信号、サンプリング信号、もしくはこれらの両方として用いることを特徴とする請求項第1項に記載の瞬時に同期を確立しかつ保持できる同期発振器。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【公開番号】特開2011−147107(P2011−147107A)

【公開日】平成23年7月28日(2011.7.28)

【国際特許分類】

【出願番号】特願2010−229811(P2010−229811)

【出願日】平成22年10月12日(2010.10.12)

【出願人】(395007299)有限会社アール・シー・エス (51)

【Fターム(参考)】

【公開日】平成23年7月28日(2011.7.28)

【国際特許分類】

【出願日】平成22年10月12日(2010.10.12)

【出願人】(395007299)有限会社アール・シー・エス (51)

【Fターム(参考)】

[ Back to top ]