短絡が減少したOLEDデバイス

【課題】OLEDディスプレイとOLEDデバイスの短絡を減らすさまざまな構造を提供すること。

【解決手段】(a)基板と;

(b)この基板の上に配置された第1の電極層と;

(c)この第1の電極層の上に配置された無機短絡低減層と;

(d)この無機短絡低減層の上に配置された電荷注入層と;

(e)この電荷注入層の上に配置された有機EL素子と;

(f)この有機EL素子の上に配置された第2の電極層を備えていて、上記短絡低減層が、短絡に起因する漏れ電流と、それに付随する発光効率の損失とを減らすのに十分な厚さと抵抗率を持つように選択されているOLEDデバイス。

【解決手段】(a)基板と;

(b)この基板の上に配置された第1の電極層と;

(c)この第1の電極層の上に配置された無機短絡低減層と;

(d)この無機短絡低減層の上に配置された電荷注入層と;

(e)この電荷注入層の上に配置された有機EL素子と;

(f)この有機EL素子の上に配置された第2の電極層を備えていて、上記短絡低減層が、短絡に起因する漏れ電流と、それに付随する発光効率の損失とを減らすのに十分な厚さと抵抗率を持つように選択されているOLEDデバイス。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、OLEDデバイスとOLEDディスプレイにおける短絡の減少に関する。

【背景技術】

【0002】

有機エレクトロルミネッセンス(EL)デバイスまたは有機発光ダイオード(OLED)は、印加した電圧に応答して光を出す電子デバイスである。Tangらは、Applied Physics Letters、第51巻、913ページ、1987年;Journal of Applied Physics、第65巻、3610ページ、1989年;譲受人に譲渡されたアメリカ合衆国特許第4,769,292号において、高効率のOLEDを提示している。そのとき以来、ポリマー材料を含む別の層構造を持つ多数のOLEDが発表され、デバイスの性能が向上してきている。

【0003】

OLEDは、アノードと、カソードと、アノードとカソードに挟まれた有機EL素子とを備える薄膜デバイスである。動作中は電圧がアノードとカソードの間に印加されることで、電子がカソードから注入され、正孔がアノードから注入される。適切に構成されているならば、注入された電子と正孔が有機EL素子内の発光層で再結合し、これら電荷担体の再結合によってデバイスから光が出る。一般に、有機EL素子は厚さが約100〜500nmであり、電極間に印加される電圧は約3〜10ボルトであり、動作電流は約1〜20mA/cm2である。

【0004】

アノードとカソードの間はわずかしか離れていないため、OLEDデバイスでは短絡という欠陥が発生しやすい。OLEDデバイスの構造中のピンホール、割れ目、段差や、コーティングの凹凸などにより、アノードとカソードが直接接触したり、欠陥のある領域で有機層が他の領域よりも薄くなったりする可能性がある。欠陥のある領域は、電流が流れるための低抵抗経路を提供するため、有機EL素子を流れる電流が少なくなったり、極端な場合には電流が流れなくなったりする。したがってOLEDデバイスの光出力が低下したり消失したりする。マルチ画素ディスプレイ装置では、短絡によって発光しなかったり平均以下の強度の光しか出さなかったりする死んだ画素が生まれる可能性があるため、ディスプレイの品質が低下する。照明その他の低解像度の用途では、短絡によってかなりの領域が機能しなくなる可能性がある。短絡という問題があるため、OLEDデバイスは一般にクリーン・ルームの中で製造される。しかしクリーンな環境でさえ、短絡をなくすのに有効ではない。多くの場合、2つの電極の間隔を大きくして短絡の数を減らすため、有機層の厚さは、デバイスが機能する上で実際に必要であるよりも厚くされる。この方法だとOLEDデバイスの製造コストが上昇し、しかもこの方法でさえ、短絡を完全になくすことはできない。

【0005】

日本国特開2002-100483Aには、アノードの透明な結晶性導電膜が局所的に突起していることに起因する短絡を、透明なアモルファス導電膜を透明な結晶性導電膜の上に堆積させることによって減らす方法が開示されている。アモルファス膜の滑らかな表面により、結晶膜からの局所的突起がOLEDデバイスに短絡またはダーク・スポットを形成するのを阻止できるという主張がなされている。この方法の有効性は疑わしい。なぜなら、透明なアモルファス導電膜の形成に利用する真空蒸着法は平均化機能を持たないため、透明なアモルファス導電膜の表面は、その下にある透明な結晶性導電膜の表面をそのまま再現していることが予想されるからである。さらに、この方法は、ダスト粒子、断片、構造上の不連続性や、OLEDの製造法で一般的な他の原因によるピンホールの問題に対処していない。

【0006】

日本国特開2002-208479Aには、透明な金属酸化物からなる中間抵抗膜(その膜の厚さは10nm〜10μmであり、膜厚方向の抵抗値は0.01〜2Ωcm2であり、この抵抗膜の表面におけるイオン化エネルギーは5.1eV以上である)を、ガラスまたは樹脂からなる透明な基板の上に透明電極パターンとして形成された正電極上または負電極上の発光領域の全体または一部の上に被せることによって短絡を減らす方法が開示されている。この方法には利点があるものの、記載されている範囲の抵抗率は、多くのOLEDディスプレイまたはOLEDデバイスで短絡に起因する漏れ電流を減らすのに有効ではない。さらに、イオン化エネルギーの条件によって選択できる材料が厳しく制限される。またこの条件では、性能が優れていて寿命が長いOLEDデバイスを実現する上で極めて重要であることが知られている適切な正孔注入が保証されない。さらに、イオン化エネルギーの大きな材料は電子を注入できないため、カソードと有機発光層の間で利用することはできない。カソード材料と有機発光層の間に抵抗膜を用いること、またはカソードと有機発光材料の間、およびアノードと有機発光材料の間の両方に抵抗膜を用いることが望ましい場合がしばしばある。

【発明の概要】

【発明が解決しようとする課題】

【0007】

したがって本発明の1つの目的は、短絡に起因する漏れ電流が減るという改善がなされたOLEDデバイスまたはOLEDディスプレイを提供することである。

【課題を解決するための手段】

【0008】

この目的は、

(a)基板と;

(b)この基板の上に配置された第1の電極層と;

(c)この第1の電極層の上に配置された無機短絡低減層と;

(d)この無機短絡低減層の上に配置された電荷注入層と;

(e)この電荷注入層の上に配置された有機EL素子と;

(f)この有機EL素子の上に配置された第2の電極層を備えていて、上記短絡低減層が、短絡に起因する漏れ電流と、それに付随する発光効率の損失とを減らすのに十分な厚さと抵抗率を持つように選択されているOLEDデバイスによって達成される。

【発明の効果】

【0009】

短絡が起こったときにその効果を最少にできることが、本発明の1つの利点である。

【図面の簡単な説明】

【0010】

【図1】短絡のある従来技術のデバイスの概略断面図である。

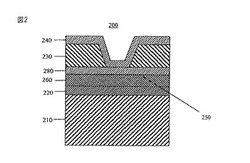

【図2】本発明によるOLEDデバイスの概略断面図である。

【図3】本発明による積層型OLEDデバイスの概略断面図である。

【図4】良好なOLEDデバイスの数を短絡低減層の厚さの関数として示したグラフである。

【図5】良好なOLEDデバイスの数を短絡低減層の厚さの関数として示したグラフである。

【発明を実施するための形態】

【0011】

図1は、短絡のある従来のOLEDデバイス100の概略断面図である。このデバイス100は、基板110と、第1の電極層120と、有機EL素子130と、第2の電極層140を備えている。電極層の一方はアノードであり、他方の電極層はカソードである。物理的な保護その他の目的で第2の電極層140の上に他の層が存在していることがしばしばある。カソードと有機EL素子130の間に有機または無機の電子注入層が存在し、アノードと有機EL素子130の間に有機または無機の正孔注入層が存在していることもしばしばある。

【0012】

ボトム・エミッション型OLEDデバイスでは、基板110は、OLEDデバイス100から発生する光に対して透明である。基板110の一般的な材料はガラスまたはプラスチックである。第1の電極層120も発生する光に対して透明である。第1の電極層120の一般的な材料は、透明な導電性酸化物(インジウム-スズ酸化物(ITO)、インジウム-亜鉛酸化物(IZO)など)である。あるいは第1の電極層120は、半透明な金属(例えばAg、Au、Mg、Ca)またはその合金で製造することもできる。半透明な金属を第1の電極層120として用いる場合には、OLEDデバイス100はマイクロキャビティ構造を持つと言われる。有機EL素子130は少なくとも1つの発光層(LEL)を備えているが、他の機能層(例えば電子輸送層(ETL)、正孔輸送層(HTL)、電子阻止層(EBL)、正孔阻止層(HBL)など)も備えていることがしばしばある。以下の説明は機能層の数とは無関係であり、有機EL素子130の材料の選択とも無関係である。第2の電極層140は、通常は、反射性金属層(例えばAl、Ag、Au、Mg、Ca、またはその合金)である。正孔注入層を有機EL素子130とアノードの間に追加し、電子注入層を有機EL素子130とカソードの間に追加することがしばしばある。動作中は、正電位をアノードに印加し、負電位をカソードに印加する。電子がカソードから有機EL素子130に注入されると、印加した電場によって駆動されてアノードに向かって移動する。それに対して正孔がアノードから有機EL素子130に注入されると、印加した電場によって駆動されてカソードに向かって移動する。電子と正孔が有機EL素子130の中で結合すると光が発生し、OLEDデバイス100から放出される。

【0013】

トップ・エミッション型OLEDデバイスでは、光が基板110とは反対の方向に出る。このような場合、基板110を出る光に対して不透明にすることができ、金属やSiなどの材料を基板110に使用することができる。第1の電極層120は不透明で反射性のあるものにできるのに対し、第2の電極層140は、透明または半透明になっている必要がある。

【0014】

図1には、有機EL素子130内で有機材料が不足している領域によって生じる短絡150も簡単に図示してある。以下の説明は、有機EL素子130内の有機材料の厚さがデバイスの残りの領域の厚さと比べて実質的に薄い領域によって生じる短絡にも当てはまる。短絡には可能な多くの原因がある。例えば基板110の上にダスト粒子または断片があると有機EL素子130を堆積させている間に材料の流れが局所的に止まる可能性があるため、有機膜の厚さにギャップができたり有機膜の厚さが実質的により薄くなったりし、堆積された第1の電極層120と第2の電極層140の間の電気抵抗が小さくなる。粒子または断片は、基板を真空チェンバーの中に装填する前に大気中からやってくる可能性や、第1の電極層120または有機層を堆積させている間にボートから供給材料の粒子が放出されたり、堆積チェンバーの壁面や固定物から堆積物が剥がれたりすることによって発生する可能性がある。こうした粒子または断片は、有機層の堆積中または堆積後に、その有機堆積物に発生する機械的振動や応力によって剥がれ落ちたり、単に重力によって剥がれ落ちたりする可能性もある。有機物堆積プロセスの間に基板110上に存在していてその後剥がれ落ちる粒子や断片は、最も大きなダメージを引き起こす可能性がある。この場合、粒子や断片は有機材料が基板110上に堆積されるのを阻止し、粒子や断片が剥がれ落ちる場合には、第1の電極層120の領域があとから堆積される第2の電極層140に対して完全に露出した状態になる。

【0015】

短絡の別の原因としては、OLEDデバイス構造の段差がある。それは例えばアクティブ・マトリックスOLEDディスプレイ装置のTFT(薄膜トランジスタ)構造に付随する段差であり、基板110の表面上または第1の電極層120の表面上の有機層や凹凸によっては完全にカバーすることができない。短絡150により、第2の電極層140が直接に、または有機層の非常に薄い部分を通じて第1の電極層120と接触し、デバイスに電流を流す低抵抗の経路が提供される。電圧をアノードとカソードの間に印加するとき、かなりの電流が、アノードからデバイスの無欠陥領域を迂回して短絡150を通ってカソードへと流れることができる。したがって短絡はOLEDデバイス100の発光出力を顕著に低下させ、多くの場合にOLEDデバイス100がまったく発光しなくなる可能性がある。

【0016】

図2は、本発明の一実施態様によるOLEDデバイス200の概略断面図である。このOLEDデバイス200は、基板210と、第1の電極層220と、有機EL素子230と、第2の電極層240を備えている。第1の電極層220と有機EL素子230の間には短絡低減層(SRL)260と電荷注入層280が配置されている。第1の電極層220がアノードである場合には、電荷注入層280は正孔注入層である。それに対して第1の電極層220がカソードである場合には、電荷注入層280は電子注入層である。図2では、電荷注入層280が短絡250を覆うように描かれている。多くの場合、電荷注入層280が短絡250の位置に存在していなくてもよい。電荷注入層280が短絡250の位置にこのように存在していない状態は、例えば電荷注入層280が有機層コーティング・プロセスの一部としてコーティングされる場合や、短絡250が基板200または第1の電極層220の表面の凹凸によって生じる場合に起こる可能性がある。電荷注入層280は通常は非常に薄くて数ナノメートル以下であるため、どちらの場合にも電荷注入層280は短絡を通る抵抗にそれほど寄与せず、以下の説明には影響しない。

【0017】

OLEDデバイスを本発明に従って構成する場合、有機EL素子230に短絡250がある場所では第2の電極層240がピンホール内で第1の電極層220と直接接触することはなく、短絡低減層260を通じての接触となる。短絡低減層260は、適切に選択すると、第1の電極層220と第2の電極層240の間に抵抗項Rsrlを付加することができ、短絡250を通じた漏れ電流を実質的に減らす。本発明の効果は以下のようにして分析される。AをOLEDデバイス200の面積(単位はcm2)、αをOLEDデバイス200内のあらゆる短絡の全面積(単位はcm2)、tを厚さ(単位はcm)、ρを短絡低減層260のバルクの抵抗率(単位はΩcm)、I0を動作電流密度(単位はmA/cm2)、V0をOLEDデバイス200の動作電圧(単位はボルト)であるとすると、短絡を流れる電流は以下のように計算される。

【0018】

【数1】

【0019】

短絡低減層260は、短絡250のマイナスの影響を減らし、デバイスの性能を許容できるレベルまで向上させる。短絡のマイナスの影響は、パラメータf、すなわち短絡を流れる漏れ電流をデバイスの全電流で割った比から評価することができる。

【0020】

【数2】

【0021】

許容可能な比f0を実現するには、短絡低減層260の厚さ方向抵抗率ρtの最小値が以下のようになっていなくてはならない。

【0022】

【数3】

【0023】

したがって有効な短絡低減層260として使用できる材料は、面積Aと;OLEDデバイス200の動作条件V0およびI0と;許容できる性能損失のレベルf0と;短絡の全面積αと;デバイスに組み込むことのできる短絡低減層260の厚さtとを考慮して選択される。

【0024】

短絡低減層260の厚さは、2つの考慮事項に基づいて選択する。1)典型的なOLEDデバイスは、有機層を合計した厚さが100〜300nmであり、この層の厚さは、デバイスの発光効率が最適になるように光学的にチューニングされる。短絡低減層はデバイスの光学的構造の一部となるため、その厚さは約200nmを超えてはならない。短絡低減層があまりに厚くてもOLEDデバイスの製造コストが上昇する。2)短絡低減層は、短絡を効果的に覆うのに十分な厚さがなければならない。合理的な下限は約20nmである。本発明では、短絡低減層の厚さが20nm〜200nmの範囲であることが好ましい。

【0025】

OLEDデバイスは多くの異なった用途で用いられている。OLEDデバイスは、デバイスの面積と動作条件が非常に異なっていてもよい。例えば照明の用途では、OLEDデバイスは、大きな発光区画に分割されることが多く(アメリカ合衆国特許第6,693,296号)、その区画は1平方センチメートルよりも大きく、比較的少数のレベルの電流密度で動作する。エリア・カラー・ディスプレイでは、画素はより小さくて数平方ミリメートルのオーダーになるであろうが、動作条件はここでも大きくは違わない。画素化された高解像度OLEDディスプレイでは、背面がアクティブ・マトリックスであれパッシブ・マトリックスであれ、画素ははるかに小さくて0.3mm×0.3mm以下のオーダーになり、しかもOLEDデバイスがダイナミック・レンジを提供する必要がある。8ビットの解像度では、デバイスの動作電流の範囲が1〜256倍となっている必要がある。式3は、こうしたさまざまなOLEDデバイスが短絡低減層として広範な材料を必要とするであろうことを示唆している。

【実施例】

【0026】

例1

短絡低減層の選択の一例として、画素化された高解像度OLEDディスプレイの単一の画素に短絡が与える影響を分析する。この分析では、あるサイズの1つの短絡が画素内に存在していると仮定する。その代わりにより小さな短絡(例えば基板または第1の電極層の凹凸によって起こる欠陥)がいくつか存在していて単一の欠陥と全面積が同じである場合には、分析の結果は同じであろう。画素のサイズは0.1mm×0.1mmであると仮定し、欠陥のサイズは、ダスト粒子の典型的なサイズである1μm×1μmであると仮定する。

【0027】

従来のボトム・エミッション型アクティブ・マトリックスOLEDディスプレイは、最も明るくしたときの輝度が約200cd/m2である。この明るさは、開口比が約0.25のOLEDディスプレイにより、透過率が約50%の偏光膜を通じて実現される。したがって最も明るくしたときのOLEDデバイスの表面における実際の明るさは、約1600cd/m2である。8ビットの色深度では、OLEDデバイスは、約6.3cd/m2まで動作する必要もある。従来のOLEDデバイスの効率は約10cd/Aであり、動作電圧は約10ボルトである。これは、このデバイスが約0.063mA/cm2から約16mA/cm2まで動作せねばならないことを意味する。この実施例と以下の実施例では、デバイスの動作電圧は、動作電流とは独立であると仮定する。実際ほとんどのデバイスでは、動作電圧は動作電流の対数で変化する。これら実施例では約2.5桁にわたる範囲の動作電流を考慮しているため、一定電圧の仮定は合理的かつ無難な仮定である。OLEDディスプレイにおいて漏れを効果的に減らすのに必要な厚さ20nmの短絡低減層の抵抗率を約1μm×1μmのサイズの欠陥に関して計算し、計算した結果を表1に示してある。表1には、短絡低減層に起因する直列抵抗の増加と、短絡低減層の面抵抗率も示してある。後者の値は、画素間で起こる可能性のあるクロストークを評価するのに必要とされる。

【0028】

【表1】

【0029】

第1列には、明るさのレベルがcd/m2を単位としていくつか示してあり、明るさの8ビット表示になっている。第2列には、これらレベルでのOLEDデバイスの動作電流密度が示してある。第3列には、これらレベルでのOLED画素のデバイス等価抵抗の値が示してある。第4列には、漏れ電流が動作電流の10%である場合に、短絡の位置にSRLを有するときの短絡の抵抗値が示してある。これら抵抗値は、第3列に示した対応する値の10倍である。第5列には、SRLの対応する厚さ方向抵抗率が示してある。これらの値は、第4列の値に短絡の面積(この計算では10-8cm2に等しい)を掛けることによって得られる。第6列には、第5列に示した対応する厚さ方向抵抗率を実現するのに必要なバルクの抵抗率が示してある。この実施例では、SRLの厚さを20nmと仮定した。第7列には、SRLによってOLEDデバイスに付加される直列抵抗の値が示してある。第8列には、SRLの面抵抗率が示してある。もし面抵抗率がデバイスの等価抵抗に匹敵する場合には、クロストークが問題になろう。

【0030】

表1から、このOLEDに関しては、厚さ方向抵抗率が10Ωcm2のSRLにより、明るさのレベルが約100cd/cm2まで、漏れ電流を10%未満のレベルに減らせることがわかる。しかしこの抵抗率のSRLを通じて流れる漏れ電流は、暗いほどデバイスの電流の大きな割合を占め、最も暗いレベルではデバイスの電流の50%にも達する可能性がある。これは比較的暗い場合であるため、多くの用途では問題にならない可能性がある。漏れ電流は、SRLの抵抗率が大きくなるにつれて小さくなる。約160Ωcm2では、漏れ電流は、6.25cd/cm2という最低動作条件まで、デバイスの電流の10%未満である。160Ωcm2は、SRLによる直列抵抗が最も明るいOLEDデバイスの等価抵抗のかなりの割合になるレベルでもある。したがって例1で考慮した一連の条件下では、厚さ方向抵抗率が約10Ωcm2〜約160Ωcm2である短絡低減層を使用できる。厚さ方向抵抗率が10Ωcm2でさえ、SRLの面抵抗率がデバイスの等価抵抗よりもはるかに大きいことに注意されたい。短絡低減層によるクロストークはしたがって問題でない。

【0031】

例2

例2では、欠陥のサイズがSRLの選択に及ぼす効果を調べる。例2で用いるどのパラメータも例1のパラメータと同じであるが、短絡の面積を変えた点が異なっている。表2には、漏れ電流を顕著に減らすのに必要なSRLの厚さ方向抵抗率の計算結果と、デバイスの直列抵抗を顕著に増大させることが予想されるSRLの厚さ方向抵抗率の計算結果を示してある。

【0032】

【表2】

【0033】

第1列には、欠陥の全面積をcmを単位として示してある。第2列には、明るさが100cd/m2のレベルで漏れ電流を10%未満に減らすのに必要なSRLの厚さ方向抵抗率の値が示してある。第3列にはSRLの厚さ方向抵抗率が示してあり、厚さ方向抵抗率がこの値を超えると大きな直列抵抗がOLEDデバイスに付加される。表2から、欠陥の面積が大きくなると、SRLの厚さ方向抵抗率も比例して大きくなることがわかる。しかし直接抵抗を顕著に大きくする厚さ方向抵抗率は、一定値に留まる。表2から、厚さ方向抵抗率が大きくなるにつれてSRLの有効性が大きくなることが証明される。直列抵抗の付加をあまり大きくすることがないという条件のもとで、厚さ方向抵抗率ができるだけ大きな値のSRL材料を用いることが非常に望ましい。

【0034】

例3

OLEDデバイスの効率を大きくするための多大な努力がこれまでになされてきたため、例3では、デバイスの効率がSRLの選択に及ぼす効果を調べる。例3で用いるどのパラメータも例1のパラメータと同じであるが、デバイスの効率を変えた点が異なっている。表3には、デバイスの直列抵抗を顕著に大きくすることが予想されるSRLの厚さ方向抵抗率の計算結果が示してある。

【0035】

【表3】

【0036】

第1列には、デバイスの効率をcd/Aを単位として示してある。第2列には、明るさのレベルが100cd/m2であるときに漏れ電流をデバイスの電流の10%未満に減らすのに必要なSRLの厚さ方向抵抗率が示してある。第3列にはSRLの厚さ方向抵抗率が示してあり、厚さ方向抵抗率がこの値を超えると大きな直列抵抗がOLEDデバイスに付加される。表3から、デバイスの効率が大きくなると、100cd/m2で漏れ電流をデバイスの電流の10%未満に減らすのに必要なSRLの厚さ方向抵抗率も比例して大きくなることがわかる。直列抵抗を顕著に大きくする厚さ方向抵抗率も比例して大きくなる。デバイス効率が所定の値であるOLEDデバイスでは、厚さ方向抵抗率がこれらの列に示した2つの値の間にあるSRL膜を使用することにより、重要な直列抵抗の問題なしに漏れ電流を減らすことができる。しかし実施例2で説明したように、この範囲内でできるだけ大きな厚さ方向抵抗率を用いることで、より大きなサイズの欠陥に対するSRLの効果を大きくすることが望ましい。

【0037】

例4

この実施例では、動作電圧がSRLの選択に及ぼす効果を調べる。動作電圧はOLEDデバイスの電力効率と直接関係しているため、動作電圧を小さくするための多大な努力がこれまでになされてきた。例4で用いるどのパラメータも例1のパラメータと同じであるが、デバイスの動作電圧を変えた点が異なっている。式3を利用し、漏れ電流を顕著に減らすのに必要なSRLの厚さ方向抵抗率と、デバイスの直列抵抗を顕著に大きくすることが予想される厚さ方向抵抗率を計算した。表4に計算の結果を示してある。

【0038】

【表4】

【0039】

第1列には、デバイスの動作電圧を示してある。第2列には、明るさのレベルが100cd/m2であるときに漏れ電流をデバイスの電流の10%未満に減らすのに必要なSRLの厚さ方向抵抗率が示してある。第3列にはSRLの厚さ方向抵抗率が示してあり、厚さ方向抵抗率がこの値を超えると大きな直列抵抗がOLEDデバイスに付加される。表4から、デバイスの動作電圧が低下すると、100cd/m2で漏れ電流をデバイスの電流の10%未満に減らすのに必要なSRLの厚さ方向抵抗率も比例して小さくなることがわかる。直列抵抗を顕著に大きくする厚さ方向抵抗率も比例して小さくなる。動作電圧が所定の値であるOLEDデバイスでは、厚さ方向抵抗率がこれらの列に示した2つの値の間にあるSRL膜を使用することにより、重要な直列抵抗の問題なしに漏れ電流を減らすことができる。しかし例2で明らかにしたように、この範囲内でできるだけ大きな厚さ方向抵抗率を用いることで、より大きなサイズの欠陥に対するSRLの効果を大きくすることが望ましい。

【0040】

例5

例5では、OLEDデバイスのサイズがSRLの選択に及ぼす効果を調べる。ここで検討している実施例では、単一の画素がOLEDデバイスである。例5で用いるどのパラメータも例1のパラメータと同じであるが、デバイスのサイズを変えた点が異なっている。式3を利用し、漏れを顕著に減らすのに必要なSRLの厚さ方向抵抗率と、デバイスの直列抵抗を顕著に大きくすることが予想される厚さ方向抵抗率を計算した。表5に計算の結果を示してある。

【0041】

【表5】

【0042】

第1列には、デバイスのサイズをcm2単位で示してある。第2列には、明るさのレベルが100cd/m2であるときに漏れ電流をデバイスの電流の10%未満に減らすのに必要なSRLの厚さ方向抵抗率が示してある。第3列にはSRLの厚さ方向抵抗率が示してあり、厚さ方向抵抗率がこの値を超えると大きな直列抵抗がOLEDデバイスに付加される。所定のサイズのOLEDデバイスでは、厚さ方向抵抗率がこれらの列に示した2つの値の間にあるSRL膜を使用することにより、重要な直列抵抗の問題なしに漏れ電流を減らすことができる。しかし例2で明らかにしたように、この範囲内でできるだけ大きな厚さ方向抵抗率を用いることで、より大きなサイズの欠陥に対するSRLの効果を大きくすることが望ましい。表5から、デバイスまたは画素のサイズが小さくなるほど、漏れを少なくするためのSRLの厚さ方向抵抗率が大きくなることがわかる。

【0043】

例6

例6では、1つ以上の大きな発光区画を有するOLEDデバイスのための短絡低減層の設計について調べる。この用途では、大きな発光区画は、面積が0.1cm2以上の区画である。このようなデバイスの一例は、画素のサイズが0.1cm2以上である大面積パッシブ・マトリックスOLEDデバイスである。別の一例は、アメリカ合衆国特許第6,693,296号に記載されているような、発光区画が0.1cm2以上である分割されたモノリシック直列接続構造を有するOLED照明デバイスまたはOLEDイルミネーション・デバイスである。通常は、このデバイスは、輝度レベルが限られた範囲でしか動作しない。式3はこうしたOLEDデバイスにも適用され、この式から、厚さ方向抵抗率の値に関する条件は、高解像度ディスプレイに必要とされる値に関する条件とは非常に異なることがわかる。この実施例では、イルミネーション用の大きな発光区画を有するOLEDデバイスを調べる。OLEDデバイスは、市販されているコンパクトな蛍光灯に匹敵するよう、約2000cd/m2で動作しているときの電力効率が約40 lm/Wでなくてはならない。このような高レベルの電力効率は、駆動電圧の低下と電流効率の増大を通じて実現される可能性が最も高い。駆動電圧が白色発光デバイスの理論的限界値に近い3ボルトまで下がるのであれば、デバイスの電流効率は約40cd/Aになる必要がある。というのも、OLEDデバイスは発光パターンがランバート方式に近いからである。全面積が約10-8cm2である短絡に起因する漏れ損失がここでも10%であることを許容すると、厚さ20nmの短絡低減層に対する抵抗率の条件を計算することができる。その結果を表6に示してある。

【0044】

【表6】

【0045】

第1列には、OLEDイルミネーション・デバイスで使用される可能性のある発光区画のサイズが示してある。第2列には、このOLEDデバイスにおける発光区画のデバイス等価抵抗値が示してある。第3列には、漏れ電流が動作電流の10%である場合にSRLを有する短絡の抵抗値が示してある。その抵抗値は、第2列に示した対応する値の10倍である。第4列には、SRLの対応する厚さ方向抵抗率が示してある。これらの値は、第3列の値に短絡の面積(この計算では10-8cmに等しい)を掛けることによって得られる。第5列には、第4列に示した対応する厚さ方向抵抗率を実現するのに必要なバルクの抵抗率が示してある。この実施例ではSRLの厚さを20nmと仮定した。第6列には、SRLによってOLEDの発光区画に付加される直列抵抗値が示してある。第7列には、SRLからの直列抵抗への寄与が発光区画の等価直列抵抗の10%に制限されている場合に、所定のサイズの発光区画で可能な厚さ方向抵抗率の最大値が示してある。第8列には、SRLの面抵抗が示してある。もし面抵抗率がデバイスの等価抵抗に匹敵する場合には、クロストークが問題になろう。

【0046】

イルミネーションとしての発光区画が1cm2である場合の結果を示す行を参照すると、漏れ電流を発光区画の動作電流の10%未満に制限するためには、短絡低減層の持つ厚さ貫通抵抗率が約6×10-5Ωcm2になっているだけでよいことが計算からわかる。これは、バルクの抵抗率が約6Ωcmであることに対応する。抵抗率の値がより大きいと、短絡からよりよく保護されるが、OLED発光区画にはより大きな直列抵抗が付加される。しかし第7列の値は、OLED発光区画に大きな直列抵抗を付加することなく、60Ωcm2という大きな厚さ貫通抵抗率を使用できることを示している。数値の幅がこのように広いと、実用的なOLEDデバイスを製造する際に他の多くの条件を満たさねばならない可能性のある短絡低減層を発見または開発するのが容易になる。本発明のデバイス構造に電荷注入層280を組み込むと、短絡低減材料の探索または開発がより容易になることを指摘しておくことが重要である。

【0047】

表6から、抵抗率に関する条件が発光区画のサイズに強く依存していることがはっきりとわかる。10cm2の発光区画では、利用できる厚さ方向抵抗率の範囲は6×10-6〜6×10-1Ωcm2に低下し、100cm2の発光区画では、この範囲はさらに狭くなって6×10-2〜6×10-3Ωcm2となる。

【0048】

上記の実施例から、高分解能ディスプレイでは厚さ方向抵抗率の範囲が約10〜1600Ωcm2になっている必要のあることがわかる。この範囲は、10〜1000Ωcm2であることが最も好ましい。大きな発光区画を有するOLEDデバイスでは、利用可能な範囲はより広く、実施例6で考えた動作パラメータの範囲では10-2〜103Ωcm2であるが、動作パラメータの別のセットでは、この範囲外の値でもよい。しかし選択する適切な厚さ方向抵抗率の値は、式3を用いて容易に計算することができる。

【0049】

短絡低減層が発光経路の途中にあるOLEDディスプレイまたはOLEDデバイスでは、短絡低減層は、短絡低減層として効果的に機能するためには、発生した光に合った透明度を持つ必要がある。ここで考えている用途では、合理的な透明度は、OLEDデバイスの発光帯域幅で積分した透過率が80%以上であることと定義される。短絡低減層が発光経路の途中にない場合には、短絡低減層は必ずしも透明でなくてもよい。OLEDディスプレイ装置のコントラストを改善するため、短絡低減層が反射性アノードまたは反射性カソードのための反射防止層としても機能することさえ望ましかろう。

【0050】

短絡低減層のための材料としては、無機酸化物(例えばインジウム酸化物、ガリウム酸化物、亜鉛酸化物、スズ酸化物、モリブデン酸化物、バナジウム酸化物、アンチモン酸化物、ビスマス酸化物、レニウム酸化物、タンタル酸化物、タングステン酸化物、ニオブ酸化物、ニッケル酸化物など)が挙げられる。これら酸化物は不定比化合物であるために導電性である。これら材料の抵抗率は、不定比の程度と移動度に依存する。これらの性質と光の透過率は、堆積条件を変えることによって制御可能である。実現可能な抵抗率と光の透過率の範囲は、不純物をドーピングすることによってさらに拡張することができる。例えばスズ酸化物やインジウム酸化物へのFのドーピング、亜鉛酸化物へのAl、In、Gaのドーピングは、これら酸化物の導電率と光の透過率を改善することがわかっている。これら酸化物のうちの2種類以上を混合することにより、さらに範囲を広げることができる。例えばインジウム酸化物とスズ酸化物の混合物、インジウム酸化物と亜鉛酸化物の混合物、亜鉛酸化物とスズ酸化物の混合物、カドミウム酸化物とスズ酸化物の混合物は、最もよく用いられてきた透明な導電体である。

【0051】

従来技術では、たいていの場合、バルクの導電率が10-3Ωcm以下という大きな導電率の透明な導体が注目されてきた。このような材料は、短絡低減層として用いるには導電性がありすぎる。しかしこれら酸化物を用いた抵抗率の大きな薄膜が、ガス・センサー、帯電防止コーティングなどの用途で使用できることもわかっている。抵抗率のより大きな薄膜は、導電率の大きな透明な導電体に関して最適化した組成と堆積条件を変えることによって調製できる。より大きな抵抗率は、特に、モリブデン酸化物、バナジウム酸化物、アンチモン酸化物、ビスマス酸化物、レニウム酸化物、タンタル酸化物、タングステン酸化物、ニオブ酸化物、ニッケル酸化物のいずれかをを含む材料を用いて実現することもできる。堆積条件を適切に制御することにより、またこれら酸化物を組み合わせた後、より導電性のある他の酸化物(例えばインジウム酸化物、ガリウム酸化物、亜鉛酸化物、スズ酸化物など)を混合することにより、大きな発光区画を有するOLEDデバイスと高分解能OLEDディスプレイ装置の両方での必要性を満たす広い範囲の抵抗率を得ることができる。

【0052】

短絡低減層で用いるのに適した他の材料として、導電率のより大きな酸化物材料と絶縁材料(酸化物、フッ化物、窒化物、硫化物の中から選択する)の混合物などがある。この混合物層の抵抗率は、これら2種類の材料の割合を調節することにより、望む範囲にすることができる。例えばPalら(A.M. Pal、A.J. Adorjan、P.D. Hambourger、J.A. Dever、H. Fu、アメリカ物理学会、OFM96会議の要約集CE.07)は、ITOとフッ化マグネシウム(MgF2)の混合物からなる薄膜が3×10-5〜3×103Ωcmという範囲の抵抗率をカバーすることを報告している。この混合薄膜は、従来の薄膜堆積法(例えばスパッタリング、蒸着、化学蒸着、プラズマ支援化学蒸着など)で調製することができる。酸化物膜に関しては、酸素または酸素含有ガス(例えば水蒸気やオゾン)を蒸着中に導入することで、組成と膜の性質を制御することができる。

【0053】

Minami(MRS Bulletin、2000年8月)は、導電性酸化物の調製と性質に関する詳細な概説を発表した。彼は、上に示したたいていの酸化物材料は仕事関数が約4.0eV〜5.0eVであることを示した。これらの値は正孔注入体として機能するには小さすぎ、電子注入体として機能するには大きすぎる。短絡低減層用に選択した材料が十分な電荷を注入できない場合には、本発明では、第1の電極がアノードだと短絡低減層と有機EL素子の間に正孔注入層を追加し、第1の電極がカソードだと短絡低減層と有機EL素子の間に電子注入層を追加する。電荷注入層を付加することにより、短絡低減層のための材料選択の範囲が広がり、他の追加条件に基づいてさらに洗練された選択を行なうことが可能になる。正孔注入層で用いるのに適した材料としては、アメリカ合衆国特許第4,720,432号に記載されているポルフィリン化合物、譲受人に譲渡されたアメリカ合衆国特許第6,208,075号に記載されているプラズマ堆積させたフルオロカーボン・ポリマーなどがある。有機ELデバイスで有用であることが報告されている別の正孔注入材料は、ヨーロッパ特許公開第0,891,121 A1号および第1,029,909 A1号に記載されているとともに、Tikitoら(J. Phys. D.、第29巻、2750ページ、1996年)によって記載されており、例えば、バナジウム酸化物(VOx)、モリブデン酸化物(MoOx)、ニッケル酸化物(NiOx)などがある。電子注入層としては、アメリカ合衆国特許第5,608,287号、第5,776,622号、第5,776,623号、第6,137,223号、第6,140,763号に記載されているもの(その開示内容は、参考としてこの明細書に組み込まれているものとする)を利用できる。仕事関数が小さなアルカリ金属またはアルカリ土類金属(例えばLi、Cs、Ca、Mg)を含む薄膜を用いることができる。さらに、仕事関数が小さなこれら金属をドープした有機材料も、電子注入層として使用することができる。具体例は、LiまたはCsをドープしたAlqである。

【0054】

本発明の別の一実施態様では、短絡低減層が有機EL素子と第2の電極層の間に配置される。この実施態様における短絡低減層の有効性は、短絡低減層が有機EL素子と第1の電極層の間に配置されている実施態様と同様である。短絡低減層の有効性は、短絡低減層を有機EL素子と第1の電極層の間と、有機EL素子と第2の電極層の間の両方に用いることによってさらに大きくすることができる。

【0055】

本発明の別の一実施態様では、OLEDデバイスは、アメリカ合衆国特許第6,337,492号に記載されているような積層式OLEDデバイスである。図3を参照すると、OLEDデバイス300は、積層式OLEDデバイスであることがわかる。基板310の上には、3つの有機発光デバイス331、332、333が存在していて、それぞれのデバイスは、正孔輸送層(331c、332c、333c)と、発光層(331b、332b、333b)と、電子輸送層(331a、332a、333a)を備えている。有機発光デバイス相互の間には、その有機発光デバイスの上にある正孔輸送層に正孔を供給し、その有機発光デバイスの下にある電子輸送層に電子を供給するコネクタ371と372が存在している。図3では、短絡低減層360は、有機発光デバイス331とコネクタ371の間に配置されている状態が図示されているが、第1の電極層320と有機発光デバイス331の間、コネクタ371と有機発光デバイス332の間、有機発光デバイス332とコネクタ372の間、コネクタ372と有機発光デバイス333の間、有機発光デバイス333と第2の電極層340の間に配置することもできる。本発明では、1つ以上の短絡低減層を使用することができる。ここでも、本発明によれば、選択した短絡低減層が電荷を十分に注入しない場合には、電荷注入層があると好ましい。

【0056】

本発明の別の一実施態様では、OLEDデバイスがマイクロキャビティ構造を有する。このデバイスは、基板と、金属からなる第1のアノード層(金属は、Au、Ag、Mg、Ca、またはこれらの合金の中から選択することが好ましい)と、短絡低減層と、有機EL素子と、金属からなる第2のアノード層(金属は、Au、Al、Ag、Mg、Ca、またはこれらの合金の中から選択することが好ましい)を備えている。金属製電極の1つは実質的に不透明かつ反射性であり、他方の電極は半透明である。2つの反射性金属製電極が存在しているため、デバイスはマイクロキャビティ構造を有する。この構造では、共鳴条件において光の強い干渉が起こる。共鳴波長近傍の発光は増幅され、共鳴波長から離れた発光は抑制される。

【0057】

従来は電極層と有機EL素子の間に無機層を使用していたが、短絡が少なくなる可能性のあることは認められておらず、使用されるスペーサ層は、短絡低減層として有効に機能するには導電性がありすぎたり、十分に透明でなかったりしたことに注意されたい。例えばTokito他(S. Tokito、K. Noda、Y. Taga、J. Phys. D. Appl. Phys.、第29巻、1996年、2750〜2753ページ)には、正孔注入層としてVOx、MoOx、RuOxをスパッタリングで厚さ30nmにした薄膜を用いることが報告されている。薄膜は、発光経路の途中に堆積されているが、どの薄膜の透光率も70%以下であり、最後の2つの薄膜の抵抗率は、短絡低減層として有効に機能するには小さすぎた。

【0058】

例7

ITOでコーティングしたガラス基板の上に一連のOLEDデバイスを作った。ITOアノード層の厚さは約42nmであり、そのITO層の上に短絡低減層(SRL)と、HTL層として機能する15nmのN,N'-ジ(ナフタレン-1-イル)-N,N'-ジフェニル-ベンジジン(NPB)層と、ETLおよびLELとして機能する15nmのトリス(8-ヒドロキシキノリン)アルミニウム(III)(Alq)層と、EILとして機能する厚さ1nmのLi層と、カソード層として機能する厚さ100nmのAgを堆積させた。ITOはガラス上にすでにコーティングされたものを販売者から購入したが、そのITOを除くどの層も、チェンバー内の真空度を約10-6トルにした真空蒸着によってコーティングした。熱で蒸発させたMoO3層をSRLとして使用した。MoO3層は、Taボートから約0.1nm/秒の速度で2nm〜30nmの厚さに蒸着した。供給源の材料は、純度99.9998%のMoO3粉末であった。膜の組成は調べなかったが、MoO3の組成からわずかにずれている可能性がある。膜は可視光に対して透明で透過率が約90%であり、電気的抵抗率は約105Ωcmであった。これらの層を堆積させた後、デバイスを蒸着チェンバーからドライ・ボックスに移して封入した。完成したデバイスの構造は、ガラス/ITO(42)/MoO3(さまざまな値)/NPB(15)/AlQ(15)/Li(0.1)/Ag(100)と表記される。括弧内の数値は、ナノメートルを単位として表記した厚さである。

【0059】

合計で12枚の基板をコーティングし、そのときMoO3の厚さ1つにつき2枚の基板を使用した。それぞれの基板上には、0.1cm2のOLEDデバイスが4個存在しており、MoO3の厚さ1つにつき合計で8個のOLEDデバイスを用意した。この実験では合計で48個のOLEDデバイスが存在していた。これらデバイスをOLEDの性能に関して調べた。予想通り、MoO3層が2nmの8個のデバイスのうちの7個が短絡した。というのも、有機層の全厚さが30nmというのは薄すぎるため、デバイスに短絡が極めて発生しやすくなり、2nmのMoO3は短絡低減層として十分に機能しないからである。短絡したデバイスの数は、MoO3を厚くするにつれて少なくなった。MoO3層の厚さが12nm以上だと、30個のデバイスのうちで4個だけが短絡した。

【0060】

しかしOLEDデバイスに短絡が存在する確率は、有機EL層の厚さに強く依存することを指摘しておく必要がある。有機EL層が薄くなるほど、短絡が生じる確率が大きくなる。典型的なOLEDデバイスでは、厚さが100nmを超える有機EL層が用いられる。短絡の数をできるだけ少なくするため、有機EL層の厚さを300nm以上にすることがしばしばある。この実施例では、短絡低減層の有効性を示すため、極めて薄い30nmという厚さにして、十分な数の短絡が確実に存在しているようにした。図4に示したデータから、極めて薄い有機EL層を有するこれらOLEDデバイスで短絡を減らすのに短絡低減層が有効であったことがわかる。同じ有効な効果が、はるかに厚い有機EL層を有するOLEDデバイスでも予想される。

【0061】

例8

短絡低減層の有効性をさらに証明するため、別の一連のOLEDデバイスを作った。製造条件とこれらデバイスの層構造は実施例1と同様であるが、この実施例ではMoO3短絡低減層とNPBからなるHTL層を合計した厚さが75nmという一定値に維持されるようにした点が異なっている。5枚の基板を利用し、それぞれの基板上に4つのOLEDデバイスを作った。その結果、0.1cm2のOLEDデバイスが全部で20個得られた。図5には、短絡していないデバイスの数をMoO3短絡低減層の厚さに対してプロットしてある。ここでも、MoO3層が厚くなるにつれて短絡していないデバイスの数が増えることが明らかである。この場合には、MoO3が厚くなるにつれて有機EL層の厚さが実際には薄くなり、そのことによって短絡の確率が大きくなったはずであることを指摘しておかねばならない。実際のデータで見られた逆の傾向は、短絡低減層の利点が、有機層の厚さ低下に起因する短絡確率の増加に打ち勝ったことを示している。

【0062】

本発明をいくつかの好ましい実施態様を特に参照して詳細に説明したが、本発明の精神と範囲の中でさまざまな変形や変更が可能であることが理解されよう。

【符号の説明】

【0063】

100、200、300 OLEDデバイス

110、210、310 基板

120、220、320 第1の電極層

130、230 有機EL層

140、240、340 第2の電極層

150、250 短絡

260 短絡低減層

280 電荷注入層

331、332、333 有機発光デバイス

331a、332a、333a 電子輸送層

331b、332b、333b 発光層

331c、332c、333c 正孔輸送層

360 短絡低減層

371、372 コネクタ

【技術分野】

【0001】

本発明は、OLEDデバイスとOLEDディスプレイにおける短絡の減少に関する。

【背景技術】

【0002】

有機エレクトロルミネッセンス(EL)デバイスまたは有機発光ダイオード(OLED)は、印加した電圧に応答して光を出す電子デバイスである。Tangらは、Applied Physics Letters、第51巻、913ページ、1987年;Journal of Applied Physics、第65巻、3610ページ、1989年;譲受人に譲渡されたアメリカ合衆国特許第4,769,292号において、高効率のOLEDを提示している。そのとき以来、ポリマー材料を含む別の層構造を持つ多数のOLEDが発表され、デバイスの性能が向上してきている。

【0003】

OLEDは、アノードと、カソードと、アノードとカソードに挟まれた有機EL素子とを備える薄膜デバイスである。動作中は電圧がアノードとカソードの間に印加されることで、電子がカソードから注入され、正孔がアノードから注入される。適切に構成されているならば、注入された電子と正孔が有機EL素子内の発光層で再結合し、これら電荷担体の再結合によってデバイスから光が出る。一般に、有機EL素子は厚さが約100〜500nmであり、電極間に印加される電圧は約3〜10ボルトであり、動作電流は約1〜20mA/cm2である。

【0004】

アノードとカソードの間はわずかしか離れていないため、OLEDデバイスでは短絡という欠陥が発生しやすい。OLEDデバイスの構造中のピンホール、割れ目、段差や、コーティングの凹凸などにより、アノードとカソードが直接接触したり、欠陥のある領域で有機層が他の領域よりも薄くなったりする可能性がある。欠陥のある領域は、電流が流れるための低抵抗経路を提供するため、有機EL素子を流れる電流が少なくなったり、極端な場合には電流が流れなくなったりする。したがってOLEDデバイスの光出力が低下したり消失したりする。マルチ画素ディスプレイ装置では、短絡によって発光しなかったり平均以下の強度の光しか出さなかったりする死んだ画素が生まれる可能性があるため、ディスプレイの品質が低下する。照明その他の低解像度の用途では、短絡によってかなりの領域が機能しなくなる可能性がある。短絡という問題があるため、OLEDデバイスは一般にクリーン・ルームの中で製造される。しかしクリーンな環境でさえ、短絡をなくすのに有効ではない。多くの場合、2つの電極の間隔を大きくして短絡の数を減らすため、有機層の厚さは、デバイスが機能する上で実際に必要であるよりも厚くされる。この方法だとOLEDデバイスの製造コストが上昇し、しかもこの方法でさえ、短絡を完全になくすことはできない。

【0005】

日本国特開2002-100483Aには、アノードの透明な結晶性導電膜が局所的に突起していることに起因する短絡を、透明なアモルファス導電膜を透明な結晶性導電膜の上に堆積させることによって減らす方法が開示されている。アモルファス膜の滑らかな表面により、結晶膜からの局所的突起がOLEDデバイスに短絡またはダーク・スポットを形成するのを阻止できるという主張がなされている。この方法の有効性は疑わしい。なぜなら、透明なアモルファス導電膜の形成に利用する真空蒸着法は平均化機能を持たないため、透明なアモルファス導電膜の表面は、その下にある透明な結晶性導電膜の表面をそのまま再現していることが予想されるからである。さらに、この方法は、ダスト粒子、断片、構造上の不連続性や、OLEDの製造法で一般的な他の原因によるピンホールの問題に対処していない。

【0006】

日本国特開2002-208479Aには、透明な金属酸化物からなる中間抵抗膜(その膜の厚さは10nm〜10μmであり、膜厚方向の抵抗値は0.01〜2Ωcm2であり、この抵抗膜の表面におけるイオン化エネルギーは5.1eV以上である)を、ガラスまたは樹脂からなる透明な基板の上に透明電極パターンとして形成された正電極上または負電極上の発光領域の全体または一部の上に被せることによって短絡を減らす方法が開示されている。この方法には利点があるものの、記載されている範囲の抵抗率は、多くのOLEDディスプレイまたはOLEDデバイスで短絡に起因する漏れ電流を減らすのに有効ではない。さらに、イオン化エネルギーの条件によって選択できる材料が厳しく制限される。またこの条件では、性能が優れていて寿命が長いOLEDデバイスを実現する上で極めて重要であることが知られている適切な正孔注入が保証されない。さらに、イオン化エネルギーの大きな材料は電子を注入できないため、カソードと有機発光層の間で利用することはできない。カソード材料と有機発光層の間に抵抗膜を用いること、またはカソードと有機発光材料の間、およびアノードと有機発光材料の間の両方に抵抗膜を用いることが望ましい場合がしばしばある。

【発明の概要】

【発明が解決しようとする課題】

【0007】

したがって本発明の1つの目的は、短絡に起因する漏れ電流が減るという改善がなされたOLEDデバイスまたはOLEDディスプレイを提供することである。

【課題を解決するための手段】

【0008】

この目的は、

(a)基板と;

(b)この基板の上に配置された第1の電極層と;

(c)この第1の電極層の上に配置された無機短絡低減層と;

(d)この無機短絡低減層の上に配置された電荷注入層と;

(e)この電荷注入層の上に配置された有機EL素子と;

(f)この有機EL素子の上に配置された第2の電極層を備えていて、上記短絡低減層が、短絡に起因する漏れ電流と、それに付随する発光効率の損失とを減らすのに十分な厚さと抵抗率を持つように選択されているOLEDデバイスによって達成される。

【発明の効果】

【0009】

短絡が起こったときにその効果を最少にできることが、本発明の1つの利点である。

【図面の簡単な説明】

【0010】

【図1】短絡のある従来技術のデバイスの概略断面図である。

【図2】本発明によるOLEDデバイスの概略断面図である。

【図3】本発明による積層型OLEDデバイスの概略断面図である。

【図4】良好なOLEDデバイスの数を短絡低減層の厚さの関数として示したグラフである。

【図5】良好なOLEDデバイスの数を短絡低減層の厚さの関数として示したグラフである。

【発明を実施するための形態】

【0011】

図1は、短絡のある従来のOLEDデバイス100の概略断面図である。このデバイス100は、基板110と、第1の電極層120と、有機EL素子130と、第2の電極層140を備えている。電極層の一方はアノードであり、他方の電極層はカソードである。物理的な保護その他の目的で第2の電極層140の上に他の層が存在していることがしばしばある。カソードと有機EL素子130の間に有機または無機の電子注入層が存在し、アノードと有機EL素子130の間に有機または無機の正孔注入層が存在していることもしばしばある。

【0012】

ボトム・エミッション型OLEDデバイスでは、基板110は、OLEDデバイス100から発生する光に対して透明である。基板110の一般的な材料はガラスまたはプラスチックである。第1の電極層120も発生する光に対して透明である。第1の電極層120の一般的な材料は、透明な導電性酸化物(インジウム-スズ酸化物(ITO)、インジウム-亜鉛酸化物(IZO)など)である。あるいは第1の電極層120は、半透明な金属(例えばAg、Au、Mg、Ca)またはその合金で製造することもできる。半透明な金属を第1の電極層120として用いる場合には、OLEDデバイス100はマイクロキャビティ構造を持つと言われる。有機EL素子130は少なくとも1つの発光層(LEL)を備えているが、他の機能層(例えば電子輸送層(ETL)、正孔輸送層(HTL)、電子阻止層(EBL)、正孔阻止層(HBL)など)も備えていることがしばしばある。以下の説明は機能層の数とは無関係であり、有機EL素子130の材料の選択とも無関係である。第2の電極層140は、通常は、反射性金属層(例えばAl、Ag、Au、Mg、Ca、またはその合金)である。正孔注入層を有機EL素子130とアノードの間に追加し、電子注入層を有機EL素子130とカソードの間に追加することがしばしばある。動作中は、正電位をアノードに印加し、負電位をカソードに印加する。電子がカソードから有機EL素子130に注入されると、印加した電場によって駆動されてアノードに向かって移動する。それに対して正孔がアノードから有機EL素子130に注入されると、印加した電場によって駆動されてカソードに向かって移動する。電子と正孔が有機EL素子130の中で結合すると光が発生し、OLEDデバイス100から放出される。

【0013】

トップ・エミッション型OLEDデバイスでは、光が基板110とは反対の方向に出る。このような場合、基板110を出る光に対して不透明にすることができ、金属やSiなどの材料を基板110に使用することができる。第1の電極層120は不透明で反射性のあるものにできるのに対し、第2の電極層140は、透明または半透明になっている必要がある。

【0014】

図1には、有機EL素子130内で有機材料が不足している領域によって生じる短絡150も簡単に図示してある。以下の説明は、有機EL素子130内の有機材料の厚さがデバイスの残りの領域の厚さと比べて実質的に薄い領域によって生じる短絡にも当てはまる。短絡には可能な多くの原因がある。例えば基板110の上にダスト粒子または断片があると有機EL素子130を堆積させている間に材料の流れが局所的に止まる可能性があるため、有機膜の厚さにギャップができたり有機膜の厚さが実質的により薄くなったりし、堆積された第1の電極層120と第2の電極層140の間の電気抵抗が小さくなる。粒子または断片は、基板を真空チェンバーの中に装填する前に大気中からやってくる可能性や、第1の電極層120または有機層を堆積させている間にボートから供給材料の粒子が放出されたり、堆積チェンバーの壁面や固定物から堆積物が剥がれたりすることによって発生する可能性がある。こうした粒子または断片は、有機層の堆積中または堆積後に、その有機堆積物に発生する機械的振動や応力によって剥がれ落ちたり、単に重力によって剥がれ落ちたりする可能性もある。有機物堆積プロセスの間に基板110上に存在していてその後剥がれ落ちる粒子や断片は、最も大きなダメージを引き起こす可能性がある。この場合、粒子や断片は有機材料が基板110上に堆積されるのを阻止し、粒子や断片が剥がれ落ちる場合には、第1の電極層120の領域があとから堆積される第2の電極層140に対して完全に露出した状態になる。

【0015】

短絡の別の原因としては、OLEDデバイス構造の段差がある。それは例えばアクティブ・マトリックスOLEDディスプレイ装置のTFT(薄膜トランジスタ)構造に付随する段差であり、基板110の表面上または第1の電極層120の表面上の有機層や凹凸によっては完全にカバーすることができない。短絡150により、第2の電極層140が直接に、または有機層の非常に薄い部分を通じて第1の電極層120と接触し、デバイスに電流を流す低抵抗の経路が提供される。電圧をアノードとカソードの間に印加するとき、かなりの電流が、アノードからデバイスの無欠陥領域を迂回して短絡150を通ってカソードへと流れることができる。したがって短絡はOLEDデバイス100の発光出力を顕著に低下させ、多くの場合にOLEDデバイス100がまったく発光しなくなる可能性がある。

【0016】

図2は、本発明の一実施態様によるOLEDデバイス200の概略断面図である。このOLEDデバイス200は、基板210と、第1の電極層220と、有機EL素子230と、第2の電極層240を備えている。第1の電極層220と有機EL素子230の間には短絡低減層(SRL)260と電荷注入層280が配置されている。第1の電極層220がアノードである場合には、電荷注入層280は正孔注入層である。それに対して第1の電極層220がカソードである場合には、電荷注入層280は電子注入層である。図2では、電荷注入層280が短絡250を覆うように描かれている。多くの場合、電荷注入層280が短絡250の位置に存在していなくてもよい。電荷注入層280が短絡250の位置にこのように存在していない状態は、例えば電荷注入層280が有機層コーティング・プロセスの一部としてコーティングされる場合や、短絡250が基板200または第1の電極層220の表面の凹凸によって生じる場合に起こる可能性がある。電荷注入層280は通常は非常に薄くて数ナノメートル以下であるため、どちらの場合にも電荷注入層280は短絡を通る抵抗にそれほど寄与せず、以下の説明には影響しない。

【0017】

OLEDデバイスを本発明に従って構成する場合、有機EL素子230に短絡250がある場所では第2の電極層240がピンホール内で第1の電極層220と直接接触することはなく、短絡低減層260を通じての接触となる。短絡低減層260は、適切に選択すると、第1の電極層220と第2の電極層240の間に抵抗項Rsrlを付加することができ、短絡250を通じた漏れ電流を実質的に減らす。本発明の効果は以下のようにして分析される。AをOLEDデバイス200の面積(単位はcm2)、αをOLEDデバイス200内のあらゆる短絡の全面積(単位はcm2)、tを厚さ(単位はcm)、ρを短絡低減層260のバルクの抵抗率(単位はΩcm)、I0を動作電流密度(単位はmA/cm2)、V0をOLEDデバイス200の動作電圧(単位はボルト)であるとすると、短絡を流れる電流は以下のように計算される。

【0018】

【数1】

【0019】

短絡低減層260は、短絡250のマイナスの影響を減らし、デバイスの性能を許容できるレベルまで向上させる。短絡のマイナスの影響は、パラメータf、すなわち短絡を流れる漏れ電流をデバイスの全電流で割った比から評価することができる。

【0020】

【数2】

【0021】

許容可能な比f0を実現するには、短絡低減層260の厚さ方向抵抗率ρtの最小値が以下のようになっていなくてはならない。

【0022】

【数3】

【0023】

したがって有効な短絡低減層260として使用できる材料は、面積Aと;OLEDデバイス200の動作条件V0およびI0と;許容できる性能損失のレベルf0と;短絡の全面積αと;デバイスに組み込むことのできる短絡低減層260の厚さtとを考慮して選択される。

【0024】

短絡低減層260の厚さは、2つの考慮事項に基づいて選択する。1)典型的なOLEDデバイスは、有機層を合計した厚さが100〜300nmであり、この層の厚さは、デバイスの発光効率が最適になるように光学的にチューニングされる。短絡低減層はデバイスの光学的構造の一部となるため、その厚さは約200nmを超えてはならない。短絡低減層があまりに厚くてもOLEDデバイスの製造コストが上昇する。2)短絡低減層は、短絡を効果的に覆うのに十分な厚さがなければならない。合理的な下限は約20nmである。本発明では、短絡低減層の厚さが20nm〜200nmの範囲であることが好ましい。

【0025】

OLEDデバイスは多くの異なった用途で用いられている。OLEDデバイスは、デバイスの面積と動作条件が非常に異なっていてもよい。例えば照明の用途では、OLEDデバイスは、大きな発光区画に分割されることが多く(アメリカ合衆国特許第6,693,296号)、その区画は1平方センチメートルよりも大きく、比較的少数のレベルの電流密度で動作する。エリア・カラー・ディスプレイでは、画素はより小さくて数平方ミリメートルのオーダーになるであろうが、動作条件はここでも大きくは違わない。画素化された高解像度OLEDディスプレイでは、背面がアクティブ・マトリックスであれパッシブ・マトリックスであれ、画素ははるかに小さくて0.3mm×0.3mm以下のオーダーになり、しかもOLEDデバイスがダイナミック・レンジを提供する必要がある。8ビットの解像度では、デバイスの動作電流の範囲が1〜256倍となっている必要がある。式3は、こうしたさまざまなOLEDデバイスが短絡低減層として広範な材料を必要とするであろうことを示唆している。

【実施例】

【0026】

例1

短絡低減層の選択の一例として、画素化された高解像度OLEDディスプレイの単一の画素に短絡が与える影響を分析する。この分析では、あるサイズの1つの短絡が画素内に存在していると仮定する。その代わりにより小さな短絡(例えば基板または第1の電極層の凹凸によって起こる欠陥)がいくつか存在していて単一の欠陥と全面積が同じである場合には、分析の結果は同じであろう。画素のサイズは0.1mm×0.1mmであると仮定し、欠陥のサイズは、ダスト粒子の典型的なサイズである1μm×1μmであると仮定する。

【0027】

従来のボトム・エミッション型アクティブ・マトリックスOLEDディスプレイは、最も明るくしたときの輝度が約200cd/m2である。この明るさは、開口比が約0.25のOLEDディスプレイにより、透過率が約50%の偏光膜を通じて実現される。したがって最も明るくしたときのOLEDデバイスの表面における実際の明るさは、約1600cd/m2である。8ビットの色深度では、OLEDデバイスは、約6.3cd/m2まで動作する必要もある。従来のOLEDデバイスの効率は約10cd/Aであり、動作電圧は約10ボルトである。これは、このデバイスが約0.063mA/cm2から約16mA/cm2まで動作せねばならないことを意味する。この実施例と以下の実施例では、デバイスの動作電圧は、動作電流とは独立であると仮定する。実際ほとんどのデバイスでは、動作電圧は動作電流の対数で変化する。これら実施例では約2.5桁にわたる範囲の動作電流を考慮しているため、一定電圧の仮定は合理的かつ無難な仮定である。OLEDディスプレイにおいて漏れを効果的に減らすのに必要な厚さ20nmの短絡低減層の抵抗率を約1μm×1μmのサイズの欠陥に関して計算し、計算した結果を表1に示してある。表1には、短絡低減層に起因する直列抵抗の増加と、短絡低減層の面抵抗率も示してある。後者の値は、画素間で起こる可能性のあるクロストークを評価するのに必要とされる。

【0028】

【表1】

【0029】

第1列には、明るさのレベルがcd/m2を単位としていくつか示してあり、明るさの8ビット表示になっている。第2列には、これらレベルでのOLEDデバイスの動作電流密度が示してある。第3列には、これらレベルでのOLED画素のデバイス等価抵抗の値が示してある。第4列には、漏れ電流が動作電流の10%である場合に、短絡の位置にSRLを有するときの短絡の抵抗値が示してある。これら抵抗値は、第3列に示した対応する値の10倍である。第5列には、SRLの対応する厚さ方向抵抗率が示してある。これらの値は、第4列の値に短絡の面積(この計算では10-8cm2に等しい)を掛けることによって得られる。第6列には、第5列に示した対応する厚さ方向抵抗率を実現するのに必要なバルクの抵抗率が示してある。この実施例では、SRLの厚さを20nmと仮定した。第7列には、SRLによってOLEDデバイスに付加される直列抵抗の値が示してある。第8列には、SRLの面抵抗率が示してある。もし面抵抗率がデバイスの等価抵抗に匹敵する場合には、クロストークが問題になろう。

【0030】

表1から、このOLEDに関しては、厚さ方向抵抗率が10Ωcm2のSRLにより、明るさのレベルが約100cd/cm2まで、漏れ電流を10%未満のレベルに減らせることがわかる。しかしこの抵抗率のSRLを通じて流れる漏れ電流は、暗いほどデバイスの電流の大きな割合を占め、最も暗いレベルではデバイスの電流の50%にも達する可能性がある。これは比較的暗い場合であるため、多くの用途では問題にならない可能性がある。漏れ電流は、SRLの抵抗率が大きくなるにつれて小さくなる。約160Ωcm2では、漏れ電流は、6.25cd/cm2という最低動作条件まで、デバイスの電流の10%未満である。160Ωcm2は、SRLによる直列抵抗が最も明るいOLEDデバイスの等価抵抗のかなりの割合になるレベルでもある。したがって例1で考慮した一連の条件下では、厚さ方向抵抗率が約10Ωcm2〜約160Ωcm2である短絡低減層を使用できる。厚さ方向抵抗率が10Ωcm2でさえ、SRLの面抵抗率がデバイスの等価抵抗よりもはるかに大きいことに注意されたい。短絡低減層によるクロストークはしたがって問題でない。

【0031】

例2

例2では、欠陥のサイズがSRLの選択に及ぼす効果を調べる。例2で用いるどのパラメータも例1のパラメータと同じであるが、短絡の面積を変えた点が異なっている。表2には、漏れ電流を顕著に減らすのに必要なSRLの厚さ方向抵抗率の計算結果と、デバイスの直列抵抗を顕著に増大させることが予想されるSRLの厚さ方向抵抗率の計算結果を示してある。

【0032】

【表2】

【0033】

第1列には、欠陥の全面積をcmを単位として示してある。第2列には、明るさが100cd/m2のレベルで漏れ電流を10%未満に減らすのに必要なSRLの厚さ方向抵抗率の値が示してある。第3列にはSRLの厚さ方向抵抗率が示してあり、厚さ方向抵抗率がこの値を超えると大きな直列抵抗がOLEDデバイスに付加される。表2から、欠陥の面積が大きくなると、SRLの厚さ方向抵抗率も比例して大きくなることがわかる。しかし直接抵抗を顕著に大きくする厚さ方向抵抗率は、一定値に留まる。表2から、厚さ方向抵抗率が大きくなるにつれてSRLの有効性が大きくなることが証明される。直列抵抗の付加をあまり大きくすることがないという条件のもとで、厚さ方向抵抗率ができるだけ大きな値のSRL材料を用いることが非常に望ましい。

【0034】

例3

OLEDデバイスの効率を大きくするための多大な努力がこれまでになされてきたため、例3では、デバイスの効率がSRLの選択に及ぼす効果を調べる。例3で用いるどのパラメータも例1のパラメータと同じであるが、デバイスの効率を変えた点が異なっている。表3には、デバイスの直列抵抗を顕著に大きくすることが予想されるSRLの厚さ方向抵抗率の計算結果が示してある。

【0035】

【表3】

【0036】

第1列には、デバイスの効率をcd/Aを単位として示してある。第2列には、明るさのレベルが100cd/m2であるときに漏れ電流をデバイスの電流の10%未満に減らすのに必要なSRLの厚さ方向抵抗率が示してある。第3列にはSRLの厚さ方向抵抗率が示してあり、厚さ方向抵抗率がこの値を超えると大きな直列抵抗がOLEDデバイスに付加される。表3から、デバイスの効率が大きくなると、100cd/m2で漏れ電流をデバイスの電流の10%未満に減らすのに必要なSRLの厚さ方向抵抗率も比例して大きくなることがわかる。直列抵抗を顕著に大きくする厚さ方向抵抗率も比例して大きくなる。デバイス効率が所定の値であるOLEDデバイスでは、厚さ方向抵抗率がこれらの列に示した2つの値の間にあるSRL膜を使用することにより、重要な直列抵抗の問題なしに漏れ電流を減らすことができる。しかし実施例2で説明したように、この範囲内でできるだけ大きな厚さ方向抵抗率を用いることで、より大きなサイズの欠陥に対するSRLの効果を大きくすることが望ましい。

【0037】

例4

この実施例では、動作電圧がSRLの選択に及ぼす効果を調べる。動作電圧はOLEDデバイスの電力効率と直接関係しているため、動作電圧を小さくするための多大な努力がこれまでになされてきた。例4で用いるどのパラメータも例1のパラメータと同じであるが、デバイスの動作電圧を変えた点が異なっている。式3を利用し、漏れ電流を顕著に減らすのに必要なSRLの厚さ方向抵抗率と、デバイスの直列抵抗を顕著に大きくすることが予想される厚さ方向抵抗率を計算した。表4に計算の結果を示してある。

【0038】

【表4】

【0039】

第1列には、デバイスの動作電圧を示してある。第2列には、明るさのレベルが100cd/m2であるときに漏れ電流をデバイスの電流の10%未満に減らすのに必要なSRLの厚さ方向抵抗率が示してある。第3列にはSRLの厚さ方向抵抗率が示してあり、厚さ方向抵抗率がこの値を超えると大きな直列抵抗がOLEDデバイスに付加される。表4から、デバイスの動作電圧が低下すると、100cd/m2で漏れ電流をデバイスの電流の10%未満に減らすのに必要なSRLの厚さ方向抵抗率も比例して小さくなることがわかる。直列抵抗を顕著に大きくする厚さ方向抵抗率も比例して小さくなる。動作電圧が所定の値であるOLEDデバイスでは、厚さ方向抵抗率がこれらの列に示した2つの値の間にあるSRL膜を使用することにより、重要な直列抵抗の問題なしに漏れ電流を減らすことができる。しかし例2で明らかにしたように、この範囲内でできるだけ大きな厚さ方向抵抗率を用いることで、より大きなサイズの欠陥に対するSRLの効果を大きくすることが望ましい。

【0040】

例5

例5では、OLEDデバイスのサイズがSRLの選択に及ぼす効果を調べる。ここで検討している実施例では、単一の画素がOLEDデバイスである。例5で用いるどのパラメータも例1のパラメータと同じであるが、デバイスのサイズを変えた点が異なっている。式3を利用し、漏れを顕著に減らすのに必要なSRLの厚さ方向抵抗率と、デバイスの直列抵抗を顕著に大きくすることが予想される厚さ方向抵抗率を計算した。表5に計算の結果を示してある。

【0041】

【表5】

【0042】

第1列には、デバイスのサイズをcm2単位で示してある。第2列には、明るさのレベルが100cd/m2であるときに漏れ電流をデバイスの電流の10%未満に減らすのに必要なSRLの厚さ方向抵抗率が示してある。第3列にはSRLの厚さ方向抵抗率が示してあり、厚さ方向抵抗率がこの値を超えると大きな直列抵抗がOLEDデバイスに付加される。所定のサイズのOLEDデバイスでは、厚さ方向抵抗率がこれらの列に示した2つの値の間にあるSRL膜を使用することにより、重要な直列抵抗の問題なしに漏れ電流を減らすことができる。しかし例2で明らかにしたように、この範囲内でできるだけ大きな厚さ方向抵抗率を用いることで、より大きなサイズの欠陥に対するSRLの効果を大きくすることが望ましい。表5から、デバイスまたは画素のサイズが小さくなるほど、漏れを少なくするためのSRLの厚さ方向抵抗率が大きくなることがわかる。

【0043】

例6

例6では、1つ以上の大きな発光区画を有するOLEDデバイスのための短絡低減層の設計について調べる。この用途では、大きな発光区画は、面積が0.1cm2以上の区画である。このようなデバイスの一例は、画素のサイズが0.1cm2以上である大面積パッシブ・マトリックスOLEDデバイスである。別の一例は、アメリカ合衆国特許第6,693,296号に記載されているような、発光区画が0.1cm2以上である分割されたモノリシック直列接続構造を有するOLED照明デバイスまたはOLEDイルミネーション・デバイスである。通常は、このデバイスは、輝度レベルが限られた範囲でしか動作しない。式3はこうしたOLEDデバイスにも適用され、この式から、厚さ方向抵抗率の値に関する条件は、高解像度ディスプレイに必要とされる値に関する条件とは非常に異なることがわかる。この実施例では、イルミネーション用の大きな発光区画を有するOLEDデバイスを調べる。OLEDデバイスは、市販されているコンパクトな蛍光灯に匹敵するよう、約2000cd/m2で動作しているときの電力効率が約40 lm/Wでなくてはならない。このような高レベルの電力効率は、駆動電圧の低下と電流効率の増大を通じて実現される可能性が最も高い。駆動電圧が白色発光デバイスの理論的限界値に近い3ボルトまで下がるのであれば、デバイスの電流効率は約40cd/Aになる必要がある。というのも、OLEDデバイスは発光パターンがランバート方式に近いからである。全面積が約10-8cm2である短絡に起因する漏れ損失がここでも10%であることを許容すると、厚さ20nmの短絡低減層に対する抵抗率の条件を計算することができる。その結果を表6に示してある。

【0044】

【表6】

【0045】

第1列には、OLEDイルミネーション・デバイスで使用される可能性のある発光区画のサイズが示してある。第2列には、このOLEDデバイスにおける発光区画のデバイス等価抵抗値が示してある。第3列には、漏れ電流が動作電流の10%である場合にSRLを有する短絡の抵抗値が示してある。その抵抗値は、第2列に示した対応する値の10倍である。第4列には、SRLの対応する厚さ方向抵抗率が示してある。これらの値は、第3列の値に短絡の面積(この計算では10-8cmに等しい)を掛けることによって得られる。第5列には、第4列に示した対応する厚さ方向抵抗率を実現するのに必要なバルクの抵抗率が示してある。この実施例ではSRLの厚さを20nmと仮定した。第6列には、SRLによってOLEDの発光区画に付加される直列抵抗値が示してある。第7列には、SRLからの直列抵抗への寄与が発光区画の等価直列抵抗の10%に制限されている場合に、所定のサイズの発光区画で可能な厚さ方向抵抗率の最大値が示してある。第8列には、SRLの面抵抗が示してある。もし面抵抗率がデバイスの等価抵抗に匹敵する場合には、クロストークが問題になろう。

【0046】

イルミネーションとしての発光区画が1cm2である場合の結果を示す行を参照すると、漏れ電流を発光区画の動作電流の10%未満に制限するためには、短絡低減層の持つ厚さ貫通抵抗率が約6×10-5Ωcm2になっているだけでよいことが計算からわかる。これは、バルクの抵抗率が約6Ωcmであることに対応する。抵抗率の値がより大きいと、短絡からよりよく保護されるが、OLED発光区画にはより大きな直列抵抗が付加される。しかし第7列の値は、OLED発光区画に大きな直列抵抗を付加することなく、60Ωcm2という大きな厚さ貫通抵抗率を使用できることを示している。数値の幅がこのように広いと、実用的なOLEDデバイスを製造する際に他の多くの条件を満たさねばならない可能性のある短絡低減層を発見または開発するのが容易になる。本発明のデバイス構造に電荷注入層280を組み込むと、短絡低減材料の探索または開発がより容易になることを指摘しておくことが重要である。

【0047】

表6から、抵抗率に関する条件が発光区画のサイズに強く依存していることがはっきりとわかる。10cm2の発光区画では、利用できる厚さ方向抵抗率の範囲は6×10-6〜6×10-1Ωcm2に低下し、100cm2の発光区画では、この範囲はさらに狭くなって6×10-2〜6×10-3Ωcm2となる。

【0048】

上記の実施例から、高分解能ディスプレイでは厚さ方向抵抗率の範囲が約10〜1600Ωcm2になっている必要のあることがわかる。この範囲は、10〜1000Ωcm2であることが最も好ましい。大きな発光区画を有するOLEDデバイスでは、利用可能な範囲はより広く、実施例6で考えた動作パラメータの範囲では10-2〜103Ωcm2であるが、動作パラメータの別のセットでは、この範囲外の値でもよい。しかし選択する適切な厚さ方向抵抗率の値は、式3を用いて容易に計算することができる。

【0049】

短絡低減層が発光経路の途中にあるOLEDディスプレイまたはOLEDデバイスでは、短絡低減層は、短絡低減層として効果的に機能するためには、発生した光に合った透明度を持つ必要がある。ここで考えている用途では、合理的な透明度は、OLEDデバイスの発光帯域幅で積分した透過率が80%以上であることと定義される。短絡低減層が発光経路の途中にない場合には、短絡低減層は必ずしも透明でなくてもよい。OLEDディスプレイ装置のコントラストを改善するため、短絡低減層が反射性アノードまたは反射性カソードのための反射防止層としても機能することさえ望ましかろう。

【0050】

短絡低減層のための材料としては、無機酸化物(例えばインジウム酸化物、ガリウム酸化物、亜鉛酸化物、スズ酸化物、モリブデン酸化物、バナジウム酸化物、アンチモン酸化物、ビスマス酸化物、レニウム酸化物、タンタル酸化物、タングステン酸化物、ニオブ酸化物、ニッケル酸化物など)が挙げられる。これら酸化物は不定比化合物であるために導電性である。これら材料の抵抗率は、不定比の程度と移動度に依存する。これらの性質と光の透過率は、堆積条件を変えることによって制御可能である。実現可能な抵抗率と光の透過率の範囲は、不純物をドーピングすることによってさらに拡張することができる。例えばスズ酸化物やインジウム酸化物へのFのドーピング、亜鉛酸化物へのAl、In、Gaのドーピングは、これら酸化物の導電率と光の透過率を改善することがわかっている。これら酸化物のうちの2種類以上を混合することにより、さらに範囲を広げることができる。例えばインジウム酸化物とスズ酸化物の混合物、インジウム酸化物と亜鉛酸化物の混合物、亜鉛酸化物とスズ酸化物の混合物、カドミウム酸化物とスズ酸化物の混合物は、最もよく用いられてきた透明な導電体である。

【0051】

従来技術では、たいていの場合、バルクの導電率が10-3Ωcm以下という大きな導電率の透明な導体が注目されてきた。このような材料は、短絡低減層として用いるには導電性がありすぎる。しかしこれら酸化物を用いた抵抗率の大きな薄膜が、ガス・センサー、帯電防止コーティングなどの用途で使用できることもわかっている。抵抗率のより大きな薄膜は、導電率の大きな透明な導電体に関して最適化した組成と堆積条件を変えることによって調製できる。より大きな抵抗率は、特に、モリブデン酸化物、バナジウム酸化物、アンチモン酸化物、ビスマス酸化物、レニウム酸化物、タンタル酸化物、タングステン酸化物、ニオブ酸化物、ニッケル酸化物のいずれかをを含む材料を用いて実現することもできる。堆積条件を適切に制御することにより、またこれら酸化物を組み合わせた後、より導電性のある他の酸化物(例えばインジウム酸化物、ガリウム酸化物、亜鉛酸化物、スズ酸化物など)を混合することにより、大きな発光区画を有するOLEDデバイスと高分解能OLEDディスプレイ装置の両方での必要性を満たす広い範囲の抵抗率を得ることができる。

【0052】

短絡低減層で用いるのに適した他の材料として、導電率のより大きな酸化物材料と絶縁材料(酸化物、フッ化物、窒化物、硫化物の中から選択する)の混合物などがある。この混合物層の抵抗率は、これら2種類の材料の割合を調節することにより、望む範囲にすることができる。例えばPalら(A.M. Pal、A.J. Adorjan、P.D. Hambourger、J.A. Dever、H. Fu、アメリカ物理学会、OFM96会議の要約集CE.07)は、ITOとフッ化マグネシウム(MgF2)の混合物からなる薄膜が3×10-5〜3×103Ωcmという範囲の抵抗率をカバーすることを報告している。この混合薄膜は、従来の薄膜堆積法(例えばスパッタリング、蒸着、化学蒸着、プラズマ支援化学蒸着など)で調製することができる。酸化物膜に関しては、酸素または酸素含有ガス(例えば水蒸気やオゾン)を蒸着中に導入することで、組成と膜の性質を制御することができる。

【0053】

Minami(MRS Bulletin、2000年8月)は、導電性酸化物の調製と性質に関する詳細な概説を発表した。彼は、上に示したたいていの酸化物材料は仕事関数が約4.0eV〜5.0eVであることを示した。これらの値は正孔注入体として機能するには小さすぎ、電子注入体として機能するには大きすぎる。短絡低減層用に選択した材料が十分な電荷を注入できない場合には、本発明では、第1の電極がアノードだと短絡低減層と有機EL素子の間に正孔注入層を追加し、第1の電極がカソードだと短絡低減層と有機EL素子の間に電子注入層を追加する。電荷注入層を付加することにより、短絡低減層のための材料選択の範囲が広がり、他の追加条件に基づいてさらに洗練された選択を行なうことが可能になる。正孔注入層で用いるのに適した材料としては、アメリカ合衆国特許第4,720,432号に記載されているポルフィリン化合物、譲受人に譲渡されたアメリカ合衆国特許第6,208,075号に記載されているプラズマ堆積させたフルオロカーボン・ポリマーなどがある。有機ELデバイスで有用であることが報告されている別の正孔注入材料は、ヨーロッパ特許公開第0,891,121 A1号および第1,029,909 A1号に記載されているとともに、Tikitoら(J. Phys. D.、第29巻、2750ページ、1996年)によって記載されており、例えば、バナジウム酸化物(VOx)、モリブデン酸化物(MoOx)、ニッケル酸化物(NiOx)などがある。電子注入層としては、アメリカ合衆国特許第5,608,287号、第5,776,622号、第5,776,623号、第6,137,223号、第6,140,763号に記載されているもの(その開示内容は、参考としてこの明細書に組み込まれているものとする)を利用できる。仕事関数が小さなアルカリ金属またはアルカリ土類金属(例えばLi、Cs、Ca、Mg)を含む薄膜を用いることができる。さらに、仕事関数が小さなこれら金属をドープした有機材料も、電子注入層として使用することができる。具体例は、LiまたはCsをドープしたAlqである。

【0054】

本発明の別の一実施態様では、短絡低減層が有機EL素子と第2の電極層の間に配置される。この実施態様における短絡低減層の有効性は、短絡低減層が有機EL素子と第1の電極層の間に配置されている実施態様と同様である。短絡低減層の有効性は、短絡低減層を有機EL素子と第1の電極層の間と、有機EL素子と第2の電極層の間の両方に用いることによってさらに大きくすることができる。

【0055】

本発明の別の一実施態様では、OLEDデバイスは、アメリカ合衆国特許第6,337,492号に記載されているような積層式OLEDデバイスである。図3を参照すると、OLEDデバイス300は、積層式OLEDデバイスであることがわかる。基板310の上には、3つの有機発光デバイス331、332、333が存在していて、それぞれのデバイスは、正孔輸送層(331c、332c、333c)と、発光層(331b、332b、333b)と、電子輸送層(331a、332a、333a)を備えている。有機発光デバイス相互の間には、その有機発光デバイスの上にある正孔輸送層に正孔を供給し、その有機発光デバイスの下にある電子輸送層に電子を供給するコネクタ371と372が存在している。図3では、短絡低減層360は、有機発光デバイス331とコネクタ371の間に配置されている状態が図示されているが、第1の電極層320と有機発光デバイス331の間、コネクタ371と有機発光デバイス332の間、有機発光デバイス332とコネクタ372の間、コネクタ372と有機発光デバイス333の間、有機発光デバイス333と第2の電極層340の間に配置することもできる。本発明では、1つ以上の短絡低減層を使用することができる。ここでも、本発明によれば、選択した短絡低減層が電荷を十分に注入しない場合には、電荷注入層があると好ましい。

【0056】

本発明の別の一実施態様では、OLEDデバイスがマイクロキャビティ構造を有する。このデバイスは、基板と、金属からなる第1のアノード層(金属は、Au、Ag、Mg、Ca、またはこれらの合金の中から選択することが好ましい)と、短絡低減層と、有機EL素子と、金属からなる第2のアノード層(金属は、Au、Al、Ag、Mg、Ca、またはこれらの合金の中から選択することが好ましい)を備えている。金属製電極の1つは実質的に不透明かつ反射性であり、他方の電極は半透明である。2つの反射性金属製電極が存在しているため、デバイスはマイクロキャビティ構造を有する。この構造では、共鳴条件において光の強い干渉が起こる。共鳴波長近傍の発光は増幅され、共鳴波長から離れた発光は抑制される。

【0057】

従来は電極層と有機EL素子の間に無機層を使用していたが、短絡が少なくなる可能性のあることは認められておらず、使用されるスペーサ層は、短絡低減層として有効に機能するには導電性がありすぎたり、十分に透明でなかったりしたことに注意されたい。例えばTokito他(S. Tokito、K. Noda、Y. Taga、J. Phys. D. Appl. Phys.、第29巻、1996年、2750〜2753ページ)には、正孔注入層としてVOx、MoOx、RuOxをスパッタリングで厚さ30nmにした薄膜を用いることが報告されている。薄膜は、発光経路の途中に堆積されているが、どの薄膜の透光率も70%以下であり、最後の2つの薄膜の抵抗率は、短絡低減層として有効に機能するには小さすぎた。

【0058】

例7

ITOでコーティングしたガラス基板の上に一連のOLEDデバイスを作った。ITOアノード層の厚さは約42nmであり、そのITO層の上に短絡低減層(SRL)と、HTL層として機能する15nmのN,N'-ジ(ナフタレン-1-イル)-N,N'-ジフェニル-ベンジジン(NPB)層と、ETLおよびLELとして機能する15nmのトリス(8-ヒドロキシキノリン)アルミニウム(III)(Alq)層と、EILとして機能する厚さ1nmのLi層と、カソード層として機能する厚さ100nmのAgを堆積させた。ITOはガラス上にすでにコーティングされたものを販売者から購入したが、そのITOを除くどの層も、チェンバー内の真空度を約10-6トルにした真空蒸着によってコーティングした。熱で蒸発させたMoO3層をSRLとして使用した。MoO3層は、Taボートから約0.1nm/秒の速度で2nm〜30nmの厚さに蒸着した。供給源の材料は、純度99.9998%のMoO3粉末であった。膜の組成は調べなかったが、MoO3の組成からわずかにずれている可能性がある。膜は可視光に対して透明で透過率が約90%であり、電気的抵抗率は約105Ωcmであった。これらの層を堆積させた後、デバイスを蒸着チェンバーからドライ・ボックスに移して封入した。完成したデバイスの構造は、ガラス/ITO(42)/MoO3(さまざまな値)/NPB(15)/AlQ(15)/Li(0.1)/Ag(100)と表記される。括弧内の数値は、ナノメートルを単位として表記した厚さである。

【0059】

合計で12枚の基板をコーティングし、そのときMoO3の厚さ1つにつき2枚の基板を使用した。それぞれの基板上には、0.1cm2のOLEDデバイスが4個存在しており、MoO3の厚さ1つにつき合計で8個のOLEDデバイスを用意した。この実験では合計で48個のOLEDデバイスが存在していた。これらデバイスをOLEDの性能に関して調べた。予想通り、MoO3層が2nmの8個のデバイスのうちの7個が短絡した。というのも、有機層の全厚さが30nmというのは薄すぎるため、デバイスに短絡が極めて発生しやすくなり、2nmのMoO3は短絡低減層として十分に機能しないからである。短絡したデバイスの数は、MoO3を厚くするにつれて少なくなった。MoO3層の厚さが12nm以上だと、30個のデバイスのうちで4個だけが短絡した。

【0060】

しかしOLEDデバイスに短絡が存在する確率は、有機EL層の厚さに強く依存することを指摘しておく必要がある。有機EL層が薄くなるほど、短絡が生じる確率が大きくなる。典型的なOLEDデバイスでは、厚さが100nmを超える有機EL層が用いられる。短絡の数をできるだけ少なくするため、有機EL層の厚さを300nm以上にすることがしばしばある。この実施例では、短絡低減層の有効性を示すため、極めて薄い30nmという厚さにして、十分な数の短絡が確実に存在しているようにした。図4に示したデータから、極めて薄い有機EL層を有するこれらOLEDデバイスで短絡を減らすのに短絡低減層が有効であったことがわかる。同じ有効な効果が、はるかに厚い有機EL層を有するOLEDデバイスでも予想される。

【0061】

例8

短絡低減層の有効性をさらに証明するため、別の一連のOLEDデバイスを作った。製造条件とこれらデバイスの層構造は実施例1と同様であるが、この実施例ではMoO3短絡低減層とNPBからなるHTL層を合計した厚さが75nmという一定値に維持されるようにした点が異なっている。5枚の基板を利用し、それぞれの基板上に4つのOLEDデバイスを作った。その結果、0.1cm2のOLEDデバイスが全部で20個得られた。図5には、短絡していないデバイスの数をMoO3短絡低減層の厚さに対してプロットしてある。ここでも、MoO3層が厚くなるにつれて短絡していないデバイスの数が増えることが明らかである。この場合には、MoO3が厚くなるにつれて有機EL層の厚さが実際には薄くなり、そのことによって短絡の確率が大きくなったはずであることを指摘しておかねばならない。実際のデータで見られた逆の傾向は、短絡低減層の利点が、有機層の厚さ低下に起因する短絡確率の増加に打ち勝ったことを示している。

【0062】

本発明をいくつかの好ましい実施態様を特に参照して詳細に説明したが、本発明の精神と範囲の中でさまざまな変形や変更が可能であることが理解されよう。

【符号の説明】

【0063】

100、200、300 OLEDデバイス

110、210、310 基板

120、220、320 第1の電極層

130、230 有機EL層

140、240、340 第2の電極層

150、250 短絡

260 短絡低減層

280 電荷注入層

331、332、333 有機発光デバイス

331a、332a、333a 電子輸送層

331b、332b、333b 発光層

331c、332c、333c 正孔輸送層

360 短絡低減層

371、372 コネクタ

【特許請求の範囲】

【請求項1】

(a)基板と;

(b)この基板の上に配置された第1の電極層と;

(c)この第1の電極層の上に配置された無機短絡低減層と;

(d)この無機短絡低減層の上に配置された電荷注入層と;

(e)この電荷注入層の上に配置された有機EL素子と;

(f)この有機EL素子の上に配置された第2の電極層を備えていて、上記短絡低減層が、短絡に起因する漏れ電流と、それに付随する発光効率の損失とを減らすのに十分な厚さと抵抗率を持つように選択されているOLEDデバイス。

【請求項2】

上記第1の電極層がアノードである、請求項1に記載のOLEDデバイス。

【請求項3】

上記短絡低減層が、インジウム酸化物、ガリウム酸化物、亜鉛酸化物、スズ酸化物、モリブデン酸化物、バナジウム酸化物、アンチモン酸化物、ビスマス酸化物、レニウム酸化物、タンタル酸化物、タングステン酸化物、ニオブ酸化物、ニッケル酸化物の中から選択されている、請求項1に記載のOLEDデバイス。

【請求項4】

上記短絡低減層が、上記酸化物のうちの少なくとも2つの混合物である、請求項3に記載のOLEDデバイス。

【請求項5】

上記短絡低減層が、上記酸化物のうちの少なくとも1つと、絶縁性の酸化物材料、フッ化物材料、窒化物材料、硫化物材料いずれかとの混合物である、請求項3に記載のOLEDデバイス。

【請求項6】

上記2つの電極層のうちの一方が透明な導電性酸化物層であり、他方の電極層が金属である、請求項1に記載のOLEDデバイス。

【請求項7】

上記2つの電極層の両方が金属であり、その一方が、発生する光に対して半透明である、請求項1に記載のOLEDデバイス。

【請求項8】

上記短絡低減層の厚さが10nm以上である、請求項1に記載のOLEDデバイス。

【請求項9】

上記短絡低減層の厚さが20nm〜200nmである、請求項1に記載のOLEDデバイス。

【請求項10】

(a)基板と;

(b)この基板の上に配置された第1の電極層と;

(c)この第1の電極層の上に配置された有機EL素子と;

(d)この有機EL素子の上に配置された電荷注入層と;

(e)この電荷注入層の上に配置された無機短絡低減層と;

(f)この無機短絡低減層の上に配置された第2の電極層を備えていて、上記短絡低減層が、短絡に起因する漏れ電流と、それに付随する発光効率の損失とを減らすのに十分な厚さと抵抗率を持つように選択されているOLEDデバイス。

【請求項11】

(a)基板と;

(b)この基板の上に配置された第1の電極層と;

(c)この第1の電極層の上に配置された無機短絡低減層と;

(d)この無機短絡低減層の上に配置された有機EL素子と;

(e)この有機EL素子の上に配置された第2の電極層を備えていて、上記短絡低減層が、10Ωcm2〜1500Ωcm2という厚さ方向抵抗率を持つように選択されている、画素化された高解像度OLEDディスプレイ。

【請求項12】

電荷注入層が、上記無機短絡低減層と上記有機EL素子の間に配置されている、請求項11に記載のOLEDディスプレイ。

【請求項13】

上記短絡低減層が、インジウム酸化物、ガリウム酸化物、亜鉛酸化物、スズ酸化物、モリブデン酸化物、バナジウム酸化物、アンチモン酸化物、ビスマス酸化物、レニウム酸化物、タンタル酸化物、タングステン酸化物、ニオブ酸化物、ニッケル酸化物の中から選択されている、請求項11に記載のOLEDディスプレイ。

【請求項14】

上記短絡低減層が、上記酸化物のうちの少なくとも2つの混合物である、請求項13に記載のOLEDディスプレイ。

【請求項15】

上記短絡低減層が、上記酸化物のうちの少なくとも1つと、絶縁性の酸化物材料、フッ化物材料、窒化物材料、硫化物材料いずれかとの混合物である、請求項13に記載のOLEDディスプレイ。

【請求項16】

上記2つの電極層のうちの一方が透明な導電性酸化物層であり、他方の電極層が金属である、請求項11に記載のOLEDディスプレイ。

【請求項17】

上記2つの電極層の両方が金属であり、その一方が、発生する光に対して半透明である、請求項11に記載のOLEDディスプレイ。

【請求項18】

上記短絡低減層の厚さが10nm以上である、請求項11に記載のOLEDディスプレイ。

【請求項19】

上記短絡低減層の厚さが20nm〜200nmである、請求項11に記載のOLEDディスプレイ。

【請求項20】

(a)基板と;

(b)この基板の上に配置された第1の電極層と;

(c)この第1の電極層の上に配置された無機短絡低減層と;

(d)この無機短絡低減層の上に配置された有機EL素子と;

(e)この有機EL素子の上に配置された第2の電極層を備えていて、上記短絡低減層が、10-2Ωcm2〜10-7Ωcm2という厚さ方向抵抗率を持つように選択されている、1つ以上の大きな発光区画を有するOLEDデバイス。

【請求項21】

電荷注入層が、上記無機短絡低減層と上記有機EL素子の間に配置されている、請求項20に記載のOLEDデバイス。

【請求項22】

上記短絡低減層が、インジウム酸化物、ガリウム酸化物、亜鉛酸化物、スズ酸化物、モリブデン酸化物、バナジウム酸化物、アンチモン酸化物、ビスマス酸化物、レニウム酸化物、タンタル酸化物、タングステン酸化物、ニオブ酸化物、ニッケル酸化物の中から選択されている、請求項20に記載のOLEDデバイス。

【請求項23】

上記短絡低減層が、上記酸化物のうちの少なくとも2つの混合物である、請求項22に記載のOLEDデバイス。

【請求項24】

上記短絡低減層が、上記酸化物のうちの少なくとも1つと、絶縁性の酸化物材料、フッ化物材料、窒化物材料、硫化物材料いずれかとの混合物である、請求項22に記載のOLEDデバイス。

【請求項25】

上記2つの電極層のうちの一方が透明な導電性酸化物層であり、他方の電極層が金属である、請求項20に記載のOLEDデバイス。

【請求項26】

上記2つの電極層の両方が金属であり、その一方が、発生する光に対して半透明である、請求項20に記載のOLEDデバイス。

【請求項27】

上記短絡低減層の厚さが10nm以上である、請求項20に記載のOLEDデバイス。

【請求項28】

上記短絡低減層の厚さが20nm〜200nmである、請求項20に記載のOLEDデバイス。

【請求項1】

(a)基板と;

(b)この基板の上に配置された第1の電極層と;

(c)この第1の電極層の上に配置された無機短絡低減層と;

(d)この無機短絡低減層の上に配置された電荷注入層と;

(e)この電荷注入層の上に配置された有機EL素子と;

(f)この有機EL素子の上に配置された第2の電極層を備えていて、上記短絡低減層が、短絡に起因する漏れ電流と、それに付随する発光効率の損失とを減らすのに十分な厚さと抵抗率を持つように選択されているOLEDデバイス。

【請求項2】

上記第1の電極層がアノードである、請求項1に記載のOLEDデバイス。

【請求項3】

上記短絡低減層が、インジウム酸化物、ガリウム酸化物、亜鉛酸化物、スズ酸化物、モリブデン酸化物、バナジウム酸化物、アンチモン酸化物、ビスマス酸化物、レニウム酸化物、タンタル酸化物、タングステン酸化物、ニオブ酸化物、ニッケル酸化物の中から選択されている、請求項1に記載のOLEDデバイス。

【請求項4】

上記短絡低減層が、上記酸化物のうちの少なくとも2つの混合物である、請求項3に記載のOLEDデバイス。

【請求項5】

上記短絡低減層が、上記酸化物のうちの少なくとも1つと、絶縁性の酸化物材料、フッ化物材料、窒化物材料、硫化物材料いずれかとの混合物である、請求項3に記載のOLEDデバイス。

【請求項6】

上記2つの電極層のうちの一方が透明な導電性酸化物層であり、他方の電極層が金属である、請求項1に記載のOLEDデバイス。

【請求項7】

上記2つの電極層の両方が金属であり、その一方が、発生する光に対して半透明である、請求項1に記載のOLEDデバイス。

【請求項8】

上記短絡低減層の厚さが10nm以上である、請求項1に記載のOLEDデバイス。

【請求項9】

上記短絡低減層の厚さが20nm〜200nmである、請求項1に記載のOLEDデバイス。

【請求項10】

(a)基板と;

(b)この基板の上に配置された第1の電極層と;

(c)この第1の電極層の上に配置された有機EL素子と;

(d)この有機EL素子の上に配置された電荷注入層と;

(e)この電荷注入層の上に配置された無機短絡低減層と;

(f)この無機短絡低減層の上に配置された第2の電極層を備えていて、上記短絡低減層が、短絡に起因する漏れ電流と、それに付随する発光効率の損失とを減らすのに十分な厚さと抵抗率を持つように選択されているOLEDデバイス。

【請求項11】

(a)基板と;

(b)この基板の上に配置された第1の電極層と;

(c)この第1の電極層の上に配置された無機短絡低減層と;

(d)この無機短絡低減層の上に配置された有機EL素子と;

(e)この有機EL素子の上に配置された第2の電極層を備えていて、上記短絡低減層が、10Ωcm2〜1500Ωcm2という厚さ方向抵抗率を持つように選択されている、画素化された高解像度OLEDディスプレイ。

【請求項12】

電荷注入層が、上記無機短絡低減層と上記有機EL素子の間に配置されている、請求項11に記載のOLEDディスプレイ。

【請求項13】

上記短絡低減層が、インジウム酸化物、ガリウム酸化物、亜鉛酸化物、スズ酸化物、モリブデン酸化物、バナジウム酸化物、アンチモン酸化物、ビスマス酸化物、レニウム酸化物、タンタル酸化物、タングステン酸化物、ニオブ酸化物、ニッケル酸化物の中から選択されている、請求項11に記載のOLEDディスプレイ。

【請求項14】

上記短絡低減層が、上記酸化物のうちの少なくとも2つの混合物である、請求項13に記載のOLEDディスプレイ。

【請求項15】

上記短絡低減層が、上記酸化物のうちの少なくとも1つと、絶縁性の酸化物材料、フッ化物材料、窒化物材料、硫化物材料いずれかとの混合物である、請求項13に記載のOLEDディスプレイ。

【請求項16】

上記2つの電極層のうちの一方が透明な導電性酸化物層であり、他方の電極層が金属である、請求項11に記載のOLEDディスプレイ。

【請求項17】

上記2つの電極層の両方が金属であり、その一方が、発生する光に対して半透明である、請求項11に記載のOLEDディスプレイ。

【請求項18】

上記短絡低減層の厚さが10nm以上である、請求項11に記載のOLEDディスプレイ。

【請求項19】

上記短絡低減層の厚さが20nm〜200nmである、請求項11に記載のOLEDディスプレイ。

【請求項20】

(a)基板と;

(b)この基板の上に配置された第1の電極層と;

(c)この第1の電極層の上に配置された無機短絡低減層と;

(d)この無機短絡低減層の上に配置された有機EL素子と;

(e)この有機EL素子の上に配置された第2の電極層を備えていて、上記短絡低減層が、10-2Ωcm2〜10-7Ωcm2という厚さ方向抵抗率を持つように選択されている、1つ以上の大きな発光区画を有するOLEDデバイス。

【請求項21】

電荷注入層が、上記無機短絡低減層と上記有機EL素子の間に配置されている、請求項20に記載のOLEDデバイス。

【請求項22】

上記短絡低減層が、インジウム酸化物、ガリウム酸化物、亜鉛酸化物、スズ酸化物、モリブデン酸化物、バナジウム酸化物、アンチモン酸化物、ビスマス酸化物、レニウム酸化物、タンタル酸化物、タングステン酸化物、ニオブ酸化物、ニッケル酸化物の中から選択されている、請求項20に記載のOLEDデバイス。

【請求項23】

上記短絡低減層が、上記酸化物のうちの少なくとも2つの混合物である、請求項22に記載のOLEDデバイス。

【請求項24】

上記短絡低減層が、上記酸化物のうちの少なくとも1つと、絶縁性の酸化物材料、フッ化物材料、窒化物材料、硫化物材料いずれかとの混合物である、請求項22に記載のOLEDデバイス。

【請求項25】

上記2つの電極層のうちの一方が透明な導電性酸化物層であり、他方の電極層が金属である、請求項20に記載のOLEDデバイス。

【請求項26】

上記2つの電極層の両方が金属であり、その一方が、発生する光に対して半透明である、請求項20に記載のOLEDデバイス。

【請求項27】

上記短絡低減層の厚さが10nm以上である、請求項20に記載のOLEDデバイス。

【請求項28】

上記短絡低減層の厚さが20nm〜200nmである、請求項20に記載のOLEDデバイス。

【図1】

【図2】

【図3】

【図4】

【図5】

【図2】

【図3】

【図4】

【図5】

【公開番号】特開2012−49146(P2012−49146A)

【公開日】平成24年3月8日(2012.3.8)

【国際特許分類】

【出願番号】特願2011−238629(P2011−238629)

【出願日】平成23年10月31日(2011.10.31)

【分割の表示】特願2007−508374(P2007−508374)の分割

【原出願日】平成17年3月29日(2005.3.29)

【出願人】(510059907)グローバル オーエルイーディー テクノロジー リミティド ライアビリティ カンパニー (45)

【Fターム(参考)】

【公開日】平成24年3月8日(2012.3.8)

【国際特許分類】

【出願日】平成23年10月31日(2011.10.31)

【分割の表示】特願2007−508374(P2007−508374)の分割

【原出願日】平成17年3月29日(2005.3.29)

【出願人】(510059907)グローバル オーエルイーディー テクノロジー リミティド ライアビリティ カンパニー (45)

【Fターム(参考)】

[ Back to top ]