磁気センサ

【課題】ホール素子を有する磁気センサにおいて、簡易な回路構成である信号処理回路で、ホール素子の出力電圧に含まれるオフセット電圧及びフリッカノイズを除去することのできる磁気センサを提供する。

【解決手段】ホールプレートHは、ホールプレートHを流れる電流のキャリアの種類を、ゲート電極Gの電位Vgにより、電子または正孔のいずれか一方にすることが可能な両極性材料から形成される。さらに、入出力端子TA,TA’,TB,TB’が、ホールプレートHの面内で対向する電流入力端子対と電圧出力端子対とになり、その際に電流入出力端子対と電圧出力端子対とが互いに直交するような位置に形成される。

【解決手段】ホールプレートHは、ホールプレートHを流れる電流のキャリアの種類を、ゲート電極Gの電位Vgにより、電子または正孔のいずれか一方にすることが可能な両極性材料から形成される。さらに、入出力端子TA,TA’,TB,TB’が、ホールプレートHの面内で対向する電流入力端子対と電圧出力端子対とになり、その際に電流入出力端子対と電圧出力端子対とが互いに直交するような位置に形成される。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、磁気センサに関し、特にホール効果を用いて磁界の強度を検出するホール素子を有する磁気センサに関する。

【背景技術】

【0002】

磁界の強度を検出する磁気センサの一つとして、ホール効果を用いて磁界の強度を検出するホール素子を有する磁気センサが一般に知られている。このホール効果とは、磁界中を移動する電子または正孔が、磁界の方向と電子または正孔の移動方向とのそれぞれに対して垂直方向に働く力を受けることによって、電圧が生じる現象である。

ここで、図5を参照して、従来技術における一般的なホール素子100の機略構成・動作を説明する。図5に示すホール素子100は、一般的にホール効果を有するホールプレートHと、その中心を軸として4回対称になるような位置に4つの入出力端子TA,TA’,TB,TB’を備えて構成される。なお、印加される磁界の向きは、紙面に垂直な方向として説明する。

【0003】

ホールプレートHは、ホール効果を有する材質を用いて形成される。また、入出力端子TA,TA’,TB,TB’は、入出力端子TAと入出力端子TA’とが組になっており、また入出力端子TBと入出力端子TB’とが組になっている。ホール素子100は、入出力端子TA,TA’,TB,TB’のうちの、電子または正孔の移動方向に対応する2つの入出力端子(以下、「電流入力端子対」という。)間に電流を流すことで、電子または正孔の移動方向と直交する方向の他の2つの入出力端子(以下、「電圧出力端子対」という。)間に印加された磁界に応じた電位差を出力する。例えば、ホール素子100は、電流入力端子対TA−TA’間に電流を流すことで、電圧出力端子対TB−TB’間に、印加された磁界に応じた電位差が出力される。

【0004】

この電圧出力端子対間に出力される電位差は、印加された磁界の磁束密度に比例し、理想的には磁束密度がゼロである時にゼロである。しかしながら、ホール素子100の製造プロセスのバラツキ等により磁束密度がゼロであっても、電圧出力端子対間に出力される電位差がゼロにならず、電位差にいわゆるオフセット電圧が生じることが多い。

このオフセット電圧を除去する方法としては、スピニングカレント法が一般的に用いられている(特許文献1参照)。この方法では、ホール素子100の電流入力端子対と電圧出力端子対とを交互に切り替える。これにより、電流入力端子対と電圧出力端子対とを交互に切り替える前後のオフセット電圧を逆相の関係にして、オフセット電圧を除去する。これは、ホイートストンブリッジを非平衡状態にするのに似ている。

【0005】

ここで、ホール素子100のホール係数をRhとし、ホールプレートHの厚さをdとし、電流入力端子対間に流れる電流の電流値をIとし、電圧出力端子対間に印加された磁界の磁束密度をBとし、オフセット電圧をVoffとする。すると、電流入力端子対TA−TA’間に電流値Iの電流を流した時の電圧出力端子対TB−TB’間に出力される電位差V1を、下記の式(1)に示す式のように表すことができる。また、電流入力端子対TA−TA’と電圧出力端子対TB−TB’とを切り替えて、電流入力端子対TB−TB’間に電流値Iの電流を流した時の電圧出力端子対TA−TA’間に出力される電位差V2を、下記の式(2)に示す式のように表すことができる。

V1=Rh/d × I ×B + Voff ……式(1)

V2=Rh/d × I ×B − Voff ……式(2)

【0006】

従って、電圧出力端子対TB−TB’間に出力される電位差V1と、電圧出力端子対TA−TA’間に出力される電位差V2とを足し合わせることにより、オフセット電圧Voffを除去することができる。この時に、強度がホール素子100から出力された出力電圧(信号)の周波数に反比例するノイズ成分であるフリッカノイズも除去することができる。このようにして、オフセット電圧Voff及びフリッカノイズを除去することで、磁束密度Bに比例した磁界に応じた電位差を得ることができる。

【先行技術文献】

【特許文献】

【0007】

【特許文献1】特開2001−337147号公報

【発明の概要】

【発明が解決しようとする課題】

【0008】

しかしながら、上記のスピニングカレント法を用いたホール素子100では、入出力端子TA,TA’,TB,TB’を、電流入力端子対と電圧出力端子対とに交互に切り替えた時に、ホールプレートHの内部を流れる電流の領域が中央部を除いて異なる。このため、オフセット電圧及びフリッカノイズを十分に除去することができない場合があった。

また、上記のホール素子100では、ホール素子の4つの入出力端子TA,TA’,TB,TB’に対して、それぞれを電流入力端子対または電圧出力端子対として切り替えて使用するためのスイッチング素子を含むスイッチング回路を設ける必要がある。従って、ホール素子100の信号処理を行う信号処理回路は、スイッチング回路の制御も行わなければならないため、その分だけ信号処理回路の回路構成が複雑になる場合があった。

そこで、本発明は、上記の課題に鑑み、ホール素子を有する磁気センサにおいて、簡易な回路構成である信号処理回路で、ホール素子の出力電圧に含まれるオフセット電圧及びフリッカノイズを除去することのできる磁気センサを提供することを目的とする。

【課題を解決するための手段】

【0009】

本発明による発振器は、上記の目的を達成するために、次のように構成される。

本発明による第1の磁気センサは、ホール効果を有するホールプレートと、前記ホールプレートと電気的に接続されるように形成された入出力端子と、前記ホールプレートの上部または下部の少なくとも一方に絶縁膜を介して形成されたゲート電極とからなるホール素子を備え、前記ホールプレートは、前記ホールプレートを移動するキャリアの種類を、前記ゲート電極の電位により電子または正孔のいずれか一方に変更することが可能な両極性材料を用いて形成され、前記入出力端子は、前記ホールプレートの面内で互いにそれぞれ対向し合う2組の入出力端子であって、一方の組の入出力端子が電流入力端子対になり、他方の組の入出力端子が電圧出力端子対になり、前記電流入出力端子対と前記電圧出力端子対とが互いに直交するような位置に形成されたことを特徴とする。

【0010】

上記の第1の磁気センサによれば、ホールプレートが両極性材料を用いて形成される。このため、ホールプレートを移動するキャリアを、ゲート電極に印加する電圧により電子または正孔のいずれか一方に変えて、電圧出力端子対に出力される電位差の極性を反転させることができる。但し、ホールプレートに磁界が印加された状態でゲート電極に印加する電圧によりキャリアの種類を変更した時に、電圧出力端子対に出力される電位差は位相が反転するが、オフセット電圧は位相が反転しない。

従って、ホールプレートを移動するキャリアの種類を変更する前後の電圧出力端子対間に出力される電位差の差分をとることにより、電圧出力端子対間に出力される電位差に含まれるオフセット電圧及びフリッカノイズを容易に除去することが可能となる。

【0011】

本発明による第2の磁気センサは、前記ゲート電極のゲート電圧を制御するゲート電圧制御回路を備えることを特徴とする。

上記の第2の磁気センサによれば、ゲート電圧制御回路が、ゲート電極のゲート電圧を変調することが可能となる。

【0012】

本発明による第3の磁気センサは、前記ゲート電極は、前記ホールプレートを挟み込むように、当該ホールプレートの上部に形成されたゲート電極と、当該ホールプレートの下部に形成されたゲート電極とからなり、前記ゲート電圧制御回路は、前記ホールプレートの上部に形成されたゲート電極のゲート電圧と、前記ホールプレートの下部に形成されたゲート電極のゲート電圧とを個別に制御することを特徴とすることを特徴とする。

【0013】

上記の第3の磁気センサによれば、ゲート電圧制御回路が、2つのゲート電極のゲート電圧を、個別に変調することが可能となる。また、ゲート電圧制御回路が、ホールプレートと電気的に接続された入力電流端子の電位に対するゲート電極の電圧と、ホールプレートの面に対して垂直方向の電界の強度とを、個別に制御することが可能となる。

本発明による第4の磁気センサは、クロックを生成するクロック生成回路を備え、前記クロック生成回路により生成されたクロックが前記ゲート電圧制御回路に入力され、当該クロックに同期して前記ゲート電圧制御回路により前記ゲート電圧が変調されることによって、前記電圧出力端子対間に出力される電位差が交流信号に変換されることを特徴とする。

【0014】

上記の第4の磁気センサによれば、クロック生成回路から生成されたクロックによってゲート電極に印加する交流電圧が変調され、出力される。これにより、ホール素子から出力された出力電圧を交流信号に変換することが可能となる。フィルタ回路等で電圧出力端子対に出力された電位差から直流成分を除去し、交流成分のみを抽出することにより、オフセット電圧及びフリッカノイズを除去することができる。

【0015】

本発明による第5の磁気センサは、前記電流入力端子対間に印加する電圧が一定値になるように制御する定電圧回路を備えることを特徴とする。

上記の第5の磁気センサによれば、定電圧回路が、電流入力端子対間に印加される電圧が一定値にすることが可能となる。

【0016】

本発明による第6の磁気センサは、前記電流入力端子対間に流れる電流が一定値になるように制御する定電流回路を備えることを特徴とする。

上記の第6の磁気センサによれば、定電流回路が、ホールプレートを流れる電流が一定値になるように制御する。オフセット電圧は、電流入力端子対間に流す電流値に依存する。しかしながら、電流入力端子対間に流す電流値が一定値であれば、オフセット電圧はキャリアの種類によらず同じにすることが可能となる。

【0017】

本発明による第7の磁気センサは、前記ホールプレートは、材料にグラフェンを用いて形成されたグラフェン層であって、当該グラフェン層の層数が単層または複層で形成されたことを特徴とする。

上記の第7の磁気センサによれば、ホールプレートが、グラフェンを用いて形成された単層または複層のグラフェン層で形成される。単層のグラフェン層は、バンドギャップがゼロの半導体である。これにより、ゲート電極に印加する電圧によって、電圧出力端子対に出力される電位差の極性を容易に反転することができる。このため、ゲート電圧に対するキャリアの濃度及び電流量を、電子と正孔の濃度が等しいディラックポイントを中心にして、その前後で同じになるようにすることが可能となる。

【0018】

本発明による第8の磁気センサは、前記ホールプレートは、材料にグラフェンを用いて形成されたグラフェン層であって、当該グラフェン層の層数が2層で形成されたことを特徴とする。

上記の第8の磁気センサによれば、ホールプレートが、グラフェンを用いて形成された2層のグラフェン層で形成される。2層のグラフェン層は、2つのゲート電極によりグラフェン層の面に対して垂直方向に電界が印加された時に、バンドギャップが形成される。これにより、電荷中性点でのキャリアの濃度を低減することできる。このため、磁気センサの出力の温度特性を改善することが可能となる。

【0019】

本発明による第9の磁気センサは、前記ホール素子の信号処理を行う信号処理回路と前記ホールプレートとは、同一の半導体基板上に形成されたことを特徴とする。

上記の第9の磁気センサによれば、一つの半導体基板上に、検出素子であるホール素子と、そのホール素子の信号処理を行うための信号処理回路とを形成する。これにより、ホール素子と信号処理回路とを別々の半導体基板上に形成した時よりも、磁気センサのサイズを小型化することが可能となる。

【発明の効果】

【0020】

本発明の磁気センサによれば、従来より簡易な構成の信号処理回路で、ホール素子の出力電圧に含まれるオフセット電圧及びフリッカノイズを容易に除去することができる。

【図面の簡単な説明】

【0021】

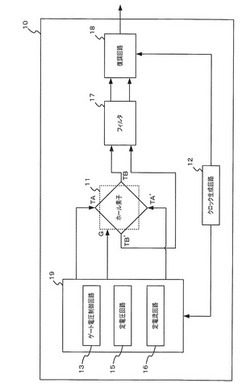

【図1】本発明の実施形態に係る磁気センサ10の回路構成を示すブロック図である。

【図2】本発明の実施形態に係る磁気センサ10が有するホール素子11を上面から見た時の上面図である。

【図3】ホール素子11の断面線A−Aにおける断面を表す断面図である。

【図4】電流入力端子対TA−TA’間に電圧を印加した時の、ゲート電極Gに印加するゲート電圧Vgと、電流入力端子対TA−TA'間に流れる電流Idとの関係を示すグラフである。

【図5】一般的なホール素子100を上面から見たときのホール素子100の機略構造を示す模式図である。

【発明を実施するための形態】

【0022】

以下、添付図面を参照しながら、本発明の磁気センサの好適な実施形態を詳細に説明する。なお、図面の説明において、同一の要素には同一の符号を付し、重複する説明を省略する。

(磁気センサ10の回路構成)

まず、図1を参照して、本発明の実施形態に係る磁気センサ10の回路構成を説明する。図1は、本発明の実施形態に係る磁気センサ10の回路構成を示すブロック図である。

【0023】

図1に示す磁気センサ10は、ホール素子11と、クロック生成回路12と、ゲート電圧制御回路13と、定電圧回路15と、定電流回路16と、フィルタ17と、復調回路18とを備えて構成される。

ホール素子11は、ホール素子100と同様に、ホール効果を用いて磁界の強度を検出する検出素子である。

【0024】

クロック生成回路12は、ゲート電圧制御回路13がホール素子11に出力するゲート電圧を変調する処理と、復調回路18がフィルタ17を介してホール素子11から出力された出力電圧を復調する処理との同期をとるためのクロックを生成する。

ゲート電圧制御回路13は、変調回路を兼ねており、クロック生成回路12により生成されたクロックに同期して、後述するゲート電極のゲート電圧を変調する。これによって、ホール素子11の電圧出力端子対TB−TB’間に出力される電位差も変調される。

【0025】

定電圧回路15は、ゲート電圧制御回路13によりホール素子11に入力されるゲート電圧が変調される時に、ホール素子11の入力電流端子対TA−TA’間を流れる電圧が一定値になるように制御する。

定電流回路16は、ゲート電圧制御回路13によりホール素子11に入力されるゲート電圧が変調される時に、ホール素子11の入力電流端子対TA−TA’間を流れる電流が一定値になるように制御する。また、定電流回路16は、ホール素子11に入力されるゲート電圧の値も制御する。

【0026】

フィルタ17は、ホール素子11の電圧出力端子対TB−TB’間に出力される電位差から、オフセット電圧(直流成分)を除去して、変調されている交流信号の周波数成分(交流成分)のみを抽出する。

復調回路18は、クロック生成回路12により生成されたクロックに同期して、変調されている交流信号を復調して、ホール素子11に印加された磁界の磁束密度に比例した電位差を出力する。

【0027】

上記のゲート電圧制御回路13と、定電圧回路15と、定電流回路16とが、ホール素子11の動作を制御する制御回路19として機能する。さらに、クロック生成回路12と、フィルタ17と、復調回路18と、制御回路19とが、ホール素子11の信号処理を行う信号処理回路として機能する。また、上記のホール素子11は、その信号処理回路が形成された図示しない半導体基板上に形成される。ホール素子11と信号処理回路とを別々の半導体基板上に形成した時よりも、磁気センサ10のサイズの小型化を図ることができる。

【0028】

(ホール素子11の積層構造)

続いて、図2及び図3を参照して、磁気センサ10が有するホール素子11の積層構造を説明する。

図2は、本発明の実施形態に係る磁気センサ10が有するホール素子11を上面から見た時の上面図である。また、図3は、ホール素子11の断面線A−Aにおける断面を表す断面図である。

【0029】

図2及び図3に示すホール素子11は、半導体基板21と、絶縁膜22と、ホールプレートHと、ゲート電極Gと、入出力端子TA,TA’,TB,TB’を備えて構成される。

半導体基板21としては、シリコン(Si)、炭化ケイ素(SiC)等の材料を用いて形成される。なお、半導体基板21は、半導体デバイスの製造で用いられる一般的な材料を用いて形成することができるが、シリコンを用いて形成されたシリコン基板が特に好ましい。

【0030】

絶縁膜22は、酸化シリコン、窒化シリコン、六方晶窒化ホウ素、アルミナ、ハフニア、ジルコニア、イットリア等の半導体デバイスの製造で用いられる周知の材料を用いて形成される。絶縁膜22は、六方晶窒化ホウ素を用いて形成された六方晶窒化ホウ素絶縁膜が特に好ましい。また、絶縁膜22は、CVD法やスパッタリング法等の半導体デバイスの製造で用いられる周知の製造方法を用いて形成することができる。より低いゲート電圧で極性を反転することができるように制御するためには、絶縁膜22の比誘電率をより大きくし、厚みをより薄くすると良い。

【0031】

ホールプレートHは、半導体基板21の上部に絶縁膜22を介して形成される。ホールプレートHは、一般的なホール素子100と同様にホール効果を有する材質を用いて形成される。しかしながら、ホール素子11のホールプレートHは、ホールプレートHを移動するキャリアの種類を、ゲート電極の電位により電子または正孔のいずれか一方に変更することが可能な両極性材料を用いて形成される。

【0032】

一般的なホール素子100は半導体材料により形成されている。従って、ホールプレートHを移動するキャリアは、ホールプレートHがn型半導体である場合には電子になり、ホールプレートHがp型半導体である場合には正孔になる。よって、磁界が印加された時のホール素子100から出力された出力電圧の位相は、ホールプレートHを移動するキャリアの種類により定められていた。

【0033】

ところが、ホール素子11のホールプレートHは、両極性材料により形成されている。この場合には、ホールプレートHを移動するキャリアを、ゲート電極Gの電位により電子または正孔のいずれか一方に変えることができる。

具体的な両極性材料としては、グラフェン、有機半導体等のπ共役系材料がその一つであるが、その中でもグラフェンが特に好ましい。例えば、炭素により構成されたグラフェンは、単層ではエネルギーギャップがゼロである半導体である。しかしながら、グラフェンをチャネルにした電界効果トランジスタでは、チャネルに誘起されるキャリアが、ゲート電極に印加する電圧により、電子あるいは正孔となる両極性を有することが知られている。

【0034】

ホールプレートHをグラフェンを用いたグラフェン層として形成する場合には、例えば「W. Zhu, V. Pererbeinos, M. Freitag and P. Avouris: Carrier scattering, mobilities and electrostatic potential in mono-, bi- and tri-layer graphenes: Phys. Rev. B 80, 235402 (2009)」の文献に記載されるような半導体デバイスの製造で用いられる周知の製造方法を用いて、ホールプレートHを形成することができる。また、グラフェン層は、単層または複層のどちらでも形成することができるが、単層または2層で形成したものが特に好ましい。

【0035】

ホールプレートHが単層のグラフェン層で形成される場合には、ホールプレートHは、バンドギャップがゼロの半導体である。よって、グラフェン層は、ゲート電極Gに印加する電圧により、電圧出力端子対TB−TB’間に出力される電位差の極性を反転させることができる。また、グラフェン層は、ゲート電圧に対するキャリアの濃度及び電流量を、電子と正孔の濃度が等しくなるディラックポイントを中心にして、その前後で同じになるようにすることができる。

【0036】

また、ホールプレートHが2層のグラフェン層で形成される場合には、ホールプレートHは、2つのゲート電極によりグラフェン層の面に対して垂直方向に電界が印加された時に、バンドギャップが形成された半導体である。これにより、グラフェン層は、電荷中性点でのキャリアの濃度を低減することできる。このため、磁気センサの出力電圧の温度特性を良好に改善することができる。

【0037】

入出力端子TA,TA’,TB,TB’は、ホールプレートHと電気的に接続されるように形成される。入出力端子TA,TA’,TB,TB’は、ホールプレートHとの接触抵抗が比較的小さい金属等を用いて形成される。入出力端子TA,TA’,TB,TB’は、金属を用いて形成されることが好ましく、具体的には、Cr,Ni,Ti,Co,Pd,Al,Ag,Cu,Au,Pt等を用いて形成されることが特に好ましい。入出力端子TA,TA’,TB,TB’は、スパッタリングやメッキ、ソルダーレジストのスクリーン印刷等の半導体デバイスの製造で用いられる周知の製造方法を用いて形成することができる。

【0038】

ゲート電極Gは、ホールプレートHの上部に絶縁膜22を介して形成される。ゲート電極Gは、半導体あるいは金属を用いて形成されることが好ましく、具体的には、Si,Cr,Ni,Ti,Co,Pd,Al,Ag,Cu,Au,Pt等を用いて形成されることが特に好ましい。ゲート電極Gは、スパッタリングやCVD,メッキ、ソルダーレジストのスクリーン印刷等の半導体デバイスの製造で用いられる周知の製造方法を用いて形成することができる。

【0039】

また、ホール素子11は、上記のホールプレートHの上部のゲート電極Gの他にも、半導体基板21をホールプレートHの下部のゲート電極として機能させることが可能である。従って、ゲート電圧制御回路13は、ホールプレートHの上部及び下部に形成された2つのゲート電極として機能する部分のゲート電圧を個別に制御する。これにより、ホールプレートHと電気的に接続された電流入力端子TAあるいは電流入力端子TA’の電位に対するゲート電極の電圧と、ホールプレートHの面に垂直方向の電界の強度とを、ゲート電圧制御回路13によって個別に制御することができる。また、半導体基板21に限らず、さらに別のゲート電極を形成しても良い。

【0040】

(磁気センサ10の検出動作)

続いて、図4を参照して、磁気センサ10が備えるホール素子11の検出動作を説明する。

図4は、ホール素子11の電流入力端子対TA−TA’間に電圧を印加した時の、ゲート電極Gに印加するゲート電圧Vgと、電流入力端子対TA−TA'間に流れる電流Idとの関係を示すグラフである。

ゲート電極Gと同様に機能する半導体基板21の電位は、図4のグラフに示すように、ゲート電圧Vg=0(V)の時に、電流入力端子対TA−TA'間に流れる電流Idが最小値になることが好ましい。この場合に、半導体基板21は、電荷中性点を設定するもう一つのゲート電極として機能する。従って、半導体基板21の電位を変化させることで、電荷中性点をずらすことができる。

【0041】

また、図4のグラフに示すように、ゲート電圧Vg>0(V)の時に、電流入力端子対TA−TA’間に流れる電流Idは、ホールプレートHを移動するキャリアが主に電子によるものである。また、ゲート電圧Vg<0(V)の時に、電流入力端子対TA−TA’間に流れる電流Idは、ホールプレートHを移動するキャリアが主に正孔によるものである。電流入力端子対TA−TA’間に印加した電圧を固定し、ゲート電圧Vg>0(V)の時に、電流入力端子対TA−TA'間に流れる電流Idが所定の電流値Ibになるゲート電圧をVg1とする。また、ゲート電圧Vg<0(V)の時に、電流入力端子対TA−TA'間に流れる電流Idが所定の電流値Ibになるゲート電圧をVg2とする。

【0042】

図3に示すホール素子11において、図3中の上側から下側に向かって磁束密度Bの磁場を印加した時に、オフセット電圧Voffがゼロである理想的な状態では、電圧出力端子対TB−TB’間に出力される電位差Vhは、次のようになる。

まず、ゲート電圧Vg>0(V)の時に、電圧出力端子対TB−TB’間に出力される電位差Vh=−Vh1(V)になる。また、ゲート電圧Vg<0(V)の時に、電圧出力端子対TB−TB’間に出力される電位差Vh=Vh2(V)になる。この時、Vh1(V)の値と、Vh2(V)の値とは、同じ符号である。従って、オフセット電圧Voffが存在する時に、電流入力端子対TA−TA’間に印加した電圧が一定値であれば、ゲート電圧Vg>0(V)の時のオフセット電圧と、ゲート電圧Vg<0(V)の時のオフセット電圧とは、ほぼ同じ値となる。

【0043】

ゲート電圧Vg>0(V)の時に、電圧出力端子対TB−TB’間に出力される電位差Vh+を、下記の式(3)に示す式のように表わすことができる。また、ゲート電圧Vg<0(V)の時に、電圧出力端子対TB−TB’間に出力される電位差Vh−を、下記の式(4)に示す式のように表わすことができる。

Vh+=−Vh1 + Voff ……式(3)

Vh−= Vh2 + Voff ……式(4)

【0044】

この時に、上記の式(3)に示す式と、式(4)に示す式との差分をとると、電圧出力端子対TB−TB’間に出力される電圧Vhを、下記の式(5)に示す式のように表わすことができる。

Vh=Vh1 + Vh2 ……式(5)

従って、ゲート電圧VgによりホールプレートHを移動するキャリアの種類を変更する前後の電圧出力端子対TB−TB’間に出力される電位差の差分をとると、オフセット電圧Voffを除去することができる。

【0045】

また、フリッカノイズは、その強度がホール素子11から出力された出力電圧の周波数に反比例するノイズ成分であり、素子中の結晶が欠陥していることによるキャリアのトラップ等に起因して生じる。なお、キャリアは、電子である時にも、正孔である時にも、同じホールプレートHを移動する。このため、ゲート電圧Vg>0(V)の時のフリッカノイズと、ゲート電圧Vg<0(V)の時のフリッカノイズとは、ほぼ同じになる。従って、オフセット電圧Voffと同様に、ゲート電極に印加するゲート電圧VgによりホールプレートHを移動するキャリアの種類を変更する前後の電圧出力端子対TB−TB’間に印加された磁界に応じた電位差の差分をとることにより、フリッカノイズを除去することができる。なお、ゲート電圧Vg>0(V)またはゲート電圧Vg<0(V)に切り替えるゲート電圧Vgの周波数は、フリッカノイズの周波数より十分大きい必要がある。

【0046】

なお、本実施形態で説明したホール素子11は、4つの入出力端子TA,TA’,TB,TB’が、ホール素子11の中心を軸として4回対称になるように配置されている。しかしながら、4回対称であることは必須ではなく、入出力端子TB,TB’を、入出力端子TAと入出力端子TATA’とを通る直線に対して線対称となるように配置しても良い。

【0047】

例えば、入出力端子の配置を変えて電流が流れる幅を広くすることで、電流入力端子対TA−TA’間に印加する電圧に対して流れる電流より、多くの電流が流れるようになる。これにより、ホール素子11から出力される出力電圧がより高くなるため、ホール素子11が磁界の強度を検出する感度をより高めることができる。

【産業上の利用可能性】

【0048】

本発明の磁気センサは、各種の電子機器用の磁界の強度を検出する磁気センサとして用いることができる。

【符号の説明】

【0049】

10……磁気センサ

11……ホール素子

12……クロック生成回路

13……ゲート電圧制御回路

15……定電圧回路

16……定電流回路

17……フィルタ

18……復調回路

21……半導体基板

22……絶縁膜

G……ゲート電極

H……ホールプレート

TA,TA’,TB,TB’……入出力端子

【技術分野】

【0001】

本発明は、磁気センサに関し、特にホール効果を用いて磁界の強度を検出するホール素子を有する磁気センサに関する。

【背景技術】

【0002】

磁界の強度を検出する磁気センサの一つとして、ホール効果を用いて磁界の強度を検出するホール素子を有する磁気センサが一般に知られている。このホール効果とは、磁界中を移動する電子または正孔が、磁界の方向と電子または正孔の移動方向とのそれぞれに対して垂直方向に働く力を受けることによって、電圧が生じる現象である。

ここで、図5を参照して、従来技術における一般的なホール素子100の機略構成・動作を説明する。図5に示すホール素子100は、一般的にホール効果を有するホールプレートHと、その中心を軸として4回対称になるような位置に4つの入出力端子TA,TA’,TB,TB’を備えて構成される。なお、印加される磁界の向きは、紙面に垂直な方向として説明する。

【0003】

ホールプレートHは、ホール効果を有する材質を用いて形成される。また、入出力端子TA,TA’,TB,TB’は、入出力端子TAと入出力端子TA’とが組になっており、また入出力端子TBと入出力端子TB’とが組になっている。ホール素子100は、入出力端子TA,TA’,TB,TB’のうちの、電子または正孔の移動方向に対応する2つの入出力端子(以下、「電流入力端子対」という。)間に電流を流すことで、電子または正孔の移動方向と直交する方向の他の2つの入出力端子(以下、「電圧出力端子対」という。)間に印加された磁界に応じた電位差を出力する。例えば、ホール素子100は、電流入力端子対TA−TA’間に電流を流すことで、電圧出力端子対TB−TB’間に、印加された磁界に応じた電位差が出力される。

【0004】

この電圧出力端子対間に出力される電位差は、印加された磁界の磁束密度に比例し、理想的には磁束密度がゼロである時にゼロである。しかしながら、ホール素子100の製造プロセスのバラツキ等により磁束密度がゼロであっても、電圧出力端子対間に出力される電位差がゼロにならず、電位差にいわゆるオフセット電圧が生じることが多い。

このオフセット電圧を除去する方法としては、スピニングカレント法が一般的に用いられている(特許文献1参照)。この方法では、ホール素子100の電流入力端子対と電圧出力端子対とを交互に切り替える。これにより、電流入力端子対と電圧出力端子対とを交互に切り替える前後のオフセット電圧を逆相の関係にして、オフセット電圧を除去する。これは、ホイートストンブリッジを非平衡状態にするのに似ている。

【0005】

ここで、ホール素子100のホール係数をRhとし、ホールプレートHの厚さをdとし、電流入力端子対間に流れる電流の電流値をIとし、電圧出力端子対間に印加された磁界の磁束密度をBとし、オフセット電圧をVoffとする。すると、電流入力端子対TA−TA’間に電流値Iの電流を流した時の電圧出力端子対TB−TB’間に出力される電位差V1を、下記の式(1)に示す式のように表すことができる。また、電流入力端子対TA−TA’と電圧出力端子対TB−TB’とを切り替えて、電流入力端子対TB−TB’間に電流値Iの電流を流した時の電圧出力端子対TA−TA’間に出力される電位差V2を、下記の式(2)に示す式のように表すことができる。

V1=Rh/d × I ×B + Voff ……式(1)

V2=Rh/d × I ×B − Voff ……式(2)

【0006】

従って、電圧出力端子対TB−TB’間に出力される電位差V1と、電圧出力端子対TA−TA’間に出力される電位差V2とを足し合わせることにより、オフセット電圧Voffを除去することができる。この時に、強度がホール素子100から出力された出力電圧(信号)の周波数に反比例するノイズ成分であるフリッカノイズも除去することができる。このようにして、オフセット電圧Voff及びフリッカノイズを除去することで、磁束密度Bに比例した磁界に応じた電位差を得ることができる。

【先行技術文献】

【特許文献】

【0007】

【特許文献1】特開2001−337147号公報

【発明の概要】

【発明が解決しようとする課題】

【0008】

しかしながら、上記のスピニングカレント法を用いたホール素子100では、入出力端子TA,TA’,TB,TB’を、電流入力端子対と電圧出力端子対とに交互に切り替えた時に、ホールプレートHの内部を流れる電流の領域が中央部を除いて異なる。このため、オフセット電圧及びフリッカノイズを十分に除去することができない場合があった。

また、上記のホール素子100では、ホール素子の4つの入出力端子TA,TA’,TB,TB’に対して、それぞれを電流入力端子対または電圧出力端子対として切り替えて使用するためのスイッチング素子を含むスイッチング回路を設ける必要がある。従って、ホール素子100の信号処理を行う信号処理回路は、スイッチング回路の制御も行わなければならないため、その分だけ信号処理回路の回路構成が複雑になる場合があった。

そこで、本発明は、上記の課題に鑑み、ホール素子を有する磁気センサにおいて、簡易な回路構成である信号処理回路で、ホール素子の出力電圧に含まれるオフセット電圧及びフリッカノイズを除去することのできる磁気センサを提供することを目的とする。

【課題を解決するための手段】

【0009】

本発明による発振器は、上記の目的を達成するために、次のように構成される。

本発明による第1の磁気センサは、ホール効果を有するホールプレートと、前記ホールプレートと電気的に接続されるように形成された入出力端子と、前記ホールプレートの上部または下部の少なくとも一方に絶縁膜を介して形成されたゲート電極とからなるホール素子を備え、前記ホールプレートは、前記ホールプレートを移動するキャリアの種類を、前記ゲート電極の電位により電子または正孔のいずれか一方に変更することが可能な両極性材料を用いて形成され、前記入出力端子は、前記ホールプレートの面内で互いにそれぞれ対向し合う2組の入出力端子であって、一方の組の入出力端子が電流入力端子対になり、他方の組の入出力端子が電圧出力端子対になり、前記電流入出力端子対と前記電圧出力端子対とが互いに直交するような位置に形成されたことを特徴とする。

【0010】

上記の第1の磁気センサによれば、ホールプレートが両極性材料を用いて形成される。このため、ホールプレートを移動するキャリアを、ゲート電極に印加する電圧により電子または正孔のいずれか一方に変えて、電圧出力端子対に出力される電位差の極性を反転させることができる。但し、ホールプレートに磁界が印加された状態でゲート電極に印加する電圧によりキャリアの種類を変更した時に、電圧出力端子対に出力される電位差は位相が反転するが、オフセット電圧は位相が反転しない。

従って、ホールプレートを移動するキャリアの種類を変更する前後の電圧出力端子対間に出力される電位差の差分をとることにより、電圧出力端子対間に出力される電位差に含まれるオフセット電圧及びフリッカノイズを容易に除去することが可能となる。

【0011】

本発明による第2の磁気センサは、前記ゲート電極のゲート電圧を制御するゲート電圧制御回路を備えることを特徴とする。

上記の第2の磁気センサによれば、ゲート電圧制御回路が、ゲート電極のゲート電圧を変調することが可能となる。

【0012】

本発明による第3の磁気センサは、前記ゲート電極は、前記ホールプレートを挟み込むように、当該ホールプレートの上部に形成されたゲート電極と、当該ホールプレートの下部に形成されたゲート電極とからなり、前記ゲート電圧制御回路は、前記ホールプレートの上部に形成されたゲート電極のゲート電圧と、前記ホールプレートの下部に形成されたゲート電極のゲート電圧とを個別に制御することを特徴とすることを特徴とする。

【0013】

上記の第3の磁気センサによれば、ゲート電圧制御回路が、2つのゲート電極のゲート電圧を、個別に変調することが可能となる。また、ゲート電圧制御回路が、ホールプレートと電気的に接続された入力電流端子の電位に対するゲート電極の電圧と、ホールプレートの面に対して垂直方向の電界の強度とを、個別に制御することが可能となる。

本発明による第4の磁気センサは、クロックを生成するクロック生成回路を備え、前記クロック生成回路により生成されたクロックが前記ゲート電圧制御回路に入力され、当該クロックに同期して前記ゲート電圧制御回路により前記ゲート電圧が変調されることによって、前記電圧出力端子対間に出力される電位差が交流信号に変換されることを特徴とする。

【0014】

上記の第4の磁気センサによれば、クロック生成回路から生成されたクロックによってゲート電極に印加する交流電圧が変調され、出力される。これにより、ホール素子から出力された出力電圧を交流信号に変換することが可能となる。フィルタ回路等で電圧出力端子対に出力された電位差から直流成分を除去し、交流成分のみを抽出することにより、オフセット電圧及びフリッカノイズを除去することができる。

【0015】

本発明による第5の磁気センサは、前記電流入力端子対間に印加する電圧が一定値になるように制御する定電圧回路を備えることを特徴とする。

上記の第5の磁気センサによれば、定電圧回路が、電流入力端子対間に印加される電圧が一定値にすることが可能となる。

【0016】

本発明による第6の磁気センサは、前記電流入力端子対間に流れる電流が一定値になるように制御する定電流回路を備えることを特徴とする。

上記の第6の磁気センサによれば、定電流回路が、ホールプレートを流れる電流が一定値になるように制御する。オフセット電圧は、電流入力端子対間に流す電流値に依存する。しかしながら、電流入力端子対間に流す電流値が一定値であれば、オフセット電圧はキャリアの種類によらず同じにすることが可能となる。

【0017】

本発明による第7の磁気センサは、前記ホールプレートは、材料にグラフェンを用いて形成されたグラフェン層であって、当該グラフェン層の層数が単層または複層で形成されたことを特徴とする。

上記の第7の磁気センサによれば、ホールプレートが、グラフェンを用いて形成された単層または複層のグラフェン層で形成される。単層のグラフェン層は、バンドギャップがゼロの半導体である。これにより、ゲート電極に印加する電圧によって、電圧出力端子対に出力される電位差の極性を容易に反転することができる。このため、ゲート電圧に対するキャリアの濃度及び電流量を、電子と正孔の濃度が等しいディラックポイントを中心にして、その前後で同じになるようにすることが可能となる。

【0018】

本発明による第8の磁気センサは、前記ホールプレートは、材料にグラフェンを用いて形成されたグラフェン層であって、当該グラフェン層の層数が2層で形成されたことを特徴とする。

上記の第8の磁気センサによれば、ホールプレートが、グラフェンを用いて形成された2層のグラフェン層で形成される。2層のグラフェン層は、2つのゲート電極によりグラフェン層の面に対して垂直方向に電界が印加された時に、バンドギャップが形成される。これにより、電荷中性点でのキャリアの濃度を低減することできる。このため、磁気センサの出力の温度特性を改善することが可能となる。

【0019】

本発明による第9の磁気センサは、前記ホール素子の信号処理を行う信号処理回路と前記ホールプレートとは、同一の半導体基板上に形成されたことを特徴とする。

上記の第9の磁気センサによれば、一つの半導体基板上に、検出素子であるホール素子と、そのホール素子の信号処理を行うための信号処理回路とを形成する。これにより、ホール素子と信号処理回路とを別々の半導体基板上に形成した時よりも、磁気センサのサイズを小型化することが可能となる。

【発明の効果】

【0020】

本発明の磁気センサによれば、従来より簡易な構成の信号処理回路で、ホール素子の出力電圧に含まれるオフセット電圧及びフリッカノイズを容易に除去することができる。

【図面の簡単な説明】

【0021】

【図1】本発明の実施形態に係る磁気センサ10の回路構成を示すブロック図である。

【図2】本発明の実施形態に係る磁気センサ10が有するホール素子11を上面から見た時の上面図である。

【図3】ホール素子11の断面線A−Aにおける断面を表す断面図である。

【図4】電流入力端子対TA−TA’間に電圧を印加した時の、ゲート電極Gに印加するゲート電圧Vgと、電流入力端子対TA−TA'間に流れる電流Idとの関係を示すグラフである。

【図5】一般的なホール素子100を上面から見たときのホール素子100の機略構造を示す模式図である。

【発明を実施するための形態】

【0022】

以下、添付図面を参照しながら、本発明の磁気センサの好適な実施形態を詳細に説明する。なお、図面の説明において、同一の要素には同一の符号を付し、重複する説明を省略する。

(磁気センサ10の回路構成)

まず、図1を参照して、本発明の実施形態に係る磁気センサ10の回路構成を説明する。図1は、本発明の実施形態に係る磁気センサ10の回路構成を示すブロック図である。

【0023】

図1に示す磁気センサ10は、ホール素子11と、クロック生成回路12と、ゲート電圧制御回路13と、定電圧回路15と、定電流回路16と、フィルタ17と、復調回路18とを備えて構成される。

ホール素子11は、ホール素子100と同様に、ホール効果を用いて磁界の強度を検出する検出素子である。

【0024】

クロック生成回路12は、ゲート電圧制御回路13がホール素子11に出力するゲート電圧を変調する処理と、復調回路18がフィルタ17を介してホール素子11から出力された出力電圧を復調する処理との同期をとるためのクロックを生成する。

ゲート電圧制御回路13は、変調回路を兼ねており、クロック生成回路12により生成されたクロックに同期して、後述するゲート電極のゲート電圧を変調する。これによって、ホール素子11の電圧出力端子対TB−TB’間に出力される電位差も変調される。

【0025】

定電圧回路15は、ゲート電圧制御回路13によりホール素子11に入力されるゲート電圧が変調される時に、ホール素子11の入力電流端子対TA−TA’間を流れる電圧が一定値になるように制御する。

定電流回路16は、ゲート電圧制御回路13によりホール素子11に入力されるゲート電圧が変調される時に、ホール素子11の入力電流端子対TA−TA’間を流れる電流が一定値になるように制御する。また、定電流回路16は、ホール素子11に入力されるゲート電圧の値も制御する。

【0026】

フィルタ17は、ホール素子11の電圧出力端子対TB−TB’間に出力される電位差から、オフセット電圧(直流成分)を除去して、変調されている交流信号の周波数成分(交流成分)のみを抽出する。

復調回路18は、クロック生成回路12により生成されたクロックに同期して、変調されている交流信号を復調して、ホール素子11に印加された磁界の磁束密度に比例した電位差を出力する。

【0027】

上記のゲート電圧制御回路13と、定電圧回路15と、定電流回路16とが、ホール素子11の動作を制御する制御回路19として機能する。さらに、クロック生成回路12と、フィルタ17と、復調回路18と、制御回路19とが、ホール素子11の信号処理を行う信号処理回路として機能する。また、上記のホール素子11は、その信号処理回路が形成された図示しない半導体基板上に形成される。ホール素子11と信号処理回路とを別々の半導体基板上に形成した時よりも、磁気センサ10のサイズの小型化を図ることができる。

【0028】

(ホール素子11の積層構造)

続いて、図2及び図3を参照して、磁気センサ10が有するホール素子11の積層構造を説明する。

図2は、本発明の実施形態に係る磁気センサ10が有するホール素子11を上面から見た時の上面図である。また、図3は、ホール素子11の断面線A−Aにおける断面を表す断面図である。

【0029】

図2及び図3に示すホール素子11は、半導体基板21と、絶縁膜22と、ホールプレートHと、ゲート電極Gと、入出力端子TA,TA’,TB,TB’を備えて構成される。

半導体基板21としては、シリコン(Si)、炭化ケイ素(SiC)等の材料を用いて形成される。なお、半導体基板21は、半導体デバイスの製造で用いられる一般的な材料を用いて形成することができるが、シリコンを用いて形成されたシリコン基板が特に好ましい。

【0030】

絶縁膜22は、酸化シリコン、窒化シリコン、六方晶窒化ホウ素、アルミナ、ハフニア、ジルコニア、イットリア等の半導体デバイスの製造で用いられる周知の材料を用いて形成される。絶縁膜22は、六方晶窒化ホウ素を用いて形成された六方晶窒化ホウ素絶縁膜が特に好ましい。また、絶縁膜22は、CVD法やスパッタリング法等の半導体デバイスの製造で用いられる周知の製造方法を用いて形成することができる。より低いゲート電圧で極性を反転することができるように制御するためには、絶縁膜22の比誘電率をより大きくし、厚みをより薄くすると良い。

【0031】

ホールプレートHは、半導体基板21の上部に絶縁膜22を介して形成される。ホールプレートHは、一般的なホール素子100と同様にホール効果を有する材質を用いて形成される。しかしながら、ホール素子11のホールプレートHは、ホールプレートHを移動するキャリアの種類を、ゲート電極の電位により電子または正孔のいずれか一方に変更することが可能な両極性材料を用いて形成される。

【0032】

一般的なホール素子100は半導体材料により形成されている。従って、ホールプレートHを移動するキャリアは、ホールプレートHがn型半導体である場合には電子になり、ホールプレートHがp型半導体である場合には正孔になる。よって、磁界が印加された時のホール素子100から出力された出力電圧の位相は、ホールプレートHを移動するキャリアの種類により定められていた。

【0033】

ところが、ホール素子11のホールプレートHは、両極性材料により形成されている。この場合には、ホールプレートHを移動するキャリアを、ゲート電極Gの電位により電子または正孔のいずれか一方に変えることができる。

具体的な両極性材料としては、グラフェン、有機半導体等のπ共役系材料がその一つであるが、その中でもグラフェンが特に好ましい。例えば、炭素により構成されたグラフェンは、単層ではエネルギーギャップがゼロである半導体である。しかしながら、グラフェンをチャネルにした電界効果トランジスタでは、チャネルに誘起されるキャリアが、ゲート電極に印加する電圧により、電子あるいは正孔となる両極性を有することが知られている。

【0034】

ホールプレートHをグラフェンを用いたグラフェン層として形成する場合には、例えば「W. Zhu, V. Pererbeinos, M. Freitag and P. Avouris: Carrier scattering, mobilities and electrostatic potential in mono-, bi- and tri-layer graphenes: Phys. Rev. B 80, 235402 (2009)」の文献に記載されるような半導体デバイスの製造で用いられる周知の製造方法を用いて、ホールプレートHを形成することができる。また、グラフェン層は、単層または複層のどちらでも形成することができるが、単層または2層で形成したものが特に好ましい。

【0035】

ホールプレートHが単層のグラフェン層で形成される場合には、ホールプレートHは、バンドギャップがゼロの半導体である。よって、グラフェン層は、ゲート電極Gに印加する電圧により、電圧出力端子対TB−TB’間に出力される電位差の極性を反転させることができる。また、グラフェン層は、ゲート電圧に対するキャリアの濃度及び電流量を、電子と正孔の濃度が等しくなるディラックポイントを中心にして、その前後で同じになるようにすることができる。

【0036】

また、ホールプレートHが2層のグラフェン層で形成される場合には、ホールプレートHは、2つのゲート電極によりグラフェン層の面に対して垂直方向に電界が印加された時に、バンドギャップが形成された半導体である。これにより、グラフェン層は、電荷中性点でのキャリアの濃度を低減することできる。このため、磁気センサの出力電圧の温度特性を良好に改善することができる。

【0037】

入出力端子TA,TA’,TB,TB’は、ホールプレートHと電気的に接続されるように形成される。入出力端子TA,TA’,TB,TB’は、ホールプレートHとの接触抵抗が比較的小さい金属等を用いて形成される。入出力端子TA,TA’,TB,TB’は、金属を用いて形成されることが好ましく、具体的には、Cr,Ni,Ti,Co,Pd,Al,Ag,Cu,Au,Pt等を用いて形成されることが特に好ましい。入出力端子TA,TA’,TB,TB’は、スパッタリングやメッキ、ソルダーレジストのスクリーン印刷等の半導体デバイスの製造で用いられる周知の製造方法を用いて形成することができる。

【0038】

ゲート電極Gは、ホールプレートHの上部に絶縁膜22を介して形成される。ゲート電極Gは、半導体あるいは金属を用いて形成されることが好ましく、具体的には、Si,Cr,Ni,Ti,Co,Pd,Al,Ag,Cu,Au,Pt等を用いて形成されることが特に好ましい。ゲート電極Gは、スパッタリングやCVD,メッキ、ソルダーレジストのスクリーン印刷等の半導体デバイスの製造で用いられる周知の製造方法を用いて形成することができる。

【0039】

また、ホール素子11は、上記のホールプレートHの上部のゲート電極Gの他にも、半導体基板21をホールプレートHの下部のゲート電極として機能させることが可能である。従って、ゲート電圧制御回路13は、ホールプレートHの上部及び下部に形成された2つのゲート電極として機能する部分のゲート電圧を個別に制御する。これにより、ホールプレートHと電気的に接続された電流入力端子TAあるいは電流入力端子TA’の電位に対するゲート電極の電圧と、ホールプレートHの面に垂直方向の電界の強度とを、ゲート電圧制御回路13によって個別に制御することができる。また、半導体基板21に限らず、さらに別のゲート電極を形成しても良い。

【0040】

(磁気センサ10の検出動作)

続いて、図4を参照して、磁気センサ10が備えるホール素子11の検出動作を説明する。

図4は、ホール素子11の電流入力端子対TA−TA’間に電圧を印加した時の、ゲート電極Gに印加するゲート電圧Vgと、電流入力端子対TA−TA'間に流れる電流Idとの関係を示すグラフである。

ゲート電極Gと同様に機能する半導体基板21の電位は、図4のグラフに示すように、ゲート電圧Vg=0(V)の時に、電流入力端子対TA−TA'間に流れる電流Idが最小値になることが好ましい。この場合に、半導体基板21は、電荷中性点を設定するもう一つのゲート電極として機能する。従って、半導体基板21の電位を変化させることで、電荷中性点をずらすことができる。

【0041】

また、図4のグラフに示すように、ゲート電圧Vg>0(V)の時に、電流入力端子対TA−TA’間に流れる電流Idは、ホールプレートHを移動するキャリアが主に電子によるものである。また、ゲート電圧Vg<0(V)の時に、電流入力端子対TA−TA’間に流れる電流Idは、ホールプレートHを移動するキャリアが主に正孔によるものである。電流入力端子対TA−TA’間に印加した電圧を固定し、ゲート電圧Vg>0(V)の時に、電流入力端子対TA−TA'間に流れる電流Idが所定の電流値Ibになるゲート電圧をVg1とする。また、ゲート電圧Vg<0(V)の時に、電流入力端子対TA−TA'間に流れる電流Idが所定の電流値Ibになるゲート電圧をVg2とする。

【0042】

図3に示すホール素子11において、図3中の上側から下側に向かって磁束密度Bの磁場を印加した時に、オフセット電圧Voffがゼロである理想的な状態では、電圧出力端子対TB−TB’間に出力される電位差Vhは、次のようになる。

まず、ゲート電圧Vg>0(V)の時に、電圧出力端子対TB−TB’間に出力される電位差Vh=−Vh1(V)になる。また、ゲート電圧Vg<0(V)の時に、電圧出力端子対TB−TB’間に出力される電位差Vh=Vh2(V)になる。この時、Vh1(V)の値と、Vh2(V)の値とは、同じ符号である。従って、オフセット電圧Voffが存在する時に、電流入力端子対TA−TA’間に印加した電圧が一定値であれば、ゲート電圧Vg>0(V)の時のオフセット電圧と、ゲート電圧Vg<0(V)の時のオフセット電圧とは、ほぼ同じ値となる。

【0043】

ゲート電圧Vg>0(V)の時に、電圧出力端子対TB−TB’間に出力される電位差Vh+を、下記の式(3)に示す式のように表わすことができる。また、ゲート電圧Vg<0(V)の時に、電圧出力端子対TB−TB’間に出力される電位差Vh−を、下記の式(4)に示す式のように表わすことができる。

Vh+=−Vh1 + Voff ……式(3)

Vh−= Vh2 + Voff ……式(4)

【0044】

この時に、上記の式(3)に示す式と、式(4)に示す式との差分をとると、電圧出力端子対TB−TB’間に出力される電圧Vhを、下記の式(5)に示す式のように表わすことができる。

Vh=Vh1 + Vh2 ……式(5)

従って、ゲート電圧VgによりホールプレートHを移動するキャリアの種類を変更する前後の電圧出力端子対TB−TB’間に出力される電位差の差分をとると、オフセット電圧Voffを除去することができる。

【0045】

また、フリッカノイズは、その強度がホール素子11から出力された出力電圧の周波数に反比例するノイズ成分であり、素子中の結晶が欠陥していることによるキャリアのトラップ等に起因して生じる。なお、キャリアは、電子である時にも、正孔である時にも、同じホールプレートHを移動する。このため、ゲート電圧Vg>0(V)の時のフリッカノイズと、ゲート電圧Vg<0(V)の時のフリッカノイズとは、ほぼ同じになる。従って、オフセット電圧Voffと同様に、ゲート電極に印加するゲート電圧VgによりホールプレートHを移動するキャリアの種類を変更する前後の電圧出力端子対TB−TB’間に印加された磁界に応じた電位差の差分をとることにより、フリッカノイズを除去することができる。なお、ゲート電圧Vg>0(V)またはゲート電圧Vg<0(V)に切り替えるゲート電圧Vgの周波数は、フリッカノイズの周波数より十分大きい必要がある。

【0046】

なお、本実施形態で説明したホール素子11は、4つの入出力端子TA,TA’,TB,TB’が、ホール素子11の中心を軸として4回対称になるように配置されている。しかしながら、4回対称であることは必須ではなく、入出力端子TB,TB’を、入出力端子TAと入出力端子TATA’とを通る直線に対して線対称となるように配置しても良い。

【0047】

例えば、入出力端子の配置を変えて電流が流れる幅を広くすることで、電流入力端子対TA−TA’間に印加する電圧に対して流れる電流より、多くの電流が流れるようになる。これにより、ホール素子11から出力される出力電圧がより高くなるため、ホール素子11が磁界の強度を検出する感度をより高めることができる。

【産業上の利用可能性】

【0048】

本発明の磁気センサは、各種の電子機器用の磁界の強度を検出する磁気センサとして用いることができる。

【符号の説明】

【0049】

10……磁気センサ

11……ホール素子

12……クロック生成回路

13……ゲート電圧制御回路

15……定電圧回路

16……定電流回路

17……フィルタ

18……復調回路

21……半導体基板

22……絶縁膜

G……ゲート電極

H……ホールプレート

TA,TA’,TB,TB’……入出力端子

【特許請求の範囲】

【請求項1】

ホール効果を有するホールプレートと、前記ホールプレートと電気的に接続されるように形成された入出力端子と、前記ホールプレートの上部または下部の少なくとも一方に絶縁膜を介して形成されたゲート電極とからなるホール素子を備え、

前記ホールプレートは、前記ホールプレートを移動するキャリアの種類を、前記ゲート電極の電位により電子または正孔のいずれか一方に変更することが可能な両極性材料を用いて形成され、

前記入出力端子は、前記ホールプレートの面内で互いにそれぞれ対向し合う2組の入出力端子であって、一方の組の入出力端子が電流入力端子対になり、他方の組の入出力端子が電圧出力端子対になり、前記電流入出力端子対と前記電圧出力端子対とが互いに直交するような位置に形成されたことを特徴とする磁気センサ。

【請求項2】

前記ゲート電極のゲート電圧を制御するゲート電圧制御回路を備えることを特徴とする、

請求項1記載の磁気センサ。

【請求項3】

前記ゲート電極は、前記ホールプレートを挟み込むように、当該ホールプレートの上部に形成されたゲート電極と、当該ホールプレートの下部に形成されたゲート電極とからなり、

前記ゲート電圧制御回路は、前記ホールプレートの上部に形成されたゲート電極のゲート電圧と、前記ホールプレートの下部に形成されたゲート電極のゲート電圧とを個別に制御することを特徴とすることを特徴とする

請求項2記載の磁気センサ。

【請求項4】

クロックを生成するクロック生成回路を備え、

前記クロック生成回路により生成されたクロックが前記ゲート電圧制御回路に入力され、当該クロックに同期して前記ゲート電圧制御回路により前記ゲート電圧が変調されることによって、前記電圧出力端子対間に出力される電位差が交流信号に変換されることを特徴とする、

請求項1から請求項3までのいずれか1項に記載の磁気センサ。

【請求項5】

前記電流入力端子対間に印加する電圧が一定値になるように制御する定電圧回路を備えることを特徴とする、

請求項1から請求項4までのいずれか1項に記載の磁気センサ。

【請求項6】

前記電流入力端子対間に流れる電流が一定値になるように制御する定電流回路を備えることを特徴とする、

請求項1から請求項5のいずれか1項に記載の磁気センサ。

【請求項7】

前記ホールプレートは、材料にグラフェンを用いて形成されたグラフェン層であって、当該グラフェン層の層数が単層または複層で形成されたことを特徴とする、

請求項1から請求項6のいずれか1項に記載の磁気センサ。

【請求項8】

前記ホールプレートは、材料にグラフェンを用いて形成されたグラフェン層であって、当該グラフェン層の層数が2層で形成されたことを特徴とする、

請求項7記載の磁気センサ。

【請求項9】

前記ホール素子の信号処理を行う信号処理回路と前記ホールプレートとは、同一の半導体基板上に形成されたことを特徴とする、

請求項1から請求項8のいずれか1項に記載の磁気センサ。

【請求項1】

ホール効果を有するホールプレートと、前記ホールプレートと電気的に接続されるように形成された入出力端子と、前記ホールプレートの上部または下部の少なくとも一方に絶縁膜を介して形成されたゲート電極とからなるホール素子を備え、

前記ホールプレートは、前記ホールプレートを移動するキャリアの種類を、前記ゲート電極の電位により電子または正孔のいずれか一方に変更することが可能な両極性材料を用いて形成され、

前記入出力端子は、前記ホールプレートの面内で互いにそれぞれ対向し合う2組の入出力端子であって、一方の組の入出力端子が電流入力端子対になり、他方の組の入出力端子が電圧出力端子対になり、前記電流入出力端子対と前記電圧出力端子対とが互いに直交するような位置に形成されたことを特徴とする磁気センサ。

【請求項2】

前記ゲート電極のゲート電圧を制御するゲート電圧制御回路を備えることを特徴とする、

請求項1記載の磁気センサ。

【請求項3】

前記ゲート電極は、前記ホールプレートを挟み込むように、当該ホールプレートの上部に形成されたゲート電極と、当該ホールプレートの下部に形成されたゲート電極とからなり、

前記ゲート電圧制御回路は、前記ホールプレートの上部に形成されたゲート電極のゲート電圧と、前記ホールプレートの下部に形成されたゲート電極のゲート電圧とを個別に制御することを特徴とすることを特徴とする

請求項2記載の磁気センサ。

【請求項4】

クロックを生成するクロック生成回路を備え、

前記クロック生成回路により生成されたクロックが前記ゲート電圧制御回路に入力され、当該クロックに同期して前記ゲート電圧制御回路により前記ゲート電圧が変調されることによって、前記電圧出力端子対間に出力される電位差が交流信号に変換されることを特徴とする、

請求項1から請求項3までのいずれか1項に記載の磁気センサ。

【請求項5】

前記電流入力端子対間に印加する電圧が一定値になるように制御する定電圧回路を備えることを特徴とする、

請求項1から請求項4までのいずれか1項に記載の磁気センサ。

【請求項6】

前記電流入力端子対間に流れる電流が一定値になるように制御する定電流回路を備えることを特徴とする、

請求項1から請求項5のいずれか1項に記載の磁気センサ。

【請求項7】

前記ホールプレートは、材料にグラフェンを用いて形成されたグラフェン層であって、当該グラフェン層の層数が単層または複層で形成されたことを特徴とする、

請求項1から請求項6のいずれか1項に記載の磁気センサ。

【請求項8】

前記ホールプレートは、材料にグラフェンを用いて形成されたグラフェン層であって、当該グラフェン層の層数が2層で形成されたことを特徴とする、

請求項7記載の磁気センサ。

【請求項9】

前記ホール素子の信号処理を行う信号処理回路と前記ホールプレートとは、同一の半導体基板上に形成されたことを特徴とする、

請求項1から請求項8のいずれか1項に記載の磁気センサ。

【図1】

【図2】

【図3】

【図4】

【図5】

【図2】

【図3】

【図4】

【図5】

【公開番号】特開2012−215498(P2012−215498A)

【公開日】平成24年11月8日(2012.11.8)

【国際特許分類】

【出願番号】特願2011−81784(P2011−81784)

【出願日】平成23年4月1日(2011.4.1)

【出願人】(000000033)旭化成株式会社 (901)

【Fターム(参考)】

【公開日】平成24年11月8日(2012.11.8)

【国際特許分類】

【出願日】平成23年4月1日(2011.4.1)

【出願人】(000000033)旭化成株式会社 (901)

【Fターム(参考)】

[ Back to top ]