磁気検出素子及びそれを用いた磁気センサ、並びに、磁気検出素子の製造方法

【課題】 特に固定磁性層をセルフピン止め型とした構成において、Ta保護層の膜厚を適正化し、従来に比べて安定して優れた軟磁気特性を得ることが可能な磁気検出素子及びそれを用いた磁気センサ、並びに磁気検出素子の製造方法を提供することを目的とする。

【解決手段】 本実施形態の磁気検出素子1は、固定磁性層3とフリー磁性層5とが非磁性材料層4を介して積層された積層膜を備え、前記固定磁性層3は、第1磁性層3aと第2磁性層3cとが非磁性中間層3bを介して積層され、前記第1磁性層3aと前記第2磁性層3cとが反平行に磁化固定されたセルフピン止め型であり、前記積層膜の最上層は、Taからなる保護層6であり、前記保護層6の成膜時における成膜時膜厚は55Å以上であることを特徴とする。

【解決手段】 本実施形態の磁気検出素子1は、固定磁性層3とフリー磁性層5とが非磁性材料層4を介して積層された積層膜を備え、前記固定磁性層3は、第1磁性層3aと第2磁性層3cとが非磁性中間層3bを介して積層され、前記第1磁性層3aと前記第2磁性層3cとが反平行に磁化固定されたセルフピン止め型であり、前記積層膜の最上層は、Taからなる保護層6であり、前記保護層6の成膜時における成膜時膜厚は55Å以上であることを特徴とする。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、セルフピン止め型の磁気検出素子に関する。

【背景技術】

【0002】

従来、反強磁性層を用いて固定磁性層を交換結合磁界(Hex)により磁化固定する方法では、反強磁性層の結晶配向制御や固定磁性層の磁化分散を低減(単磁区化の促進)させるために、磁場中アニール(熱処理)を真空中で行うのが一般的であった。なお、真空中アニールでは酸化等の影響が小さいためにTaによる保護層の膜厚を30Å〜50Å程度に薄くしてもΔMR(抵抗変化率)等の特性に対する影響は小さかった。

【0003】

しかしながら磁場中アニール装置は高価であり、また真空中アニール時間が長時間になる問題があった。

【0004】

特許文献1,2は、固定磁性層をセルフピン止め型とし反強磁性層を設けていない。特許文献1,2ではTa保護層の膜厚を40Åにしている。

【0005】

セルフピン止め構造とすれば、磁場中アニール処理は不要となるが、磁気検出素子の成膜後、磁気センサの製造工程で曝される高温プロセスや、磁気センサの高温環境下での使用によっても特性変動が生じないように、無磁場でのアニール処理を行うことが必要である。このとき使用されるアニール装置は通常、低価格でアニール時間も短時間で済むが、特許文献1,2に示すようにTa保護層の膜厚を40Å程度に設定すると、特性劣化が問題になることが、今回の実験によりわかった。

【0006】

また特許文献3には固定磁性層をセルフピン止め型とし、Ru保護層を設けた発明が開示されている。特許文献3ではTa保護層を比較例として用いているが、膜厚が定かでない。ただし実施例に記載されているRu保護層と同じ膜厚であると仮定すれば30Åである。そして30Åの膜厚では、40Åの場合と同様に特性劣化が問題になる。

【0007】

また特許文献4も固定磁性層をセルフピン止め型としているが保護層の材質及び膜厚が定かでない。

【先行技術文献】

【特許文献】

【0008】

【特許文献1】US 7,019,949 B2

【特許文献2】US 7,196,878 B2

【特許文献3】特開2008−306112号公報

【特許文献4】特開2009−180604号公報

【発明の概要】

【発明が解決しようとする課題】

【0009】

そこで本発明は、上記従来の課題を解決するためのものであり、特に固定磁性層をセルフピン止め型とした構成において、Ta保護層の膜厚を適正化し、従来に比べて安定して優れた軟磁気特性を得ることが可能な磁気検出素子及びそれを用いた磁気センサ、並びに磁気検出素子の製造方法を提供することを目的とする。

【課題を解決するための手段】

【0010】

本発明における磁気検出素子は、固定磁性層とフリー磁性層とが非磁性材料層を介して積層された積層膜を備え、

前記固定磁性層は、第1磁性層と第2磁性層とが非磁性中間層を介して積層され、前記第1磁性層と前記第2磁性層とが反平行に磁化固定されたセルフピン止め型であり、

前記積層膜の最上層は、Taからなる保護層であり、前記保護層の成膜時における成膜時膜厚は55Å以上であることを特徴とするものである。

【0011】

また本発明は、固定磁性層とフリー磁性層とが非磁性材料層を介して積層された積層膜を備えた磁気検出素子の製造方法において、

前記固定磁性層を、第1磁性層と第2磁性層とが非磁性中間層を介して積層され、前記第1磁性層と前記第2磁性層とが反平行に磁化固定されたセルフピン止め型で形成し、

前記積層膜の最上層を、成膜時膜厚が55Å以上のTaからなる保護層で形成し、

大気中あるいは不活性ガスフロー中にて無磁場でのアニール処理を行うことを特徴とするものである。

【0012】

本発明では、固定磁性層をセルフピン止め型とした構成において、Ta保護層の成膜時の成膜時膜厚を、後述の実験結果に基づいて55Å以上に設定した。Ta保護層の膜厚の下限値を55Åとしたのは、55Åよりも小さいと、フリー磁性層と固定磁性層間に作用する層間結合磁界Hinが急激に大きくなり、ΔMRが急激に低下するためである。また、Ta保護層の膜厚の上限値は特に限定しないが、Ta保護層の膜厚を厚くしすぎるとTa保護層に分流する電流量が増えてしまい(シャントロス)、ΔMRが小さくなりやすい。よって、Ta保護層の膜厚上限値を調整することで他の磁気特性の信頼性を劣化させることなくΔMR値の調整が可能になる。

【0013】

以上により本発明によれば、固定磁性層をセルフピン止め型とした構成において、安定して優れた軟磁気特性を得ることが可能である。

【0014】

なお本発明における55Å以上としたTa保護層の膜厚は成膜時におけるものである。よって成膜後にアニール処理を行うことで、Ta保護層の一部が酸化されて保護層の膜厚は成膜時より厚くなる。このとき後述する実験結果に示すように、アニール後の状態の分析によりTa保護層の成膜時の膜厚を予測することが可能である。

【0015】

また本発明では、前記保護層の成膜時における成膜時膜厚は100Å以下であることが好ましい。Ta保護層の成膜時膜厚を30Åとした成膜時(As Depo)のΔMRを基準値とすると、Ta保護層の成膜時膜厚を100Å以下とすることで、無磁場アニール時のΔMRを基準値から最大で5%程度の低下で抑えることができるとわかった。また、前記保護層の前記フリー磁性層と接触する部分は金属Taであることが好ましい。

【0016】

また本発明では、前記保護層の膜厚は70Å以上で100Å以下であることが好ましい。Ta保護層の膜厚の下限値を55Åから70Åにずらすことで、多少、成膜時の膜厚が狙い値よりずれても、安定して優れた軟磁気特性を得ることが可能になる。

【0017】

また本発明における磁気センサは、同一基板上に、感度軸方向の異なる複数の上記に記載された磁気検出素子が配置されていることを特徴とするものである。

【0018】

本発明の磁気センサでは、上記したセルフピン止め型の磁気検出素子を使用することにより、様々な用途で、安定して優れた出力特性を得ることができる。

【発明の効果】

【0019】

本発明では、固定磁性層をセルフピン止め型とした構成において、従来に比べて、安定して優れた軟磁気特性を得ることが可能である。

【図面の簡単な説明】

【0020】

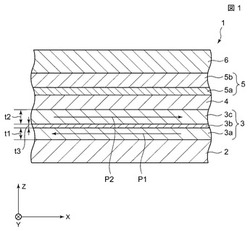

【図1】本実施形態における磁気検出素子の部分拡大縦断面図、

【図2】図1に示す磁気検出素子と、磁気検出素子に接続されるハードバイアス層との位置関係を示す部分縦断面図、

【図3】本実施形態における磁気センサの回路構成図、

【図4】本実施形態における磁気センサの製造方法を示す一工程図(平面図)、

【図5】(a)〜(d)は、Ta保護層の膜厚を代えた各磁気検出素子の成膜時(As Depo)におけるヒステリシスループ、(e)〜(h)は、Ta保護層の膜厚を代えた各磁気検出素子のアニール処理後におけるヒステリシスループ、(i)、(j)は、(e)、(f)と同じ磁気検出素子を用い、(e)、(f)に比べて外部磁界のレンジを広げたヒステリシスループ、

【図6】アニール処理後、及び成膜時(As Depo)における、Ta保護層の膜厚とΔMRとの関係を示すグラフ、

【図7】図6の縦軸を拡大して示したグラフ、

【図8】アニール処理後、及び成膜時(As Depo)における、Ta保護層の膜厚とHinとの関係を示すグラフ、

【図9】(a)は、Ta保護層の膜厚を50Åとした磁気検出素子の成膜時(As Depo)におけるオージェ・デプス・プロファイル、(b)は、Ta保護層の膜厚を50Åとした磁気検出素子のアニール処理後におけるオージェ・デプス・プロファイル、(c)は、Ta保護層の膜厚を70Åとした磁気検出素子のアニール処理後におけるオージェ・デプス・プロファイル、

【図10】(a)は、Ta保護層の膜厚を30Åとした磁気検出素子のアニール処理後におけるTEM写真、(b)は、Ta保護層の膜厚を70Åとした磁気検出素子のアニール処理後におけるTEM写真、(c)は、Ta保護層の膜厚を50Åとした磁気検出素子の成膜時(As Depo)におけるTEM写真。

【発明を実施するための形態】

【0021】

図1は、本実施形態における磁気検出素子の部分拡大縦断面図である。

図1に示すように本実施形態の磁気検出素子(GMR素子)1は、下から、シード層2、固定磁性層3、非磁性材料層4、フリー磁性層5及び保護層6の順に積層されて成膜される。磁気検出素子1を構成する各層は、例えばスパッタにて成膜される。

【0022】

シード層2は、NiFeCrあるいはCr等で形成される。またシード層2の膜厚は、36〜60Å程度である。シード層2と、図示しない基板との間に、Ta,Hf,Nb,Zr,Ti,Mo,W等からなる下地層が形成されていてもよい。

【0023】

固定磁性層3は、第1磁性層3aと第2磁性層3cと、第1磁性層3a及び第2磁性層3c間に介在する非磁性中間層3bとのAAF(artificial antiferromagnetic structure)構造である。

【0024】

図1に示すように第1磁性層3aの固定磁化方向(P1)と、第2磁性層3cの固定磁化方向(P2)は反平行となっている。

【0025】

図1に示すように、第1磁性層3aはシード層2上に形成されており、第2磁性層3cは、後述する非磁性材料層4に接して形成されている。

【0026】

本実施形態における第1磁性層3aは、第2磁性層3cよりも高保磁力材料のFexCo100-x(xは、55at%以上65at%以下であることが好ましい)で形成される。

【0027】

また図1に示すように、第1磁性層3aの膜厚は、例えば、14Å以上20.5Å以下の範囲内であり、第2磁性層3cの膜厚よりも薄くされている。

【0028】

これにより本実施形態では第1磁性層3aの保磁力Hcを高く安定した値にできる。例えば、50(kA/m)以上の保磁力Hcを得ることが可能である。

【0029】

非磁性材料層4に接する第2磁性層3cは磁気抵抗効果(GMR効果)に寄与する層であり、第2磁性層3cには、アップスピンを持つ伝導電子とダウンスピンを持つ伝導電子の平均自由行程差を大きくできる磁性材料が選択される。

【0030】

具体的には第2磁性層3cは、CoyFe100-y(yは85at%以上で100at%よりも小さいことが好ましい)あるいはCoで形成される。

【0031】

そして第2磁性層3cの膜厚は、例えば、16.5Å以上26Å以下の範囲内であり、第1磁性層3aの膜厚よりも厚く形成されている。

【0032】

第1磁性層3a及び第2磁性層3cの各膜厚は、第1磁性層3aと第2磁性層3cの磁化量(飽和磁化Ms・膜厚t)の差が実質的にゼロとなるように調整されている。

【0033】

本実施形態における固定磁性層3は、SFP構造によるセルフピン止め型である。すなわち反強磁性層を備えない構成であり、これにより磁気検出素子1の温度特性が反強磁性層のブロッキング温度に制約を受ける問題を解決できる。

【0034】

ここで、固定磁性層3の磁化固定力を高めるには、上記したように、第1磁性層3aの保磁力Hcを高めること、第1磁性層3aと第2磁性層3cの磁化量の差を実質的にゼロに調整すること、更に非磁性中間層3bの膜厚を調整して第1磁性層3aと第2磁性層3c間に生じるRKKY相互作用による反平行結合磁界を強めることが重要とされている。

【0035】

第1磁性層3aと第2磁性層3cの間に位置する非磁性中間層3bはRuで形成され、非磁性中間層3bの膜厚は、3.4Å以上4.2Å以下であることが好ましい。

【0036】

非磁性材料層4は、Cu(銅)などの非磁性導電材料で形成される。また、非磁性材料層4は絶縁層で形成されTMR素子にも適用できる。フリー磁性層5は、NiFe、CoFe、CoFeNiなどの軟磁性材料で形成される。図1に示す構造では、フリー磁性層5は、CoFe合金層5aとNiFe合金層5bとの積層構造であるが、フリー磁性層5の構造は限定されるものでない。すなわちフリー磁性層5の材質を限定するものでなく、また、単層構造、積層構造、及び積層フェリ構造の別を問わない。

【0037】

積層膜の最上層に位置する保護層6は、Ta(タンタル)で形成される。以下、Ta保護層6と称する。Ta保護層6の膜厚t1は、成膜時、55Å以上で形成される。特に断らない限り膜厚t1は成膜時膜厚を指す。

【0038】

図2は、図1に示す磁気検出素子1と、磁気検出素子1に接続されるハードバイアス層との位置関係を示す部分縦断面図である。

【0039】

図2(a)に示すように、磁気検出素子1は、支持基板9上に絶縁層50を介して形成されている。図2(a)に示すように磁気検出素子1上には、絶縁層51が設けられ、各ハードバイアス層36が絶縁層51の平坦化面上に形成される。

【0040】

あるいは図2(b)に示すように、磁気検出素子1の一部を除去して、その除去された凹部1a上にハードバイアス層36を形成してもよい。または図2(c)に示すように、ハードバイアス層36の形成位置における磁気検出素子1を全て削除して、分離した各磁気検出素子1の間に各ハードバイアス層36を介在させる構成とすることも出来る。

【0041】

これにより、磁気検出素子1を構成するフリー磁性層5(図1参照)にY方向からバイアス磁界が供給され、フリー磁性層5の磁化は、固定磁性層3の固定磁化方向に対して直交する方向に向けられる。

【0042】

本実施形態では図2に示すY方向に長く延びる磁気検出素子1がX方向に間隔を空けて複数本、配置され、各磁気検出素子1の端部間が導電層により接続されたミアンダ形状となっている。

【0043】

この実施形態では、磁気検出素子1を構成する非磁性材料層4はCu等の非磁性導電層であり、電流が積層膜の膜面と略平行な方向に流される。

【0044】

ミアンダ形状にて構成された磁気検出素子1は、複数個、設けられ、図3に示すブリッジ回路を構成する。図3では、各磁気検出素子1を区別するために第1磁気検出素子1b〜1e、第2磁気検出素子1f〜1iと符号を付すこととする。

【0045】

図3に示すように、本実施形態の磁気センサSは、4個の第1磁気検出素子1b〜1eにより構成された第1ブリッジ回路10と、4個の第2磁気検出素子1f〜1iにより構成された第2ブリッジ回路11とを有して構成される。

【0046】

図3に示すように、第1ブリッジ回路10を構成する第1磁気検出素子1b,1eの感度軸方向(図1に示す固定磁性層3を構成する第2磁性層3cの固定磁化方向(P2))と、第1磁気検出素子1c,1dの感度軸方向とは、反平行にされている。そして、第1磁気検出素子1bと第1磁気検出素子1c、及び、第1磁気検出素子1dと第1磁気検出素子1eとが、夫々、直列に接続される。第1磁気検出素子1b,1dは、入力端子(Vdd)20に接続され、第1磁気検出素子1c,1eはグランド端子(GND)21に接続され、第1磁気検出素子1bと第1磁気検出素子1cとの間、及び第1磁気検出素子1dと第1磁気検出素子1eとの間に夫々、出力端子(VX1,VX2)22,23が接続されている。

【0047】

また、図3に示すように第2ブリッジ回路11を構成する第2磁気検出素子1f,1iの感度軸方向(図3では、「P3」で示す)と、第2磁気検出素子1g,1hの感度軸方向とは、反平行にされている。そして、第2磁気検出素子1fと第2磁気検出素子1g、及び、第2磁気検出素子1hと第2磁気検出素子1iとが、夫々、直列に接続される。第2磁気検出素子1f,1hは、入力端子(Vdd)20に接続され、第2磁気検出素子1g,1iはグランド端子(GND)21に接続され、第2磁気検出素子1fと第2磁気検出素子1gとの間、及び第2磁気検出素子1hと第2磁気検出素子1iとの間に夫々、出力端子(VY1,VY2)24,25が接続されている。

【0048】

図3に示すように各第1磁気検出素子1b〜1eの感度軸方向(P2)と、各第2磁気検出素子1f〜1iの感度軸方向(P3)とは直交している。

【0049】

図3に示す磁気センサSには、例えば、図示しない磁石が高さ方向(Z)に間隔を空けて対向している。そして磁石から各磁気検出素子1b〜1iに外部磁界Hが作用する。

【0050】

例えば外部磁界Hが図3に示す方向に作用したとすると、第1ブリッジ回路10を構成する第1磁気検出素子1b,1eでは感度軸方向と外部磁界Hの方向が一致するため電気抵抗値は小さくなり、一方、第1磁気検出素子1c,1dでは、感度軸方向と外部磁界Hの方向が反対であるため電気抵抗値は大きくなり、出力端子22,23の中点電位が変動することでセンサ出力を得ることが出来る。一方、第2ブリッジ回路11では、外部磁界Hが各感度軸方向(P3)に対して直交する方向から作用するため、各第2磁気検出素子1f〜1iの電気抵抗値は等しくなり、出力端子24,25の中点電位は変動しない(センサ出力はゼロである)。外部磁界Hの方向が変動すれば、それに伴い各ブリッジ回路10,11のセンサ出力も変動する。

【0051】

そして、各ブリッジ回路10、11から得られるセンサ出力に基づいて、磁石の移動方向や移動量(相対位置)を知ることができる。

【0052】

本実施形態の磁気センサSは、例えば、磁気検出素子が基板上に1個で、残りが固定抵抗からなるブリッジ回路とすることも可能である。

【0053】

本実施形態の磁気センサSは、地磁気センサ、回転センサ、磁気スイッチ等、特に用途が限定されるものでない。

【0054】

本実施形態における磁気検出素子1の特徴的部分は、Ta保護層6の膜厚t1が、成膜時、55Å以上にて調整される点である。

【0055】

本実施形態のように、積層膜内に反強磁性層を有さず、固定磁性層3をセルフピン止め型とした構成では、磁場中アニールが不要である。ただし、磁気検出素子1の成膜後、磁気センサSの製造工程で曝される高温プロセスや、磁気センサSの高温環境下での使用によっても特性変動が生じないように、大気中あるいは窒素不活性ガスフロー中にて無磁場でのアニール処理(以下、無磁場アニールという)を行うことが必要である。このとき使用されるアニール装置は通常、低価格でアニール時間も短時間で済むが、Ta保護層6の膜厚t1を薄くすると、Ta保護層6及びTa保護層6下の積層膜が酸化の影響を受けて、特性劣化が問題になることが、今回の実験によりわかった。

【0056】

そこで、本実施形態では、固定磁性層3をセルフピン止め型とした構成において、Ta保護層6の成膜時における膜厚t1を、後述の実験結果に基づいて55Å以上に設定した。Ta保護層6の膜厚t1の下限値を55Åとしたのは、55Åよりも小さいと、フリー磁性層5と固定磁性層3間に作用する層間結合磁界Hinが急激に大きくなり、ΔMR(抵抗変化率)が急激に低下するためである。Ta保護層6の膜厚t1を55Å以上とすることで、無磁場アニールに曝しても、Ta保護層6の表面側は酸化されるものの一部の金属Taが残留し、酸素が、Ta保護層6の直下に位置するフリー磁性層5にまで届いておらず、あるいはフリー磁性層5に届く酸素量を極力、小さくできる。この結果、フリー磁性層5の内部状態、及びフリー磁性層5と非磁性材料層4との界面状態等を、成膜時(As Depo)とほぼ同じ状態に維持できると推測され、これにより、安定して優れた軟磁気特性が得られるものと考えられる。また、Ta保護層6の膜厚の上限値は特に限定しないが、Ta保護層6の膜厚を厚くしすぎるとTa保護層6に分流する電流量が増えてしまい(シャントロス)、ΔMRが小さくなりやすい。よってTa保護層6の膜厚を厚くすることで、Ta保護層6に分流する電流量を増やし、ΔMR値を微調整することができる。このため、Ta保護層の膜厚上限値を調整することで他の磁気特性の信頼性を劣化させることなくΔMR値の調整が可能になる。

【0057】

本実施形態では,Ta保護層6の膜厚上限は100Åであることが好ましい。後述する実験では、Ta保護層6の膜厚を30Åとした成膜時(As Depo)のΔMRを基準値とすると、Ta保護層6の膜厚t1を100Å以下とすることで、無磁場アニール時のΔMRを基準値から最大で5%程度の低下で抑えることができるとわかった。

【0058】

以上により本実施形態によれば、固定磁性層3をセルフピン止め型とした構成において、安定して優れた軟磁気特性を得ることが可能である。本実施形態では、Hinを20Oe以下に、好ましくはほぼゼロにまで小さくでき、またアニール処理前と同等以上のΔMRを得ることができる。

【0059】

したがって図3に示す磁気センサSでは、本実施形態のセルフピン止め型の磁気検出素子1を使用することで、安定して優れた軟磁気特性を得ることができ、様々な用途で出力特性に優れた使用が可能である。

【0060】

なお本実施形態における55Å以上としたTa保護層6の膜厚t1は成膜時(As Depo)におけるものである。よって成膜後に無磁場アニールを行うことで、Ta保護層6の一部が酸化されて保護層の膜厚は成膜時より厚くなるが、後述する実験結果に示すように、アニール後の状態からTa保護層6の成膜時の膜厚t1を予測することが可能である。Ta保護層6の膜厚t1を55Åとした場合、無磁場アニール後にて金属Taとして残される膜厚は5Å程度で、酸化Taとなる膜厚は100Å程度である。また、Ta保護層6の膜厚t1を70Åとした場合、金属Taとして残される膜厚は20Å程度で、酸化Taとなる膜厚は100Å程度である。アニール温度及びアニール時間によって、無磁場アニール後の膜厚は変動するが、アニール温度を250〜300℃程度、アニール時間を1〜4時間程度とすれば、概ね、上記の膜厚範囲内に収めることが可能である。後述するように例えば、TEM写真により、酸化Taの膜厚と、金属Taの膜厚を知ることができる。この酸化Taの膜厚値と、金属Taの膜厚値、及び膜厚比率から、成膜時のTa保護層6の膜厚t1を推測することが可能である。

【0061】

また本実施形態では、Ta保護層6の膜厚t1を70Å以上で100Å以下の範囲内にて調整することが好ましい。Ta保護層6の膜厚t1の下限値を55Åから70Åにずらすことで、多少、成膜時の膜厚t1が狙い値から外れても、安定して優れた軟磁気特性を得ることが可能である。

【0062】

図3に示す磁気センサSは、例えば、次のようにして製造することができる。図4(a)〜図4(b)は本実施形態における磁気センサSの製造方法を示す一工程図である。各図は製造工程中における平面図を示している。

【0063】

図4(a)では、基板65を用意する。基板65は、第1センサ領域65aと、第2センサ領域65bとを有している。

【0064】

図4(a)の工程では、基板65の第1センサ領域65a及び第2センサ領域65bに夫々、2個ずつ第1磁気検出素子1b〜1eを形成する。磁場中成膜を施してAAF構造からなるセルフピン止め型の固定磁性層3(図1参照)を同じX方向に磁化固定する。図4(a)に示すP2は、各第1磁気検出素子1b〜1eを構成する固定磁性層3の第2磁性層3cの固定磁化方向(感度軸方向)を示している。

【0065】

次に、図4(b)の工程では、基材65の第1センサ領域65a及び第2センサ領域65bに夫々、2個ずつ第2磁気検出素子1f〜1iを形成する。磁場中成膜を施してAAF構造からなるセルフピン止め構造の固定磁性層3を同じY方向に磁化固定する。図4(b)に示すP3は、各第2磁気検出素子1f〜1iを構成する固定磁性層3の第2磁性層3cの固定磁化方向(感度軸方向)を示している。

【0066】

本実施形態では、各固定磁性層3の磁化固定制御に対してアニール処理を施さないため、図4(b)の工程で、第2磁気検出素子1f〜1iの固定磁性層3をY方向に磁化固定するために磁場を施しても、図4(a)の工程にて、既に形成された第1磁気検出素子1b〜1eの固定磁性層3の固定磁化方向(P2)をX方向に向けた状態のまま適切に保つことが出来る。

【0067】

本実施形態では、各磁気検出素子1b〜1iのTa保護層6を、55Å以上、好ましくは55Å以上で100Å以下、さらに好ましくは70Å以上で100Å以下の範囲内にて成膜する。

【0068】

その後、各磁気検出素子1b〜1iの両側にハードバイアス層36を配置し、各磁気検出素子1b〜1iとハードバイアス層36とを組み合わせた平面形状をミアンダ状にする。

【0069】

本実施形態では、各磁気検出素子1b〜1iの成膜後、大気中、あるいは不活性ガスフロー中(例えば安価な窒素不活性ガスを用いる)にて、無磁場アニールを施す。無磁場アニールのタイミングは、各磁気検出素子1b〜1iの成膜後であれば特に問わないが、磁気センサSの製造工程で曝される高温プロセス前や、前記高温プロセスを有さない場合には、磁気センサSの製造工程中に行われる。

【0070】

ここでアニール温度としては、250〜300℃程度、アニール時間としては、1〜4時間程度である。

【0071】

その後、図4に示す第1センサ領域65aと第2センサ領域65bとを分離し、第2センサ領域65bを第1センサ領域65aに対して180度反転させた状態として、図3に示す入力端子20、グランド端子21及び各出力端子22〜25との間で電気的接続を行う。これにより図3に示す第1ブリッジ回路10と第2ブリッジ回路11とを形成することが出来る。

【実施例】

【0072】

(Ta保護層の膜厚を変化させたときのRHカーブの実験)

以下の積層膜を有する磁気検出素子を作製した。

基板/シード層:NiFeCr(42)/固定磁性層[第1磁性層:Fe60at%Co40at%(18.7)/非磁性中間層:Ru(3.6)/第2磁性層Co90at%Fe10at%(24)]/非磁性材料層:Cu(22)/フリー磁性層[Co90at%Fe10at%(12)/NiFe(20)]/保護層:Ta(X)

各層における括弧内の数値は膜厚を示し、単位はÅである。

【0073】

まず成膜時(As Depo)のRHカーブを測定した。

実験では、Ta保護層の膜厚を30Å、50Å、55Å及び70Åとして、各磁気検出素子のRHカーブを測定した。図5(a)は、Ta保護層の膜厚を30Åとした磁気検出素子のRHカーブ(成膜時(As Depo))、図5(b)は、Ta保護層の膜厚を50Åとした磁気検出素子のRHカーブ(成膜時(As Depo))、図5(c)は、Ta保護層の膜厚を55Åとした磁気検出素子のRHカーブ(成膜時(As Depo))、図5(d)は、Ta保護層の膜厚を70Åとした磁気検出素子のRHカーブ(成膜時(As Depo))である。なお実験では磁気検出素子に印加する外部磁界を±100Oeの範囲とした。ここで外部磁界のプラス値は、固定磁性層の固定磁化方向に対して反対方向であり、外部磁界のマイナス値は、固定磁性層の固定磁化方向と同方向である。

【0074】

フリー磁性層と固定磁性層との間に作用する層間結合磁界Hinは、各図5(a)〜図5(d)におけるRHカーブの最大ΔMR及び最小ΔMRの中間値であって、ヒステリシスループの広がり幅の中心値を「中点」としたとき、前記中点から外部磁界H=0(Oe)のラインまでの磁界の強さで決定される。図5(a)に中点Oを示した。図5(a)に示すように中点Oは、ほぼ外部磁界H=0のライン上にある。よって、Hinはほぼ0(Oe)である。

【0075】

図5(a)〜図5(d)に示すように、Ta保護層の膜厚にかかわらず、成膜時(As Depo)のHinは、ほぼ0(Oe)になることがわかった。

【0076】

次に、各磁気検出素子に対し、窒素不活性フロー中にてアニール処理を270℃、アニール時間を3時間とした無磁場アニールを行った。そして、各磁気検出素子のRHカーブを測定した。図5(e)は、Ta保護層の膜厚を30Åとした磁気検出素子のRHカーブ(無磁場アニール後)、図5(f)は、Ta保護層の膜厚を50Åとした磁気検出素子のRHカーブ(無磁場アニール後)、図5(g)は、Ta保護層の膜厚を55Åとした磁気検出素子のRHカーブ(無磁場アニール後)、図5(h)は、Ta保護層の膜厚を70Åとした磁気検出素子のRHカーブ(無磁場アニール後)である。なお実験では、外部磁界を±100Oeの範囲とした。

【0077】

図5(g)(h)に示すように、Ta保護層の膜厚を55Å、70Åとした場合、無磁場アニールを行うと、成膜時(As Depo)と比べて、若干、保磁力Hcが大きくなったが(ヒステリシスループの前記中点を通る横軸方向への広がり幅が保磁力の2倍に相当する)、ΔMR及びHinについては、あまり変化しないことがわかった。むしろ、後述するように、無磁場アニール後のΔMRは、成膜時のΔMRよりもやや高くなった。

【0078】

これに対して、図5(e)に示すように、Ta保護層の膜厚を30Åとした場合、外部磁界を±100Oeの範囲とすると、ΔMRは飽和せずに変動領域にあるため、ヒステリシスループ全体が見えるように、外部磁界のレンジを±500Oeまで広げたのが図5(i)である。図5(i)に示すようにヒステリシスループの中点Oは外部磁界H=0のラインから大きく外れてしまい、Hinが大幅に上昇していることがわかった。具体的にはHinは、90Oe程度にまで大きくなっている。またΔMRについて見ると、100Oeの外部磁界が作用したときのΔMR(図5(e)参照)は、図5(a)の成膜時に比べて大幅に低下することがわかった。

【0079】

図5(f)は、Ta保護層の膜厚を50Åとした場合のRHカーブ(外部磁界を±100Oe)、図5(j)は、Ta保護層の膜厚を50Åとした場合のRHカーブ(外部磁界を±500Oe)である。図5(f)(j)に示すように、ヒステリシスループの中点Oは外部磁界H=0のラインから外れて、Hinが50Oe程度にまで上昇していることがわかった。またΔMRについて見ると、100Oeの外部磁界が作用したときのΔMR(図5(f)参照)は、図5(b)の成膜時に比べて明らかに低下することがわかった。

【0080】

この実験結果によりΔMR低下の主要因は、Hinの増大にあるとわかった。Hinの増大は、後述する実験結果に示すように、酸素がフリー磁性層内部やフリー磁性層と非磁性材料層との界面にまで及びダメージを与えていることが原因の一つと考えられる。

【0081】

(Ta保護層の膜厚とΔMRとの関係、及び、Ta保護層の膜厚とHinとの関係について)

上記のRHカーブの実験結果をもとにして、Ta保護層の膜厚とΔMR、及び、Ta保護層の膜厚とHinとの関係について調べた。

【0082】

図6は、Ta保護層の膜厚とΔMRとの関係を示すグラフである。図6には、成膜時(As depo)でのΔMR及び無磁場アニール(アニール処理;270℃、アニール時間;3時間 窒素不活性フロー中)後のΔMRの双方が示されている。なお、ΔMRは外部磁界を100Oeとしたときの測定結果である。

【0083】

図7は、図6の横軸はそのままで縦軸を広げて示したTa保護層の膜厚とΔMRとの関係を示すグラフである。

【0084】

図6,図7に示すように、Ta保護層の膜厚を55Å以上にすると、無磁場アニール後でのΔMRを安定した高い値に維持できることがわかった。また図6,図7に示すように、Ta保護層の膜厚を55Å以上にすると、無磁場アニール後のΔMRを、成膜時(As depo)のΔMRよりも高くできることがわかった。

【0085】

図6,図7に示すように無磁場アニール後のΔMRは、Ta保護層の膜厚を55Åとしたときに最大値となり、Ta保護層の膜厚を55Åよりも大きくしていくと、徐々に小さくなることがわかった。これは、Ta保護層の膜厚が大きくなることで、Ta保護層に分流する電流値が増えたためである(シャントロス)。この効果を利用して、Ta保護層の膜厚を調整することで、ΔMR値、ひいてはブリッジ回路によるセンサ出力値を微調整することが出来る。

【0086】

ここで、Ta保護層の膜厚を30Åとした磁気検出素子の成膜時(As depo)でのΔMR(=11.9%)を基準値とし、無磁場アニール後のΔMRを、前記基準値から0.5%以内の低下に収めるにはTa保護層の膜厚を100Å以下に設定することが好ましいとわかった。

【0087】

またTa保護層の膜厚を70Å以上とすることで、成膜時に多少、Ta保護層の膜厚が狙い値より外れても、高くかつ安定したΔMRを得ることが出来る。

【0088】

図8は、Ta保護層の膜厚とHinとの関係を示すグラフである。図8には、成膜時(As depo)でのHin及び無磁場アニール(アニール処理;270℃、アニール時間;3時間 窒素不活性フロー中)後のHinの双方が示されている。

【0089】

図8に示すように、Ta保護層の膜厚を、55Å以上とすることで、無磁場アニール後においても、Hinをほぼ0Oeにできることがわかった。図8に示すように、Ta保護層の膜厚にかかわらず、成膜時であればHinをほぼゼロにできる。一方、無磁場アニールを行うとTa保護層の膜厚が小さくなるほどHinが大きくなり、特に膜厚=55Åを境として急激に上昇することがわかった。この点については図5のRHカーブを示しながらも説明した。

【0090】

以上の実験結果に基づいて、Ta保護層の膜厚を55Å以上、好ましくは55Å以上で100Å以下に設定し、さらに好ましくは70Å以上で100Å以下の範囲とした。

【0091】

(オージェ・デプス・プロファイルによる分析結果)

続いて、Ta保護層の膜厚と積層膜内の酸化状態との関係について、オージェ・デプス・プロファイルにより分析した。なお、積層膜の構造や無磁場アニール条件は上記実験と同じである。

【0092】

図9(a)は、Ta保護層の膜厚を50Åとした磁気検出素子に対し、成膜時(As depo)に測定したオージェ・デプス・プロファイルの分析結果、図9(b)は、Ta保護層の膜厚を50Åとした磁気検出素子に対し、無磁場アニール後にて測定したオージェ・デプス・プロファイルの分析結果、図9(c)は、Ta保護層の膜厚を70Åとした磁気検出素子に対し、無磁場アニール後にて測定したオージェ・デプス・プロファイルの分析結果である。

【0093】

図9(a)では、酸化は、Ta保護層(膜厚50Å)の表面から中間程度で止まり、酸素は、フリー磁性層(NiFe)に届いていないことがわかった。ただし図9(a)は、成膜時(As depo)の実験結果である。

【0094】

一方、図9(b)のように、Ta保護層の膜厚を50Åとし、無磁場アニールを施した場合では、Ta保護層の膜厚全体がほぼ酸化されており、酸素はフリー磁性層にも達していることがわかった。したがって50ÅのTa保護層では、フリー磁性層を酸化から保護できないことがわかった。

【0095】

これに対して、図9(c)に示すように、Ta保護層の膜厚を70Åとし、無磁場アニールを施した場合では、Ta保護層の一部に金属Taを残すことができ(図9(c)の矢印部分)、酸素はフリー磁性層に届いていないか、届いていたとしても、酸素量を非常に小さくできることがわかった。

【0096】

(TEM写真による分析結果)

続いて、Ta保護層の状態について、TEM写真により分析した。なお、積層膜の構造や無磁場アニール条件は上記実験と同じである。

【0097】

図10(a)は、Ta保護層の膜厚を30Åとした磁気検出素子の無磁場アニール後のTEM写真である。また図10(b)は、Ta保護層の膜厚を70Åとした磁気検出素子の無磁場アニール後のTEM写真である。

【0098】

図10(a)では、金属Taの部分は見られず、Ta保護層の全体が酸化していることがわかった。これによりTa保護層の酸化防止機能は失われ、Ta保護層下の積層膜内に酸化ダメージが及んでいるものと推測される。なお、図10(a)では、無磁場アニール後のTa保護層の膜厚は、成膜時の30Åから約80Åにまで膨らんでいることがわかった。

【0099】

一方、図10(b)では、金属Taが20Å程度残存していることがわかった。したがってTa保護層の膜厚中、50Åは酸化しており、酸化部分が100Å程度にまで膨らんでいることがわかった。このように図10(b)では、Ta保護層の酸化防止機能は失われておらず、Ta保護層下の積層膜に対する酸化ダメージを抑制することが可能である。

【0100】

図10(c)は、Ta保護層の膜厚を50Åとした磁気検出素子の成膜時(As Depo)でのTEM写真である。なお実験では、固定磁性層を構成する第1磁性層(FeCo)の膜厚を16.5Åにし、非磁性中間層(Ru)の膜厚を4Åとし、第2磁性層(CoFe)の膜厚を20Åとし、フリー磁性層を構成するCoFe層の膜厚を10Åとし、NiFe層の膜厚を40Åとした。その他の層の膜厚は、前述した実験のものと同じである。

【0101】

図10(c)に示すように、無磁場アニールをしなくても、磁気検出素子が大気中に曝されることでTa保護層の一部は酸化されることがわかった。図10(c)では、Ta保護層の約10Åが酸化して20Å程度の膜厚に膨らんでいることがわかった。

【0102】

図9,図10に示す実験結果から本実施例では、無磁場アニール後においても、Ta保護層の一部は金属Taとして残され、Ta保護層下の積層膜に対する酸化ダメージが抑制されていると推測される。そして、酸化ダメージの抑制により、本実施例の磁気検出素子では、安定して優れた磁気検出素子を得ることができると考えられる。

【0103】

なお図10に示すTEM写真などにより内部状態を観察し、Ta保護層のうち、残存する金属Taと酸化Taとの膜厚比や、金属Ta及び酸化Taの各膜厚値の測定結果から、成膜時のTa保護層の膜厚を推測することが可能である。

【符号の説明】

【0104】

P1、P2、P3 固定磁化方向(感度軸方向)

S 磁気センサ

1 磁気検出素子

1b〜1e 第1磁気検出素子

1f〜1i 第2磁気検出素子

2 シード層

3 固定磁性層

3a 第1磁性層

3b 非磁性中間層

3c 第2磁性層

4 非磁性材料層

5 フリー磁性層

6 保護層(Ta保護層)

10、11 ブリッジ回路

36 ハードバイアス層

65 基板

65a、65b センサ領域

【技術分野】

【0001】

本発明は、セルフピン止め型の磁気検出素子に関する。

【背景技術】

【0002】

従来、反強磁性層を用いて固定磁性層を交換結合磁界(Hex)により磁化固定する方法では、反強磁性層の結晶配向制御や固定磁性層の磁化分散を低減(単磁区化の促進)させるために、磁場中アニール(熱処理)を真空中で行うのが一般的であった。なお、真空中アニールでは酸化等の影響が小さいためにTaによる保護層の膜厚を30Å〜50Å程度に薄くしてもΔMR(抵抗変化率)等の特性に対する影響は小さかった。

【0003】

しかしながら磁場中アニール装置は高価であり、また真空中アニール時間が長時間になる問題があった。

【0004】

特許文献1,2は、固定磁性層をセルフピン止め型とし反強磁性層を設けていない。特許文献1,2ではTa保護層の膜厚を40Åにしている。

【0005】

セルフピン止め構造とすれば、磁場中アニール処理は不要となるが、磁気検出素子の成膜後、磁気センサの製造工程で曝される高温プロセスや、磁気センサの高温環境下での使用によっても特性変動が生じないように、無磁場でのアニール処理を行うことが必要である。このとき使用されるアニール装置は通常、低価格でアニール時間も短時間で済むが、特許文献1,2に示すようにTa保護層の膜厚を40Å程度に設定すると、特性劣化が問題になることが、今回の実験によりわかった。

【0006】

また特許文献3には固定磁性層をセルフピン止め型とし、Ru保護層を設けた発明が開示されている。特許文献3ではTa保護層を比較例として用いているが、膜厚が定かでない。ただし実施例に記載されているRu保護層と同じ膜厚であると仮定すれば30Åである。そして30Åの膜厚では、40Åの場合と同様に特性劣化が問題になる。

【0007】

また特許文献4も固定磁性層をセルフピン止め型としているが保護層の材質及び膜厚が定かでない。

【先行技術文献】

【特許文献】

【0008】

【特許文献1】US 7,019,949 B2

【特許文献2】US 7,196,878 B2

【特許文献3】特開2008−306112号公報

【特許文献4】特開2009−180604号公報

【発明の概要】

【発明が解決しようとする課題】

【0009】

そこで本発明は、上記従来の課題を解決するためのものであり、特に固定磁性層をセルフピン止め型とした構成において、Ta保護層の膜厚を適正化し、従来に比べて安定して優れた軟磁気特性を得ることが可能な磁気検出素子及びそれを用いた磁気センサ、並びに磁気検出素子の製造方法を提供することを目的とする。

【課題を解決するための手段】

【0010】

本発明における磁気検出素子は、固定磁性層とフリー磁性層とが非磁性材料層を介して積層された積層膜を備え、

前記固定磁性層は、第1磁性層と第2磁性層とが非磁性中間層を介して積層され、前記第1磁性層と前記第2磁性層とが反平行に磁化固定されたセルフピン止め型であり、

前記積層膜の最上層は、Taからなる保護層であり、前記保護層の成膜時における成膜時膜厚は55Å以上であることを特徴とするものである。

【0011】

また本発明は、固定磁性層とフリー磁性層とが非磁性材料層を介して積層された積層膜を備えた磁気検出素子の製造方法において、

前記固定磁性層を、第1磁性層と第2磁性層とが非磁性中間層を介して積層され、前記第1磁性層と前記第2磁性層とが反平行に磁化固定されたセルフピン止め型で形成し、

前記積層膜の最上層を、成膜時膜厚が55Å以上のTaからなる保護層で形成し、

大気中あるいは不活性ガスフロー中にて無磁場でのアニール処理を行うことを特徴とするものである。

【0012】

本発明では、固定磁性層をセルフピン止め型とした構成において、Ta保護層の成膜時の成膜時膜厚を、後述の実験結果に基づいて55Å以上に設定した。Ta保護層の膜厚の下限値を55Åとしたのは、55Åよりも小さいと、フリー磁性層と固定磁性層間に作用する層間結合磁界Hinが急激に大きくなり、ΔMRが急激に低下するためである。また、Ta保護層の膜厚の上限値は特に限定しないが、Ta保護層の膜厚を厚くしすぎるとTa保護層に分流する電流量が増えてしまい(シャントロス)、ΔMRが小さくなりやすい。よって、Ta保護層の膜厚上限値を調整することで他の磁気特性の信頼性を劣化させることなくΔMR値の調整が可能になる。

【0013】

以上により本発明によれば、固定磁性層をセルフピン止め型とした構成において、安定して優れた軟磁気特性を得ることが可能である。

【0014】

なお本発明における55Å以上としたTa保護層の膜厚は成膜時におけるものである。よって成膜後にアニール処理を行うことで、Ta保護層の一部が酸化されて保護層の膜厚は成膜時より厚くなる。このとき後述する実験結果に示すように、アニール後の状態の分析によりTa保護層の成膜時の膜厚を予測することが可能である。

【0015】

また本発明では、前記保護層の成膜時における成膜時膜厚は100Å以下であることが好ましい。Ta保護層の成膜時膜厚を30Åとした成膜時(As Depo)のΔMRを基準値とすると、Ta保護層の成膜時膜厚を100Å以下とすることで、無磁場アニール時のΔMRを基準値から最大で5%程度の低下で抑えることができるとわかった。また、前記保護層の前記フリー磁性層と接触する部分は金属Taであることが好ましい。

【0016】

また本発明では、前記保護層の膜厚は70Å以上で100Å以下であることが好ましい。Ta保護層の膜厚の下限値を55Åから70Åにずらすことで、多少、成膜時の膜厚が狙い値よりずれても、安定して優れた軟磁気特性を得ることが可能になる。

【0017】

また本発明における磁気センサは、同一基板上に、感度軸方向の異なる複数の上記に記載された磁気検出素子が配置されていることを特徴とするものである。

【0018】

本発明の磁気センサでは、上記したセルフピン止め型の磁気検出素子を使用することにより、様々な用途で、安定して優れた出力特性を得ることができる。

【発明の効果】

【0019】

本発明では、固定磁性層をセルフピン止め型とした構成において、従来に比べて、安定して優れた軟磁気特性を得ることが可能である。

【図面の簡単な説明】

【0020】

【図1】本実施形態における磁気検出素子の部分拡大縦断面図、

【図2】図1に示す磁気検出素子と、磁気検出素子に接続されるハードバイアス層との位置関係を示す部分縦断面図、

【図3】本実施形態における磁気センサの回路構成図、

【図4】本実施形態における磁気センサの製造方法を示す一工程図(平面図)、

【図5】(a)〜(d)は、Ta保護層の膜厚を代えた各磁気検出素子の成膜時(As Depo)におけるヒステリシスループ、(e)〜(h)は、Ta保護層の膜厚を代えた各磁気検出素子のアニール処理後におけるヒステリシスループ、(i)、(j)は、(e)、(f)と同じ磁気検出素子を用い、(e)、(f)に比べて外部磁界のレンジを広げたヒステリシスループ、

【図6】アニール処理後、及び成膜時(As Depo)における、Ta保護層の膜厚とΔMRとの関係を示すグラフ、

【図7】図6の縦軸を拡大して示したグラフ、

【図8】アニール処理後、及び成膜時(As Depo)における、Ta保護層の膜厚とHinとの関係を示すグラフ、

【図9】(a)は、Ta保護層の膜厚を50Åとした磁気検出素子の成膜時(As Depo)におけるオージェ・デプス・プロファイル、(b)は、Ta保護層の膜厚を50Åとした磁気検出素子のアニール処理後におけるオージェ・デプス・プロファイル、(c)は、Ta保護層の膜厚を70Åとした磁気検出素子のアニール処理後におけるオージェ・デプス・プロファイル、

【図10】(a)は、Ta保護層の膜厚を30Åとした磁気検出素子のアニール処理後におけるTEM写真、(b)は、Ta保護層の膜厚を70Åとした磁気検出素子のアニール処理後におけるTEM写真、(c)は、Ta保護層の膜厚を50Åとした磁気検出素子の成膜時(As Depo)におけるTEM写真。

【発明を実施するための形態】

【0021】

図1は、本実施形態における磁気検出素子の部分拡大縦断面図である。

図1に示すように本実施形態の磁気検出素子(GMR素子)1は、下から、シード層2、固定磁性層3、非磁性材料層4、フリー磁性層5及び保護層6の順に積層されて成膜される。磁気検出素子1を構成する各層は、例えばスパッタにて成膜される。

【0022】

シード層2は、NiFeCrあるいはCr等で形成される。またシード層2の膜厚は、36〜60Å程度である。シード層2と、図示しない基板との間に、Ta,Hf,Nb,Zr,Ti,Mo,W等からなる下地層が形成されていてもよい。

【0023】

固定磁性層3は、第1磁性層3aと第2磁性層3cと、第1磁性層3a及び第2磁性層3c間に介在する非磁性中間層3bとのAAF(artificial antiferromagnetic structure)構造である。

【0024】

図1に示すように第1磁性層3aの固定磁化方向(P1)と、第2磁性層3cの固定磁化方向(P2)は反平行となっている。

【0025】

図1に示すように、第1磁性層3aはシード層2上に形成されており、第2磁性層3cは、後述する非磁性材料層4に接して形成されている。

【0026】

本実施形態における第1磁性層3aは、第2磁性層3cよりも高保磁力材料のFexCo100-x(xは、55at%以上65at%以下であることが好ましい)で形成される。

【0027】

また図1に示すように、第1磁性層3aの膜厚は、例えば、14Å以上20.5Å以下の範囲内であり、第2磁性層3cの膜厚よりも薄くされている。

【0028】

これにより本実施形態では第1磁性層3aの保磁力Hcを高く安定した値にできる。例えば、50(kA/m)以上の保磁力Hcを得ることが可能である。

【0029】

非磁性材料層4に接する第2磁性層3cは磁気抵抗効果(GMR効果)に寄与する層であり、第2磁性層3cには、アップスピンを持つ伝導電子とダウンスピンを持つ伝導電子の平均自由行程差を大きくできる磁性材料が選択される。

【0030】

具体的には第2磁性層3cは、CoyFe100-y(yは85at%以上で100at%よりも小さいことが好ましい)あるいはCoで形成される。

【0031】

そして第2磁性層3cの膜厚は、例えば、16.5Å以上26Å以下の範囲内であり、第1磁性層3aの膜厚よりも厚く形成されている。

【0032】

第1磁性層3a及び第2磁性層3cの各膜厚は、第1磁性層3aと第2磁性層3cの磁化量(飽和磁化Ms・膜厚t)の差が実質的にゼロとなるように調整されている。

【0033】

本実施形態における固定磁性層3は、SFP構造によるセルフピン止め型である。すなわち反強磁性層を備えない構成であり、これにより磁気検出素子1の温度特性が反強磁性層のブロッキング温度に制約を受ける問題を解決できる。

【0034】

ここで、固定磁性層3の磁化固定力を高めるには、上記したように、第1磁性層3aの保磁力Hcを高めること、第1磁性層3aと第2磁性層3cの磁化量の差を実質的にゼロに調整すること、更に非磁性中間層3bの膜厚を調整して第1磁性層3aと第2磁性層3c間に生じるRKKY相互作用による反平行結合磁界を強めることが重要とされている。

【0035】

第1磁性層3aと第2磁性層3cの間に位置する非磁性中間層3bはRuで形成され、非磁性中間層3bの膜厚は、3.4Å以上4.2Å以下であることが好ましい。

【0036】

非磁性材料層4は、Cu(銅)などの非磁性導電材料で形成される。また、非磁性材料層4は絶縁層で形成されTMR素子にも適用できる。フリー磁性層5は、NiFe、CoFe、CoFeNiなどの軟磁性材料で形成される。図1に示す構造では、フリー磁性層5は、CoFe合金層5aとNiFe合金層5bとの積層構造であるが、フリー磁性層5の構造は限定されるものでない。すなわちフリー磁性層5の材質を限定するものでなく、また、単層構造、積層構造、及び積層フェリ構造の別を問わない。

【0037】

積層膜の最上層に位置する保護層6は、Ta(タンタル)で形成される。以下、Ta保護層6と称する。Ta保護層6の膜厚t1は、成膜時、55Å以上で形成される。特に断らない限り膜厚t1は成膜時膜厚を指す。

【0038】

図2は、図1に示す磁気検出素子1と、磁気検出素子1に接続されるハードバイアス層との位置関係を示す部分縦断面図である。

【0039】

図2(a)に示すように、磁気検出素子1は、支持基板9上に絶縁層50を介して形成されている。図2(a)に示すように磁気検出素子1上には、絶縁層51が設けられ、各ハードバイアス層36が絶縁層51の平坦化面上に形成される。

【0040】

あるいは図2(b)に示すように、磁気検出素子1の一部を除去して、その除去された凹部1a上にハードバイアス層36を形成してもよい。または図2(c)に示すように、ハードバイアス層36の形成位置における磁気検出素子1を全て削除して、分離した各磁気検出素子1の間に各ハードバイアス層36を介在させる構成とすることも出来る。

【0041】

これにより、磁気検出素子1を構成するフリー磁性層5(図1参照)にY方向からバイアス磁界が供給され、フリー磁性層5の磁化は、固定磁性層3の固定磁化方向に対して直交する方向に向けられる。

【0042】

本実施形態では図2に示すY方向に長く延びる磁気検出素子1がX方向に間隔を空けて複数本、配置され、各磁気検出素子1の端部間が導電層により接続されたミアンダ形状となっている。

【0043】

この実施形態では、磁気検出素子1を構成する非磁性材料層4はCu等の非磁性導電層であり、電流が積層膜の膜面と略平行な方向に流される。

【0044】

ミアンダ形状にて構成された磁気検出素子1は、複数個、設けられ、図3に示すブリッジ回路を構成する。図3では、各磁気検出素子1を区別するために第1磁気検出素子1b〜1e、第2磁気検出素子1f〜1iと符号を付すこととする。

【0045】

図3に示すように、本実施形態の磁気センサSは、4個の第1磁気検出素子1b〜1eにより構成された第1ブリッジ回路10と、4個の第2磁気検出素子1f〜1iにより構成された第2ブリッジ回路11とを有して構成される。

【0046】

図3に示すように、第1ブリッジ回路10を構成する第1磁気検出素子1b,1eの感度軸方向(図1に示す固定磁性層3を構成する第2磁性層3cの固定磁化方向(P2))と、第1磁気検出素子1c,1dの感度軸方向とは、反平行にされている。そして、第1磁気検出素子1bと第1磁気検出素子1c、及び、第1磁気検出素子1dと第1磁気検出素子1eとが、夫々、直列に接続される。第1磁気検出素子1b,1dは、入力端子(Vdd)20に接続され、第1磁気検出素子1c,1eはグランド端子(GND)21に接続され、第1磁気検出素子1bと第1磁気検出素子1cとの間、及び第1磁気検出素子1dと第1磁気検出素子1eとの間に夫々、出力端子(VX1,VX2)22,23が接続されている。

【0047】

また、図3に示すように第2ブリッジ回路11を構成する第2磁気検出素子1f,1iの感度軸方向(図3では、「P3」で示す)と、第2磁気検出素子1g,1hの感度軸方向とは、反平行にされている。そして、第2磁気検出素子1fと第2磁気検出素子1g、及び、第2磁気検出素子1hと第2磁気検出素子1iとが、夫々、直列に接続される。第2磁気検出素子1f,1hは、入力端子(Vdd)20に接続され、第2磁気検出素子1g,1iはグランド端子(GND)21に接続され、第2磁気検出素子1fと第2磁気検出素子1gとの間、及び第2磁気検出素子1hと第2磁気検出素子1iとの間に夫々、出力端子(VY1,VY2)24,25が接続されている。

【0048】

図3に示すように各第1磁気検出素子1b〜1eの感度軸方向(P2)と、各第2磁気検出素子1f〜1iの感度軸方向(P3)とは直交している。

【0049】

図3に示す磁気センサSには、例えば、図示しない磁石が高さ方向(Z)に間隔を空けて対向している。そして磁石から各磁気検出素子1b〜1iに外部磁界Hが作用する。

【0050】

例えば外部磁界Hが図3に示す方向に作用したとすると、第1ブリッジ回路10を構成する第1磁気検出素子1b,1eでは感度軸方向と外部磁界Hの方向が一致するため電気抵抗値は小さくなり、一方、第1磁気検出素子1c,1dでは、感度軸方向と外部磁界Hの方向が反対であるため電気抵抗値は大きくなり、出力端子22,23の中点電位が変動することでセンサ出力を得ることが出来る。一方、第2ブリッジ回路11では、外部磁界Hが各感度軸方向(P3)に対して直交する方向から作用するため、各第2磁気検出素子1f〜1iの電気抵抗値は等しくなり、出力端子24,25の中点電位は変動しない(センサ出力はゼロである)。外部磁界Hの方向が変動すれば、それに伴い各ブリッジ回路10,11のセンサ出力も変動する。

【0051】

そして、各ブリッジ回路10、11から得られるセンサ出力に基づいて、磁石の移動方向や移動量(相対位置)を知ることができる。

【0052】

本実施形態の磁気センサSは、例えば、磁気検出素子が基板上に1個で、残りが固定抵抗からなるブリッジ回路とすることも可能である。

【0053】

本実施形態の磁気センサSは、地磁気センサ、回転センサ、磁気スイッチ等、特に用途が限定されるものでない。

【0054】

本実施形態における磁気検出素子1の特徴的部分は、Ta保護層6の膜厚t1が、成膜時、55Å以上にて調整される点である。

【0055】

本実施形態のように、積層膜内に反強磁性層を有さず、固定磁性層3をセルフピン止め型とした構成では、磁場中アニールが不要である。ただし、磁気検出素子1の成膜後、磁気センサSの製造工程で曝される高温プロセスや、磁気センサSの高温環境下での使用によっても特性変動が生じないように、大気中あるいは窒素不活性ガスフロー中にて無磁場でのアニール処理(以下、無磁場アニールという)を行うことが必要である。このとき使用されるアニール装置は通常、低価格でアニール時間も短時間で済むが、Ta保護層6の膜厚t1を薄くすると、Ta保護層6及びTa保護層6下の積層膜が酸化の影響を受けて、特性劣化が問題になることが、今回の実験によりわかった。

【0056】

そこで、本実施形態では、固定磁性層3をセルフピン止め型とした構成において、Ta保護層6の成膜時における膜厚t1を、後述の実験結果に基づいて55Å以上に設定した。Ta保護層6の膜厚t1の下限値を55Åとしたのは、55Åよりも小さいと、フリー磁性層5と固定磁性層3間に作用する層間結合磁界Hinが急激に大きくなり、ΔMR(抵抗変化率)が急激に低下するためである。Ta保護層6の膜厚t1を55Å以上とすることで、無磁場アニールに曝しても、Ta保護層6の表面側は酸化されるものの一部の金属Taが残留し、酸素が、Ta保護層6の直下に位置するフリー磁性層5にまで届いておらず、あるいはフリー磁性層5に届く酸素量を極力、小さくできる。この結果、フリー磁性層5の内部状態、及びフリー磁性層5と非磁性材料層4との界面状態等を、成膜時(As Depo)とほぼ同じ状態に維持できると推測され、これにより、安定して優れた軟磁気特性が得られるものと考えられる。また、Ta保護層6の膜厚の上限値は特に限定しないが、Ta保護層6の膜厚を厚くしすぎるとTa保護層6に分流する電流量が増えてしまい(シャントロス)、ΔMRが小さくなりやすい。よってTa保護層6の膜厚を厚くすることで、Ta保護層6に分流する電流量を増やし、ΔMR値を微調整することができる。このため、Ta保護層の膜厚上限値を調整することで他の磁気特性の信頼性を劣化させることなくΔMR値の調整が可能になる。

【0057】

本実施形態では,Ta保護層6の膜厚上限は100Åであることが好ましい。後述する実験では、Ta保護層6の膜厚を30Åとした成膜時(As Depo)のΔMRを基準値とすると、Ta保護層6の膜厚t1を100Å以下とすることで、無磁場アニール時のΔMRを基準値から最大で5%程度の低下で抑えることができるとわかった。

【0058】

以上により本実施形態によれば、固定磁性層3をセルフピン止め型とした構成において、安定して優れた軟磁気特性を得ることが可能である。本実施形態では、Hinを20Oe以下に、好ましくはほぼゼロにまで小さくでき、またアニール処理前と同等以上のΔMRを得ることができる。

【0059】

したがって図3に示す磁気センサSでは、本実施形態のセルフピン止め型の磁気検出素子1を使用することで、安定して優れた軟磁気特性を得ることができ、様々な用途で出力特性に優れた使用が可能である。

【0060】

なお本実施形態における55Å以上としたTa保護層6の膜厚t1は成膜時(As Depo)におけるものである。よって成膜後に無磁場アニールを行うことで、Ta保護層6の一部が酸化されて保護層の膜厚は成膜時より厚くなるが、後述する実験結果に示すように、アニール後の状態からTa保護層6の成膜時の膜厚t1を予測することが可能である。Ta保護層6の膜厚t1を55Åとした場合、無磁場アニール後にて金属Taとして残される膜厚は5Å程度で、酸化Taとなる膜厚は100Å程度である。また、Ta保護層6の膜厚t1を70Åとした場合、金属Taとして残される膜厚は20Å程度で、酸化Taとなる膜厚は100Å程度である。アニール温度及びアニール時間によって、無磁場アニール後の膜厚は変動するが、アニール温度を250〜300℃程度、アニール時間を1〜4時間程度とすれば、概ね、上記の膜厚範囲内に収めることが可能である。後述するように例えば、TEM写真により、酸化Taの膜厚と、金属Taの膜厚を知ることができる。この酸化Taの膜厚値と、金属Taの膜厚値、及び膜厚比率から、成膜時のTa保護層6の膜厚t1を推測することが可能である。

【0061】

また本実施形態では、Ta保護層6の膜厚t1を70Å以上で100Å以下の範囲内にて調整することが好ましい。Ta保護層6の膜厚t1の下限値を55Åから70Åにずらすことで、多少、成膜時の膜厚t1が狙い値から外れても、安定して優れた軟磁気特性を得ることが可能である。

【0062】

図3に示す磁気センサSは、例えば、次のようにして製造することができる。図4(a)〜図4(b)は本実施形態における磁気センサSの製造方法を示す一工程図である。各図は製造工程中における平面図を示している。

【0063】

図4(a)では、基板65を用意する。基板65は、第1センサ領域65aと、第2センサ領域65bとを有している。

【0064】

図4(a)の工程では、基板65の第1センサ領域65a及び第2センサ領域65bに夫々、2個ずつ第1磁気検出素子1b〜1eを形成する。磁場中成膜を施してAAF構造からなるセルフピン止め型の固定磁性層3(図1参照)を同じX方向に磁化固定する。図4(a)に示すP2は、各第1磁気検出素子1b〜1eを構成する固定磁性層3の第2磁性層3cの固定磁化方向(感度軸方向)を示している。

【0065】

次に、図4(b)の工程では、基材65の第1センサ領域65a及び第2センサ領域65bに夫々、2個ずつ第2磁気検出素子1f〜1iを形成する。磁場中成膜を施してAAF構造からなるセルフピン止め構造の固定磁性層3を同じY方向に磁化固定する。図4(b)に示すP3は、各第2磁気検出素子1f〜1iを構成する固定磁性層3の第2磁性層3cの固定磁化方向(感度軸方向)を示している。

【0066】

本実施形態では、各固定磁性層3の磁化固定制御に対してアニール処理を施さないため、図4(b)の工程で、第2磁気検出素子1f〜1iの固定磁性層3をY方向に磁化固定するために磁場を施しても、図4(a)の工程にて、既に形成された第1磁気検出素子1b〜1eの固定磁性層3の固定磁化方向(P2)をX方向に向けた状態のまま適切に保つことが出来る。

【0067】

本実施形態では、各磁気検出素子1b〜1iのTa保護層6を、55Å以上、好ましくは55Å以上で100Å以下、さらに好ましくは70Å以上で100Å以下の範囲内にて成膜する。

【0068】

その後、各磁気検出素子1b〜1iの両側にハードバイアス層36を配置し、各磁気検出素子1b〜1iとハードバイアス層36とを組み合わせた平面形状をミアンダ状にする。

【0069】

本実施形態では、各磁気検出素子1b〜1iの成膜後、大気中、あるいは不活性ガスフロー中(例えば安価な窒素不活性ガスを用いる)にて、無磁場アニールを施す。無磁場アニールのタイミングは、各磁気検出素子1b〜1iの成膜後であれば特に問わないが、磁気センサSの製造工程で曝される高温プロセス前や、前記高温プロセスを有さない場合には、磁気センサSの製造工程中に行われる。

【0070】

ここでアニール温度としては、250〜300℃程度、アニール時間としては、1〜4時間程度である。

【0071】

その後、図4に示す第1センサ領域65aと第2センサ領域65bとを分離し、第2センサ領域65bを第1センサ領域65aに対して180度反転させた状態として、図3に示す入力端子20、グランド端子21及び各出力端子22〜25との間で電気的接続を行う。これにより図3に示す第1ブリッジ回路10と第2ブリッジ回路11とを形成することが出来る。

【実施例】

【0072】

(Ta保護層の膜厚を変化させたときのRHカーブの実験)

以下の積層膜を有する磁気検出素子を作製した。

基板/シード層:NiFeCr(42)/固定磁性層[第1磁性層:Fe60at%Co40at%(18.7)/非磁性中間層:Ru(3.6)/第2磁性層Co90at%Fe10at%(24)]/非磁性材料層:Cu(22)/フリー磁性層[Co90at%Fe10at%(12)/NiFe(20)]/保護層:Ta(X)

各層における括弧内の数値は膜厚を示し、単位はÅである。

【0073】

まず成膜時(As Depo)のRHカーブを測定した。

実験では、Ta保護層の膜厚を30Å、50Å、55Å及び70Åとして、各磁気検出素子のRHカーブを測定した。図5(a)は、Ta保護層の膜厚を30Åとした磁気検出素子のRHカーブ(成膜時(As Depo))、図5(b)は、Ta保護層の膜厚を50Åとした磁気検出素子のRHカーブ(成膜時(As Depo))、図5(c)は、Ta保護層の膜厚を55Åとした磁気検出素子のRHカーブ(成膜時(As Depo))、図5(d)は、Ta保護層の膜厚を70Åとした磁気検出素子のRHカーブ(成膜時(As Depo))である。なお実験では磁気検出素子に印加する外部磁界を±100Oeの範囲とした。ここで外部磁界のプラス値は、固定磁性層の固定磁化方向に対して反対方向であり、外部磁界のマイナス値は、固定磁性層の固定磁化方向と同方向である。

【0074】

フリー磁性層と固定磁性層との間に作用する層間結合磁界Hinは、各図5(a)〜図5(d)におけるRHカーブの最大ΔMR及び最小ΔMRの中間値であって、ヒステリシスループの広がり幅の中心値を「中点」としたとき、前記中点から外部磁界H=0(Oe)のラインまでの磁界の強さで決定される。図5(a)に中点Oを示した。図5(a)に示すように中点Oは、ほぼ外部磁界H=0のライン上にある。よって、Hinはほぼ0(Oe)である。

【0075】

図5(a)〜図5(d)に示すように、Ta保護層の膜厚にかかわらず、成膜時(As Depo)のHinは、ほぼ0(Oe)になることがわかった。

【0076】

次に、各磁気検出素子に対し、窒素不活性フロー中にてアニール処理を270℃、アニール時間を3時間とした無磁場アニールを行った。そして、各磁気検出素子のRHカーブを測定した。図5(e)は、Ta保護層の膜厚を30Åとした磁気検出素子のRHカーブ(無磁場アニール後)、図5(f)は、Ta保護層の膜厚を50Åとした磁気検出素子のRHカーブ(無磁場アニール後)、図5(g)は、Ta保護層の膜厚を55Åとした磁気検出素子のRHカーブ(無磁場アニール後)、図5(h)は、Ta保護層の膜厚を70Åとした磁気検出素子のRHカーブ(無磁場アニール後)である。なお実験では、外部磁界を±100Oeの範囲とした。

【0077】

図5(g)(h)に示すように、Ta保護層の膜厚を55Å、70Åとした場合、無磁場アニールを行うと、成膜時(As Depo)と比べて、若干、保磁力Hcが大きくなったが(ヒステリシスループの前記中点を通る横軸方向への広がり幅が保磁力の2倍に相当する)、ΔMR及びHinについては、あまり変化しないことがわかった。むしろ、後述するように、無磁場アニール後のΔMRは、成膜時のΔMRよりもやや高くなった。

【0078】

これに対して、図5(e)に示すように、Ta保護層の膜厚を30Åとした場合、外部磁界を±100Oeの範囲とすると、ΔMRは飽和せずに変動領域にあるため、ヒステリシスループ全体が見えるように、外部磁界のレンジを±500Oeまで広げたのが図5(i)である。図5(i)に示すようにヒステリシスループの中点Oは外部磁界H=0のラインから大きく外れてしまい、Hinが大幅に上昇していることがわかった。具体的にはHinは、90Oe程度にまで大きくなっている。またΔMRについて見ると、100Oeの外部磁界が作用したときのΔMR(図5(e)参照)は、図5(a)の成膜時に比べて大幅に低下することがわかった。

【0079】

図5(f)は、Ta保護層の膜厚を50Åとした場合のRHカーブ(外部磁界を±100Oe)、図5(j)は、Ta保護層の膜厚を50Åとした場合のRHカーブ(外部磁界を±500Oe)である。図5(f)(j)に示すように、ヒステリシスループの中点Oは外部磁界H=0のラインから外れて、Hinが50Oe程度にまで上昇していることがわかった。またΔMRについて見ると、100Oeの外部磁界が作用したときのΔMR(図5(f)参照)は、図5(b)の成膜時に比べて明らかに低下することがわかった。

【0080】

この実験結果によりΔMR低下の主要因は、Hinの増大にあるとわかった。Hinの増大は、後述する実験結果に示すように、酸素がフリー磁性層内部やフリー磁性層と非磁性材料層との界面にまで及びダメージを与えていることが原因の一つと考えられる。

【0081】

(Ta保護層の膜厚とΔMRとの関係、及び、Ta保護層の膜厚とHinとの関係について)

上記のRHカーブの実験結果をもとにして、Ta保護層の膜厚とΔMR、及び、Ta保護層の膜厚とHinとの関係について調べた。

【0082】

図6は、Ta保護層の膜厚とΔMRとの関係を示すグラフである。図6には、成膜時(As depo)でのΔMR及び無磁場アニール(アニール処理;270℃、アニール時間;3時間 窒素不活性フロー中)後のΔMRの双方が示されている。なお、ΔMRは外部磁界を100Oeとしたときの測定結果である。

【0083】

図7は、図6の横軸はそのままで縦軸を広げて示したTa保護層の膜厚とΔMRとの関係を示すグラフである。

【0084】

図6,図7に示すように、Ta保護層の膜厚を55Å以上にすると、無磁場アニール後でのΔMRを安定した高い値に維持できることがわかった。また図6,図7に示すように、Ta保護層の膜厚を55Å以上にすると、無磁場アニール後のΔMRを、成膜時(As depo)のΔMRよりも高くできることがわかった。

【0085】

図6,図7に示すように無磁場アニール後のΔMRは、Ta保護層の膜厚を55Åとしたときに最大値となり、Ta保護層の膜厚を55Åよりも大きくしていくと、徐々に小さくなることがわかった。これは、Ta保護層の膜厚が大きくなることで、Ta保護層に分流する電流値が増えたためである(シャントロス)。この効果を利用して、Ta保護層の膜厚を調整することで、ΔMR値、ひいてはブリッジ回路によるセンサ出力値を微調整することが出来る。

【0086】

ここで、Ta保護層の膜厚を30Åとした磁気検出素子の成膜時(As depo)でのΔMR(=11.9%)を基準値とし、無磁場アニール後のΔMRを、前記基準値から0.5%以内の低下に収めるにはTa保護層の膜厚を100Å以下に設定することが好ましいとわかった。

【0087】

またTa保護層の膜厚を70Å以上とすることで、成膜時に多少、Ta保護層の膜厚が狙い値より外れても、高くかつ安定したΔMRを得ることが出来る。

【0088】

図8は、Ta保護層の膜厚とHinとの関係を示すグラフである。図8には、成膜時(As depo)でのHin及び無磁場アニール(アニール処理;270℃、アニール時間;3時間 窒素不活性フロー中)後のHinの双方が示されている。

【0089】

図8に示すように、Ta保護層の膜厚を、55Å以上とすることで、無磁場アニール後においても、Hinをほぼ0Oeにできることがわかった。図8に示すように、Ta保護層の膜厚にかかわらず、成膜時であればHinをほぼゼロにできる。一方、無磁場アニールを行うとTa保護層の膜厚が小さくなるほどHinが大きくなり、特に膜厚=55Åを境として急激に上昇することがわかった。この点については図5のRHカーブを示しながらも説明した。

【0090】

以上の実験結果に基づいて、Ta保護層の膜厚を55Å以上、好ましくは55Å以上で100Å以下に設定し、さらに好ましくは70Å以上で100Å以下の範囲とした。

【0091】

(オージェ・デプス・プロファイルによる分析結果)

続いて、Ta保護層の膜厚と積層膜内の酸化状態との関係について、オージェ・デプス・プロファイルにより分析した。なお、積層膜の構造や無磁場アニール条件は上記実験と同じである。

【0092】

図9(a)は、Ta保護層の膜厚を50Åとした磁気検出素子に対し、成膜時(As depo)に測定したオージェ・デプス・プロファイルの分析結果、図9(b)は、Ta保護層の膜厚を50Åとした磁気検出素子に対し、無磁場アニール後にて測定したオージェ・デプス・プロファイルの分析結果、図9(c)は、Ta保護層の膜厚を70Åとした磁気検出素子に対し、無磁場アニール後にて測定したオージェ・デプス・プロファイルの分析結果である。

【0093】

図9(a)では、酸化は、Ta保護層(膜厚50Å)の表面から中間程度で止まり、酸素は、フリー磁性層(NiFe)に届いていないことがわかった。ただし図9(a)は、成膜時(As depo)の実験結果である。

【0094】

一方、図9(b)のように、Ta保護層の膜厚を50Åとし、無磁場アニールを施した場合では、Ta保護層の膜厚全体がほぼ酸化されており、酸素はフリー磁性層にも達していることがわかった。したがって50ÅのTa保護層では、フリー磁性層を酸化から保護できないことがわかった。

【0095】

これに対して、図9(c)に示すように、Ta保護層の膜厚を70Åとし、無磁場アニールを施した場合では、Ta保護層の一部に金属Taを残すことができ(図9(c)の矢印部分)、酸素はフリー磁性層に届いていないか、届いていたとしても、酸素量を非常に小さくできることがわかった。

【0096】

(TEM写真による分析結果)

続いて、Ta保護層の状態について、TEM写真により分析した。なお、積層膜の構造や無磁場アニール条件は上記実験と同じである。

【0097】

図10(a)は、Ta保護層の膜厚を30Åとした磁気検出素子の無磁場アニール後のTEM写真である。また図10(b)は、Ta保護層の膜厚を70Åとした磁気検出素子の無磁場アニール後のTEM写真である。

【0098】

図10(a)では、金属Taの部分は見られず、Ta保護層の全体が酸化していることがわかった。これによりTa保護層の酸化防止機能は失われ、Ta保護層下の積層膜内に酸化ダメージが及んでいるものと推測される。なお、図10(a)では、無磁場アニール後のTa保護層の膜厚は、成膜時の30Åから約80Åにまで膨らんでいることがわかった。

【0099】

一方、図10(b)では、金属Taが20Å程度残存していることがわかった。したがってTa保護層の膜厚中、50Åは酸化しており、酸化部分が100Å程度にまで膨らんでいることがわかった。このように図10(b)では、Ta保護層の酸化防止機能は失われておらず、Ta保護層下の積層膜に対する酸化ダメージを抑制することが可能である。

【0100】

図10(c)は、Ta保護層の膜厚を50Åとした磁気検出素子の成膜時(As Depo)でのTEM写真である。なお実験では、固定磁性層を構成する第1磁性層(FeCo)の膜厚を16.5Åにし、非磁性中間層(Ru)の膜厚を4Åとし、第2磁性層(CoFe)の膜厚を20Åとし、フリー磁性層を構成するCoFe層の膜厚を10Åとし、NiFe層の膜厚を40Åとした。その他の層の膜厚は、前述した実験のものと同じである。

【0101】

図10(c)に示すように、無磁場アニールをしなくても、磁気検出素子が大気中に曝されることでTa保護層の一部は酸化されることがわかった。図10(c)では、Ta保護層の約10Åが酸化して20Å程度の膜厚に膨らんでいることがわかった。

【0102】

図9,図10に示す実験結果から本実施例では、無磁場アニール後においても、Ta保護層の一部は金属Taとして残され、Ta保護層下の積層膜に対する酸化ダメージが抑制されていると推測される。そして、酸化ダメージの抑制により、本実施例の磁気検出素子では、安定して優れた磁気検出素子を得ることができると考えられる。

【0103】

なお図10に示すTEM写真などにより内部状態を観察し、Ta保護層のうち、残存する金属Taと酸化Taとの膜厚比や、金属Ta及び酸化Taの各膜厚値の測定結果から、成膜時のTa保護層の膜厚を推測することが可能である。

【符号の説明】

【0104】

P1、P2、P3 固定磁化方向(感度軸方向)

S 磁気センサ

1 磁気検出素子

1b〜1e 第1磁気検出素子

1f〜1i 第2磁気検出素子

2 シード層

3 固定磁性層

3a 第1磁性層

3b 非磁性中間層

3c 第2磁性層

4 非磁性材料層

5 フリー磁性層

6 保護層(Ta保護層)

10、11 ブリッジ回路

36 ハードバイアス層

65 基板

65a、65b センサ領域

【特許請求の範囲】

【請求項1】

固定磁性層とフリー磁性層とが非磁性材料層を介して積層された積層膜を備え、

前記固定磁性層は、第1磁性層と第2磁性層とが非磁性中間層を介して積層され、前記第1磁性層と前記第2磁性層とが反平行に磁化固定されたセルフピン止め型であり、

前記積層膜の最上層は、Taからなる保護層であり、前記保護層の成膜時における成膜時膜厚は55Å以上であることを特徴とする磁気検出素子。

【請求項2】

前記保護層の成膜時における成膜時膜厚は100Å以下である請求項1記載の磁気検出素子。

【請求項3】

前記保護層の前記フリー磁性層と接触する部分は金属Taである請求項1又は2に記載の磁気検出素子。

【請求項4】

前記保護層の成膜時膜厚は70Å以上で100Å以下である請求項1ないし3のいずれか1項に記載の磁気検出素子。

【請求項5】

同一基板上に、感度軸方向の異なる複数の請求項1ないし4のいずれか1項に記載された磁気検出素子が配置されていることを特徴とする磁気センサ。

【請求項6】

固定磁性層とフリー磁性層とが非磁性材料層を介して積層された積層膜を備えた磁気検出素子の製造方法において、

前記固定磁性層を、第1磁性層と第2磁性層とが非磁性中間層を介して積層され、前記第1磁性層と前記第2磁性層とが反平行に磁化固定されたセルフピン止め型で形成し、

前記積層膜の最上層を、成膜時膜厚が55Å以上のTaからなる保護層で形成し、

大気中あるいは不活性ガスフロー中にて無磁場でのアニール処理を行うことを特徴とする磁気検出素子の製造方法。

【請求項7】

前記成膜時膜厚が100Å以下のTaからなる保護層を形成する請求項6記載の磁気検出素子の製造方法。

【請求項8】

前記保護層を70Å以上で100Å以下の膜厚範囲内で形成する請求項6又は7に記載の磁気検出素子の製造方法。

【請求項1】

固定磁性層とフリー磁性層とが非磁性材料層を介して積層された積層膜を備え、

前記固定磁性層は、第1磁性層と第2磁性層とが非磁性中間層を介して積層され、前記第1磁性層と前記第2磁性層とが反平行に磁化固定されたセルフピン止め型であり、

前記積層膜の最上層は、Taからなる保護層であり、前記保護層の成膜時における成膜時膜厚は55Å以上であることを特徴とする磁気検出素子。

【請求項2】

前記保護層の成膜時における成膜時膜厚は100Å以下である請求項1記載の磁気検出素子。

【請求項3】

前記保護層の前記フリー磁性層と接触する部分は金属Taである請求項1又は2に記載の磁気検出素子。

【請求項4】

前記保護層の成膜時膜厚は70Å以上で100Å以下である請求項1ないし3のいずれか1項に記載の磁気検出素子。

【請求項5】

同一基板上に、感度軸方向の異なる複数の請求項1ないし4のいずれか1項に記載された磁気検出素子が配置されていることを特徴とする磁気センサ。

【請求項6】

固定磁性層とフリー磁性層とが非磁性材料層を介して積層された積層膜を備えた磁気検出素子の製造方法において、

前記固定磁性層を、第1磁性層と第2磁性層とが非磁性中間層を介して積層され、前記第1磁性層と前記第2磁性層とが反平行に磁化固定されたセルフピン止め型で形成し、

前記積層膜の最上層を、成膜時膜厚が55Å以上のTaからなる保護層で形成し、

大気中あるいは不活性ガスフロー中にて無磁場でのアニール処理を行うことを特徴とする磁気検出素子の製造方法。

【請求項7】

前記成膜時膜厚が100Å以下のTaからなる保護層を形成する請求項6記載の磁気検出素子の製造方法。

【請求項8】

前記保護層を70Å以上で100Å以下の膜厚範囲内で形成する請求項6又は7に記載の磁気検出素子の製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【公開番号】特開2013−16609(P2013−16609A)

【公開日】平成25年1月24日(2013.1.24)

【国際特許分類】

【出願番号】特願2011−147941(P2011−147941)

【出願日】平成23年7月4日(2011.7.4)

【出願人】(000010098)アルプス電気株式会社 (4,263)

【Fターム(参考)】

【公開日】平成25年1月24日(2013.1.24)

【国際特許分類】

【出願日】平成23年7月4日(2011.7.4)

【出願人】(000010098)アルプス電気株式会社 (4,263)

【Fターム(参考)】

[ Back to top ]