積層インダクタ素子の製造方法、および積層インダクタ素子

【課題】マザー基板からの個片化が容易であり、高品質な積層型インダクタ素子を形成できる積層型インダクタ素子の製造方法を提供する。

【解決手段】第1非磁性体層121、第1磁性体層111、第2非磁性体層122、第2磁性体層112、第3非磁性体層123の順で層状化されたマザー基板100を形成する。マザー基板100の第1非磁性体層121に個片化用の溝140を形成する。溝140が形成されたマザー基板100を焼成する。焼成後のマザー基板100における第3非磁性体層123側の面に、所定の押圧力でダイヤモンドスクライバー200を接触させる。これにより、接触位置から略積層方向に沿ってクラック150が発生する。マザー基板100に対して外部から曲げ応力を加えることで、クラック150と溝140とを結ぶようにマザー基板100が割れ、マザー基板100から複数の積層型インダクタ素子へ個片化される。

【解決手段】第1非磁性体層121、第1磁性体層111、第2非磁性体層122、第2磁性体層112、第3非磁性体層123の順で層状化されたマザー基板100を形成する。マザー基板100の第1非磁性体層121に個片化用の溝140を形成する。溝140が形成されたマザー基板100を焼成する。焼成後のマザー基板100における第3非磁性体層123側の面に、所定の押圧力でダイヤモンドスクライバー200を接触させる。これにより、接触位置から略積層方向に沿ってクラック150が発生する。マザー基板100に対して外部から曲げ応力を加えることで、クラック150と溝140とを結ぶようにマザー基板100が割れ、マザー基板100から複数の積層型インダクタ素子へ個片化される。

【発明の詳細な説明】

【技術分野】

【0001】

この発明は、磁性体を含む積層体内にコイル導体のパターンが形成された積層インダクタ素子の製造方法、および当該製造方法で製造される積層インダクタ素子に関するものである。

【背景技術】

【0002】

従来、積層型チップ素子を製造する際には、最終的に複数の積層型チップ素子を配列されるマザー基板の状態で機能部となる積層部を形成する。そして、マザー基板を素子単位で分割することで、個別の積層型チップ素子を製造している。

【0003】

磁性体を用いない積層セラミックコンデンサ等の従来の一般的な積層型チップ素子の場合、マザー基板から各積層型チップ素子を分割する際には、例えば特許文献1に示すように、マザー基板における分割すべき位置にブレイク用の溝を形成する。ブレイク用の溝は、マザー基板の表面から比較的浅く(表層付近だけ)形成されている。

【0004】

このような誘電体を用いた積層型チップ素子とは別に、現在、インダクタンスの大きなパワーインダクタ用として、磁性体を含む積層体からなる積層型インダクタ素子が多く利用されている。

【0005】

図10は、特許文献1に示した積層型チップ素子の製造工程を、磁性体を含む積層型インダクタ素子に適用した場合の製造フローチャートである。この工法を、従来の工法とする。図11は、特許文献1に示した積層型チップ素子の製造工程を、磁性体を含む積層型インダクタ素子に適用した場合の分割前の断面図である。

【0006】

図10に示すように、従来の工法では、まず第1非磁性体層121、第1磁性体層111,第2非磁性体層122、第2磁性体層112、および第3非磁性体層123をこの順で積層して、焼成前のマザー基板100を形成する(S901)。第1磁性体層111、第2磁性体層112には、ペースト状の導体パターン130が形成されている。次に、マザー基板100の第1非磁性体層121側の表面および第3非磁性体層123側の表面に、個片化用の溝140、141を形成する(S902)。この際、溝140、141は、第1非磁性体層121内および第3非磁性体層123内に止まる深さで形成されている。次に、マザー基板100を焼成することで、磁性体および非磁性体の焼結と、導体パターンのメッキ処理を行う(S903)。これにより、図11に示すような断面形状からなるマザー基板100が形成される。溝141はV字状に形成されており、最後に、焼成後のマザー基板100に作業者が手で負荷をかけることにより、溝141に沿ってマザー基板100を個片に分割する(S904)。これにより、個片化された積層型インダクタ素子の筐体が完成する。そして、筐体の所定位置に外部電極を形成することで、積層型インダクタ素子が実現される。

【0007】

図12は、図11で示した積層型インダクタ素子よりも厚みの厚い、磁性体を含む積層型インダクタ素子を製造する場合の分割前の断面図である。

【0008】

厚みの厚い積層型インダクタ素子を製造する場合では、まず第1非磁性体層121、第1磁性体層111,第2非磁性体層122、第2磁性体層112、および第3非磁性体層123をこの順で積層して、焼成前のマザー基板100を形成する。第1磁性体層111、第2磁性体層112には、導体パターン130が形成されている。次に、マザー基板100の第1非磁性体層121側の表面のみに、個片化用の溝140を形成する。この際、溝140は、第1非磁性体層121内および第3非磁性体層123内に止まる深さで形成されている。次に、マザー基板100の第3非磁性体層123側から、MC(マシニングセンター)やレーザスクライブ工法により、所定の深さまで個片化用のV字状の切り込み溝160を形成する。次に、マザー基板100を焼成することで、磁性体および非磁性体の焼結と、導体パターンのメッキ処理を行う。これにより、図12に示すような断面形状からなるマザー基板100が形成される。最後に、焼成後のマザー基板100に作業者が手で負荷をかけることにより、マザー基板100を個片に分割する。この際、マザー基板100は、溝140と切り込み溝160とを結ぶように分割される。

【先行技術文献】

【特許文献】

【0009】

【特許文献1】特開2005−57031号公報

【発明の概要】

【発明が解決しようとする課題】

【0010】

しかしながら、従来の工法を用いた場合、分割用のV字溝を表層付近にしか形成されていないようにすると、比較的厚みの薄い基板でないと分割できない。

【0011】

比較的厚みの厚い基板を分割しようとすると、V字状の切り込み溝を磁性体層に達するまで入れなければ分割できないため、焼成時に導体パターンに含まれるAg(銀)等が端面(切り込み溝160による切断面)に浮き出てしまう。このため、その後のメッキ処理においてメッキの析出・成長を行うことによって、層を跨る導体パターン同士が端面で短絡する等の不良が発生する可能性がある。

【0012】

したがって、本発明の目的は、マザー基板からの個片化が容易であり、高品質な積層型インダクタ素子を形成できる積層型インダクタ素子の製造方法を提供することにある。

【課題を解決するための手段】

【0013】

この発明は、次の工程を含む積層型インダクタ素子の製造方法に関する。本願の製造方法では、磁性体シートを含む複数の絶縁性シートに対して導体パターンおよび内部配線パターンを形成する工程と、絶縁性シートおよび磁性体シートよりも線膨張係数の小さい非磁性体シートを用いて、非磁性体シートを備える第1非磁性体層、磁性体シートを備える第1磁性体層、非磁性体シートを備える第2非磁性体層、磁性体シートを備える第2磁性体層、および非磁性体シートを備える第3非磁性体層を順に積層し、導体パターンを接続することでインダクタを形成し、該インダクタ内蔵型の積層体を形成する工程と、を有する。この製造方法では、積層体は、複数のインダクタを含むマザー基板である。この製造方法では、マザー基板の第1非磁性体層の表面に、該第1非磁性体層内に収まる深さからなる溝を、複数のインダクタを区分する境界に沿って、焼成前に形成する工程を有する。この製造方法では、焼成後のマザー基板の第3非磁性体層の表面側から、境界に略沿って所定の押圧力でスクライブ手段を接触させ、部分的なクラックを形成する工程を有する。この製造方法では、クラック形成後のマザー基板に対して外部から応力を加えることにより、個片の積層型インダクタ素子に分割する工程を有する。

【0014】

この製造方法では、マザー基板の焼成後に、第3非磁性体層内では留まらない部分的なクラックが形成される。これにより、マザー基板から複数の積層型インダクタ素子へ、容易に個片化することができる。また、焼成後にスクライブをすることで、導体パターンを構成する金属が焼成時に析出しない。

【0015】

また、この発明の積層型インダクタ素子の製造方法における部分的なクラックを形成する工程は、クラックが第2非磁性体層に達する押圧力でスクライブ手段を接触させることが好ましい。

【0016】

この製造方法では、具体的なスクライブ手段の押圧力について示している。非磁性体層は、磁性体層よりも線膨張係数が小さい。したがって、第2非磁性体層には、これを挟む第1磁性体層および第2磁性体層との線膨張係数の差によって、積層方向に直交する方向に沿った応力が加わった状態で焼結する。このため、積層方向に沿ったクラックは、第2非磁性体層を超えて進行しにくい。したがって、所定の押圧力範囲であれば、部分クラックは、第2非磁性体層に達したところでとまる。これにより、設定可能な押圧力の範囲が広くなり、製造条件を設定しやすく、押圧力のばらつきの影響を受け難い。

【0017】

また、この発明の積層型インダクタ素子の製造方法における積層体を形成する工程では、第1磁性体層と第2非磁性体層との間に、磁性体シートを備える第3磁性体層、非磁性体シートを備える第4非磁性体層を、さらに積層することもできる。

【0018】

このような製造方法を用いれば、押圧力が強すぎて、万が一、クラックが第2非磁性体層を貫いても、第4非磁性体層で止めることできる。

【0019】

この発明の積層型インダクタ素子は、非磁性体を備える第1非磁性体層、磁性体を備える第1磁性体層、非磁性体を備える第2非磁性体層、磁性体を備える第2磁性体層、非磁性体を備える第3非磁性体層の順で積層された積層体を備え、該積層体の内部に導体パターンからなるインダクタが形成されており、積層方向に直交する端面の少なくとも一面は、第2非磁性体層の位置で積層方向に沿って屈曲していることを特徴としている。

【発明の効果】

【0020】

この発明によれば、マザー基板から複数の積層型インダクタ素子へ容易に個片化することができる。また、高品質な積層型インダクタ素子を容易に形成することができる。

【図面の簡単な説明】

【0021】

【図1】本発明の第1の実施形態に係る積層型インダクタ素子の製造工程を示すフローチャートである。

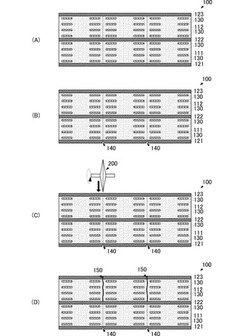

【図2】第1の実施形態に係る積層型インダクタ素子の製造工程別の模式断面図である。

【図3】クラックの形成概念を示すための模式断面図である。

【図4】本実施形態のマザー基板100の構成を用いて押圧力を変化させた場合のクラックの進行を示す模式断面図である。

【図5】他の積層構成を用いて押圧力を変化させた場合のクラックの進行を示す模式断面図である。

【図6】個片化した積層型インダクタ素子10の模式断面図である。

【図7】スクライブ位置と溝140の位置が一致しない場合のクラックの進行の仕方を説明する図である。

【図8】第2非磁性体層122の位置を変化させたマザー基板100Aの模式断面図である。

【図9】中間の非磁性体層を二層も受けたマザー基板100Bの模式断面図である。

【図10】特許文献1に示した積層型チップ素子の製造工程を、磁性体を含む積層型インダクタ素子に適用した場合の製造フローチャートである。

【図11】特許文献1に示した積層型チップ素子の製造工程を、磁性体を含む積層型インダクタ素子に適用した場合の分割前の模式断面図である。

【図12】図11で示した積層型インダクタ素子よりも厚みの厚い、磁性体を含む積層型インダクタ素子を製造する場合の分割前の模式断面図である。

【発明を実施するための形態】

【0022】

本発明の第1の実施形態に係る積層型インダクタ素子の製造方法、および積層型インダクタ素子について、図を参照して説明する。図1は、本発明の第1の実施形態に係る積層型インダクタ素子の製造工程を示すフローチャートである。図2は、第1の実施形態に係る積層型インダクタ素子の製造工程別の模式断面図である。図2(A)は積層工程での断面図である。図2(B)は第1の溝を形成する工程での断面図である。図2(C)、図2(D)はダイヤモンドスクライブを用いて部分的なクラックを形成する工程の断面図であり、図2(C)はクラック形成前を示し、図2(D)はクラック形成状態を示す。図3は、クラックの形成概念を示すための模式断面図である。なお、図2、図3は、積層方向に平行な面を見た断面図である。

【0023】

図1のフローに沿って、本発明の第1の実施形態に係る積層型インダクタ素子の製造方法を説明する。

【0024】

第1非磁性体層121、第1磁性体層111、第2非磁性体層122、第2磁性体層112、および第3非磁性体層123の順で層状化された積層体からなるマザー基板100を形成する(S101)。

【0025】

第1磁性体層111、第2磁性体層112は、それぞれ複数の磁性体シートを積層してなる。磁性体シートは、例えば、ニッケル、亜鉛、および銅を含むフェライトとセラミック材料とを主成分とする硬化されていないシートである。所定の磁性体シートには、Ag等の導電性材料からなる導体パターン130が形成されている。導体パターン130は、積層型インダクタ素子として形成された状態で、積層方向を軸方向とするヘリカル状のコイル(インダクタ)が形成されるような形状で形成されている。また、所定の磁性体シートには、導体パターン130と同様に、Ag等の導電性材料からなる引き回し導体パターン(図示せず)が形成されている。

【0026】

第1非磁性体層121、第2非磁性体層122、および第3非磁性体層123は、非磁性体シートを積層することで実現される。非磁性体シートは、例えば、鉄、亜鉛、および銅を含むフェライトとセラミック材料とを主成分とするものである。非磁性体シートは、磁性体シートよりも線膨張係数が小さくなる組成で形成されている。

【0027】

なお、第1、第2磁性体層111,112の厚み、第1、第2、第3非磁性体層121,122,123の厚みは、積層型インダクタ素子として所望する特性が得られるように、適宜設定されている。

【0028】

また、本工程では、第1非磁性体層121、第1磁性体層111、第2非磁性体層122、第2磁性体層112、および第3非磁性体層123をそれぞれ個別に形成した後に、これらを積層するのではなく、非磁性体シートおよび磁性体シートを順次積層して、第1非磁性体層121、第1磁性体層111、第2非磁性体層122、第2磁性体層112、および第3非磁性体層123からなる層構造を実現している。

【0029】

これにより、図2(A)に示すような焼成前のマザー基板100が形成される。すなわち、積層方向の一方端に第1非磁性体層121があり、他方端に第3非磁性体層123があるマザー基板100が形成される。積層方向の第1非磁性体層121と第3非磁性体層123との間には、第1磁性体層111と第2磁性体層112とがあり、第1磁性体層111と第2磁性体層112との間には第2非磁性体層122がある。

【0030】

次に、マザー基板100の第1非磁性体層121に個片化用の溝140を形成する(S102)。溝140は、最終的に複数のインダクタ素子となる領域を区分する境界に沿って形成されている。溝140は、図2(B)に示すように、第1非磁性体層121内で収まる深さで形成されている。

【0031】

次に、溝140が形成されたマザー基板100を所定の温度プロファイルによって焼成し、磁性体シートおよび非磁性体シートを焼結するとともに、導体パターン130のメッキ処理を行う(S103)。

【0032】

次に、図2(C)に示すように、焼成後のマザー基板100における第3非磁性体層123側の面に、所定の押圧力でダイヤモンドスクライバー200を接触させる。この際、ダイヤモンドスクライバー200は、第1非磁性体層111に形成した溝140と対向する位置に接触させる。これにより、図2(D)に示すように、接触位置から略積層方向に沿ってクラック150が発生する(S104)。このダイヤモンドスクライバー200が本発明の「スクライブ手段」に相当する。なお、このようなクラックを発生できる工法であれば、ダイヤモンドスクライバー200に限ることなく、他の工法を利用してもよい。

【0033】

次に、マザー基板100に対して外部から曲げ応力を加えることで、クラック150と溝140とを結ぶようにマザー基板100が割れる。これにより、マザー基板100は、複数の積層型インダクタ素子に個片化される(S105)。

【0034】

ところで、上述のように、押圧力は、所定の押圧力範囲に設定されている。この押圧力範囲の下限値は、クラック150が第3非磁性体層123を少なくとも貫通する程度(破断強度以上)とする。また、この押圧力範囲は、非磁性体層123の物性、ダイヤモンドスクライバー200の形状等から予め推定することができ、予め実験等で確認することもできる。

【0035】

このように、ダイヤモンドスクライバー200の接触によってマザー基板100に発生したクラック150は、第2磁性体層112を貫通して第2非磁性体層122で止まる。これは、次の理由によるものである。

【0036】

磁性体シートと非磁性体シートとの間には、上述のように線膨張係数の差がある。したがって、第2非磁性体層122は、当該層を挟む第1磁性体層111および第2磁性体層112よりも線膨張係数が小さくなる。したがって、マザー基板100の焼成後には、図3に示すように、第2磁性体層112と第2非磁性体層122との境界面付近では、第2非磁性体層122は、積層方向に直交する方向に沿った引っ張り応力(図3の黒矢印500参照)を受ける。したがって、第2非磁性体層122は、積層方向に沿って進行するクラックに対して強くなり、クラック150は、第2非磁性体層122の第2磁性体層112側の表面までしか進行しない。

【0037】

図4は、本実施形態のマザー基板100の構成を用いて押圧力を変化させた場合のクラックの進行を示す模式断面図である。図4(A)は押圧力P1でダイヤモンドスクライブを行った場合、図4(B)は押圧力P2でダイヤモンドスクライブを行った場合、図4(C)は押圧力P3でダイヤモンドスクライブを行った場合、図4(D)は押圧力P4でダイヤモンドスクライブを行った場合を示す。押圧力P1,P2,P3,P4は、P1<P2<P3<P4の関係である。

【0038】

押圧力P1は低い押圧力であり、クラック150P1は第3非磁性体層123を貫通しない。

【0039】

押圧力P2は押圧力P1よりも高く、第3非磁性体層123の積層方向の破断強度の上限値よりも高い。この場合、クラック150P2は第3非磁性体層123を貫通し、第2磁性体層112に達する。第2磁性体層112は、焼結時の応力によって、積層方向にクラックが入りやすい。したがって、押圧力P2により、第2磁性体層112に達したクラック150P2は第2磁性体層112を貫通し、第2非磁性体層122の表面まで達する。

【0040】

押圧力P3は押圧力P2よりも高い。しかしながら、上述のように、第2非磁性体層122は、積層方向のクラックに強いため、積層方向の破断強度の上限値となる押圧力P3までは、第2非磁性体層122内にクラックが進行しない。したがって、押圧力P3によるクラック150P3は、第2非磁性体層122の表面に留まり、第2非磁性体層122内まで進行しない。

【0041】

押圧力P4は押圧力P3よりも高い。そして、この押圧力P4は、第2非磁性体層212の積層方向の破断強度の上限値よりも高い。この場合、クラック150P4は第2非磁性体層122を貫通し、第1磁性体層111に達する。第1磁性体層111は、焼結時の応力によって、積層方向にクラックが入りやすい。したがって、押圧力P4により、第1磁性体層111に達したクラック150P4は第1磁性体層111を貫通し、第1非磁性体層121の表面まで達する。

【0042】

このように、本実施形態の積層構造であれば、押圧力P2から押圧力P3までの押圧力範囲に設定することで、クラックの進行を、マザー基板100(積層体)の中間の第2非磁性体層122までにすることができる。すなわち、第3非磁性体層123の破断強度を超える押圧力以上であって、第2非磁性体層122の破断強度と第3非磁性体層123の破断強度とを合わせた破断強度、より正確には第2非磁性体層122の破断強度と第2磁性体層112の破断強度と第3非磁性体層123の破断強度とをあわせた破断強度未満とすればよい。

【0043】

このような押圧力範囲は、第2非磁性体層122が上述のように積層方向に沿ったクラックに対して強いため、広い押圧力範囲に設定することができる。これにより、押圧力の設定範囲を広く取ることができ、押圧力の設定が容易になる。また、この押圧力範囲であれば、クラックを第2非磁性体層122までとすることができ、所望とする深さのクラックを安定して形成することができる。

【0044】

しかしながら、本願発明の構成を用いない場合には、本願発明のように積層方向の途中でクラックの進行を留めることは容易ではない。言い換えれば、積層方向の途中の所望とする位置まで安定してクラックを形成することができない。図5は、他の積層構成を用いて押圧力を変化させた場合のクラックの進行を示す模式断面図である。図5(A)〜図5(D)は磁性体層111Xの積層方向の両面にそれぞれ第1非磁性体層121、第3非磁性体層123が形成されたマザー基板100Xの場合を示す。すなわち、本発明の構成に対して、積層方向の中間の非磁性体層が無い場合を示す。図5(E)〜図5(H)は磁性体層111Yのみから形成されたマザー基板100Yの場合を示す。すなわち、本発明の構成に対して、非磁性体層が無い場合を示す。

【0045】

図5(A)〜図5(D)に示すように、中間の非磁性体層が無い場合、第3非磁性体層123を貫通する押圧力P2,P3,P4であれば、いずれの場合でも、クラック150P2,150P3,150P4は、磁性体層111Xを貫通し、第1非磁性体層121まで到達してしまう。すなわち、押圧力P2以上であれば、略分割された状態となってしまう。この場合、クラックの進行方向が不安定になり、きれいな断面が形成できない可能性が高くなる。

【0046】

図5(E)〜図5(H)に示すように、非磁性体層が無い場合、押圧力P1,P2,P3,P4に応じてクラック150P1,150P2,150P3,150P4の進行距離は長くなる。しかしながら、磁性体層は積層方向へのクラックに対する強度が高くないため、押圧力とクラックの進行距離とを正確に一致させることができない。すなわち、所望とする深さのクラックを安定して形成することが容易ではない。

【0047】

このように製造した積層型インダクタ素子は、図6は、個片化した積層型インダクタ素子10の模式断面図である。図6に示すように、本実施形態の製造方法を用いれば、積層型インダクタ素子10の側面、すなわち上述の方法で分割した面は、第3非磁性体層123、第2磁性体層112、および第2非磁性体層122に亘る間の壁面162が、クラック150によって形成される。また、第2非磁性体層122、第1磁性体層111、および第1非磁性体層121に亘る間の壁面161が、外部から曲げ応力による分割工程によって形成される。これらは、外部からの応力によって割れるものであり、フェライトの粒子間の結合が分離されて生じる割れである。したがって、ダイヤモンドスクライブによって粒界を無視して強制的に切断する工法よりも、分割面はあれにくく、表面の形状、品質も良好となる。したがって、きれいに分割された面となり、外形形状も品質も良好な積層型インダクタ素子となる。

【0048】

また、ダイヤモンドスクライバー200によってクラック150を発生させる工程を、マザー基板100の焼成後に行うことで、従来の第2の工法のように、導体パターンに含まれるAg(銀)等が端面に浮き出すことがない。これにより、異なる層に形成された導体パターン間の不要な短絡を防止できる。

【0049】

また、クラック150が積層方向の中間位置まで進行していることで、分割工程において、マザー基板100を容易に分割することができる。外部からの曲げ応力によって予期しない形状で分割されることを抑制することができる。

【0050】

なお、製造ばらつきにより、ダイヤモンドスクライバー200を第3非磁性体層123の表面に接触させる位置(スクライブ位置)と、溝140の位置とが、マザー基板100を平面視して(積層方向に沿って見て)、一致しない場合がある。図7(A),(B)は、スクライブ位置と溝140の位置が一致しない場合のクラックの進行の仕方を説明する図である。図7(A),(B)に示すように、第3非磁性体層123、第2磁性体層112に生じるクラック151,153は、スクライブ位置から積層方向に沿って略真っ直ぐに進行する。このため、クラック151,153の第2非磁性体層122側の端点の位置は、マザー基板100を平面視して(積層方向に沿って見て)、溝140の位置と一致しない。

【0051】

このような状態でマザー基板100を分割すると、分割によるクラック152は、クラック151の第2非磁性体層122側の端点から、溝140に向かって進行する。同様に、分割によるクラック154は、クラック153の第2非磁性体層122側の端点から、溝140に向かって進行する。すなわち、積層型インダクタ素子の端面(分割面)は、第2非磁性体層122を境界にして屈曲する構造となる。しかしながら、本発明の製造方法を用いることで、フェライトの粒界は破壊されないので、きれいな断面を得ることできる。このように、第2非磁性体層122を境界に端面が屈曲する形状は、上述の製造方法を用いることで特徴的に現れるものであり、逆に第2非磁性体層122を境界に端面が屈曲する積層型インダクタ素子であれば、上述の製造方法で製造したものと推定でき、上述の製造方法で得られる積層型インダクタ素子としての利点を有することができる。

【0052】

上述の説明では、第2非磁性体層122が積層方向の略中央にある場合を示した。しかしながら、第2非磁性体層122の位置は、必要とするクラックの深さに応じて適宜設定すればよい。図8は、第2非磁性体層122の位置を変化させたマザー基板100Aの模式断面図である。マザー基板100Aは、上述のマザー基板100に対して第1磁性体層111Aが厚く、第2磁性体層112Aが薄くなっている。このような構成では、上述のようにダイヤモンドスクライバー200の押圧力を第2、第3非磁性体層122,123の破断強度に応じて設定することで、クラック150Aを、マザー基板100のクラック150よりも浅くすることができる。すなわち、積層方向の中間にある非磁性体層の位置を変化させることで、ダイヤモンドスクライバー200によるクラックの深さを可変することができる。なお、このように積層方向の中間にある非磁性体層の位置を変化させたとしても、積層型インダクタ素子の電気的特性には殆ど変化がないことは、発明者によって実験的確認している。

【0053】

これにより、積層型インダクタ素子としての特性を変化させることなく、マザー基板の厚みに応じた適正な位置(分割しやすく、きれいに個片化できる位置)までクラックを進行させるようにすることができる。

【0054】

また、上述の説明では、中間の非磁性体層を一層だけ設けた場合を示したが、二層以上設けてもよい。図9は中間の非磁性体層を二層も受けたマザー基板100Bの模式断面図である。

【0055】

マザー基板100Bは、第1非磁性体層121、第1磁性体層111B、第4非磁性体層122B2、第3磁性体層113B、第2非磁性体層122B1、第2磁性体層112B、第3非磁性体層123の順に積層された積層体からなる。第1磁性体層111B、第2磁性体層112B、第3磁性体層113Bには、インダクタとなる導体パターンが形成されている。

【0056】

この状態において、ダイヤモンドスクライバー200の押圧力を第2非磁性体層122B1に到達する程度に設定する。この場合、殆どのクラックは、図9のクラック150B1に示すように、第2非磁性体層122B1の表面で進行が停止する。ここで、例えば、製造ばらつき等によって押圧力が強くなった場合に、図9のクラック150B2に示すように、第2非磁性体層122B1を貫通することがある。しかしながら、第3非磁性体層122B2を設けておくことで、クラック150B2の進行を第3非磁性体層122B2の表面で停止させることができる。すなわち、所定の押圧力範囲であれば、クラックが積層方向の全長に亘って進行することを防止できる。

【0057】

これにより、より確実にクラックの進行を積層方向の中間位置までにすることができる。

【符号の説明】

【0058】

10:積層型インダクタ素子、

100,100A,100B:マザー基板、

111,111A,111B:第1磁性体層、

112,112A,112B:第2磁性体層、

113B:第3磁性体層、

121:第1非磁性体層、

122,122B1:第2非磁性体層、

123:第3非磁性体層、

122B2:第4非磁性体層、

130:導体パターン、

140,141:溝、

150,150A,150B1,150B2,151,152,153,154:クラック、

160:切り込み溝、

200:ダイヤモンドスクライバー

【技術分野】

【0001】

この発明は、磁性体を含む積層体内にコイル導体のパターンが形成された積層インダクタ素子の製造方法、および当該製造方法で製造される積層インダクタ素子に関するものである。

【背景技術】

【0002】

従来、積層型チップ素子を製造する際には、最終的に複数の積層型チップ素子を配列されるマザー基板の状態で機能部となる積層部を形成する。そして、マザー基板を素子単位で分割することで、個別の積層型チップ素子を製造している。

【0003】

磁性体を用いない積層セラミックコンデンサ等の従来の一般的な積層型チップ素子の場合、マザー基板から各積層型チップ素子を分割する際には、例えば特許文献1に示すように、マザー基板における分割すべき位置にブレイク用の溝を形成する。ブレイク用の溝は、マザー基板の表面から比較的浅く(表層付近だけ)形成されている。

【0004】

このような誘電体を用いた積層型チップ素子とは別に、現在、インダクタンスの大きなパワーインダクタ用として、磁性体を含む積層体からなる積層型インダクタ素子が多く利用されている。

【0005】

図10は、特許文献1に示した積層型チップ素子の製造工程を、磁性体を含む積層型インダクタ素子に適用した場合の製造フローチャートである。この工法を、従来の工法とする。図11は、特許文献1に示した積層型チップ素子の製造工程を、磁性体を含む積層型インダクタ素子に適用した場合の分割前の断面図である。

【0006】

図10に示すように、従来の工法では、まず第1非磁性体層121、第1磁性体層111,第2非磁性体層122、第2磁性体層112、および第3非磁性体層123をこの順で積層して、焼成前のマザー基板100を形成する(S901)。第1磁性体層111、第2磁性体層112には、ペースト状の導体パターン130が形成されている。次に、マザー基板100の第1非磁性体層121側の表面および第3非磁性体層123側の表面に、個片化用の溝140、141を形成する(S902)。この際、溝140、141は、第1非磁性体層121内および第3非磁性体層123内に止まる深さで形成されている。次に、マザー基板100を焼成することで、磁性体および非磁性体の焼結と、導体パターンのメッキ処理を行う(S903)。これにより、図11に示すような断面形状からなるマザー基板100が形成される。溝141はV字状に形成されており、最後に、焼成後のマザー基板100に作業者が手で負荷をかけることにより、溝141に沿ってマザー基板100を個片に分割する(S904)。これにより、個片化された積層型インダクタ素子の筐体が完成する。そして、筐体の所定位置に外部電極を形成することで、積層型インダクタ素子が実現される。

【0007】

図12は、図11で示した積層型インダクタ素子よりも厚みの厚い、磁性体を含む積層型インダクタ素子を製造する場合の分割前の断面図である。

【0008】

厚みの厚い積層型インダクタ素子を製造する場合では、まず第1非磁性体層121、第1磁性体層111,第2非磁性体層122、第2磁性体層112、および第3非磁性体層123をこの順で積層して、焼成前のマザー基板100を形成する。第1磁性体層111、第2磁性体層112には、導体パターン130が形成されている。次に、マザー基板100の第1非磁性体層121側の表面のみに、個片化用の溝140を形成する。この際、溝140は、第1非磁性体層121内および第3非磁性体層123内に止まる深さで形成されている。次に、マザー基板100の第3非磁性体層123側から、MC(マシニングセンター)やレーザスクライブ工法により、所定の深さまで個片化用のV字状の切り込み溝160を形成する。次に、マザー基板100を焼成することで、磁性体および非磁性体の焼結と、導体パターンのメッキ処理を行う。これにより、図12に示すような断面形状からなるマザー基板100が形成される。最後に、焼成後のマザー基板100に作業者が手で負荷をかけることにより、マザー基板100を個片に分割する。この際、マザー基板100は、溝140と切り込み溝160とを結ぶように分割される。

【先行技術文献】

【特許文献】

【0009】

【特許文献1】特開2005−57031号公報

【発明の概要】

【発明が解決しようとする課題】

【0010】

しかしながら、従来の工法を用いた場合、分割用のV字溝を表層付近にしか形成されていないようにすると、比較的厚みの薄い基板でないと分割できない。

【0011】

比較的厚みの厚い基板を分割しようとすると、V字状の切り込み溝を磁性体層に達するまで入れなければ分割できないため、焼成時に導体パターンに含まれるAg(銀)等が端面(切り込み溝160による切断面)に浮き出てしまう。このため、その後のメッキ処理においてメッキの析出・成長を行うことによって、層を跨る導体パターン同士が端面で短絡する等の不良が発生する可能性がある。

【0012】

したがって、本発明の目的は、マザー基板からの個片化が容易であり、高品質な積層型インダクタ素子を形成できる積層型インダクタ素子の製造方法を提供することにある。

【課題を解決するための手段】

【0013】

この発明は、次の工程を含む積層型インダクタ素子の製造方法に関する。本願の製造方法では、磁性体シートを含む複数の絶縁性シートに対して導体パターンおよび内部配線パターンを形成する工程と、絶縁性シートおよび磁性体シートよりも線膨張係数の小さい非磁性体シートを用いて、非磁性体シートを備える第1非磁性体層、磁性体シートを備える第1磁性体層、非磁性体シートを備える第2非磁性体層、磁性体シートを備える第2磁性体層、および非磁性体シートを備える第3非磁性体層を順に積層し、導体パターンを接続することでインダクタを形成し、該インダクタ内蔵型の積層体を形成する工程と、を有する。この製造方法では、積層体は、複数のインダクタを含むマザー基板である。この製造方法では、マザー基板の第1非磁性体層の表面に、該第1非磁性体層内に収まる深さからなる溝を、複数のインダクタを区分する境界に沿って、焼成前に形成する工程を有する。この製造方法では、焼成後のマザー基板の第3非磁性体層の表面側から、境界に略沿って所定の押圧力でスクライブ手段を接触させ、部分的なクラックを形成する工程を有する。この製造方法では、クラック形成後のマザー基板に対して外部から応力を加えることにより、個片の積層型インダクタ素子に分割する工程を有する。

【0014】

この製造方法では、マザー基板の焼成後に、第3非磁性体層内では留まらない部分的なクラックが形成される。これにより、マザー基板から複数の積層型インダクタ素子へ、容易に個片化することができる。また、焼成後にスクライブをすることで、導体パターンを構成する金属が焼成時に析出しない。

【0015】

また、この発明の積層型インダクタ素子の製造方法における部分的なクラックを形成する工程は、クラックが第2非磁性体層に達する押圧力でスクライブ手段を接触させることが好ましい。

【0016】

この製造方法では、具体的なスクライブ手段の押圧力について示している。非磁性体層は、磁性体層よりも線膨張係数が小さい。したがって、第2非磁性体層には、これを挟む第1磁性体層および第2磁性体層との線膨張係数の差によって、積層方向に直交する方向に沿った応力が加わった状態で焼結する。このため、積層方向に沿ったクラックは、第2非磁性体層を超えて進行しにくい。したがって、所定の押圧力範囲であれば、部分クラックは、第2非磁性体層に達したところでとまる。これにより、設定可能な押圧力の範囲が広くなり、製造条件を設定しやすく、押圧力のばらつきの影響を受け難い。

【0017】

また、この発明の積層型インダクタ素子の製造方法における積層体を形成する工程では、第1磁性体層と第2非磁性体層との間に、磁性体シートを備える第3磁性体層、非磁性体シートを備える第4非磁性体層を、さらに積層することもできる。

【0018】

このような製造方法を用いれば、押圧力が強すぎて、万が一、クラックが第2非磁性体層を貫いても、第4非磁性体層で止めることできる。

【0019】

この発明の積層型インダクタ素子は、非磁性体を備える第1非磁性体層、磁性体を備える第1磁性体層、非磁性体を備える第2非磁性体層、磁性体を備える第2磁性体層、非磁性体を備える第3非磁性体層の順で積層された積層体を備え、該積層体の内部に導体パターンからなるインダクタが形成されており、積層方向に直交する端面の少なくとも一面は、第2非磁性体層の位置で積層方向に沿って屈曲していることを特徴としている。

【発明の効果】

【0020】

この発明によれば、マザー基板から複数の積層型インダクタ素子へ容易に個片化することができる。また、高品質な積層型インダクタ素子を容易に形成することができる。

【図面の簡単な説明】

【0021】

【図1】本発明の第1の実施形態に係る積層型インダクタ素子の製造工程を示すフローチャートである。

【図2】第1の実施形態に係る積層型インダクタ素子の製造工程別の模式断面図である。

【図3】クラックの形成概念を示すための模式断面図である。

【図4】本実施形態のマザー基板100の構成を用いて押圧力を変化させた場合のクラックの進行を示す模式断面図である。

【図5】他の積層構成を用いて押圧力を変化させた場合のクラックの進行を示す模式断面図である。

【図6】個片化した積層型インダクタ素子10の模式断面図である。

【図7】スクライブ位置と溝140の位置が一致しない場合のクラックの進行の仕方を説明する図である。

【図8】第2非磁性体層122の位置を変化させたマザー基板100Aの模式断面図である。

【図9】中間の非磁性体層を二層も受けたマザー基板100Bの模式断面図である。

【図10】特許文献1に示した積層型チップ素子の製造工程を、磁性体を含む積層型インダクタ素子に適用した場合の製造フローチャートである。

【図11】特許文献1に示した積層型チップ素子の製造工程を、磁性体を含む積層型インダクタ素子に適用した場合の分割前の模式断面図である。

【図12】図11で示した積層型インダクタ素子よりも厚みの厚い、磁性体を含む積層型インダクタ素子を製造する場合の分割前の模式断面図である。

【発明を実施するための形態】

【0022】

本発明の第1の実施形態に係る積層型インダクタ素子の製造方法、および積層型インダクタ素子について、図を参照して説明する。図1は、本発明の第1の実施形態に係る積層型インダクタ素子の製造工程を示すフローチャートである。図2は、第1の実施形態に係る積層型インダクタ素子の製造工程別の模式断面図である。図2(A)は積層工程での断面図である。図2(B)は第1の溝を形成する工程での断面図である。図2(C)、図2(D)はダイヤモンドスクライブを用いて部分的なクラックを形成する工程の断面図であり、図2(C)はクラック形成前を示し、図2(D)はクラック形成状態を示す。図3は、クラックの形成概念を示すための模式断面図である。なお、図2、図3は、積層方向に平行な面を見た断面図である。

【0023】

図1のフローに沿って、本発明の第1の実施形態に係る積層型インダクタ素子の製造方法を説明する。

【0024】

第1非磁性体層121、第1磁性体層111、第2非磁性体層122、第2磁性体層112、および第3非磁性体層123の順で層状化された積層体からなるマザー基板100を形成する(S101)。

【0025】

第1磁性体層111、第2磁性体層112は、それぞれ複数の磁性体シートを積層してなる。磁性体シートは、例えば、ニッケル、亜鉛、および銅を含むフェライトとセラミック材料とを主成分とする硬化されていないシートである。所定の磁性体シートには、Ag等の導電性材料からなる導体パターン130が形成されている。導体パターン130は、積層型インダクタ素子として形成された状態で、積層方向を軸方向とするヘリカル状のコイル(インダクタ)が形成されるような形状で形成されている。また、所定の磁性体シートには、導体パターン130と同様に、Ag等の導電性材料からなる引き回し導体パターン(図示せず)が形成されている。

【0026】

第1非磁性体層121、第2非磁性体層122、および第3非磁性体層123は、非磁性体シートを積層することで実現される。非磁性体シートは、例えば、鉄、亜鉛、および銅を含むフェライトとセラミック材料とを主成分とするものである。非磁性体シートは、磁性体シートよりも線膨張係数が小さくなる組成で形成されている。

【0027】

なお、第1、第2磁性体層111,112の厚み、第1、第2、第3非磁性体層121,122,123の厚みは、積層型インダクタ素子として所望する特性が得られるように、適宜設定されている。

【0028】

また、本工程では、第1非磁性体層121、第1磁性体層111、第2非磁性体層122、第2磁性体層112、および第3非磁性体層123をそれぞれ個別に形成した後に、これらを積層するのではなく、非磁性体シートおよび磁性体シートを順次積層して、第1非磁性体層121、第1磁性体層111、第2非磁性体層122、第2磁性体層112、および第3非磁性体層123からなる層構造を実現している。

【0029】

これにより、図2(A)に示すような焼成前のマザー基板100が形成される。すなわち、積層方向の一方端に第1非磁性体層121があり、他方端に第3非磁性体層123があるマザー基板100が形成される。積層方向の第1非磁性体層121と第3非磁性体層123との間には、第1磁性体層111と第2磁性体層112とがあり、第1磁性体層111と第2磁性体層112との間には第2非磁性体層122がある。

【0030】

次に、マザー基板100の第1非磁性体層121に個片化用の溝140を形成する(S102)。溝140は、最終的に複数のインダクタ素子となる領域を区分する境界に沿って形成されている。溝140は、図2(B)に示すように、第1非磁性体層121内で収まる深さで形成されている。

【0031】

次に、溝140が形成されたマザー基板100を所定の温度プロファイルによって焼成し、磁性体シートおよび非磁性体シートを焼結するとともに、導体パターン130のメッキ処理を行う(S103)。

【0032】

次に、図2(C)に示すように、焼成後のマザー基板100における第3非磁性体層123側の面に、所定の押圧力でダイヤモンドスクライバー200を接触させる。この際、ダイヤモンドスクライバー200は、第1非磁性体層111に形成した溝140と対向する位置に接触させる。これにより、図2(D)に示すように、接触位置から略積層方向に沿ってクラック150が発生する(S104)。このダイヤモンドスクライバー200が本発明の「スクライブ手段」に相当する。なお、このようなクラックを発生できる工法であれば、ダイヤモンドスクライバー200に限ることなく、他の工法を利用してもよい。

【0033】

次に、マザー基板100に対して外部から曲げ応力を加えることで、クラック150と溝140とを結ぶようにマザー基板100が割れる。これにより、マザー基板100は、複数の積層型インダクタ素子に個片化される(S105)。

【0034】

ところで、上述のように、押圧力は、所定の押圧力範囲に設定されている。この押圧力範囲の下限値は、クラック150が第3非磁性体層123を少なくとも貫通する程度(破断強度以上)とする。また、この押圧力範囲は、非磁性体層123の物性、ダイヤモンドスクライバー200の形状等から予め推定することができ、予め実験等で確認することもできる。

【0035】

このように、ダイヤモンドスクライバー200の接触によってマザー基板100に発生したクラック150は、第2磁性体層112を貫通して第2非磁性体層122で止まる。これは、次の理由によるものである。

【0036】

磁性体シートと非磁性体シートとの間には、上述のように線膨張係数の差がある。したがって、第2非磁性体層122は、当該層を挟む第1磁性体層111および第2磁性体層112よりも線膨張係数が小さくなる。したがって、マザー基板100の焼成後には、図3に示すように、第2磁性体層112と第2非磁性体層122との境界面付近では、第2非磁性体層122は、積層方向に直交する方向に沿った引っ張り応力(図3の黒矢印500参照)を受ける。したがって、第2非磁性体層122は、積層方向に沿って進行するクラックに対して強くなり、クラック150は、第2非磁性体層122の第2磁性体層112側の表面までしか進行しない。

【0037】

図4は、本実施形態のマザー基板100の構成を用いて押圧力を変化させた場合のクラックの進行を示す模式断面図である。図4(A)は押圧力P1でダイヤモンドスクライブを行った場合、図4(B)は押圧力P2でダイヤモンドスクライブを行った場合、図4(C)は押圧力P3でダイヤモンドスクライブを行った場合、図4(D)は押圧力P4でダイヤモンドスクライブを行った場合を示す。押圧力P1,P2,P3,P4は、P1<P2<P3<P4の関係である。

【0038】

押圧力P1は低い押圧力であり、クラック150P1は第3非磁性体層123を貫通しない。

【0039】

押圧力P2は押圧力P1よりも高く、第3非磁性体層123の積層方向の破断強度の上限値よりも高い。この場合、クラック150P2は第3非磁性体層123を貫通し、第2磁性体層112に達する。第2磁性体層112は、焼結時の応力によって、積層方向にクラックが入りやすい。したがって、押圧力P2により、第2磁性体層112に達したクラック150P2は第2磁性体層112を貫通し、第2非磁性体層122の表面まで達する。

【0040】

押圧力P3は押圧力P2よりも高い。しかしながら、上述のように、第2非磁性体層122は、積層方向のクラックに強いため、積層方向の破断強度の上限値となる押圧力P3までは、第2非磁性体層122内にクラックが進行しない。したがって、押圧力P3によるクラック150P3は、第2非磁性体層122の表面に留まり、第2非磁性体層122内まで進行しない。

【0041】

押圧力P4は押圧力P3よりも高い。そして、この押圧力P4は、第2非磁性体層212の積層方向の破断強度の上限値よりも高い。この場合、クラック150P4は第2非磁性体層122を貫通し、第1磁性体層111に達する。第1磁性体層111は、焼結時の応力によって、積層方向にクラックが入りやすい。したがって、押圧力P4により、第1磁性体層111に達したクラック150P4は第1磁性体層111を貫通し、第1非磁性体層121の表面まで達する。

【0042】

このように、本実施形態の積層構造であれば、押圧力P2から押圧力P3までの押圧力範囲に設定することで、クラックの進行を、マザー基板100(積層体)の中間の第2非磁性体層122までにすることができる。すなわち、第3非磁性体層123の破断強度を超える押圧力以上であって、第2非磁性体層122の破断強度と第3非磁性体層123の破断強度とを合わせた破断強度、より正確には第2非磁性体層122の破断強度と第2磁性体層112の破断強度と第3非磁性体層123の破断強度とをあわせた破断強度未満とすればよい。

【0043】

このような押圧力範囲は、第2非磁性体層122が上述のように積層方向に沿ったクラックに対して強いため、広い押圧力範囲に設定することができる。これにより、押圧力の設定範囲を広く取ることができ、押圧力の設定が容易になる。また、この押圧力範囲であれば、クラックを第2非磁性体層122までとすることができ、所望とする深さのクラックを安定して形成することができる。

【0044】

しかしながら、本願発明の構成を用いない場合には、本願発明のように積層方向の途中でクラックの進行を留めることは容易ではない。言い換えれば、積層方向の途中の所望とする位置まで安定してクラックを形成することができない。図5は、他の積層構成を用いて押圧力を変化させた場合のクラックの進行を示す模式断面図である。図5(A)〜図5(D)は磁性体層111Xの積層方向の両面にそれぞれ第1非磁性体層121、第3非磁性体層123が形成されたマザー基板100Xの場合を示す。すなわち、本発明の構成に対して、積層方向の中間の非磁性体層が無い場合を示す。図5(E)〜図5(H)は磁性体層111Yのみから形成されたマザー基板100Yの場合を示す。すなわち、本発明の構成に対して、非磁性体層が無い場合を示す。

【0045】

図5(A)〜図5(D)に示すように、中間の非磁性体層が無い場合、第3非磁性体層123を貫通する押圧力P2,P3,P4であれば、いずれの場合でも、クラック150P2,150P3,150P4は、磁性体層111Xを貫通し、第1非磁性体層121まで到達してしまう。すなわち、押圧力P2以上であれば、略分割された状態となってしまう。この場合、クラックの進行方向が不安定になり、きれいな断面が形成できない可能性が高くなる。

【0046】

図5(E)〜図5(H)に示すように、非磁性体層が無い場合、押圧力P1,P2,P3,P4に応じてクラック150P1,150P2,150P3,150P4の進行距離は長くなる。しかしながら、磁性体層は積層方向へのクラックに対する強度が高くないため、押圧力とクラックの進行距離とを正確に一致させることができない。すなわち、所望とする深さのクラックを安定して形成することが容易ではない。

【0047】

このように製造した積層型インダクタ素子は、図6は、個片化した積層型インダクタ素子10の模式断面図である。図6に示すように、本実施形態の製造方法を用いれば、積層型インダクタ素子10の側面、すなわち上述の方法で分割した面は、第3非磁性体層123、第2磁性体層112、および第2非磁性体層122に亘る間の壁面162が、クラック150によって形成される。また、第2非磁性体層122、第1磁性体層111、および第1非磁性体層121に亘る間の壁面161が、外部から曲げ応力による分割工程によって形成される。これらは、外部からの応力によって割れるものであり、フェライトの粒子間の結合が分離されて生じる割れである。したがって、ダイヤモンドスクライブによって粒界を無視して強制的に切断する工法よりも、分割面はあれにくく、表面の形状、品質も良好となる。したがって、きれいに分割された面となり、外形形状も品質も良好な積層型インダクタ素子となる。

【0048】

また、ダイヤモンドスクライバー200によってクラック150を発生させる工程を、マザー基板100の焼成後に行うことで、従来の第2の工法のように、導体パターンに含まれるAg(銀)等が端面に浮き出すことがない。これにより、異なる層に形成された導体パターン間の不要な短絡を防止できる。

【0049】

また、クラック150が積層方向の中間位置まで進行していることで、分割工程において、マザー基板100を容易に分割することができる。外部からの曲げ応力によって予期しない形状で分割されることを抑制することができる。

【0050】

なお、製造ばらつきにより、ダイヤモンドスクライバー200を第3非磁性体層123の表面に接触させる位置(スクライブ位置)と、溝140の位置とが、マザー基板100を平面視して(積層方向に沿って見て)、一致しない場合がある。図7(A),(B)は、スクライブ位置と溝140の位置が一致しない場合のクラックの進行の仕方を説明する図である。図7(A),(B)に示すように、第3非磁性体層123、第2磁性体層112に生じるクラック151,153は、スクライブ位置から積層方向に沿って略真っ直ぐに進行する。このため、クラック151,153の第2非磁性体層122側の端点の位置は、マザー基板100を平面視して(積層方向に沿って見て)、溝140の位置と一致しない。

【0051】

このような状態でマザー基板100を分割すると、分割によるクラック152は、クラック151の第2非磁性体層122側の端点から、溝140に向かって進行する。同様に、分割によるクラック154は、クラック153の第2非磁性体層122側の端点から、溝140に向かって進行する。すなわち、積層型インダクタ素子の端面(分割面)は、第2非磁性体層122を境界にして屈曲する構造となる。しかしながら、本発明の製造方法を用いることで、フェライトの粒界は破壊されないので、きれいな断面を得ることできる。このように、第2非磁性体層122を境界に端面が屈曲する形状は、上述の製造方法を用いることで特徴的に現れるものであり、逆に第2非磁性体層122を境界に端面が屈曲する積層型インダクタ素子であれば、上述の製造方法で製造したものと推定でき、上述の製造方法で得られる積層型インダクタ素子としての利点を有することができる。

【0052】

上述の説明では、第2非磁性体層122が積層方向の略中央にある場合を示した。しかしながら、第2非磁性体層122の位置は、必要とするクラックの深さに応じて適宜設定すればよい。図8は、第2非磁性体層122の位置を変化させたマザー基板100Aの模式断面図である。マザー基板100Aは、上述のマザー基板100に対して第1磁性体層111Aが厚く、第2磁性体層112Aが薄くなっている。このような構成では、上述のようにダイヤモンドスクライバー200の押圧力を第2、第3非磁性体層122,123の破断強度に応じて設定することで、クラック150Aを、マザー基板100のクラック150よりも浅くすることができる。すなわち、積層方向の中間にある非磁性体層の位置を変化させることで、ダイヤモンドスクライバー200によるクラックの深さを可変することができる。なお、このように積層方向の中間にある非磁性体層の位置を変化させたとしても、積層型インダクタ素子の電気的特性には殆ど変化がないことは、発明者によって実験的確認している。

【0053】

これにより、積層型インダクタ素子としての特性を変化させることなく、マザー基板の厚みに応じた適正な位置(分割しやすく、きれいに個片化できる位置)までクラックを進行させるようにすることができる。

【0054】

また、上述の説明では、中間の非磁性体層を一層だけ設けた場合を示したが、二層以上設けてもよい。図9は中間の非磁性体層を二層も受けたマザー基板100Bの模式断面図である。

【0055】

マザー基板100Bは、第1非磁性体層121、第1磁性体層111B、第4非磁性体層122B2、第3磁性体層113B、第2非磁性体層122B1、第2磁性体層112B、第3非磁性体層123の順に積層された積層体からなる。第1磁性体層111B、第2磁性体層112B、第3磁性体層113Bには、インダクタとなる導体パターンが形成されている。

【0056】

この状態において、ダイヤモンドスクライバー200の押圧力を第2非磁性体層122B1に到達する程度に設定する。この場合、殆どのクラックは、図9のクラック150B1に示すように、第2非磁性体層122B1の表面で進行が停止する。ここで、例えば、製造ばらつき等によって押圧力が強くなった場合に、図9のクラック150B2に示すように、第2非磁性体層122B1を貫通することがある。しかしながら、第3非磁性体層122B2を設けておくことで、クラック150B2の進行を第3非磁性体層122B2の表面で停止させることができる。すなわち、所定の押圧力範囲であれば、クラックが積層方向の全長に亘って進行することを防止できる。

【0057】

これにより、より確実にクラックの進行を積層方向の中間位置までにすることができる。

【符号の説明】

【0058】

10:積層型インダクタ素子、

100,100A,100B:マザー基板、

111,111A,111B:第1磁性体層、

112,112A,112B:第2磁性体層、

113B:第3磁性体層、

121:第1非磁性体層、

122,122B1:第2非磁性体層、

123:第3非磁性体層、

122B2:第4非磁性体層、

130:導体パターン、

140,141:溝、

150,150A,150B1,150B2,151,152,153,154:クラック、

160:切り込み溝、

200:ダイヤモンドスクライバー

【特許請求の範囲】

【請求項1】

磁性体シートを含む複数の絶縁性シートに対して導体パターンおよび内部配線パターンを形成する工程と、

前記絶縁性シートと、前記磁性体シートよりも線膨張係数の小さい非磁性体シートとを用いて、前記非磁性体シートを備える第1非磁性体層、前記磁性体シートを備える第1磁性体層、前記非磁性体シートを備える第2非磁性体層、前記磁性体シートを備える第2磁性体層、および前記非磁性体シートを備える第3非磁性体層を順に積層し、前記導体パターンを接続することでインダクタを形成し、該インダクタ内蔵型の積層体を形成する工程と、を有する積層型インダクタ素子の製造方法であって、

前記積層体は、複数のインダクタが配列されたマザー基板であり、

前記マザー基板の前記第1非磁性体層の表面に、該第1非磁性体層内に収まる深さからなる溝を、前記複数のインダクタを区分する境界に沿って、焼成前に形成する工程と、

焼成後の前記マザー基板の前記第3非磁性体層の表面側から、前記境界に略沿って所定の押圧力でスクライブ手段を接触させ、部分的なクラックを形成する工程と、

クラック形成後の前記マザー基板に対して外部から応力を加えることにより、個片の積層型インダクタ素子に分割する工程と、を有することを特徴とする積層型インダクタ素子の製造方法。

【請求項2】

前記部分的なクラックを形成する工程は、前記クラックが前記第2非磁性体層に達する押圧力で前記スクライブ手段を接触させている、請求項1に記載の積層型インダクタ素子の製造方法。

【請求項3】

前記積層体を形成する工程は、

前記第1磁性体層と前記第2非磁性体層との間に、前記磁性体シートを備える第3磁性体層、前記非磁性体シートを備える第4非磁性体層を、さらに積層する、請求項1または請求項2に記載の積層型インダクタ素子の製造方法。

【請求項4】

非磁性体を備える第1非磁性体層、磁性体を備える第1磁性体層、非磁性体を備える第2非磁性体層、磁性体を備える第2磁性体層、非磁性体を備える第3非磁性体層の順で積層された積層体を備え、該積層体の内部に導体パターンからなるインダクタが形成された積層型インダクタ素子であって、

前記積層方向に直交する端面の少なくとも一面は、前記第2非磁性体層の位置で、積層方向に沿って屈曲している、積層型インダクタ素子。

【請求項1】

磁性体シートを含む複数の絶縁性シートに対して導体パターンおよび内部配線パターンを形成する工程と、

前記絶縁性シートと、前記磁性体シートよりも線膨張係数の小さい非磁性体シートとを用いて、前記非磁性体シートを備える第1非磁性体層、前記磁性体シートを備える第1磁性体層、前記非磁性体シートを備える第2非磁性体層、前記磁性体シートを備える第2磁性体層、および前記非磁性体シートを備える第3非磁性体層を順に積層し、前記導体パターンを接続することでインダクタを形成し、該インダクタ内蔵型の積層体を形成する工程と、を有する積層型インダクタ素子の製造方法であって、

前記積層体は、複数のインダクタが配列されたマザー基板であり、

前記マザー基板の前記第1非磁性体層の表面に、該第1非磁性体層内に収まる深さからなる溝を、前記複数のインダクタを区分する境界に沿って、焼成前に形成する工程と、

焼成後の前記マザー基板の前記第3非磁性体層の表面側から、前記境界に略沿って所定の押圧力でスクライブ手段を接触させ、部分的なクラックを形成する工程と、

クラック形成後の前記マザー基板に対して外部から応力を加えることにより、個片の積層型インダクタ素子に分割する工程と、を有することを特徴とする積層型インダクタ素子の製造方法。

【請求項2】

前記部分的なクラックを形成する工程は、前記クラックが前記第2非磁性体層に達する押圧力で前記スクライブ手段を接触させている、請求項1に記載の積層型インダクタ素子の製造方法。

【請求項3】

前記積層体を形成する工程は、

前記第1磁性体層と前記第2非磁性体層との間に、前記磁性体シートを備える第3磁性体層、前記非磁性体シートを備える第4非磁性体層を、さらに積層する、請求項1または請求項2に記載の積層型インダクタ素子の製造方法。

【請求項4】

非磁性体を備える第1非磁性体層、磁性体を備える第1磁性体層、非磁性体を備える第2非磁性体層、磁性体を備える第2磁性体層、非磁性体を備える第3非磁性体層の順で積層された積層体を備え、該積層体の内部に導体パターンからなるインダクタが形成された積層型インダクタ素子であって、

前記積層方向に直交する端面の少なくとも一面は、前記第2非磁性体層の位置で、積層方向に沿って屈曲している、積層型インダクタ素子。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【公開番号】特開2013−115227(P2013−115227A)

【公開日】平成25年6月10日(2013.6.10)

【国際特許分類】

【出願番号】特願2011−259925(P2011−259925)

【出願日】平成23年11月29日(2011.11.29)

【出願人】(000006231)株式会社村田製作所 (3,635)

【Fターム(参考)】

【公開日】平成25年6月10日(2013.6.10)

【国際特許分類】

【出願日】平成23年11月29日(2011.11.29)

【出願人】(000006231)株式会社村田製作所 (3,635)

【Fターム(参考)】

[ Back to top ]