積層コンデンサ及びコンデンサ内蔵配線基板

【課題】特性が異なる複数の領域からなる積層コンデンサを一体的に作製し、周波数特性の広帯域化を容易に実現可能な積層コンデンサを提供する。

【解決手段】本発明の積層コンデンサは、誘電体層20〜22と内部電極層30〜33とを交互に積層してなり、第1領域R1及び第2領域R2を含むコンデンサ本体部と、アレイ状に配置された全貫通型のビア導体40、41、50、51と、その両端部に接続される外部電極60、61、70、71を備えている。第1ビア導体群であるビア導体40、41は、第1領域R1及び第2領域R2の内部電極層30〜33と電気的に接続され、第2ビア導体群であるビア導体50、51は、第1領域R1の内部電極層30、31と電気的に接続され、かつ第2領域R2の内部電極層32、33と電気的に接続されない。ビア導体50、51は、第2領域R2におけるビア径が第1領域R1におけるビア径よりも小さくなるように形成される。

【解決手段】本発明の積層コンデンサは、誘電体層20〜22と内部電極層30〜33とを交互に積層してなり、第1領域R1及び第2領域R2を含むコンデンサ本体部と、アレイ状に配置された全貫通型のビア導体40、41、50、51と、その両端部に接続される外部電極60、61、70、71を備えている。第1ビア導体群であるビア導体40、41は、第1領域R1及び第2領域R2の内部電極層30〜33と電気的に接続され、第2ビア導体群であるビア導体50、51は、第1領域R1の内部電極層30、31と電気的に接続され、かつ第2領域R2の内部電極層32、33と電気的に接続されない。ビア導体50、51は、第2領域R2におけるビア径が第1領域R1におけるビア径よりも小さくなるように形成される。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、コンデンサ本体部を積層方向に貫通するアレイ状の複数のビア導体を備えた積層コンデンサと、この積層コンデンサを内蔵したコンデンサ内蔵配線基板に関するものである。

【背景技術】

【0002】

従来から、高誘電率のセラミック材料からなるビアアレイ型の積層コンデンサが広く用いられている。この種の積層コンデンサは、例えば、ディジタル回路やマイクロプロセッサなどの各種回路における電源配線のノイズを低減するためのデカップリング用途のコンデンサとして用いられる。また、デカップリング用途の積層コンデンサをICパッケージ等の配線基板に内蔵する構造も採用されている。近年、各種回路の高速化及び高周波化の進展に伴い、デカップリング用途の積層コンデンサに対して広帯域の周波数特性が求められている。一般に、積層コンデンサの共振周波数は、容量と等価直列インダクタンスとの積の平方根に反比例する。そこで、積層コンデンサにおいて、等価直列インダクタンスが小さいコンデンサ部と、等価直列インダクタンスが大きいコンデンサ部とを組み合わせることで、異なる共振周波数を有する広帯域の周波数特性を実現することができる。例えば、積層コンデンサのビア密度を変えることで、等価直列インダクタンスに応じた共振周波数が異なる2つのコンデンサ部を複合化した構成が提案されている(例えば、特許文献1〜3参照)。また、このように複合化した構成を有する積層コンデンサを製造するに際し、等価直列インダクタンスが小さいコンデンサ部と等価直列インダクタンスが大きいコンデンサ部とを別々に作製して一体化するか、あるいは一方を作製した後に他方を順次積層する製造方法が提案されている(例えば、特許文献4参照)。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特許第3995596号公報

【特許文献2】特開2004−31926号公報

【特許文献3】特許第4458812号公報

【特許文献4】特許第4079120号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

しかしながら、上記従来の構造を有する積層コンデンサにおいては、広帯域の周波数特性が得られるものの、等価直列インダクタンスの大小に応じた2つのコンデンサ部からなる積層コンデンサの製法が複雑になることは避けられない。例えば、特許文献4に開示されている製造方法では、2つのコンデンサ部を別々に作製する手法と、一方を作製した後に他方を順次積層する手法のいずれを採用したとしても複雑な工程が必要となり、製造コストが増加する。特に、さらなる広帯域化のために、特性が異なる多数のコンデンサ部を複合化する場合には、コンデンサ部の数の増加に伴い工程が細分化し、製造コストのさらなる増加につながる。また、上記従来の製造方法で作製した積層コンデンサには、一方のコンデンサ部のみに接続される半貫通ビア導体と、2つのコンデンサ部の一体化後に両方に接続される全貫通ビア導体が存在するが、広帯域化のために半貫通ビア導体に比べて全貫通ビア導体が少なくなっている。そのため、ビア導体群全体の抵抗が高くなり、積層方向に大電流を流す電源供給路に利用することは不適切であるとともに、熱伝導性が劣化するという欠点もある。

【0005】

本発明はこれらの問題を解決するためになされたものであり、等価直列インダクタンスが異なる複数の領域からなる積層コンデンサを複雑な工程を導入することなく一体的に作製し、周波数特性の広帯域化が容易に実現可能であるとともに低抵抗かつ大電流の供給路に適した積層コンデンサを提供することを目的とする。

【課題を解決するための手段】

【0006】

上記課題を解決するために、本発明の積層コンデンサは、誘電体層と内部電極層とを交互に積層してなるコンデンサ本体部と、アレイ状に配置され前記コンデンサ本体部を積層方向に貫通する複数のビア導体と、前記複数のビア導体のそれぞれの両端部に接続される複数の外部電極と、を備えた積層コンデンサにおいて、前記複数のビア導体は、前記コンデンサ本体部の一方の主面側の第1領域及び他方の主面側の第2領域における前記内部電極層と電気的に接続された第1ビア導体群と、前記第1領域における前記内部電極層と電気的に接続され、かつ前記第2領域における前記内部電極層と電気的に接続されない第2ビア導体群と、を含み前記第2ビア導体群は、前記第2領域におけるビア径が前記第1領域におけるビア径よりも小さくなるように形成されていることを特徴としている。

【0007】

本発明の積層コンデンサによれば、コンデンサ本体部は一方の主面側の第1領域及び他方の主面側の第2領域を含み、第1ビア導体群は第1領域及び第2領域の両方の内部電極層と電気的に接続されるのに対し、第2ビア導体群は第1領域の内部電極層と電気的に接続されるが第2領域の内部電極層とは電気的に非接続である。これに加えて、第2ビア導体群のビア径は、第1領域に比べて第2領域において小さくなるように形成される。このような構造により、第1領域はビア導体の接続本数が多く、かつ第2領域はビア導体の接続本数が少ないため、等価直列インダクタンスや容量を互いに異ならせて両者を複合化することで、例えば、広帯域の周波数特性などの所望の特性を容易に実現することができる。そして、第1領域と第2領域を別々に作製するための複雑な工程は不要であり、誘電体層と電極層とを交互に積層する工程を繰り返すことで一体的に作製可能である。また、第1ビア導体群と第2ビア導体群はいずれも全貫通型であり、ビア導体群全体として低い抵抗を保つことができる。

【0008】

本発明の積層コンデンサにおいて、第1領域における等価直列インダクタンスが第2領域における等価直列インダクタンスよりも小さいことが望ましい。すなわち、第2領域におけるビア導体の接続本数は、第1領域におけるビア導体の接続本数に比べ、第2ビア導体群の分だけ少なくなるので、他の構成が概ね共通である限り、等価直列インダクタンスは第1領域に比べて第2領域において増加する。第2ビア導体群の本数を第1ビア導体群の本数よりも十分に多く設定すれば、等価直列インダクタンスの相違を拡大して周波数帯域の広帯域化を容易に実現することができる。

【0009】

本発明における典型的な接続形態は、複数の外部電極を、互いに異なる電位に接続される第1外部電極と第2外部電極とに区分し、第1領域及び第2領域において、第1外部電極と各ビア導体を介して電気的に接続される内部導体層と、第2外部電極と各ビア導体を介して電気的に接続される内部導体層とを積層方向で交互に配置することである。例えば、積層コンデンサを互いに異なる電位の間に接続されるデカップリングコンデンサとして機能させることができる。

【0010】

本発明の積層コンデンサにおいて、上記構成要素は多様な形態を持たせることができる。例えば、第1ビア導体群は平面視でコンデンサ本体部の外周側に配置し、第2ビア導体群は平面視でコンデンサ本体部の内周側に配置してもよい。この場合、コンデンサ本体部は平面視で矩形に形成し、第1ビア導体群は矩形のそれぞれの角部に配置してもよい。かかる構造により、第2領域における第1ビア導体群の各ビア導体間の距離を大きく取ることができ、第2領域の等価直列インダクタンスを上げやすくなる。

【0011】

本発明の積層コンデンサにおいて、第1ビア導体群と異極側の内部電極層との間、及び第2ビア導体群と異極側又は同極側の内部電極層との間におけるそれぞれの面方向の間隔(クリアランス径)を適宜に設定することができる。例えば、第2ビア導体群は、第2領域における同極側又は異極側の内部電極層との面方向の間隔を、第1領域における異極側の内部電極層との面方向の間隔よりも小さく設定してもよい。これにより、第2領域における内部電極層の面積を拡大して容量を高めることができる。また例えば、第2ビア導体群は、第2領域における同極側の内部電極層との面方向の間隔を、第2領域における異極側の内部電極層との面方向の間隔よりも小さく設定してもよい。これにより、第2ビア導体群の近傍において、積層方向の導体パターンの粗密差を緩和する効果を得られる。

【0012】

また、本発明の積層コンデンサを内蔵したコンデンサ内蔵配線基板を実現してもよい。このようなコンデンサ内蔵配線基板において、例えば、コア材を開口した収容部(空洞)内に本発明の積層コンデンサを内蔵し、コア材の上部と下部にビルドアップ層を形成してもよい。これにより、広帯域の周波数特性を有する積層コンデンサをデカップリングコンデンサとして利用可能なコンデンサ内蔵配線基板を容易に実現することができる。なお、前記コンデンサ本体部に接続される電源供給路を介して電源が供給される素子をさらに設けてもよく、この場合は、前記素子を前記第1領域の近傍側の表面に配置することが望ましい。

【発明の効果】

【0013】

本発明によれば、積層コンデンサの2つの領域に全貫通型のビア導体群を形成し、2つの領域におけるビア径と接続本数を適宜に調整することで、等価直列インダクタンスが異なる2つの領域を複合化した広帯域の周波数特性を容易に実現することができる。また、2つの領域を別々に作製することなく一体的に積層コンデンサを作製でき、複雑な工程を不要として製造コストの低減が可能となる。さらに、積層コンデンサの全てのビア導体が全貫通型であって、半貫通型のビア導体を用いていないため、ビア導体群全体の抵抗を低くすることができ、積層方向に大電流を流す電源供給路への利用に適しているとともに、良好な熱伝導性を得ることができる。

【図面の簡単な説明】

【0014】

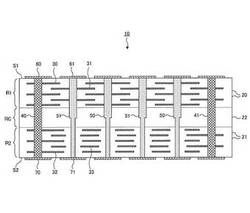

【図1】本実施形態の積層コンデンサ10の概略の断面構造図である。

【図2】本実施形態の積層コンデンサ10を主面S1側から見た斜視図である。

【図3】本実施形態の積層コンデンサ10において、第1領域R1の内部電極層30、31の導体パターンを示す図である。

【図4】本実施形態の積層コンデンサ10において、第2領域R2の内部電極層32、33の導体パターンを示す図である。

【図5】本実施形態の積層コンデンサ10を内蔵したコンデンサ内蔵配線基板100の概略の断面構造図を示す図である。

【図6】本実施形態の積層コンデンサ10の製造方法を説明する第1の断面構造図である。

【図7】図6の積層体10aに対するレーザ加工を説明する図である。

【図8】本実施形態の積層コンデンサ10の製造方法を説明する第2の断面構造図である。

【図9】本実施形態の積層コンデンサ10とは貫通孔V1、V2の形成方法が異なる場合の図1に対応する断面構造図である。

【発明を実施するための形態】

【0015】

以下、本発明の好適な実施形態について、図面を参照しながら説明する。ただし、以下に述べる実施形態は本発明の技術思想を適用した形態の一例であって、本発明が本実施形態の内容により限定されることはない。

【0016】

まず、本発明を適用した積層コンデンサ10の基本構造について説明する。図1は、本実施形態の積層コンデンサ10の概略の断面構造図を示し、図2は、図1の積層コンデンサ10を斜め上方から見た斜視図である。なお、図1は、図2のA―A’断面に対応している。本実施形態の積層コンデンサ10は、例えばチタン酸バリウム等の高誘電率セラミックを焼成したセラミック焼結体からなるビアアレイ型の積層セラミックコンデンサである。図1に示すように、積層コンデンサ10におけるコンデンサ本体部は、一方の主面S1の側の第1領域R1と、他方の主面S2の側の第2領域R2と、第1領域R1と第2領域R2とに挟まれた中間領域RCとに区分される。

【0017】

第1領域R1は、複数のセラミック誘電体層20を積層形成した構造を有し、それぞれのセラミック誘電体層20の間には内部電極層30、31が交互に配置されている。2種類の内部電極層30、31が各セラミック誘電体層20を挟んで対向することで両電極層の間に所定の容量が形成される。また、第2領域R2は、複数のセラミック誘電体層21を積層形成した構造を有し、それぞれのセラミック誘電体層21の間には内部電極層32、33が交互に配置されている。2種類の内部電極層32、33が各セラミック誘電体層21を挟んで対向することで両電極層の間に所定の容量が形成される。一方、中間領域RCは、単層のセラミック誘電体層22のみを含み、内部電極層は形成されていない。なお、以下の説明では、内部電極層30、32を第1電位(例えば、グランド電位)に接続し、内部電極層31、33を第2電位(例えば、所定の電源電圧)に接続することを前提とする。

【0018】

図1の積層コンデンサ10には、第1領域R1、中間領域RC、第2領域R2のそれぞれを積層方向に貫通する複数の貫通孔に導体を埋め込んだ複数のビア導体40、41、50、51が形成されている。これらのビア導体40、41、50、51は全貫通型のビア導体であり、コンデンサ本体部を積層方向に貫通して上下を電気的に接続する役割がある。このうち、複数のビア導体40、41は、本発明の第1ビア導体群として機能し、第1領域R1及び第2領域R2の内部電極層30〜33と接続されている。すなわち、一方のビア導体40は第1電位用の内部電極層30、32に接続され、他方のビア導体41は第2電位用の内部電極層31、33に接続される。これに対し、複数のビア導体50、51は、本発明の第2ビア導体群として機能し、第1領域R1の内部電極層30、31に接続されるが、第2領域R2の内部電極層32、33には接続されない。すなわち、一方のビア導体50は第1電位用の内部電極層30に接続され、他方のビア導体51は第2電位用の内部電極層31に接続される。そして、図1に示すように、第1ビア導体群であるビア導体40、41は積層コンデンサ10の全領域で一定のビア径を有するのに対し、第2ビア導体群であるビア導体50、51は第1領域R1のビア径に比べて第2領域R2のビア径が小さくなっている。この点に関しては後述する。

【0019】

一方の主面S1側の外部電極層には、それぞれのビア導体40、41、50、51の上端部に接続された複数の外部電極60、61が形成されている。また、他方の主面S2側の外部電極層には、それぞれのビア導体40、41、50、51の下端部に接続された複数の外部電極70、71が形成されている。このうち、積層方向で対向する複数の外部電極60、70が第1電位用の外部電極群であり、積層方向で対向する複数の外部電極61、71が第2電位用の外部電極群である。図2に示すように、主面S1側の外部電極層においては、第1電位用の外部電極60と第2電位用の外部電極61がアレイ状に配置されている。外部電極60、61はいずれも共通の直径かつ共通の間隔で並んでいる。図示しない主面S2側の外部電極層においても、図2の外部電極60、61と同様の構造を有する外部電極70、71がアレイ状に配置されている。

【0020】

ここで、図2の例では、全部で36個(6×6個)の外部電極60、61が示されている。このうち、図2の主面S1側の外部電極層において、方形の4隅に位置する4個(2個ずつ)の外部電極60、61が第1ビア導体群であるビア導体40、41に接続され、それ以外の32個の(16個ずつの)外部電極60、61が第2ビア導体群であるビア導体50、51に接続される。従って、第1ビア導体群は4隅に位置する4本の(2本ずつの)ビア導体40、41のみを含み、第2ビア導体群はそれ以外の32本の(16本ずつの)ビア導体50、51のみを含む。第1ビア導体群のビア本数が第2ビア導体群のビア本数より十分に少ないのは、第1領域R1及び第2領域R2の特性上の相違に基づくものであるが、この点については後述する。なお、本実施形態の第1及び第2ビア導体群は図2の配置には限定されず、かつ第1ビア導体群の位置は4隅に限定されないが、第1ビア導体群を外周側における互いに比較的離れた位置に配置することが望ましい。なお、平面視で略方形の積層コンデンサ10を前提にすると、4隅の対角同士が最も大きな距離となる。

【0021】

一般にコンデンサは、容量Cと等価直列インダクタンス(ESL:Equivalent Series Inductance)Lと直列抵抗Rとの直列回路により表すことができる。高周波領域を含む広い周波数範囲を想定する場合は、直列抵抗Rの影響が小さいので、主に容量Cと等価直列インダクタンスLの関係を考えればよい。この場合、コンデンサの自己共振周波数f0は、f0=1/[2π(LC)1/2]と表すことができる。本実施形態の積層コンデンサ10は、第1領域R1の等価直列インダクタンスを、第2領域R2の等価直列インダクタンスに比べて十分小さくなるような特性を有することを特徴としている。これにより、第2領域R2に比べて第1領域R1の自己共振周波数f0が相対的に高くなるので、広帯域の周波数特性を実現することができる。

【0022】

図1の例を参照すると、第1領域R1においては、36本のビア導体40、41、50、51の全てを介して5層の内部電極層30、31が電気的に接続されている。これに対し、第2領域R2においては、4本のビア導体40、41(第1ビア導体群)のみを介して5層の内部電極層32、33が電気的に接続されている。換言すれば、第1領域R1と第2領域R2を比べると、内部電極層のトータルの面積は大きな違いはないが、ビア導体の接続本数が大きく異なる。そのため、ビア導体の接続本数が多い第1領域R1の等価直列インダクタンスは、ビア導体の接続本数が少ない第2領域R2の等価直列インダクタンスに比べ、大幅に小さい値になる。なお、第1領域R1の容量と第2領域R2の容量についても、内部電極層30〜33の配置に依存する相違があるが、この点は後述する。

【0023】

また、積層コンデンサ10の直流特性に着目すると、全てのビア導体40、41、50、51が全貫通型であるため、上端の外部電極60、61と下端の外部電極70、71とを結ぶ36本のビア導体40、41、50、51の全てを経由して電流が流れる。例えば、一部に半貫通型のビア導体を含む場合は、その部分では電流が流れないため直流抵抗が増加することが避けられないのに対し、本実施形態の構造では全貫通型のビア導体40、41、50、51のビア導体群全体における抵抗の増加を防止することができる。よって、積層コンデンサ10をデカップリング及び電源供給路用途に用いる場合は、上端の外部電極60、61と下端の外部電極70、71の間に大きな電流を流すことができる。さらに、全貫通型のビア導体40、41、50、51を用いれば、良好な熱伝導性を保つことができる。

【0024】

次に、図1の積層コンデンサ10において、各内部電極層30〜33の具体的な導体パターンについて図3及び図4を参照して説明する。図3(A)は、第1領域R1の第1電位用の内部電極層30の導体パターンを示している。図3(A)に示すように、図2の配置と同様、4隅の4本のビア導体40、41(第1ビア導体群)と、それ以外の32本のビア導体50、51(第2ビア導体群)がアレイ状に配置されている。それぞれのビア導体40、41、50、51は、いずれもビア径D1を有する。そして、第1電位用の2本のビア導体40及び第1電位用の16本のビア導体50は、同極である内部電極層30と電気的に接続されている。これに対し、第2電位用の2本のビア導体41及び第2電位用の16本のビア導体51のそれぞれの周囲にはクリアランスホールCHが形成され、異極である内部電極層30と絶縁されている。それぞれのクリアランスホールCHは、クリアランス径C1(直径)の円形の形状を有する。

【0025】

また、図3(B)は、第1領域R1の第2電位用の内部電極層31の導体パターンを示している。図3(B)におけるビア導体40、41、50、51の配置、及びそれぞれのビア径D1については、図3(A)と同様である。第2電位用の2本のビア導体41及び第2電位用の16本のビア導体51は、同極である内部電極層31と電気的に接続されている。これに対し、第1電位用の2本のビア導体40及び第1電位用の16本のビア導体50のそれぞれの周囲には、図3(A)と同様のクリアランス径C1で円形のクリアランスホールCHが形成され、異極である内部電極層31と絶縁されている。

【0026】

なお、図3において、ビア導体40、41、50、51のビア径D1は、例えば、0.08〜0.12mm程度に設定される。また、ビア導体40、41、50、51の各クリアランスホールCHのクリアランス径C1は、例えば、0.3〜0.4mm程度に設定される。

【0027】

次に図4(A)は、第2領域R2の第1電位用の内部電極層32の導体パターンを示している。図4(A)に示すように、図3の配置と同様、4隅の4本のビア導体40、41(第1ビア導体群)と、それ以外の32本のビア導体50、51(第2ビア導体群)がアレイ状に配置されている。第1ビア導体群の各ビア導体40、41は図3と同様のビア径D1を有するのに対し、第2ビア導体群の各ビア導体50、51は、ビア径D1より小さいビア径D2を有する。そして、第1電位用の2本のビア導体40は、同極である内部電極層32と電気的に接続されている。これに対し、第2電位用の2本のビア導体41の周囲には、図3と同様のクリアランス径C1で円形のクリアランスホールCHが形成され、異極である内部電極層32と絶縁されている。また、第1電位用の16本のビア導体50の周囲には、クリアランス径C2で円形のクリアランスホールCHが形成され、同極である内部電極層32と絶縁されている。さらに、第2電位用の16本のビア導体51の周囲には、クリアランス径C3で円形のクリアランスホールCHが形成され、異極である内部電極層32と絶縁されている。

【0028】

また、図4(B)は、第2領域R2の第2電位用の内部電極層33の導体パターンを示している。図4(B)におけるビア導体40、41、50、51の配置、及びそれぞれのビア径D1、D2については、図4(A)と同様である。第2電位用の2本のビア導体41は、同極である内部電極層33と電気的に接続されている。これに対し、第1電位用の2本のビア導体40の周囲には、図4(A)と同様のクリアランス径C1で円形のクリアランスホールCHが形成され、異極である内部電極層33と絶縁されている。また、第2電位用の16本のビア導体51の周囲には、図4(A)と同様のクリアランス径C2で円形のクリアランスホールCHが形成され、同極である内部電極層33と絶縁されている。さらに、第1電位用の16本のビア導体50の周囲には、図4(A)と同様のクリアランス径C3で円形のクリアランスホールCHが形成され、異極である内部電極層33と絶縁されている。

【0029】

なお、図4において、ビア導体50、51のビア径D2は、例えば、0.04〜0.08mm程度に設定される。また、ビア導体50、51の各クリアランスホールCHに関し、クリアランス径C2は、例えば、0.21〜0.33mm程度に設定され、クリアランス径C3は、例えば、0.24〜0.36mm程度に設定される。ビア導体40、41のビア径D1及びクリアランス径C1については、上述した通りである。

【0030】

以上のように、第2領域R2においてビア導体50、51のビア径D2を小さく設定したことにより、クリアランス径C2、C3をそれほど大きくしなくても、ビア導体50、51と内部電極層32、33との間の絶縁を確実に確保することができる。仮に、第2領域R2においてビア径D2がビア径D1と同じ値である場合は内部電極層32、33との絶縁確保のためにクリアランス径C2、C3を大きくせざるを得ない。よって、内部電極層32、33の対向面積が小さくなり、その分だけ第2領域R2の容量値が小さくなるが、本実施形態においてはクリアランス径C2、C3を小さくすることで内部電極層32、33の対向面積を確保して第2領域R2の容量値を大きくすることができる。

【0031】

図4において、第2ビア導体群に対し同極側のクリアランス径C2と異極側のクリアランス径C3は、C2<C3の関係を満たしているが、これは、同極側については部分的に接触したときに第2領域R2のインダクタンス値の誤差の要因となるだけであるのに対し、異極側については電気的ショートによって積層コンデンサ10として機能しなくなる事態を防止する観点から十分なマージンを取ったものである。一方、第2領域R2におけるクリアランスホールCHの部分が積層方向で重なり、導体パターンの有無による粗密差が生じるが、上記のように同極側と異極側でクリアランス径C2、C3を異ならせることにより、粗密差を緩和する効果がある。これにより、積層コンデンサ10の反り等の変形を抑制することができる。

【0032】

以上、図1〜図4に示した積層コンデンサ10は一例であって、基本構造を有する限り、寸法パラメータや配置等については多様な変更が可能である。例えば、実際の積層コンデンサ10では、内部電極層30〜33の積層数やビア導体40、41、50、51の本数をより増加させることができる。また、各クリアランスホールCHのクリアランス径C1、C2、C3は、本発明の特徴を損わない限り、適宜に変更可能である。さらに、図1においては、第1領域R1と第2領域R2とに挟まれた中間領域RCを示しているが、第1領域R1の内部電極層30、31と第2領域R2の内部電極層32、33との間を広く確保する必要がなければ、中間領域RCは設けなくてもよい。

【0033】

以下の表1は、本実施形態の積層コンデンサ10に関し、所定の設計条件の下で得られた特性例を示している。すなわち、方形の積層コンデンサ10のサイズを平面視で18.6mm×18.6mmに設定し、ビア導体40、41、50、51の本数を全部で1000本とし、そのうち4隅にはビア導体40、41を2本ずつ配置するとともに、内部電極層30〜33の積層数を全部で110層とし、そのうち第1領域R1と第2領域R2の積増数をそれぞれ55層とした。このような条件の下、第1領域R1及び第2領域R2において、それぞれの容量及び等価直列インダクタンス(ESL)として、表1に示す評価結果が得られた。

【0034】

【表1】

【0035】

このように、等価直列インダクタタンスに関しては、接続されるビア導体の本数の相違を反映して、第1領域R1に比べて第2領域R2の方が十分に大きな値を得られることが確認された。また、容量に関しては、主に内部電極層30〜33の面積の若干の相違(クリアランス径の相違)を反映して、第1領域R1に比べて第2領域R2の方が大きな値を得られることが確認された。従って、表1の結果から、積層コンデンサ10の特性として、自己共振周波数f0が大きく異なる2つの特性を含む広帯域の周波数特性を実現することができる。このように、第1領域R1と第2領域R2との周波数特性の違いは、両者の等価直列インダクタタンスの違いが支配的であるが、両者の容量の違いも寄与していることがわかる。

【0036】

次に、本実施形態の積層コンデンサ10の応用例の一つとして、積層コンデンサ10を内蔵したコンデンサ内蔵配線基板について説明する。図5は、コンデンサ内蔵配線基板100(以下、単に配線基板100と呼ぶ)の概略の断面構造図を示している。図5に示すように、本実施形態の配線基板100は、コア材101と、コア材101の上面側のビルドアップ層102(積層部)と、コア材101の下面側のビルドアップ層103(積層部)とを含む構造を有している。本実施形態の配線基板100は、その内部に部品としての積層コンデンサ10が内蔵されるとともに、上部に半導体素子である半導体チップ200が載置されている。

【0037】

コア材101は、例えば、ガラス繊維を含んだエポキシ樹脂からなる。コア材101には、中央領域を貫通する収容穴部101aが形成され、この収容穴部101aに本実施形態の積層コンデンサ10が埋め込まれた状態で収容されている。コア材101には、外周領域を積層方向に貫通する複数のスルーホール導体111が形成され、スルーホール導体111の内部が例えばSiO2などのフィラー材を含有するエポキシ等からなる閉塞体112で埋められている。また、収容穴部101aと積層コンデンサ10の側面との間隙部には樹脂充填材110が充填されている。樹脂充填材110は、例えば熱硬化性樹脂からなり、コア材101に対する積層コンデンサ10の相対的な変形を吸収するように作用する。積層コンデンサ10の上側の各外部電極60、61(図1)は上方のビルドアップ層102と電気的に接続されるとともに、積層コンデンサ10の下側の各外部電極70、71(図1)は下方のビルドアップ層103と電気的に接続される。

【0038】

上方のビルドアップ層102は、コア材101の上部の樹脂絶縁層104と、樹脂絶縁層104の上部の樹脂絶縁層105と、樹脂絶縁層105の上部のソルダーレジスト層106とが積層形成された構造を有する。樹脂絶縁層104の上面には導体層121が形成され、樹脂絶縁層105の上面には複数の端子パッド123が形成されている。樹脂絶縁層104の所定箇所には、積層コンデンサ10の外部電極60、61と導体層121を積層方向に接続導通する複数のビア導体120が設けられている。また、樹脂絶縁層105の所定箇所には、導体層121と複数の端子パッド123を積層方向に接続導通する複数のビア導体122が設けられている。ソルダーレジスト層106は、複数箇所が開口されて複数の端子パッド123が露出し、そこに複数の半田バンプ124が形成されている。各々の半田バンプ124は、配線基板100に載置される半導体チップ200の各パッド201に接続される。

【0039】

下方のビルドアップ層103は、コア材101の下部の樹脂絶縁層107と、樹脂絶縁層107の下部の樹脂絶縁層108と、樹脂絶縁層108の下部のソルダーレジスト層109とが積層形成された構造を有する。樹脂絶縁層107の下面には導体層131が形成され、樹脂絶縁層108の下面には複数のBGA用パッド133が形成されている。樹脂絶縁層107の所定箇所には、積層コンデンサ10の外部電極70、71と導体層131を積層方向に接続導通する複数のビア導体130が設けられている。また、樹脂絶縁層108の所定箇所には、導体層131と複数のBGA用パッド133を積層方向に接続導通する複数のビア導体132が設けられている。ソルダーレジスト層109は、複数箇所が開口されて複数のBGA用パッド133が露出し、そこに複数の半田ボール134が接続される。なお、配線基板100は、複数の半田ボール134を介して、図示されない外部基材と電気的に接続される。

【0040】

図5の配線基板100の断面構造において、積層コンデンサ10の上側では、半田バンプ124、端子パッド123、ビア導体122、導体層121、ビア導体120を経由して、半導体チップ200の所定のパッド201と積層コンデンサ10の外部電極60、61の間が電気的に接続される。同様に、積層コンデンサ10の下側では、ビア導体130、導体層131、ビア導体132、BGA用パッド133、半田ボール134を経由して、積層コンデンサ10の外部電極70、71と外部基材の所定の端子の間が電気的に接続される。そして、積層コンデンサ10を、半導体チップ200に供給される電源電圧のデカップリング用のコンデンサとして機能させる場合は、上記の経路により、積層コンデンサ10の正極を半導体チップ200の電源電圧用のパッド201に接続し、積層コンデンサ10の負極を半導体チップ200のグランド電位用のパッド201に接続すればよい。

【0041】

以下、本実施形態の積層コンデンサ10の製造方法の概略について説明する。まず、周知の手法に従って、セラミックグリーンシートを用意し、その表面に導体層となる導電性ペーストをスクリーン印刷により形成した状態で積層する。そして、かかる工程を繰り返すことにより、図6に示すように、セラミック誘電体層20、21、22となるべきセラミックグリーンシートと、内部電極層30、31、32、33となるべき導電性ペーストとが交互に積層された積層体10aが得られる。このように、本実施形態においては、積層コンデンサ10の第1領域R1と第2領域R2とを別々に作製する必要がない。

【0042】

次いで、積層体10aに対し、ビア導体40、41、50、51を形成するためのレーザ加工を施す。例えば、図7(A)に示すように、積層体10aの主面S1においてビア導体40、41、50、51の形成予定位置PVに対し、所定の順番でレーザの位置を順次移動させながら上方から下方にレーザ照射を行う。このとき、レーザのビーム径やショット数などの加工条件を適切に制御することにより、4隅のビア導体40、41に対応する貫通孔V1と、それ以外のビア導体50、51に対応する貫通孔V2とを順次形成する。

【0043】

一般に、レーザは図7(B)に示すようなパルス波形によって発振する。すなわち、パルス波形の1周期Tがレーザの1ショットを構成し、1ショット内にパルス幅PWの1つのパルスが含まれる。レーザ照射時のエネルギーは、パルス幅PWとレーザ出力の積に比例する。また、レーザビームの焦点を調節することにより、ビーム径を変更することができる。そして、図7(B)の1ショット毎に各々の形成予定位置PVを変更し、それを所定のショット数に達するまで周期的に繰り返すことにより(サイクル加工)、貫通孔V1、V2を徐々に深くすることができる。

【0044】

また、図8に示すように、第1領域R1では貫通孔V1、V2が共通のビア径D1(図3)となるように同一のビーム径でレーザ加工を制御するとともに、第2領域R2では貫通孔V1、V2が異なるビア径D1、D2(図4)となるように異なるビーム径でレーザ加工を制御する。すなわち、ビア導体40、41に対応する貫通孔V1はビア径D1が固定であるため、全てのショットで同一のビーム径を維持する一方、ビア導体50、51に対応する貫通孔V2はビア径D1からビア径D2に細くなるので、図8の中間領域RCの境界位置に対応する所定のショット数に達したときにビーム径を減少させればよい。これにより、積層体10aには、図8に示す断面形状を有する貫通孔V1、V2を形成することができる。ただし、上記の説明では積層体10aの一方の主面S1の側からレーザ照射を行う場合を説明したが、これに限らず、積層体10aの両方の主面S1、S2の側からレーザ照射を行ってもよい。この場合、貫通孔V2については、上方からのレーザ照射でビア径D1に対応する広いビーム径とし、下方からのレーザ照射でビア径D2に対応する細いビーム径として、それぞれのレーザ加工を制御すればよい。

【0045】

次いで、図1に示すように、図8の貫通孔V1、V2のそれぞれの内部に導電性ペーストを充填する。これにより、貫通孔V1、V2内の導電性ペーストがそれぞれ対応する内部電極層30〜33に接続される。また、それぞれの貫通孔V1、V2の上端側の外部電極60、61となる導電性ペーストがスクリーン印刷により形成されるとともに、それぞれの貫通孔V1、V2の下端側の外部電極70、71となる導電性ペーストがスクリーン印刷により形成される。その後、積層体10aを乾燥させ、所定の条件で同時焼成することにより焼成積層体を形成する。これにより、各層のセラミックグリーンシートが焼結し、内部電極層30〜33、ビア導体40、41、50、51、外部電極60、61、70、71にそれぞれ含まれる導電性ペースト中の成分が焼結してセラミック焼結体となる。以上のようにして、図1の構造を有する積層コンデンサ10が得られる。

【0046】

本実施形態の積層コンデンサ10は、上記の製造方法によって説明したように、第1領域R1と第2領域R2とを別々に作製することは必要なく、一体的なコンデンサ本体部として作製することができる。よって、周波数特性が異なる2つのコンデンサ本体部を作製するための複雑な工程が不要となるし、個々の領域に半貫通型のビア導体を形成する必要もない。従って、本実施形態の積層コンデンサ10の構造を採用することにより、製造工程を簡素化して製造コストを低減する効果がある。また、本実施形態の積層コンデンサ10は、ビア導体40、41、50、51の接続本数とビア径を調節することで、所望の周波数特性を容易に実現することができる。

【0047】

本実施形態の積層コンデンサ10に関しては、上述の製造方法に限らず多様な変形例がある。図9は、上述の製造方法とは貫通孔V1、V2の形成方法が異なる場合の図1に対応する断面構造図を示している。具体的には、図9の断面構造においては、第2ビア導体群であるビア導体50、51が第1領域R1では図1と同様のビア径D1で形成されるが、第2領域R2ではテーパ状に変化する。すなわち、第1領域R1の上部から第2領域R2の下部にかけて、ビア導体50、51のビア径が徐々に細くなっていくことがわかる。通常、レーザ加工は、その特性上、照射側の近傍から遠方にかけて貫通孔の径が細くなる傾向があり、第1領域R1で各ビア導体40、41、50、51は、実際には僅かにテーパ状になっている。しかし、ビア導体40、41及び第1領域R1のビア導体50、51は、レーザ照射の際に融点が低い内部電極層30〜33の領域を含めて開口するのに対し、内部電極層32、33に接続されない第2領域R2のビア導体50、51は、融点が高いセラミックの領域のみを開口することになり、他の部分と比べてテーパの形状が顕著になる。このように、図9に示すようなテーパ状のビア導体50、51を有する場合であっても、第1領域R1に比べて第2領域R2のビア径が細いため、本実施形態の積層コンデンサ10の効果を得ることができる。

【0048】

以上、本実施形態に基づき本発明の内容を具体的に説明したが、本発明は上述の実施形態に限定されるものではなく、その要旨を逸脱しない範囲で多様な変更を施すことができる。例えば、本実施形態では、積層コンデンサ10のコンデンサ本体部が、互いに等価直列インダクタンスが異なる第1領域R1と第2領域R2を含む場合を説明したが、これに限らず、互いに等価直列インダクタンスが異なる3つ以上の領域を複合化して積層コンデンサ10を構成してもよい。この場合、3つ以上の領域におけるビア導体との接続本数やビア径を適切に設定することにより、より広帯域の周波数特性を有する積層コンデンサを実現可能となる。さらに、その他の点についても上記実施形態により本発明の内容が限定されるものではなく、本発明の作用効果を得られる限り、上記実施形態に開示した内容には限定されることなく適宜に変更可能である。

【符号の説明】

【0049】

10…積層コンデンサ

20、21、22…セラミック誘電体層

30、31、32、33…内部電極層

40、41、50、51…ビア導体

60、61、70、71…外部電極

100…コンデンサ内蔵配線基板

R1…第1領域

R2…第2領域

RC…中間領域

CH…クリアランスホール

【技術分野】

【0001】

本発明は、コンデンサ本体部を積層方向に貫通するアレイ状の複数のビア導体を備えた積層コンデンサと、この積層コンデンサを内蔵したコンデンサ内蔵配線基板に関するものである。

【背景技術】

【0002】

従来から、高誘電率のセラミック材料からなるビアアレイ型の積層コンデンサが広く用いられている。この種の積層コンデンサは、例えば、ディジタル回路やマイクロプロセッサなどの各種回路における電源配線のノイズを低減するためのデカップリング用途のコンデンサとして用いられる。また、デカップリング用途の積層コンデンサをICパッケージ等の配線基板に内蔵する構造も採用されている。近年、各種回路の高速化及び高周波化の進展に伴い、デカップリング用途の積層コンデンサに対して広帯域の周波数特性が求められている。一般に、積層コンデンサの共振周波数は、容量と等価直列インダクタンスとの積の平方根に反比例する。そこで、積層コンデンサにおいて、等価直列インダクタンスが小さいコンデンサ部と、等価直列インダクタンスが大きいコンデンサ部とを組み合わせることで、異なる共振周波数を有する広帯域の周波数特性を実現することができる。例えば、積層コンデンサのビア密度を変えることで、等価直列インダクタンスに応じた共振周波数が異なる2つのコンデンサ部を複合化した構成が提案されている(例えば、特許文献1〜3参照)。また、このように複合化した構成を有する積層コンデンサを製造するに際し、等価直列インダクタンスが小さいコンデンサ部と等価直列インダクタンスが大きいコンデンサ部とを別々に作製して一体化するか、あるいは一方を作製した後に他方を順次積層する製造方法が提案されている(例えば、特許文献4参照)。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特許第3995596号公報

【特許文献2】特開2004−31926号公報

【特許文献3】特許第4458812号公報

【特許文献4】特許第4079120号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

しかしながら、上記従来の構造を有する積層コンデンサにおいては、広帯域の周波数特性が得られるものの、等価直列インダクタンスの大小に応じた2つのコンデンサ部からなる積層コンデンサの製法が複雑になることは避けられない。例えば、特許文献4に開示されている製造方法では、2つのコンデンサ部を別々に作製する手法と、一方を作製した後に他方を順次積層する手法のいずれを採用したとしても複雑な工程が必要となり、製造コストが増加する。特に、さらなる広帯域化のために、特性が異なる多数のコンデンサ部を複合化する場合には、コンデンサ部の数の増加に伴い工程が細分化し、製造コストのさらなる増加につながる。また、上記従来の製造方法で作製した積層コンデンサには、一方のコンデンサ部のみに接続される半貫通ビア導体と、2つのコンデンサ部の一体化後に両方に接続される全貫通ビア導体が存在するが、広帯域化のために半貫通ビア導体に比べて全貫通ビア導体が少なくなっている。そのため、ビア導体群全体の抵抗が高くなり、積層方向に大電流を流す電源供給路に利用することは不適切であるとともに、熱伝導性が劣化するという欠点もある。

【0005】

本発明はこれらの問題を解決するためになされたものであり、等価直列インダクタンスが異なる複数の領域からなる積層コンデンサを複雑な工程を導入することなく一体的に作製し、周波数特性の広帯域化が容易に実現可能であるとともに低抵抗かつ大電流の供給路に適した積層コンデンサを提供することを目的とする。

【課題を解決するための手段】

【0006】

上記課題を解決するために、本発明の積層コンデンサは、誘電体層と内部電極層とを交互に積層してなるコンデンサ本体部と、アレイ状に配置され前記コンデンサ本体部を積層方向に貫通する複数のビア導体と、前記複数のビア導体のそれぞれの両端部に接続される複数の外部電極と、を備えた積層コンデンサにおいて、前記複数のビア導体は、前記コンデンサ本体部の一方の主面側の第1領域及び他方の主面側の第2領域における前記内部電極層と電気的に接続された第1ビア導体群と、前記第1領域における前記内部電極層と電気的に接続され、かつ前記第2領域における前記内部電極層と電気的に接続されない第2ビア導体群と、を含み前記第2ビア導体群は、前記第2領域におけるビア径が前記第1領域におけるビア径よりも小さくなるように形成されていることを特徴としている。

【0007】

本発明の積層コンデンサによれば、コンデンサ本体部は一方の主面側の第1領域及び他方の主面側の第2領域を含み、第1ビア導体群は第1領域及び第2領域の両方の内部電極層と電気的に接続されるのに対し、第2ビア導体群は第1領域の内部電極層と電気的に接続されるが第2領域の内部電極層とは電気的に非接続である。これに加えて、第2ビア導体群のビア径は、第1領域に比べて第2領域において小さくなるように形成される。このような構造により、第1領域はビア導体の接続本数が多く、かつ第2領域はビア導体の接続本数が少ないため、等価直列インダクタンスや容量を互いに異ならせて両者を複合化することで、例えば、広帯域の周波数特性などの所望の特性を容易に実現することができる。そして、第1領域と第2領域を別々に作製するための複雑な工程は不要であり、誘電体層と電極層とを交互に積層する工程を繰り返すことで一体的に作製可能である。また、第1ビア導体群と第2ビア導体群はいずれも全貫通型であり、ビア導体群全体として低い抵抗を保つことができる。

【0008】

本発明の積層コンデンサにおいて、第1領域における等価直列インダクタンスが第2領域における等価直列インダクタンスよりも小さいことが望ましい。すなわち、第2領域におけるビア導体の接続本数は、第1領域におけるビア導体の接続本数に比べ、第2ビア導体群の分だけ少なくなるので、他の構成が概ね共通である限り、等価直列インダクタンスは第1領域に比べて第2領域において増加する。第2ビア導体群の本数を第1ビア導体群の本数よりも十分に多く設定すれば、等価直列インダクタンスの相違を拡大して周波数帯域の広帯域化を容易に実現することができる。

【0009】

本発明における典型的な接続形態は、複数の外部電極を、互いに異なる電位に接続される第1外部電極と第2外部電極とに区分し、第1領域及び第2領域において、第1外部電極と各ビア導体を介して電気的に接続される内部導体層と、第2外部電極と各ビア導体を介して電気的に接続される内部導体層とを積層方向で交互に配置することである。例えば、積層コンデンサを互いに異なる電位の間に接続されるデカップリングコンデンサとして機能させることができる。

【0010】

本発明の積層コンデンサにおいて、上記構成要素は多様な形態を持たせることができる。例えば、第1ビア導体群は平面視でコンデンサ本体部の外周側に配置し、第2ビア導体群は平面視でコンデンサ本体部の内周側に配置してもよい。この場合、コンデンサ本体部は平面視で矩形に形成し、第1ビア導体群は矩形のそれぞれの角部に配置してもよい。かかる構造により、第2領域における第1ビア導体群の各ビア導体間の距離を大きく取ることができ、第2領域の等価直列インダクタンスを上げやすくなる。

【0011】

本発明の積層コンデンサにおいて、第1ビア導体群と異極側の内部電極層との間、及び第2ビア導体群と異極側又は同極側の内部電極層との間におけるそれぞれの面方向の間隔(クリアランス径)を適宜に設定することができる。例えば、第2ビア導体群は、第2領域における同極側又は異極側の内部電極層との面方向の間隔を、第1領域における異極側の内部電極層との面方向の間隔よりも小さく設定してもよい。これにより、第2領域における内部電極層の面積を拡大して容量を高めることができる。また例えば、第2ビア導体群は、第2領域における同極側の内部電極層との面方向の間隔を、第2領域における異極側の内部電極層との面方向の間隔よりも小さく設定してもよい。これにより、第2ビア導体群の近傍において、積層方向の導体パターンの粗密差を緩和する効果を得られる。

【0012】

また、本発明の積層コンデンサを内蔵したコンデンサ内蔵配線基板を実現してもよい。このようなコンデンサ内蔵配線基板において、例えば、コア材を開口した収容部(空洞)内に本発明の積層コンデンサを内蔵し、コア材の上部と下部にビルドアップ層を形成してもよい。これにより、広帯域の周波数特性を有する積層コンデンサをデカップリングコンデンサとして利用可能なコンデンサ内蔵配線基板を容易に実現することができる。なお、前記コンデンサ本体部に接続される電源供給路を介して電源が供給される素子をさらに設けてもよく、この場合は、前記素子を前記第1領域の近傍側の表面に配置することが望ましい。

【発明の効果】

【0013】

本発明によれば、積層コンデンサの2つの領域に全貫通型のビア導体群を形成し、2つの領域におけるビア径と接続本数を適宜に調整することで、等価直列インダクタンスが異なる2つの領域を複合化した広帯域の周波数特性を容易に実現することができる。また、2つの領域を別々に作製することなく一体的に積層コンデンサを作製でき、複雑な工程を不要として製造コストの低減が可能となる。さらに、積層コンデンサの全てのビア導体が全貫通型であって、半貫通型のビア導体を用いていないため、ビア導体群全体の抵抗を低くすることができ、積層方向に大電流を流す電源供給路への利用に適しているとともに、良好な熱伝導性を得ることができる。

【図面の簡単な説明】

【0014】

【図1】本実施形態の積層コンデンサ10の概略の断面構造図である。

【図2】本実施形態の積層コンデンサ10を主面S1側から見た斜視図である。

【図3】本実施形態の積層コンデンサ10において、第1領域R1の内部電極層30、31の導体パターンを示す図である。

【図4】本実施形態の積層コンデンサ10において、第2領域R2の内部電極層32、33の導体パターンを示す図である。

【図5】本実施形態の積層コンデンサ10を内蔵したコンデンサ内蔵配線基板100の概略の断面構造図を示す図である。

【図6】本実施形態の積層コンデンサ10の製造方法を説明する第1の断面構造図である。

【図7】図6の積層体10aに対するレーザ加工を説明する図である。

【図8】本実施形態の積層コンデンサ10の製造方法を説明する第2の断面構造図である。

【図9】本実施形態の積層コンデンサ10とは貫通孔V1、V2の形成方法が異なる場合の図1に対応する断面構造図である。

【発明を実施するための形態】

【0015】

以下、本発明の好適な実施形態について、図面を参照しながら説明する。ただし、以下に述べる実施形態は本発明の技術思想を適用した形態の一例であって、本発明が本実施形態の内容により限定されることはない。

【0016】

まず、本発明を適用した積層コンデンサ10の基本構造について説明する。図1は、本実施形態の積層コンデンサ10の概略の断面構造図を示し、図2は、図1の積層コンデンサ10を斜め上方から見た斜視図である。なお、図1は、図2のA―A’断面に対応している。本実施形態の積層コンデンサ10は、例えばチタン酸バリウム等の高誘電率セラミックを焼成したセラミック焼結体からなるビアアレイ型の積層セラミックコンデンサである。図1に示すように、積層コンデンサ10におけるコンデンサ本体部は、一方の主面S1の側の第1領域R1と、他方の主面S2の側の第2領域R2と、第1領域R1と第2領域R2とに挟まれた中間領域RCとに区分される。

【0017】

第1領域R1は、複数のセラミック誘電体層20を積層形成した構造を有し、それぞれのセラミック誘電体層20の間には内部電極層30、31が交互に配置されている。2種類の内部電極層30、31が各セラミック誘電体層20を挟んで対向することで両電極層の間に所定の容量が形成される。また、第2領域R2は、複数のセラミック誘電体層21を積層形成した構造を有し、それぞれのセラミック誘電体層21の間には内部電極層32、33が交互に配置されている。2種類の内部電極層32、33が各セラミック誘電体層21を挟んで対向することで両電極層の間に所定の容量が形成される。一方、中間領域RCは、単層のセラミック誘電体層22のみを含み、内部電極層は形成されていない。なお、以下の説明では、内部電極層30、32を第1電位(例えば、グランド電位)に接続し、内部電極層31、33を第2電位(例えば、所定の電源電圧)に接続することを前提とする。

【0018】

図1の積層コンデンサ10には、第1領域R1、中間領域RC、第2領域R2のそれぞれを積層方向に貫通する複数の貫通孔に導体を埋め込んだ複数のビア導体40、41、50、51が形成されている。これらのビア導体40、41、50、51は全貫通型のビア導体であり、コンデンサ本体部を積層方向に貫通して上下を電気的に接続する役割がある。このうち、複数のビア導体40、41は、本発明の第1ビア導体群として機能し、第1領域R1及び第2領域R2の内部電極層30〜33と接続されている。すなわち、一方のビア導体40は第1電位用の内部電極層30、32に接続され、他方のビア導体41は第2電位用の内部電極層31、33に接続される。これに対し、複数のビア導体50、51は、本発明の第2ビア導体群として機能し、第1領域R1の内部電極層30、31に接続されるが、第2領域R2の内部電極層32、33には接続されない。すなわち、一方のビア導体50は第1電位用の内部電極層30に接続され、他方のビア導体51は第2電位用の内部電極層31に接続される。そして、図1に示すように、第1ビア導体群であるビア導体40、41は積層コンデンサ10の全領域で一定のビア径を有するのに対し、第2ビア導体群であるビア導体50、51は第1領域R1のビア径に比べて第2領域R2のビア径が小さくなっている。この点に関しては後述する。

【0019】

一方の主面S1側の外部電極層には、それぞれのビア導体40、41、50、51の上端部に接続された複数の外部電極60、61が形成されている。また、他方の主面S2側の外部電極層には、それぞれのビア導体40、41、50、51の下端部に接続された複数の外部電極70、71が形成されている。このうち、積層方向で対向する複数の外部電極60、70が第1電位用の外部電極群であり、積層方向で対向する複数の外部電極61、71が第2電位用の外部電極群である。図2に示すように、主面S1側の外部電極層においては、第1電位用の外部電極60と第2電位用の外部電極61がアレイ状に配置されている。外部電極60、61はいずれも共通の直径かつ共通の間隔で並んでいる。図示しない主面S2側の外部電極層においても、図2の外部電極60、61と同様の構造を有する外部電極70、71がアレイ状に配置されている。

【0020】

ここで、図2の例では、全部で36個(6×6個)の外部電極60、61が示されている。このうち、図2の主面S1側の外部電極層において、方形の4隅に位置する4個(2個ずつ)の外部電極60、61が第1ビア導体群であるビア導体40、41に接続され、それ以外の32個の(16個ずつの)外部電極60、61が第2ビア導体群であるビア導体50、51に接続される。従って、第1ビア導体群は4隅に位置する4本の(2本ずつの)ビア導体40、41のみを含み、第2ビア導体群はそれ以外の32本の(16本ずつの)ビア導体50、51のみを含む。第1ビア導体群のビア本数が第2ビア導体群のビア本数より十分に少ないのは、第1領域R1及び第2領域R2の特性上の相違に基づくものであるが、この点については後述する。なお、本実施形態の第1及び第2ビア導体群は図2の配置には限定されず、かつ第1ビア導体群の位置は4隅に限定されないが、第1ビア導体群を外周側における互いに比較的離れた位置に配置することが望ましい。なお、平面視で略方形の積層コンデンサ10を前提にすると、4隅の対角同士が最も大きな距離となる。

【0021】

一般にコンデンサは、容量Cと等価直列インダクタンス(ESL:Equivalent Series Inductance)Lと直列抵抗Rとの直列回路により表すことができる。高周波領域を含む広い周波数範囲を想定する場合は、直列抵抗Rの影響が小さいので、主に容量Cと等価直列インダクタンスLの関係を考えればよい。この場合、コンデンサの自己共振周波数f0は、f0=1/[2π(LC)1/2]と表すことができる。本実施形態の積層コンデンサ10は、第1領域R1の等価直列インダクタンスを、第2領域R2の等価直列インダクタンスに比べて十分小さくなるような特性を有することを特徴としている。これにより、第2領域R2に比べて第1領域R1の自己共振周波数f0が相対的に高くなるので、広帯域の周波数特性を実現することができる。

【0022】

図1の例を参照すると、第1領域R1においては、36本のビア導体40、41、50、51の全てを介して5層の内部電極層30、31が電気的に接続されている。これに対し、第2領域R2においては、4本のビア導体40、41(第1ビア導体群)のみを介して5層の内部電極層32、33が電気的に接続されている。換言すれば、第1領域R1と第2領域R2を比べると、内部電極層のトータルの面積は大きな違いはないが、ビア導体の接続本数が大きく異なる。そのため、ビア導体の接続本数が多い第1領域R1の等価直列インダクタンスは、ビア導体の接続本数が少ない第2領域R2の等価直列インダクタンスに比べ、大幅に小さい値になる。なお、第1領域R1の容量と第2領域R2の容量についても、内部電極層30〜33の配置に依存する相違があるが、この点は後述する。

【0023】

また、積層コンデンサ10の直流特性に着目すると、全てのビア導体40、41、50、51が全貫通型であるため、上端の外部電極60、61と下端の外部電極70、71とを結ぶ36本のビア導体40、41、50、51の全てを経由して電流が流れる。例えば、一部に半貫通型のビア導体を含む場合は、その部分では電流が流れないため直流抵抗が増加することが避けられないのに対し、本実施形態の構造では全貫通型のビア導体40、41、50、51のビア導体群全体における抵抗の増加を防止することができる。よって、積層コンデンサ10をデカップリング及び電源供給路用途に用いる場合は、上端の外部電極60、61と下端の外部電極70、71の間に大きな電流を流すことができる。さらに、全貫通型のビア導体40、41、50、51を用いれば、良好な熱伝導性を保つことができる。

【0024】

次に、図1の積層コンデンサ10において、各内部電極層30〜33の具体的な導体パターンについて図3及び図4を参照して説明する。図3(A)は、第1領域R1の第1電位用の内部電極層30の導体パターンを示している。図3(A)に示すように、図2の配置と同様、4隅の4本のビア導体40、41(第1ビア導体群)と、それ以外の32本のビア導体50、51(第2ビア導体群)がアレイ状に配置されている。それぞれのビア導体40、41、50、51は、いずれもビア径D1を有する。そして、第1電位用の2本のビア導体40及び第1電位用の16本のビア導体50は、同極である内部電極層30と電気的に接続されている。これに対し、第2電位用の2本のビア導体41及び第2電位用の16本のビア導体51のそれぞれの周囲にはクリアランスホールCHが形成され、異極である内部電極層30と絶縁されている。それぞれのクリアランスホールCHは、クリアランス径C1(直径)の円形の形状を有する。

【0025】

また、図3(B)は、第1領域R1の第2電位用の内部電極層31の導体パターンを示している。図3(B)におけるビア導体40、41、50、51の配置、及びそれぞれのビア径D1については、図3(A)と同様である。第2電位用の2本のビア導体41及び第2電位用の16本のビア導体51は、同極である内部電極層31と電気的に接続されている。これに対し、第1電位用の2本のビア導体40及び第1電位用の16本のビア導体50のそれぞれの周囲には、図3(A)と同様のクリアランス径C1で円形のクリアランスホールCHが形成され、異極である内部電極層31と絶縁されている。

【0026】

なお、図3において、ビア導体40、41、50、51のビア径D1は、例えば、0.08〜0.12mm程度に設定される。また、ビア導体40、41、50、51の各クリアランスホールCHのクリアランス径C1は、例えば、0.3〜0.4mm程度に設定される。

【0027】

次に図4(A)は、第2領域R2の第1電位用の内部電極層32の導体パターンを示している。図4(A)に示すように、図3の配置と同様、4隅の4本のビア導体40、41(第1ビア導体群)と、それ以外の32本のビア導体50、51(第2ビア導体群)がアレイ状に配置されている。第1ビア導体群の各ビア導体40、41は図3と同様のビア径D1を有するのに対し、第2ビア導体群の各ビア導体50、51は、ビア径D1より小さいビア径D2を有する。そして、第1電位用の2本のビア導体40は、同極である内部電極層32と電気的に接続されている。これに対し、第2電位用の2本のビア導体41の周囲には、図3と同様のクリアランス径C1で円形のクリアランスホールCHが形成され、異極である内部電極層32と絶縁されている。また、第1電位用の16本のビア導体50の周囲には、クリアランス径C2で円形のクリアランスホールCHが形成され、同極である内部電極層32と絶縁されている。さらに、第2電位用の16本のビア導体51の周囲には、クリアランス径C3で円形のクリアランスホールCHが形成され、異極である内部電極層32と絶縁されている。

【0028】

また、図4(B)は、第2領域R2の第2電位用の内部電極層33の導体パターンを示している。図4(B)におけるビア導体40、41、50、51の配置、及びそれぞれのビア径D1、D2については、図4(A)と同様である。第2電位用の2本のビア導体41は、同極である内部電極層33と電気的に接続されている。これに対し、第1電位用の2本のビア導体40の周囲には、図4(A)と同様のクリアランス径C1で円形のクリアランスホールCHが形成され、異極である内部電極層33と絶縁されている。また、第2電位用の16本のビア導体51の周囲には、図4(A)と同様のクリアランス径C2で円形のクリアランスホールCHが形成され、同極である内部電極層33と絶縁されている。さらに、第1電位用の16本のビア導体50の周囲には、図4(A)と同様のクリアランス径C3で円形のクリアランスホールCHが形成され、異極である内部電極層33と絶縁されている。

【0029】

なお、図4において、ビア導体50、51のビア径D2は、例えば、0.04〜0.08mm程度に設定される。また、ビア導体50、51の各クリアランスホールCHに関し、クリアランス径C2は、例えば、0.21〜0.33mm程度に設定され、クリアランス径C3は、例えば、0.24〜0.36mm程度に設定される。ビア導体40、41のビア径D1及びクリアランス径C1については、上述した通りである。

【0030】

以上のように、第2領域R2においてビア導体50、51のビア径D2を小さく設定したことにより、クリアランス径C2、C3をそれほど大きくしなくても、ビア導体50、51と内部電極層32、33との間の絶縁を確実に確保することができる。仮に、第2領域R2においてビア径D2がビア径D1と同じ値である場合は内部電極層32、33との絶縁確保のためにクリアランス径C2、C3を大きくせざるを得ない。よって、内部電極層32、33の対向面積が小さくなり、その分だけ第2領域R2の容量値が小さくなるが、本実施形態においてはクリアランス径C2、C3を小さくすることで内部電極層32、33の対向面積を確保して第2領域R2の容量値を大きくすることができる。

【0031】

図4において、第2ビア導体群に対し同極側のクリアランス径C2と異極側のクリアランス径C3は、C2<C3の関係を満たしているが、これは、同極側については部分的に接触したときに第2領域R2のインダクタンス値の誤差の要因となるだけであるのに対し、異極側については電気的ショートによって積層コンデンサ10として機能しなくなる事態を防止する観点から十分なマージンを取ったものである。一方、第2領域R2におけるクリアランスホールCHの部分が積層方向で重なり、導体パターンの有無による粗密差が生じるが、上記のように同極側と異極側でクリアランス径C2、C3を異ならせることにより、粗密差を緩和する効果がある。これにより、積層コンデンサ10の反り等の変形を抑制することができる。

【0032】

以上、図1〜図4に示した積層コンデンサ10は一例であって、基本構造を有する限り、寸法パラメータや配置等については多様な変更が可能である。例えば、実際の積層コンデンサ10では、内部電極層30〜33の積層数やビア導体40、41、50、51の本数をより増加させることができる。また、各クリアランスホールCHのクリアランス径C1、C2、C3は、本発明の特徴を損わない限り、適宜に変更可能である。さらに、図1においては、第1領域R1と第2領域R2とに挟まれた中間領域RCを示しているが、第1領域R1の内部電極層30、31と第2領域R2の内部電極層32、33との間を広く確保する必要がなければ、中間領域RCは設けなくてもよい。

【0033】

以下の表1は、本実施形態の積層コンデンサ10に関し、所定の設計条件の下で得られた特性例を示している。すなわち、方形の積層コンデンサ10のサイズを平面視で18.6mm×18.6mmに設定し、ビア導体40、41、50、51の本数を全部で1000本とし、そのうち4隅にはビア導体40、41を2本ずつ配置するとともに、内部電極層30〜33の積層数を全部で110層とし、そのうち第1領域R1と第2領域R2の積増数をそれぞれ55層とした。このような条件の下、第1領域R1及び第2領域R2において、それぞれの容量及び等価直列インダクタンス(ESL)として、表1に示す評価結果が得られた。

【0034】

【表1】

【0035】

このように、等価直列インダクタタンスに関しては、接続されるビア導体の本数の相違を反映して、第1領域R1に比べて第2領域R2の方が十分に大きな値を得られることが確認された。また、容量に関しては、主に内部電極層30〜33の面積の若干の相違(クリアランス径の相違)を反映して、第1領域R1に比べて第2領域R2の方が大きな値を得られることが確認された。従って、表1の結果から、積層コンデンサ10の特性として、自己共振周波数f0が大きく異なる2つの特性を含む広帯域の周波数特性を実現することができる。このように、第1領域R1と第2領域R2との周波数特性の違いは、両者の等価直列インダクタタンスの違いが支配的であるが、両者の容量の違いも寄与していることがわかる。

【0036】

次に、本実施形態の積層コンデンサ10の応用例の一つとして、積層コンデンサ10を内蔵したコンデンサ内蔵配線基板について説明する。図5は、コンデンサ内蔵配線基板100(以下、単に配線基板100と呼ぶ)の概略の断面構造図を示している。図5に示すように、本実施形態の配線基板100は、コア材101と、コア材101の上面側のビルドアップ層102(積層部)と、コア材101の下面側のビルドアップ層103(積層部)とを含む構造を有している。本実施形態の配線基板100は、その内部に部品としての積層コンデンサ10が内蔵されるとともに、上部に半導体素子である半導体チップ200が載置されている。

【0037】

コア材101は、例えば、ガラス繊維を含んだエポキシ樹脂からなる。コア材101には、中央領域を貫通する収容穴部101aが形成され、この収容穴部101aに本実施形態の積層コンデンサ10が埋め込まれた状態で収容されている。コア材101には、外周領域を積層方向に貫通する複数のスルーホール導体111が形成され、スルーホール導体111の内部が例えばSiO2などのフィラー材を含有するエポキシ等からなる閉塞体112で埋められている。また、収容穴部101aと積層コンデンサ10の側面との間隙部には樹脂充填材110が充填されている。樹脂充填材110は、例えば熱硬化性樹脂からなり、コア材101に対する積層コンデンサ10の相対的な変形を吸収するように作用する。積層コンデンサ10の上側の各外部電極60、61(図1)は上方のビルドアップ層102と電気的に接続されるとともに、積層コンデンサ10の下側の各外部電極70、71(図1)は下方のビルドアップ層103と電気的に接続される。

【0038】

上方のビルドアップ層102は、コア材101の上部の樹脂絶縁層104と、樹脂絶縁層104の上部の樹脂絶縁層105と、樹脂絶縁層105の上部のソルダーレジスト層106とが積層形成された構造を有する。樹脂絶縁層104の上面には導体層121が形成され、樹脂絶縁層105の上面には複数の端子パッド123が形成されている。樹脂絶縁層104の所定箇所には、積層コンデンサ10の外部電極60、61と導体層121を積層方向に接続導通する複数のビア導体120が設けられている。また、樹脂絶縁層105の所定箇所には、導体層121と複数の端子パッド123を積層方向に接続導通する複数のビア導体122が設けられている。ソルダーレジスト層106は、複数箇所が開口されて複数の端子パッド123が露出し、そこに複数の半田バンプ124が形成されている。各々の半田バンプ124は、配線基板100に載置される半導体チップ200の各パッド201に接続される。

【0039】

下方のビルドアップ層103は、コア材101の下部の樹脂絶縁層107と、樹脂絶縁層107の下部の樹脂絶縁層108と、樹脂絶縁層108の下部のソルダーレジスト層109とが積層形成された構造を有する。樹脂絶縁層107の下面には導体層131が形成され、樹脂絶縁層108の下面には複数のBGA用パッド133が形成されている。樹脂絶縁層107の所定箇所には、積層コンデンサ10の外部電極70、71と導体層131を積層方向に接続導通する複数のビア導体130が設けられている。また、樹脂絶縁層108の所定箇所には、導体層131と複数のBGA用パッド133を積層方向に接続導通する複数のビア導体132が設けられている。ソルダーレジスト層109は、複数箇所が開口されて複数のBGA用パッド133が露出し、そこに複数の半田ボール134が接続される。なお、配線基板100は、複数の半田ボール134を介して、図示されない外部基材と電気的に接続される。

【0040】

図5の配線基板100の断面構造において、積層コンデンサ10の上側では、半田バンプ124、端子パッド123、ビア導体122、導体層121、ビア導体120を経由して、半導体チップ200の所定のパッド201と積層コンデンサ10の外部電極60、61の間が電気的に接続される。同様に、積層コンデンサ10の下側では、ビア導体130、導体層131、ビア導体132、BGA用パッド133、半田ボール134を経由して、積層コンデンサ10の外部電極70、71と外部基材の所定の端子の間が電気的に接続される。そして、積層コンデンサ10を、半導体チップ200に供給される電源電圧のデカップリング用のコンデンサとして機能させる場合は、上記の経路により、積層コンデンサ10の正極を半導体チップ200の電源電圧用のパッド201に接続し、積層コンデンサ10の負極を半導体チップ200のグランド電位用のパッド201に接続すればよい。

【0041】

以下、本実施形態の積層コンデンサ10の製造方法の概略について説明する。まず、周知の手法に従って、セラミックグリーンシートを用意し、その表面に導体層となる導電性ペーストをスクリーン印刷により形成した状態で積層する。そして、かかる工程を繰り返すことにより、図6に示すように、セラミック誘電体層20、21、22となるべきセラミックグリーンシートと、内部電極層30、31、32、33となるべき導電性ペーストとが交互に積層された積層体10aが得られる。このように、本実施形態においては、積層コンデンサ10の第1領域R1と第2領域R2とを別々に作製する必要がない。

【0042】

次いで、積層体10aに対し、ビア導体40、41、50、51を形成するためのレーザ加工を施す。例えば、図7(A)に示すように、積層体10aの主面S1においてビア導体40、41、50、51の形成予定位置PVに対し、所定の順番でレーザの位置を順次移動させながら上方から下方にレーザ照射を行う。このとき、レーザのビーム径やショット数などの加工条件を適切に制御することにより、4隅のビア導体40、41に対応する貫通孔V1と、それ以外のビア導体50、51に対応する貫通孔V2とを順次形成する。

【0043】

一般に、レーザは図7(B)に示すようなパルス波形によって発振する。すなわち、パルス波形の1周期Tがレーザの1ショットを構成し、1ショット内にパルス幅PWの1つのパルスが含まれる。レーザ照射時のエネルギーは、パルス幅PWとレーザ出力の積に比例する。また、レーザビームの焦点を調節することにより、ビーム径を変更することができる。そして、図7(B)の1ショット毎に各々の形成予定位置PVを変更し、それを所定のショット数に達するまで周期的に繰り返すことにより(サイクル加工)、貫通孔V1、V2を徐々に深くすることができる。

【0044】

また、図8に示すように、第1領域R1では貫通孔V1、V2が共通のビア径D1(図3)となるように同一のビーム径でレーザ加工を制御するとともに、第2領域R2では貫通孔V1、V2が異なるビア径D1、D2(図4)となるように異なるビーム径でレーザ加工を制御する。すなわち、ビア導体40、41に対応する貫通孔V1はビア径D1が固定であるため、全てのショットで同一のビーム径を維持する一方、ビア導体50、51に対応する貫通孔V2はビア径D1からビア径D2に細くなるので、図8の中間領域RCの境界位置に対応する所定のショット数に達したときにビーム径を減少させればよい。これにより、積層体10aには、図8に示す断面形状を有する貫通孔V1、V2を形成することができる。ただし、上記の説明では積層体10aの一方の主面S1の側からレーザ照射を行う場合を説明したが、これに限らず、積層体10aの両方の主面S1、S2の側からレーザ照射を行ってもよい。この場合、貫通孔V2については、上方からのレーザ照射でビア径D1に対応する広いビーム径とし、下方からのレーザ照射でビア径D2に対応する細いビーム径として、それぞれのレーザ加工を制御すればよい。

【0045】

次いで、図1に示すように、図8の貫通孔V1、V2のそれぞれの内部に導電性ペーストを充填する。これにより、貫通孔V1、V2内の導電性ペーストがそれぞれ対応する内部電極層30〜33に接続される。また、それぞれの貫通孔V1、V2の上端側の外部電極60、61となる導電性ペーストがスクリーン印刷により形成されるとともに、それぞれの貫通孔V1、V2の下端側の外部電極70、71となる導電性ペーストがスクリーン印刷により形成される。その後、積層体10aを乾燥させ、所定の条件で同時焼成することにより焼成積層体を形成する。これにより、各層のセラミックグリーンシートが焼結し、内部電極層30〜33、ビア導体40、41、50、51、外部電極60、61、70、71にそれぞれ含まれる導電性ペースト中の成分が焼結してセラミック焼結体となる。以上のようにして、図1の構造を有する積層コンデンサ10が得られる。

【0046】

本実施形態の積層コンデンサ10は、上記の製造方法によって説明したように、第1領域R1と第2領域R2とを別々に作製することは必要なく、一体的なコンデンサ本体部として作製することができる。よって、周波数特性が異なる2つのコンデンサ本体部を作製するための複雑な工程が不要となるし、個々の領域に半貫通型のビア導体を形成する必要もない。従って、本実施形態の積層コンデンサ10の構造を採用することにより、製造工程を簡素化して製造コストを低減する効果がある。また、本実施形態の積層コンデンサ10は、ビア導体40、41、50、51の接続本数とビア径を調節することで、所望の周波数特性を容易に実現することができる。

【0047】

本実施形態の積層コンデンサ10に関しては、上述の製造方法に限らず多様な変形例がある。図9は、上述の製造方法とは貫通孔V1、V2の形成方法が異なる場合の図1に対応する断面構造図を示している。具体的には、図9の断面構造においては、第2ビア導体群であるビア導体50、51が第1領域R1では図1と同様のビア径D1で形成されるが、第2領域R2ではテーパ状に変化する。すなわち、第1領域R1の上部から第2領域R2の下部にかけて、ビア導体50、51のビア径が徐々に細くなっていくことがわかる。通常、レーザ加工は、その特性上、照射側の近傍から遠方にかけて貫通孔の径が細くなる傾向があり、第1領域R1で各ビア導体40、41、50、51は、実際には僅かにテーパ状になっている。しかし、ビア導体40、41及び第1領域R1のビア導体50、51は、レーザ照射の際に融点が低い内部電極層30〜33の領域を含めて開口するのに対し、内部電極層32、33に接続されない第2領域R2のビア導体50、51は、融点が高いセラミックの領域のみを開口することになり、他の部分と比べてテーパの形状が顕著になる。このように、図9に示すようなテーパ状のビア導体50、51を有する場合であっても、第1領域R1に比べて第2領域R2のビア径が細いため、本実施形態の積層コンデンサ10の効果を得ることができる。

【0048】

以上、本実施形態に基づき本発明の内容を具体的に説明したが、本発明は上述の実施形態に限定されるものではなく、その要旨を逸脱しない範囲で多様な変更を施すことができる。例えば、本実施形態では、積層コンデンサ10のコンデンサ本体部が、互いに等価直列インダクタンスが異なる第1領域R1と第2領域R2を含む場合を説明したが、これに限らず、互いに等価直列インダクタンスが異なる3つ以上の領域を複合化して積層コンデンサ10を構成してもよい。この場合、3つ以上の領域におけるビア導体との接続本数やビア径を適切に設定することにより、より広帯域の周波数特性を有する積層コンデンサを実現可能となる。さらに、その他の点についても上記実施形態により本発明の内容が限定されるものではなく、本発明の作用効果を得られる限り、上記実施形態に開示した内容には限定されることなく適宜に変更可能である。

【符号の説明】

【0049】

10…積層コンデンサ

20、21、22…セラミック誘電体層

30、31、32、33…内部電極層

40、41、50、51…ビア導体

60、61、70、71…外部電極

100…コンデンサ内蔵配線基板

R1…第1領域

R2…第2領域

RC…中間領域

CH…クリアランスホール

【特許請求の範囲】

【請求項1】

誘電体層と内部電極層とを交互に積層してなるコンデンサ本体部と、アレイ状に配置され前記コンデンサ本体部を積層方向に貫通する複数のビア導体と、前記複数のビア導体のそれぞれの両端部に接続される複数の外部電極と、を備えた積層コンデンサにおいて、

前記複数のビア導体は、

前記コンデンサ本体部の一方の主面側の第1領域及び他方の主面側の第2領域における前記内部電極層と電気的に接続された第1ビア導体群と、

前記第1領域における前記内部電極層と電気的に接続され、かつ前記第2領域における前記内部電極層と電気的に接続されない第2ビア導体群と、

を含み

前記第2ビア導体群は、前記第2領域におけるビア径が前記第1領域におけるビア径よりも小さくなるように形成されていることを特徴とする積層コンデンサ。

【請求項2】

前記複数の外部電極は、互いに異なる電位に接続される第1外部電極と第2外部電極とに区分され、

前記第1領域及び前記第2領域において、前記第1外部電極と前記ビア導体を介して電気的に接続される前記内部導体層と、前記第2外部電極と前記ビア導体を介して電気的に接続される前記内部導体層とが積層方向で交互に配置されることを特徴とする請求項1に記載の積層コンデンサ。

【請求項3】

前記第1領域における等価直列インダクタンスが前記第2領域における等価直列インダクタンスよりも小さいことを特徴とする請求項1又は2に記載の積層コンデンサ。

【請求項4】

前記第1ビア導体群は、平面視で前記コンデンサ本体部の外周側に配置され、前記第2ビア導体群は、平面視で前記コンデンサ本体部の内周側に配置されているビア導体を含むことを特徴とする請求項1から3のいずれか一項に記載の積層コンデンサ。

【請求項5】

前記コンデンサ本体部は平面視で矩形に形成され、前記第1ビア導体群は前記矩形のそれぞれの角部に配置されていることを特徴とする請求項4に記載の積層コンデンサ。

【請求項6】

前記第2ビア導体群は、前記第2領域における前記内部電極層との面方向の間隔が、前記第1領域における異極側の前記内部電極層との面方向の間隔よりも小さく設定されていることを特徴とする請求項1から5のいずれか一項に記載の積層コンデンサ。

【請求項7】

前記第2ビア導体群は、前記第2領域における同極側の前記内部電極層との面方向の間隔が、前記第2領域における異極側の前記内部電極層との面方向の間隔よりも小さく設定されていることを特徴とする請求項6に記載の積層コンデンサ

【請求項8】

請求項1から7のいずれか一項に記載の積層コンデンサを内蔵したことを特徴とするコンデンサ内蔵配線基板。

【請求項9】

前記積層コンデンサに接続される電源供給路を介して電源が供給される素子をさらに備え、当該素子は前記第1領域の近傍側の表面に配置されることを特徴とする請求項8に記載のコンデンサ内蔵配線基板。

【請求項1】

誘電体層と内部電極層とを交互に積層してなるコンデンサ本体部と、アレイ状に配置され前記コンデンサ本体部を積層方向に貫通する複数のビア導体と、前記複数のビア導体のそれぞれの両端部に接続される複数の外部電極と、を備えた積層コンデンサにおいて、

前記複数のビア導体は、

前記コンデンサ本体部の一方の主面側の第1領域及び他方の主面側の第2領域における前記内部電極層と電気的に接続された第1ビア導体群と、

前記第1領域における前記内部電極層と電気的に接続され、かつ前記第2領域における前記内部電極層と電気的に接続されない第2ビア導体群と、

を含み

前記第2ビア導体群は、前記第2領域におけるビア径が前記第1領域におけるビア径よりも小さくなるように形成されていることを特徴とする積層コンデンサ。

【請求項2】

前記複数の外部電極は、互いに異なる電位に接続される第1外部電極と第2外部電極とに区分され、

前記第1領域及び前記第2領域において、前記第1外部電極と前記ビア導体を介して電気的に接続される前記内部導体層と、前記第2外部電極と前記ビア導体を介して電気的に接続される前記内部導体層とが積層方向で交互に配置されることを特徴とする請求項1に記載の積層コンデンサ。

【請求項3】

前記第1領域における等価直列インダクタンスが前記第2領域における等価直列インダクタンスよりも小さいことを特徴とする請求項1又は2に記載の積層コンデンサ。

【請求項4】

前記第1ビア導体群は、平面視で前記コンデンサ本体部の外周側に配置され、前記第2ビア導体群は、平面視で前記コンデンサ本体部の内周側に配置されているビア導体を含むことを特徴とする請求項1から3のいずれか一項に記載の積層コンデンサ。

【請求項5】

前記コンデンサ本体部は平面視で矩形に形成され、前記第1ビア導体群は前記矩形のそれぞれの角部に配置されていることを特徴とする請求項4に記載の積層コンデンサ。

【請求項6】

前記第2ビア導体群は、前記第2領域における前記内部電極層との面方向の間隔が、前記第1領域における異極側の前記内部電極層との面方向の間隔よりも小さく設定されていることを特徴とする請求項1から5のいずれか一項に記載の積層コンデンサ。

【請求項7】

前記第2ビア導体群は、前記第2領域における同極側の前記内部電極層との面方向の間隔が、前記第2領域における異極側の前記内部電極層との面方向の間隔よりも小さく設定されていることを特徴とする請求項6に記載の積層コンデンサ

【請求項8】

請求項1から7のいずれか一項に記載の積層コンデンサを内蔵したことを特徴とするコンデンサ内蔵配線基板。

【請求項9】

前記積層コンデンサに接続される電源供給路を介して電源が供給される素子をさらに備え、当該素子は前記第1領域の近傍側の表面に配置されることを特徴とする請求項8に記載のコンデンサ内蔵配線基板。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【公開番号】特開2013−42083(P2013−42083A)

【公開日】平成25年2月28日(2013.2.28)

【国際特許分類】

【出願番号】特願2011−179680(P2011−179680)

【出願日】平成23年8月19日(2011.8.19)

【出願人】(000004547)日本特殊陶業株式会社 (2,912)

【Fターム(参考)】

【公開日】平成25年2月28日(2013.2.28)

【国際特許分類】

【出願日】平成23年8月19日(2011.8.19)

【出願人】(000004547)日本特殊陶業株式会社 (2,912)

【Fターム(参考)】

[ Back to top ]