積層コンデンサ

【課題】設計の自由度が高く、経済的で、構造欠陥が発生しにくい、低ESL化が図られた積層コンデンサを提供する。

【解決手段】第1および第2の内部電極42および43の各々の引出し部52および53、ならびに第3および第4の内部電極44および45の各々の引出し部54および55を、側面36,37の長さ方向に関して交互に露出するように配置する。第1および第3の内部電極ならびに第2および第4の内部電極43および45の各々を、好ましくは、同一面内において、側面36,37の長さ方向に並びかつ互いの間に所定の間隔を隔てて配置する。誘電体層32の積層方向で見たとき、第1および第4の内部電極42および45の各々の容量形成部48および51が重なり合わず、第2および第3の内部電極43および44の各々の容量形成部49および50が重なり合わない。

【解決手段】第1および第2の内部電極42および43の各々の引出し部52および53、ならびに第3および第4の内部電極44および45の各々の引出し部54および55を、側面36,37の長さ方向に関して交互に露出するように配置する。第1および第3の内部電極ならびに第2および第4の内部電極43および45の各々を、好ましくは、同一面内において、側面36,37の長さ方向に並びかつ互いの間に所定の間隔を隔てて配置する。誘電体層32の積層方向で見たとき、第1および第4の内部電極42および45の各々の容量形成部48および51が重なり合わず、第2および第3の内部電極43および44の各々の容量形成部49および50が重なり合わない。

【発明の詳細な説明】

【技術分野】

【0001】

この発明は、積層コンデンサに関するもので、特に、等価直列インダクタンス(ESL)を低減するために多端子タイプとされた積層コンデンサに関するものである。

【背景技術】

【0002】

電源回路においては、電源ラインやグラウンドに存在するインピーダンスによって、電源ラインでの電圧変動が大きくなると、駆動する回路の動作が不安定になったり、電源回路を経由して回路間の干渉が起こったり、発振を起こしたりする。そこで、通常、電源ラインとグラウンドとの間には、デカップリングコンデンサが接続されている。デカップリングコンデンサは、電源ラインとグラウンドとの間のインピーダンスを低減し、電源電圧の変動や回路間の干渉を抑える役割を果たしている。

【0003】

さて、近年、携帯電話などの通信機器やパーソナルコンピュータなどの情報処理機器では、大量の情報を処理するために信号の高速化が進んでおり、使用されるICのクロック周波数も高周波化が進んでいる。このため、高調波成分を多く含むノイズが発生しやすくなり、IC電源回路においては、より強力なデカップリングを施す必要がある。

【0004】

デカップリング効果を高めるためには、インピーダンス周波数特性の優れたコンデンサを用いることが有効であり、これに適したコンデンサとしては、積層コンデンサが挙げられる。積層コンデンサは、ESLが小さいため、電解コンデンサに比べて、広い周波数帯域にわたってノイズ吸収効果に優れている。

【0005】

通常、ICのデッカプリングコンデンサとして用いられる積層コンデンサは、ICの近傍に配置される。これは、電源ラインに電圧変動が生じた際、コンデンサからICに迅速に電荷を供給し、ICの立ち上がりが遅れるのを防止するためである。

【0006】

しかし、コンデンサに充放電が起こるとき、コンデンサには、式:dV=L・di/dtで表わされる逆起電力dVが生じ、dVが大きいとICへの電荷の供給が遅くなってしまう。ICのクロック周波数が高周波化する中で、時間当たりの電流変動量di/dtは大きくなる傾向にある。すなわち、dVを小さくするためには、インダクタンスLを小さくする必要がある。Lには、ICの電源ピンからコンデンサまでのパターンのインダクタンスと、コンデンサからグラウンドまでのパターンのインダクタンスと、コンデンサ内部のESLとが含まれるが、回路の設計上、パターンのインダクタンスを下げることには制約がある。このため、コンデンサのESLをより低減できることが望まれている。

【0007】

そこで、ESLがより低減された積層コンデンサとして、特開2002−151349号公報(特許文献1)、特開2004−103883号公報(特許文献2)および特開2006−32904号公報(特許文献3)に記載されたものが提案されている。

【0008】

図13ないし図16は、積層コンデンサの内部構造を、内部電極が通る断面をもって示す平面図であるが、特許文献1に記載されたものが図13に、特許文献2に記載されたものが図14に、特許文献3に記載されたものが図15および図16にそれぞれ示されている。

【0009】

図13ないし図16において、共通して、積層された複数の誘電体層1をもって形成され、かつ相対向する第1および第2の側面2および3ならびに相対向する第3および第4の側面4および5を有する、直方体状の積層体6が図示されている。また、図13ないし図16において、電流の流れの一例が破線の矢印で示されている。

【0010】

まず、図13を参照して、特許文献1では、積層体6の相対向する第1および第2の側面2および3上に合計8個の外部端子電極7が形成された、多端子タイプの積層コンデンサ8が開示されている。この積層コンデンサ8では、第1の側面2に引き出された内部電極9が、第1の側面2と対向する第2の側面3に引き出された内部電極10と面内で対向するように配置されていて、同様に、内部電極11が内部電極12と面内で対向するように配置されている。このような構造によれば、内部電極9〜12を流れる電流が対向部分において逆向きとなり、それによって、電流のまわりに発生する磁界が相殺され、積層コンデンサ8のESLが低減する。

【0011】

次に、図14を参照して、特許文献2では、積層体6の第1ないし第4の側面2〜5に合計8個の外部端子電極13が形成された、多端子タイプの積層コンデンサ14が開示されている。この積層コンデンサ14では、同一面内で対向するようにそれぞれ配置された内部電極15、16および17ならびに内部電極18、19および20は、積層体6の相対向する第1および第2の側面2および3に互い違いに引き出されている。また、内部電極15〜17および内部電極18〜20は、共通の内部電極21および22と積層方向に対向して容量を形成しており、これら共通の内部電極21および22は、それぞれ、積層体6の相対向する第3および第4の側面4および5に引き出されている。このような構造によれば、内部電極15〜20をそれぞれ流れる電流が、対向部分において逆向きとなることにより、電流のまわりに発生する磁界が相殺され、積層コンデンサ14のESLが低減する。

【0012】

次に、特許文献3では、種々の多端子タイプの積層コンデンサが開示されているが、たとえば、図15に示すように、積層体6の相対向する第1および第2の側面2および3上に合計8個の外部端子電極23が形成された、多端子タイプの積層コンデンサ24が開示されている。この積層コンデンサ24では、それぞれ面内で対向するコの字状の内部電極25および26ならびに内部電極27および28の各々において、対向部分で電流が逆向きになることにより、電流のまわりに発生する磁界が相殺され、積層コンデンサ24のESLが低減する。

【0013】

特許文献3では、また、図16に示すような多端子タイプの積層コンデンサ24aも開示されている。この積層コンデンサ24aでは、積層方向に対向する内部電極25aおよび26aと内部電極27aおよび28aにおいて、対向部分での電流の向きを直交方向とすることにより、電流のまわりに発生する磁界が弱まり、積層コンデンサ24aのESLが低減する。

【0014】

しかしながら、上述した特許文献1ないし3の各々に記載された構造には、以下のように、解決されるべき課題がある。

【0015】

特許文献1に記載された構造では、内部電極9および10の互いに対向する端縁の長さ、あるいは、内部電極11および12の互いに対向する端縁の長さが、内部電極9および12の各々の引出し部間の距離すなわち外部端子電極7間のピッチに左右される。外部端子電極7間のピッチについては、短絡の問題を考慮して、一定以上の距離を確保しようとする一方、積層コンデンサ8の小型化を考慮して、一定以下の距離まで短縮しようとする。このため、実際の設計上、外部端子電極7間のピッチには制約があり、その結果、内部電極9および10あるいは内部電極11および12の互いに対向する端縁の長さについても制約が課せられる。したがって、上述の対向端縁の長さを調整することによって、電流経路の長さを調整するという方法を単純には採用することができず、積層コンデンサ8の等価直列抵抗(ESR)を調整することが必ずしも容易ではない。

【0016】

上述したESRは、電源回路の安定化に影響を及ぼすものである。すなわち、低ESL化が図られた積層コンデンサにおいては、多端子化に伴い、内部電極の引出し部の数が増え、その結果、ESRが低くなる傾向がある。ESRが低すぎる場合には、周辺回路のインダクタンスによって共振現象を招いたとき、電源電圧が大きく落ち込んだり、あるいはリンギングなどの減衰振動を起こしたりしやすくなるという問題がある。そのため、ESRについては、ある程度高くする要求があるが、特許文献1に記載の構造では、前述したように、このようなESRの調整が必ずしも容易ではない。

【0017】

また、特許文献1に記載の構造では、2つの独立したコンデンサ部が形成されるが、コンデンサ部の数を増やそうとした場合、積層体6の幅方向すなわち第3および第4の側面4および5の延びる方向に新たなコンデンサ部を追加することはできない。したがって、積層体6の長手方向すなわち第1および第2の側面2および3の延びる方向に新たなコンデンサ部を追加することになるが、この場合、図示した内部電極9〜12と同様に対向する1対以上の内部電極を形成することとなり、コンデンサ部は2の倍数で増加し、外部端子電極7の数は長手方向に4の倍数で増加することとなる。このため、設計の自由度が低いばかりでなく、コンデンサ部を追加しようとする際に、積層体6が長細くなりすぎて、積層体6の抗折強度が低くなってしまうという問題に遭遇する。

【0018】

次に、特許文献2に記載された構造では、内部電極15〜17または内部電極18〜20と共通に対向する内部電極21および22については、容量形成に寄与しない部分が存在しており、このような容量形成の観点から見た場合には、電極材料に無駄が生じていると言える。また、共通の内部電極21および22の各々を界面に位置させる隣り合う誘電体層1同士の接合面積が小さくなるため、積層体6においてデラミネーションなどの構造欠陥が発生しやすいという問題もある。さらに、共通の内部電極21および22については、内部電極15〜20を引き出した第1および第2の側面2および3とは異なる第3および第4の側面4および5に引き出していることから、外部端子電極13を必ず4つの側面2〜5の各々に形成する必要があり、設計の自由度が低いという問題もある。

【0019】

次に、特許文献3に記載の構造であって、図15に示した積層コンデンサ24については、前述の特許文献1に記載の構造と同様の問題を有している。また、図16に示した積層コンデンサ24aについては、特許文献2の場合と同様、内部電極25a〜28aが容量形成に寄与しない部分を備えており、容量形成の観点から見たとき、電極材料の無駄があるという問題を有している。また、特許文献3に記載の構造では、特許文献2の場合と同様、内部電極25〜28または25a〜28aの各々を界面に位置させる隣り合う誘電体層1同士の接合面積が小さくなり、積層体6にデラミネーションなどの構造欠陥が発生しやすいという問題もある。

【特許文献1】特開2002−151349号公報(特に、図3、図6および図8)

【特許文献2】特開2004−103883号公報(特に、図1)

【特許文献3】特開2006−32904号公報(特に、図4、図7および図13)

【発明の開示】

【発明が解決しようとする課題】

【0020】

そこで、この発明の目的は、設計の自由度が高く、電極材料に関して経済的であり、構造欠陥が発生しにくい、多端子タイプの積層コンデンサを提供しようとすることである。

【課題を解決するための手段】

【0021】

この発明に係る積層コンデンサは、積層された複数の誘電体層をもって構成され、かつ相対向する第1および第2の側面を有する、直方体状の積層体と、第1および第2の側面上に形成される、複数の外部端子電極とを備える。積層体の内部には、第1のコンデンサ部を形成するため、第1および第2の内部電極が形成されるとともに、第2のコンデンサ部を形成するため、第3および第4の内部電極が形成される。

【0022】

第1および第2の内部電極は、それぞれ、特定の誘電体層を介して互いに対向する容量形成部と、容量形成部から第1および第2の側面に露出するように引き出されて特定の外部端子電極に電気的に接続される2つ以上の引出し部とを有し、第1の内部電極の引出し部と第2の内部電極の引出し部とは、第1および第2の側面の長さ方向に関して交互に露出するように配置される。

【0023】

第3および第4の内部電極は、それぞれ、特定の誘電体層を介して互いに対向する容量形成部と、容量形成部から第1および第2の側面に露出するように引き出されて特定の外部端子電極に電気的に接続される2つ以上の引出し部とを有し、第3の内部電極の引出し部と第4の内部電極の引出し部とは、第1および第2の側面の長さ方向に関して交互に露出するように配置される。

【0024】

第1および第3の内部電極は、第1および第2の側面の長さ方向に並びながら、互いの間に所定の間隔を隔てて配置される。第2および第4の内部電極は、第1および第2の側面の長さ方向に並びながら、互いの間に所定の間隔を隔てて配置される。

【0025】

そして、誘電体層の積層方向で見たとき、第1の内部電極の容量形成部と第4の内部電極の容量形成部とは重なり合わず、第2の内部電極の容量形成部と第3の内部電極の容量形成部とは重なり合わないようにされる。

【0026】

この発明に係る積層コンデンサにおいて、第1および第2の側面の長さ方向に関して、第1の内部電極の引出し部と第3の内部電極の引出し部とが隣り合い、かつ、第2の内部電極の引出し部と第4の内部電極の引出し部とが隣り合うように配置されることが好ましい。

【0027】

また、この発明に係る積層コンデンサにおいて、第1および第3の内部電極は同一面内に位置され、かつ、第2および第4の内部電極は同一面内に位置されることが好ましい。

【0028】

上述の場合、第1および第2の内部電極は積層方向に複数組配置され、複数の第1の内部電極のうちの一部については、同一面内に、第3の内部電極を位置させておらず、複数の第2の内部電極のうちの一部については、同一面内に、第4の内部電極を位置させていなくてもよい。

【0029】

なお、この発明に係る積層コンデンサにおいて、第1および第3の内部電極は積層方向にずれて位置され、かつ、第2および第4の内部電極は積層方向にずれて位置されていてもよい。

【0030】

また、第1および第2の内部電極の各々の容量形成部の面積と第3および第4の内部電極の各々の容量形成部の面積とは互いに異なっていてもよい。この場合、面積がより広い方の容量形成部を有する内部電極の引出し部の数は、面積がより狭い方の容量形成部を有する内部電極の引出し部の数より多くてもよい。

【0031】

この発明に係る積層コンデンサは、積層体の内部に、第3のコンデンサ部を形成するため、第5および第6の内部電極をさらに備えていてもよい。この場合、第5および第6の内部電極は、それぞれ、特定の誘電体層を介して互いに対向する容量形成部と、容量形成部から第1および第2の側面に露出するように引き出されて特定の外部端子電極に電気的に接続される2つ以上の引出し部とを有し、第5の内部電極の引出し部と第6の内部電極の引出し部とは、第1および第2の側面の長さ方向に関して交互に露出するように配置され、第1、第3および第5の内部電極は、第1および第2の側面の長さ方向に並びながら、互いの間に所定の間隔を隔てて配置され、第2、第4および第6の内部電極は、第1および第2の側面の長さ方向に並びながら、互いの間に所定の間隔を隔てて配置され、誘電体層の積層方向で見たとき、第5の内部電極の容量形成部は第2および第4の内部電極のいずれの容量形成部とも重なり合わず、第6の内部電極の容量形成部は第1および第3の内部電極のいずれの容量形成部とも重なり合わないようにされる。

【発明の効果】

【0032】

この発明によれば、第1ないし第4の内部電極の各々が、容量形成部から第1および第2の側面に露出するように引き出されて特定の外部端子電極に電気的に接続される2つ以上の引出し部を有し、また、第1および第3の内部電極が、第1および第2の側面の長さ方向に並びながら、互いの間に所定の間隔を隔てて配置され、第2および第4の内部電極が、第1および第2の側面の長さの方向に並びながら、互いの間に所定の間隔を隔てて配置されている。

【0033】

したがって、外部端子電極間のピッチの制約を受けず、第1および第3の内部電極が互いに対向する端縁の長さ、ならびに第2および第4の内部電極が互いに対向する端縁の長さを調整することが可能となる。これにより、電流経路を長くしたり短くしたりすることが比較的自由にできるため、たとえば、積層コンデンサのESRを任意に制御することが可能となる。

【0034】

また、第1および第2のコンデンサ部以外に、たとえば第3のコンデンサ部というように、コンデンサ部を追加しようとする場合には、第1および第2の側面の長さ方向に沿って、コンデンサ部を1つずつ追加することができる。よって、積層コンデンサの設計の自由度を高めることができる。

【0035】

また、この発明によれば、第1および第4の内部電極の各々の容量形成部同士は互いに重なり合わず、第2および第3の内部電極の各々の容量形成部同士は互いに重なり合わない。したがって、容量形成の観点から無駄となる部分が各内部電極に実質的に存在しないようにすることができるため、電極材料の無駄を抑えることができるばかりでなく、内部電極を互いの間の界面に位置させる隣り合う誘電体層同士の接合面積を確保して、積層体においてデラミネーションなどの構造欠陥を生じさせにくくすることができる。

【0036】

また、この発明によれば、各内部電極が2つ以上の引出し部を有していて、引出し部の各々の位置に関しては、第1の内部電極の引出し部と第2の内部電極の引出し部とが、第1および第2の側面の長さ方向に関して交互に露出するように配置され、第3の内部電極の第4の内部電極の引出し部とが、第1および第2の側面の長さ方向に関して交互に露出するように配置されているので、各内部電極上での電流の流れを種々の方向に向けることができるとともに、隣り合う引出し部での電流の流れを逆向きにすることができるので、磁界を効果的に相殺することができ、その結果、ESLを小さくすることができる。

【0037】

この発明に係る積層コンデンサにおいて、第1および第2の側面の長さ方向に関して、第1の内部電極の引出し部と第3の内部電極の引出し部とが隣り合い、かつ、第2の内部電極の引出し部と第4の内部電極の引出し部とが隣り合うように配置されると、磁界相殺の効果がより高くなる。

【0038】

この発明に係る積層コンデンサにおいて、第1および第3の内部電極が同一面内に位置され、かつ、第2および第4の内部電極が同一面内に位置されると、各々の組をなす内部電極が積層方向にずれて位置される場合に比べて、磁界を相殺する効果を高めることができる。

【0039】

上述の場合において、第1および第2の内部電極が積層方向に複数組配置され、複数の第1の内部電極の一部については、同一面内に、第3の内部電極を位置させておらず、複数の第2の内部電極のうちの一部については、同一面内に、第4の内部電極を位置させていない場合、第1のコンデンサ部に比べて第2のコンデンサ部の容量を小さくすることができる。このように、第1および第2のコンデンサ部間で容量を異ならせることにより、各コンデンサ部の共振周波数が変わるため、より広い周波数帯域においてデカップリングコンデンサとしての機能を実現することが可能となる。

【0040】

この発明において、第1および第2の内部電極の各々の容量形成部の面積と第3および第4の内部電極の各々の容量形成部の面積とが互いに異なっていると、第1および第2のコンデンサ部間で容量を異ならせることができる。したがって、上述の場合と同様、各コンデンサ部の共振周波数が変わるため、より広い周波数帯域においてデカップリングコンデンサとしての機能を実現することが可能となる。

【0041】

上述の実施態様において、面積がより広い方の容量形成部を有する内部電極の引出し部の数を、面積がより狭い方の容量形成部を有する内部電極の引出し部の数より多くすることにより、面積がより広い方の容量形成部を有する内部電極によって与えられるコンデンサ部におけるESLをより低減することができる。

【0042】

この発明において、第5および第6の内部電極が追加されることにより、第3のコンデンサ部が形成されると、たとえば、第1ないし第3のコンデンサ部の各々の容量を互いに異ならせることにより、より広い周波数帯域においてデカップリングコンデンサとしての機能を実現することが可能となる。

【発明を実施するための最良の形態】

【0043】

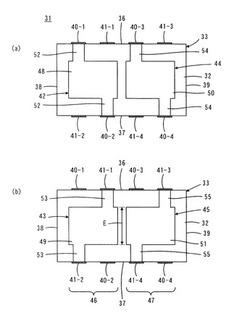

図1ないし図4は、この発明の第1の実施形態による積層コンデンサ31を説明するためのものである。ここで、図1は、積層コンデンサ31の外観を示す斜視図であり、図2は、積層コンデンサ31の外観を示す平面図である。図3は、積層コンデンサ31の内部構造を、いくつかの特定の断面をもって示す平面図である。図4は、図3と同様の図面であるが、電流の流れを示す破線の矢印を加えたものである。

【0044】

積層コンデンサ31は、積層された複数の誘電体層32をもって構成される、直方体状の積層体33を備えている。誘電体層32は、たとえば、BaTiO3、CaTiO3、SrTiO3、CaZrO3などを主成分とする誘電体セラミックから構成される。なお、これら主成分に、Mn化合物、Fe化合物、Cr化合物、Co化合物、Ni化合物などの副成分が添加されていてもよい。また、誘電体層32の厚みは、たとえば1〜10μmとされる。

【0045】

積層体33は、相対向する第1および第2の主面34および35と、第1および第2の主面34および35間を結ぶものであって、相対向する第1および第2の側面36および37ならびに相対向する第3および第4の側面38および39とを有している。ここで、誘電体層32は、主面34および35の方向に延び、側面36〜39は、誘電体層32の積層方向に延びている。また、第1および第2の側面36および37が誘電体層32の長辺に沿う位置にある。

【0046】

積層体33の第1および第2の側面36および37上には、複数の外部端子電極40および41が形成される。この実施形態では、第1の側面36上に4個の外部端子電極40および41が形成され、第2の側面37上に4個の外部端子電極40および41が形成される。また、外部端子電極40および41のうち、第1の外部端子電極40には第1の極性が割り当てられ、第2の外部端子電極41には第2の極性が割り当てられる。これら第1および第2の外部端子電極40および41は、交互に並ぶように配置される。

【0047】

なお、4個の第1の外部端子電極40の間で区別する必要があるときには、第1の外部端子電極について、「40−1」、「40−2」、「40−3」および「40−4」の参照符号を用い、他方、4個の第2の外部端子電極41の間で区別する必要があるときには、第2の外部端子電極について、「41−1」、「41−2」、「41−3」および「41−4」の参照符号を用いることにする。

【0048】

外部端子電極40および41の導電成分として、たとえば、Cu、Ni、Ag、Pd、Ag−Pd合金、またはAuなどを用いることができる。外部端子電極40および41は、通常、導電性ペーストを塗布し、焼成することによって形成されるが、この場合、導電性ペーストは、積層体33が未焼結状態にあるときに塗布され、後述する内部電極と同時焼成によって形成されても、積層体33を焼成した後に塗布され、再び焼成されることによって形成されてもよい。外部端子電極40および41の厚みは、最も厚い部分で20〜100μmであることが好ましい。

【0049】

外部端子電極40および41上には、必要に応じて、めっき膜が形成されてもよい。めっき膜を構成する金属としては、たとえば、Cu、Ni、Sn、Auなどを用いることができ、また、Ni−Sn、Ni−Au、Cu−Ni−Auなどの複数層からなるめっき膜を形成してもよい。めっき膜の1層当たりの厚みは、1〜10μmであることが好ましい。また、外部端子電極40とめっき膜との間に、応力緩和用の樹脂層が形成されていてもよい。また、外部端子電極40および41は、積層体33上に、直接、めっきを施すことにより形成されてもよい。

【0050】

積層体33の内部には、図3に示すように、第1ないし第4の内部電極42〜45が形成される。内部電極42〜45に含まれる導電成分としては、たとえば、Ni、Cu、Ag、Pd、Ag−Pd合金、またはAuなどを用いることができる。また、内部電極42〜45の各々の厚みは、0.5〜2.0μmであることが好ましい。

【0051】

第1および第2の内部電極42および43は、第1のコンデンサ部46を形成するためのものであり、第3および第4の内部電極44および45は第2のコンデンサ部47を形成するためのものである。なお、積層体33の積層方向での両端部には、いずれの内部電極もが形成されない誘電体層32が所定数積層される。また、図3(a)に示した内部電極42および44のパターンと同(b)に示した内部電極43および45のパターンとは、積層方向に複数回繰り返される。

【0052】

第1および第2の内部電極42および43は、それぞれ、特定の誘電体層32を介して互いに対向する容量形成部48および49を有している。また、第1の内部電極42は、容量形成部48から第1および第2の側面36および37に露出するように引き出されて外部端子電極40−1および40−2に電気的に接続される2つの引出し部52を有している。他方、第2の内部電極43は、容量形成部49から第1および第2の側面36および37に露出するように引き出されて外部端子電極41−1および41−2に電気的に接続される2つの引出し部53を有している。これら第1の内部電極42の引出し部52と第2の内部電極43の引出し部53とは、第1および第2の側面36および37の長さ方向に関して交互に露出するように配置されている。

【0053】

同様に、第3および第4の内部電極44および45は、それぞれ、特定の誘電体層32を介して互いに対向する容量形成部50および51を有している。また、第3の内部電極44は、容量形成部50から第1および第2の側面36および37に露出するように引き出されて外部端子電極40−3および40−4に電気的に接続される2つの引出し部54を有している。他方、第4の内部電極45は、容量形成部51から第1および第2の側面36および37に露出するように引き出されて外部端子電極41−3および41−4に電気的に接続される2つの引出し部55を有している。上述した第3の内部電極44の引出し部54と第4の内部電極44の引出し部55とは、第1および第2の側面36および37の長さ方向に関して交互に露出するように配置されている。

【0054】

第1および第3の内部電極42および44は、図3(a)に示すように、同一面内において、第1および第2の側面36および37の長さ方向に並びながら、互いの間に所定の間隔を隔てて配置されている。同様に、第2および第4の内部電極43および45は、図3(b)に示すように、同一面内において、第1および第2の側面36および37の長さ方向に並びながら、互いの間に所定の間隔を隔てて配置されている。

【0055】

また、図3(a)と同(b)とを参照すればわかるように、誘電体層32の積層方向で見たとき、第1の内部電極42の容量形成部48と第4の内部電極45の容量形成部51とは重なり合わず、また、第2の内部電極43の容量形成部49と第3の内部電極44の容量形成部50とは重なり合っていない。

【0056】

図4には、電流の流れの一例が破線の矢印で示されている。第1および第2の内部電極42および43の引出し部52および53に着目すると、特定の誘電体層32を挟んで、これら引出し部52および53が交互に配置され、かつ、引出し部52および53の各々を流れる電流の方向が逆になっている。したがって、引出し部52および53を流れる電流のまわりに発生する磁界が相殺され、ESLが低減する。第3および第4の内部電極44および45の引出し部54および55についても同様のことが言える。

【0057】

また、第2および第3の内部電極43および44の引出し部53および54に着目した場合でも、特定の誘電体層32を挟んで、これら引出し部53および54が交互に配置され、かつ、引出し部53および54の各々を流れる電流の向きが逆になっている。したがって、引出し部53および54を流れる電流のまわりに発生する磁界が相殺され、ESLが低減する。第1および第4の内部電極42および45の引出し部52および55についても同様のことが言える。

【0058】

さらに、容量形成部48〜51に着目すると、同一面内において、第1の内部電極42と第3の内部電極44とが所定の間隔を隔てて並ぶように配置されているため、第1の内部電極42の容量形成部48の端縁を流れる電流と第3の内部電極44の容量形成部50の端縁を流れる電流とが逆向きとなる。したがって、それぞれの端縁を流れる電流のまわりに発生する磁界が相殺され、ESLが低減する。第2の内部電極43と第4の内部電極45とについても同様のことが言える。

【0059】

また、図3(b)において図示するように、第2および第4の内部電極43および45の各々の容量形成部49および51の互いに対向する端縁の長さE、ならびに第1および第3の内部電極42および44の各々の互いに対向する端縁の長さは、外部端子電極40および41間のピッチにかかわらず、自由に調整することができ、そのため、積層コンデンサ31のESRを調整することが容易である。

【0060】

図5は、積層コンデンサ31をデカップリング回路に組み込んだ状態を示す回路図である。図5において、C1が第1のコンデンサ部46に対応し、C2が第2のコンデンサ部47に対応している。前述したように、第1および第2のコンデンサ部C1およびC2のESLが低いため、ICへ迅速に電荷を供給することができる。

【0061】

次に、積層コンデンサ31の製造方法の一例について説明する。

【0062】

まず、誘電体層32となるべきセラミックグリーンシート、内部電極42〜45のための導電性ペースト、ならびに外部端子電極40および41のための導電性ペーストがそれぞれ用意される。ここで、セラミックグリーンシートおよび導電性ペーストには、バインダおよび溶剤が含まれるが、これらバインダおよび溶剤としては、公知の有機バインダおよび有機溶剤を用いることができる。また、外部端子電極40および41のための導電性ペーストには、ガラス成分が含まれることが多い。

【0063】

次に、セラミックグリーンシート上に、たとえばスクリーン印刷法などにより所定のパターンをもって導電性ペーストが印刷される。これによって、内部電極42〜45の各々となるべき導電性ペースト膜が形成されたセラミックグリーンシートが得られる。

【0064】

次に、上述のように導電性ペースト膜が形成されたセラミックグリーンシートを所定の順序で積層し、その上下に導電性ペースト膜が形成されていない外層用セラミックグリーンシートを所定枚数積層することによって、生の状態のマザー積層体が得られる。生のマザー積層体は、必要に応じて、静水圧プレスなどの手段により積層方向にプレスされる。

【0065】

次に、生のマザー積層体は所定のサイズにカットされ、それによって、積層体33の生の状態のものが切り出される。

【0066】

次に、生の積層体33が焼成される。焼成温度は、セラミックグリーンシートに含まれるセラミック材料や導電性ペースト膜に含まれる金属材料にもよるが、たとえば900〜1300℃に選ばれる。

【0067】

次に、焼成後の積層体33の第1および第2の側面36および37の各々上に導電性ペーストが塗布され、外部端子電極40および41のための導電性ペースト膜が形成される。この導電性ペースト膜は、好ましくは、第1および第2の側面36および37の各々から主面34および35の各々の一部にまで延びるように形成される。

【0068】

次に、上記導電性ペースト膜が焼成され、それによって、外部端子電極40および41が形成される。この焼成温度は、たとえば700〜900℃に選ばれる。また、焼成時の雰囲気としては、導電性ペーストに含まれる金属の種類に応じて、大気、N2、水蒸気+N2などの雰囲気が使い分けられる。

【0069】

このようにして、積層コンデンサ31が得られる。なお、必要に応じて、外部端子電極40および41の表面にめっきが施されてもよい。

【0070】

図6は、この発明の第2の実施形態による積層コンデンサ31aを説明するための図3に対応する図である。なお、図6において、(a)〜(d)は積層順序をも示している。図6において、図3に示した要素に相当する要素には同様の参照符号を付し、重複する説明は省略する。

【0071】

第2の実施形態による積層コンデンサ31aでは、第1および第3の内部電極42および44は、第1および第2の側面36および37の長さ方向に並びながら、互いの間に所定の間隔を隔てて配置されるが、同一面内に位置していない。同様に、第2および第4の内部電極43および45は、第1および第2の側面36および37の長さ方向に並びながら、互いの間に所定の間隔を隔てて配置されるが、同一面内に位置していない。したがって、第2の実施形態では、簡単に言えば、3次元的に見て、磁界が相殺されることになる。

【0072】

図6に示した構造では、第1および第3の内部電極42および44が、誘電体層32の1層分だけ、積層方向にずれており、第2および第4の内部電極43および45も、同様に、誘電体層32の1層分だけ、積層方向にずれているが、これらのずれは、誘電体層32の2層分以上であってもよい。

【0073】

図7は、この発明の第3の実施形態による積層コンデンサ31bを説明するための図4に対応する図である。図7において、図4に示した要素に相当する要素には同様の参照符号を付し、重複する説明は省略する。

【0074】

第3の実施形態による積層コンデンサ31bは、第1および第2の側面36および37の長さ方向に関して、同一面内にある第1の内部電極42の引出し部52と第3の内部電極44の引出し部54とが隣り合い、かつ、同一面内にある第2の内部電極43の引出し部53と第4の内部電極45の引出し部55とが隣り合うように配置されていることを特徴としている。この第3の実施形態によれば、前述した第1の実施形態に比べて、同一面内における磁界相殺の効果が高くなる。

【0075】

図8は、この発明の第4の実施形態による積層コンデンサ31cを説明するための図3に対応する図である。なお、図8において、(a)〜(d)は積層順序をも示している。図8において、図3に示した要素に相当する要素には同様の参照符号を付し、重複する説明は省略する。

【0076】

第4の実施形態による積層コンデンサ31cでは、少なくとも第1および第2の内部電極42および43については、積層方向に複数組配置される。そして、図8(a)に示すように、複数の第1の内部電極42のうちの一部については、同一面内に、第3の内部電極44を位置させておらず、また、図8(b)に示すように、複数の第2の内部電極43のうちの一部については、同一面内に、第4の内部電極45を位置させていないことを特徴としている。

【0077】

この実施形態では、好ましくは、積層体33において、上から、所定枚数の外層用誘電体層、図8(a)および(b)に示したパターンの所定回数の繰り返し、図8(c)および(d)に示したパターンの所定回数の繰り返し、図8(a)および(b)に示したパターンの所定回数の繰り返し、所定枚数の外層用誘電体層、といった積層順序が採用される。

【0078】

この第4の実施形態によれば、第3および第4の内部電極44および45の積層枚数を減らすことにより、第1のコンデンサ部46に比べて、第2のコンデンサ部47の容量が小さくなる。このように、第1および第2のコンデンサ部46および47間で容量を異ならせることにより、コンデンサ部46および47の各々の共振周波数を互いに異ならせることができ、そのため、より広い周波数帯域においてデカップリングコンデンサとしての機能を実現することが可能となる。

【0079】

図9および図10は、この発明の第5の実施形態による積層コンデンサ31dを説明するためのもので、それぞれ、図2および図3に対応する図である。図9および図10において、図2および図3に示した要素に相当する要素には同様の参照符号を付し、重複する説明は省略する。

【0080】

第5の実施形態による積層コンデンサ31dは、第1および第2の内部電極42および43の各々の容量形成部48および49の面積と、第3および第4の内部電極44および45の各々の容量形成部50および51とが互いに異なることを特徴としている。より具体的には、第1および第2の内部電極42および43の各々の容量形成部48および49の面積に比べて、第3および第4の内部電極44および45の各々の容量形成部50および51の面積がより大きくされる。その結果、第1のコンデンサ部46に比べて、第2のコンデンサ部47の容量が大きくなる。また、第1および第2の内部電極42および43に比べて、第3および第4の内部電極44および45の各々の引出し部54および55の数が増やされ、積層コンデンサ31d全体として、合計10個の外部端子電極40および41が形成される。

【0081】

この第5の実施形態によれば、第4の実施形態の場合と同様、第1および第2のコンデンサ部46および47間で容量を異ならせることにより、第1および第2のコンデンサ部46および47間で共振周波数を互いに異ならせることができるので、より広い周波数帯域においてデカップリングコンデンサとしての機能を実現することが可能となる。また、第2のコンデンサ部47において、一層の低ESL化を図ることができる。

【0082】

図11および図12は、この発明の第6の実施形態による積層コンデンサ31eを説明するためのもので、それぞれ、図2および図3に対応する図である。図11および図12において、図2および図3に示した要素に相当する要素には同様の参照符号を付し、重複する説明は省略する。

【0083】

第6の実施形態による積層コンデンサ31eは、第5および第6の内部電極56および57が追加され、それによって、第3のコンデンサ部58がさらに形成されることを特徴としている。

【0084】

第5および第6の内部電極56および57は、それぞれ、特定の誘電体層32を介して互いに対向する容量形成部59および60を有している。また、第5の内部電極56は、容量形成部59から第1および第2の側面36および37に露出するように引き出されて外部端子電極40−5および40−6に電気的に接続される2つの引出し部61を有している。また、第6の内部電極57は、容量形成部60から第1および第2の側面36および37に露出するように引き出されて外部端子電極41−5および41−6に電気的に接続される2つの引出し部62を有している。

【0085】

そして、第5の内部電極56の引出し部61と第6の内部電極57の引出し部62とは、第1および第2の側面36および37の長さ方向に関して交互に露出するように配置される。

【0086】

また、第1、第3および第5の内部電極42、44および56は、図12(a)に示すように、同一面内において、第1および第2の側面36および37の長さ方向に並びながら、互いの間に所定の間隔を隔てて配置される。同様に、第2、第4および第6の内部電極43、45および57は、図12(b)に示すように、同一面内において、第1および第2の側面36および37の長さ方向に並びながら、互いの間に所定の間隔を隔てて配置される。

【0087】

また、図12(a)および同(b)をともに参照すればわかるように、誘電体層32の積層方向で見たとき、第5の内部電極56の容量形成部59は第2および第4の内部電極43および45の容量形成部49および51のいずれとも重なり合わず、また、第6の内部電極57の容量形成部60は第1および第3の内部電極42および44の容量形成部48および50のいずれとも重なり合わないように配置されている。

【0088】

このようにコンデンサ部の数を増やしながら、たとえば、第1ないし第3のコンデンサ部46、47および48間で容量を異ならせると、より広い周波数帯域においてデカップリングコンデンサとしての機能を実現することができる。また、コンデンサ部46、47および58のそれぞれが互いに独立しているため、コンデンサ部の数を3個に限らず、さらに任意に増やしていくことが可能であり、設計の自由度が高い。

【図面の簡単な説明】

【0089】

【図1】この発明の第1の実施形態による積層コンデンサ31の外観を示す斜視図である。

【図2】図1に示した積層コンデンサ31の外観を示す平面図である。

【図3】図1に示した積層コンデンサ31の内部構造を、内部電極が通る断面をもって示す平面図である。

【図4】図3において、電流の流れの一例を破線の矢印で加えた図である。

【図5】図1に示した積層コンデンサをデカップリング回路に組み込んだ状態を示す回路図である。

【図6】この発明の第2の実施形態による積層コンデンサ31aを説明するための図3に対応する図である。

【図7】この発明の第3の実施形態による積層コンデンサ31bを説明するための図4に対応する図である。

【図8】この発明の第4の実施形態による積層コンデンサ31cを説明するための図3に対応する図である。

【図9】この発明の第5の実施形態による積層コンデンサ31dを説明するための図2に対応する図である。

【図10】図9に示した積層コンデンサ31dを説明するための図3に対応する図である。

【図11】この発明の第6の実施形態による積層コンデンサ31eを説明するための図2に対応する図である。

【図12】図11に示した積層コンデンサ31eを説明するための図3に対応する図である。

【図13】特許文献1において開示された積層コンデンサ8の内部構造を、内部電極が通る断面をもって示す平面図である。

【図14】特許文献2において開示された積層コンデンサ14の内部構造を、内部電極が通る断面をもって示す平面図である。

【図15】特許文献3に開示された積層コンデンサ24の内部構造を、内部電極が通る断面をもって示す平面図である。

【図16】特許文献3において開示された他の積層コンデンサ24aの内部構造を、内部電極が通る断面をもって示す平面図である。

【符号の説明】

【0090】

31,31a,31b,31c,31d,31e 積層コンデンサ

32 誘電体層

33 積層体

36 第1の側面

37 第2の側面

40 第1の外部端子電極

41 第2の外部端子電極

42 第1の内部電極

43 第2の内部電極

44 第3の内部電極

45 第4の内部電極

46 第1のコンデンサ部

47 第2のコンデンサ部

48〜51,59,60 容量形成部

52〜55,61,62 引出し部

56 第5の内部電極

57 第6の内部電極

58 第3のコンデンサ部

【技術分野】

【0001】

この発明は、積層コンデンサに関するもので、特に、等価直列インダクタンス(ESL)を低減するために多端子タイプとされた積層コンデンサに関するものである。

【背景技術】

【0002】

電源回路においては、電源ラインやグラウンドに存在するインピーダンスによって、電源ラインでの電圧変動が大きくなると、駆動する回路の動作が不安定になったり、電源回路を経由して回路間の干渉が起こったり、発振を起こしたりする。そこで、通常、電源ラインとグラウンドとの間には、デカップリングコンデンサが接続されている。デカップリングコンデンサは、電源ラインとグラウンドとの間のインピーダンスを低減し、電源電圧の変動や回路間の干渉を抑える役割を果たしている。

【0003】

さて、近年、携帯電話などの通信機器やパーソナルコンピュータなどの情報処理機器では、大量の情報を処理するために信号の高速化が進んでおり、使用されるICのクロック周波数も高周波化が進んでいる。このため、高調波成分を多く含むノイズが発生しやすくなり、IC電源回路においては、より強力なデカップリングを施す必要がある。

【0004】

デカップリング効果を高めるためには、インピーダンス周波数特性の優れたコンデンサを用いることが有効であり、これに適したコンデンサとしては、積層コンデンサが挙げられる。積層コンデンサは、ESLが小さいため、電解コンデンサに比べて、広い周波数帯域にわたってノイズ吸収効果に優れている。

【0005】

通常、ICのデッカプリングコンデンサとして用いられる積層コンデンサは、ICの近傍に配置される。これは、電源ラインに電圧変動が生じた際、コンデンサからICに迅速に電荷を供給し、ICの立ち上がりが遅れるのを防止するためである。

【0006】

しかし、コンデンサに充放電が起こるとき、コンデンサには、式:dV=L・di/dtで表わされる逆起電力dVが生じ、dVが大きいとICへの電荷の供給が遅くなってしまう。ICのクロック周波数が高周波化する中で、時間当たりの電流変動量di/dtは大きくなる傾向にある。すなわち、dVを小さくするためには、インダクタンスLを小さくする必要がある。Lには、ICの電源ピンからコンデンサまでのパターンのインダクタンスと、コンデンサからグラウンドまでのパターンのインダクタンスと、コンデンサ内部のESLとが含まれるが、回路の設計上、パターンのインダクタンスを下げることには制約がある。このため、コンデンサのESLをより低減できることが望まれている。

【0007】

そこで、ESLがより低減された積層コンデンサとして、特開2002−151349号公報(特許文献1)、特開2004−103883号公報(特許文献2)および特開2006−32904号公報(特許文献3)に記載されたものが提案されている。

【0008】

図13ないし図16は、積層コンデンサの内部構造を、内部電極が通る断面をもって示す平面図であるが、特許文献1に記載されたものが図13に、特許文献2に記載されたものが図14に、特許文献3に記載されたものが図15および図16にそれぞれ示されている。

【0009】

図13ないし図16において、共通して、積層された複数の誘電体層1をもって形成され、かつ相対向する第1および第2の側面2および3ならびに相対向する第3および第4の側面4および5を有する、直方体状の積層体6が図示されている。また、図13ないし図16において、電流の流れの一例が破線の矢印で示されている。

【0010】

まず、図13を参照して、特許文献1では、積層体6の相対向する第1および第2の側面2および3上に合計8個の外部端子電極7が形成された、多端子タイプの積層コンデンサ8が開示されている。この積層コンデンサ8では、第1の側面2に引き出された内部電極9が、第1の側面2と対向する第2の側面3に引き出された内部電極10と面内で対向するように配置されていて、同様に、内部電極11が内部電極12と面内で対向するように配置されている。このような構造によれば、内部電極9〜12を流れる電流が対向部分において逆向きとなり、それによって、電流のまわりに発生する磁界が相殺され、積層コンデンサ8のESLが低減する。

【0011】

次に、図14を参照して、特許文献2では、積層体6の第1ないし第4の側面2〜5に合計8個の外部端子電極13が形成された、多端子タイプの積層コンデンサ14が開示されている。この積層コンデンサ14では、同一面内で対向するようにそれぞれ配置された内部電極15、16および17ならびに内部電極18、19および20は、積層体6の相対向する第1および第2の側面2および3に互い違いに引き出されている。また、内部電極15〜17および内部電極18〜20は、共通の内部電極21および22と積層方向に対向して容量を形成しており、これら共通の内部電極21および22は、それぞれ、積層体6の相対向する第3および第4の側面4および5に引き出されている。このような構造によれば、内部電極15〜20をそれぞれ流れる電流が、対向部分において逆向きとなることにより、電流のまわりに発生する磁界が相殺され、積層コンデンサ14のESLが低減する。

【0012】

次に、特許文献3では、種々の多端子タイプの積層コンデンサが開示されているが、たとえば、図15に示すように、積層体6の相対向する第1および第2の側面2および3上に合計8個の外部端子電極23が形成された、多端子タイプの積層コンデンサ24が開示されている。この積層コンデンサ24では、それぞれ面内で対向するコの字状の内部電極25および26ならびに内部電極27および28の各々において、対向部分で電流が逆向きになることにより、電流のまわりに発生する磁界が相殺され、積層コンデンサ24のESLが低減する。

【0013】

特許文献3では、また、図16に示すような多端子タイプの積層コンデンサ24aも開示されている。この積層コンデンサ24aでは、積層方向に対向する内部電極25aおよび26aと内部電極27aおよび28aにおいて、対向部分での電流の向きを直交方向とすることにより、電流のまわりに発生する磁界が弱まり、積層コンデンサ24aのESLが低減する。

【0014】

しかしながら、上述した特許文献1ないし3の各々に記載された構造には、以下のように、解決されるべき課題がある。

【0015】

特許文献1に記載された構造では、内部電極9および10の互いに対向する端縁の長さ、あるいは、内部電極11および12の互いに対向する端縁の長さが、内部電極9および12の各々の引出し部間の距離すなわち外部端子電極7間のピッチに左右される。外部端子電極7間のピッチについては、短絡の問題を考慮して、一定以上の距離を確保しようとする一方、積層コンデンサ8の小型化を考慮して、一定以下の距離まで短縮しようとする。このため、実際の設計上、外部端子電極7間のピッチには制約があり、その結果、内部電極9および10あるいは内部電極11および12の互いに対向する端縁の長さについても制約が課せられる。したがって、上述の対向端縁の長さを調整することによって、電流経路の長さを調整するという方法を単純には採用することができず、積層コンデンサ8の等価直列抵抗(ESR)を調整することが必ずしも容易ではない。

【0016】

上述したESRは、電源回路の安定化に影響を及ぼすものである。すなわち、低ESL化が図られた積層コンデンサにおいては、多端子化に伴い、内部電極の引出し部の数が増え、その結果、ESRが低くなる傾向がある。ESRが低すぎる場合には、周辺回路のインダクタンスによって共振現象を招いたとき、電源電圧が大きく落ち込んだり、あるいはリンギングなどの減衰振動を起こしたりしやすくなるという問題がある。そのため、ESRについては、ある程度高くする要求があるが、特許文献1に記載の構造では、前述したように、このようなESRの調整が必ずしも容易ではない。

【0017】

また、特許文献1に記載の構造では、2つの独立したコンデンサ部が形成されるが、コンデンサ部の数を増やそうとした場合、積層体6の幅方向すなわち第3および第4の側面4および5の延びる方向に新たなコンデンサ部を追加することはできない。したがって、積層体6の長手方向すなわち第1および第2の側面2および3の延びる方向に新たなコンデンサ部を追加することになるが、この場合、図示した内部電極9〜12と同様に対向する1対以上の内部電極を形成することとなり、コンデンサ部は2の倍数で増加し、外部端子電極7の数は長手方向に4の倍数で増加することとなる。このため、設計の自由度が低いばかりでなく、コンデンサ部を追加しようとする際に、積層体6が長細くなりすぎて、積層体6の抗折強度が低くなってしまうという問題に遭遇する。

【0018】

次に、特許文献2に記載された構造では、内部電極15〜17または内部電極18〜20と共通に対向する内部電極21および22については、容量形成に寄与しない部分が存在しており、このような容量形成の観点から見た場合には、電極材料に無駄が生じていると言える。また、共通の内部電極21および22の各々を界面に位置させる隣り合う誘電体層1同士の接合面積が小さくなるため、積層体6においてデラミネーションなどの構造欠陥が発生しやすいという問題もある。さらに、共通の内部電極21および22については、内部電極15〜20を引き出した第1および第2の側面2および3とは異なる第3および第4の側面4および5に引き出していることから、外部端子電極13を必ず4つの側面2〜5の各々に形成する必要があり、設計の自由度が低いという問題もある。

【0019】

次に、特許文献3に記載の構造であって、図15に示した積層コンデンサ24については、前述の特許文献1に記載の構造と同様の問題を有している。また、図16に示した積層コンデンサ24aについては、特許文献2の場合と同様、内部電極25a〜28aが容量形成に寄与しない部分を備えており、容量形成の観点から見たとき、電極材料の無駄があるという問題を有している。また、特許文献3に記載の構造では、特許文献2の場合と同様、内部電極25〜28または25a〜28aの各々を界面に位置させる隣り合う誘電体層1同士の接合面積が小さくなり、積層体6にデラミネーションなどの構造欠陥が発生しやすいという問題もある。

【特許文献1】特開2002−151349号公報(特に、図3、図6および図8)

【特許文献2】特開2004−103883号公報(特に、図1)

【特許文献3】特開2006−32904号公報(特に、図4、図7および図13)

【発明の開示】

【発明が解決しようとする課題】

【0020】

そこで、この発明の目的は、設計の自由度が高く、電極材料に関して経済的であり、構造欠陥が発生しにくい、多端子タイプの積層コンデンサを提供しようとすることである。

【課題を解決するための手段】

【0021】

この発明に係る積層コンデンサは、積層された複数の誘電体層をもって構成され、かつ相対向する第1および第2の側面を有する、直方体状の積層体と、第1および第2の側面上に形成される、複数の外部端子電極とを備える。積層体の内部には、第1のコンデンサ部を形成するため、第1および第2の内部電極が形成されるとともに、第2のコンデンサ部を形成するため、第3および第4の内部電極が形成される。

【0022】

第1および第2の内部電極は、それぞれ、特定の誘電体層を介して互いに対向する容量形成部と、容量形成部から第1および第2の側面に露出するように引き出されて特定の外部端子電極に電気的に接続される2つ以上の引出し部とを有し、第1の内部電極の引出し部と第2の内部電極の引出し部とは、第1および第2の側面の長さ方向に関して交互に露出するように配置される。

【0023】

第3および第4の内部電極は、それぞれ、特定の誘電体層を介して互いに対向する容量形成部と、容量形成部から第1および第2の側面に露出するように引き出されて特定の外部端子電極に電気的に接続される2つ以上の引出し部とを有し、第3の内部電極の引出し部と第4の内部電極の引出し部とは、第1および第2の側面の長さ方向に関して交互に露出するように配置される。

【0024】

第1および第3の内部電極は、第1および第2の側面の長さ方向に並びながら、互いの間に所定の間隔を隔てて配置される。第2および第4の内部電極は、第1および第2の側面の長さ方向に並びながら、互いの間に所定の間隔を隔てて配置される。

【0025】

そして、誘電体層の積層方向で見たとき、第1の内部電極の容量形成部と第4の内部電極の容量形成部とは重なり合わず、第2の内部電極の容量形成部と第3の内部電極の容量形成部とは重なり合わないようにされる。

【0026】

この発明に係る積層コンデンサにおいて、第1および第2の側面の長さ方向に関して、第1の内部電極の引出し部と第3の内部電極の引出し部とが隣り合い、かつ、第2の内部電極の引出し部と第4の内部電極の引出し部とが隣り合うように配置されることが好ましい。

【0027】

また、この発明に係る積層コンデンサにおいて、第1および第3の内部電極は同一面内に位置され、かつ、第2および第4の内部電極は同一面内に位置されることが好ましい。

【0028】

上述の場合、第1および第2の内部電極は積層方向に複数組配置され、複数の第1の内部電極のうちの一部については、同一面内に、第3の内部電極を位置させておらず、複数の第2の内部電極のうちの一部については、同一面内に、第4の内部電極を位置させていなくてもよい。

【0029】

なお、この発明に係る積層コンデンサにおいて、第1および第3の内部電極は積層方向にずれて位置され、かつ、第2および第4の内部電極は積層方向にずれて位置されていてもよい。

【0030】

また、第1および第2の内部電極の各々の容量形成部の面積と第3および第4の内部電極の各々の容量形成部の面積とは互いに異なっていてもよい。この場合、面積がより広い方の容量形成部を有する内部電極の引出し部の数は、面積がより狭い方の容量形成部を有する内部電極の引出し部の数より多くてもよい。

【0031】

この発明に係る積層コンデンサは、積層体の内部に、第3のコンデンサ部を形成するため、第5および第6の内部電極をさらに備えていてもよい。この場合、第5および第6の内部電極は、それぞれ、特定の誘電体層を介して互いに対向する容量形成部と、容量形成部から第1および第2の側面に露出するように引き出されて特定の外部端子電極に電気的に接続される2つ以上の引出し部とを有し、第5の内部電極の引出し部と第6の内部電極の引出し部とは、第1および第2の側面の長さ方向に関して交互に露出するように配置され、第1、第3および第5の内部電極は、第1および第2の側面の長さ方向に並びながら、互いの間に所定の間隔を隔てて配置され、第2、第4および第6の内部電極は、第1および第2の側面の長さ方向に並びながら、互いの間に所定の間隔を隔てて配置され、誘電体層の積層方向で見たとき、第5の内部電極の容量形成部は第2および第4の内部電極のいずれの容量形成部とも重なり合わず、第6の内部電極の容量形成部は第1および第3の内部電極のいずれの容量形成部とも重なり合わないようにされる。

【発明の効果】

【0032】

この発明によれば、第1ないし第4の内部電極の各々が、容量形成部から第1および第2の側面に露出するように引き出されて特定の外部端子電極に電気的に接続される2つ以上の引出し部を有し、また、第1および第3の内部電極が、第1および第2の側面の長さ方向に並びながら、互いの間に所定の間隔を隔てて配置され、第2および第4の内部電極が、第1および第2の側面の長さの方向に並びながら、互いの間に所定の間隔を隔てて配置されている。

【0033】

したがって、外部端子電極間のピッチの制約を受けず、第1および第3の内部電極が互いに対向する端縁の長さ、ならびに第2および第4の内部電極が互いに対向する端縁の長さを調整することが可能となる。これにより、電流経路を長くしたり短くしたりすることが比較的自由にできるため、たとえば、積層コンデンサのESRを任意に制御することが可能となる。

【0034】

また、第1および第2のコンデンサ部以外に、たとえば第3のコンデンサ部というように、コンデンサ部を追加しようとする場合には、第1および第2の側面の長さ方向に沿って、コンデンサ部を1つずつ追加することができる。よって、積層コンデンサの設計の自由度を高めることができる。

【0035】

また、この発明によれば、第1および第4の内部電極の各々の容量形成部同士は互いに重なり合わず、第2および第3の内部電極の各々の容量形成部同士は互いに重なり合わない。したがって、容量形成の観点から無駄となる部分が各内部電極に実質的に存在しないようにすることができるため、電極材料の無駄を抑えることができるばかりでなく、内部電極を互いの間の界面に位置させる隣り合う誘電体層同士の接合面積を確保して、積層体においてデラミネーションなどの構造欠陥を生じさせにくくすることができる。

【0036】

また、この発明によれば、各内部電極が2つ以上の引出し部を有していて、引出し部の各々の位置に関しては、第1の内部電極の引出し部と第2の内部電極の引出し部とが、第1および第2の側面の長さ方向に関して交互に露出するように配置され、第3の内部電極の第4の内部電極の引出し部とが、第1および第2の側面の長さ方向に関して交互に露出するように配置されているので、各内部電極上での電流の流れを種々の方向に向けることができるとともに、隣り合う引出し部での電流の流れを逆向きにすることができるので、磁界を効果的に相殺することができ、その結果、ESLを小さくすることができる。

【0037】

この発明に係る積層コンデンサにおいて、第1および第2の側面の長さ方向に関して、第1の内部電極の引出し部と第3の内部電極の引出し部とが隣り合い、かつ、第2の内部電極の引出し部と第4の内部電極の引出し部とが隣り合うように配置されると、磁界相殺の効果がより高くなる。

【0038】

この発明に係る積層コンデンサにおいて、第1および第3の内部電極が同一面内に位置され、かつ、第2および第4の内部電極が同一面内に位置されると、各々の組をなす内部電極が積層方向にずれて位置される場合に比べて、磁界を相殺する効果を高めることができる。

【0039】

上述の場合において、第1および第2の内部電極が積層方向に複数組配置され、複数の第1の内部電極の一部については、同一面内に、第3の内部電極を位置させておらず、複数の第2の内部電極のうちの一部については、同一面内に、第4の内部電極を位置させていない場合、第1のコンデンサ部に比べて第2のコンデンサ部の容量を小さくすることができる。このように、第1および第2のコンデンサ部間で容量を異ならせることにより、各コンデンサ部の共振周波数が変わるため、より広い周波数帯域においてデカップリングコンデンサとしての機能を実現することが可能となる。

【0040】

この発明において、第1および第2の内部電極の各々の容量形成部の面積と第3および第4の内部電極の各々の容量形成部の面積とが互いに異なっていると、第1および第2のコンデンサ部間で容量を異ならせることができる。したがって、上述の場合と同様、各コンデンサ部の共振周波数が変わるため、より広い周波数帯域においてデカップリングコンデンサとしての機能を実現することが可能となる。

【0041】

上述の実施態様において、面積がより広い方の容量形成部を有する内部電極の引出し部の数を、面積がより狭い方の容量形成部を有する内部電極の引出し部の数より多くすることにより、面積がより広い方の容量形成部を有する内部電極によって与えられるコンデンサ部におけるESLをより低減することができる。

【0042】

この発明において、第5および第6の内部電極が追加されることにより、第3のコンデンサ部が形成されると、たとえば、第1ないし第3のコンデンサ部の各々の容量を互いに異ならせることにより、より広い周波数帯域においてデカップリングコンデンサとしての機能を実現することが可能となる。

【発明を実施するための最良の形態】

【0043】

図1ないし図4は、この発明の第1の実施形態による積層コンデンサ31を説明するためのものである。ここで、図1は、積層コンデンサ31の外観を示す斜視図であり、図2は、積層コンデンサ31の外観を示す平面図である。図3は、積層コンデンサ31の内部構造を、いくつかの特定の断面をもって示す平面図である。図4は、図3と同様の図面であるが、電流の流れを示す破線の矢印を加えたものである。

【0044】

積層コンデンサ31は、積層された複数の誘電体層32をもって構成される、直方体状の積層体33を備えている。誘電体層32は、たとえば、BaTiO3、CaTiO3、SrTiO3、CaZrO3などを主成分とする誘電体セラミックから構成される。なお、これら主成分に、Mn化合物、Fe化合物、Cr化合物、Co化合物、Ni化合物などの副成分が添加されていてもよい。また、誘電体層32の厚みは、たとえば1〜10μmとされる。

【0045】

積層体33は、相対向する第1および第2の主面34および35と、第1および第2の主面34および35間を結ぶものであって、相対向する第1および第2の側面36および37ならびに相対向する第3および第4の側面38および39とを有している。ここで、誘電体層32は、主面34および35の方向に延び、側面36〜39は、誘電体層32の積層方向に延びている。また、第1および第2の側面36および37が誘電体層32の長辺に沿う位置にある。

【0046】

積層体33の第1および第2の側面36および37上には、複数の外部端子電極40および41が形成される。この実施形態では、第1の側面36上に4個の外部端子電極40および41が形成され、第2の側面37上に4個の外部端子電極40および41が形成される。また、外部端子電極40および41のうち、第1の外部端子電極40には第1の極性が割り当てられ、第2の外部端子電極41には第2の極性が割り当てられる。これら第1および第2の外部端子電極40および41は、交互に並ぶように配置される。

【0047】

なお、4個の第1の外部端子電極40の間で区別する必要があるときには、第1の外部端子電極について、「40−1」、「40−2」、「40−3」および「40−4」の参照符号を用い、他方、4個の第2の外部端子電極41の間で区別する必要があるときには、第2の外部端子電極について、「41−1」、「41−2」、「41−3」および「41−4」の参照符号を用いることにする。

【0048】

外部端子電極40および41の導電成分として、たとえば、Cu、Ni、Ag、Pd、Ag−Pd合金、またはAuなどを用いることができる。外部端子電極40および41は、通常、導電性ペーストを塗布し、焼成することによって形成されるが、この場合、導電性ペーストは、積層体33が未焼結状態にあるときに塗布され、後述する内部電極と同時焼成によって形成されても、積層体33を焼成した後に塗布され、再び焼成されることによって形成されてもよい。外部端子電極40および41の厚みは、最も厚い部分で20〜100μmであることが好ましい。

【0049】

外部端子電極40および41上には、必要に応じて、めっき膜が形成されてもよい。めっき膜を構成する金属としては、たとえば、Cu、Ni、Sn、Auなどを用いることができ、また、Ni−Sn、Ni−Au、Cu−Ni−Auなどの複数層からなるめっき膜を形成してもよい。めっき膜の1層当たりの厚みは、1〜10μmであることが好ましい。また、外部端子電極40とめっき膜との間に、応力緩和用の樹脂層が形成されていてもよい。また、外部端子電極40および41は、積層体33上に、直接、めっきを施すことにより形成されてもよい。

【0050】

積層体33の内部には、図3に示すように、第1ないし第4の内部電極42〜45が形成される。内部電極42〜45に含まれる導電成分としては、たとえば、Ni、Cu、Ag、Pd、Ag−Pd合金、またはAuなどを用いることができる。また、内部電極42〜45の各々の厚みは、0.5〜2.0μmであることが好ましい。

【0051】

第1および第2の内部電極42および43は、第1のコンデンサ部46を形成するためのものであり、第3および第4の内部電極44および45は第2のコンデンサ部47を形成するためのものである。なお、積層体33の積層方向での両端部には、いずれの内部電極もが形成されない誘電体層32が所定数積層される。また、図3(a)に示した内部電極42および44のパターンと同(b)に示した内部電極43および45のパターンとは、積層方向に複数回繰り返される。

【0052】

第1および第2の内部電極42および43は、それぞれ、特定の誘電体層32を介して互いに対向する容量形成部48および49を有している。また、第1の内部電極42は、容量形成部48から第1および第2の側面36および37に露出するように引き出されて外部端子電極40−1および40−2に電気的に接続される2つの引出し部52を有している。他方、第2の内部電極43は、容量形成部49から第1および第2の側面36および37に露出するように引き出されて外部端子電極41−1および41−2に電気的に接続される2つの引出し部53を有している。これら第1の内部電極42の引出し部52と第2の内部電極43の引出し部53とは、第1および第2の側面36および37の長さ方向に関して交互に露出するように配置されている。

【0053】

同様に、第3および第4の内部電極44および45は、それぞれ、特定の誘電体層32を介して互いに対向する容量形成部50および51を有している。また、第3の内部電極44は、容量形成部50から第1および第2の側面36および37に露出するように引き出されて外部端子電極40−3および40−4に電気的に接続される2つの引出し部54を有している。他方、第4の内部電極45は、容量形成部51から第1および第2の側面36および37に露出するように引き出されて外部端子電極41−3および41−4に電気的に接続される2つの引出し部55を有している。上述した第3の内部電極44の引出し部54と第4の内部電極44の引出し部55とは、第1および第2の側面36および37の長さ方向に関して交互に露出するように配置されている。

【0054】

第1および第3の内部電極42および44は、図3(a)に示すように、同一面内において、第1および第2の側面36および37の長さ方向に並びながら、互いの間に所定の間隔を隔てて配置されている。同様に、第2および第4の内部電極43および45は、図3(b)に示すように、同一面内において、第1および第2の側面36および37の長さ方向に並びながら、互いの間に所定の間隔を隔てて配置されている。

【0055】

また、図3(a)と同(b)とを参照すればわかるように、誘電体層32の積層方向で見たとき、第1の内部電極42の容量形成部48と第4の内部電極45の容量形成部51とは重なり合わず、また、第2の内部電極43の容量形成部49と第3の内部電極44の容量形成部50とは重なり合っていない。

【0056】

図4には、電流の流れの一例が破線の矢印で示されている。第1および第2の内部電極42および43の引出し部52および53に着目すると、特定の誘電体層32を挟んで、これら引出し部52および53が交互に配置され、かつ、引出し部52および53の各々を流れる電流の方向が逆になっている。したがって、引出し部52および53を流れる電流のまわりに発生する磁界が相殺され、ESLが低減する。第3および第4の内部電極44および45の引出し部54および55についても同様のことが言える。

【0057】

また、第2および第3の内部電極43および44の引出し部53および54に着目した場合でも、特定の誘電体層32を挟んで、これら引出し部53および54が交互に配置され、かつ、引出し部53および54の各々を流れる電流の向きが逆になっている。したがって、引出し部53および54を流れる電流のまわりに発生する磁界が相殺され、ESLが低減する。第1および第4の内部電極42および45の引出し部52および55についても同様のことが言える。

【0058】

さらに、容量形成部48〜51に着目すると、同一面内において、第1の内部電極42と第3の内部電極44とが所定の間隔を隔てて並ぶように配置されているため、第1の内部電極42の容量形成部48の端縁を流れる電流と第3の内部電極44の容量形成部50の端縁を流れる電流とが逆向きとなる。したがって、それぞれの端縁を流れる電流のまわりに発生する磁界が相殺され、ESLが低減する。第2の内部電極43と第4の内部電極45とについても同様のことが言える。

【0059】

また、図3(b)において図示するように、第2および第4の内部電極43および45の各々の容量形成部49および51の互いに対向する端縁の長さE、ならびに第1および第3の内部電極42および44の各々の互いに対向する端縁の長さは、外部端子電極40および41間のピッチにかかわらず、自由に調整することができ、そのため、積層コンデンサ31のESRを調整することが容易である。

【0060】

図5は、積層コンデンサ31をデカップリング回路に組み込んだ状態を示す回路図である。図5において、C1が第1のコンデンサ部46に対応し、C2が第2のコンデンサ部47に対応している。前述したように、第1および第2のコンデンサ部C1およびC2のESLが低いため、ICへ迅速に電荷を供給することができる。

【0061】

次に、積層コンデンサ31の製造方法の一例について説明する。

【0062】

まず、誘電体層32となるべきセラミックグリーンシート、内部電極42〜45のための導電性ペースト、ならびに外部端子電極40および41のための導電性ペーストがそれぞれ用意される。ここで、セラミックグリーンシートおよび導電性ペーストには、バインダおよび溶剤が含まれるが、これらバインダおよび溶剤としては、公知の有機バインダおよび有機溶剤を用いることができる。また、外部端子電極40および41のための導電性ペーストには、ガラス成分が含まれることが多い。

【0063】

次に、セラミックグリーンシート上に、たとえばスクリーン印刷法などにより所定のパターンをもって導電性ペーストが印刷される。これによって、内部電極42〜45の各々となるべき導電性ペースト膜が形成されたセラミックグリーンシートが得られる。

【0064】

次に、上述のように導電性ペースト膜が形成されたセラミックグリーンシートを所定の順序で積層し、その上下に導電性ペースト膜が形成されていない外層用セラミックグリーンシートを所定枚数積層することによって、生の状態のマザー積層体が得られる。生のマザー積層体は、必要に応じて、静水圧プレスなどの手段により積層方向にプレスされる。

【0065】

次に、生のマザー積層体は所定のサイズにカットされ、それによって、積層体33の生の状態のものが切り出される。

【0066】

次に、生の積層体33が焼成される。焼成温度は、セラミックグリーンシートに含まれるセラミック材料や導電性ペースト膜に含まれる金属材料にもよるが、たとえば900〜1300℃に選ばれる。

【0067】

次に、焼成後の積層体33の第1および第2の側面36および37の各々上に導電性ペーストが塗布され、外部端子電極40および41のための導電性ペースト膜が形成される。この導電性ペースト膜は、好ましくは、第1および第2の側面36および37の各々から主面34および35の各々の一部にまで延びるように形成される。

【0068】

次に、上記導電性ペースト膜が焼成され、それによって、外部端子電極40および41が形成される。この焼成温度は、たとえば700〜900℃に選ばれる。また、焼成時の雰囲気としては、導電性ペーストに含まれる金属の種類に応じて、大気、N2、水蒸気+N2などの雰囲気が使い分けられる。

【0069】

このようにして、積層コンデンサ31が得られる。なお、必要に応じて、外部端子電極40および41の表面にめっきが施されてもよい。

【0070】

図6は、この発明の第2の実施形態による積層コンデンサ31aを説明するための図3に対応する図である。なお、図6において、(a)〜(d)は積層順序をも示している。図6において、図3に示した要素に相当する要素には同様の参照符号を付し、重複する説明は省略する。

【0071】

第2の実施形態による積層コンデンサ31aでは、第1および第3の内部電極42および44は、第1および第2の側面36および37の長さ方向に並びながら、互いの間に所定の間隔を隔てて配置されるが、同一面内に位置していない。同様に、第2および第4の内部電極43および45は、第1および第2の側面36および37の長さ方向に並びながら、互いの間に所定の間隔を隔てて配置されるが、同一面内に位置していない。したがって、第2の実施形態では、簡単に言えば、3次元的に見て、磁界が相殺されることになる。

【0072】

図6に示した構造では、第1および第3の内部電極42および44が、誘電体層32の1層分だけ、積層方向にずれており、第2および第4の内部電極43および45も、同様に、誘電体層32の1層分だけ、積層方向にずれているが、これらのずれは、誘電体層32の2層分以上であってもよい。

【0073】

図7は、この発明の第3の実施形態による積層コンデンサ31bを説明するための図4に対応する図である。図7において、図4に示した要素に相当する要素には同様の参照符号を付し、重複する説明は省略する。

【0074】

第3の実施形態による積層コンデンサ31bは、第1および第2の側面36および37の長さ方向に関して、同一面内にある第1の内部電極42の引出し部52と第3の内部電極44の引出し部54とが隣り合い、かつ、同一面内にある第2の内部電極43の引出し部53と第4の内部電極45の引出し部55とが隣り合うように配置されていることを特徴としている。この第3の実施形態によれば、前述した第1の実施形態に比べて、同一面内における磁界相殺の効果が高くなる。

【0075】

図8は、この発明の第4の実施形態による積層コンデンサ31cを説明するための図3に対応する図である。なお、図8において、(a)〜(d)は積層順序をも示している。図8において、図3に示した要素に相当する要素には同様の参照符号を付し、重複する説明は省略する。

【0076】

第4の実施形態による積層コンデンサ31cでは、少なくとも第1および第2の内部電極42および43については、積層方向に複数組配置される。そして、図8(a)に示すように、複数の第1の内部電極42のうちの一部については、同一面内に、第3の内部電極44を位置させておらず、また、図8(b)に示すように、複数の第2の内部電極43のうちの一部については、同一面内に、第4の内部電極45を位置させていないことを特徴としている。

【0077】

この実施形態では、好ましくは、積層体33において、上から、所定枚数の外層用誘電体層、図8(a)および(b)に示したパターンの所定回数の繰り返し、図8(c)および(d)に示したパターンの所定回数の繰り返し、図8(a)および(b)に示したパターンの所定回数の繰り返し、所定枚数の外層用誘電体層、といった積層順序が採用される。

【0078】

この第4の実施形態によれば、第3および第4の内部電極44および45の積層枚数を減らすことにより、第1のコンデンサ部46に比べて、第2のコンデンサ部47の容量が小さくなる。このように、第1および第2のコンデンサ部46および47間で容量を異ならせることにより、コンデンサ部46および47の各々の共振周波数を互いに異ならせることができ、そのため、より広い周波数帯域においてデカップリングコンデンサとしての機能を実現することが可能となる。

【0079】

図9および図10は、この発明の第5の実施形態による積層コンデンサ31dを説明するためのもので、それぞれ、図2および図3に対応する図である。図9および図10において、図2および図3に示した要素に相当する要素には同様の参照符号を付し、重複する説明は省略する。

【0080】

第5の実施形態による積層コンデンサ31dは、第1および第2の内部電極42および43の各々の容量形成部48および49の面積と、第3および第4の内部電極44および45の各々の容量形成部50および51とが互いに異なることを特徴としている。より具体的には、第1および第2の内部電極42および43の各々の容量形成部48および49の面積に比べて、第3および第4の内部電極44および45の各々の容量形成部50および51の面積がより大きくされる。その結果、第1のコンデンサ部46に比べて、第2のコンデンサ部47の容量が大きくなる。また、第1および第2の内部電極42および43に比べて、第3および第4の内部電極44および45の各々の引出し部54および55の数が増やされ、積層コンデンサ31d全体として、合計10個の外部端子電極40および41が形成される。

【0081】

この第5の実施形態によれば、第4の実施形態の場合と同様、第1および第2のコンデンサ部46および47間で容量を異ならせることにより、第1および第2のコンデンサ部46および47間で共振周波数を互いに異ならせることができるので、より広い周波数帯域においてデカップリングコンデンサとしての機能を実現することが可能となる。また、第2のコンデンサ部47において、一層の低ESL化を図ることができる。

【0082】

図11および図12は、この発明の第6の実施形態による積層コンデンサ31eを説明するためのもので、それぞれ、図2および図3に対応する図である。図11および図12において、図2および図3に示した要素に相当する要素には同様の参照符号を付し、重複する説明は省略する。

【0083】

第6の実施形態による積層コンデンサ31eは、第5および第6の内部電極56および57が追加され、それによって、第3のコンデンサ部58がさらに形成されることを特徴としている。

【0084】

第5および第6の内部電極56および57は、それぞれ、特定の誘電体層32を介して互いに対向する容量形成部59および60を有している。また、第5の内部電極56は、容量形成部59から第1および第2の側面36および37に露出するように引き出されて外部端子電極40−5および40−6に電気的に接続される2つの引出し部61を有している。また、第6の内部電極57は、容量形成部60から第1および第2の側面36および37に露出するように引き出されて外部端子電極41−5および41−6に電気的に接続される2つの引出し部62を有している。

【0085】

そして、第5の内部電極56の引出し部61と第6の内部電極57の引出し部62とは、第1および第2の側面36および37の長さ方向に関して交互に露出するように配置される。

【0086】

また、第1、第3および第5の内部電極42、44および56は、図12(a)に示すように、同一面内において、第1および第2の側面36および37の長さ方向に並びながら、互いの間に所定の間隔を隔てて配置される。同様に、第2、第4および第6の内部電極43、45および57は、図12(b)に示すように、同一面内において、第1および第2の側面36および37の長さ方向に並びながら、互いの間に所定の間隔を隔てて配置される。

【0087】

また、図12(a)および同(b)をともに参照すればわかるように、誘電体層32の積層方向で見たとき、第5の内部電極56の容量形成部59は第2および第4の内部電極43および45の容量形成部49および51のいずれとも重なり合わず、また、第6の内部電極57の容量形成部60は第1および第3の内部電極42および44の容量形成部48および50のいずれとも重なり合わないように配置されている。

【0088】

このようにコンデンサ部の数を増やしながら、たとえば、第1ないし第3のコンデンサ部46、47および48間で容量を異ならせると、より広い周波数帯域においてデカップリングコンデンサとしての機能を実現することができる。また、コンデンサ部46、47および58のそれぞれが互いに独立しているため、コンデンサ部の数を3個に限らず、さらに任意に増やしていくことが可能であり、設計の自由度が高い。

【図面の簡単な説明】

【0089】

【図1】この発明の第1の実施形態による積層コンデンサ31の外観を示す斜視図である。

【図2】図1に示した積層コンデンサ31の外観を示す平面図である。

【図3】図1に示した積層コンデンサ31の内部構造を、内部電極が通る断面をもって示す平面図である。

【図4】図3において、電流の流れの一例を破線の矢印で加えた図である。

【図5】図1に示した積層コンデンサをデカップリング回路に組み込んだ状態を示す回路図である。

【図6】この発明の第2の実施形態による積層コンデンサ31aを説明するための図3に対応する図である。

【図7】この発明の第3の実施形態による積層コンデンサ31bを説明するための図4に対応する図である。

【図8】この発明の第4の実施形態による積層コンデンサ31cを説明するための図3に対応する図である。

【図9】この発明の第5の実施形態による積層コンデンサ31dを説明するための図2に対応する図である。

【図10】図9に示した積層コンデンサ31dを説明するための図3に対応する図である。

【図11】この発明の第6の実施形態による積層コンデンサ31eを説明するための図2に対応する図である。

【図12】図11に示した積層コンデンサ31eを説明するための図3に対応する図である。

【図13】特許文献1において開示された積層コンデンサ8の内部構造を、内部電極が通る断面をもって示す平面図である。

【図14】特許文献2において開示された積層コンデンサ14の内部構造を、内部電極が通る断面をもって示す平面図である。

【図15】特許文献3に開示された積層コンデンサ24の内部構造を、内部電極が通る断面をもって示す平面図である。

【図16】特許文献3において開示された他の積層コンデンサ24aの内部構造を、内部電極が通る断面をもって示す平面図である。

【符号の説明】

【0090】

31,31a,31b,31c,31d,31e 積層コンデンサ

32 誘電体層

33 積層体

36 第1の側面

37 第2の側面

40 第1の外部端子電極

41 第2の外部端子電極

42 第1の内部電極

43 第2の内部電極

44 第3の内部電極

45 第4の内部電極

46 第1のコンデンサ部

47 第2のコンデンサ部

48〜51,59,60 容量形成部

52〜55,61,62 引出し部

56 第5の内部電極

57 第6の内部電極

58 第3のコンデンサ部

【特許請求の範囲】

【請求項1】

積層された複数の誘電体層をもって構成され、かつ相対向する第1および第2の側面を有する、直方体状の積層体と、

前記第1および第2の側面上に形成される、複数の外部端子電極と

を備え、

前記積層体の内部には、第1のコンデンサ部を形成するため、第1および第2の内部電極が形成されるとともに、第2のコンデンサ部を形成するため、第3および第4の内部電極が形成され、

前記第1および第2の内部電極は、それぞれ、特定の前記誘電体層を介して互いに対向する容量形成部と、前記容量形成部から前記第1および第2の側面に露出するように引き出されて特定の前記外部端子電極に電気的に接続される2つ以上の引出し部とを有し、前記第1の内部電極の前記引出し部と前記第2の内部電極の前記引出し部とは、前記第1および第2の側面の長さ方向に関して交互に露出するように配置され、

前記第3および第4の内部電極は、それぞれ、特定の前記誘電体層を介して互いに対向する容量形成部と、前記容量形成部から前記第1および第2の側面に露出するように引き出されて特定の前記外部端子電極に電気的に接続される2つ以上の引出し部とを有し、前記第3の内部電極の前記引出し部と前記第4の内部電極の前記引出し部とは、前記第1および第2の側面の長さ方向に関して交互に露出するように配置され、

前記第1および第3の内部電極は、前記第1および第2の側面の長さ方向に並びながら、互いの間に所定の間隔を隔てて配置され、

前記第2および第4の内部電極は、前記第1および第2の側面の長さ方向に並びながら、互いの間に所定の間隔を隔てて配置され、

前記誘電体層の積層方向で見たとき、前記第1の内部電極の前記容量形成部と前記第4の内部電極の前記容量形成部とは重なり合わず、前記第2の内部電極の前記容量形成部と前記第3の内部電極の前記容量形成部とは重なり合わない、

積層コンデンサ。

【請求項2】

前記第1および第2の側面の長さ方向に関して、前記第1の内部電極の前記引出し部と前記第3の内部電極の前記引出し部とが隣り合い、かつ、前記第2の内部電極の前記引出し部と前記第4の内部電極の前記引出し部とが隣り合うように配置される、請求項1に記載の積層コンデンサ。

【請求項3】

前記第1および第3の内部電極は同一面内に位置され、かつ、前記第2および第4の内部電極は同一面内に位置される、請求項1または2に記載の積層コンデンサ。

【請求項4】

前記第1および第2の内部電極は積層方向に複数組配置され、複数の前記第1の内部電極のうちの一部については、同一面内に、前記第3の内部電極を位置させておらず、複数の前記第2の内部電極のうちの一部については、同一面内に、前記第4の内部電極を位置させていない、請求項3に記載の積層コンデンサ。

【請求項5】

前記第1および第3の内部電極は積層方向にずれて位置され、かつ、前記第2および第4の内部電極は積層方向にずれて位置される、請求項1または2に記載の積層コンデンサ。

【請求項6】

前記第1および第2の内部電極の各々の容量形成部の面積と前記第3および第4の内部電極の各々の容量形成部の面積とは互いに異なる、請求項1ないし5のいずれかに記載の積層コンデンサ。

【請求項7】

面積がより広い方の前記容量形成部を有する前記内部電極の前記引出し部の数は、面積がより狭い方の前記容量形成部を有する前記内部電極の前記引出し部の数より多い、請求項6に記載の積層コンデンサ。

【請求項8】

前記積層体の内部には、第3のコンデンサ部を形成するため、第5および第6の内部電極がさらに形成され、

前記第5および第6の内部電極は、それぞれ、特定の前記誘電体層を介して互いに対向する容量形成部と、前記容量形成部から前記第1および第2の側面に露出するように引き出されて特定の前記外部端子電極に電気的に接続される2つ以上の引出し部とを有し、前記第5の内部電極の前記引出し部と前記第6の内部電極の前記引出し部とは、前記第1および第2の側面の長さ方向に関して交互に露出するように配置され、

前記第1、第3および第5の内部電極は、前記第1および第2の側面の長さ方向に並びながら、互いの間に所定の間隔を隔てて配置され、

前記第2、第4および第6の内部電極は、前記第1および第2の側面の長さ方向に並びながら、互いの間に所定の間隔を隔てて配置され、

前記誘電体層の積層方向で見たとき、前記第5の内部電極の前記容量形成部は前記第2および第4の内部電極のいずれの前記容量形成部とも重なり合わず、前記第6の内部電極の前記容量形成部は前記第1および第3の内部電極のいずれの前記容量形成部とも重なり合わない、

請求項1ないし7のいずれかに記載の積層コンデンサ。

【請求項1】

積層された複数の誘電体層をもって構成され、かつ相対向する第1および第2の側面を有する、直方体状の積層体と、

前記第1および第2の側面上に形成される、複数の外部端子電極と

を備え、

前記積層体の内部には、第1のコンデンサ部を形成するため、第1および第2の内部電極が形成されるとともに、第2のコンデンサ部を形成するため、第3および第4の内部電極が形成され、

前記第1および第2の内部電極は、それぞれ、特定の前記誘電体層を介して互いに対向する容量形成部と、前記容量形成部から前記第1および第2の側面に露出するように引き出されて特定の前記外部端子電極に電気的に接続される2つ以上の引出し部とを有し、前記第1の内部電極の前記引出し部と前記第2の内部電極の前記引出し部とは、前記第1および第2の側面の長さ方向に関して交互に露出するように配置され、

前記第3および第4の内部電極は、それぞれ、特定の前記誘電体層を介して互いに対向する容量形成部と、前記容量形成部から前記第1および第2の側面に露出するように引き出されて特定の前記外部端子電極に電気的に接続される2つ以上の引出し部とを有し、前記第3の内部電極の前記引出し部と前記第4の内部電極の前記引出し部とは、前記第1および第2の側面の長さ方向に関して交互に露出するように配置され、

前記第1および第3の内部電極は、前記第1および第2の側面の長さ方向に並びながら、互いの間に所定の間隔を隔てて配置され、

前記第2および第4の内部電極は、前記第1および第2の側面の長さ方向に並びながら、互いの間に所定の間隔を隔てて配置され、

前記誘電体層の積層方向で見たとき、前記第1の内部電極の前記容量形成部と前記第4の内部電極の前記容量形成部とは重なり合わず、前記第2の内部電極の前記容量形成部と前記第3の内部電極の前記容量形成部とは重なり合わない、

積層コンデンサ。

【請求項2】

前記第1および第2の側面の長さ方向に関して、前記第1の内部電極の前記引出し部と前記第3の内部電極の前記引出し部とが隣り合い、かつ、前記第2の内部電極の前記引出し部と前記第4の内部電極の前記引出し部とが隣り合うように配置される、請求項1に記載の積層コンデンサ。

【請求項3】

前記第1および第3の内部電極は同一面内に位置され、かつ、前記第2および第4の内部電極は同一面内に位置される、請求項1または2に記載の積層コンデンサ。

【請求項4】

前記第1および第2の内部電極は積層方向に複数組配置され、複数の前記第1の内部電極のうちの一部については、同一面内に、前記第3の内部電極を位置させておらず、複数の前記第2の内部電極のうちの一部については、同一面内に、前記第4の内部電極を位置させていない、請求項3に記載の積層コンデンサ。

【請求項5】

前記第1および第3の内部電極は積層方向にずれて位置され、かつ、前記第2および第4の内部電極は積層方向にずれて位置される、請求項1または2に記載の積層コンデンサ。

【請求項6】

前記第1および第2の内部電極の各々の容量形成部の面積と前記第3および第4の内部電極の各々の容量形成部の面積とは互いに異なる、請求項1ないし5のいずれかに記載の積層コンデンサ。

【請求項7】

面積がより広い方の前記容量形成部を有する前記内部電極の前記引出し部の数は、面積がより狭い方の前記容量形成部を有する前記内部電極の前記引出し部の数より多い、請求項6に記載の積層コンデンサ。

【請求項8】

前記積層体の内部には、第3のコンデンサ部を形成するため、第5および第6の内部電極がさらに形成され、

前記第5および第6の内部電極は、それぞれ、特定の前記誘電体層を介して互いに対向する容量形成部と、前記容量形成部から前記第1および第2の側面に露出するように引き出されて特定の前記外部端子電極に電気的に接続される2つ以上の引出し部とを有し、前記第5の内部電極の前記引出し部と前記第6の内部電極の前記引出し部とは、前記第1および第2の側面の長さ方向に関して交互に露出するように配置され、

前記第1、第3および第5の内部電極は、前記第1および第2の側面の長さ方向に並びながら、互いの間に所定の間隔を隔てて配置され、

前記第2、第4および第6の内部電極は、前記第1および第2の側面の長さ方向に並びながら、互いの間に所定の間隔を隔てて配置され、

前記誘電体層の積層方向で見たとき、前記第5の内部電極の前記容量形成部は前記第2および第4の内部電極のいずれの前記容量形成部とも重なり合わず、前記第6の内部電極の前記容量形成部は前記第1および第3の内部電極のいずれの前記容量形成部とも重なり合わない、

請求項1ないし7のいずれかに記載の積層コンデンサ。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【公開番号】特開2008−117990(P2008−117990A)

【公開日】平成20年5月22日(2008.5.22)

【国際特許分類】

【出願番号】特願2006−301137(P2006−301137)

【出願日】平成18年11月7日(2006.11.7)

【出願人】(000006231)株式会社村田製作所 (3,635)

【Fターム(参考)】

【公開日】平成20年5月22日(2008.5.22)

【国際特許分類】

【出願日】平成18年11月7日(2006.11.7)

【出願人】(000006231)株式会社村田製作所 (3,635)

【Fターム(参考)】

[ Back to top ]