積層セラミックコンデンサおよびこれを用いたジャンパ実装構造

【課題】 従来の積層セラミックコンデンサを用いると、両面回路基板の表面に実装された、電源およびグランド接続端子が信号線接続端子よりも内側に配置された負荷ICへ、両面回路基板の裏面において電源配線をジャンパ接続することができない。

【解決手段】 積層セラミックコンデンサ31の胴体部分の長さが、負荷IC41の信号線接続端子群42aにつながる基板裏面に形成された信号線配線パターンの形成領域を跨ぐ長さに単に設定されることで、胴体部分が信号線配線パターンに電気接触することなく、長手方向両側の一方の外部電極34a,34bが、基板裏面の電源配線パターン51と、負荷IC41の電源接続端子42につながるビアホールとに接続される。また、長手方向両側の他方の外部電極35a,35bが、基板裏面のグランド配線パターン52と、負荷IC41のグランド接続端子42につながるビアホールとに接続される。

【解決手段】 積層セラミックコンデンサ31の胴体部分の長さが、負荷IC41の信号線接続端子群42aにつながる基板裏面に形成された信号線配線パターンの形成領域を跨ぐ長さに単に設定されることで、胴体部分が信号線配線パターンに電気接触することなく、長手方向両側の一方の外部電極34a,34bが、基板裏面の電源配線パターン51と、負荷IC41の電源接続端子42につながるビアホールとに接続される。また、長手方向両側の他方の外部電極35a,35bが、基板裏面のグランド配線パターン52と、負荷IC41のグランド接続端子42につながるビアホールとに接続される。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、信号線接続端子が基板実装面の外周側、電源接続端子および基準電位接続端子が信号線接続端子よりも内側に配置された負荷ICへ電源配線をジャンパ接続する積層セラミックコンデンサ、およびこれを用いたジャンパ実装構造に関するものである。

【背景技術】

【0002】

従来、積層セラミックコンデンサ構造を用いた貫通コンデンサとして、特許文献1に開示された3端子コンデンサがある。この種の3端子コンデンサは、コンデンサ長手方向の両側に設けられたホット外部電極間を導通させる貫通内部電極をコンデンサ内部に有する。また、この貫通内部電極との間で静電容量を形成するグランド内部電極をコンデンサ内部に有し、このグランド内部電極に接続されるグランド外部電極を、コンデンサ長手方向に直交する短手方向の両側に有する。

【0003】

3端子コンデンサ1は、例えば、図1(a)の斜視図に示すように、回路基板2に実装される。回路基板2には、スイッチングレギュレータIC3、パワーインダクタ4、および電解コンデンサ5からなるDC/DCコンバータモジュール6が回路電源として構成されている。DC/DCコンバータモジュール6から出力される電源は、電源供給側電源配線パターン7、3端子コンデンサ1、および負荷側電源配線パターン8を経由して、終端負荷IC(Integrated Circuit:LSI(Large Scale Integrated Circuit)を含む)9へ供給される。この際、3端子コンデンサ1は、電源供給側電源配線パターン7と負荷側電源配線パターン8との間に形成されたグランド配線パターン10をジャンパして、ホット外部電極1a,1bが電源配線パターン7,8に接続され、また、グランド外部電極1c,1dが共にグランド配線パターン10に接続される。

【0004】

このときの3端子コンデンサ1の挿入損失特性は、図1(b)に示す3端子コンデンサ1の概略斜視図のように、貫通内部電極11aの信号伝搬方向に対する誘導成分Lと、グランド内部電極11bに対する容量成分Cとにより構成される伝送線路型フィルタとなる。この伝送線路型フィルタの等価回路図は図1(c)に示され、電源配線パターン7,8によって終端負荷IC9へ供給される電源に重畳する高周波ノイズは、3端子コンデンサ1自身が持つ挿入損失特性によって除去される。

【0005】

ところで、回路基板の高密度実装化に伴い、ICのパッケージにはBGA(Ball Grid Array)パッケージが用いられている。BGAパッケージの負荷IC22は、例えば、図2(a)の断面図に示すように回路基板21の表面に実装され、通常、その基板実装面に形成されたボール状接続端子23がビアホール24によって回路基板21に多層に形成された各内層25に接続され、配線接続される。しかし、電子部品を用いて構成される完成品セットの最近のコストダウン競争により、完成品セットに用いられている多層回路基板21も層数削減を迫られている。このため、多端子の負荷IC22も、図2(b)の断面図に示すように、安価な両面回路基板26に実装されるようになっている。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開平10−154632号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

BGAパッケージの負荷IC22は、図3(a)の裏面図に示すように、基板実装面に複数のボール状接続端子23が面状に配置され、ボール状接続端子23の中の高周波信号を取り扱う信号線接続端子群23aが優先的に基板実装面の外周側に配置されている。ボール状接続端子23の中の電源およびグランド接続端子群23bは、信号線接続端子群23aよりも内側に集中して配置されている。

【0008】

このため、内側に集中配置された電源およびグランド接続端子群23bを図2(b)に示すような両面回路基板26の回路各部と接続するには、必ず、ビアホール27を介して電源およびグランド接続端子群23bを回路基板26の裏面に露出させて、図3(b)に示すように負荷側電源・グランド配線パターン28に接続する。そして、信号線接続端子群23aがビアホール27を介して回路基板26の裏面に露出する領域を跨いで、負荷側電源・グランド配線パターン28を電源供給側電源・グランド配線パターン29に接続しなければならない。

【0009】

この場合、図1(a)に示す回路基板2のように3端子コンデンサ1を用いて、負荷側電源・グランド配線パターン28と電源供給側電源・グランド配線パターン29との間をジャンパ接続しようとしても、3端子コンデンサ1のホット外部電極1a,1b間に形成された貫通内部電極11aの長さが足りず、ジャンパ接続できない。また、この貫通内部電極11aの長さを単に長くしても、3端子コンデンサ1の胴体部分に形成されたグランド外部電極1c,1dが、信号線接続端子群23aにビアホール27を介してつながる、回路基板26の裏面に露出する図示しない信号線配線パターンに電気接触してしまい、ジャンパ接続できない。

【0010】

また、3端子コンデンサ1を用いずに、負荷側と電源供給側の電源・グランド配線パターン28,29の間を配線パターンで接続するには、信号線接続端子群23aにつながる多くの信号線配線パターンの間を縫って、非常に細い配線パターンで接続しなければならず、電源配線の直流抵抗が高くなって好ましくない。

【課題を解決するための手段】

【0011】

本発明はこのような課題を解決するためになされたもので、

長手方向の両側に形成された互いに導通する一方の外部電極と、長手方向の両側に一方の外部電極と電気的に絶縁されて形成された互いに導通する他方の外部電極と、長手方向の両側に形成された各外部電極間に構成された絶縁体で覆われた胴体部分とを備える積層セラミックコンデンサを構成した。

【0012】

また、本発明は、

基板実装面に複数の接続端子が面状に配置され、複数の接続端子の中の信号線接続端子が基板実装面の外周側、複数の接続端子の中の電源接続端子および基準電位接続端子が信号線接続端子よりも内側の基板実装面に配置された負荷ICが回路基板の一方の基板面に実装され、

長手方向の両側に互いに導通する一方の外部電極、長手方向の両側に一方の外部電極と電気的に絶縁された互いに導通する他方の外部電極が形成され、長手方向の両側に形成された各外部電極間の胴体部分が絶縁体で覆われた積層セラミックコンデンサが回路基板の他方の基板面に実装され、

信号線接続端子にビアホールを介して接続される他方の基板面に形成された信号線配線パターンを胴体部分が跨り、

長手方向一端側の一方の外部電極が他方の基板面に形成された電源配線パターンに接続され、長手方向他端側の一方の外部電極がビアホールを介して電源接続端子に接続され、長手方向一端側の他方の外部電極が他方の基板面に形成された基準電位配線パターンに接続され、長手方向他端側の他方の外部電極がビアホールを介して基準電位接続端子に接続される

ジャンパ実装構造を構成した。

【0013】

本構成によれば、積層セラミックコンデンサの絶縁体で覆われた胴体部分の長さが、負荷ICの信号線接続端子群につながる基板裏面に形成された信号線配線パターンの形成領域を跨ぐ長さに単に設定されることで、胴体部分が信号線配線パターンに電気接触することなく信号線配線パターンの形成領域を跨いで、積層セラミックコンデンサの長手方向の両側に形成された一方の外部電極のそれぞれが、基板裏面に形成された電源供給側電源配線パターンと、負荷ICの電源接続端子につながるビアホールとに接続される。また、長手方向の両側に形成された他方の外部電極のそれぞれが、基板裏面に形成された電源供給側基準電位配線パターンと、負荷ICの基準電位接続端子につながるビアホールとに接続される。このため、電源供給側電源配線パターンと負荷ICの電源接続端子につながるビアホールとの間は、積層セラミックコンデンサの長手方向の両側に形成された互いに導通する一方の外部電極により、電源配線の直流抵抗が高くなることなく、ジャンパ接続される。また、電源供給側基準電位配線パターンと負荷ICの基準電位接続端子につながるビアホールとの間は、積層セラミックコンデンサの長手方向の両側に形成された互いに導通する他方の外部電極により、基準電位配線の直流抵抗が高くなることなく、ジャンパ接続される。

【0014】

また、負荷ICの電源接続端子につながるビアホールと電源供給側電源配線パターンとの間に積層セラミックコンデンサの一方の外部電極間の内部電極が介在させられ、負荷ICの基準電位接続端子につながるビアホールと電源供給側基準電位配線パターンとの間に積層セラミックコンデンサの他方の外部電極間の内部電極が介在させられる。このため、一方の外部電極間および他方の外部電極間の双方の内部電極において信号伝搬方向に対する誘導成分Lが分布定数的に生じ、また、これらの内部電極間に容量成分Cが分布定数的に生じて、従来の3端子コンデンサによる伝送線路型フィルタに比べて信号伝搬方向に対する誘導成分Lの大きな伝送線路型フィルタが構成される。このため、負荷ICの基板実装面の内側に孤立して配置された電源接続端子および基準電位接続端子形成領域に、負荷ICの電源接続端子および基準電位接続端子間に発生した高周波ノイズを閉じ込め、また、負荷ICから外に出ようとする高周波ノイズを分布定数的に低減させることが可能になる。また、積層セラミックコンデンサは電源および基準電位間のデカップリングコンデンサとしても働き、分布定数的に生じる容量成分Cに蓄えられる電荷が電圧低下時に放出されることにより、電圧変動の抑制も可能になる。

【0015】

また、本発明は、外部電極が、積層セラミックコンデンサが実装される回路基板表面から胴体部分を浮かせる形状を有することを特徴とする。

【0016】

積層セラミックコンデンサの胴体部分が細長く形成されることにより、回路基板に生じるたわみによって回路基板に実装された積層セラミックコンデンサの胴体部分に応力が加わり、胴体部分が折れるのが懸念される。しかし、本構成によれば、外部電極によって胴体部分が回路基板表面から浮かせられるため、回路基板に生じるたわみによる応力は胴体部分に直接伝わらず、外部電極に加わる。このため、外部電極おいて、回路基板に生じるたわみによる応力を吸収することで、積層セラミックコンデンサの胴体部分が折れるのを防止することが出来る。

【0017】

また、本発明は、一方の外部電極と他方の外部電極との形成される個数が異なることを特徴とする。

【0018】

また、本発明は、積層セラミックコンデンサが3端子コンデンサであり、一方の外部電極が長手方向を貫通する貫通内部電極に接続されるホット外部電極であり、他方の外部電極が、貫通内部電極と静電容量を形成するグランド内部電極に接続されるグランド外部電極であって、長手方向の一端側と他端側とに分割されていることを特徴とする。

【0019】

これらの各構成によっても、積層セラミックコンデンサの絶縁体で覆われた胴体部分の長さが、負荷ICの信号線接続端子群につながる基板裏面に形成された信号線配線パターンの形成領域を跨ぐ長さに単に設定されることで、上記各効果を有する積層セラミックコンデンサおよびこれを用いたジャンパ実装構造が提供される。

【発明の効果】

【0020】

本発明によれば、上記のように、積層セラミックコンデンサの胴体部分が信号線配線パターンに電気接触することなく信号線配線パターンの形成領域を跨いで、配線の直流抵抗が高くなることなく、負荷ICの基板実装面内側に配置された電源および基準電位接続端子につながるビアホールと電源供給側配線パターンとの間をジャンパ接続することが可能な積層セラミックコンデンサ、およびこれを用いたジャンパ実装構造が提供される。

【図面の簡単な説明】

【0021】

【図1】(a)は従来の積層セラミックコンデンサを用いたジャンパ実装構造を示す斜視図、(b)は(a)に示す積層セラミックコンデンサに生じる誘導成分および容量成分の構成を示す概略斜視図、(c)は(b)に示す積層セラミックコンデンサの等価回路図である。

【図2】(a)は一般的な多層回路基板の断面図、(b)は一般的な両面回路基板の断面図である。

【図3】(a)はBGAパッケージICの基板実装面の平面図、(b)は(a)に示すBGAパッケージICを両面回路基板に実装する際に生じる問題点を説明するための断面図である。

【図4】(a)は本発明の一実施の形態による積層セラミックコンデンサの外観斜視図、(b)はその内部構成を示す分解斜視図である。

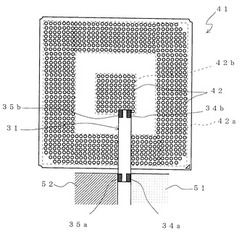

【図5】本発明の一実施の形態による積層セラミックコンデンサを用いたジャンパ実装構造を示す回路基板の裏面図である。

【図6】(a)は図5に示す積層セラミックコンデンサに生じる誘導成分および容量成分の構成を示す概略斜視図、(b)は(a)に示す積層セラミックコンデンサの等価回路図である。

【図7】(a)は本発明の効果を確認するために用いられた積層セラミックコンデンサ構造を示す図、(b)は(a)に示す積層セラミックコンデンサの挿入損失特性を従来品と比較した測定結果を示すグラフである。

【図8】(a)は一実施の形態の第1の変形例による積層セラミックコンデンサの外観斜視図、(b)は一実施の形態の第2の変形例による積層セラミックコンデンサの外観斜視図、(c)は一実施の形態の第3の変形例による積層セラミックコンデンサの外観斜視図である。

【発明を実施するための形態】

【0022】

次に、本発明の一実施の形態による積層セラミックコンデンサおよびこれを用いたジャンパ実装構造について、説明する。

【0023】

図4(a)は、本実施の形態による積層セラミックコンデンサの外観斜視図、同図(b)はその内部構成を示す分解斜視図である。

【0024】

積層セラミックコンデンサ31は、表面実装型のチップ・コンデンサであり、セラミック層32が積層されて略直方体の形状をした誘電体33の長手方向の両側に、一方の外部電極34a,34bと他方の外部電極35a,35bとを備える。また、長手方向の両側に形成された各外部電極34a,34bおよび35a,35b間には、誘電体33からなる絶縁体で覆われた胴体部分が構成されている。

【0025】

誘電体33の内部において、各セラミック層32には、一方の外部電極34a,34bの形成側の長辺に寄った内部電極34cと、他方の外部電極35a,35bの形成側の長辺に寄った内部電極35cとが、交互に形成されている。一方の外部電極34a,34bは、セラミック層32に形成された複数の内部電極34cによって互いに導通する。他方の外部電極35a,35bは、セラミック層32に形成された複数の内部電極35cによって互いに導通し、一方の外部電極34a,34bと電気的に絶縁されている。

【0026】

図5は、上記のような構成をした積層セラミックコンデンサ31を用いた本実施の形態によるャンパ実装構造を示す回路基板の裏面図である。なお、回路基板は、内層を有しない両面回路基板であり、同図では図示されておらず、透視された状態が示されている。

【0027】

両面回路基板の表面の一方の基板面には、BGAパッケージの負荷IC(LSIを含む)41が実装されている。負荷IC41は、基板実装面に複数のボール状接続端子42が面状に配置され、複数のボール状接続端子42の中の信号線接続端子群42aが基板実装面の外周側、複数のボール状接続端子42の中の電源およびグランド接続端子群42bが信号線接続端子群42aよりも内側の基板実装面に配置されている。

【0028】

また、両面回路基板の裏面の他方の基板面には、上記の積層セラミックコンデンサ31が実装されており、また、DC/DCコンバータの出力電源およびグランドにつながる電源供給側電源配線パターン51および電源供給側グランド配線パターン52が形成されている。負荷IC41の信号線接続端子群42aは、両面回路基板に形成された図示しないビアホールを介して両面回路基板の裏面に導出され、両面回路基板の裏面に形成された図示しない信号線配線パターンに接続される。積層セラミックコンデンサ31は、この信号線配線パターンを胴体部分が跨り、両面回路基板の裏面に実装されている。

【0029】

また、積層セラミックコンデンサ31の長手方向一端側の一方の外部電極34aは電源供給側電源配線パターン51に接続され、長手方向他端側の一方の外部電極34bは、両面回路基板に形成された図示しないビアホールを介して、電源およびグランド接続端子群42bの中の電源接続端子42に接続されている。また、長手方向一端側の他方の外部電極35aは電源供給側グランド配線パターン52に接続され、長手方向他端側の他方の外部電極35bは、両面回路基板に形成された図示しないビアホールを介して、電源およびグランド接続端子群42bの中のグランド接続端子42に接続されている。

【0030】

このような本実施の形態によれば、積層セラミックコンデンサ31の絶縁体で覆われた胴体部分の誘電体33の長さが、負荷IC41の信号線接続端子群42aにつながる基板裏面に形成された信号線配線パターンの形成領域を跨ぐ長さに単に設定されることで、胴体部分が信号線配線パターンに電気接触することなく信号線配線パターンの形成領域を跨いで、積層セラミックコンデンサ31の長手方向の両側に形成された一方の外部電極34a,34bのそれぞれが、基板裏面に形成された電源供給側電源配線パターン51と、負荷IC41の電源接続端子42につながるビアホールとに接続される。また、長手方向の両側に形成された他方の外部電極35a,35bのそれぞれが、基板裏面に形成された電源供給側グランド配線パターン52と、負荷IC41のグランド接続端子42につながるビアホールとに接続される。このため、電源供給側電源配線パターン51と負荷IC41の電源接続端子42につながるビアホールとの間は、積層セラミックコンデンサ31の長手方向の両側に形成された互いに導通する一方の外部電極34a,34bにより、電源配線の直流抵抗が高くなることなく、ジャンパ接続される。また、電源供給側グランド配線パターン52と負荷IC41のグランド接続端子42につながるビアホールとの間は、積層セラミックコンデンサ41の長手方向の両側に形成された互いに導通する他方の外部電極35a,35bにより、グランド配線の直流抵抗が高くなることなく、ジャンパ接続される。

【0031】

また、負荷IC41の電源接続端子42につながるビアホールと電源供給側電源配線パターン51との間に積層セラミックコンデンサ31の一方の外部電極34a,34b間の内部電極34cが介在させられ、負荷IC41のグランド接続端子42につながるビアホールと電源供給側グランド配線パターン52との間に積層セラミックコンデンサ31の他方の外部電極35a,35b間の内部電極35cが介在させられる。このため、図6(a)に示すように、一方の外部電極34a,34b間および他方の外部電極35a,35b間の双方の内部電極34c,35cにおいて信号伝搬方向に対する誘導成分Lが分布定数的に生じ、また、これらの内部電極34c,35c間に容量成分Cが分布定数的に生じて、従来の3端子コンデンサによる伝送線路型フィルタに比べて信号伝搬方向に対する誘導成分Lの大きな伝送線路型フィルタが構成される。図6(b)はこの伝送線路型フィルタの等価回路図を示す。このため、負荷IC41の基板実装面の内側に孤立して配置された電源およびグランド接続端子群42bの形成領域に、負荷IC41の電源接続端子42およびグランド接続端子42間に発生した高周波ノイズを閉じ込め、また、負荷IC41から外に出ようとする高周波ノイズを分布定数的に低減させることが可能になる。また、積層セラミックコンデンサ31は電源およびグランド間のデカップリングコンデンサとしても働き、分布定数的に生じる容量成分Cに蓄えられる電荷が電圧低下時に放出されることにより、電圧変動の抑制も可能になる。

【0032】

上述した積層セラミックコンデンサ31を用いた本実施の形態によるャンパ実装構造により奏される効果を確認するため、ノイズ対策効果を定量的に示す量である挿入損失の周波数特性を測定した。

【0033】

この測定では、ジャンパ型伝送線路コンデンサとして機能する上述した積層セラミックコンデンサ31を、図7(a)に示すように、1005サイズ(長辺1.0mm×短辺0.5mm)で容量が0.1μFのLW逆転コンデンサ61を10個並列に並べて、模擬構成した。LW逆転コンデンサ61は、一方の外部電極61aおよび他方の外部電極61bが略直方体形状をした誘電体62の長手方向に沿って平行に形成されている。

【0034】

図7(b)に示すグラフは、測定結果を示し、横軸は周波数(Frequency)[MHz]、縦軸は挿入損失(Insertion Loss)[dB]を示す。また、実線で示す特性線65は、上記のように模擬構成した本実施の形態によるジャンパ型伝送線路コンデンサについての挿入損失の測定結果、点線で示す特性線66は、従来仕様の3端子コンデンサについての挿入損失の測定結果を表す。従来仕様の3端子コンデンサは、1608サイズ(長辺1.6mm×短辺0.8mm)で容量が1μFの図1に示す従来品の伝送線路コンデンサである。

【0035】

同グラフに示されるように、特性線65で表される本実施の形態によるジャンパ型伝送線路コンデンサは、特性線66で表される従来仕様の3端子コンデンサとほぼ同等の性能を示しているが、高周波領域では本実施の形態によるジャンパ型伝送線路コンデンサの挿入損失が大きくなり、従来仕様の3端子コンデンサを一部上回る性能を示している。これは、図6(b)に等価回路図が表される本実施の形態によるジャンパ型伝送線路コンデンサは、図1(c)に等価回路図が表される従来仕様の3端子コンデンサに比べ、グランド側外部電極35a,35b間の信号伝搬方向に誘導成分Lが分布定数的に生じるからである。

【0036】

本測定で模擬構成した積層セラミックコンデンサは、図7(a)に示すように一方の外部電極61aおよび他方の外部電極61bが長手方向の両側辺に連なって形成されているため、信号伝搬方向に生じる誘導成分Lは実際の製品より小さくなっている。しかし、これら連なる外部電極61aおよび61bを本実施の形態のように長手方向の両端側に分離させて形成することで、実際の製品では、信号伝搬方向に生じる誘導成分Lは模擬品より大きくなり、高周波領域で一部上回る特性は同図(b)に示すグラフよりもさらに向上するものと考えられる。

【0037】

図8(a)は、本実施の形態による積層セラミックコンデンサ31の第1の変形例による積層セラミックコンデンサ31Aの外観斜視図である。なお、同図において図4と同一または相当する部分には同一符号を付して説明する。

【0038】

この積層セラミックコンデンサ31Aは、誘電体33の両側に形成された各外部電極34a,34b、35a,35bに外部金属端子36が半田接続されている点が、上述した本実施の形態による積層セラミックコンデンサ31と相違する。その他の構成は積層セラミックコンデンサ31と同じである。外部金属端子36は、L字状に端部が折り曲げられた薄板状の金属板からなる。各外部電極34a,34b、35a,35bは、この外部金属端子36により、積層セラミックコンデンサ31Aが実装される回路基板表面からその胴体部分を浮かせる形状を有すことになる。

【0039】

積層セラミックコンデンサ31のジャンパ接続される距離の関係上、積層セラミックコンデンサ31の胴体部分が細長く形成されることが予想される。その際、回路基板に生じるたわみによって回路基板に実装された積層セラミックコンデンサ31の胴体部分に応力が加わり、胴体部分が折れるのが懸念される。しかし、本変形例の積層セラミックコンデンサ31Aの構成によれば、外部金属端子36が設けられた外部電極34a,34b、35a,35bによって積層セラミックコンデンサ31Aの胴体部分が回路基板表面から浮かせられるため、回路基板に生じるたわみによる応力は胴体部分に直接伝わらず、外部電極34a,34b、35a,35bに設けられた各外部金属端子36に加わる。このため、本変形例による積層セラミックコンデンサ31Aによれば、本実施の形態による積層セラミックコンデンサ31およびこれを用いたジャンパ実装構造と同様な前述した各効果が奏されると共に、外部電極34a,34b、35a,35bの各外部金属端子36おいて、回路基板に生じるたわみによる応力を吸収することで、積層セラミックコンデンサ31Aの胴体部分が折れるのを防止することが出来る。

【0040】

図8(b)は、本実施の形態による積層セラミックコンデンサ31の第2の変形例による積層セラミックコンデンサ31Bの外観斜視図である。なお、同図において図4と同一または相当する部分には同一符号を付して説明する。

【0041】

本変形例による積層セラミックコンデンサ31Bは、長手方向両側の各中央に2個の一方の外部電極34a,34b、長手方向両側の各角に4個の他方の外部電極35a,35b,35d,35eが形成されており、一方の外部電極34a,34bと他方の外部電極35a,35b,35d,35eとは形成される個数が異なっている。電源配線に接続される一方の外部電極34a,34bは内部電極34cによって互いに導通しており、グランド配線に接続される他方の外部電極35a,35b,35d,35eは内部電極35cによって互いに導通している。なお、ここでは、一方の外部電極34を2個、他方の外部電極35を4個としているが、その個数はこれに限られるものでなく、適宜変更される。

【0042】

図8(c)は、本実施の形態による積層セラミックコンデンサ31の第3の変形例による積層セラミックコンデンサ31Cの外観斜視図である。なお、同図において図4と同一または相当する部分には同一符号を付して説明する。

【0043】

本変形例による積層セラミックコンデンサ31Cは3端子コンデンサであり、長手方向の両端部に一方の外部電極34a,34b、この一方の外部電極34a,34bよりも内側両側部の長手方向両側には他方の外部電極35a,35b,35d,35eが形成されている。電源配線に接続される一方の外部電極34a,34bは3端子コンデンサのホット外部電極であり、コンデンサ内部で長手方向を貫通する貫通内部電極に接続されている。また、グランド配線に接続される他方の外部電極35a,35b,35d,35eは、3端子コンデンサのグランド外部電極であって長手方向の一端側と他端側とに分割されており、コンデンサ内部で貫通内部電極と静電容量を形成するグランド内部電極に接続されている。

【0044】

図8(b)に示す積層セラミックコンデンサ31Bや図8(c)に示す積層セラミックコンデンサ31Cでも、積層セラミックコンデンサ31B,31Cの絶縁体で覆われた胴体部分の誘電体33の長さが、負荷IC41の信号線接続端子群42aにつながる基板裏面に形成された信号線配線パターンの形成領域を跨ぐ長さに単に設定されることで、胴体部分が信号線配線パターンに電気接触することなく信号線配線パターンの形成領域を跨いで、積層セラミックコンデンサ31B,31Cの長手方向一端側に形成された一方の外部電極34aが基板裏面に形成された電源供給側電源配線パターンと接続され、長手方向他端側に形成された一方の外部電極34bが負荷IC41の電源接続端子42につながるビアホールに接続される。また、長手方向一端側に形成された他方の外部電極35a,35dのそれぞれが基板裏面に形成された電源供給側グランド配線パターンと接続され、長手方向他端側に形成された他方の外部電極35b,35eのそれぞれが負荷IC41のグランド接続端子42につながるビアホールに接続される。このため、図8(b)に示す積層セラミックコンデンサ31Bや図8(c)に示す積層セラミックコンデンサ31Cの各構成によっても、本実施の形態による積層セラミックコンデンサ31およびこれを用いたジャンパ実装構造と同様な前述した各効果が奏される。

【産業上の利用可能性】

【0045】

本実施形態では、積層セラミックコンデンサ31および負荷IC41が実装される回路基板が両面回路基板である場合のジャンパ実装構造について、説明した。しかし、図2(a)に示すような、内層25を有する多層回路基板21にも、技術的には、本発明による積層セラミックコンデンサおよびこれを用いたジャンパ実装構造を適用することが出来る。その場合にも上述した実施形態と同様な作用効果が奏されるが、多層回路基板21を用いることでコストの抑制は期待できない。

【0046】

また、上述した実施形態では、電源供給側グランド配線パターン52がグランド電位に接続され、負荷IC41の基準電位がグランド電位に設定される場合について説明したが、基準電位はグランド電位に限定されるものでなく、所定の電位に適宜設定される。その場合にも上述した実施形態と同様な作用効果が奏される。

【符号の説明】

【0047】

31,31A,31B,31C…積層セラミックコンデンサ

32…セラミック層

33…誘電体

34a,34b…一方の外部電極

35a,35b,35d,35e…他方の外部電極

34c,35c…内部電極

36…外部金属端子

41…負荷IC

42…ボール状接続端子

42a…信号線接続端子群

42b…電源およびグランド接続端子群

51…電源供給側電源配線パターン

52…電源供給側グランド配線パターン

L…誘導成分

C…容量成分

【技術分野】

【0001】

本発明は、信号線接続端子が基板実装面の外周側、電源接続端子および基準電位接続端子が信号線接続端子よりも内側に配置された負荷ICへ電源配線をジャンパ接続する積層セラミックコンデンサ、およびこれを用いたジャンパ実装構造に関するものである。

【背景技術】

【0002】

従来、積層セラミックコンデンサ構造を用いた貫通コンデンサとして、特許文献1に開示された3端子コンデンサがある。この種の3端子コンデンサは、コンデンサ長手方向の両側に設けられたホット外部電極間を導通させる貫通内部電極をコンデンサ内部に有する。また、この貫通内部電極との間で静電容量を形成するグランド内部電極をコンデンサ内部に有し、このグランド内部電極に接続されるグランド外部電極を、コンデンサ長手方向に直交する短手方向の両側に有する。

【0003】

3端子コンデンサ1は、例えば、図1(a)の斜視図に示すように、回路基板2に実装される。回路基板2には、スイッチングレギュレータIC3、パワーインダクタ4、および電解コンデンサ5からなるDC/DCコンバータモジュール6が回路電源として構成されている。DC/DCコンバータモジュール6から出力される電源は、電源供給側電源配線パターン7、3端子コンデンサ1、および負荷側電源配線パターン8を経由して、終端負荷IC(Integrated Circuit:LSI(Large Scale Integrated Circuit)を含む)9へ供給される。この際、3端子コンデンサ1は、電源供給側電源配線パターン7と負荷側電源配線パターン8との間に形成されたグランド配線パターン10をジャンパして、ホット外部電極1a,1bが電源配線パターン7,8に接続され、また、グランド外部電極1c,1dが共にグランド配線パターン10に接続される。

【0004】

このときの3端子コンデンサ1の挿入損失特性は、図1(b)に示す3端子コンデンサ1の概略斜視図のように、貫通内部電極11aの信号伝搬方向に対する誘導成分Lと、グランド内部電極11bに対する容量成分Cとにより構成される伝送線路型フィルタとなる。この伝送線路型フィルタの等価回路図は図1(c)に示され、電源配線パターン7,8によって終端負荷IC9へ供給される電源に重畳する高周波ノイズは、3端子コンデンサ1自身が持つ挿入損失特性によって除去される。

【0005】

ところで、回路基板の高密度実装化に伴い、ICのパッケージにはBGA(Ball Grid Array)パッケージが用いられている。BGAパッケージの負荷IC22は、例えば、図2(a)の断面図に示すように回路基板21の表面に実装され、通常、その基板実装面に形成されたボール状接続端子23がビアホール24によって回路基板21に多層に形成された各内層25に接続され、配線接続される。しかし、電子部品を用いて構成される完成品セットの最近のコストダウン競争により、完成品セットに用いられている多層回路基板21も層数削減を迫られている。このため、多端子の負荷IC22も、図2(b)の断面図に示すように、安価な両面回路基板26に実装されるようになっている。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開平10−154632号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

BGAパッケージの負荷IC22は、図3(a)の裏面図に示すように、基板実装面に複数のボール状接続端子23が面状に配置され、ボール状接続端子23の中の高周波信号を取り扱う信号線接続端子群23aが優先的に基板実装面の外周側に配置されている。ボール状接続端子23の中の電源およびグランド接続端子群23bは、信号線接続端子群23aよりも内側に集中して配置されている。

【0008】

このため、内側に集中配置された電源およびグランド接続端子群23bを図2(b)に示すような両面回路基板26の回路各部と接続するには、必ず、ビアホール27を介して電源およびグランド接続端子群23bを回路基板26の裏面に露出させて、図3(b)に示すように負荷側電源・グランド配線パターン28に接続する。そして、信号線接続端子群23aがビアホール27を介して回路基板26の裏面に露出する領域を跨いで、負荷側電源・グランド配線パターン28を電源供給側電源・グランド配線パターン29に接続しなければならない。

【0009】

この場合、図1(a)に示す回路基板2のように3端子コンデンサ1を用いて、負荷側電源・グランド配線パターン28と電源供給側電源・グランド配線パターン29との間をジャンパ接続しようとしても、3端子コンデンサ1のホット外部電極1a,1b間に形成された貫通内部電極11aの長さが足りず、ジャンパ接続できない。また、この貫通内部電極11aの長さを単に長くしても、3端子コンデンサ1の胴体部分に形成されたグランド外部電極1c,1dが、信号線接続端子群23aにビアホール27を介してつながる、回路基板26の裏面に露出する図示しない信号線配線パターンに電気接触してしまい、ジャンパ接続できない。

【0010】

また、3端子コンデンサ1を用いずに、負荷側と電源供給側の電源・グランド配線パターン28,29の間を配線パターンで接続するには、信号線接続端子群23aにつながる多くの信号線配線パターンの間を縫って、非常に細い配線パターンで接続しなければならず、電源配線の直流抵抗が高くなって好ましくない。

【課題を解決するための手段】

【0011】

本発明はこのような課題を解決するためになされたもので、

長手方向の両側に形成された互いに導通する一方の外部電極と、長手方向の両側に一方の外部電極と電気的に絶縁されて形成された互いに導通する他方の外部電極と、長手方向の両側に形成された各外部電極間に構成された絶縁体で覆われた胴体部分とを備える積層セラミックコンデンサを構成した。

【0012】

また、本発明は、

基板実装面に複数の接続端子が面状に配置され、複数の接続端子の中の信号線接続端子が基板実装面の外周側、複数の接続端子の中の電源接続端子および基準電位接続端子が信号線接続端子よりも内側の基板実装面に配置された負荷ICが回路基板の一方の基板面に実装され、

長手方向の両側に互いに導通する一方の外部電極、長手方向の両側に一方の外部電極と電気的に絶縁された互いに導通する他方の外部電極が形成され、長手方向の両側に形成された各外部電極間の胴体部分が絶縁体で覆われた積層セラミックコンデンサが回路基板の他方の基板面に実装され、

信号線接続端子にビアホールを介して接続される他方の基板面に形成された信号線配線パターンを胴体部分が跨り、

長手方向一端側の一方の外部電極が他方の基板面に形成された電源配線パターンに接続され、長手方向他端側の一方の外部電極がビアホールを介して電源接続端子に接続され、長手方向一端側の他方の外部電極が他方の基板面に形成された基準電位配線パターンに接続され、長手方向他端側の他方の外部電極がビアホールを介して基準電位接続端子に接続される

ジャンパ実装構造を構成した。

【0013】

本構成によれば、積層セラミックコンデンサの絶縁体で覆われた胴体部分の長さが、負荷ICの信号線接続端子群につながる基板裏面に形成された信号線配線パターンの形成領域を跨ぐ長さに単に設定されることで、胴体部分が信号線配線パターンに電気接触することなく信号線配線パターンの形成領域を跨いで、積層セラミックコンデンサの長手方向の両側に形成された一方の外部電極のそれぞれが、基板裏面に形成された電源供給側電源配線パターンと、負荷ICの電源接続端子につながるビアホールとに接続される。また、長手方向の両側に形成された他方の外部電極のそれぞれが、基板裏面に形成された電源供給側基準電位配線パターンと、負荷ICの基準電位接続端子につながるビアホールとに接続される。このため、電源供給側電源配線パターンと負荷ICの電源接続端子につながるビアホールとの間は、積層セラミックコンデンサの長手方向の両側に形成された互いに導通する一方の外部電極により、電源配線の直流抵抗が高くなることなく、ジャンパ接続される。また、電源供給側基準電位配線パターンと負荷ICの基準電位接続端子につながるビアホールとの間は、積層セラミックコンデンサの長手方向の両側に形成された互いに導通する他方の外部電極により、基準電位配線の直流抵抗が高くなることなく、ジャンパ接続される。

【0014】

また、負荷ICの電源接続端子につながるビアホールと電源供給側電源配線パターンとの間に積層セラミックコンデンサの一方の外部電極間の内部電極が介在させられ、負荷ICの基準電位接続端子につながるビアホールと電源供給側基準電位配線パターンとの間に積層セラミックコンデンサの他方の外部電極間の内部電極が介在させられる。このため、一方の外部電極間および他方の外部電極間の双方の内部電極において信号伝搬方向に対する誘導成分Lが分布定数的に生じ、また、これらの内部電極間に容量成分Cが分布定数的に生じて、従来の3端子コンデンサによる伝送線路型フィルタに比べて信号伝搬方向に対する誘導成分Lの大きな伝送線路型フィルタが構成される。このため、負荷ICの基板実装面の内側に孤立して配置された電源接続端子および基準電位接続端子形成領域に、負荷ICの電源接続端子および基準電位接続端子間に発生した高周波ノイズを閉じ込め、また、負荷ICから外に出ようとする高周波ノイズを分布定数的に低減させることが可能になる。また、積層セラミックコンデンサは電源および基準電位間のデカップリングコンデンサとしても働き、分布定数的に生じる容量成分Cに蓄えられる電荷が電圧低下時に放出されることにより、電圧変動の抑制も可能になる。

【0015】

また、本発明は、外部電極が、積層セラミックコンデンサが実装される回路基板表面から胴体部分を浮かせる形状を有することを特徴とする。

【0016】

積層セラミックコンデンサの胴体部分が細長く形成されることにより、回路基板に生じるたわみによって回路基板に実装された積層セラミックコンデンサの胴体部分に応力が加わり、胴体部分が折れるのが懸念される。しかし、本構成によれば、外部電極によって胴体部分が回路基板表面から浮かせられるため、回路基板に生じるたわみによる応力は胴体部分に直接伝わらず、外部電極に加わる。このため、外部電極おいて、回路基板に生じるたわみによる応力を吸収することで、積層セラミックコンデンサの胴体部分が折れるのを防止することが出来る。

【0017】

また、本発明は、一方の外部電極と他方の外部電極との形成される個数が異なることを特徴とする。

【0018】

また、本発明は、積層セラミックコンデンサが3端子コンデンサであり、一方の外部電極が長手方向を貫通する貫通内部電極に接続されるホット外部電極であり、他方の外部電極が、貫通内部電極と静電容量を形成するグランド内部電極に接続されるグランド外部電極であって、長手方向の一端側と他端側とに分割されていることを特徴とする。

【0019】

これらの各構成によっても、積層セラミックコンデンサの絶縁体で覆われた胴体部分の長さが、負荷ICの信号線接続端子群につながる基板裏面に形成された信号線配線パターンの形成領域を跨ぐ長さに単に設定されることで、上記各効果を有する積層セラミックコンデンサおよびこれを用いたジャンパ実装構造が提供される。

【発明の効果】

【0020】

本発明によれば、上記のように、積層セラミックコンデンサの胴体部分が信号線配線パターンに電気接触することなく信号線配線パターンの形成領域を跨いで、配線の直流抵抗が高くなることなく、負荷ICの基板実装面内側に配置された電源および基準電位接続端子につながるビアホールと電源供給側配線パターンとの間をジャンパ接続することが可能な積層セラミックコンデンサ、およびこれを用いたジャンパ実装構造が提供される。

【図面の簡単な説明】

【0021】

【図1】(a)は従来の積層セラミックコンデンサを用いたジャンパ実装構造を示す斜視図、(b)は(a)に示す積層セラミックコンデンサに生じる誘導成分および容量成分の構成を示す概略斜視図、(c)は(b)に示す積層セラミックコンデンサの等価回路図である。

【図2】(a)は一般的な多層回路基板の断面図、(b)は一般的な両面回路基板の断面図である。

【図3】(a)はBGAパッケージICの基板実装面の平面図、(b)は(a)に示すBGAパッケージICを両面回路基板に実装する際に生じる問題点を説明するための断面図である。

【図4】(a)は本発明の一実施の形態による積層セラミックコンデンサの外観斜視図、(b)はその内部構成を示す分解斜視図である。

【図5】本発明の一実施の形態による積層セラミックコンデンサを用いたジャンパ実装構造を示す回路基板の裏面図である。

【図6】(a)は図5に示す積層セラミックコンデンサに生じる誘導成分および容量成分の構成を示す概略斜視図、(b)は(a)に示す積層セラミックコンデンサの等価回路図である。

【図7】(a)は本発明の効果を確認するために用いられた積層セラミックコンデンサ構造を示す図、(b)は(a)に示す積層セラミックコンデンサの挿入損失特性を従来品と比較した測定結果を示すグラフである。

【図8】(a)は一実施の形態の第1の変形例による積層セラミックコンデンサの外観斜視図、(b)は一実施の形態の第2の変形例による積層セラミックコンデンサの外観斜視図、(c)は一実施の形態の第3の変形例による積層セラミックコンデンサの外観斜視図である。

【発明を実施するための形態】

【0022】

次に、本発明の一実施の形態による積層セラミックコンデンサおよびこれを用いたジャンパ実装構造について、説明する。

【0023】

図4(a)は、本実施の形態による積層セラミックコンデンサの外観斜視図、同図(b)はその内部構成を示す分解斜視図である。

【0024】

積層セラミックコンデンサ31は、表面実装型のチップ・コンデンサであり、セラミック層32が積層されて略直方体の形状をした誘電体33の長手方向の両側に、一方の外部電極34a,34bと他方の外部電極35a,35bとを備える。また、長手方向の両側に形成された各外部電極34a,34bおよび35a,35b間には、誘電体33からなる絶縁体で覆われた胴体部分が構成されている。

【0025】

誘電体33の内部において、各セラミック層32には、一方の外部電極34a,34bの形成側の長辺に寄った内部電極34cと、他方の外部電極35a,35bの形成側の長辺に寄った内部電極35cとが、交互に形成されている。一方の外部電極34a,34bは、セラミック層32に形成された複数の内部電極34cによって互いに導通する。他方の外部電極35a,35bは、セラミック層32に形成された複数の内部電極35cによって互いに導通し、一方の外部電極34a,34bと電気的に絶縁されている。

【0026】

図5は、上記のような構成をした積層セラミックコンデンサ31を用いた本実施の形態によるャンパ実装構造を示す回路基板の裏面図である。なお、回路基板は、内層を有しない両面回路基板であり、同図では図示されておらず、透視された状態が示されている。

【0027】

両面回路基板の表面の一方の基板面には、BGAパッケージの負荷IC(LSIを含む)41が実装されている。負荷IC41は、基板実装面に複数のボール状接続端子42が面状に配置され、複数のボール状接続端子42の中の信号線接続端子群42aが基板実装面の外周側、複数のボール状接続端子42の中の電源およびグランド接続端子群42bが信号線接続端子群42aよりも内側の基板実装面に配置されている。

【0028】

また、両面回路基板の裏面の他方の基板面には、上記の積層セラミックコンデンサ31が実装されており、また、DC/DCコンバータの出力電源およびグランドにつながる電源供給側電源配線パターン51および電源供給側グランド配線パターン52が形成されている。負荷IC41の信号線接続端子群42aは、両面回路基板に形成された図示しないビアホールを介して両面回路基板の裏面に導出され、両面回路基板の裏面に形成された図示しない信号線配線パターンに接続される。積層セラミックコンデンサ31は、この信号線配線パターンを胴体部分が跨り、両面回路基板の裏面に実装されている。

【0029】

また、積層セラミックコンデンサ31の長手方向一端側の一方の外部電極34aは電源供給側電源配線パターン51に接続され、長手方向他端側の一方の外部電極34bは、両面回路基板に形成された図示しないビアホールを介して、電源およびグランド接続端子群42bの中の電源接続端子42に接続されている。また、長手方向一端側の他方の外部電極35aは電源供給側グランド配線パターン52に接続され、長手方向他端側の他方の外部電極35bは、両面回路基板に形成された図示しないビアホールを介して、電源およびグランド接続端子群42bの中のグランド接続端子42に接続されている。

【0030】

このような本実施の形態によれば、積層セラミックコンデンサ31の絶縁体で覆われた胴体部分の誘電体33の長さが、負荷IC41の信号線接続端子群42aにつながる基板裏面に形成された信号線配線パターンの形成領域を跨ぐ長さに単に設定されることで、胴体部分が信号線配線パターンに電気接触することなく信号線配線パターンの形成領域を跨いで、積層セラミックコンデンサ31の長手方向の両側に形成された一方の外部電極34a,34bのそれぞれが、基板裏面に形成された電源供給側電源配線パターン51と、負荷IC41の電源接続端子42につながるビアホールとに接続される。また、長手方向の両側に形成された他方の外部電極35a,35bのそれぞれが、基板裏面に形成された電源供給側グランド配線パターン52と、負荷IC41のグランド接続端子42につながるビアホールとに接続される。このため、電源供給側電源配線パターン51と負荷IC41の電源接続端子42につながるビアホールとの間は、積層セラミックコンデンサ31の長手方向の両側に形成された互いに導通する一方の外部電極34a,34bにより、電源配線の直流抵抗が高くなることなく、ジャンパ接続される。また、電源供給側グランド配線パターン52と負荷IC41のグランド接続端子42につながるビアホールとの間は、積層セラミックコンデンサ41の長手方向の両側に形成された互いに導通する他方の外部電極35a,35bにより、グランド配線の直流抵抗が高くなることなく、ジャンパ接続される。

【0031】

また、負荷IC41の電源接続端子42につながるビアホールと電源供給側電源配線パターン51との間に積層セラミックコンデンサ31の一方の外部電極34a,34b間の内部電極34cが介在させられ、負荷IC41のグランド接続端子42につながるビアホールと電源供給側グランド配線パターン52との間に積層セラミックコンデンサ31の他方の外部電極35a,35b間の内部電極35cが介在させられる。このため、図6(a)に示すように、一方の外部電極34a,34b間および他方の外部電極35a,35b間の双方の内部電極34c,35cにおいて信号伝搬方向に対する誘導成分Lが分布定数的に生じ、また、これらの内部電極34c,35c間に容量成分Cが分布定数的に生じて、従来の3端子コンデンサによる伝送線路型フィルタに比べて信号伝搬方向に対する誘導成分Lの大きな伝送線路型フィルタが構成される。図6(b)はこの伝送線路型フィルタの等価回路図を示す。このため、負荷IC41の基板実装面の内側に孤立して配置された電源およびグランド接続端子群42bの形成領域に、負荷IC41の電源接続端子42およびグランド接続端子42間に発生した高周波ノイズを閉じ込め、また、負荷IC41から外に出ようとする高周波ノイズを分布定数的に低減させることが可能になる。また、積層セラミックコンデンサ31は電源およびグランド間のデカップリングコンデンサとしても働き、分布定数的に生じる容量成分Cに蓄えられる電荷が電圧低下時に放出されることにより、電圧変動の抑制も可能になる。

【0032】

上述した積層セラミックコンデンサ31を用いた本実施の形態によるャンパ実装構造により奏される効果を確認するため、ノイズ対策効果を定量的に示す量である挿入損失の周波数特性を測定した。

【0033】

この測定では、ジャンパ型伝送線路コンデンサとして機能する上述した積層セラミックコンデンサ31を、図7(a)に示すように、1005サイズ(長辺1.0mm×短辺0.5mm)で容量が0.1μFのLW逆転コンデンサ61を10個並列に並べて、模擬構成した。LW逆転コンデンサ61は、一方の外部電極61aおよび他方の外部電極61bが略直方体形状をした誘電体62の長手方向に沿って平行に形成されている。

【0034】

図7(b)に示すグラフは、測定結果を示し、横軸は周波数(Frequency)[MHz]、縦軸は挿入損失(Insertion Loss)[dB]を示す。また、実線で示す特性線65は、上記のように模擬構成した本実施の形態によるジャンパ型伝送線路コンデンサについての挿入損失の測定結果、点線で示す特性線66は、従来仕様の3端子コンデンサについての挿入損失の測定結果を表す。従来仕様の3端子コンデンサは、1608サイズ(長辺1.6mm×短辺0.8mm)で容量が1μFの図1に示す従来品の伝送線路コンデンサである。

【0035】

同グラフに示されるように、特性線65で表される本実施の形態によるジャンパ型伝送線路コンデンサは、特性線66で表される従来仕様の3端子コンデンサとほぼ同等の性能を示しているが、高周波領域では本実施の形態によるジャンパ型伝送線路コンデンサの挿入損失が大きくなり、従来仕様の3端子コンデンサを一部上回る性能を示している。これは、図6(b)に等価回路図が表される本実施の形態によるジャンパ型伝送線路コンデンサは、図1(c)に等価回路図が表される従来仕様の3端子コンデンサに比べ、グランド側外部電極35a,35b間の信号伝搬方向に誘導成分Lが分布定数的に生じるからである。

【0036】

本測定で模擬構成した積層セラミックコンデンサは、図7(a)に示すように一方の外部電極61aおよび他方の外部電極61bが長手方向の両側辺に連なって形成されているため、信号伝搬方向に生じる誘導成分Lは実際の製品より小さくなっている。しかし、これら連なる外部電極61aおよび61bを本実施の形態のように長手方向の両端側に分離させて形成することで、実際の製品では、信号伝搬方向に生じる誘導成分Lは模擬品より大きくなり、高周波領域で一部上回る特性は同図(b)に示すグラフよりもさらに向上するものと考えられる。

【0037】

図8(a)は、本実施の形態による積層セラミックコンデンサ31の第1の変形例による積層セラミックコンデンサ31Aの外観斜視図である。なお、同図において図4と同一または相当する部分には同一符号を付して説明する。

【0038】

この積層セラミックコンデンサ31Aは、誘電体33の両側に形成された各外部電極34a,34b、35a,35bに外部金属端子36が半田接続されている点が、上述した本実施の形態による積層セラミックコンデンサ31と相違する。その他の構成は積層セラミックコンデンサ31と同じである。外部金属端子36は、L字状に端部が折り曲げられた薄板状の金属板からなる。各外部電極34a,34b、35a,35bは、この外部金属端子36により、積層セラミックコンデンサ31Aが実装される回路基板表面からその胴体部分を浮かせる形状を有すことになる。

【0039】

積層セラミックコンデンサ31のジャンパ接続される距離の関係上、積層セラミックコンデンサ31の胴体部分が細長く形成されることが予想される。その際、回路基板に生じるたわみによって回路基板に実装された積層セラミックコンデンサ31の胴体部分に応力が加わり、胴体部分が折れるのが懸念される。しかし、本変形例の積層セラミックコンデンサ31Aの構成によれば、外部金属端子36が設けられた外部電極34a,34b、35a,35bによって積層セラミックコンデンサ31Aの胴体部分が回路基板表面から浮かせられるため、回路基板に生じるたわみによる応力は胴体部分に直接伝わらず、外部電極34a,34b、35a,35bに設けられた各外部金属端子36に加わる。このため、本変形例による積層セラミックコンデンサ31Aによれば、本実施の形態による積層セラミックコンデンサ31およびこれを用いたジャンパ実装構造と同様な前述した各効果が奏されると共に、外部電極34a,34b、35a,35bの各外部金属端子36おいて、回路基板に生じるたわみによる応力を吸収することで、積層セラミックコンデンサ31Aの胴体部分が折れるのを防止することが出来る。

【0040】

図8(b)は、本実施の形態による積層セラミックコンデンサ31の第2の変形例による積層セラミックコンデンサ31Bの外観斜視図である。なお、同図において図4と同一または相当する部分には同一符号を付して説明する。

【0041】

本変形例による積層セラミックコンデンサ31Bは、長手方向両側の各中央に2個の一方の外部電極34a,34b、長手方向両側の各角に4個の他方の外部電極35a,35b,35d,35eが形成されており、一方の外部電極34a,34bと他方の外部電極35a,35b,35d,35eとは形成される個数が異なっている。電源配線に接続される一方の外部電極34a,34bは内部電極34cによって互いに導通しており、グランド配線に接続される他方の外部電極35a,35b,35d,35eは内部電極35cによって互いに導通している。なお、ここでは、一方の外部電極34を2個、他方の外部電極35を4個としているが、その個数はこれに限られるものでなく、適宜変更される。

【0042】

図8(c)は、本実施の形態による積層セラミックコンデンサ31の第3の変形例による積層セラミックコンデンサ31Cの外観斜視図である。なお、同図において図4と同一または相当する部分には同一符号を付して説明する。

【0043】

本変形例による積層セラミックコンデンサ31Cは3端子コンデンサであり、長手方向の両端部に一方の外部電極34a,34b、この一方の外部電極34a,34bよりも内側両側部の長手方向両側には他方の外部電極35a,35b,35d,35eが形成されている。電源配線に接続される一方の外部電極34a,34bは3端子コンデンサのホット外部電極であり、コンデンサ内部で長手方向を貫通する貫通内部電極に接続されている。また、グランド配線に接続される他方の外部電極35a,35b,35d,35eは、3端子コンデンサのグランド外部電極であって長手方向の一端側と他端側とに分割されており、コンデンサ内部で貫通内部電極と静電容量を形成するグランド内部電極に接続されている。

【0044】

図8(b)に示す積層セラミックコンデンサ31Bや図8(c)に示す積層セラミックコンデンサ31Cでも、積層セラミックコンデンサ31B,31Cの絶縁体で覆われた胴体部分の誘電体33の長さが、負荷IC41の信号線接続端子群42aにつながる基板裏面に形成された信号線配線パターンの形成領域を跨ぐ長さに単に設定されることで、胴体部分が信号線配線パターンに電気接触することなく信号線配線パターンの形成領域を跨いで、積層セラミックコンデンサ31B,31Cの長手方向一端側に形成された一方の外部電極34aが基板裏面に形成された電源供給側電源配線パターンと接続され、長手方向他端側に形成された一方の外部電極34bが負荷IC41の電源接続端子42につながるビアホールに接続される。また、長手方向一端側に形成された他方の外部電極35a,35dのそれぞれが基板裏面に形成された電源供給側グランド配線パターンと接続され、長手方向他端側に形成された他方の外部電極35b,35eのそれぞれが負荷IC41のグランド接続端子42につながるビアホールに接続される。このため、図8(b)に示す積層セラミックコンデンサ31Bや図8(c)に示す積層セラミックコンデンサ31Cの各構成によっても、本実施の形態による積層セラミックコンデンサ31およびこれを用いたジャンパ実装構造と同様な前述した各効果が奏される。

【産業上の利用可能性】

【0045】

本実施形態では、積層セラミックコンデンサ31および負荷IC41が実装される回路基板が両面回路基板である場合のジャンパ実装構造について、説明した。しかし、図2(a)に示すような、内層25を有する多層回路基板21にも、技術的には、本発明による積層セラミックコンデンサおよびこれを用いたジャンパ実装構造を適用することが出来る。その場合にも上述した実施形態と同様な作用効果が奏されるが、多層回路基板21を用いることでコストの抑制は期待できない。

【0046】

また、上述した実施形態では、電源供給側グランド配線パターン52がグランド電位に接続され、負荷IC41の基準電位がグランド電位に設定される場合について説明したが、基準電位はグランド電位に限定されるものでなく、所定の電位に適宜設定される。その場合にも上述した実施形態と同様な作用効果が奏される。

【符号の説明】

【0047】

31,31A,31B,31C…積層セラミックコンデンサ

32…セラミック層

33…誘電体

34a,34b…一方の外部電極

35a,35b,35d,35e…他方の外部電極

34c,35c…内部電極

36…外部金属端子

41…負荷IC

42…ボール状接続端子

42a…信号線接続端子群

42b…電源およびグランド接続端子群

51…電源供給側電源配線パターン

52…電源供給側グランド配線パターン

L…誘導成分

C…容量成分

【特許請求の範囲】

【請求項1】

長手方向の両側に形成された互いに導通する一方の外部電極と、長手方向の両側に前記一方の外部電極と電気的に絶縁されて形成された互いに導通する他方の外部電極と、長手方向の両側に形成された各前記外部電極間に構成された絶縁体で覆われた胴体部分とを備える積層セラミックコンデンサ。

【請求項2】

基板実装面に複数の接続端子が面状に配置され、前記複数の接続端子の中の信号線接続端子が基板実装面の外周側、前記複数の接続端子の中の電源接続端子および基準電位接続端子が前記信号線接続端子よりも内側の基板実装面に配置された負荷ICが回路基板の一方の基板面に実装され、

長手方向の両側に互いに導通する一方の外部電極、長手方向の両側に前記一方の外部電極と電気的に絶縁された互いに導通する他方の外部電極が形成され、長手方向の両側に形成された各前記外部電極間の胴体部分が絶縁体で覆われた積層セラミックコンデンサが前記回路基板の他方の基板面に実装され、

前記信号線接続端子にビアホールを介して接続される前記他方の基板面に形成された信号線配線パターンを前記胴体部分が跨り、

長手方向一端側の前記一方の外部電極が前記他方の基板面に形成された電源配線パターンに接続され、長手方向他端側の前記一方の外部電極がビアホールを介して前記電源接続端子に接続され、長手方向一端側の前記他方の外部電極が前記他方の基板面に形成された基準電位配線パターンに接続され、長手方向他端側の前記他方の外部電極がビアホールを介して前記基準電位接続端子に接続される

ジャンパ実装構造。

【請求項3】

前記外部電極は、前記積層セラミックコンデンサが実装される回路基板表面から前記胴体部分を浮かせる形状を有することを特徴とする請求項1に記載の積層セラミックコンデンサまたは請求項2に記載のジャンパ実装構造。

【請求項4】

前記一方の外部電極と前記他方の外部電極とは形成される個数が異なることを特徴とする請求項1もしくは請求項3に記載の積層セラミックコンデンサまたは請求項2もしくは請求項3に記載のジャンパ実装構造。

【請求項5】

前記積層セラミックコンデンサは3端子コンデンサであり、前記一方の外部電極は長手方向を貫通する貫通内部電極に接続されるホット外部電極であり、前記他方の外部電極は、前記貫通内部電極と静電容量を形成するグランド内部電極に接続されるグランド外部電極であって、長手方向の一端側と他端側とに分割されていることを特徴とする請求項1もしくは請求項3もしくは請求項4に記載の積層セラミックコンデンサまたは請求項2もしくは請求項3もしくは請求項4に記載のジャンパ実装構造。

【請求項1】

長手方向の両側に形成された互いに導通する一方の外部電極と、長手方向の両側に前記一方の外部電極と電気的に絶縁されて形成された互いに導通する他方の外部電極と、長手方向の両側に形成された各前記外部電極間に構成された絶縁体で覆われた胴体部分とを備える積層セラミックコンデンサ。

【請求項2】

基板実装面に複数の接続端子が面状に配置され、前記複数の接続端子の中の信号線接続端子が基板実装面の外周側、前記複数の接続端子の中の電源接続端子および基準電位接続端子が前記信号線接続端子よりも内側の基板実装面に配置された負荷ICが回路基板の一方の基板面に実装され、

長手方向の両側に互いに導通する一方の外部電極、長手方向の両側に前記一方の外部電極と電気的に絶縁された互いに導通する他方の外部電極が形成され、長手方向の両側に形成された各前記外部電極間の胴体部分が絶縁体で覆われた積層セラミックコンデンサが前記回路基板の他方の基板面に実装され、

前記信号線接続端子にビアホールを介して接続される前記他方の基板面に形成された信号線配線パターンを前記胴体部分が跨り、

長手方向一端側の前記一方の外部電極が前記他方の基板面に形成された電源配線パターンに接続され、長手方向他端側の前記一方の外部電極がビアホールを介して前記電源接続端子に接続され、長手方向一端側の前記他方の外部電極が前記他方の基板面に形成された基準電位配線パターンに接続され、長手方向他端側の前記他方の外部電極がビアホールを介して前記基準電位接続端子に接続される

ジャンパ実装構造。

【請求項3】

前記外部電極は、前記積層セラミックコンデンサが実装される回路基板表面から前記胴体部分を浮かせる形状を有することを特徴とする請求項1に記載の積層セラミックコンデンサまたは請求項2に記載のジャンパ実装構造。

【請求項4】

前記一方の外部電極と前記他方の外部電極とは形成される個数が異なることを特徴とする請求項1もしくは請求項3に記載の積層セラミックコンデンサまたは請求項2もしくは請求項3に記載のジャンパ実装構造。

【請求項5】

前記積層セラミックコンデンサは3端子コンデンサであり、前記一方の外部電極は長手方向を貫通する貫通内部電極に接続されるホット外部電極であり、前記他方の外部電極は、前記貫通内部電極と静電容量を形成するグランド内部電極に接続されるグランド外部電極であって、長手方向の一端側と他端側とに分割されていることを特徴とする請求項1もしくは請求項3もしくは請求項4に記載の積層セラミックコンデンサまたは請求項2もしくは請求項3もしくは請求項4に記載のジャンパ実装構造。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【公開番号】特開2013−30718(P2013−30718A)

【公開日】平成25年2月7日(2013.2.7)

【国際特許分類】

【出願番号】特願2011−167723(P2011−167723)

【出願日】平成23年7月29日(2011.7.29)

【出願人】(000006231)株式会社村田製作所 (3,635)

【Fターム(参考)】

【公開日】平成25年2月7日(2013.2.7)

【国際特許分類】

【出願日】平成23年7月29日(2011.7.29)

【出願人】(000006231)株式会社村田製作所 (3,635)

【Fターム(参考)】

[ Back to top ]