積層セラミックコンデンサ

【課題】積層セラミックコンデンサの、基板上への実装状態での電界印加時における「鳴き」を抑制する。

【解決手段】コンデンサ本体29における内部電極27,28の対向による静電容量形成に寄与する活性部37を、積層方向に沿って分布する第1領域40と基板22側の第2領域41とに区分し、第2領域41における誘電体セラミック層25の誘電率を、第1領域40における誘電体セラミック層24の誘電率より低くし、かつ第2領域41における誘電体セラミック層25の体積に対する内部電極27,28の体積の比率を、第1領域40における誘電体セラミック層24の体積に対する内部電極27,28の体積の比率より高くする。

【解決手段】コンデンサ本体29における内部電極27,28の対向による静電容量形成に寄与する活性部37を、積層方向に沿って分布する第1領域40と基板22側の第2領域41とに区分し、第2領域41における誘電体セラミック層25の誘電率を、第1領域40における誘電体セラミック層24の誘電率より低くし、かつ第2領域41における誘電体セラミック層25の体積に対する内部電極27,28の体積の比率を、第1領域40における誘電体セラミック層24の体積に対する内部電極27,28の体積の比率より高くする。

【発明の詳細な説明】

【技術分野】

【0001】

この発明は、積層セラミックコンデンサに関するもので、特に、積層セラミックコンデンサの、基板上への実装状態での電界印加時における「鳴き」を抑制するための改良に関するものである。

【背景技術】

【0002】

積層セラミックコンデンサにおいて、外部電極間に電圧を印加したとき、内部電極の隣り合うものが互いに対向している部分に誘電分極が発生する。この誘電分極によってもたらされた静電容量は、外部電極を通して取り出すことができる。

【0003】

上述のような内部電極の対向による静電容量の形成に寄与する、コンデンサ本体の活性部に存在する誘電体セラミック層によって与えられる誘電体は、印加される電圧に応じて、電界誘起歪みを起こす。積層セラミックコンデンサが基板上に表面実装されている場合、この電界誘起歪みにより、積層セラミックコンデンサが基板を変形させ、この変形の周波数によっては「鳴き」と呼ばれる音を生じさせる。そして、この「鳴き」が大きくなると、騒音の問題を引き起こす。

【0004】

上述の「鳴き」の抑制を意図したものではないが、この発明にとって興味ある積層セラミックコンデンサがたとえば特開2000−243657号公報(特許文献1)に記載されている。図6には、特許文献1に記載された積層セラミックコンデンサ1が基板2上に実装された状態で示されている。

【0005】

積層セラミックコンデンサ1は、複数の誘電体セラミック層3および4と誘電体セラミック層3および4間の複数の界面に沿ってそれぞれ形成された複数の内部電極5および6とからなる積層構造を有する、コンデンサ本体7を備えている。コンデンサ本体7は、誘電体セラミック層3および4の延びる方向に延びる第1および第2の主面8および9と、主面8および9に直交する方向にそれぞれ延びる、第1および第2の端面10および11と、第1および第2の側面(図6の紙面に平行な面であるが、図6では図示されない。)とによって規定される直方体形状をなしている。

【0006】

積層セラミックコンデンサ1は、また、誘電体セラミック層3または4を介しての内部電極5および6の対向によって形成される静電容量を取り出すように内部電極5および6にそれぞれ接続される、第1および第2の外部電極12および13を備えている。第1および第2の外部電極12および13は、コンデンサ本体7の第1および第2の端面10および11上にそれぞれ形成されている。このような積層セラミックコンデンサ1は、コンデンサ本体7の第2の主面9が基板2に対向した状態で、外部電極12および13がはんだまたは導電性接着剤のような導電性接合材14によって接合されることによって基板2上に実装される。

【0007】

コンデンサ本体7は、基板2側とは反対側の上領域15と基板2側の下領域16とに区分され、上領域15では比較的大きい容量が取り出されるようにされ、下領域16では比較的小さい容量が取り出されるようにされる。

【0008】

より詳細には、上領域15においては、誘電体セラミック層3を構成する誘電体セラミックとして誘電率の比較的高いものが用いられるとともに、内部電極5および6の積層数が比較的多くされ、かつ内部電極5および6間の間隔が比較的小さくされる。他方、下領域6においては、誘電体セラミック層4を構成する誘電体セラミックとして誘電率の比較的低いものが用いられるとともに、内部電極5および6の積層数が比較的少なくされ、かつ内部電極5および6間の間隔が比較的大きくされる。

【0009】

このようにして、図6に示した積層セラミックコンデンサ1によれば、取得静電容量の比較的大きい上領域15と比較的小さい下領域16とを有しているので、比較的広い周波数範囲にわたって良好な伝達特性を得ることができる。

【0010】

また、特許文献1には記載されていないが、下領域16において取得静電容量が比較的小さくされることによって、前述した電界誘起歪みが小さくなり、このことから、基板2上への実装状態での電界印加時における「鳴き」の低減が期待される。

【0011】

しかしながら、図6に示したような構造の積層セラミックコンデンサ1では、電界誘起歪みの低減効果が十分ではなく、それゆえ、「鳴き」を低減する効果について、より改善されるべき余地がある。

【先行技術文献】

【特許文献】

【0012】

【特許文献1】特開2000−243657号公報

【発明の概要】

【発明が解決しようとする課題】

【0013】

そこで、この発明の目的は、上述した課題を解決し得る積層セラミックコンデンサを提供しようとすることである。

【課題を解決するための手段】

【0014】

この発明に係る積層セラミックコンデンサは、コンデンサ本体と第1および第2の外部電極とを備えている。

【0015】

コンデンサ本体は、複数の誘電体セラミック層と誘電体セラミック層間の複数の界面に沿ってそれぞれ形成された複数の内部電極とからなる積層構造を有し、誘電体セラミック層の延びる方向に延びる第1および第2の主面と、主面に直交する方向にそれぞれ延びる、第1および第2の端面と、第1および第2の側面とによって規定される実質的に直方体形状をなしている。

【0016】

第1および第2の外部電極は、誘電体セラミック層を介しての内部電極の対向によって形成される静電容量を取り出すように内部電極の特定のものに接続されながら、コンデンサ本体の第1および第2の端面上にそれぞれ形成される。

【0017】

また、この積層セラミックコンデンサは、コンデンサ本体の第2の主面が基板に対向した状態で、外部電極が導電性接合材によって接合されることによって基板上に実装される。

【0018】

このような構成の積層セラミックコンデンサにおいて、前述した技術的課題を解決するため、この発明では、次のような構成を備えることを特徴としている。

【0019】

コンデンサ本体における内部電極の対向による静電容量形成に寄与する活性部は、積層方向に沿って分布する少なくとも第1領域と第2領域とを含む複数の領域に区分され、第1領域より第2の主面側には第2領域が位置される。

【0020】

そして、第2領域における誘電体セラミック層の誘電率は、第1領域における誘電体セラミック層の誘電率より低くされるとともに、第2領域における誘電体セラミック層の体積に対する内部電極の体積の比率は、第1領域における誘電体セラミック層の体積に対する内部電極の体積の比率より高くされることを特徴としている。

【0021】

この発明において、第2領域における誘電体セラミック層の誘電率は、第1領域における誘電体セラミック層の誘電率の0.63倍以下であるとともに、第2領域における誘電体セラミック層の体積に対する内部電極の体積の比率は、第1領域における誘電体セラミック層の体積に対する内部電極の体積の比率の1.2倍以上であることが好ましい。

【0022】

より好ましくは、第2領域における誘電体セラミック層の誘電率は、第1領域における誘電体セラミック層の誘電率の0.02〜0.43倍であるとともに、第2領域における誘電体セラミック層の体積に対する内部電極の体積の比率は、第1領域における誘電体セラミック層の体積に対する内部電極の体積の比率の1.5倍以上であり、さらに、第2領域の厚みは、第1領域の厚みの0.20〜0.96倍である。

【0023】

この発明に係る積層セラミックコンデンサにおいて、活性部は2つの第2領域を含み、2つの第2領域は、第1領域を積層方向に挟むように分布していてもよい。

【0024】

あるいは、活性部はさらに第3領域を含み、この第3領域は第1領域より第1の主面側に位置されていてもよい。この場合、第3領域における誘電体セラミック層の誘電率は、第1領域における誘電体セラミック層の誘電率より高くされたり、第3領域における誘電体セラミック層の体積に対する内部電極の体積の比率は、第1領域における誘電体セラミック層の体積に対する内部電極の体積の比率より高くされたりすることができる。

【発明の効果】

【0025】

基板の「鳴き」を低減するには、積層セラミックコンデンサにおける、特に基板側の変位量を低減することが効果的である。この発明によれば、コンデンサ本体における基板側の第2領域において、比較的低い誘電率の誘電体セラミック層を採用するとともに、内部電極の体積割合を比較的高くすることにより、変位量を効果的に低減することができる。すなわち、低誘電率の誘電体を用いたことによって電界誘起歪みが低減され、また、この電界誘起歪みの低減に加えて、内部電極による物理的な歪み抑制が相乗的に作用し、予想外に大きな変位抑制を実現することができる。

【0026】

なお、第2領域における誘電体セラミック層の誘電率を比較的低くすることによって容量が低下するといった懸念については、内部電極の体積割合の増加を、内部電極の枚数を多くすることによって達成するようにすれば、内部電極の重なり面積が増加するとともに、内部電極間の誘電体セラミック層の厚みも小さくなるため、容量低下を有利に補償することができる。このことから、「鳴き」を低減できるだけでなく、これと静電容量との両立も図ることができる。

【0027】

この発明において、第2領域における誘電体セラミック層の誘電率が、第1領域における誘電体セラミック層の誘電率の0.63倍以下であり、第2領域における誘電体セラミック層の体積に対する内部電極の体積の比率が、第1領域における誘電体セラミック層の体積に対する内部電極の体積の比率の1.2倍以上であるとき、変位抑制効果をより高めることができる。

【0028】

また、より限定的に、第2領域における誘電体セラミック層の誘電率が、第1領域における誘電体セラミック層の誘電率の0.02〜0.43倍であり、第2領域における誘電体セラミック層の体積に対する内部電極の体積の比率が、第1領域における誘電体セラミック層の体積に対する内部電極の比率の1.5倍以上であり、第2領域の厚みが、第1領域の厚みの0.20〜0.96倍であるとき上述した変位抑制効果をより一層高めることができる。

【0029】

この発明に係る積層セラミックコンデンサにおいて、活性部が2つの第2領域を含み、これら2つの第2領域が、第1領域を積層方向に挟むように分布していると、積層セラミックコンデンサの積層方向での方向性をなくすことができ、積層セラミックコンデンサを上下対称の構造とすることができる。したがって、基板への実装時において、積層セラミックコンデンサの上下方向を管理する必要がなく、実装工程において煩雑さを招かないようにすることができるとともに、実装ミスを生じにくくすることができる。

【0030】

この発明に係る積層セラミックコンデンサにおいて、活性部が前述したような第3領域を含んでいると、基板変位を小さく保ちながら、積層セラミックコンデンサの容量等の特性を容易に調整することができる。

【図面の簡単な説明】

【0031】

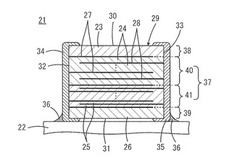

【図1】この発明の第1の実施形態による積層セラミックコンデンサ21を基板22上に実装された状態で示す断面図である。

【図2】この発明の第2の実施形態による積層セラミックコンデンサ51を基板22上に実装された状態で示す断面図である。

【図3】この発明の第3の実施形態による積層セラミックコンデンサ61を基板22上に実装された状態で示す断面図である。

【図4】この発明の第4の実施形態による積層セラミックコンデンサ71を基板22上に実装された状態で示す断面図である。

【図5】この発明による効果を確認するために実施した実験例において評価した基板変位の測定方法を説明するための図である。

【図6】この発明にとって興味ある従来の積層セラミックコンデンサ1を基板2上に実装された状態で示す断面図である。

【発明を実施するための形態】

【0032】

図1は、この発明の第1の実施形態による積層セラミックコンデンサ21を基板22上に実装された状態で示す断面図である。

【0033】

積層セラミックコンデンサ21は、複数の誘電体セラミック層23〜26と誘電体セラミック層23〜26間の複数の界面に沿ってそれぞれ形成された複数の内部電極27および28からなる積層構造を有する、コンデンサ本体29を備えている。コンデンサ本体29は、誘電体セラミック層23〜26の延びる方向に延びる第1および第2の主面30および31と、主面30および31に直交する方向にそれぞれ延びる、第1および第2の端面32および33と、第1および第2の側面(図1の紙面に平行な面であるが、図1では図示されない。)とによって規定される実質的に直方体形状をなしている。

【0034】

積層セラミックコンデンサ21は、また、誘電体セラミック層23〜26を介しての内部電極27および28の対向によって形成される静電容量を取り出すように内部電極27および28にそれぞれ接続される、第1および第2の外部電極34および35を備えている。第1および第2の外部電極34および35は、それぞれコンデンサ本体29の第1および第2の端面32および33上に形成されている。

【0035】

このような積層セラミックコンデンサ21は、コンデンサ本体29の第2の主面31が基板22に対向した状態で、外部電極34および35がはんだまたは導電性接着剤のような導電性接合材36によって接合されることによって基板22上に実装される。

【0036】

以上説明した構成は、図6に示した積層セラミックコンデンサ1の場合と共通している。以下に、図1に示した積層セラミックコンデンサ21の特徴的構成について説明する。

【0037】

コンデンサ本体29は、内部電極27および28の対向による静電容量形成に寄与する活性部37と静電容量形成に寄与しない外層部38および39とに区分されるが、活性部37は、さらに、積層方向に沿って分布する第1領域40と第2領域41とに区分される。このとき、第1領域40より第2の主面31側には、第2領域41が位置するようにされる。

【0038】

第2領域41における誘電体セラミック層25の誘電率は、第1領域40における誘電体セラミック層24の誘電率より低くされる。好ましくは、前者は後者の0.63倍以下とされ、より好ましくは、前者は後者の0.02〜0.43倍とされる。

【0039】

なお、外層部38および39における誘電体セラミック層23および26については、その誘電率を任意に選ぶことができるが、好ましくは、誘電体セラミック層23は、これに隣接する誘電体セラミック層24と同じ誘電体セラミックから構成され、誘電体セラミック層26は、これに隣接する誘電体セラミック層25と同じ誘電体セラミックから構成される。

【0040】

また、第2領域41における誘電体セラミック層25の体積に対する内部電極27および28の体積の比率は、第1領域40における誘電体セラミック層24の体積に対する内部電極27および28の体積の比率より高くされる。好ましくは、前者は後者の1.2倍以上とされ、より好ましくは、前者は後者の1.5倍以上とされる。

【0041】

上記のように内部電極27および28の体積比率を高めるため、たとえば内部電極27および28の各々の厚みを大きくすることがまず考えられるが、好ましくは次のような構成が採用される。すなわち、図1に示した第1領域40での内部電極27および28の形成態様と第2領域41での内部電極27および28の形成態様とを比較すればわかるように、第2領域41での内部電極27および28の隣り合う間隔は、第1領域40における内部電極27および28のそれより狭くされる。その結果、第2領域41での誘電体セラミック層25の厚みは、第1領域40での誘電体セラミック層24の厚みより小さくなる。これらのことから、第2領域41における誘電体セラミック層25の誘電率が低くされても、容量低下をそれほど招かないようにすることができる。

【0042】

このように、積層セラミックコンデンサ21によれば、基板22側の第2領域41において、誘電体セラミック層25の誘電率を低くすることにより、電界誘起歪みを低減することができるとともに、これに加え、内部電極27および28による物理的な歪み抑制作用を営ませることができるため、実装状態において、電界印加時の基板22の変位を抑制することができ、そのため、「鳴き」を抑制することができる。

【0043】

なお、第2領域41の厚みは、第1領域40の厚みの0.20〜0.96倍であることが好ましい。0.20倍未満であると、基板22の変位抑制効果が不十分な場合がある。他方、0.96倍を超える場合、基板22の変位抑制効果が、0.96倍以下の場合とほぼ同等となる。したがって、0.96倍を超えても、基板22の変位抑制効果がほぼ飽和し、変位抑制効果向上の点であまり意味がない。また、0.96倍を超えて第2領域41の厚みが厚くなればなるほど、内部電極27および28の枚数または厚みが増すので、コスト高につながる。

【0044】

なお、第1および第2領域40および41の境界付近において、セラミック成分の相互拡散層が若干生成することがあるが、特に問題とはならない。

【0045】

図2は、この発明の第2の実施形態による積層セラミックコンデンサ51を示す図1に対応する図である。図2において、図1に示す要素に相当する要素には同様の参照符号を付し、重複する説明は省略する。

【0046】

図2に示した積層セラミックコンデンサ51は、コンデンサ本体29に形成される活性部37において、2つの第2領域41を備え、これら2つの第2領域41が、第1領域40を積層方向に挟むように分布していることを特徴としている。

【0047】

このような積層セラミックコンデンサ51によれば、上下対称の構造となるので、図2に示したように、コンデンサ本体29の第2の主面31を基板22側に向けた状態で実装されても、逆に第1の主面30を基板22側に向けた状態で実装されても、第2領域41による基板22の変位抑制効果を発揮させることができる。

【0048】

図3は、この発明の第3の実施形態による積層セラミックコンデンサ61を示す図1に対応するものである。図3において、図1に示す要素に相当する要素には同様の参照符号を付し、重複する説明は省略する。

【0049】

図3に示した積層セラミックコンデンサ61は、コンデンサ本体29に形成される活性部37において、さらに第3領域62を備えることを特徴としている。第3領域62は第1領域40より第1の主面30側に位置される。第3領域62における誘電体セラミック層63の誘電率は、第1領域40における誘電体セラミック層24の誘電率より高くされる。

【0050】

上述した積層セラミックコンデンサ61によれば、第2領域41による基板22の変位抑制効果を維持しながら、積層セラミックコンデンサ61全体での容量等の特性を容易に調整することができる。

【0051】

なお、図3において、第3領域62における内部電極27および28が占める体積比率は、第1領域40における内部電極27および28が占める体積比率と同等であるように図示されたが、第3領域62における内部電極27および28の体積比率については任意に選ぶことができる。

【0052】

図4は、この発明の第4の実施形態による積層セラミックコンデンサ71を示す図1に対応する図である。図4において、図1に示す要素に相当する要素には同様の参照符号を付し、重複する説明は省略する。

【0053】

図4に示した積層セラミックコンデンサ71は、コンデンサ本体29に形成される活性部37がさらに第3領域72を備えることを特徴としている。第3領域72は第1領域40より第1の主面30側に位置される。なお、第3領域72は、図3に示した第3領域62とは次のような点で異なっている。すなわち、第3領域72における誘電体セラミック層73の体積に対する内部電極27および28の体積の比率は、第1領域40における誘電体セラミック層24の体積に対する内部電極27および28の比率より高くされる。この実施形態では、第3領域72での内部電極27および28の体積比率を高めるため、第2領域41の場合と同様、内部電極27および28の積層枚数が多くされ、かつ誘電体セラミック層73の厚みも小さくされる。

【0054】

上述した積層セラミックコンデンサ71によれば、図3に示した積層セラミックコンデンサ61の場合と同様、第2領域41による基板22の変位抑制効果を維持しながら、積層セラミックコンデンサ71全体での容量等の特性を容易に調整することができる。

【0055】

なお、積層セラミックコンデンサ71において、第3領域72における誘電体セラミック層73の誘電率は、たとえば第1領域40における誘電体セラミック層24の誘電率と同等に選ばれるが、これに限定されるものではなく、任意に選ばれることができる。

【0056】

次に、この発明による効果を確認するために実施した実験例について説明する。

【0057】

(実験例1)

実験例1では、図1に示した積層セラミックコンデンサ21と同様の構造を有する積層セラミックコンデンサを試料として作製した。ここで、各試料に係る積層セラミックコンデンサ全体の静電容量を10μFに固定し、表1に示すように、各種パラメータを変動させ、基板変位を評価した。なお、試料1は、活性部を第1領域のみで構成した比較例である。

【0058】

表1に示した各種パラメータは次のとおりである。

【0059】

ε1:第1領域における誘電体セラミック層の誘電率

ε2:第2領域における誘電体セラミック層の誘電率

d1:第1領域における誘電体セラミック層の厚み

d2:第2領域における誘電体セラミック層の厚み

m1:第1領域における内部電極の厚み

m2:第2領域における内部電極の厚み

n1:第1領域における内部電極の枚数

n1:第2領域における内部電極の枚数

T1:第1領域の厚み

T2:第2領域の厚み

TG:上側外層部と下側外層との合計厚み(ただし、上側外層部の厚みと下側外層部の厚みとは互いに同じである。)

なお、表1に示した(m2/d2)/(m1/d1)は、第1領域における誘電体セラミック層の厚みに対する内部電極の厚みの比率を分母とし、第2領域における誘電体セラミック層の厚みに対する内部電極の厚みの比率を分子とした比率であり、この比率が1を超える場合は、第2領域における誘電体セラミック層の体積に対する内部電極の体積の比率が、第1領域における誘電体セラミック層の体積に対する内部電極体積の比率より高いことを示している。

【0060】

また、表1に示した基板変位は、次のように評価したものである。図5には、基板変位の評価方法が示されていて、(a)は平面図であり、(b)は正面図である。

【0061】

図5に示すように、長さ100mm×幅40mm×厚さ1mmのガラスエポキシ樹脂からなる基板46を用意し、基板46の中央に各試料となる積層セラミックコンデンサ47を実装した。ここで、実装のための導電性接合材としてはんだを用い、積層セラミックコンデンサ47の長さ方向が基板46の長さ方向と平行になるようにした。そして、AC1kHzであってV0−P=3Vの正弦波を積層セラミックコンデンサ47に印加したときに生じる基板46の変位量48を、基板46の長辺の端から3mm内側の測定位置49においてレーザードップラー変位計を用いて測定した。すなわち、電圧が印加されると、積層セラミックコンデンサ47は積層方向に伸び、長さ方向および幅方向では縮むように歪み、応じて、基板46の端は持ち上がるように変位するので、この変位量48を上述のようにして測定した。表1に示した基板変位において、μmを単位として示した数値は、上記のように持ち上がった量に相当する変位量であり、%を単位とする数値は、試料1の変位量を100%としたときの比率を示している。

【0062】

また、各試料に係る積層セラミックコンデンサおよびその作製条件の詳細は次のとおりである。

【0063】

誘電体セラミック層を構成する誘電体セラミックとしては、誘電率が3500、2800、2200、1500、800、300および80の7種類のものを用意した。

【0064】

ここで、誘電率が3500、2800、2200、1500および800の5種類の誘電体セラミックについては、それぞれ焼結体粒径が0.5μm、0.4μm、0.3μm、0.2μmおよび0.1μmに対応しており、主成分がBaTiO3であり、副成分が共通してDy2O3、MgO、MnOおよびSiO2であり、粒径制御は、副成分の含有量を変えることによって制御した。焼成にあたっては1200℃の温度を適用した。

【0065】

誘電率が300の誘電体セラミックについては、主成分がBaTiO3であり、副成分がBaZrO3、Gd2O3、MgO、MnOおよびSiO2であり、焼結体粒径が約0.4μmであった。また、焼成にあたっては1250℃の温度を適用した。

【0066】

誘電率が80である誘電体セラミックについては、主成分がCa(Ti,Zr)O3であり、副成分がMnOおよびSiO2であり、焼結体粒径が約0.6μmであった。焼成にあたっては1200℃の温度を適用した。

【0067】

内部電極の主成分はNiであり、誘電体セラミック層と共焼結させた。焼成時の酸素分圧は、10−9.5MPa前後に設定した。

【0068】

各試料に係る積層セラミックコンデンサに備えるコンデンサ本体は、長さ方向寸法が3.2mm、幅方向寸法が1.6mmとした。なお、コンデンサ本体の厚み方向寸法については、第1領域および第2領域の設計に応じて変えた。

【0069】

また、誘電体セラミック層を介して互いに対向する内部電極の1対あたりの重なり面積は、3.3mm2とした。

【0070】

なお、それぞれの領域の誘電率は、片側の外部電極を除去し、内部電極の露出端にプローブを当てて静電容量を測定することにより、確認することが可能である。

【0071】

【表1】

【0072】

表1に示した基板変位に関して、試料1の基板変位を100%としたとき、80%以下のものが好ましく、65%以下のものがより好ましいと評価できる。

【0073】

試料2〜8は、第2領域における誘電体セラミック層の誘電率ε2が1500と比較的低く、第1領域に対する第2領域の内部電極の比率(m2/d2)/(m1/d1)が1.4と比較的高い。その結果、試料2〜8によれば、基板変位が比較的小さくなっている。

【0074】

特に、試料3〜6では、第2領域での第1領域に対する厚みの比率T2/T1が0.20〜0.96であるので、基板変位を65%以下に抑制することができ、より好ましい結果が得られている。特に、試料2では、基板変位を55%まで下げることができている。

【0075】

試料9〜15では、第2領域における誘電体セラミック層として、誘電率ε2が3500、2800、2200、1500、800、300および80のものがそれぞれ用いられている。すなわち、ε2/ε1の欄からわかるように試料9では、第2領域における誘電体セラミック層の誘電率ε2は、第1領域における誘電体セラミック層の誘電率ε1と同じであり、試料10〜15では、第2領域における誘電体セラミック層の誘電率のε2は、第1領域における誘電体セラミック層の誘電率ε1より低い。

【0076】

そのため、試料10〜15では、試料1に比べて基板変位を小さくすることができる。特に、試料11〜15では、ε2/ε1が0.63以下であるので、基板変位を71%以下に抑制することができ、さらに、試料12〜15では、ε2/ε1が0.02〜0.43の範囲にあるため、基板変位を56%以下に抑制することができる。

【0077】

試料16〜23では、第2領域における誘電体セラミック層の厚みd2または内部電極の厚みm2を変化させることにより、第1領域に対する第2領域の内部電極体積比率(m2/d2)/(m1/d1)を変化させている。試料17〜20、22および23のように、第2領域における誘電体セラミック層の体積に対する内部電極の体積の比率を、第1領域における誘電体セラミック層の体積に対する内部電極の体積の比率より高くすることにより、特に、(m2/d2)/(m1/d1)を1.2以上とすることにより、基板変位を73%以下に抑制することができ、さらに、試料18〜20、22および23のように(m2/d2)/(m1/d1)を1.5以上とすることにより、基板変位を58%以下に抑制することができる。

【0078】

試料24および25は、それぞれ、外層部の厚みTGを30μmおよび250μmとしたものである。これら試料24および25のように、外層部の厚みTGが100μmである他の試料に比べて極端に薄いか厚い場合であっても、第2領域を設けることにより、他の試料の場合と同様、基板変位を小さくすることができる。

【0079】

(実験例2)

実験例2では、図1に示した積層セラミックコンデンサ21と同様の構造を有する積層セラミックコンデンサを試料27として作製し、活性部を第1領域のみで構成した比較例となる積層セラミックコンデンサを試料26として作製した。ここで、各試料に係る積層セラミックコンデンサ全体の静電容量を47μFに固定し、表2に示すように、各種パラメータを設定し、実験例1の場合と同様に基板変位を評価した。

【0080】

実験例2において、誘電率3500の誘電体セラミックについては、実験例に1おける誘電率3500の誘電体セラミックと同じ材料を用い、他方、誘電率16000の誘電体セラミックについては、主成分がBa(Ti,Zr)O3であり、副成分がGd2O3、MgO、MnOおよびSiO2であり、焼結体粒径が約1.5μmのものを用いた。

【0081】

その他の条件は実験例1の場合と同様とした。

【0082】

【表2】

【0083】

試料27によれば、第2領域を設けていない試料26に比べて、基板変位を小さくすることができる。そして、この試料27から、第2領域における誘電体セラミック層の誘電率のε2が3500と比較的高くても、第1領域における誘電体セラミック層の誘電率ε1に対する比が小さければ、基板変位を効果的に抑制できることがわかる。

【0084】

(実験例3)

実験例3では、図1に示した積層セラミックコンデンサ21と同様の構造を有する積層セラミックコンデンサを試料29として作製するとともに、活性部を第1領域のみで構成した比較例としての積層セラミックコンデンサを試料28として作製した。ここで、各試料に係る積層セラミックコンデンサ全体の静電容量を4.7μFに固定し、表3に示すように、各種パラメータを設定し、実験例1および2の場合と同様に基板変位を評価した。

【0085】

実験例3において用いた誘電体セラミックの誘電率は1500および300であるが、これらの誘電体セラミックとしては実験例1で用いたものと同じ材料を用いた。

【0086】

その他の条件については実験例1と同様とした。

【0087】

【表3】

【0088】

試料29によれば、第2領域を設けない試料28に比べて、基板変位を小さくすることができる。また、試料29から、第1領域における誘電体セラミック層の誘電率が1500と比較的低くても、第2領域における誘電体セラミックの誘電率の比がさらに小さければ、基板変位を効果的に抑制できることがわかる。

【0089】

(実験例4)

実験例4では、図3に示した積層セラミックコンデンサ61と同様の構造を有する積層セラミックコンデンサを試料30として作製した。ここで、試料30に係る積層セラミックコンデンサ全体の静電容量を15μFとし、表2に示すように、各種パラメータを設定し、実験例1の場合と同様に基板変位を評価した。なお、実験例4における基板変位において、%を単位とする数値は、表1に示した試料1の基板変位を100%としたときの比率を示している。

【0090】

表4に示した各種パラメータであって、表1に示されていないものは次のとおりである。

【0091】

ε3:第3領域における誘電体セラミック層の誘電率

d3:第3領域における誘電体セラミック層の厚み

m3:第3領域における内部電極の厚み

n3:第3領域における内部電極の枚数

T3:第3領域の厚み

実験例4では、第1領域において、誘電率ε1が3500の誘電体セラミックを用いたが、これは実験例1で用いたものと同じである。また、第2領域において、誘電率ε2が800の誘電体セラミックを用いたが、これは、実験例1において用いたものと同じである。また、第3領域において、誘電率ε3が16000の誘電体セラミックを用いたが、これは実験例2で用いたものと同じである。

【0092】

その他の条件については実験例1と同様とした。

【0093】

【表4】

【0094】

試料30から、第1領域および第2領域について、この発明を規定する条件を満たしていれば、第3領域が設けられても、基板変位を小さく維持することができ、さらに、第3領域を設けることにより、容量等の特性を変え得ることがわかる。

【0095】

(実験例5)

実験例5では、図4に示した積層セラミックコンデンサ71と同様の構造を有する積層セラミックコンデンサを試料31として作製した。ここで、試料31に係る積層セラミックコンデンサ全体の静電容量を15μFとし、表5に示すように、各種パラメータを設定し、実験例1の場合と同様に基板変位を評価した。表5に示した各種パラメータは、表4に示した各種パラメータと同様である。また、表5に示した基板変位において、%を単位とする数値は、表1に示した試料1の基板変位を100%としたときの比率を示している。

【0096】

実験例5において、第1領域で用いた誘電率ε1および第3領域で用いた誘電率ε3が3500である誘電体セラミックとしては、実験例1で用いたものと同じものを用い、第2領域で用いた誘電率ε2が800の誘電体セラミックについても、実験例1において用いたものと同じものを用いた。

【0097】

その他の条件については実験例1と同様とした。

【0098】

【表5】

【0099】

試料31から、第1領域および第2領域の関係がこの発明において規定される条件を満たしていれば、第3領域が設けられても、基板変位を小さく維持することができ、また、第3領域が設けられることにより、容量等の特性を容易に変え得ることがわかる。

【符号の説明】

【0100】

21,51,61,71 積層セラミックコンデンサ

22 基板

23〜26,63,73 誘電体セラミック層

27,28 内部電極

29 コンデンサ本体

30 第1の主面

31 第2の主面

32 第1の端面

33 第2の端面

34 第1の外部電極

35 第2の外部電極

36 導電性接合材

37 活性部

40 第1領域

41 第2領域

62,72 第3領域

【技術分野】

【0001】

この発明は、積層セラミックコンデンサに関するもので、特に、積層セラミックコンデンサの、基板上への実装状態での電界印加時における「鳴き」を抑制するための改良に関するものである。

【背景技術】

【0002】

積層セラミックコンデンサにおいて、外部電極間に電圧を印加したとき、内部電極の隣り合うものが互いに対向している部分に誘電分極が発生する。この誘電分極によってもたらされた静電容量は、外部電極を通して取り出すことができる。

【0003】

上述のような内部電極の対向による静電容量の形成に寄与する、コンデンサ本体の活性部に存在する誘電体セラミック層によって与えられる誘電体は、印加される電圧に応じて、電界誘起歪みを起こす。積層セラミックコンデンサが基板上に表面実装されている場合、この電界誘起歪みにより、積層セラミックコンデンサが基板を変形させ、この変形の周波数によっては「鳴き」と呼ばれる音を生じさせる。そして、この「鳴き」が大きくなると、騒音の問題を引き起こす。

【0004】

上述の「鳴き」の抑制を意図したものではないが、この発明にとって興味ある積層セラミックコンデンサがたとえば特開2000−243657号公報(特許文献1)に記載されている。図6には、特許文献1に記載された積層セラミックコンデンサ1が基板2上に実装された状態で示されている。

【0005】

積層セラミックコンデンサ1は、複数の誘電体セラミック層3および4と誘電体セラミック層3および4間の複数の界面に沿ってそれぞれ形成された複数の内部電極5および6とからなる積層構造を有する、コンデンサ本体7を備えている。コンデンサ本体7は、誘電体セラミック層3および4の延びる方向に延びる第1および第2の主面8および9と、主面8および9に直交する方向にそれぞれ延びる、第1および第2の端面10および11と、第1および第2の側面(図6の紙面に平行な面であるが、図6では図示されない。)とによって規定される直方体形状をなしている。

【0006】

積層セラミックコンデンサ1は、また、誘電体セラミック層3または4を介しての内部電極5および6の対向によって形成される静電容量を取り出すように内部電極5および6にそれぞれ接続される、第1および第2の外部電極12および13を備えている。第1および第2の外部電極12および13は、コンデンサ本体7の第1および第2の端面10および11上にそれぞれ形成されている。このような積層セラミックコンデンサ1は、コンデンサ本体7の第2の主面9が基板2に対向した状態で、外部電極12および13がはんだまたは導電性接着剤のような導電性接合材14によって接合されることによって基板2上に実装される。

【0007】

コンデンサ本体7は、基板2側とは反対側の上領域15と基板2側の下領域16とに区分され、上領域15では比較的大きい容量が取り出されるようにされ、下領域16では比較的小さい容量が取り出されるようにされる。

【0008】

より詳細には、上領域15においては、誘電体セラミック層3を構成する誘電体セラミックとして誘電率の比較的高いものが用いられるとともに、内部電極5および6の積層数が比較的多くされ、かつ内部電極5および6間の間隔が比較的小さくされる。他方、下領域6においては、誘電体セラミック層4を構成する誘電体セラミックとして誘電率の比較的低いものが用いられるとともに、内部電極5および6の積層数が比較的少なくされ、かつ内部電極5および6間の間隔が比較的大きくされる。

【0009】

このようにして、図6に示した積層セラミックコンデンサ1によれば、取得静電容量の比較的大きい上領域15と比較的小さい下領域16とを有しているので、比較的広い周波数範囲にわたって良好な伝達特性を得ることができる。

【0010】

また、特許文献1には記載されていないが、下領域16において取得静電容量が比較的小さくされることによって、前述した電界誘起歪みが小さくなり、このことから、基板2上への実装状態での電界印加時における「鳴き」の低減が期待される。

【0011】

しかしながら、図6に示したような構造の積層セラミックコンデンサ1では、電界誘起歪みの低減効果が十分ではなく、それゆえ、「鳴き」を低減する効果について、より改善されるべき余地がある。

【先行技術文献】

【特許文献】

【0012】

【特許文献1】特開2000−243657号公報

【発明の概要】

【発明が解決しようとする課題】

【0013】

そこで、この発明の目的は、上述した課題を解決し得る積層セラミックコンデンサを提供しようとすることである。

【課題を解決するための手段】

【0014】

この発明に係る積層セラミックコンデンサは、コンデンサ本体と第1および第2の外部電極とを備えている。

【0015】

コンデンサ本体は、複数の誘電体セラミック層と誘電体セラミック層間の複数の界面に沿ってそれぞれ形成された複数の内部電極とからなる積層構造を有し、誘電体セラミック層の延びる方向に延びる第1および第2の主面と、主面に直交する方向にそれぞれ延びる、第1および第2の端面と、第1および第2の側面とによって規定される実質的に直方体形状をなしている。

【0016】

第1および第2の外部電極は、誘電体セラミック層を介しての内部電極の対向によって形成される静電容量を取り出すように内部電極の特定のものに接続されながら、コンデンサ本体の第1および第2の端面上にそれぞれ形成される。

【0017】

また、この積層セラミックコンデンサは、コンデンサ本体の第2の主面が基板に対向した状態で、外部電極が導電性接合材によって接合されることによって基板上に実装される。

【0018】

このような構成の積層セラミックコンデンサにおいて、前述した技術的課題を解決するため、この発明では、次のような構成を備えることを特徴としている。

【0019】

コンデンサ本体における内部電極の対向による静電容量形成に寄与する活性部は、積層方向に沿って分布する少なくとも第1領域と第2領域とを含む複数の領域に区分され、第1領域より第2の主面側には第2領域が位置される。

【0020】

そして、第2領域における誘電体セラミック層の誘電率は、第1領域における誘電体セラミック層の誘電率より低くされるとともに、第2領域における誘電体セラミック層の体積に対する内部電極の体積の比率は、第1領域における誘電体セラミック層の体積に対する内部電極の体積の比率より高くされることを特徴としている。

【0021】

この発明において、第2領域における誘電体セラミック層の誘電率は、第1領域における誘電体セラミック層の誘電率の0.63倍以下であるとともに、第2領域における誘電体セラミック層の体積に対する内部電極の体積の比率は、第1領域における誘電体セラミック層の体積に対する内部電極の体積の比率の1.2倍以上であることが好ましい。

【0022】

より好ましくは、第2領域における誘電体セラミック層の誘電率は、第1領域における誘電体セラミック層の誘電率の0.02〜0.43倍であるとともに、第2領域における誘電体セラミック層の体積に対する内部電極の体積の比率は、第1領域における誘電体セラミック層の体積に対する内部電極の体積の比率の1.5倍以上であり、さらに、第2領域の厚みは、第1領域の厚みの0.20〜0.96倍である。

【0023】

この発明に係る積層セラミックコンデンサにおいて、活性部は2つの第2領域を含み、2つの第2領域は、第1領域を積層方向に挟むように分布していてもよい。

【0024】

あるいは、活性部はさらに第3領域を含み、この第3領域は第1領域より第1の主面側に位置されていてもよい。この場合、第3領域における誘電体セラミック層の誘電率は、第1領域における誘電体セラミック層の誘電率より高くされたり、第3領域における誘電体セラミック層の体積に対する内部電極の体積の比率は、第1領域における誘電体セラミック層の体積に対する内部電極の体積の比率より高くされたりすることができる。

【発明の効果】

【0025】

基板の「鳴き」を低減するには、積層セラミックコンデンサにおける、特に基板側の変位量を低減することが効果的である。この発明によれば、コンデンサ本体における基板側の第2領域において、比較的低い誘電率の誘電体セラミック層を採用するとともに、内部電極の体積割合を比較的高くすることにより、変位量を効果的に低減することができる。すなわち、低誘電率の誘電体を用いたことによって電界誘起歪みが低減され、また、この電界誘起歪みの低減に加えて、内部電極による物理的な歪み抑制が相乗的に作用し、予想外に大きな変位抑制を実現することができる。

【0026】

なお、第2領域における誘電体セラミック層の誘電率を比較的低くすることによって容量が低下するといった懸念については、内部電極の体積割合の増加を、内部電極の枚数を多くすることによって達成するようにすれば、内部電極の重なり面積が増加するとともに、内部電極間の誘電体セラミック層の厚みも小さくなるため、容量低下を有利に補償することができる。このことから、「鳴き」を低減できるだけでなく、これと静電容量との両立も図ることができる。

【0027】

この発明において、第2領域における誘電体セラミック層の誘電率が、第1領域における誘電体セラミック層の誘電率の0.63倍以下であり、第2領域における誘電体セラミック層の体積に対する内部電極の体積の比率が、第1領域における誘電体セラミック層の体積に対する内部電極の体積の比率の1.2倍以上であるとき、変位抑制効果をより高めることができる。

【0028】

また、より限定的に、第2領域における誘電体セラミック層の誘電率が、第1領域における誘電体セラミック層の誘電率の0.02〜0.43倍であり、第2領域における誘電体セラミック層の体積に対する内部電極の体積の比率が、第1領域における誘電体セラミック層の体積に対する内部電極の比率の1.5倍以上であり、第2領域の厚みが、第1領域の厚みの0.20〜0.96倍であるとき上述した変位抑制効果をより一層高めることができる。

【0029】

この発明に係る積層セラミックコンデンサにおいて、活性部が2つの第2領域を含み、これら2つの第2領域が、第1領域を積層方向に挟むように分布していると、積層セラミックコンデンサの積層方向での方向性をなくすことができ、積層セラミックコンデンサを上下対称の構造とすることができる。したがって、基板への実装時において、積層セラミックコンデンサの上下方向を管理する必要がなく、実装工程において煩雑さを招かないようにすることができるとともに、実装ミスを生じにくくすることができる。

【0030】

この発明に係る積層セラミックコンデンサにおいて、活性部が前述したような第3領域を含んでいると、基板変位を小さく保ちながら、積層セラミックコンデンサの容量等の特性を容易に調整することができる。

【図面の簡単な説明】

【0031】

【図1】この発明の第1の実施形態による積層セラミックコンデンサ21を基板22上に実装された状態で示す断面図である。

【図2】この発明の第2の実施形態による積層セラミックコンデンサ51を基板22上に実装された状態で示す断面図である。

【図3】この発明の第3の実施形態による積層セラミックコンデンサ61を基板22上に実装された状態で示す断面図である。

【図4】この発明の第4の実施形態による積層セラミックコンデンサ71を基板22上に実装された状態で示す断面図である。

【図5】この発明による効果を確認するために実施した実験例において評価した基板変位の測定方法を説明するための図である。

【図6】この発明にとって興味ある従来の積層セラミックコンデンサ1を基板2上に実装された状態で示す断面図である。

【発明を実施するための形態】

【0032】

図1は、この発明の第1の実施形態による積層セラミックコンデンサ21を基板22上に実装された状態で示す断面図である。

【0033】

積層セラミックコンデンサ21は、複数の誘電体セラミック層23〜26と誘電体セラミック層23〜26間の複数の界面に沿ってそれぞれ形成された複数の内部電極27および28からなる積層構造を有する、コンデンサ本体29を備えている。コンデンサ本体29は、誘電体セラミック層23〜26の延びる方向に延びる第1および第2の主面30および31と、主面30および31に直交する方向にそれぞれ延びる、第1および第2の端面32および33と、第1および第2の側面(図1の紙面に平行な面であるが、図1では図示されない。)とによって規定される実質的に直方体形状をなしている。

【0034】

積層セラミックコンデンサ21は、また、誘電体セラミック層23〜26を介しての内部電極27および28の対向によって形成される静電容量を取り出すように内部電極27および28にそれぞれ接続される、第1および第2の外部電極34および35を備えている。第1および第2の外部電極34および35は、それぞれコンデンサ本体29の第1および第2の端面32および33上に形成されている。

【0035】

このような積層セラミックコンデンサ21は、コンデンサ本体29の第2の主面31が基板22に対向した状態で、外部電極34および35がはんだまたは導電性接着剤のような導電性接合材36によって接合されることによって基板22上に実装される。

【0036】

以上説明した構成は、図6に示した積層セラミックコンデンサ1の場合と共通している。以下に、図1に示した積層セラミックコンデンサ21の特徴的構成について説明する。

【0037】

コンデンサ本体29は、内部電極27および28の対向による静電容量形成に寄与する活性部37と静電容量形成に寄与しない外層部38および39とに区分されるが、活性部37は、さらに、積層方向に沿って分布する第1領域40と第2領域41とに区分される。このとき、第1領域40より第2の主面31側には、第2領域41が位置するようにされる。

【0038】

第2領域41における誘電体セラミック層25の誘電率は、第1領域40における誘電体セラミック層24の誘電率より低くされる。好ましくは、前者は後者の0.63倍以下とされ、より好ましくは、前者は後者の0.02〜0.43倍とされる。

【0039】

なお、外層部38および39における誘電体セラミック層23および26については、その誘電率を任意に選ぶことができるが、好ましくは、誘電体セラミック層23は、これに隣接する誘電体セラミック層24と同じ誘電体セラミックから構成され、誘電体セラミック層26は、これに隣接する誘電体セラミック層25と同じ誘電体セラミックから構成される。

【0040】

また、第2領域41における誘電体セラミック層25の体積に対する内部電極27および28の体積の比率は、第1領域40における誘電体セラミック層24の体積に対する内部電極27および28の体積の比率より高くされる。好ましくは、前者は後者の1.2倍以上とされ、より好ましくは、前者は後者の1.5倍以上とされる。

【0041】

上記のように内部電極27および28の体積比率を高めるため、たとえば内部電極27および28の各々の厚みを大きくすることがまず考えられるが、好ましくは次のような構成が採用される。すなわち、図1に示した第1領域40での内部電極27および28の形成態様と第2領域41での内部電極27および28の形成態様とを比較すればわかるように、第2領域41での内部電極27および28の隣り合う間隔は、第1領域40における内部電極27および28のそれより狭くされる。その結果、第2領域41での誘電体セラミック層25の厚みは、第1領域40での誘電体セラミック層24の厚みより小さくなる。これらのことから、第2領域41における誘電体セラミック層25の誘電率が低くされても、容量低下をそれほど招かないようにすることができる。

【0042】

このように、積層セラミックコンデンサ21によれば、基板22側の第2領域41において、誘電体セラミック層25の誘電率を低くすることにより、電界誘起歪みを低減することができるとともに、これに加え、内部電極27および28による物理的な歪み抑制作用を営ませることができるため、実装状態において、電界印加時の基板22の変位を抑制することができ、そのため、「鳴き」を抑制することができる。

【0043】

なお、第2領域41の厚みは、第1領域40の厚みの0.20〜0.96倍であることが好ましい。0.20倍未満であると、基板22の変位抑制効果が不十分な場合がある。他方、0.96倍を超える場合、基板22の変位抑制効果が、0.96倍以下の場合とほぼ同等となる。したがって、0.96倍を超えても、基板22の変位抑制効果がほぼ飽和し、変位抑制効果向上の点であまり意味がない。また、0.96倍を超えて第2領域41の厚みが厚くなればなるほど、内部電極27および28の枚数または厚みが増すので、コスト高につながる。

【0044】

なお、第1および第2領域40および41の境界付近において、セラミック成分の相互拡散層が若干生成することがあるが、特に問題とはならない。

【0045】

図2は、この発明の第2の実施形態による積層セラミックコンデンサ51を示す図1に対応する図である。図2において、図1に示す要素に相当する要素には同様の参照符号を付し、重複する説明は省略する。

【0046】

図2に示した積層セラミックコンデンサ51は、コンデンサ本体29に形成される活性部37において、2つの第2領域41を備え、これら2つの第2領域41が、第1領域40を積層方向に挟むように分布していることを特徴としている。

【0047】

このような積層セラミックコンデンサ51によれば、上下対称の構造となるので、図2に示したように、コンデンサ本体29の第2の主面31を基板22側に向けた状態で実装されても、逆に第1の主面30を基板22側に向けた状態で実装されても、第2領域41による基板22の変位抑制効果を発揮させることができる。

【0048】

図3は、この発明の第3の実施形態による積層セラミックコンデンサ61を示す図1に対応するものである。図3において、図1に示す要素に相当する要素には同様の参照符号を付し、重複する説明は省略する。

【0049】

図3に示した積層セラミックコンデンサ61は、コンデンサ本体29に形成される活性部37において、さらに第3領域62を備えることを特徴としている。第3領域62は第1領域40より第1の主面30側に位置される。第3領域62における誘電体セラミック層63の誘電率は、第1領域40における誘電体セラミック層24の誘電率より高くされる。

【0050】

上述した積層セラミックコンデンサ61によれば、第2領域41による基板22の変位抑制効果を維持しながら、積層セラミックコンデンサ61全体での容量等の特性を容易に調整することができる。

【0051】

なお、図3において、第3領域62における内部電極27および28が占める体積比率は、第1領域40における内部電極27および28が占める体積比率と同等であるように図示されたが、第3領域62における内部電極27および28の体積比率については任意に選ぶことができる。

【0052】

図4は、この発明の第4の実施形態による積層セラミックコンデンサ71を示す図1に対応する図である。図4において、図1に示す要素に相当する要素には同様の参照符号を付し、重複する説明は省略する。

【0053】

図4に示した積層セラミックコンデンサ71は、コンデンサ本体29に形成される活性部37がさらに第3領域72を備えることを特徴としている。第3領域72は第1領域40より第1の主面30側に位置される。なお、第3領域72は、図3に示した第3領域62とは次のような点で異なっている。すなわち、第3領域72における誘電体セラミック層73の体積に対する内部電極27および28の体積の比率は、第1領域40における誘電体セラミック層24の体積に対する内部電極27および28の比率より高くされる。この実施形態では、第3領域72での内部電極27および28の体積比率を高めるため、第2領域41の場合と同様、内部電極27および28の積層枚数が多くされ、かつ誘電体セラミック層73の厚みも小さくされる。

【0054】

上述した積層セラミックコンデンサ71によれば、図3に示した積層セラミックコンデンサ61の場合と同様、第2領域41による基板22の変位抑制効果を維持しながら、積層セラミックコンデンサ71全体での容量等の特性を容易に調整することができる。

【0055】

なお、積層セラミックコンデンサ71において、第3領域72における誘電体セラミック層73の誘電率は、たとえば第1領域40における誘電体セラミック層24の誘電率と同等に選ばれるが、これに限定されるものではなく、任意に選ばれることができる。

【0056】

次に、この発明による効果を確認するために実施した実験例について説明する。

【0057】

(実験例1)

実験例1では、図1に示した積層セラミックコンデンサ21と同様の構造を有する積層セラミックコンデンサを試料として作製した。ここで、各試料に係る積層セラミックコンデンサ全体の静電容量を10μFに固定し、表1に示すように、各種パラメータを変動させ、基板変位を評価した。なお、試料1は、活性部を第1領域のみで構成した比較例である。

【0058】

表1に示した各種パラメータは次のとおりである。

【0059】

ε1:第1領域における誘電体セラミック層の誘電率

ε2:第2領域における誘電体セラミック層の誘電率

d1:第1領域における誘電体セラミック層の厚み

d2:第2領域における誘電体セラミック層の厚み

m1:第1領域における内部電極の厚み

m2:第2領域における内部電極の厚み

n1:第1領域における内部電極の枚数

n1:第2領域における内部電極の枚数

T1:第1領域の厚み

T2:第2領域の厚み

TG:上側外層部と下側外層との合計厚み(ただし、上側外層部の厚みと下側外層部の厚みとは互いに同じである。)

なお、表1に示した(m2/d2)/(m1/d1)は、第1領域における誘電体セラミック層の厚みに対する内部電極の厚みの比率を分母とし、第2領域における誘電体セラミック層の厚みに対する内部電極の厚みの比率を分子とした比率であり、この比率が1を超える場合は、第2領域における誘電体セラミック層の体積に対する内部電極の体積の比率が、第1領域における誘電体セラミック層の体積に対する内部電極体積の比率より高いことを示している。

【0060】

また、表1に示した基板変位は、次のように評価したものである。図5には、基板変位の評価方法が示されていて、(a)は平面図であり、(b)は正面図である。

【0061】

図5に示すように、長さ100mm×幅40mm×厚さ1mmのガラスエポキシ樹脂からなる基板46を用意し、基板46の中央に各試料となる積層セラミックコンデンサ47を実装した。ここで、実装のための導電性接合材としてはんだを用い、積層セラミックコンデンサ47の長さ方向が基板46の長さ方向と平行になるようにした。そして、AC1kHzであってV0−P=3Vの正弦波を積層セラミックコンデンサ47に印加したときに生じる基板46の変位量48を、基板46の長辺の端から3mm内側の測定位置49においてレーザードップラー変位計を用いて測定した。すなわち、電圧が印加されると、積層セラミックコンデンサ47は積層方向に伸び、長さ方向および幅方向では縮むように歪み、応じて、基板46の端は持ち上がるように変位するので、この変位量48を上述のようにして測定した。表1に示した基板変位において、μmを単位として示した数値は、上記のように持ち上がった量に相当する変位量であり、%を単位とする数値は、試料1の変位量を100%としたときの比率を示している。

【0062】

また、各試料に係る積層セラミックコンデンサおよびその作製条件の詳細は次のとおりである。

【0063】

誘電体セラミック層を構成する誘電体セラミックとしては、誘電率が3500、2800、2200、1500、800、300および80の7種類のものを用意した。

【0064】

ここで、誘電率が3500、2800、2200、1500および800の5種類の誘電体セラミックについては、それぞれ焼結体粒径が0.5μm、0.4μm、0.3μm、0.2μmおよび0.1μmに対応しており、主成分がBaTiO3であり、副成分が共通してDy2O3、MgO、MnOおよびSiO2であり、粒径制御は、副成分の含有量を変えることによって制御した。焼成にあたっては1200℃の温度を適用した。

【0065】

誘電率が300の誘電体セラミックについては、主成分がBaTiO3であり、副成分がBaZrO3、Gd2O3、MgO、MnOおよびSiO2であり、焼結体粒径が約0.4μmであった。また、焼成にあたっては1250℃の温度を適用した。

【0066】

誘電率が80である誘電体セラミックについては、主成分がCa(Ti,Zr)O3であり、副成分がMnOおよびSiO2であり、焼結体粒径が約0.6μmであった。焼成にあたっては1200℃の温度を適用した。

【0067】

内部電極の主成分はNiであり、誘電体セラミック層と共焼結させた。焼成時の酸素分圧は、10−9.5MPa前後に設定した。

【0068】

各試料に係る積層セラミックコンデンサに備えるコンデンサ本体は、長さ方向寸法が3.2mm、幅方向寸法が1.6mmとした。なお、コンデンサ本体の厚み方向寸法については、第1領域および第2領域の設計に応じて変えた。

【0069】

また、誘電体セラミック層を介して互いに対向する内部電極の1対あたりの重なり面積は、3.3mm2とした。

【0070】

なお、それぞれの領域の誘電率は、片側の外部電極を除去し、内部電極の露出端にプローブを当てて静電容量を測定することにより、確認することが可能である。

【0071】

【表1】

【0072】

表1に示した基板変位に関して、試料1の基板変位を100%としたとき、80%以下のものが好ましく、65%以下のものがより好ましいと評価できる。

【0073】

試料2〜8は、第2領域における誘電体セラミック層の誘電率ε2が1500と比較的低く、第1領域に対する第2領域の内部電極の比率(m2/d2)/(m1/d1)が1.4と比較的高い。その結果、試料2〜8によれば、基板変位が比較的小さくなっている。

【0074】

特に、試料3〜6では、第2領域での第1領域に対する厚みの比率T2/T1が0.20〜0.96であるので、基板変位を65%以下に抑制することができ、より好ましい結果が得られている。特に、試料2では、基板変位を55%まで下げることができている。

【0075】

試料9〜15では、第2領域における誘電体セラミック層として、誘電率ε2が3500、2800、2200、1500、800、300および80のものがそれぞれ用いられている。すなわち、ε2/ε1の欄からわかるように試料9では、第2領域における誘電体セラミック層の誘電率ε2は、第1領域における誘電体セラミック層の誘電率ε1と同じであり、試料10〜15では、第2領域における誘電体セラミック層の誘電率のε2は、第1領域における誘電体セラミック層の誘電率ε1より低い。

【0076】

そのため、試料10〜15では、試料1に比べて基板変位を小さくすることができる。特に、試料11〜15では、ε2/ε1が0.63以下であるので、基板変位を71%以下に抑制することができ、さらに、試料12〜15では、ε2/ε1が0.02〜0.43の範囲にあるため、基板変位を56%以下に抑制することができる。

【0077】

試料16〜23では、第2領域における誘電体セラミック層の厚みd2または内部電極の厚みm2を変化させることにより、第1領域に対する第2領域の内部電極体積比率(m2/d2)/(m1/d1)を変化させている。試料17〜20、22および23のように、第2領域における誘電体セラミック層の体積に対する内部電極の体積の比率を、第1領域における誘電体セラミック層の体積に対する内部電極の体積の比率より高くすることにより、特に、(m2/d2)/(m1/d1)を1.2以上とすることにより、基板変位を73%以下に抑制することができ、さらに、試料18〜20、22および23のように(m2/d2)/(m1/d1)を1.5以上とすることにより、基板変位を58%以下に抑制することができる。

【0078】

試料24および25は、それぞれ、外層部の厚みTGを30μmおよび250μmとしたものである。これら試料24および25のように、外層部の厚みTGが100μmである他の試料に比べて極端に薄いか厚い場合であっても、第2領域を設けることにより、他の試料の場合と同様、基板変位を小さくすることができる。

【0079】

(実験例2)

実験例2では、図1に示した積層セラミックコンデンサ21と同様の構造を有する積層セラミックコンデンサを試料27として作製し、活性部を第1領域のみで構成した比較例となる積層セラミックコンデンサを試料26として作製した。ここで、各試料に係る積層セラミックコンデンサ全体の静電容量を47μFに固定し、表2に示すように、各種パラメータを設定し、実験例1の場合と同様に基板変位を評価した。

【0080】

実験例2において、誘電率3500の誘電体セラミックについては、実験例に1おける誘電率3500の誘電体セラミックと同じ材料を用い、他方、誘電率16000の誘電体セラミックについては、主成分がBa(Ti,Zr)O3であり、副成分がGd2O3、MgO、MnOおよびSiO2であり、焼結体粒径が約1.5μmのものを用いた。

【0081】

その他の条件は実験例1の場合と同様とした。

【0082】

【表2】

【0083】

試料27によれば、第2領域を設けていない試料26に比べて、基板変位を小さくすることができる。そして、この試料27から、第2領域における誘電体セラミック層の誘電率のε2が3500と比較的高くても、第1領域における誘電体セラミック層の誘電率ε1に対する比が小さければ、基板変位を効果的に抑制できることがわかる。

【0084】

(実験例3)

実験例3では、図1に示した積層セラミックコンデンサ21と同様の構造を有する積層セラミックコンデンサを試料29として作製するとともに、活性部を第1領域のみで構成した比較例としての積層セラミックコンデンサを試料28として作製した。ここで、各試料に係る積層セラミックコンデンサ全体の静電容量を4.7μFに固定し、表3に示すように、各種パラメータを設定し、実験例1および2の場合と同様に基板変位を評価した。

【0085】

実験例3において用いた誘電体セラミックの誘電率は1500および300であるが、これらの誘電体セラミックとしては実験例1で用いたものと同じ材料を用いた。

【0086】

その他の条件については実験例1と同様とした。

【0087】

【表3】

【0088】

試料29によれば、第2領域を設けない試料28に比べて、基板変位を小さくすることができる。また、試料29から、第1領域における誘電体セラミック層の誘電率が1500と比較的低くても、第2領域における誘電体セラミックの誘電率の比がさらに小さければ、基板変位を効果的に抑制できることがわかる。

【0089】

(実験例4)

実験例4では、図3に示した積層セラミックコンデンサ61と同様の構造を有する積層セラミックコンデンサを試料30として作製した。ここで、試料30に係る積層セラミックコンデンサ全体の静電容量を15μFとし、表2に示すように、各種パラメータを設定し、実験例1の場合と同様に基板変位を評価した。なお、実験例4における基板変位において、%を単位とする数値は、表1に示した試料1の基板変位を100%としたときの比率を示している。

【0090】

表4に示した各種パラメータであって、表1に示されていないものは次のとおりである。

【0091】

ε3:第3領域における誘電体セラミック層の誘電率

d3:第3領域における誘電体セラミック層の厚み

m3:第3領域における内部電極の厚み

n3:第3領域における内部電極の枚数

T3:第3領域の厚み

実験例4では、第1領域において、誘電率ε1が3500の誘電体セラミックを用いたが、これは実験例1で用いたものと同じである。また、第2領域において、誘電率ε2が800の誘電体セラミックを用いたが、これは、実験例1において用いたものと同じである。また、第3領域において、誘電率ε3が16000の誘電体セラミックを用いたが、これは実験例2で用いたものと同じである。

【0092】

その他の条件については実験例1と同様とした。

【0093】

【表4】

【0094】

試料30から、第1領域および第2領域について、この発明を規定する条件を満たしていれば、第3領域が設けられても、基板変位を小さく維持することができ、さらに、第3領域を設けることにより、容量等の特性を変え得ることがわかる。

【0095】

(実験例5)

実験例5では、図4に示した積層セラミックコンデンサ71と同様の構造を有する積層セラミックコンデンサを試料31として作製した。ここで、試料31に係る積層セラミックコンデンサ全体の静電容量を15μFとし、表5に示すように、各種パラメータを設定し、実験例1の場合と同様に基板変位を評価した。表5に示した各種パラメータは、表4に示した各種パラメータと同様である。また、表5に示した基板変位において、%を単位とする数値は、表1に示した試料1の基板変位を100%としたときの比率を示している。

【0096】

実験例5において、第1領域で用いた誘電率ε1および第3領域で用いた誘電率ε3が3500である誘電体セラミックとしては、実験例1で用いたものと同じものを用い、第2領域で用いた誘電率ε2が800の誘電体セラミックについても、実験例1において用いたものと同じものを用いた。

【0097】

その他の条件については実験例1と同様とした。

【0098】

【表5】

【0099】

試料31から、第1領域および第2領域の関係がこの発明において規定される条件を満たしていれば、第3領域が設けられても、基板変位を小さく維持することができ、また、第3領域が設けられることにより、容量等の特性を容易に変え得ることがわかる。

【符号の説明】

【0100】

21,51,61,71 積層セラミックコンデンサ

22 基板

23〜26,63,73 誘電体セラミック層

27,28 内部電極

29 コンデンサ本体

30 第1の主面

31 第2の主面

32 第1の端面

33 第2の端面

34 第1の外部電極

35 第2の外部電極

36 導電性接合材

37 活性部

40 第1領域

41 第2領域

62,72 第3領域

【特許請求の範囲】

【請求項1】

複数の誘電体セラミック層と前記誘電体セラミック層間の複数の界面に沿ってそれぞれ形成された複数の内部電極とからなる積層構造を有し、前記誘電体セラミック層の延びる方向に延びる第1および第2の主面と、前記主面に直交する方向にそれぞれ延びる、第1および第2の端面と、第1および第2の側面とによって規定される実質的に直方体形状をなす、コンデンサ本体と、

前記誘電体セラミック層を介しての前記内部電極の対向によって形成される静電容量を取り出すように前記内部電極の特定のものに接続されながら、前記コンデンサ本体の前記第1および第2の端面上にそれぞれ形成される、第1および第2の外部電極と

を備え、

前記コンデンサ本体の前記第2の主面が基板に対向した状態で、前記外部電極が導電性接合材によって接合されることによって基板上に実装される、積層セラミックコンデンサであって、

前記コンデンサ本体における前記内部電極の対向による静電容量形成に寄与する活性部は、積層方向に沿って分布する少なくとも第1領域と第2領域とを含む複数の領域に区分され、前記第1領域より前記第2の主面側には、前記第2領域が位置され、

前記第2領域における前記誘電体セラミック層の誘電率は、前記第1領域における前記誘電体セラミック層の誘電率より低く、

前記第2領域における前記誘電体セラミック層の体積に対する前記内部電極の体積の比率は、前記第1領域における前記誘電体セラミック層の体積に対する前記内部電極の体積の比率より高い、

積層セラミックコンデンサ。

【請求項2】

前記第2領域における前記誘電体セラミック層の誘電率は、前記第1領域における前記誘電体セラミック層の誘電率の0.63倍以下であり、前記第2領域における前記誘電体セラミック層の体積に対する前記内部電極の体積の比率は、前記第1領域における前記誘電体セラミック層の体積に対する前記内部電極の体積の比率の1.2倍以上である、請求項1に記載の積層セラミックコンデンサ。

【請求項3】

前記第2領域における前記誘電体セラミック層の誘電率は、前記第1領域における前記誘電体セラミック層の誘電率の0.02〜0.43倍であり、前記第2領域における前記誘電体セラミック層の体積に対する前記内部電極の体積の比率は、前記第1領域における前記誘電体セラミック層の体積に対する前記内部電極の体積の比率の1.5倍以上であり、前記第2領域の厚みは、前記第1領域の厚みの0.20〜0.96倍である、請求項2に記載の積層セラミックコンデンサ。

【請求項4】

前記活性部は2つの前記第2領域を含み、前記2つの第2領域は、前記第1領域を積層方向に挟むように分布する、請求項1ないし3のいずれかに記載の積層セラミックコンデンサ。

【請求項5】

前記活性部はさらに第3領域を含み、前記第3領域は前記第1領域より前記第1の主面側に位置され、前記第3領域における前記誘電体セラミック層の誘電率は、前記第1領域における前記誘電体セラミック層の誘電率より高い、請求項1ないし3のいずれかに記載の積層セラミックコンデンサ。

【請求項6】

前記活性部はさらに第3領域を含み、前記第3領域は前記第1領域より前記第1の主面側に位置され、前記第3領域における前記誘電体セラミック層の体積に対する前記内部電極の体積の比率は、前記第1領域における前記誘電体セラミック層の体積に対する前記内部電極の体積の比率より高い、請求項1ないし3のいずれかに記載の積層セラミックコンデンサ。

【請求項1】

複数の誘電体セラミック層と前記誘電体セラミック層間の複数の界面に沿ってそれぞれ形成された複数の内部電極とからなる積層構造を有し、前記誘電体セラミック層の延びる方向に延びる第1および第2の主面と、前記主面に直交する方向にそれぞれ延びる、第1および第2の端面と、第1および第2の側面とによって規定される実質的に直方体形状をなす、コンデンサ本体と、

前記誘電体セラミック層を介しての前記内部電極の対向によって形成される静電容量を取り出すように前記内部電極の特定のものに接続されながら、前記コンデンサ本体の前記第1および第2の端面上にそれぞれ形成される、第1および第2の外部電極と

を備え、

前記コンデンサ本体の前記第2の主面が基板に対向した状態で、前記外部電極が導電性接合材によって接合されることによって基板上に実装される、積層セラミックコンデンサであって、

前記コンデンサ本体における前記内部電極の対向による静電容量形成に寄与する活性部は、積層方向に沿って分布する少なくとも第1領域と第2領域とを含む複数の領域に区分され、前記第1領域より前記第2の主面側には、前記第2領域が位置され、

前記第2領域における前記誘電体セラミック層の誘電率は、前記第1領域における前記誘電体セラミック層の誘電率より低く、

前記第2領域における前記誘電体セラミック層の体積に対する前記内部電極の体積の比率は、前記第1領域における前記誘電体セラミック層の体積に対する前記内部電極の体積の比率より高い、

積層セラミックコンデンサ。

【請求項2】

前記第2領域における前記誘電体セラミック層の誘電率は、前記第1領域における前記誘電体セラミック層の誘電率の0.63倍以下であり、前記第2領域における前記誘電体セラミック層の体積に対する前記内部電極の体積の比率は、前記第1領域における前記誘電体セラミック層の体積に対する前記内部電極の体積の比率の1.2倍以上である、請求項1に記載の積層セラミックコンデンサ。

【請求項3】

前記第2領域における前記誘電体セラミック層の誘電率は、前記第1領域における前記誘電体セラミック層の誘電率の0.02〜0.43倍であり、前記第2領域における前記誘電体セラミック層の体積に対する前記内部電極の体積の比率は、前記第1領域における前記誘電体セラミック層の体積に対する前記内部電極の体積の比率の1.5倍以上であり、前記第2領域の厚みは、前記第1領域の厚みの0.20〜0.96倍である、請求項2に記載の積層セラミックコンデンサ。

【請求項4】

前記活性部は2つの前記第2領域を含み、前記2つの第2領域は、前記第1領域を積層方向に挟むように分布する、請求項1ないし3のいずれかに記載の積層セラミックコンデンサ。

【請求項5】

前記活性部はさらに第3領域を含み、前記第3領域は前記第1領域より前記第1の主面側に位置され、前記第3領域における前記誘電体セラミック層の誘電率は、前記第1領域における前記誘電体セラミック層の誘電率より高い、請求項1ないし3のいずれかに記載の積層セラミックコンデンサ。

【請求項6】

前記活性部はさらに第3領域を含み、前記第3領域は前記第1領域より前記第1の主面側に位置され、前記第3領域における前記誘電体セラミック層の体積に対する前記内部電極の体積の比率は、前記第1領域における前記誘電体セラミック層の体積に対する前記内部電極の体積の比率より高い、請求項1ないし3のいずれかに記載の積層セラミックコンデンサ。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図2】

【図3】

【図4】

【図5】

【図6】

【公開番号】特開2013−102241(P2013−102241A)

【公開日】平成25年5月23日(2013.5.23)

【国際特許分類】

【出願番号】特願2013−41806(P2013−41806)

【出願日】平成25年3月4日(2013.3.4)

【分割の表示】特願2007−239026(P2007−239026)の分割

【原出願日】平成19年9月14日(2007.9.14)

【出願人】(000006231)株式会社村田製作所 (3,635)

【Fターム(参考)】

【公開日】平成25年5月23日(2013.5.23)

【国際特許分類】

【出願日】平成25年3月4日(2013.3.4)

【分割の表示】特願2007−239026(P2007−239026)の分割

【原出願日】平成19年9月14日(2007.9.14)

【出願人】(000006231)株式会社村田製作所 (3,635)

【Fターム(参考)】

[ Back to top ]