積層セラミック電子部品の製造方法

【課題】生のセラミック素体に導電性ペーストを塗布した際に生じる膨潤、歪みを抑制し得る、積層セラミック電子部品の製造方法を提供する。

【解決手段】第2のセラミックグリーンシート20bに含まれる有機バインダーの重合度をAとし、第2のセラミックグリーンシート20bに含まれる可塑剤の体積含有率をBとしたときに、180.56≦A/Bとなる。

【解決手段】第2のセラミックグリーンシート20bに含まれる有機バインダーの重合度をAとし、第2のセラミックグリーンシート20bに含まれる可塑剤の体積含有率をBとしたときに、180.56≦A/Bとなる。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、積層セラミック電子部品の製造方法に関する。

【背景技術】

【0002】

近年、携帯電話、携帯音楽プレイヤーなどの電子機器の小型化、薄型化に伴い、電子機器に搭載される積層セラミックスの小型化、薄型化が進んでいる。このような積層セラミック電子部品の製造工程においては、生のセラミック素体の表面に導電性ペーストを塗布、焼き付けすることにより、外部電極を形成することが行われている(特許文献1を参照)。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開2010−141300号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

ところが、生のセラミック素体の表面に導電性ペーストを塗布した際、導電性ペーストに含まれる溶剤などが生のセラミック素体内に染み込み、生のセラミック素体が膨潤したり、歪んだりするという問題がある。

【0005】

本発明は、生のセラミック素体に導電性ペーストを塗布した際に生じる膨潤、歪みを抑制し得る、積層セラミック電子部品の製造方法を提供することを主な目的とする。

【課題を解決するための手段】

【0006】

本発明に係る積層セラミック電子部品の製造方法では、内部電極を構成するための導電層が表面上に形成された第1のセラミックグリーンシートと、内部電極を構成するための導電層が表面上に形成されていない第2のセラミックグリーンシートとを用意する。少なくとも一枚の第2のセラミックグリーンシートと、複数の第1のセラミックグリーンシートと、少なくとも一枚の第2のセラミックグリーンシートとをこの順番で積層することにより、主面と、導電層が露出した端面とを有する生のセラミック素体を作製する。少なくとも主面の上に、導電性ペーストを塗布し、外部電極を形成するための導電性ペースト層を形成する。導電性ペースト層が形成された生のセラミック素体を焼成することにより積層セラミック電子部品を作製する。第1及び第2のセラミックグリーンシートのそれぞれは、有機バインダー及び可塑剤を含む。有機バインダーの重合度をAとし、可塑剤の体積含有率をBとする。主面を構成している第2のセラミックグリーンシートにおいて、180.56≦A/Bとなる。生のセラミック素体を作製する工程において、複数の第2のセラミックグリーンシートと、複数の第1のセラミックグリーンシートと、複数の第2のセラミックグリーンシートとをこの順番で積層し、複数の第2のセラミックグリーンシートのそれぞれにおいて、180.56≦A/Bとなることが好ましい。

【0007】

本発明に係る積層セラミック電子部品の製造方法のある特定の局面では、第1のセラミックグリーンシートに含まれる有機バインダーの重合度をA1、第1のセラミックグリーンシートに含まれる可塑剤の体積含有率をB1とする。主面を構成している第2のセラミックグリーンシートにおいて、2.74≦((A/B)/(A1/B1))≦5.00となる。生のセラミック素体を作製する工程において、複数の第2のセラミックグリーンシートと、複数の第1のセラミックグリーンシートと、複数の第2のセラミックグリーンシートとをこの順番で積層し、複数の第2のセラミックグリーンシートのそれぞれにおいて、2.74≦((A/B)/(A1/B1))≦5.00となることが好ましい。

【0008】

本発明に係る積層セラミック電子部品の製造方法の別の特定の局面では、第1及び第2のセラミックグリーンシートに含まれる有機バインダーは、それぞれポリビニルブチラール樹脂、ポリビニルホルマール樹脂、ポリビニルヘキサナール樹脂からなる群から選ばれる少なくとも一種からなる。

【0009】

本発明に係る積層セラミック電子部品の製造方法の他の特定の局面では、第1及び第2のセラミックグリーンシートに含まれる可塑剤は、フタル酸エステルである。

【発明の効果】

【0010】

本発明によれば、生のセラミック素体に導電性ペーストを塗布した際に生じる膨潤、歪みを抑制し得る、積層セラミック電子部品の製造方法を提供することができる。

【図面の簡単な説明】

【0011】

【図1】本発明の一実施形態における、表面上に導電層が形成されたセラミックグリーンシートの略図的平面図である。

【図2】本発明の一実施形態における、表面上に導電層が形成されていないセラミックグリーンシートの略図的平面図である。

【図3】本発明の一実施形態におけるマザー積層体の略図的平面図である。

【図4】本発明の一実施形態におけるマザー積層体の略図的分解側面図である。

【図5】本発明の一実施形態における生のセラミック素体の略図的断面図である。

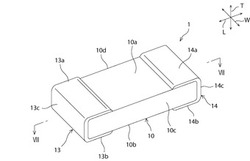

【図6】本発明の一実施形態におけるセラミック電子部品の略図的斜視図である。

【図7】本発明の一実施形態におけるセラミック電子部品の略図的側面図である。

【図8】図6の線VIII−VIIIにおける略図的断面図である。

【図9】図8の線IX−IXにおける略図的断面図である。

【発明を実施するための形態】

【0012】

以下、本発明を実施した好ましい形態の一例について説明する。但し、下記の実施形態は、単なる例示である。本発明は、下記の実施形態に何ら限定されない。

【0013】

また、実施形態等において参照する各図面において、実質的に同一の機能を有する部材は同一の符号で参照することとする。また、実施形態等において参照する図面は、模式的に記載されたものであり、図面に描画された物体の寸法の比率などは、現実の物体の寸法の比率などとは異なる場合がある。図面相互間においても、物体の寸法比率等が異なる場合がある。具体的な物体の寸法比率等は、以下の説明を参酌して判断されるべきである。

【0014】

図1は、本実施形態における、表面上に導電層が形成されたセラミックグリーンシートの略図的平面図である。図2は、本実施形態における、表面上に導電層が形成されていないセラミックグリーンシートの略図的平面図である。図3は、本実施形態におけるマザー積層体の略図的平面図である。図4は、本実施形態におけるマザー積層体の略図的分解側面図である。図5は、本実施形態における生のセラミック素体の略図的断面図である。図6は、本実施形態におけるセラミック電子部品の略図的斜視図である。以下、図1〜5を参照しながら、図6に示すセラミック電子部品1の製造方法の一例について説明する。

【0015】

まず、図1及び図2に示す第1及び第2のセラミックグリーンシート20a,20bを用意する。第1及び第2のセラミックグリーンシート20a,20bは、例えばセラミックスラリーをシート状に成形し、乾燥させることにより作製することができる。

【0016】

第1及び第2のセラミックグリーンシート20a,20bに用いられるセラミック粉末の種類は、製造しようとする積層セラミック電子部品1の特性に応じて適宜選択することができる。

【0017】

例えば、積層セラミック電子部品1が、コンデンサである場合は、セラミック粉末として、誘電体セラミックスを用いることができる。誘電体セラミックスの具体例としては、例えば、BaTiO3、CaTiO3、SrTiO3、CaZrO3などが挙げられる。

【0018】

例えば、積層セラミック電子部品1が、圧電部品である場合は、セラミック粉末として、圧電セラミックスを用いることができる。圧電セラミックスの具体例としては、例えば、PZT(チタン酸ジルコン酸鉛)系セラミックスなどが挙げられる。

【0019】

例えば、積層セラミック電子部品1が、サーミスタである場合は、セラミック粉末として、半導体セラミックスを用いることができる。半導体セラミックスの具体例としては、例えば、スピネル系セラミックスなどが挙げられる。

【0020】

例えば、積層セラミック電子部品1が、インダクタである場合は、セラミック粉末として、磁性体セラミックスを用いることができる。磁性体セラミックスの具体例としては、例えば、フェライトセラミックスなどが挙げられる。

【0021】

第1のセラミックグリーンシート20aに用いられるセラミック粉末は、上記のようなセラミック粉末以外に、第1の有機バインダー、第1の可塑剤などを含む。また、第2のセラミックグリーンシート20bに用いられるセラミック粉末は、上記のようなセラミック粉末以外に、第2の有機バインダー、第2の可塑剤などを含む。

【0022】

第1及び第2の有機バインダーの具体例としては、例えばポリビニルブチラール樹脂、ポリビニルホルマール樹脂、ポリビニルアセトアセタール樹脂、ポリビニルヘキサナール樹脂などを用いることができる。第1及び第2の有機バインダーとしては、これらの中でも、ポリビニルブチラール樹脂が好ましく用いられる。第1及び第2の有機バインダーとしては、1種類のみの有機バインダーを用いてもよいし、2種類以上の有機バインダーを混合して用いてもよい。また、第1及び第2の有機バインダーは、それぞれ同じであってもよいし、異なってもよい。

【0023】

第1及び第2の有機バインダーとしては、重合度が850〜1700程度のものを用いることが好ましく、850〜1300程度のものを用いることがより好ましい。

【0024】

第1及び第2の可塑剤としては、例えばフタル酸エステルなどを用いることができる。フタル酸エステルの具体例としては、例えばフタル酸ジオクチル、フタル酸ジメチル、フタル酸ジエチル、フタル酸ジブチル、フタル酸ビス(2−エチルヘキシル)、フタル酸ジノルマルオクチル、フタル酸ジイソノニル、フタル酸ジノニル、フタル酸ジイソデシル、フタル酸ブチルベンジルなどが挙げられる。第1の可塑剤としては、これらの中でも、フタル酸ジオクチルが好ましく用いられる。第1及び第2の可塑剤としては、1種類のみの可塑剤を用いてもよいし、2種類以上の可塑剤を混合して用いてもよい。また、第1及び第2の可塑剤は、それぞれ同じであってもよいし、異なってもよい。

【0025】

第1及び第2のセラミックグリーンシート20a,20bの厚みは、それぞれ0.5μm〜10μm程度(焼成後)とすればよい。第1及び第2のセラミックグリーンシート20a,20bそれぞれの厚みは、同じであってもよいし、異なってもよい。

【0026】

第2の有機バインダーの重合度をAとし、第2の可塑剤の体積含有率をBとしたときに、180.56≦A/Bとなる関係を充足するようにして、第2の有機バインダーと第2の可塑剤とを用いる。

【0027】

また、第1の有機バインダーの重合度をA1、第1の可塑剤の体積含有率をB1としたときに、2.74≦((A/B)/(A1/B1))≦5.00となる関係を充足するようにして、第1及び第2の有機バインダーと第1及び第2の可塑剤とを用いることが好ましい。

【0028】

図1に示すように、セラミックグリーンシート20aの上には、第1の導電性ペーストを塗布することにより、導電層21を形成する。具体的には、第1のセラミックグリーンシート20aの表面上に、内部電極を構成するための矩形状の複数の導電層21を、x方向と、x方向に対して垂直なy方向に沿って相互に間隔をおいてマトリクス状に形成する。これにより、表面上に、内部電極を構成するための矩形状の複数の導電層21が、x方向及びy方向に沿って相互に間隔をおいてマトリクス状に配された第1のセラミックグリーンシート20aを用意する。

【0029】

次に、図4に示されるように、表面上に導電層21が形成されていないセラミックグリーンシート20bを複数枚積層する。その後、図4に示されるように、表面上に複数の導電層21が形成されたセラミックグリーンシート20aを複数枚積層する。その後、図4に示されるように、表面上に導電層21が形成されていないセラミックグリーンシート20bをさらに複数枚積層する。これにより、内部に導電層21を有するマザー積層体22を作製する。

【0030】

なお、必要に応じてマザー積層体22に、プレスを施してもよい。

【0031】

次に、図3に示すように、マザー積層体22の上に、第1及び第2の外部電極13,14の第1及び第2の部分13a,13b,14a,14bを構成する部分に対応した形状の導電性ペースト層27を、スクリーン印刷法などの適宜の印刷法により形成する。

【0032】

次に、マザー積層体22をx方向及びy方向に沿って切断することにより、マザー積層体22から、生のセラミック素体23を作製する。具体的には、マザー積層体22を、各導電層21のy方向(第2の方向)における中央において、x方向(第1の方向)に沿って延びる複数のカットラインL1(図3を参照)に沿って切断する。それと共に、各導電層21のx方向における中央においてy方向に沿って延びるカットラインL2に沿って切断する。これにより、マザー積層体22を複数の生のセラミック素体23に分断する。

【0033】

なお、マザー積層体22の切断は、例えば、切断刃を押しつける押切り、ダイシング、レーザー切断などの方法により行うことができる。

【0034】

図5に示されるように、生のセラミック素体23は、直方体状のチップ本体24を有する。一対の主面24a、24bと、一対の側面(図示せず)と、一対の端面24e、24fとを有する。主面24a、24bは、長さ方向L及び幅方向Wに沿って延びている。側面は、長さ方向L及び厚み方向Tに沿って延びている。端面24e、24fは、幅方向W及び厚み方向Tに沿って延びている。

【0035】

チップ本体24の内部には、導電層21から形成された矩形状の複数の第1及び第2の内部電極25,26が配されている。複数の第1の内部電極25と、複数の第2の内部電極26とは、厚み方向Tに沿って、相互に間隔をおいて交互に配されている。厚み方向Tにおいて隣接する第1の内部電極25と第2の内部電極26とは、セラミック層29を介して対向している。

【0036】

第1及び第2の内部電極25,26は、長さ方向L及び幅方向Wに沿って配されている。第1の内部電極25は、端面24eに露出している。第1の内部電極25は、端面24fには露出していない。第2の内部電極26は、端面24fに露出している。第2の内部電極26は、端面24eには露出していない。即ち、端面24eには、第1の内部電極25が露出している一方、第2の内部電極26は露出していない。端面24fには、第2の内部電極26が露出している一方、第1の内部電極25は露出していない。

【0037】

次に、生のセラミック素体23の端面24e,24fに、ディップ法などの適宜の方法により導電性ペーストを塗布し、第1及び第2の外部電極13,14の第3の部分13c,14cに対応した形状の導電性ペースト層を形成する。この導電性ペースト層と、上記の導電性ペースト層27により、端面24e,24fの上から主面24a,24bの上にまで至る外部電極13,14を形成するための導電性ペースト層が形成される。

【0038】

導電性ペーストは、適宜の導電材料、溶剤などからなる。導電材料としては、例えばNi,Cu,Ag,Pd及びAuからなる群から選ばれた金属またはNi,Cu,Ag,Pd及びAuからなる群から選ばれた一種以上の金属を含む合金(例えば、Ag−Pd合金など)などを用いることができる。また、溶剤としては、例えば、テルピネオール、ジヒドロテルピネオール、ジヒドロターピニルアセテートなどを用いることができる。

【0039】

なお、生のセラミック素体23に、バレル研磨等を適宜施し、稜線部や角部に丸みをつけておくことが好ましい。

【0040】

次に、生のセラミック素体23を焼成することにより、セラミック素体10を得る。焼成温度は、例えば、900℃〜1300℃程度とすることができる。この焼成工程において、第1及び第2の外部電極13,14と第1及び第2の内部電極25,26が同時焼成される。

【0041】

(積層セラミック電子部品1の構成)

図6は、本実施形態において製造された積層セラミック電子部品の略図的斜視図である。図7は、本実施形態におけるセラミック電子部品の略図的側面図である。図8は、図6の線VIII−VIIIにおける略図的断面図である。図9は、図8の線IX−IXにおける略図的断面図である。

【0042】

図6〜9に示されるように、積層セラミック電子部品1は、直方体状のセラミック素体10を備えている。セラミック素体10は、長さ方向L及び幅方向Wに沿って延びる第1及び第2の主面10a、10bと、厚み方向T及び長さ方向Lに沿って延びる第1及び第2の側面10c、10dと、厚み方向T及び幅方向Wに沿って延びる第1及び第2の端面10e、10fを有する。

【0043】

なお、本発明において、「直方体状」には、角部や稜線部丸みがつけられている直方体が含まれるものとする。すなわち、「直方体状」の部材とは、第1及び第2の主面、第1及び第2の側面並びに第1及び第2の端面とを有する部材全般を意味する。また、主面、側面、端面の一部または全部に凹凸などが形成されていてもよい。

【0044】

セラミック素体10の寸法は、特に限定されない。セラミック素体10の厚さ寸法をT、長さ寸法L、幅寸法をWとしたとき、T≦W<L、1/5W≦T≦1/2W、T≦0.3mmを満たす薄型であることが好ましい。具体的には、0.1mm≦T≦0.3mm、0.4mm≦L≦1mm、0.2mm≦W≦0.5mmであることが好ましい。

【0045】

図8に示されるように、セラミック素体10の内部には、略矩形状の複数の第1及び第2の内部電極11,12が厚み方向Tに沿って等間隔に交互に配置されている。第1及び第2の内部電極11,12のそれぞれは、第1及び第2の主面10a、10bと平行である。第1及び第2の内部電極11,12は、厚み方向Tにおいて、セラミック層10gを介して、互いに対向している。

【0046】

図6〜9に示されるように、積層セラミック電子部品1は、第1及び第2の外部電極13,14を備えている。図8に示されるように、第1の外部電極13は、第1の内部電極11に接続されている。一方、第2の外部電極14は、第2の内部電極12に接続されている。

【0047】

第1及び第2の外部電極13,14は、第1及び第2の主面10a,10b上の第1及び第2の部分13a,13b,14a、14bと、第1及び第2の端面10e,10f上の第3の部分13c,14cとによって構成されている。第1及び第2の外部電極13,14は、適宜の導電材料により構成することができる。また、第1及び第2の外部電極13,14は、複数の導電膜の積層体により構成されていてもよい。

【0048】

上述の通り、積層セラミック電子部品の製造工程において、生のセラミック素体の表面に導電性ペーストを塗布した際、導電性ペーストに含まれる溶剤などが生のセラミック素体に染み込み、生のセラミック素体が膨潤したり、歪んだりするという問題がある。

【0049】

これに対して、本実施形態に係る積層セラミック電子部品1の製造方法においては、図3〜図5に示されるように、生のセラミック素体23の主面24a,24bの導電性ペーストが塗布される部分には、第2のセラミックグリーンシート20bが配される。そして、本実施形態においては、第2のセラミックグリーンシート20bに含まれる第2の有機バインダーの重合度をAとし、第2のセラミックグリーンシートに含まれる第2の可塑剤の体積含有率をBとしたときに、180.56≦A/Bの関係を充足するようにして、第2の有機バインダーと第2の可塑剤とを用いる。これにより、生のセラミック素体23の表面に導電性ペーストを塗布した際、第2のセラミックグリーンシート20bの結合が強固になり第2のセラミックグリーンシート20bが硬く形成されることになるため導電性ペーストに含まれる溶剤などが生のセラミック素体23に染み込むことが抑制される。よって、本実施形態に係る積層セラミック電子部品1の製造方法によれば、生のセラミック素体23が膨潤したり、歪むことを効果的に抑制することができる。

【0050】

また、生のセラミック素体の膨潤などに起因して、積層セラミック電子部品の内部には、剥がれ(デラミネーション)などに因る空隙が発生する場合がある。薄型の積層セラミック電子部品の場合、内部の空隙が積層セラミック電子部品の特性に与える影響は特に大きい。

【0051】

本実施形態に係る積層セラミック電子部品1の製造方法において、第1のセラミックグリーンシートに含まれる第1の有機バインダーの重合度をA1、第1のセラミックグリーンシートに含まれる第1の可塑剤の体積含有率をB1とし、第2のセラミックグリーンシートに含まれる第2の有機バインダーの重合度をAとし、第2のセラミックグリーンシートに含まれる第2の可塑剤の体積含有率をBとしたときに、さらに2.74≦((A/B)/(A1/B1))≦5.00となる関係を充足する場合、生のセラミック素体23が膨潤や歪みを効果的に抑制することができることに加えて、積層セラミック電子部品1としたときに、内部に空隙が発生することを効果的に抑制することができる。これは、第1のセラミックグリーンシート及び第2のセラミックグリーンシートが、それぞれ適切な硬さに調節されているため、第1のセラミックグリーンシート及び第2のセラミックグリーンシートにおいて収縮差が抑えられているためと考えられる。

【0052】

なお、本実施形態においては、複数の第2のセラミックグリーンシートのそれぞれにおいて、180.56≦A/Bが満たされる例について説明した。但し、本発明は、この構成に限定されない。例えば、主面を構成する最外層に位置する第2のセラミックグリーンシートのみにおいて180.56≦A/Bが満たされていてもよい。この場合であっても同様の効果が得られる。

【0053】

同様に、複数の第2のセラミックグリーンシートのそれぞれにおいて、2.74≦((A/B)/(A1/B1))≦5.00が満たされることがより好ましいが、主面を構成する最外層に位置する第2のセラミックグリーンシートのみにおいて2.74≦((A/B)/(A1/B1))≦5.00が満たされていてもよい。

【0054】

第2のセラミックグリーンシートの上には、内部電極を構成しない導電層が設けられていてもよい。例えば、第2のセラミックグリーンシートの上に、ダミー電極を構成するための導電層が設けられていてもよい。ここで、内部電極とは、例えばコンデンサの場合では容量を形成する電極であり、一般的には、電子部品の機能を発現するための電極である。

【0055】

以下、本発明について、具体的な実施例に基づいて、さらに詳細に説明するが、本発明は以下の実施例に何ら限定されるものではなく、その要旨を変更しない範囲において適宜変更して実施することが可能である。

【0056】

(実施例1)

上記実施形態に係る積層セラミック電子部品1のマザー積層体22を、上記実施形態において説明した方法で、以下の条件で作製した。

【0057】

(1)第1のセラミックグリーンシート20a

セラミック粉末: BaTiO3 79.3体積%

第1の有機バインダー:ポリビニルブチラール樹脂(重合度850) 10.2体積%

第1の可塑剤:フタル酸ジオクチル 17.0体積%

導電層21の組成:導電材料Ni、溶剤テルピネオール

第1のセラミックグリーンシート20aのサイズ:200mm×200mm 第1のセラミックグリーンシート20aの積層枚数7枚

【0058】

(2)第2のセラミックグリーンシート20b

セラミック粉末: BaTiO3 79.3体積%

第2の有機バインダー:ポリビニルブチラール樹脂(重合度1300) 22.0体積%

第2の可塑剤:フタル酸ジオクチル 5.2体積%

第2のセラミックグリーンシート20bのサイズ:200mm×200mm 第2のセラミックグリーンシート20bの積層枚数7枚

【0059】

(3)導電性ペースト層27の組成:導電材料Ni、溶剤ターピネオール

【0060】

なお、下記の表1に示すように、実施例及び比較例の各セラミックグリーンシート中において、有機バインダーと可塑剤の合計量が、27.2体積%となるように調整した。

【0061】

[膨潤・歪みの確認]

焼成後のセラミック素体23のサイズが1.0mm×0.5mm×0.15mmとなるようにして、実施例1で得られたマザー積層体22をカットした。生のセラミック素体23の膨潤、歪みの有無をニコンインスペック社製のNEXIV VMR−6555を用いて確認した。具体的には、マザー積層体22をカットした後、個々の生のセラミック素体23に分割する前に、マザー積層体22を平面視して100の領域に均等に区画し、各領域内の複数ある生のセラミック素体23のうち、各領域の中央に位置する1つの生のセラミック素体23それぞれについて、導電性ペースト層27が塗布された部分の幅方向Xの膨潤、歪みの有無を確認した。生のセラミック素体23の寸法規格として、導電性ペースト層27部分の幅方向長さにおいて一定の長さを満たさないものを膨潤、歪みが発生していると判定した。100領域中、膨潤、歪みを有する生のセラミック素体が含まれていた領域の数を表1に示す。表1に示すように、実施例1で得られた生のセラミック素体23には、膨潤、歪みはほとんど発生しなかった。

【0062】

(実施例2〜8及び比較例1,2)

第1及び第2の有機バインダーの種類(重合度)及び使用量と第1及び第2の可塑剤の使用量を表1に記載のものとし、実施例1と同様にして、実施例2〜8及び比較例1,2のマザー積層体22をそれぞれ作製した。次に、実施例2〜8及び比較例1,2で得られたマザー積層体22を用いて、実施例1と同様にして膨潤・歪みを確認した。結果を表1に示す。表1に示すように、実施例2〜8で得られた生のセラミック素体23には、膨潤・歪みはほとんど発生しなかった。一方、比較例1,2で得られた生のセラミック素体には多くの膨潤・歪みが発生した。

【0063】

[内部空隙の確認]

次に、実施例1〜8及び比較例1,2のマザー積層体22から得られた全ての生のセラミック素体23を不活性ガス雰囲気下、1200℃で2時間焼成した。得られたセラミック積層体の全てについて、超音波顕微鏡(C−SAM)を用いて内部空隙の有無を確認した。その結果、実施例2〜5で得られたセラミック積層体には、内部空隙が発生しているものは1つもなかった。

【0064】

【表1】

【符号の説明】

【0065】

1…積層セラミック電子部品

10…セラミック素体

10a、10b…主面

10c、10d…側面

10e、10f…端面

10g…セラミック層

11…第1の内部電極

12…第2の内部電極

13…第1の外部電極

14…第2の外部電極

13a,14a…第1の部分

13b,14b…第2の部分

13c,14c…第3の部分

20a…第1のセラミックグリーンシート

20b…第2のセラミックグリーンシート

21…導電層

22…マザー積層体

23…生のセラミック素体

24…チップ本体

24a、24b…主面

24e、24f…端面

25…第1の内部電極

26…第2の内部電極

27…導電性ペースト層

29…セラミック層

L1,L2…カットライン

【技術分野】

【0001】

本発明は、積層セラミック電子部品の製造方法に関する。

【背景技術】

【0002】

近年、携帯電話、携帯音楽プレイヤーなどの電子機器の小型化、薄型化に伴い、電子機器に搭載される積層セラミックスの小型化、薄型化が進んでいる。このような積層セラミック電子部品の製造工程においては、生のセラミック素体の表面に導電性ペーストを塗布、焼き付けすることにより、外部電極を形成することが行われている(特許文献1を参照)。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開2010−141300号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

ところが、生のセラミック素体の表面に導電性ペーストを塗布した際、導電性ペーストに含まれる溶剤などが生のセラミック素体内に染み込み、生のセラミック素体が膨潤したり、歪んだりするという問題がある。

【0005】

本発明は、生のセラミック素体に導電性ペーストを塗布した際に生じる膨潤、歪みを抑制し得る、積層セラミック電子部品の製造方法を提供することを主な目的とする。

【課題を解決するための手段】

【0006】

本発明に係る積層セラミック電子部品の製造方法では、内部電極を構成するための導電層が表面上に形成された第1のセラミックグリーンシートと、内部電極を構成するための導電層が表面上に形成されていない第2のセラミックグリーンシートとを用意する。少なくとも一枚の第2のセラミックグリーンシートと、複数の第1のセラミックグリーンシートと、少なくとも一枚の第2のセラミックグリーンシートとをこの順番で積層することにより、主面と、導電層が露出した端面とを有する生のセラミック素体を作製する。少なくとも主面の上に、導電性ペーストを塗布し、外部電極を形成するための導電性ペースト層を形成する。導電性ペースト層が形成された生のセラミック素体を焼成することにより積層セラミック電子部品を作製する。第1及び第2のセラミックグリーンシートのそれぞれは、有機バインダー及び可塑剤を含む。有機バインダーの重合度をAとし、可塑剤の体積含有率をBとする。主面を構成している第2のセラミックグリーンシートにおいて、180.56≦A/Bとなる。生のセラミック素体を作製する工程において、複数の第2のセラミックグリーンシートと、複数の第1のセラミックグリーンシートと、複数の第2のセラミックグリーンシートとをこの順番で積層し、複数の第2のセラミックグリーンシートのそれぞれにおいて、180.56≦A/Bとなることが好ましい。

【0007】

本発明に係る積層セラミック電子部品の製造方法のある特定の局面では、第1のセラミックグリーンシートに含まれる有機バインダーの重合度をA1、第1のセラミックグリーンシートに含まれる可塑剤の体積含有率をB1とする。主面を構成している第2のセラミックグリーンシートにおいて、2.74≦((A/B)/(A1/B1))≦5.00となる。生のセラミック素体を作製する工程において、複数の第2のセラミックグリーンシートと、複数の第1のセラミックグリーンシートと、複数の第2のセラミックグリーンシートとをこの順番で積層し、複数の第2のセラミックグリーンシートのそれぞれにおいて、2.74≦((A/B)/(A1/B1))≦5.00となることが好ましい。

【0008】

本発明に係る積層セラミック電子部品の製造方法の別の特定の局面では、第1及び第2のセラミックグリーンシートに含まれる有機バインダーは、それぞれポリビニルブチラール樹脂、ポリビニルホルマール樹脂、ポリビニルヘキサナール樹脂からなる群から選ばれる少なくとも一種からなる。

【0009】

本発明に係る積層セラミック電子部品の製造方法の他の特定の局面では、第1及び第2のセラミックグリーンシートに含まれる可塑剤は、フタル酸エステルである。

【発明の効果】

【0010】

本発明によれば、生のセラミック素体に導電性ペーストを塗布した際に生じる膨潤、歪みを抑制し得る、積層セラミック電子部品の製造方法を提供することができる。

【図面の簡単な説明】

【0011】

【図1】本発明の一実施形態における、表面上に導電層が形成されたセラミックグリーンシートの略図的平面図である。

【図2】本発明の一実施形態における、表面上に導電層が形成されていないセラミックグリーンシートの略図的平面図である。

【図3】本発明の一実施形態におけるマザー積層体の略図的平面図である。

【図4】本発明の一実施形態におけるマザー積層体の略図的分解側面図である。

【図5】本発明の一実施形態における生のセラミック素体の略図的断面図である。

【図6】本発明の一実施形態におけるセラミック電子部品の略図的斜視図である。

【図7】本発明の一実施形態におけるセラミック電子部品の略図的側面図である。

【図8】図6の線VIII−VIIIにおける略図的断面図である。

【図9】図8の線IX−IXにおける略図的断面図である。

【発明を実施するための形態】

【0012】

以下、本発明を実施した好ましい形態の一例について説明する。但し、下記の実施形態は、単なる例示である。本発明は、下記の実施形態に何ら限定されない。

【0013】

また、実施形態等において参照する各図面において、実質的に同一の機能を有する部材は同一の符号で参照することとする。また、実施形態等において参照する図面は、模式的に記載されたものであり、図面に描画された物体の寸法の比率などは、現実の物体の寸法の比率などとは異なる場合がある。図面相互間においても、物体の寸法比率等が異なる場合がある。具体的な物体の寸法比率等は、以下の説明を参酌して判断されるべきである。

【0014】

図1は、本実施形態における、表面上に導電層が形成されたセラミックグリーンシートの略図的平面図である。図2は、本実施形態における、表面上に導電層が形成されていないセラミックグリーンシートの略図的平面図である。図3は、本実施形態におけるマザー積層体の略図的平面図である。図4は、本実施形態におけるマザー積層体の略図的分解側面図である。図5は、本実施形態における生のセラミック素体の略図的断面図である。図6は、本実施形態におけるセラミック電子部品の略図的斜視図である。以下、図1〜5を参照しながら、図6に示すセラミック電子部品1の製造方法の一例について説明する。

【0015】

まず、図1及び図2に示す第1及び第2のセラミックグリーンシート20a,20bを用意する。第1及び第2のセラミックグリーンシート20a,20bは、例えばセラミックスラリーをシート状に成形し、乾燥させることにより作製することができる。

【0016】

第1及び第2のセラミックグリーンシート20a,20bに用いられるセラミック粉末の種類は、製造しようとする積層セラミック電子部品1の特性に応じて適宜選択することができる。

【0017】

例えば、積層セラミック電子部品1が、コンデンサである場合は、セラミック粉末として、誘電体セラミックスを用いることができる。誘電体セラミックスの具体例としては、例えば、BaTiO3、CaTiO3、SrTiO3、CaZrO3などが挙げられる。

【0018】

例えば、積層セラミック電子部品1が、圧電部品である場合は、セラミック粉末として、圧電セラミックスを用いることができる。圧電セラミックスの具体例としては、例えば、PZT(チタン酸ジルコン酸鉛)系セラミックスなどが挙げられる。

【0019】

例えば、積層セラミック電子部品1が、サーミスタである場合は、セラミック粉末として、半導体セラミックスを用いることができる。半導体セラミックスの具体例としては、例えば、スピネル系セラミックスなどが挙げられる。

【0020】

例えば、積層セラミック電子部品1が、インダクタである場合は、セラミック粉末として、磁性体セラミックスを用いることができる。磁性体セラミックスの具体例としては、例えば、フェライトセラミックスなどが挙げられる。

【0021】

第1のセラミックグリーンシート20aに用いられるセラミック粉末は、上記のようなセラミック粉末以外に、第1の有機バインダー、第1の可塑剤などを含む。また、第2のセラミックグリーンシート20bに用いられるセラミック粉末は、上記のようなセラミック粉末以外に、第2の有機バインダー、第2の可塑剤などを含む。

【0022】

第1及び第2の有機バインダーの具体例としては、例えばポリビニルブチラール樹脂、ポリビニルホルマール樹脂、ポリビニルアセトアセタール樹脂、ポリビニルヘキサナール樹脂などを用いることができる。第1及び第2の有機バインダーとしては、これらの中でも、ポリビニルブチラール樹脂が好ましく用いられる。第1及び第2の有機バインダーとしては、1種類のみの有機バインダーを用いてもよいし、2種類以上の有機バインダーを混合して用いてもよい。また、第1及び第2の有機バインダーは、それぞれ同じであってもよいし、異なってもよい。

【0023】

第1及び第2の有機バインダーとしては、重合度が850〜1700程度のものを用いることが好ましく、850〜1300程度のものを用いることがより好ましい。

【0024】

第1及び第2の可塑剤としては、例えばフタル酸エステルなどを用いることができる。フタル酸エステルの具体例としては、例えばフタル酸ジオクチル、フタル酸ジメチル、フタル酸ジエチル、フタル酸ジブチル、フタル酸ビス(2−エチルヘキシル)、フタル酸ジノルマルオクチル、フタル酸ジイソノニル、フタル酸ジノニル、フタル酸ジイソデシル、フタル酸ブチルベンジルなどが挙げられる。第1の可塑剤としては、これらの中でも、フタル酸ジオクチルが好ましく用いられる。第1及び第2の可塑剤としては、1種類のみの可塑剤を用いてもよいし、2種類以上の可塑剤を混合して用いてもよい。また、第1及び第2の可塑剤は、それぞれ同じであってもよいし、異なってもよい。

【0025】

第1及び第2のセラミックグリーンシート20a,20bの厚みは、それぞれ0.5μm〜10μm程度(焼成後)とすればよい。第1及び第2のセラミックグリーンシート20a,20bそれぞれの厚みは、同じであってもよいし、異なってもよい。

【0026】

第2の有機バインダーの重合度をAとし、第2の可塑剤の体積含有率をBとしたときに、180.56≦A/Bとなる関係を充足するようにして、第2の有機バインダーと第2の可塑剤とを用いる。

【0027】

また、第1の有機バインダーの重合度をA1、第1の可塑剤の体積含有率をB1としたときに、2.74≦((A/B)/(A1/B1))≦5.00となる関係を充足するようにして、第1及び第2の有機バインダーと第1及び第2の可塑剤とを用いることが好ましい。

【0028】

図1に示すように、セラミックグリーンシート20aの上には、第1の導電性ペーストを塗布することにより、導電層21を形成する。具体的には、第1のセラミックグリーンシート20aの表面上に、内部電極を構成するための矩形状の複数の導電層21を、x方向と、x方向に対して垂直なy方向に沿って相互に間隔をおいてマトリクス状に形成する。これにより、表面上に、内部電極を構成するための矩形状の複数の導電層21が、x方向及びy方向に沿って相互に間隔をおいてマトリクス状に配された第1のセラミックグリーンシート20aを用意する。

【0029】

次に、図4に示されるように、表面上に導電層21が形成されていないセラミックグリーンシート20bを複数枚積層する。その後、図4に示されるように、表面上に複数の導電層21が形成されたセラミックグリーンシート20aを複数枚積層する。その後、図4に示されるように、表面上に導電層21が形成されていないセラミックグリーンシート20bをさらに複数枚積層する。これにより、内部に導電層21を有するマザー積層体22を作製する。

【0030】

なお、必要に応じてマザー積層体22に、プレスを施してもよい。

【0031】

次に、図3に示すように、マザー積層体22の上に、第1及び第2の外部電極13,14の第1及び第2の部分13a,13b,14a,14bを構成する部分に対応した形状の導電性ペースト層27を、スクリーン印刷法などの適宜の印刷法により形成する。

【0032】

次に、マザー積層体22をx方向及びy方向に沿って切断することにより、マザー積層体22から、生のセラミック素体23を作製する。具体的には、マザー積層体22を、各導電層21のy方向(第2の方向)における中央において、x方向(第1の方向)に沿って延びる複数のカットラインL1(図3を参照)に沿って切断する。それと共に、各導電層21のx方向における中央においてy方向に沿って延びるカットラインL2に沿って切断する。これにより、マザー積層体22を複数の生のセラミック素体23に分断する。

【0033】

なお、マザー積層体22の切断は、例えば、切断刃を押しつける押切り、ダイシング、レーザー切断などの方法により行うことができる。

【0034】

図5に示されるように、生のセラミック素体23は、直方体状のチップ本体24を有する。一対の主面24a、24bと、一対の側面(図示せず)と、一対の端面24e、24fとを有する。主面24a、24bは、長さ方向L及び幅方向Wに沿って延びている。側面は、長さ方向L及び厚み方向Tに沿って延びている。端面24e、24fは、幅方向W及び厚み方向Tに沿って延びている。

【0035】

チップ本体24の内部には、導電層21から形成された矩形状の複数の第1及び第2の内部電極25,26が配されている。複数の第1の内部電極25と、複数の第2の内部電極26とは、厚み方向Tに沿って、相互に間隔をおいて交互に配されている。厚み方向Tにおいて隣接する第1の内部電極25と第2の内部電極26とは、セラミック層29を介して対向している。

【0036】

第1及び第2の内部電極25,26は、長さ方向L及び幅方向Wに沿って配されている。第1の内部電極25は、端面24eに露出している。第1の内部電極25は、端面24fには露出していない。第2の内部電極26は、端面24fに露出している。第2の内部電極26は、端面24eには露出していない。即ち、端面24eには、第1の内部電極25が露出している一方、第2の内部電極26は露出していない。端面24fには、第2の内部電極26が露出している一方、第1の内部電極25は露出していない。

【0037】

次に、生のセラミック素体23の端面24e,24fに、ディップ法などの適宜の方法により導電性ペーストを塗布し、第1及び第2の外部電極13,14の第3の部分13c,14cに対応した形状の導電性ペースト層を形成する。この導電性ペースト層と、上記の導電性ペースト層27により、端面24e,24fの上から主面24a,24bの上にまで至る外部電極13,14を形成するための導電性ペースト層が形成される。

【0038】

導電性ペーストは、適宜の導電材料、溶剤などからなる。導電材料としては、例えばNi,Cu,Ag,Pd及びAuからなる群から選ばれた金属またはNi,Cu,Ag,Pd及びAuからなる群から選ばれた一種以上の金属を含む合金(例えば、Ag−Pd合金など)などを用いることができる。また、溶剤としては、例えば、テルピネオール、ジヒドロテルピネオール、ジヒドロターピニルアセテートなどを用いることができる。

【0039】

なお、生のセラミック素体23に、バレル研磨等を適宜施し、稜線部や角部に丸みをつけておくことが好ましい。

【0040】

次に、生のセラミック素体23を焼成することにより、セラミック素体10を得る。焼成温度は、例えば、900℃〜1300℃程度とすることができる。この焼成工程において、第1及び第2の外部電極13,14と第1及び第2の内部電極25,26が同時焼成される。

【0041】

(積層セラミック電子部品1の構成)

図6は、本実施形態において製造された積層セラミック電子部品の略図的斜視図である。図7は、本実施形態におけるセラミック電子部品の略図的側面図である。図8は、図6の線VIII−VIIIにおける略図的断面図である。図9は、図8の線IX−IXにおける略図的断面図である。

【0042】

図6〜9に示されるように、積層セラミック電子部品1は、直方体状のセラミック素体10を備えている。セラミック素体10は、長さ方向L及び幅方向Wに沿って延びる第1及び第2の主面10a、10bと、厚み方向T及び長さ方向Lに沿って延びる第1及び第2の側面10c、10dと、厚み方向T及び幅方向Wに沿って延びる第1及び第2の端面10e、10fを有する。

【0043】

なお、本発明において、「直方体状」には、角部や稜線部丸みがつけられている直方体が含まれるものとする。すなわち、「直方体状」の部材とは、第1及び第2の主面、第1及び第2の側面並びに第1及び第2の端面とを有する部材全般を意味する。また、主面、側面、端面の一部または全部に凹凸などが形成されていてもよい。

【0044】

セラミック素体10の寸法は、特に限定されない。セラミック素体10の厚さ寸法をT、長さ寸法L、幅寸法をWとしたとき、T≦W<L、1/5W≦T≦1/2W、T≦0.3mmを満たす薄型であることが好ましい。具体的には、0.1mm≦T≦0.3mm、0.4mm≦L≦1mm、0.2mm≦W≦0.5mmであることが好ましい。

【0045】

図8に示されるように、セラミック素体10の内部には、略矩形状の複数の第1及び第2の内部電極11,12が厚み方向Tに沿って等間隔に交互に配置されている。第1及び第2の内部電極11,12のそれぞれは、第1及び第2の主面10a、10bと平行である。第1及び第2の内部電極11,12は、厚み方向Tにおいて、セラミック層10gを介して、互いに対向している。

【0046】

図6〜9に示されるように、積層セラミック電子部品1は、第1及び第2の外部電極13,14を備えている。図8に示されるように、第1の外部電極13は、第1の内部電極11に接続されている。一方、第2の外部電極14は、第2の内部電極12に接続されている。

【0047】

第1及び第2の外部電極13,14は、第1及び第2の主面10a,10b上の第1及び第2の部分13a,13b,14a、14bと、第1及び第2の端面10e,10f上の第3の部分13c,14cとによって構成されている。第1及び第2の外部電極13,14は、適宜の導電材料により構成することができる。また、第1及び第2の外部電極13,14は、複数の導電膜の積層体により構成されていてもよい。

【0048】

上述の通り、積層セラミック電子部品の製造工程において、生のセラミック素体の表面に導電性ペーストを塗布した際、導電性ペーストに含まれる溶剤などが生のセラミック素体に染み込み、生のセラミック素体が膨潤したり、歪んだりするという問題がある。

【0049】

これに対して、本実施形態に係る積層セラミック電子部品1の製造方法においては、図3〜図5に示されるように、生のセラミック素体23の主面24a,24bの導電性ペーストが塗布される部分には、第2のセラミックグリーンシート20bが配される。そして、本実施形態においては、第2のセラミックグリーンシート20bに含まれる第2の有機バインダーの重合度をAとし、第2のセラミックグリーンシートに含まれる第2の可塑剤の体積含有率をBとしたときに、180.56≦A/Bの関係を充足するようにして、第2の有機バインダーと第2の可塑剤とを用いる。これにより、生のセラミック素体23の表面に導電性ペーストを塗布した際、第2のセラミックグリーンシート20bの結合が強固になり第2のセラミックグリーンシート20bが硬く形成されることになるため導電性ペーストに含まれる溶剤などが生のセラミック素体23に染み込むことが抑制される。よって、本実施形態に係る積層セラミック電子部品1の製造方法によれば、生のセラミック素体23が膨潤したり、歪むことを効果的に抑制することができる。

【0050】

また、生のセラミック素体の膨潤などに起因して、積層セラミック電子部品の内部には、剥がれ(デラミネーション)などに因る空隙が発生する場合がある。薄型の積層セラミック電子部品の場合、内部の空隙が積層セラミック電子部品の特性に与える影響は特に大きい。

【0051】

本実施形態に係る積層セラミック電子部品1の製造方法において、第1のセラミックグリーンシートに含まれる第1の有機バインダーの重合度をA1、第1のセラミックグリーンシートに含まれる第1の可塑剤の体積含有率をB1とし、第2のセラミックグリーンシートに含まれる第2の有機バインダーの重合度をAとし、第2のセラミックグリーンシートに含まれる第2の可塑剤の体積含有率をBとしたときに、さらに2.74≦((A/B)/(A1/B1))≦5.00となる関係を充足する場合、生のセラミック素体23が膨潤や歪みを効果的に抑制することができることに加えて、積層セラミック電子部品1としたときに、内部に空隙が発生することを効果的に抑制することができる。これは、第1のセラミックグリーンシート及び第2のセラミックグリーンシートが、それぞれ適切な硬さに調節されているため、第1のセラミックグリーンシート及び第2のセラミックグリーンシートにおいて収縮差が抑えられているためと考えられる。

【0052】

なお、本実施形態においては、複数の第2のセラミックグリーンシートのそれぞれにおいて、180.56≦A/Bが満たされる例について説明した。但し、本発明は、この構成に限定されない。例えば、主面を構成する最外層に位置する第2のセラミックグリーンシートのみにおいて180.56≦A/Bが満たされていてもよい。この場合であっても同様の効果が得られる。

【0053】

同様に、複数の第2のセラミックグリーンシートのそれぞれにおいて、2.74≦((A/B)/(A1/B1))≦5.00が満たされることがより好ましいが、主面を構成する最外層に位置する第2のセラミックグリーンシートのみにおいて2.74≦((A/B)/(A1/B1))≦5.00が満たされていてもよい。

【0054】

第2のセラミックグリーンシートの上には、内部電極を構成しない導電層が設けられていてもよい。例えば、第2のセラミックグリーンシートの上に、ダミー電極を構成するための導電層が設けられていてもよい。ここで、内部電極とは、例えばコンデンサの場合では容量を形成する電極であり、一般的には、電子部品の機能を発現するための電極である。

【0055】

以下、本発明について、具体的な実施例に基づいて、さらに詳細に説明するが、本発明は以下の実施例に何ら限定されるものではなく、その要旨を変更しない範囲において適宜変更して実施することが可能である。

【0056】

(実施例1)

上記実施形態に係る積層セラミック電子部品1のマザー積層体22を、上記実施形態において説明した方法で、以下の条件で作製した。

【0057】

(1)第1のセラミックグリーンシート20a

セラミック粉末: BaTiO3 79.3体積%

第1の有機バインダー:ポリビニルブチラール樹脂(重合度850) 10.2体積%

第1の可塑剤:フタル酸ジオクチル 17.0体積%

導電層21の組成:導電材料Ni、溶剤テルピネオール

第1のセラミックグリーンシート20aのサイズ:200mm×200mm 第1のセラミックグリーンシート20aの積層枚数7枚

【0058】

(2)第2のセラミックグリーンシート20b

セラミック粉末: BaTiO3 79.3体積%

第2の有機バインダー:ポリビニルブチラール樹脂(重合度1300) 22.0体積%

第2の可塑剤:フタル酸ジオクチル 5.2体積%

第2のセラミックグリーンシート20bのサイズ:200mm×200mm 第2のセラミックグリーンシート20bの積層枚数7枚

【0059】

(3)導電性ペースト層27の組成:導電材料Ni、溶剤ターピネオール

【0060】

なお、下記の表1に示すように、実施例及び比較例の各セラミックグリーンシート中において、有機バインダーと可塑剤の合計量が、27.2体積%となるように調整した。

【0061】

[膨潤・歪みの確認]

焼成後のセラミック素体23のサイズが1.0mm×0.5mm×0.15mmとなるようにして、実施例1で得られたマザー積層体22をカットした。生のセラミック素体23の膨潤、歪みの有無をニコンインスペック社製のNEXIV VMR−6555を用いて確認した。具体的には、マザー積層体22をカットした後、個々の生のセラミック素体23に分割する前に、マザー積層体22を平面視して100の領域に均等に区画し、各領域内の複数ある生のセラミック素体23のうち、各領域の中央に位置する1つの生のセラミック素体23それぞれについて、導電性ペースト層27が塗布された部分の幅方向Xの膨潤、歪みの有無を確認した。生のセラミック素体23の寸法規格として、導電性ペースト層27部分の幅方向長さにおいて一定の長さを満たさないものを膨潤、歪みが発生していると判定した。100領域中、膨潤、歪みを有する生のセラミック素体が含まれていた領域の数を表1に示す。表1に示すように、実施例1で得られた生のセラミック素体23には、膨潤、歪みはほとんど発生しなかった。

【0062】

(実施例2〜8及び比較例1,2)

第1及び第2の有機バインダーの種類(重合度)及び使用量と第1及び第2の可塑剤の使用量を表1に記載のものとし、実施例1と同様にして、実施例2〜8及び比較例1,2のマザー積層体22をそれぞれ作製した。次に、実施例2〜8及び比較例1,2で得られたマザー積層体22を用いて、実施例1と同様にして膨潤・歪みを確認した。結果を表1に示す。表1に示すように、実施例2〜8で得られた生のセラミック素体23には、膨潤・歪みはほとんど発生しなかった。一方、比較例1,2で得られた生のセラミック素体には多くの膨潤・歪みが発生した。

【0063】

[内部空隙の確認]

次に、実施例1〜8及び比較例1,2のマザー積層体22から得られた全ての生のセラミック素体23を不活性ガス雰囲気下、1200℃で2時間焼成した。得られたセラミック積層体の全てについて、超音波顕微鏡(C−SAM)を用いて内部空隙の有無を確認した。その結果、実施例2〜5で得られたセラミック積層体には、内部空隙が発生しているものは1つもなかった。

【0064】

【表1】

【符号の説明】

【0065】

1…積層セラミック電子部品

10…セラミック素体

10a、10b…主面

10c、10d…側面

10e、10f…端面

10g…セラミック層

11…第1の内部電極

12…第2の内部電極

13…第1の外部電極

14…第2の外部電極

13a,14a…第1の部分

13b,14b…第2の部分

13c,14c…第3の部分

20a…第1のセラミックグリーンシート

20b…第2のセラミックグリーンシート

21…導電層

22…マザー積層体

23…生のセラミック素体

24…チップ本体

24a、24b…主面

24e、24f…端面

25…第1の内部電極

26…第2の内部電極

27…導電性ペースト層

29…セラミック層

L1,L2…カットライン

【特許請求の範囲】

【請求項1】

内部電極を構成するための導電層が表面上に形成された第1のセラミックグリーンシートと、内部電極を構成するための導電層が表面上に形成されていない第2のセラミックグリーンシートとを用意する工程と、

少なくとも一枚の前記第2のセラミックグリーンシートと、複数の前記第1のセラミックグリーンシートと、少なくとも一枚の前記第2のセラミックグリーンシートとをこの順番で積層することにより、主面と、前記導電層が露出した端面とを有する生のセラミック素体を作製する工程と、

少なくとも前記主面の上に、導電性ペーストを塗布し、外部電極を形成するための導電性ペースト層を形成する工程と、

前記導電性ペースト層が形成された前記生のセラミック素体を焼成することにより積層セラミック電子部品を作製する工程と、

を備え、

前記第1及び第2のセラミックグリーンシートのそれぞれは、有機バインダー及び可塑剤を含み、

前記有機バインダーの重合度をAとし、前記可塑剤の体積含有率をBとしたときに、前記主面を構成している第2のセラミックグリーンシートにおいて、180.56≦A/Bとなる、積層セラミック電子部品の製造方法。

【請求項2】

前記生のセラミック素体を作製する工程において、複数の前記第2のセラミックグリーンシートと、複数の前記第1のセラミックグリーンシートと、複数の前記第2のセラミックグリーンシートとをこの順番で積層し、

前記複数の第2のセラミックグリーンシートのそれぞれにおいて、180.56≦A/Bとなる、請求項1に記載の積層セラミック電子部品の製造方法。

【請求項3】

前記第1のセラミックグリーンシートに含まれる前記有機バインダーの重合度をA1、前記第1のセラミックグリーンシートに含まれる前記可塑剤の体積含有率をB1としたときに、

前記主面を構成している前記第2のセラミックグリーンシートにおいて、2.74≦((A/B)/(A1/B1))≦5.00となる、請求項1または2に記載の積層セラミック電子部品の製造方法。

【請求項4】

前記生のセラミック素体を作製する工程において、複数の前記第2のセラミックグリーンシートと、複数の前記第1のセラミックグリーンシートと、複数の前記第2のセラミックグリーンシートとをこの順番で積層し、

前記複数の第2のセラミックグリーンシートのそれぞれにおいて、2.74≦((A/B)/(A1/B1))≦5.00となる、請求項3に記載の積層セラミック電子部品の製造方法。

【請求項5】

前記第1及び第2のセラミックグリーンシートに含まれる前記有機バインダーは、それぞれポリビニルブチラール樹脂、ポリビニルホルマール樹脂、ポリビニルヘキサナール樹脂からなる群から選ばれる少なくとも一種からなる、請求項1〜4のいずれか一項に記載の積層セラミック電子部品の製造方法。

【請求項6】

前記第1及び第2のセラミックグリーンシートに含まれる前記可塑剤は、フタル酸エステルである、請求項1〜5のいずれか一項に記載の積層セラミック電子部品の製造方法。

【請求項1】

内部電極を構成するための導電層が表面上に形成された第1のセラミックグリーンシートと、内部電極を構成するための導電層が表面上に形成されていない第2のセラミックグリーンシートとを用意する工程と、

少なくとも一枚の前記第2のセラミックグリーンシートと、複数の前記第1のセラミックグリーンシートと、少なくとも一枚の前記第2のセラミックグリーンシートとをこの順番で積層することにより、主面と、前記導電層が露出した端面とを有する生のセラミック素体を作製する工程と、

少なくとも前記主面の上に、導電性ペーストを塗布し、外部電極を形成するための導電性ペースト層を形成する工程と、

前記導電性ペースト層が形成された前記生のセラミック素体を焼成することにより積層セラミック電子部品を作製する工程と、

を備え、

前記第1及び第2のセラミックグリーンシートのそれぞれは、有機バインダー及び可塑剤を含み、

前記有機バインダーの重合度をAとし、前記可塑剤の体積含有率をBとしたときに、前記主面を構成している第2のセラミックグリーンシートにおいて、180.56≦A/Bとなる、積層セラミック電子部品の製造方法。

【請求項2】

前記生のセラミック素体を作製する工程において、複数の前記第2のセラミックグリーンシートと、複数の前記第1のセラミックグリーンシートと、複数の前記第2のセラミックグリーンシートとをこの順番で積層し、

前記複数の第2のセラミックグリーンシートのそれぞれにおいて、180.56≦A/Bとなる、請求項1に記載の積層セラミック電子部品の製造方法。

【請求項3】

前記第1のセラミックグリーンシートに含まれる前記有機バインダーの重合度をA1、前記第1のセラミックグリーンシートに含まれる前記可塑剤の体積含有率をB1としたときに、

前記主面を構成している前記第2のセラミックグリーンシートにおいて、2.74≦((A/B)/(A1/B1))≦5.00となる、請求項1または2に記載の積層セラミック電子部品の製造方法。

【請求項4】

前記生のセラミック素体を作製する工程において、複数の前記第2のセラミックグリーンシートと、複数の前記第1のセラミックグリーンシートと、複数の前記第2のセラミックグリーンシートとをこの順番で積層し、

前記複数の第2のセラミックグリーンシートのそれぞれにおいて、2.74≦((A/B)/(A1/B1))≦5.00となる、請求項3に記載の積層セラミック電子部品の製造方法。

【請求項5】

前記第1及び第2のセラミックグリーンシートに含まれる前記有機バインダーは、それぞれポリビニルブチラール樹脂、ポリビニルホルマール樹脂、ポリビニルヘキサナール樹脂からなる群から選ばれる少なくとも一種からなる、請求項1〜4のいずれか一項に記載の積層セラミック電子部品の製造方法。

【請求項6】

前記第1及び第2のセラミックグリーンシートに含まれる前記可塑剤は、フタル酸エステルである、請求項1〜5のいずれか一項に記載の積層セラミック電子部品の製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【公開番号】特開2013−70024(P2013−70024A)

【公開日】平成25年4月18日(2013.4.18)

【国際特許分類】

【出願番号】特願2012−117712(P2012−117712)

【出願日】平成24年5月23日(2012.5.23)

【出願人】(000006231)株式会社村田製作所 (3,635)

【Fターム(参考)】

【公開日】平成25年4月18日(2013.4.18)

【国際特許分類】

【出願日】平成24年5月23日(2012.5.23)

【出願人】(000006231)株式会社村田製作所 (3,635)

【Fターム(参考)】

[ Back to top ]