積層セラミック電子部品及びその製造方法

【課題】直流抵抗特性及びインピーダンス特性に優れ、安くて生産性の高い積層セラミック電子部品及びその製造方法を提供する。

【解決手段】本発明はセラミック本体と、上記セラミック本体の外部に形成された外部電極と、上記セラミック本体の内部にコイル構造を形成する内部導体とを含み、上記コイルの中心軸は上記外部電極を連結する方向と平行で、上記内部導体は上記コイルの中心軸と垂直に積層されたビア導体を含み、上記ビア導体の一面の面積に対する他面の面積の比は0.9以上1.1以下であることを特徴とする。

【解決手段】本発明はセラミック本体と、上記セラミック本体の外部に形成された外部電極と、上記セラミック本体の内部にコイル構造を形成する内部導体とを含み、上記コイルの中心軸は上記外部電極を連結する方向と平行で、上記内部導体は上記コイルの中心軸と垂直に積層されたビア導体を含み、上記ビア導体の一面の面積に対する他面の面積の比は0.9以上1.1以下であることを特徴とする。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は積層セラミック電子部品に関し、具体的には、直流抵抗特性及びインピーダンス特性に優れた積層セラミック電子部品及び安くて生産性の高い積層セラミック電子部品の製造方法に関する。

【背景技術】

【0002】

積層型インダクターの場合、磁性体本体の内部に電気的に連結されたコイル構造が形成されており、コイル構造は導体パターンを連結して構成されることができる。

【0003】

積層型インダクターにおいて、外部電極を連結して延長する方向とコイルの中心軸が垂直である場合は、内部電極と外部電極の間に寄生容量が形成されることがあり、これによりインダクターの高周波特性が低下することがある。

【0004】

上記問題を解決するために、コイルの中心軸と外部電極を連結する方向が平行するように配置する構造が提案されており、これによると、内部電極導体の間に主に寄生容量が形成され、内部電極と外部電極の間では寄生容量が殆ど形成されないため、インダクターの磁気共鳴周波数(SRF、Self Resonance Frequency)が上昇し、高周波Q特性が大きく向上する。

【0005】

しかし、コイルの内面積が小さく、コイルのターン数が多いため、コイルそのものの効率が小さく、また、直流抵抗(Rdc)が高くて高電流特性が求められる製品には使用しにくい。

【0006】

これの代案として、コイルの中心軸が外部電極を連結して延長する方向と平行で、且つ、コイルの中心軸とビア導体の積層方向が垂直である構造が提案された。しかし、全グリーンシートにビア孔を加工しなければならず、また、低い直流抵抗値を具現するためにビア孔を大きく加工しなければならないが、このためには高価な設備が必要である。よって生産性が低下するという問題がある。

【発明の概要】

【発明が解決しようとする課題】

【0007】

本発明は、直流抵抗特性及びインピーダンス特性に優れた積層セラミック電子部品及び安くて生産性の高い積層セラミック電子部品の製造方法を提供することを目的とする。

【課題を解決するための手段】

【0008】

本発明が一実施形態である積層セラミック電子部品はセラミック本体と、上記セラミック本体の外部に形成された外部電極と、上記セラミック本体の内部にコイル構造を形成する内部導体とを含み、上記コイルの中心軸は上記外部電極を連結する方向と平行で、上記内部導体は上記コイルの中心軸と垂直に積層されたビア導体を含み、上記ビア導体の一面の面積に対する他面の面積の比は0.9以上1.1以下であってよい。

【0009】

上記ビア導体の積層方向から投影してみると、上記ビア導体は四角形又は円形であってよい。

【0010】

上記コイルの中心軸方向からみて、上記コイルは四角形であってよい。

【0011】

上記セラミック本体は磁性体を含んでよく、上記磁性体はフェライト材料を含むことができ、上記フェライト材料はニッケル−亜鉛−銅フェライトを含むことができる。

【0012】

上記内部導体は金、銀、銅、ニッケル、パラジウム及びこれらの合金からなるグループから選択された一つ以上を含んでよい。

【0013】

本発明の他の実施形態である積層セラミック電子部品の製造方法は、セラミックペーストを印刷してセラミックグリーンシートを用意する第1段階と、セラミックグリーンシート上に第1導電性ペーストを印刷して複数の第1導体を形成し、上記セラミックグリーンシートの上記第1導体を除いた部分にセラミックペーストを印刷する第2段階と、上記セラミックグリーンシート上に第2導電性ペーストを印刷して複数の上記第1導体の両端に接続されるように第1ビア導体を形成し、上記セラミックグリーンシートの複数の上記第1ビア導体を除いた部分に上記セラミックペーストを印刷する第3段階と、上記セラミックシート上に第2導電性ペーストを印刷して複数の上記第1ビア導体に相応する位置に複数の第2ビア導体を形成し、上記セラミックシートの複数の上記第2ビア導体を除いた部分に上記セラミックペーストを印刷する第4段階と、上記セラミックグリーンシート上に第1導電性ペーストを印刷して複数の上記第2ビア導体に接続されるように複数の第2導体を形成し、上記セラミックグリーンシートの複数の上記第2導体を除いた部分に上記セラミックペーストを印刷する第5段階と、上記セラミックグリーンシート上に上記セラミックペーストを印刷する第6段階を含んでよい。

【0014】

上記セラミックペーストは磁性体を含んでよい。

【0015】

上記磁性体はフェライトを含んでよい。

【0016】

上記フェライトはニッケル−亜鉛−銅フェライトを含んでよい。

【0017】

上記第1及び第2導電性ペーストは金、銀、銅、ニッケル、パラジウム及びこれらの合金を含むグループから選択された一つ以上を含んでよい。

【0018】

上記第1及び第2導電性ペーストは同じ材料を含んでよい。

【0019】

上記第1及び第2導体は帯状であってよい。

【0020】

上記第5段階の前に、上記第4段階を繰り返して行い柱状のビア導体を形成する段階をさらに含んでよい。

【0021】

上記ビア導体の積層方向において、上記ビア導体の一面の面積に対する上記ビア導体の他面の面積の比率は0.9以上1.1以下であってよい。

【0022】

上記ビア導体の積層方向から投影してみると、上記ビア導体は四角形又は円形であってよい。

【発明の効果】

【0023】

本発明によると、直流抵抗特性及びインピーダンス特性に優れ、且つ、安くて生産性の高い積層セラミック電子部品が得られる。

【図面の簡単な説明】

【0024】

【図1】本発明の一実施形態による積層セラミック電子部品の外観斜視図である。

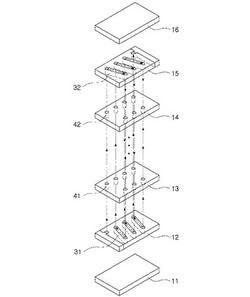

【図2】本発明の一実施形態による積層セラミック電子部品の分解斜視図である。

【図3】本発明の一実施形態による積層セラミック電子部品の投影斜視図である。

【図4】(a)および(b)は本発明の一実施形態によるビア導体の平面図である。

【図5】(a)および(b)は本発明の一実施形態によるビア導体の概略図である。

【図6】本発明の一実施形態による積層セラミック電子部品の製造工程のフローチャートである。

【図7】本発明の一実施形態によるビア導体の製造工程の模式図である。

【図8】本発明の一実施形態による積層セラミック電子部品の製造工程の模式図である。

【発明を実施するための形態】

【0025】

以下では、添付の図面を参照して本発明の好ましい実施形態を説明する。

【0026】

但し、本発明の実施形態は様々な他の形態に変形されることができ、本発明の範囲は以下で説明する実施形態に限定されない。

【0027】

また、本発明の実施形態は当業界で平均的な知識を有する者に本発明をより完全に説明するために提供されるものである。

【0028】

従って、図面における要素の形状及び大きさなどはより明確な説明のために誇張されることがあり、図面上に同じ符号で示される要素は同じ要素である。

【0029】

図1から図3を参照し、本発明の一実施形態である積層セラミック電子部品について説明する。

【0030】

図1は本発明の一実施形態である積層セラミック電子部品の外観斜視図であり、図2は本発明の一実施形態である積層セラミック電子部品の分解斜視図であり、図3は本発明の一実施形態である積層セラミック電子部品の投影斜視図である。

【0031】

積層セラミック電子部品には積層セラミックキャパシタ、積層型チップインダクター、積層型チップビーズなどがあり、以下では、積層型チップインダクターを例に挙げて説明するが、本発明はこれに限定されない。

【0032】

本実施形態は、セラミック本体10、外部電極21、22、内部導体31、32、41、42を含むことができる。

【0033】

図1を参照すると、セラミック本体10は直方体形状を有することができる。「長さ方向」は「L」方向、「幅方向」は「W」方向、「厚さ方向」は「T」方向と定義することができる。ここで、「厚さ方向」はセラミック層を積層する方向、即ち、「積層方向」と同じ概念で使用することができる。

【0034】

セラミック本体10は透磁率の高い磁性材料を含んでよく、上記磁性材料はこれに制限されないが、フェライト系材料を使用することができ、具体的にはニッケル−銅−亜鉛フェライトを使用することができる。

【0035】

セラミック本体10は複数のセラミック層を積層した後に焼結させたもので、隣接するセラミック層同士は境界が確認できない程度一体化されていてもよい。

【0036】

外部電極21、22は、セラミック本体10の外部面に対向するように形成されてよい。

【0037】

外部電極21、22は導電性金属を含む導電性ペーストを利用して形成されてよく、これに制限されないが、導電性金属は金、銀、銅、ニッケル、パラジウム及びこれらの合金などを含むことができる。

【0038】

図2及び3を参照すると、内部導体はビア導体41、42と第1及び第2導体31、32を含んでよい。

【0039】

内部導体31、32、41、42はセラミック本体10の内部に形成され、コイル形状を有するように配置されてよい。

【0040】

内部導体がコイル形状を有するように配置されるため、内部導体に電流が流れると、内部導体31、32、41、42の周りには磁場が誘導されることができ、インダクターとしての機能を行うことができる。

【0041】

コイルの中心軸は、外部電極21、22を連結する方向と平行であってよい。即ち、コイルの中心軸はセラミック本体10の長さ方向(L方向)と平行であることができる。

【0042】

この構造では、内部導体31、32、41、42の間にのみ寄生容量が主に形成され、内部導体31、32、41、42と外部電極21、22の間に形成される寄生容量は非常に少ないため、インダクターの磁気共鳴周波数(SRF、Self Resonance Frequency)が増加し高周波Q特性が向上することができる。

【0043】

ビア導体41、42は複数が積層されてビア柱を形成してもよく、ビア導体41、42の積層方向はコイルの中心軸と垂直であることができる。

【0044】

図4は本発明の一実施形態によるビア導体41、42の平面図である。

【0045】

図4を参照すると、ビア導体41、42の平面は、四角形又は円形であってよい。

【0046】

図4(a)にはビア導体41、42の平面が円形である場合を示し、図4(b)にはビア導体41、42の平面が四角形である場合を示した。

【0047】

ビア導体41、42の平面が円形より四角形の場合に断面積が広いため、ビア導体41、42の直列抵抗をさらに減少させることができる。

【0048】

図5は本発明の一実施形態によるビア導体41、42の概略図である。

【0049】

図5(b)を参照すると、ビア導体41、42の断面が四角形の場合、ビア導体41、42の上面の長さ(X又はX’)に対する下面の長さ(Y又はY’)の比(Y/X、Y’/X’)は0.9以上1.1以下であってよい。

【0050】

ビア導体41、42の上面の長さ(X又はX’)に対する下面の長さ(Y又はY’)の比(Y/X、Y’/X’)が1.0の場合、電流の流れる通路が最も広いため、最も理想的である。しかし、製造工程の誤差によりこれを具現することは困難である。

【0051】

ビア導体41、42の上面の長さ(X又はX’)に対する下面の長さ(Y又はY’)の比(Y/X、Y’/X’)が0.9未満では、電流の流れる通路が狭くなるため、直列抵抗が高くなり過ぎることがある。

【0052】

ビア導体41、42の上面の長さ(X又はX’)に対する下面の長さ(Y又はY’)の比(Y/X、Y’/X’)が1.1以上の場合にも同様に電流の流れる通路が狭くなって直列抵抗が大きくなることがある。これはビア導体41、42の上面及び下面が逆になった場合も同様であるためである。

【0053】

図5(a)を参照すると、ビア導体41、42の断面が円形の場合には、ビア導体41、42の上面の直径(X)に対する下面の直径(Y)の比(Y/X)が0.9以上1.1以下であってよい。

【0054】

長さが直径に変わったことを除き、ビア導体41、42の断面が四角形の場合と同様である。

【0055】

コイルの中心軸方向から投影してみると、上記コイルは四角形であることができる。

【0056】

コイルはビア導体41、42を積層して形成するため、円形のコイルを製造することは実質的に困難である。

【0057】

円形のコイルを製造する場合は、隣接するビア導体41、42の位置がずれるように形成しなければならないため、ビア導体41、42間の連結が切れる虞がある。

【0058】

これを防止するために、ビア導体41、42とビア導体41、42の間にビアパッド(不図示)をさらに形成してもよいが、この場合、更なる工程を必要とするため、製造費用が増加するという問題があり、また、依然としてビア導体41、42とビア導体41、42の間の電気的連結が切れる虞がある。

【0059】

内部導体31、32、41、42は電気的に導電性を有する物質であれば、特に制限されない。但し、セラミック内で焼結されるという点を考慮し、融点の高い導電性金属を使用することができる。

【0060】

具体的には、内部導体は金、銀、銅、ニッケル、パラジウム及びこれらの合金からなる群から選択された何れか1つからなることができる。

【0061】

以下では、本発明の他の実施形態である積層セラミック電子部品の製造方法について説明する。

【0062】

図6は本発明の一実施形態による積層セラミック電子部品の製造工程のフローチャートであり、図7は本発明の一実施形態によるビア導体の製造工程の模式図であり、図8は本発明の一実施形態による積層セラミック電子部品の製造工程の模式図である。

【0063】

図3及び図6を参照すると、積層セラミック電子部品の製造方法は以下の通りである。

【0064】

第1段階S1では、セラミックペーストを印刷してセラミックグリーンシート11を用意することができる。

【0065】

先ず、セラミック粉末に有機溶媒、バインダーなどを混合した後、これをボールミリングなどをし、セラミック粉末が均一に分散されたセラミックペーストを製造することができる。

【0066】

ポリエチレンなどの高分子フィルム上にスクリーンプリントなどの方法でセラミックペーストを印刷し、これを乾燥してセラミックグリーンシート11を用意することができる。

【0067】

第2段階S2では、セラミックグリーンシート11上に第1導電性ペーストを印刷して複数の第1導体31を形成し、上記セラミックグリーンシート11の上記第1導体31を除いた部分にセラミックペーストを印刷してよい。

【0068】

第1導電性ペーストは、セラミック粉末の代わりに導電性金属を含むことを除き、上記セラミックペーストと同様にして用意することができる。但し、粘度などを調節するために有機溶媒及びバインダーなどの含量は異なってもよい。

【0069】

第1導電性ペーストをスクリーン印刷してセラミックグリーンシート11上に複数の第1導体31を形成することができる。スクリーン印刷の繰り返し回数を調節することで、第1導体31の厚さを調節することができ、第1導体が厚いほど直流抵抗(Rdc)が減少する。

【0070】

第1導体31が形成された領域を除いた部分には再びセラミックペーストを印刷してセラミック領域を形成してよい。これによって、セラミック領域の中央に第1導体31が形成されたセラミックグリーンシート12が得られる。

【0071】

第3段階S3では、セラミックグリーンシート12上に第2導電性ペーストを印刷して複数の上記第1導体31の両端に接続されるように第1ビア導体41を形成し、上記セラミックグリーンシート12の複数の上記第1ビア導体41を除いた部分に上記セラミックペーストを印刷してよい。

【0072】

第1導体31の両端に対応するように第1ビア導体41を印刷してよい。印刷回数によって第1ビア導体41の厚さを調節することができる。

【0073】

第1ビア導体41が形成された領域を除いた部分には再びセラミックペーストを印刷してセラミック領域を形成してよく、これによってビア導体41がセラミックグリーンシート上13に露出した状態となる。

【0074】

ビア導体41を印刷方式で形成するため、ビア導体41の上面及び下面の寸法を殆ど等しく保持することができ、積層されたビア導体41の直流抵抗(Rdc)を最小化することができる。

【0075】

電流の流れる通路は面積の小さい上面又は下面により決まるため、ビア導体41の上面及び下面の面積が異なると、電流の流れの通路が減少することがある。

【0076】

従って、ビア導体41の上面及び下面の面積を等しく保持することで、直流抵抗を減らすことができる。

【0077】

ビア孔を形成してから導電性ペーストで埋め込む場合は、ビア導体の上面及び下面の面積を等しく形成することが困難である。ビア孔を形成する際、ビア孔の寸法を一定に形成することが困難で、ビア孔を導電性ペーストで埋め込む過程でも製造工程上の誤差などによりビア導体の寸法を一定に形成することが困難である。

【0078】

従って、ビア孔を形成してから導電性ペーストで埋め込むと、直流抵抗を減少させるのに限界がある。

【0079】

本実施形態では、このような問題を解決するために、ビア導体41、42を先ず形成した後、上記ビア導体41、42が形成された領域を除いた部分にセラミックペーストを印刷してセラミック領域を形成する。こうすることで、ビア導体41、42の寸法を安定的に形成することができる。

【0080】

即ち、ビア導体41、42の上面及び下面の面積を等しくしてビア導体41、42の直流抵抗を最大限減らすことができる。

【0081】

第4段階S4は、上記セラミックグリーンシート13上に第2導電性ペーストを印刷して複数の上記第1ビア導体41に相応する位置に複数の第2ビア導体42を形成し、上記セラミックグリーンシート13の複数の上記第2ビア導体42を除いた部分に上記セラミックペーストを印刷してよい。

【0082】

第4段階はビア柱を形成する工程であって、既に形成されたビア導体41に対応するように第2導電性ペーストを印刷して第2ビア導体42を形成してよい。第2ビア導体42が形成された領域を除いた領域にはセラミックペーストを印刷してセラミック領域を形成してよい。

【0083】

第4段階を数回繰り返して所望する高さのビア柱を形成することができる。

【0084】

第1導体31及び柱状のビア導体41、42により「U」字型の導体が並んで配置されている構造となり、各「U」字型の導体同士は分離されている。

【0085】

第5段階S5では、上記セラミックグリーンシート14上に第1導電性ペーストを印刷して複数の上記第2ビア導体42に接続されるように複数の第2導体32を形成し、上記セラミックグリーンシート14の複数の上記第2導体が形成された領域を除いた領域に上記セラミックペーストを印刷してセラミック領域を形成してよい。

【0086】

既に形成されているビア導体42に両端が接続されるように第2導体32を形成してよい。第2導体32は第1導電性ペースを印刷して形成してよい。

【0087】

第2導体32は、第5段階で形成された「U」字形の導体を相互電気的に連結して螺旋形のコイルを形成する役割をする。

【0088】

第5段階を経てコイルが完成される。

【0089】

第6段階S6では、上記セラミックグリーンシート15上に上記セラミックペーストを印刷してよい。

【0090】

既に形成された複数の第2導体32を完全に囲むようにセラミックペーストを印刷することで、第2導体32を外部から保護することができる。

【0091】

上記した内容とは異なって、第1段階は行わなくてもよい。

【0092】

図7を参照すると、高分子樹脂などのベース1上に第2から第5段階のみを行って柱状の積層ビアを形成した後、ベース1を除去しその上下にセラミックペーストを印刷してもよい。

【0093】

また、図8を参照すると、ロールツーロール工法により連続的に製造することもできる。図6の第2から第5段階(S2〜S6)を行って柱状の積層ビア導体を形成してもよい。

【0094】

セラミックペーストは磁性体を含んでよく、磁性体はフェライトを含むことができ、フェライトはニッケル−亜鉛−銅フェライトを含むことができる。

【0095】

第1及び第2導電性ペーストは金、銀、銅、ニッケル、パラジウム及びこれらの合金からなるグループから選択された何れか一つ以上を含んでよい。

【0096】

第1及び第2導電性ペーストは同じ材料を含んでよい。

【0097】

第1導電性ペーストでは第1及び第2導体を形成し、第2導電性ペーストでは複数のビア導体を形成するため、第1及び第2導電性ペーストが同一であり、第1及び第2導体とビア導体間の機械的接続及び電気的接続がさらに安定的であることができる。

【0098】

第1及び第2導体は帯状であってよい。

【0099】

第5段階の前に、第4段階を繰り返して行い柱状のビア導体を形成する段階をさらに含んでよい。

【0100】

ビア導体の積層方向において、ビア導体の一面の面積に対する上記ビア導体の他面の面積の比率は0.9以上1.1以下であってよい。

【0101】

上記ビア導体の積層方向から投影してみると、上記ビア導体は四角形又は円形であってよい。

【0102】

セラミックは磁性材料、ガラス材料及び誘電材料のうち何れか一つであってよい。

【0103】

ビア導体、セラミック材料に関する内容は上述と同一である。

【実施例】

【0104】

以下では、具体的な実施例を挙げて発明について詳細に説明する。

【0105】

先ず、ニッケル−亜鉛−銅フェライト粉末、有機溶媒としてエタノール、バインダーとしてエチルセルロースを混合した後、これを3−ロールミリングしてセラミックペーストを用意し、また、銀(Ag)粉末を含む導電性ペーストを用意した。

【0106】

次いで、セラミックペーストをポリエチレンフィルム上にスクリーン印刷してセラミックグリーンシートを製造した後、乾燥させた。

【0107】

次に、導電性ペーストを利用してセラミックグリーンシート上に帯状の第1導体を7個形成し、帯状の導体を除いた領域にセラミックペーストを印刷してセラミック領域を形成した。

【0108】

7個の帯状の導体の両端に対応するように導電性ペーストを印刷してビア導体を形成し、ビア導体を除いた領域にセラミックペーストを印刷してセラミック領域を形成した。

【0109】

ビア導体の断面は一辺が50μmである正方形となるようにした。

【0110】

この過程を10回〜40回繰り返してビア導体柱を形成した。

【0111】

次に、ビア導体と接続されるように帯状の複数の第2導体を印刷してコイル構造を形成した。

【0112】

次いで、第2導体を囲むようにセラミックペーストを印刷した。

【0113】

上記製造方法により製造された積層型インダクターに対し直流抵抗値を測定した。

【0114】

直流抵抗はAgilent 4338Bミリオームメータを利用して測定した。

【0115】

比較例ではセラミックグリーンシートにビア孔を形成した後、導電性ペーストを埋め込んでビア導体を形成し、これを積層してビア柱を形成した点を除き、実施例と同じ方法で製造した。

【0116】

実施例及び比較例に対する直流抵抗(Rdc)を測定した結果を表1に示した。

【0117】

比較例の場合、ビア導体の上面の長さに対する下面の長さの比率は0.7、0.8、1.2、1.3となるようにした。

【0118】

実施例の場合、ビア導体の上面の面積に対する下面の面積の比率は0.95〜1.05の範囲に属している。

【0119】

【表1】

【0120】

表1において、Xはビア導体の上面の長さで、Yはビア導体の下面の長さで、Y/Xはビア導体の上面の長さに対する下面の長さの比率である。

【0121】

表1を参照すると、比較例1、2はY/Xが[0.7]、[0.8]の場合であって、Rdc値が[1.4]、[1.25]で、実施例1、2、3はY/Xが[0.9]、[1.0]、[1.1]の場合であって、Rdc値が[1.15]、[1.10]、[1.11]で、比較例3、4はY/Xが[1.2]、[1.3]の場合であって、Rdc値が[1.22]、[1.34]である。

【0122】

表1の結果によると、Y/Xが[0.9]、[1.0]、[1.1]の場合、Rdc値が小さいことが分かる。

【0123】

本発明は上述した実施形態及び添付の図面により限定されず、添付の請求範囲により限定する。

【0124】

従って、請求の範囲に記載された本発明の技術的思想から外れない範囲内で当技術分野の通常の知識を有する者により多様な形態の置換、変形及び変更が可能であり、これも本発明の範囲に属する。

【符号の説明】

【0125】

10 セラミック本体

11〜16 セラミック層

31 第1導体

32 第2導体

40、41、42 ビア導体

21、22 外部電極

X、X’ ビア導体の上面の直径又は長さ

Y、Y’ ビア導体の下面の直径又は長さ

X−X’面 ビア導体の上面

Y−Y’面 ビア導体の下面

【技術分野】

【0001】

本発明は積層セラミック電子部品に関し、具体的には、直流抵抗特性及びインピーダンス特性に優れた積層セラミック電子部品及び安くて生産性の高い積層セラミック電子部品の製造方法に関する。

【背景技術】

【0002】

積層型インダクターの場合、磁性体本体の内部に電気的に連結されたコイル構造が形成されており、コイル構造は導体パターンを連結して構成されることができる。

【0003】

積層型インダクターにおいて、外部電極を連結して延長する方向とコイルの中心軸が垂直である場合は、内部電極と外部電極の間に寄生容量が形成されることがあり、これによりインダクターの高周波特性が低下することがある。

【0004】

上記問題を解決するために、コイルの中心軸と外部電極を連結する方向が平行するように配置する構造が提案されており、これによると、内部電極導体の間に主に寄生容量が形成され、内部電極と外部電極の間では寄生容量が殆ど形成されないため、インダクターの磁気共鳴周波数(SRF、Self Resonance Frequency)が上昇し、高周波Q特性が大きく向上する。

【0005】

しかし、コイルの内面積が小さく、コイルのターン数が多いため、コイルそのものの効率が小さく、また、直流抵抗(Rdc)が高くて高電流特性が求められる製品には使用しにくい。

【0006】

これの代案として、コイルの中心軸が外部電極を連結して延長する方向と平行で、且つ、コイルの中心軸とビア導体の積層方向が垂直である構造が提案された。しかし、全グリーンシートにビア孔を加工しなければならず、また、低い直流抵抗値を具現するためにビア孔を大きく加工しなければならないが、このためには高価な設備が必要である。よって生産性が低下するという問題がある。

【発明の概要】

【発明が解決しようとする課題】

【0007】

本発明は、直流抵抗特性及びインピーダンス特性に優れた積層セラミック電子部品及び安くて生産性の高い積層セラミック電子部品の製造方法を提供することを目的とする。

【課題を解決するための手段】

【0008】

本発明が一実施形態である積層セラミック電子部品はセラミック本体と、上記セラミック本体の外部に形成された外部電極と、上記セラミック本体の内部にコイル構造を形成する内部導体とを含み、上記コイルの中心軸は上記外部電極を連結する方向と平行で、上記内部導体は上記コイルの中心軸と垂直に積層されたビア導体を含み、上記ビア導体の一面の面積に対する他面の面積の比は0.9以上1.1以下であってよい。

【0009】

上記ビア導体の積層方向から投影してみると、上記ビア導体は四角形又は円形であってよい。

【0010】

上記コイルの中心軸方向からみて、上記コイルは四角形であってよい。

【0011】

上記セラミック本体は磁性体を含んでよく、上記磁性体はフェライト材料を含むことができ、上記フェライト材料はニッケル−亜鉛−銅フェライトを含むことができる。

【0012】

上記内部導体は金、銀、銅、ニッケル、パラジウム及びこれらの合金からなるグループから選択された一つ以上を含んでよい。

【0013】

本発明の他の実施形態である積層セラミック電子部品の製造方法は、セラミックペーストを印刷してセラミックグリーンシートを用意する第1段階と、セラミックグリーンシート上に第1導電性ペーストを印刷して複数の第1導体を形成し、上記セラミックグリーンシートの上記第1導体を除いた部分にセラミックペーストを印刷する第2段階と、上記セラミックグリーンシート上に第2導電性ペーストを印刷して複数の上記第1導体の両端に接続されるように第1ビア導体を形成し、上記セラミックグリーンシートの複数の上記第1ビア導体を除いた部分に上記セラミックペーストを印刷する第3段階と、上記セラミックシート上に第2導電性ペーストを印刷して複数の上記第1ビア導体に相応する位置に複数の第2ビア導体を形成し、上記セラミックシートの複数の上記第2ビア導体を除いた部分に上記セラミックペーストを印刷する第4段階と、上記セラミックグリーンシート上に第1導電性ペーストを印刷して複数の上記第2ビア導体に接続されるように複数の第2導体を形成し、上記セラミックグリーンシートの複数の上記第2導体を除いた部分に上記セラミックペーストを印刷する第5段階と、上記セラミックグリーンシート上に上記セラミックペーストを印刷する第6段階を含んでよい。

【0014】

上記セラミックペーストは磁性体を含んでよい。

【0015】

上記磁性体はフェライトを含んでよい。

【0016】

上記フェライトはニッケル−亜鉛−銅フェライトを含んでよい。

【0017】

上記第1及び第2導電性ペーストは金、銀、銅、ニッケル、パラジウム及びこれらの合金を含むグループから選択された一つ以上を含んでよい。

【0018】

上記第1及び第2導電性ペーストは同じ材料を含んでよい。

【0019】

上記第1及び第2導体は帯状であってよい。

【0020】

上記第5段階の前に、上記第4段階を繰り返して行い柱状のビア導体を形成する段階をさらに含んでよい。

【0021】

上記ビア導体の積層方向において、上記ビア導体の一面の面積に対する上記ビア導体の他面の面積の比率は0.9以上1.1以下であってよい。

【0022】

上記ビア導体の積層方向から投影してみると、上記ビア導体は四角形又は円形であってよい。

【発明の効果】

【0023】

本発明によると、直流抵抗特性及びインピーダンス特性に優れ、且つ、安くて生産性の高い積層セラミック電子部品が得られる。

【図面の簡単な説明】

【0024】

【図1】本発明の一実施形態による積層セラミック電子部品の外観斜視図である。

【図2】本発明の一実施形態による積層セラミック電子部品の分解斜視図である。

【図3】本発明の一実施形態による積層セラミック電子部品の投影斜視図である。

【図4】(a)および(b)は本発明の一実施形態によるビア導体の平面図である。

【図5】(a)および(b)は本発明の一実施形態によるビア導体の概略図である。

【図6】本発明の一実施形態による積層セラミック電子部品の製造工程のフローチャートである。

【図7】本発明の一実施形態によるビア導体の製造工程の模式図である。

【図8】本発明の一実施形態による積層セラミック電子部品の製造工程の模式図である。

【発明を実施するための形態】

【0025】

以下では、添付の図面を参照して本発明の好ましい実施形態を説明する。

【0026】

但し、本発明の実施形態は様々な他の形態に変形されることができ、本発明の範囲は以下で説明する実施形態に限定されない。

【0027】

また、本発明の実施形態は当業界で平均的な知識を有する者に本発明をより完全に説明するために提供されるものである。

【0028】

従って、図面における要素の形状及び大きさなどはより明確な説明のために誇張されることがあり、図面上に同じ符号で示される要素は同じ要素である。

【0029】

図1から図3を参照し、本発明の一実施形態である積層セラミック電子部品について説明する。

【0030】

図1は本発明の一実施形態である積層セラミック電子部品の外観斜視図であり、図2は本発明の一実施形態である積層セラミック電子部品の分解斜視図であり、図3は本発明の一実施形態である積層セラミック電子部品の投影斜視図である。

【0031】

積層セラミック電子部品には積層セラミックキャパシタ、積層型チップインダクター、積層型チップビーズなどがあり、以下では、積層型チップインダクターを例に挙げて説明するが、本発明はこれに限定されない。

【0032】

本実施形態は、セラミック本体10、外部電極21、22、内部導体31、32、41、42を含むことができる。

【0033】

図1を参照すると、セラミック本体10は直方体形状を有することができる。「長さ方向」は「L」方向、「幅方向」は「W」方向、「厚さ方向」は「T」方向と定義することができる。ここで、「厚さ方向」はセラミック層を積層する方向、即ち、「積層方向」と同じ概念で使用することができる。

【0034】

セラミック本体10は透磁率の高い磁性材料を含んでよく、上記磁性材料はこれに制限されないが、フェライト系材料を使用することができ、具体的にはニッケル−銅−亜鉛フェライトを使用することができる。

【0035】

セラミック本体10は複数のセラミック層を積層した後に焼結させたもので、隣接するセラミック層同士は境界が確認できない程度一体化されていてもよい。

【0036】

外部電極21、22は、セラミック本体10の外部面に対向するように形成されてよい。

【0037】

外部電極21、22は導電性金属を含む導電性ペーストを利用して形成されてよく、これに制限されないが、導電性金属は金、銀、銅、ニッケル、パラジウム及びこれらの合金などを含むことができる。

【0038】

図2及び3を参照すると、内部導体はビア導体41、42と第1及び第2導体31、32を含んでよい。

【0039】

内部導体31、32、41、42はセラミック本体10の内部に形成され、コイル形状を有するように配置されてよい。

【0040】

内部導体がコイル形状を有するように配置されるため、内部導体に電流が流れると、内部導体31、32、41、42の周りには磁場が誘導されることができ、インダクターとしての機能を行うことができる。

【0041】

コイルの中心軸は、外部電極21、22を連結する方向と平行であってよい。即ち、コイルの中心軸はセラミック本体10の長さ方向(L方向)と平行であることができる。

【0042】

この構造では、内部導体31、32、41、42の間にのみ寄生容量が主に形成され、内部導体31、32、41、42と外部電極21、22の間に形成される寄生容量は非常に少ないため、インダクターの磁気共鳴周波数(SRF、Self Resonance Frequency)が増加し高周波Q特性が向上することができる。

【0043】

ビア導体41、42は複数が積層されてビア柱を形成してもよく、ビア導体41、42の積層方向はコイルの中心軸と垂直であることができる。

【0044】

図4は本発明の一実施形態によるビア導体41、42の平面図である。

【0045】

図4を参照すると、ビア導体41、42の平面は、四角形又は円形であってよい。

【0046】

図4(a)にはビア導体41、42の平面が円形である場合を示し、図4(b)にはビア導体41、42の平面が四角形である場合を示した。

【0047】

ビア導体41、42の平面が円形より四角形の場合に断面積が広いため、ビア導体41、42の直列抵抗をさらに減少させることができる。

【0048】

図5は本発明の一実施形態によるビア導体41、42の概略図である。

【0049】

図5(b)を参照すると、ビア導体41、42の断面が四角形の場合、ビア導体41、42の上面の長さ(X又はX’)に対する下面の長さ(Y又はY’)の比(Y/X、Y’/X’)は0.9以上1.1以下であってよい。

【0050】

ビア導体41、42の上面の長さ(X又はX’)に対する下面の長さ(Y又はY’)の比(Y/X、Y’/X’)が1.0の場合、電流の流れる通路が最も広いため、最も理想的である。しかし、製造工程の誤差によりこれを具現することは困難である。

【0051】

ビア導体41、42の上面の長さ(X又はX’)に対する下面の長さ(Y又はY’)の比(Y/X、Y’/X’)が0.9未満では、電流の流れる通路が狭くなるため、直列抵抗が高くなり過ぎることがある。

【0052】

ビア導体41、42の上面の長さ(X又はX’)に対する下面の長さ(Y又はY’)の比(Y/X、Y’/X’)が1.1以上の場合にも同様に電流の流れる通路が狭くなって直列抵抗が大きくなることがある。これはビア導体41、42の上面及び下面が逆になった場合も同様であるためである。

【0053】

図5(a)を参照すると、ビア導体41、42の断面が円形の場合には、ビア導体41、42の上面の直径(X)に対する下面の直径(Y)の比(Y/X)が0.9以上1.1以下であってよい。

【0054】

長さが直径に変わったことを除き、ビア導体41、42の断面が四角形の場合と同様である。

【0055】

コイルの中心軸方向から投影してみると、上記コイルは四角形であることができる。

【0056】

コイルはビア導体41、42を積層して形成するため、円形のコイルを製造することは実質的に困難である。

【0057】

円形のコイルを製造する場合は、隣接するビア導体41、42の位置がずれるように形成しなければならないため、ビア導体41、42間の連結が切れる虞がある。

【0058】

これを防止するために、ビア導体41、42とビア導体41、42の間にビアパッド(不図示)をさらに形成してもよいが、この場合、更なる工程を必要とするため、製造費用が増加するという問題があり、また、依然としてビア導体41、42とビア導体41、42の間の電気的連結が切れる虞がある。

【0059】

内部導体31、32、41、42は電気的に導電性を有する物質であれば、特に制限されない。但し、セラミック内で焼結されるという点を考慮し、融点の高い導電性金属を使用することができる。

【0060】

具体的には、内部導体は金、銀、銅、ニッケル、パラジウム及びこれらの合金からなる群から選択された何れか1つからなることができる。

【0061】

以下では、本発明の他の実施形態である積層セラミック電子部品の製造方法について説明する。

【0062】

図6は本発明の一実施形態による積層セラミック電子部品の製造工程のフローチャートであり、図7は本発明の一実施形態によるビア導体の製造工程の模式図であり、図8は本発明の一実施形態による積層セラミック電子部品の製造工程の模式図である。

【0063】

図3及び図6を参照すると、積層セラミック電子部品の製造方法は以下の通りである。

【0064】

第1段階S1では、セラミックペーストを印刷してセラミックグリーンシート11を用意することができる。

【0065】

先ず、セラミック粉末に有機溶媒、バインダーなどを混合した後、これをボールミリングなどをし、セラミック粉末が均一に分散されたセラミックペーストを製造することができる。

【0066】

ポリエチレンなどの高分子フィルム上にスクリーンプリントなどの方法でセラミックペーストを印刷し、これを乾燥してセラミックグリーンシート11を用意することができる。

【0067】

第2段階S2では、セラミックグリーンシート11上に第1導電性ペーストを印刷して複数の第1導体31を形成し、上記セラミックグリーンシート11の上記第1導体31を除いた部分にセラミックペーストを印刷してよい。

【0068】

第1導電性ペーストは、セラミック粉末の代わりに導電性金属を含むことを除き、上記セラミックペーストと同様にして用意することができる。但し、粘度などを調節するために有機溶媒及びバインダーなどの含量は異なってもよい。

【0069】

第1導電性ペーストをスクリーン印刷してセラミックグリーンシート11上に複数の第1導体31を形成することができる。スクリーン印刷の繰り返し回数を調節することで、第1導体31の厚さを調節することができ、第1導体が厚いほど直流抵抗(Rdc)が減少する。

【0070】

第1導体31が形成された領域を除いた部分には再びセラミックペーストを印刷してセラミック領域を形成してよい。これによって、セラミック領域の中央に第1導体31が形成されたセラミックグリーンシート12が得られる。

【0071】

第3段階S3では、セラミックグリーンシート12上に第2導電性ペーストを印刷して複数の上記第1導体31の両端に接続されるように第1ビア導体41を形成し、上記セラミックグリーンシート12の複数の上記第1ビア導体41を除いた部分に上記セラミックペーストを印刷してよい。

【0072】

第1導体31の両端に対応するように第1ビア導体41を印刷してよい。印刷回数によって第1ビア導体41の厚さを調節することができる。

【0073】

第1ビア導体41が形成された領域を除いた部分には再びセラミックペーストを印刷してセラミック領域を形成してよく、これによってビア導体41がセラミックグリーンシート上13に露出した状態となる。

【0074】

ビア導体41を印刷方式で形成するため、ビア導体41の上面及び下面の寸法を殆ど等しく保持することができ、積層されたビア導体41の直流抵抗(Rdc)を最小化することができる。

【0075】

電流の流れる通路は面積の小さい上面又は下面により決まるため、ビア導体41の上面及び下面の面積が異なると、電流の流れの通路が減少することがある。

【0076】

従って、ビア導体41の上面及び下面の面積を等しく保持することで、直流抵抗を減らすことができる。

【0077】

ビア孔を形成してから導電性ペーストで埋め込む場合は、ビア導体の上面及び下面の面積を等しく形成することが困難である。ビア孔を形成する際、ビア孔の寸法を一定に形成することが困難で、ビア孔を導電性ペーストで埋め込む過程でも製造工程上の誤差などによりビア導体の寸法を一定に形成することが困難である。

【0078】

従って、ビア孔を形成してから導電性ペーストで埋め込むと、直流抵抗を減少させるのに限界がある。

【0079】

本実施形態では、このような問題を解決するために、ビア導体41、42を先ず形成した後、上記ビア導体41、42が形成された領域を除いた部分にセラミックペーストを印刷してセラミック領域を形成する。こうすることで、ビア導体41、42の寸法を安定的に形成することができる。

【0080】

即ち、ビア導体41、42の上面及び下面の面積を等しくしてビア導体41、42の直流抵抗を最大限減らすことができる。

【0081】

第4段階S4は、上記セラミックグリーンシート13上に第2導電性ペーストを印刷して複数の上記第1ビア導体41に相応する位置に複数の第2ビア導体42を形成し、上記セラミックグリーンシート13の複数の上記第2ビア導体42を除いた部分に上記セラミックペーストを印刷してよい。

【0082】

第4段階はビア柱を形成する工程であって、既に形成されたビア導体41に対応するように第2導電性ペーストを印刷して第2ビア導体42を形成してよい。第2ビア導体42が形成された領域を除いた領域にはセラミックペーストを印刷してセラミック領域を形成してよい。

【0083】

第4段階を数回繰り返して所望する高さのビア柱を形成することができる。

【0084】

第1導体31及び柱状のビア導体41、42により「U」字型の導体が並んで配置されている構造となり、各「U」字型の導体同士は分離されている。

【0085】

第5段階S5では、上記セラミックグリーンシート14上に第1導電性ペーストを印刷して複数の上記第2ビア導体42に接続されるように複数の第2導体32を形成し、上記セラミックグリーンシート14の複数の上記第2導体が形成された領域を除いた領域に上記セラミックペーストを印刷してセラミック領域を形成してよい。

【0086】

既に形成されているビア導体42に両端が接続されるように第2導体32を形成してよい。第2導体32は第1導電性ペースを印刷して形成してよい。

【0087】

第2導体32は、第5段階で形成された「U」字形の導体を相互電気的に連結して螺旋形のコイルを形成する役割をする。

【0088】

第5段階を経てコイルが完成される。

【0089】

第6段階S6では、上記セラミックグリーンシート15上に上記セラミックペーストを印刷してよい。

【0090】

既に形成された複数の第2導体32を完全に囲むようにセラミックペーストを印刷することで、第2導体32を外部から保護することができる。

【0091】

上記した内容とは異なって、第1段階は行わなくてもよい。

【0092】

図7を参照すると、高分子樹脂などのベース1上に第2から第5段階のみを行って柱状の積層ビアを形成した後、ベース1を除去しその上下にセラミックペーストを印刷してもよい。

【0093】

また、図8を参照すると、ロールツーロール工法により連続的に製造することもできる。図6の第2から第5段階(S2〜S6)を行って柱状の積層ビア導体を形成してもよい。

【0094】

セラミックペーストは磁性体を含んでよく、磁性体はフェライトを含むことができ、フェライトはニッケル−亜鉛−銅フェライトを含むことができる。

【0095】

第1及び第2導電性ペーストは金、銀、銅、ニッケル、パラジウム及びこれらの合金からなるグループから選択された何れか一つ以上を含んでよい。

【0096】

第1及び第2導電性ペーストは同じ材料を含んでよい。

【0097】

第1導電性ペーストでは第1及び第2導体を形成し、第2導電性ペーストでは複数のビア導体を形成するため、第1及び第2導電性ペーストが同一であり、第1及び第2導体とビア導体間の機械的接続及び電気的接続がさらに安定的であることができる。

【0098】

第1及び第2導体は帯状であってよい。

【0099】

第5段階の前に、第4段階を繰り返して行い柱状のビア導体を形成する段階をさらに含んでよい。

【0100】

ビア導体の積層方向において、ビア導体の一面の面積に対する上記ビア導体の他面の面積の比率は0.9以上1.1以下であってよい。

【0101】

上記ビア導体の積層方向から投影してみると、上記ビア導体は四角形又は円形であってよい。

【0102】

セラミックは磁性材料、ガラス材料及び誘電材料のうち何れか一つであってよい。

【0103】

ビア導体、セラミック材料に関する内容は上述と同一である。

【実施例】

【0104】

以下では、具体的な実施例を挙げて発明について詳細に説明する。

【0105】

先ず、ニッケル−亜鉛−銅フェライト粉末、有機溶媒としてエタノール、バインダーとしてエチルセルロースを混合した後、これを3−ロールミリングしてセラミックペーストを用意し、また、銀(Ag)粉末を含む導電性ペーストを用意した。

【0106】

次いで、セラミックペーストをポリエチレンフィルム上にスクリーン印刷してセラミックグリーンシートを製造した後、乾燥させた。

【0107】

次に、導電性ペーストを利用してセラミックグリーンシート上に帯状の第1導体を7個形成し、帯状の導体を除いた領域にセラミックペーストを印刷してセラミック領域を形成した。

【0108】

7個の帯状の導体の両端に対応するように導電性ペーストを印刷してビア導体を形成し、ビア導体を除いた領域にセラミックペーストを印刷してセラミック領域を形成した。

【0109】

ビア導体の断面は一辺が50μmである正方形となるようにした。

【0110】

この過程を10回〜40回繰り返してビア導体柱を形成した。

【0111】

次に、ビア導体と接続されるように帯状の複数の第2導体を印刷してコイル構造を形成した。

【0112】

次いで、第2導体を囲むようにセラミックペーストを印刷した。

【0113】

上記製造方法により製造された積層型インダクターに対し直流抵抗値を測定した。

【0114】

直流抵抗はAgilent 4338Bミリオームメータを利用して測定した。

【0115】

比較例ではセラミックグリーンシートにビア孔を形成した後、導電性ペーストを埋め込んでビア導体を形成し、これを積層してビア柱を形成した点を除き、実施例と同じ方法で製造した。

【0116】

実施例及び比較例に対する直流抵抗(Rdc)を測定した結果を表1に示した。

【0117】

比較例の場合、ビア導体の上面の長さに対する下面の長さの比率は0.7、0.8、1.2、1.3となるようにした。

【0118】

実施例の場合、ビア導体の上面の面積に対する下面の面積の比率は0.95〜1.05の範囲に属している。

【0119】

【表1】

【0120】

表1において、Xはビア導体の上面の長さで、Yはビア導体の下面の長さで、Y/Xはビア導体の上面の長さに対する下面の長さの比率である。

【0121】

表1を参照すると、比較例1、2はY/Xが[0.7]、[0.8]の場合であって、Rdc値が[1.4]、[1.25]で、実施例1、2、3はY/Xが[0.9]、[1.0]、[1.1]の場合であって、Rdc値が[1.15]、[1.10]、[1.11]で、比較例3、4はY/Xが[1.2]、[1.3]の場合であって、Rdc値が[1.22]、[1.34]である。

【0122】

表1の結果によると、Y/Xが[0.9]、[1.0]、[1.1]の場合、Rdc値が小さいことが分かる。

【0123】

本発明は上述した実施形態及び添付の図面により限定されず、添付の請求範囲により限定する。

【0124】

従って、請求の範囲に記載された本発明の技術的思想から外れない範囲内で当技術分野の通常の知識を有する者により多様な形態の置換、変形及び変更が可能であり、これも本発明の範囲に属する。

【符号の説明】

【0125】

10 セラミック本体

11〜16 セラミック層

31 第1導体

32 第2導体

40、41、42 ビア導体

21、22 外部電極

X、X’ ビア導体の上面の直径又は長さ

Y、Y’ ビア導体の下面の直径又は長さ

X−X’面 ビア導体の上面

Y−Y’面 ビア導体の下面

【特許請求の範囲】

【請求項1】

セラミック本体と、

前記セラミック本体の外部に形成された外部電極と、

前記セラミック本体の内部にコイル構造を形成する内部導体とを含み、

前記コイルの中心軸は前記外部電極を連結する方向と平行で、

前記内部導体は前記コイルの中心軸と垂直に積層されたビア導体を含み、前記ビア導体の一面の面積に対する他面の面積の比は0.9以上1.1以下である積層セラミック電子部品。

【請求項2】

前記ビア導体の積層方向から投影してみると、前記ビア導体は四角形又は円形である請求項1に記載の積層セラミック電子部品。

【請求項3】

前記コイルの中心軸方向からみて、前記コイルは四角形である請求項1に記載の積層セラミック電子部品。

【請求項4】

前記セラミック本体は、磁性体を含む請求項1に記載の積層セラミック電子部品。

【請求項5】

前記磁性体は、フェライト材料を含む請求項4に記載の積層セラミック電子部品。

【請求項6】

前記フェライト材料は、ニッケル−亜鉛−銅フェライトを含む請求項5に記載の積層セラミック電子部品。

【請求項7】

前記内部導体は金、銀、銅、ニッケル、パラジウム及びこれらの合金からなるグループから選択された一つ以上を含む請求項1に記載の積層セラミック電子部品。

【請求項8】

セラミックペーストを印刷してセラミックグリーンシートを用意する第1段階と、

セラミックグリーンシート上に第1導電性ペーストを印刷して複数の第1導体を形成し、前記セラミックグリーンシートの前記第1導体を除いた部分にセラミックペーストを印刷する第2段階と、

前記セラミックグリーンシート上に第2導電性ペーストを印刷して複数の前記第1導体の両端に接続されるように第1ビア導体を形成し、前記セラミックグリーンシートの複数の前記第1ビア導体を除いた部分に前記セラミックペーストを印刷する第3段階と、

前記セラミックシート上に第2導電性ペーストを印刷して複数の前記第1ビア導体に相応する位置に複数の第2ビア導体を形成し、前記セラミックシートの複数の前記第2ビア導体を除いた部分に前記セラミックペーストを印刷する第4段階と、

前記セラミックグリーンシート上に第1導電性ペーストを印刷して複数の前記第2ビア導体に接続されるように複数の第2導体を形成し、前記セラミックグリーンシートの複数の前記第2導体を除いた部分に前記セラミックペーストを印刷する第5段階と、

前記セラミックグリーンシート上に前記セラミックペーストを印刷する第6段階と、

を含む積層セラミック電子部品の製造方法。

【請求項9】

前記セラミックペーストは、磁性体を含む請求項8に記載の積層セラミック電子部品の製造方法。

【請求項10】

前記磁性体は、フェライトを含む請求項9に記載の積層セラミック電子部品の製造方法。

【請求項11】

前記フェライトは、ニッケル−亜鉛−銅フェライトを含む請求項10に記載の積層セラミック電子部品の製造方法。

【請求項12】

前記第1及び第2導電性ペーストは金、銀、銅、ニッケル、パラジウム及びこれらの合金を含むグループから選択された一つ以上を含む請求項8に記載の積層セラミック電子部品の製造方法。

【請求項13】

前記第1及び第2導電性ペーストは、同じ材料を含む請求項8に記載の積層セラミック電子部品の製造方法。

【請求項14】

前記第1及び第2導体は帯状である請求項8に記載の積層セラミック電子部品の製造方法。

【請求項15】

前記第5段階の前に、前記第4段階を繰り返して行い柱状のビア導体を形成する段階をさらに含む請求項8に記載の積層セラミック電子部品の製造方法。

【請求項16】

前記ビア導体の積層方向において、前記ビア導体の一面の面積に対する前記ビア導体の他面の面積の比率は0.9以上1.1以下である請求項8に記載の積層セラミック電子部品の製造方法。

【請求項17】

前記ビア導体の積層方向から投影してみると、前記ビア導体は四角形又は円形である請求項8に記載の積層セラミック電子部品の製造方法。

【請求項1】

セラミック本体と、

前記セラミック本体の外部に形成された外部電極と、

前記セラミック本体の内部にコイル構造を形成する内部導体とを含み、

前記コイルの中心軸は前記外部電極を連結する方向と平行で、

前記内部導体は前記コイルの中心軸と垂直に積層されたビア導体を含み、前記ビア導体の一面の面積に対する他面の面積の比は0.9以上1.1以下である積層セラミック電子部品。

【請求項2】

前記ビア導体の積層方向から投影してみると、前記ビア導体は四角形又は円形である請求項1に記載の積層セラミック電子部品。

【請求項3】

前記コイルの中心軸方向からみて、前記コイルは四角形である請求項1に記載の積層セラミック電子部品。

【請求項4】

前記セラミック本体は、磁性体を含む請求項1に記載の積層セラミック電子部品。

【請求項5】

前記磁性体は、フェライト材料を含む請求項4に記載の積層セラミック電子部品。

【請求項6】

前記フェライト材料は、ニッケル−亜鉛−銅フェライトを含む請求項5に記載の積層セラミック電子部品。

【請求項7】

前記内部導体は金、銀、銅、ニッケル、パラジウム及びこれらの合金からなるグループから選択された一つ以上を含む請求項1に記載の積層セラミック電子部品。

【請求項8】

セラミックペーストを印刷してセラミックグリーンシートを用意する第1段階と、

セラミックグリーンシート上に第1導電性ペーストを印刷して複数の第1導体を形成し、前記セラミックグリーンシートの前記第1導体を除いた部分にセラミックペーストを印刷する第2段階と、

前記セラミックグリーンシート上に第2導電性ペーストを印刷して複数の前記第1導体の両端に接続されるように第1ビア導体を形成し、前記セラミックグリーンシートの複数の前記第1ビア導体を除いた部分に前記セラミックペーストを印刷する第3段階と、

前記セラミックシート上に第2導電性ペーストを印刷して複数の前記第1ビア導体に相応する位置に複数の第2ビア導体を形成し、前記セラミックシートの複数の前記第2ビア導体を除いた部分に前記セラミックペーストを印刷する第4段階と、

前記セラミックグリーンシート上に第1導電性ペーストを印刷して複数の前記第2ビア導体に接続されるように複数の第2導体を形成し、前記セラミックグリーンシートの複数の前記第2導体を除いた部分に前記セラミックペーストを印刷する第5段階と、

前記セラミックグリーンシート上に前記セラミックペーストを印刷する第6段階と、

を含む積層セラミック電子部品の製造方法。

【請求項9】

前記セラミックペーストは、磁性体を含む請求項8に記載の積層セラミック電子部品の製造方法。

【請求項10】

前記磁性体は、フェライトを含む請求項9に記載の積層セラミック電子部品の製造方法。

【請求項11】

前記フェライトは、ニッケル−亜鉛−銅フェライトを含む請求項10に記載の積層セラミック電子部品の製造方法。

【請求項12】

前記第1及び第2導電性ペーストは金、銀、銅、ニッケル、パラジウム及びこれらの合金を含むグループから選択された一つ以上を含む請求項8に記載の積層セラミック電子部品の製造方法。

【請求項13】

前記第1及び第2導電性ペーストは、同じ材料を含む請求項8に記載の積層セラミック電子部品の製造方法。

【請求項14】

前記第1及び第2導体は帯状である請求項8に記載の積層セラミック電子部品の製造方法。

【請求項15】

前記第5段階の前に、前記第4段階を繰り返して行い柱状のビア導体を形成する段階をさらに含む請求項8に記載の積層セラミック電子部品の製造方法。

【請求項16】

前記ビア導体の積層方向において、前記ビア導体の一面の面積に対する前記ビア導体の他面の面積の比率は0.9以上1.1以下である請求項8に記載の積層セラミック電子部品の製造方法。

【請求項17】

前記ビア導体の積層方向から投影してみると、前記ビア導体は四角形又は円形である請求項8に記載の積層セラミック電子部品の製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【公開番号】特開2013−106030(P2013−106030A)

【公開日】平成25年5月30日(2013.5.30)

【国際特許分類】

【出願番号】特願2012−6813(P2012−6813)

【出願日】平成24年1月17日(2012.1.17)

【出願人】(594023722)サムソン エレクトロ−メカニックス カンパニーリミテッド. (1,585)

【Fターム(参考)】

【公開日】平成25年5月30日(2013.5.30)

【国際特許分類】

【出願日】平成24年1月17日(2012.1.17)

【出願人】(594023722)サムソン エレクトロ−メカニックス カンパニーリミテッド. (1,585)

【Fターム(参考)】

[ Back to top ]