積層セラミック電子部品及びその製造方法

【課題】固着強度を高めて曲がりクラックを防止できる積層セラミック電子部品及びその製造方法を提供する。

【解決手段】本発明による積層セラミック電子部品は、複数の誘電体層が積層されたセラミック素体10と、セラミック素体10内で複数の誘電体層の少なくとも一面に形成され、セラミック素体10の一面から露出する第1及び第2内部電極21,22と、セラミック素体10の一面に形成され、第1及び第2内部電極21,22の露出部により第1及び第2内部電極21,22とそれぞれ電気的に接続される第1及び第2外部電極31,32とを含み、セラミック素体10の一面の広さに対する第1又は第2外部電極31,32の広さの比が10〜40%である。

【解決手段】本発明による積層セラミック電子部品は、複数の誘電体層が積層されたセラミック素体10と、セラミック素体10内で複数の誘電体層の少なくとも一面に形成され、セラミック素体10の一面から露出する第1及び第2内部電極21,22と、セラミック素体10の一面に形成され、第1及び第2内部電極21,22の露出部により第1及び第2内部電極21,22とそれぞれ電気的に接続される第1及び第2外部電極31,32とを含み、セラミック素体10の一面の広さに対する第1又は第2外部電極31,32の広さの比が10〜40%である。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、積層セラミック電子部品及びその製造方法に関する。

【背景技術】

【0002】

セラミック材料を用いる電子部品としては、キャパシタ、インダクタ、圧電素子、バリスタ、又はサーミスタなどがある。

【0003】

このようなセラミック電子部品の1つである積層セラミックキャパシタ(MLCC:Multi−Layered Ceramic Capacitor)は、小型ながらも高容量が保証され、実装が容易であるという利点を有する。

【0004】

このような積層セラミックキャパシタは、コンピュータ、個人用の携帯情報端末(PDA:Personal Digital Assistants)、又は携帯電話などの様々な電子製品の回路基板に取り付けられて充放電を行う重要な役割を果たすチップ型コンデンサであって、使用される用途及び容量によって様々なサイズと積層形態を有する。

【0005】

特に、近年、電子製品が小型化するにつれて、電子製品に使用される積層セラミックキャパシタにも超小型化及び超高容量化が求められている。

【0006】

よって、製品の超小型化のために誘電体層及び内部電極の厚さを薄くし、超高容量化のために多数の誘電体層を積層した積層セラミックキャパシタが製造されている。

【0007】

一方、外部電極の全てが下面に位置する積層セラミックキャパシタがあるが、このような構造の積層セラミックキャパシタは、実装密度及び容量に優れてESLが低いという利点を有するが、固着強度が低く、積層体の一面が曲がってクラックが発生しやすいという欠点がある。

【発明の概要】

【発明が解決しようとする課題】

【0008】

当該技術分野においては、下面電極を用いる積層セラミックキャパシタの固着強度を高めて、曲がりクラックを防止することのできる新たな方法が求められてきた。

【課題を解決するための手段】

【0009】

本発明の一態様は、複数の誘電体層が積層されたセラミック素体と、前記セラミック素体内で前記複数の誘電体層の少なくとも一面に形成され、前記セラミック素体の一面から露出する第1及び第2内部電極と、前記セラミック素体の一面に形成され、前記第1及び第2内部電極の露出部により前記第1及び第2内部電極とそれぞれ電気的に接続される第1及び第2外部電極とを含み、前記セラミック素体の一面の広さに対する前記第1又は第2外部電極の広さの比が10〜40%である、積層セラミック電子部品を提供する。

【0010】

本発明の他の態様によれば、前記セラミック素体の一面の長さに対する前記第1又は第2外部電極と前記セラミック素体の先端との間隔の比が4〜18%でもよい。

【0011】

本発明の一実施形態においては、前記第1及び第2外部電極の広さが同じでもよい。

【0012】

本発明の一実施形態においては、前記第1及び第2外部電極の広さが異なっていてもよい。

【0013】

本発明の一実施形態においては、前記第1外部電極と前記セラミック素体の一側先端との間隔が、前記第2外部電極と前記セラミック素体の対向する先端との間隔と同じでもよい。

【0014】

本発明の一実施形態においては、前記第1外部電極と前記セラミック素体の一側先端との間隔が、前記第2外部電極と前記セラミック素体の対向する先端との間隔と異なっていてもよい。

【0015】

本発明の一実施形態において、前記第1及び第2外部電極は、前記セラミック素体の長手方向に対して一方に偏って形成されてもよい。

【0016】

本発明の一実施形態において、前記第1及び第2外部電極は、前記セラミック素体の中央に左右対称に形成されてもよい。

【0017】

本発明の一実施形態において、前記第1及び第2外部電極は、前記セラミック素体の全てのマージン部が同じ幅で形成されてもよい。

【0018】

本発明のさらに他の態様は、第1及び第2セラミックシートの少なくとも一面に第1及び第2内部電極膜を形成する段階と、前記第1及び第2内部電極膜がそれぞれ形成された前記第1及び第2セラミックシートを交互に積層して積層体を形成する段階と、前記積層体を焼成する段階と、前記第1及び第2内部電極膜と電気的に接続されるように、前記積層体の両側面に第1及び第2外部電極を形成する段階とを含み、前記セラミック素体の一面の広さに対する前記第1又は第2外部電極の広さの比が10〜40%になるようにする、積層セラミック電子部品の製造方法を提供する。

【0019】

本発明のさらに他の態様によれば、前記セラミック素体の一面の長さに対する前記第1又は第2外部電極と前記セラミック素体の先端との間隔の比が4〜18%になるように調節してもよい。

【0020】

本発明の一実施形態において、前記第1外部電極及び前記第2外部電極は、その広さが同じ広さになるように形成してもよい。

【0021】

本発明の一実施形態において、前記第1外部電極及び前記第2外部電極は、その広さが異なる広さになるように形成してもよい。

【0022】

本発明の一実施形態において、前記第1外部電極と前記セラミック素体の一側先端との間隔は、前記第2外部電極と前記セラミック素体の対向する先端との間隔と同じ間隔になるように形成してもよい。

【0023】

本発明の一実施形態において、前記第1外部電極と前記セラミック素体の一側先端との間隔は、前記第2外部電極と前記セラミック素体の対向する先端との間隔と異なる間隔になるように形成してもよい。

【0024】

本発明の一実施形態において、前記第1及び第2外部電極は、前記セラミック素体の長手方向に対して一方に偏るように形成してもよい。

【0025】

本発明の一実施形態において、前記第1及び第2外部電極は、前記セラミック素体の中央に左右対称となるように形成してもよい。

【0026】

本発明の一実施形態において、前記第1及び第2外部電極は、前記セラミック素体の全てのマージン部が同じ幅になるように形成してもよい。

【発明の効果】

【0027】

本発明の一実施形態によれば、外部電極の大きさを調節することにより、下面構造の積層セラミック電子部品の固着強度を高めて曲がりクラックを防止することができるという効果がある。

【図面の簡単な説明】

【0028】

【図1】本発明の一実施形態による積層セラミックキャパシタの概略的な構造を示す斜視図である。

【図2】図1の積層セラミックキャパシタの分解斜視図である。

【図3】図1の積層セラミックキャパシタにおける第1内部電極と第1外部電極の結合構造を示す断面図である。

【図4】図1の積層セラミックキャパシタにおける第2内部電極と第2外部電極の結合構造を示す断面図である。

【図5】図1の積層セラミックキャパシタにおける第1及び第2内部電極と第1及び第2外部電極の結合構造を示す断面図である。

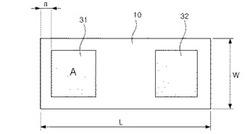

【図6】図1の積層セラミックキャパシタの正面図である。

【発明を実施するための形態】

【0029】

以下、添付図面を参照して本発明の好ましい実施形態を説明する。

【0030】

しかしながら、本発明の実施形態は様々な他の形態に変形することができ、本発明の範囲が後述する実施形態に限定されるものではない。

【0031】

また、本発明の実施形態は、当該技術分野における通常の知識を有する者に本発明をより完全に説明するために提供されるものである。

【0032】

よって、図面において、構成要素の形状及び大きさなどはより明確な説明のために誇張することもあり、同一の構成要素には同一の符号が付される。

【0033】

なお、類似の機能及び作用を果たす部分には、図面全体にわたって同一の符号が付される。

【0034】

また、明細書全体にわたって、ある構成要素を「含む」とは、特に断らない限り、他の構成要素を除くのではなく、他の構成要素をさらに含むことがあることを意味する。

【0035】

本発明は、セラミック電子部品に関し、本発明の一実施形態によるセラミック電子部品としては、積層セラミックキャパシタ、インダクタ、圧電素子、バリスタ、チップ抵抗、又はサーミスタなどがある。以下、セラミック電子部品の一例として積層セラミックキャパシタについて説明する。

【0036】

なお、本実施形態においては、説明の便宜上、セラミック素体に外部電極が形成された方向を正方向とし、内部電極の長側面に沿う方向を左右方向として説明する。

【0037】

図1〜図6に示すように、本実施形態による積層セラミックキャパシタ1は、複数の誘電体層が積層されたセラミック素体10と、セラミック素体10内で前記複数の誘電体層の少なくとも一面に形成され、セラミック素体10の一面から露出する第1及び第2内部電極21、22と、セラミック素体10の一面に形成され、第1及び第2内部電極21、22の露出部により第1及び第2内部電極21、22とそれぞれ電気的に接続する第1及び第2外部電極31、32とを含む。

【0038】

ここで、第1及び第2外部電極31、32が形成されたセラミック素体10の正方向の側面の広さに対する第1又は第2外部電極31、32の広さの比は、10〜40%にしてもよい。

【0039】

このような数値の詳細については、具体的な実施例と比較例を挙げて後述する。

【0040】

本実施形態の積層セラミックキャパシタは2端子垂直積層型キャパシタでもよい。

【0041】

「2端子(2−terminal)」とは、キャパシタの端子として2つの端子が回路基板に接続されることを意味し、「垂直積層型(vertically laminated or vertical multilayer)」とは、キャパシタ内の積層された内部電極が回路基板の実装領域面に垂直に配置されることを意味する。

【0042】

このような構造により、第1及び第2内部電極21、22は、セラミック素体10の正方向の側面から露出するように延設された第1及び第2リード部23、24をそれぞれ有する。

【0043】

すなわち、セラミック素体10の正方向の側面に形成された第1及び第2外部電極31、32は、第1及び第2リード部23、24の露出した部分に接続し、これにより第1及び第2内部電極21、22とそれぞれ電気的に接続することができる。

【0044】

セラミック素体10は、複数の誘電体層を積層して形成してもよい。

【0045】

ここで、セラミック素体10を構成する複数の誘電体層は、焼結された状態であって、隣接する誘電体層間の境界を確認できない程度に一体化されていてもよい。

【0046】

また、セラミック素体10は、その形状に特に制限はないが、一般に直方体形状でもよい。

【0047】

また、セラミック素体10は、その寸法に特に制限はないが、そのサイズを例えば0.6mm×0.3mmなどにすることにより、1.0μF以上の高容量を有する積層セラミックキャパシタ1を構成してもよい。

【0048】

さらに、必要に応じては、セラミック素体10の最外面(図における上下面)に所定厚さの誘電体カバー層(図示せず)を形成してもよい。

【0049】

このようなセラミック素体10を構成する誘電体層は、セラミック粉末、例えばBaTiO3系セラミック粉末などを含んでもよい。

【0050】

BaTiO3系セラミック粉末としては、BaTiO3にCa又はZrなどが一部固溶した(Ba1−xCax)TiO3、Ba(Ti1−yCay)O3、(Ba1−xCax)(Ti1−yZry)O3、又はBa(Ti1−yZry)O3などがあり、これに限定されるものではない。

【0051】

セラミック粉末の平均粒径は、0.8μm以下でもよく、好ましくは0.05〜0.5μmでもよいが、本発明がこれに限定されるものではない。

【0052】

誘電体層は、必要に応じて、セラミック粉末と共に、遷移金属酸化物もしくは炭化物、希土類元素、又はMg、Alの少なくとも1つをさらに含んでもよい。

【0053】

また、誘電体層の厚さは、積層セラミックキャパシタ1の容量設計によって任意に変更することができる。

【0054】

本実施形態における各誘電体層の厚さは、1.0μm以下でもよく、好ましくは0.01〜1.0μmでもよいが、本発明がこれに限定されるものではない。

【0055】

第1及び第2内部電極21、22は、導電性金属を含む導電性ペーストにより形成してもよい。

【0056】

ここで、導電性金属は、Ni、Cu、Pd、又はこれらの合金でもよいが、本発明がこれに限定されるものではない。

【0057】

このような第1及び第2内部電極21、22は、スクリーン印刷法又はグラビア印刷法などの印刷法により、誘電体層を形成するセラミックグリーンシート上に導電性ペーストで内部電極層を印刷し、その内部電極層が印刷されたセラミックグリーンシートを交互に積層した後に焼成することにより、セラミック素体10に形成することができる。

【0058】

従って、このように第1及び第2内部電極21、22が重なる領域により静電容量が形成される。

【0059】

また、第1及び第2内部電極21、22の厚さは用途に応じて決定され、例えばセラミック素体10のサイズを考慮して0.2〜1.0μmの範囲内で決定してもよいが、本発明がこれに限定されるものではない。

【0060】

このように誘電体層に第1及び第2内部電極21、22を形成する際に、水分やめっき液などが内部に浸透することを防止し、電気的な短絡を防止するために、誘電体層と第1及び第2内部電極21、22との間には所定のマージン部を残しておく。

【0061】

そして、第1及び第2内部電極21、22と誘電体層の側面に形成された異なる極性の第1及び第2外部電極31、32とを電気的に接続するために、誘電体層のマージン部に第1及び第2リード部23、24を第1及び第2内部電極21、22の一面から正方向に形成してもよい。

【0062】

第1及び第2リード部23、24の端部は、セラミック素体10の正方向の側面から露出させてもよい。

【0063】

ここで、第1及び第2リード部23、24は、それぞれ異なる極性を示す第1及び第2外部電極31、32にのみ接続するように、互いに重なる領域を有してはならない。

【0064】

つまり、第1及び第2リード部23、24は、第1及び第2内部電極21、22の長側面に沿って左右交互に配置されてもよい。

【0065】

ここで、第1及び第2リード部23、24の幅は同じ幅にすることが好ましいが、本発明がこれに限定されるものではなく、必要に応じて、第1及び第2リード部23、24の幅が異なる幅になるようにしてもよい。

【0066】

また、第1及び第2リード部23、24の厚さは、第1及び第2内部電極21、22と同じ厚さにすることが好ましい。

【0067】

例えば、本実施形態においては、第1及び第2内部電極21、22の厚さが0.2〜1.0μmであるので、第1及び第2リード部23、24の厚さも0.2〜1.0μmにするが、本発明がこれに限定されるものではない。

【0068】

本実施形態において、第1及び第2外部電極31、32は、セラミック素体10の正方向の側面にのみ形成される。

【0069】

従って、左右に外部電極が形成される他の構造に比べて全体的な実装面積が相対的に減少するので、回路基板の実装密度を向上させることができる。

【0070】

ここで、回路基板の実装密度がさらに向上するように、第1及び第2内部電極21、22を第1及び第2外部電極31、32が形成された方向に対して垂直方向に沿って積層して構成することがより好ましい。

【0071】

前述したように、第1及び第2外部電極31、32が形成されたセラミック素体10の正方向の側面の広さに対する第1又は第2外部電極31、32の広さの比は、10〜40%にしてもよい。

【0072】

ここで、第1及び第2外部電極31、32は、同じ広さになるように形成することが好ましいが、本発明がこれに限定されるものではなく、前記数値を満たす範囲内で異なる広さになるように形成してもよい。

【0073】

また、固着強度を高めて曲がりクラックを防止するために、セラミック素体10の一面の長さLに対する第1又は第2外部電極31、32とセラミック素体10の先端との間隔aの比は、4〜18%に調節してもよい。

【0074】

ここで、第1外部電極31とセラミック素体10の一側先端との間隔は、第2外部電極32とセラミック素体10の対向する先端との間隔と同じ間隔になるように形成してもよいが、本発明がこれに限定されるものではなく、前記数値を満たす範囲内で両側マージン部の間隔が異なる間隔になるように形成してもよい。

【0075】

すなわち、第1及び第2外部電極31、32は、セラミック素体10の中央に左右対称に配置してもよく、必要に応じて、セラミック素体10の左右長手方向に対して一方に偏るように形成してもよい。

【0076】

また、必要に応じて、第1及び第2外部電極31、32とセラミック素体10の正方向の側面に対する上下左右の全てのマージン部の幅が同じ幅になるように形成してもよい。

【0077】

一方、第1及び第2外部電極31、32は、上下に積層された複数の第1及び第2内部電極21、22と安定して接続されるように、セラミック素体10に対応する高さで形成してもよい。

【0078】

しかしながら、本発明がこれに限定されるものではなく、必要に応じて、第1及び第2外部電極31、32は、セラミック素体10より高く形成してもよく、低く形成してもよい。

【0079】

また、第1及び第2外部電極31、32は、めっき液の浸透を防止するために、第1及び第2リード部23、24が左右方向の中央に位置するように形成してもよい。

【0080】

本出願人は、セラミック素体10の一側面の広さに対する第1又は第2外部電極31、32の広さの比を調節して、固着強度を高めながらも曲がりクラックを防止できる範囲を確認した。

【0081】

セラミック素体10の一側面の広さに対する第1又は第2外部電極31、32の広さの比が10%未満の場合は、固着強度が低下することがあり、セラミック素体10の一側面の広さに対する第1又は第2外部電極31、32の広さの比が40%を超える場合は、第1及び第2外部電極31、32が形成されるセラミック素体10一面のマージン部が小さすぎるため、デラミネーション(層間剥離)が発生して曲がりクラックが発生し得る。

【0082】

従って、セラミック素体10の一側面の広さに対する第1又は第2外部電極31、32の広さの比の範囲は、10〜40%にすることが好ましい。

【0083】

以下、具体的な実施例と比較例を挙げて本発明をより詳細に説明する。

【0084】

前述したように、第1又は第2外部電極31、32の広さをA、セラミック素体10の長さ及び幅をそれぞれL及びW、第1又は第2外部電極31、32とセラミック素体10の先端との間隔をaとし、下記表1〜3のように積層セラミックキャパシタの特性を測定した。

【0085】

厚さ2μmの成形シートに第1及び第2リード部23、24を有する第1及び第2内部電極21、22、並びに第1及び第2外部電極31、32を各サイズに印刷してチップを製作し、評価を行った。

【0086】

下記表1においては、セラミック素体10の一面の長さLを0.4mm、幅Wを0.2mmとし、第1又は第2外部電極31、32の広さAを様々に変更した。

【0087】

その後、複数のチップのうち、第1又は第2外部電極31、32と第1又は第2リード部23、24との電気的接続が切断されたり、デラミネーションが発生したチップの数と、固着強度数値をそれぞれ確認した。

【0088】

<セラミック素体及び外部電極のスペックによる積層セラミックキャパシタの特性>

【表1】

【0089】

表1を参照すると、サンプル1及びサンプル2は、比較例であって、セラミック素体10の一面の広さに対する第1又は第2外部電極31、32の広さの比が10%未満のものを示す。この場合、固着強度が低いため、第1又は第2外部電極31、32と第1又は第2リード部23、24との接続が切断された不良製品が多数発見されたことから、信頼性に問題があることが分かる。

【0090】

また、サンプル8及びサンプル9は、比較例であって、セラミック素体10の一面の広さに対する第1又は第2外部電極31、32の広さの比が40%を超えるものを示す。この場合、第1又は第2外部電極31、32と第1又は第2リード部23、24との接続に関する問題は発見されなかったが、セラミック素体10のマージン部が減少してデラミネーションが発生した不良製品が多数発見されたことから、信頼性に問題があることが分かる。

【0091】

<セラミック素体及び外部電極のスペックによる積層セラミックキャパシタの特性>

【表2】

【0092】

表2においては、セラミック素体10の一面の長さLを0.6mm、幅Wを0.3mmとする一方、第1又は第2外部電極31、32の広さAを様々なものに変更した。そして、これらの複数のチップのうち、第1又は第2外部電極31、32と第1又は第2リード部23、24との電気的接続が切断されたり、デラミネーションが発生したチップの数と、固着強度数値をそれぞれ確認した。

【0093】

表2を参照すると、サンプル1及びサンプル2は、比較例であって、セラミック素体10の一面の広さに対する第1又は第2外部電極31、32の広さの比が10%未満のものを示す。この場合、固着強度が低いため、第1又は第2外部電極31、32と第1又は第2リード部23、24との接続が切断された不良製品が多数発見されたことから、信頼性に問題があることが分かる。

【0094】

また、サンプル7及びサンプル8は、比較例であって、セラミック素体10の一面の広さに対する第1又は第2外部電極31、32の広さの比が40%を超えるものを示す。この場合、第1又は第2外部電極31、32と第1又は第2リード部23、24との接続に関する問題は発見されなかったが、セラミック素体10のマージン部が減少してデラミネーションが発生した不良製品が多数発見されたことから、信頼性に問題があることが分かる。

【0095】

<セラミック素体及び外部電極のスペックによる積層セラミックキャパシタの特性>

【表3】

【0096】

表3においては、セラミック素体10の一面の長さLを1.0mm、幅Wを0.5mmとし、第1又は第2外部電極31、32の広さAを様々に変更した。そして、複数のチップのうち、第1又は第2外部電極31、32と第1又は第2リード部23、24との電気的接続が切断されたり、デラミネーションが発生したチップの数と、固着強度数値をそれぞれ確認した。

【0097】

表3を参照すると、サンプル1及びサンプル2は、比較例であって、セラミック素体10の一面の広さに対する第1又は第2外部電極31、32の広さの比が10%未満のものを示す。この場合、固着強度が低いため、第1又は第2外部電極31、32と第1又は第2リード部23、24との接続が切断された不良製品が多数発見されたことから、信頼性に問題があることが分かる。

【0098】

また、サンプル9及び10は、比較例であって、セラミック素体10の一面の広さに対する第1又は第2外部電極31、32の広さの比が40%を超えるものを示す。この場合、第1又は第2外部電極31、32と第1又は第2リード部23、24との接続に関する問題は発見されなかったが、セラミック素体10のマージン部が減少してデラミネーションが発生した不良製品が多数発見されたことから、信頼性に問題があることが分かる。

【0099】

つまり、表1〜表3によれば、セラミック素体10の一面の広さに対する第1又は第2外部電極31、32の広さの比が10〜40%である場合、固着強度が維持されて外部電極とリード部との接続性が安定に維持され、セラミック素体10のマージン部を十分に確保してデラミネーションの発生を防止することができる。以上のことから、セラミック素体10の一面の広さに対する第1又は第2外部電極31、32の広さの比の数値範囲は、10〜40%であることが好ましいことが分かる。

【0100】

また、表1〜表3を参照すると、セラミック素体10の一面の長さに対する第1又は第2外部電極31、32とセラミック素体10の先端との間隔の比が4〜18%を維持する場合、マージン部を十分に確保してデラミネーションの発生を防止し、電極の露出面積を十分に確保して第1又は第2外部電極31、32と第1又は第2リード部23、24との接続性を安定に維持することができる。以上のことから、セラミック素体10の一面の長さに対する第1又は第2外部電極31、32とセラミック素体10の先端との間隔の比の数値範囲は、4〜18%であることが好ましい。

【0101】

以下、本発明の一実施形態による積層セラミックキャパシタの製造方法を説明する。

【0102】

まず、複数のセラミックグリーンシートを準備する。

【0103】

前記セラミックグリーンシートは、セラミック素体10の誘電体層を形成するためのものであり、セラミック粉末、ポリマー、及び溶剤を混合してスラリーを製造し、前記スラリーをドクターブレードなどの工法により数μm厚さのシート状に製作してもよい。

【0104】

その後、前記各セラミックグリーンシートの少なくとも一面に所定の厚さ、例えば0.2〜1.0μmの厚さを有するように導電性ペーストを印刷して、第1及び第2内部電極膜を形成する。

【0105】

ここで、前記導電性ペーストの印刷は、前記セラミックグリーンシートの縁部に沿って、その内部に前記第1及び第2内部電極膜と所定の幅のマージン部が形成されるように行ってもよい。

【0106】

その後、前記第1及び第2内部電極膜の形成と同様の方法により、前記各セラミックグリーンシートの正方向のマージン部に所定の厚さ、例えば0.2〜1.0μmの厚さを有するように導電性ペーストを印刷して、前記各セラミックグリーンシートの正方向の側面と前記第1及び第2内部電極膜とが互いに接続されるように、第1及び第2リード膜を形成する。

【0107】

ここで、前記第1及び第2リード膜は、前記第1及び第2内部電極膜が異なる極性を有するので、複数のセラミックグリーンシートを積層した際に前記第1及び第2内部電極膜の長側面に沿って重なる部分がないように交互に形成する。

【0108】

また、前記第1及び第2リード膜は、その幅が同じ幅になるように形成することが好ましいが、本発明がこれに限定されるものではなく、必要に応じて、前記第1及び第2リード膜の幅が異なる幅になるように形成してもよい。

【0109】

このような導電性ペーストの印刷方法としては、スクリーン印刷法又はグラビア印刷法などを用いてもよく、前記導電性ペーストは、金属粉末、セラミック粉末、及びシリカ(SiO2)粉末などを含んでもよい。

【0110】

前記導電性ペーストの平均粒径は50〜400nmでもよいが、本発明がこれに限定されるものではない。

【0111】

また、前記金属粉末としては、ニッケル(Ni)、マンガン(Mn)、クロム(Cr)、コバルト(Co)、及びアルミニウム(Al)のいずれか1つ又はこれらの合金を使用してもよい。

【0112】

その後、前記第1及び第2内部電極膜と前記第1及び第2リード膜が形成された複数のセラミックグリーンシートを積層し、積層方向から加圧することにより、積層された複数のセラミックグリーンシートとセラミックグリーンシート上に形成された導電性ペーストとを互いに圧着する。

【0113】

これにより、複数の誘電体層と複数の第1及び第2内部電極21、22が交互に積層され、第1及び第2リード部23、24が第1及び第2内部電極21、22の長側面の方向に沿って交互に配置された積層体を構成することができる。

【0114】

その後、前記積層体を1つのキャパシタに対応する領域毎に切断してチップ化し、高温で焼成することにより、セラミック素体10を完成する。

【0115】

その後、セラミック素体10の正方向の側面から露出した第1及び第2リード部23、24の端部を覆うように、第1及び第2外部電極31、32を形成する。

【0116】

すなわち、第1及び第2外部電極31、32は、第1及び第2リード部23、24にそれぞれ接続されて、第1及び第2内部電極21、22にそれぞれ電気的に接続されることができる。

【0117】

ここで、積層体の一面の広さに対する第1又は第2外部電極31、32の広さの比が10〜40%になるように形成してもよい。

【0118】

また、積層体の一面の長さに対する第1又は第2外部電極31、32と積層体の先端との間隔の比が4〜18%になるように形成してもよい。

【0119】

また、第1及び第2外部電極31、32の表面には、必要に応じてニッケル又はスズなどでめっき処理を施してもよい。

【0120】

本発明は、前述した実施形態及び添付された図面により限定されるものではなく、添付された請求の範囲により限定される。

【0121】

よって、請求の範囲に記載された本発明の技術的思想から外れない範囲内で当該技術分野における通常の知識を有する者により様々な形態の置換、変形、及び変更が可能であり、これも本発明の範囲に属するといえるであろう。

【符号の説明】

【0122】

1 積層セラミックキャパシタ

10 セラミック素体

21、22 第1及び第2内部電極

23、24 第1及び第2リード部

31、32 第1及び第2外部電極

【技術分野】

【0001】

本発明は、積層セラミック電子部品及びその製造方法に関する。

【背景技術】

【0002】

セラミック材料を用いる電子部品としては、キャパシタ、インダクタ、圧電素子、バリスタ、又はサーミスタなどがある。

【0003】

このようなセラミック電子部品の1つである積層セラミックキャパシタ(MLCC:Multi−Layered Ceramic Capacitor)は、小型ながらも高容量が保証され、実装が容易であるという利点を有する。

【0004】

このような積層セラミックキャパシタは、コンピュータ、個人用の携帯情報端末(PDA:Personal Digital Assistants)、又は携帯電話などの様々な電子製品の回路基板に取り付けられて充放電を行う重要な役割を果たすチップ型コンデンサであって、使用される用途及び容量によって様々なサイズと積層形態を有する。

【0005】

特に、近年、電子製品が小型化するにつれて、電子製品に使用される積層セラミックキャパシタにも超小型化及び超高容量化が求められている。

【0006】

よって、製品の超小型化のために誘電体層及び内部電極の厚さを薄くし、超高容量化のために多数の誘電体層を積層した積層セラミックキャパシタが製造されている。

【0007】

一方、外部電極の全てが下面に位置する積層セラミックキャパシタがあるが、このような構造の積層セラミックキャパシタは、実装密度及び容量に優れてESLが低いという利点を有するが、固着強度が低く、積層体の一面が曲がってクラックが発生しやすいという欠点がある。

【発明の概要】

【発明が解決しようとする課題】

【0008】

当該技術分野においては、下面電極を用いる積層セラミックキャパシタの固着強度を高めて、曲がりクラックを防止することのできる新たな方法が求められてきた。

【課題を解決するための手段】

【0009】

本発明の一態様は、複数の誘電体層が積層されたセラミック素体と、前記セラミック素体内で前記複数の誘電体層の少なくとも一面に形成され、前記セラミック素体の一面から露出する第1及び第2内部電極と、前記セラミック素体の一面に形成され、前記第1及び第2内部電極の露出部により前記第1及び第2内部電極とそれぞれ電気的に接続される第1及び第2外部電極とを含み、前記セラミック素体の一面の広さに対する前記第1又は第2外部電極の広さの比が10〜40%である、積層セラミック電子部品を提供する。

【0010】

本発明の他の態様によれば、前記セラミック素体の一面の長さに対する前記第1又は第2外部電極と前記セラミック素体の先端との間隔の比が4〜18%でもよい。

【0011】

本発明の一実施形態においては、前記第1及び第2外部電極の広さが同じでもよい。

【0012】

本発明の一実施形態においては、前記第1及び第2外部電極の広さが異なっていてもよい。

【0013】

本発明の一実施形態においては、前記第1外部電極と前記セラミック素体の一側先端との間隔が、前記第2外部電極と前記セラミック素体の対向する先端との間隔と同じでもよい。

【0014】

本発明の一実施形態においては、前記第1外部電極と前記セラミック素体の一側先端との間隔が、前記第2外部電極と前記セラミック素体の対向する先端との間隔と異なっていてもよい。

【0015】

本発明の一実施形態において、前記第1及び第2外部電極は、前記セラミック素体の長手方向に対して一方に偏って形成されてもよい。

【0016】

本発明の一実施形態において、前記第1及び第2外部電極は、前記セラミック素体の中央に左右対称に形成されてもよい。

【0017】

本発明の一実施形態において、前記第1及び第2外部電極は、前記セラミック素体の全てのマージン部が同じ幅で形成されてもよい。

【0018】

本発明のさらに他の態様は、第1及び第2セラミックシートの少なくとも一面に第1及び第2内部電極膜を形成する段階と、前記第1及び第2内部電極膜がそれぞれ形成された前記第1及び第2セラミックシートを交互に積層して積層体を形成する段階と、前記積層体を焼成する段階と、前記第1及び第2内部電極膜と電気的に接続されるように、前記積層体の両側面に第1及び第2外部電極を形成する段階とを含み、前記セラミック素体の一面の広さに対する前記第1又は第2外部電極の広さの比が10〜40%になるようにする、積層セラミック電子部品の製造方法を提供する。

【0019】

本発明のさらに他の態様によれば、前記セラミック素体の一面の長さに対する前記第1又は第2外部電極と前記セラミック素体の先端との間隔の比が4〜18%になるように調節してもよい。

【0020】

本発明の一実施形態において、前記第1外部電極及び前記第2外部電極は、その広さが同じ広さになるように形成してもよい。

【0021】

本発明の一実施形態において、前記第1外部電極及び前記第2外部電極は、その広さが異なる広さになるように形成してもよい。

【0022】

本発明の一実施形態において、前記第1外部電極と前記セラミック素体の一側先端との間隔は、前記第2外部電極と前記セラミック素体の対向する先端との間隔と同じ間隔になるように形成してもよい。

【0023】

本発明の一実施形態において、前記第1外部電極と前記セラミック素体の一側先端との間隔は、前記第2外部電極と前記セラミック素体の対向する先端との間隔と異なる間隔になるように形成してもよい。

【0024】

本発明の一実施形態において、前記第1及び第2外部電極は、前記セラミック素体の長手方向に対して一方に偏るように形成してもよい。

【0025】

本発明の一実施形態において、前記第1及び第2外部電極は、前記セラミック素体の中央に左右対称となるように形成してもよい。

【0026】

本発明の一実施形態において、前記第1及び第2外部電極は、前記セラミック素体の全てのマージン部が同じ幅になるように形成してもよい。

【発明の効果】

【0027】

本発明の一実施形態によれば、外部電極の大きさを調節することにより、下面構造の積層セラミック電子部品の固着強度を高めて曲がりクラックを防止することができるという効果がある。

【図面の簡単な説明】

【0028】

【図1】本発明の一実施形態による積層セラミックキャパシタの概略的な構造を示す斜視図である。

【図2】図1の積層セラミックキャパシタの分解斜視図である。

【図3】図1の積層セラミックキャパシタにおける第1内部電極と第1外部電極の結合構造を示す断面図である。

【図4】図1の積層セラミックキャパシタにおける第2内部電極と第2外部電極の結合構造を示す断面図である。

【図5】図1の積層セラミックキャパシタにおける第1及び第2内部電極と第1及び第2外部電極の結合構造を示す断面図である。

【図6】図1の積層セラミックキャパシタの正面図である。

【発明を実施するための形態】

【0029】

以下、添付図面を参照して本発明の好ましい実施形態を説明する。

【0030】

しかしながら、本発明の実施形態は様々な他の形態に変形することができ、本発明の範囲が後述する実施形態に限定されるものではない。

【0031】

また、本発明の実施形態は、当該技術分野における通常の知識を有する者に本発明をより完全に説明するために提供されるものである。

【0032】

よって、図面において、構成要素の形状及び大きさなどはより明確な説明のために誇張することもあり、同一の構成要素には同一の符号が付される。

【0033】

なお、類似の機能及び作用を果たす部分には、図面全体にわたって同一の符号が付される。

【0034】

また、明細書全体にわたって、ある構成要素を「含む」とは、特に断らない限り、他の構成要素を除くのではなく、他の構成要素をさらに含むことがあることを意味する。

【0035】

本発明は、セラミック電子部品に関し、本発明の一実施形態によるセラミック電子部品としては、積層セラミックキャパシタ、インダクタ、圧電素子、バリスタ、チップ抵抗、又はサーミスタなどがある。以下、セラミック電子部品の一例として積層セラミックキャパシタについて説明する。

【0036】

なお、本実施形態においては、説明の便宜上、セラミック素体に外部電極が形成された方向を正方向とし、内部電極の長側面に沿う方向を左右方向として説明する。

【0037】

図1〜図6に示すように、本実施形態による積層セラミックキャパシタ1は、複数の誘電体層が積層されたセラミック素体10と、セラミック素体10内で前記複数の誘電体層の少なくとも一面に形成され、セラミック素体10の一面から露出する第1及び第2内部電極21、22と、セラミック素体10の一面に形成され、第1及び第2内部電極21、22の露出部により第1及び第2内部電極21、22とそれぞれ電気的に接続する第1及び第2外部電極31、32とを含む。

【0038】

ここで、第1及び第2外部電極31、32が形成されたセラミック素体10の正方向の側面の広さに対する第1又は第2外部電極31、32の広さの比は、10〜40%にしてもよい。

【0039】

このような数値の詳細については、具体的な実施例と比較例を挙げて後述する。

【0040】

本実施形態の積層セラミックキャパシタは2端子垂直積層型キャパシタでもよい。

【0041】

「2端子(2−terminal)」とは、キャパシタの端子として2つの端子が回路基板に接続されることを意味し、「垂直積層型(vertically laminated or vertical multilayer)」とは、キャパシタ内の積層された内部電極が回路基板の実装領域面に垂直に配置されることを意味する。

【0042】

このような構造により、第1及び第2内部電極21、22は、セラミック素体10の正方向の側面から露出するように延設された第1及び第2リード部23、24をそれぞれ有する。

【0043】

すなわち、セラミック素体10の正方向の側面に形成された第1及び第2外部電極31、32は、第1及び第2リード部23、24の露出した部分に接続し、これにより第1及び第2内部電極21、22とそれぞれ電気的に接続することができる。

【0044】

セラミック素体10は、複数の誘電体層を積層して形成してもよい。

【0045】

ここで、セラミック素体10を構成する複数の誘電体層は、焼結された状態であって、隣接する誘電体層間の境界を確認できない程度に一体化されていてもよい。

【0046】

また、セラミック素体10は、その形状に特に制限はないが、一般に直方体形状でもよい。

【0047】

また、セラミック素体10は、その寸法に特に制限はないが、そのサイズを例えば0.6mm×0.3mmなどにすることにより、1.0μF以上の高容量を有する積層セラミックキャパシタ1を構成してもよい。

【0048】

さらに、必要に応じては、セラミック素体10の最外面(図における上下面)に所定厚さの誘電体カバー層(図示せず)を形成してもよい。

【0049】

このようなセラミック素体10を構成する誘電体層は、セラミック粉末、例えばBaTiO3系セラミック粉末などを含んでもよい。

【0050】

BaTiO3系セラミック粉末としては、BaTiO3にCa又はZrなどが一部固溶した(Ba1−xCax)TiO3、Ba(Ti1−yCay)O3、(Ba1−xCax)(Ti1−yZry)O3、又はBa(Ti1−yZry)O3などがあり、これに限定されるものではない。

【0051】

セラミック粉末の平均粒径は、0.8μm以下でもよく、好ましくは0.05〜0.5μmでもよいが、本発明がこれに限定されるものではない。

【0052】

誘電体層は、必要に応じて、セラミック粉末と共に、遷移金属酸化物もしくは炭化物、希土類元素、又はMg、Alの少なくとも1つをさらに含んでもよい。

【0053】

また、誘電体層の厚さは、積層セラミックキャパシタ1の容量設計によって任意に変更することができる。

【0054】

本実施形態における各誘電体層の厚さは、1.0μm以下でもよく、好ましくは0.01〜1.0μmでもよいが、本発明がこれに限定されるものではない。

【0055】

第1及び第2内部電極21、22は、導電性金属を含む導電性ペーストにより形成してもよい。

【0056】

ここで、導電性金属は、Ni、Cu、Pd、又はこれらの合金でもよいが、本発明がこれに限定されるものではない。

【0057】

このような第1及び第2内部電極21、22は、スクリーン印刷法又はグラビア印刷法などの印刷法により、誘電体層を形成するセラミックグリーンシート上に導電性ペーストで内部電極層を印刷し、その内部電極層が印刷されたセラミックグリーンシートを交互に積層した後に焼成することにより、セラミック素体10に形成することができる。

【0058】

従って、このように第1及び第2内部電極21、22が重なる領域により静電容量が形成される。

【0059】

また、第1及び第2内部電極21、22の厚さは用途に応じて決定され、例えばセラミック素体10のサイズを考慮して0.2〜1.0μmの範囲内で決定してもよいが、本発明がこれに限定されるものではない。

【0060】

このように誘電体層に第1及び第2内部電極21、22を形成する際に、水分やめっき液などが内部に浸透することを防止し、電気的な短絡を防止するために、誘電体層と第1及び第2内部電極21、22との間には所定のマージン部を残しておく。

【0061】

そして、第1及び第2内部電極21、22と誘電体層の側面に形成された異なる極性の第1及び第2外部電極31、32とを電気的に接続するために、誘電体層のマージン部に第1及び第2リード部23、24を第1及び第2内部電極21、22の一面から正方向に形成してもよい。

【0062】

第1及び第2リード部23、24の端部は、セラミック素体10の正方向の側面から露出させてもよい。

【0063】

ここで、第1及び第2リード部23、24は、それぞれ異なる極性を示す第1及び第2外部電極31、32にのみ接続するように、互いに重なる領域を有してはならない。

【0064】

つまり、第1及び第2リード部23、24は、第1及び第2内部電極21、22の長側面に沿って左右交互に配置されてもよい。

【0065】

ここで、第1及び第2リード部23、24の幅は同じ幅にすることが好ましいが、本発明がこれに限定されるものではなく、必要に応じて、第1及び第2リード部23、24の幅が異なる幅になるようにしてもよい。

【0066】

また、第1及び第2リード部23、24の厚さは、第1及び第2内部電極21、22と同じ厚さにすることが好ましい。

【0067】

例えば、本実施形態においては、第1及び第2内部電極21、22の厚さが0.2〜1.0μmであるので、第1及び第2リード部23、24の厚さも0.2〜1.0μmにするが、本発明がこれに限定されるものではない。

【0068】

本実施形態において、第1及び第2外部電極31、32は、セラミック素体10の正方向の側面にのみ形成される。

【0069】

従って、左右に外部電極が形成される他の構造に比べて全体的な実装面積が相対的に減少するので、回路基板の実装密度を向上させることができる。

【0070】

ここで、回路基板の実装密度がさらに向上するように、第1及び第2内部電極21、22を第1及び第2外部電極31、32が形成された方向に対して垂直方向に沿って積層して構成することがより好ましい。

【0071】

前述したように、第1及び第2外部電極31、32が形成されたセラミック素体10の正方向の側面の広さに対する第1又は第2外部電極31、32の広さの比は、10〜40%にしてもよい。

【0072】

ここで、第1及び第2外部電極31、32は、同じ広さになるように形成することが好ましいが、本発明がこれに限定されるものではなく、前記数値を満たす範囲内で異なる広さになるように形成してもよい。

【0073】

また、固着強度を高めて曲がりクラックを防止するために、セラミック素体10の一面の長さLに対する第1又は第2外部電極31、32とセラミック素体10の先端との間隔aの比は、4〜18%に調節してもよい。

【0074】

ここで、第1外部電極31とセラミック素体10の一側先端との間隔は、第2外部電極32とセラミック素体10の対向する先端との間隔と同じ間隔になるように形成してもよいが、本発明がこれに限定されるものではなく、前記数値を満たす範囲内で両側マージン部の間隔が異なる間隔になるように形成してもよい。

【0075】

すなわち、第1及び第2外部電極31、32は、セラミック素体10の中央に左右対称に配置してもよく、必要に応じて、セラミック素体10の左右長手方向に対して一方に偏るように形成してもよい。

【0076】

また、必要に応じて、第1及び第2外部電極31、32とセラミック素体10の正方向の側面に対する上下左右の全てのマージン部の幅が同じ幅になるように形成してもよい。

【0077】

一方、第1及び第2外部電極31、32は、上下に積層された複数の第1及び第2内部電極21、22と安定して接続されるように、セラミック素体10に対応する高さで形成してもよい。

【0078】

しかしながら、本発明がこれに限定されるものではなく、必要に応じて、第1及び第2外部電極31、32は、セラミック素体10より高く形成してもよく、低く形成してもよい。

【0079】

また、第1及び第2外部電極31、32は、めっき液の浸透を防止するために、第1及び第2リード部23、24が左右方向の中央に位置するように形成してもよい。

【0080】

本出願人は、セラミック素体10の一側面の広さに対する第1又は第2外部電極31、32の広さの比を調節して、固着強度を高めながらも曲がりクラックを防止できる範囲を確認した。

【0081】

セラミック素体10の一側面の広さに対する第1又は第2外部電極31、32の広さの比が10%未満の場合は、固着強度が低下することがあり、セラミック素体10の一側面の広さに対する第1又は第2外部電極31、32の広さの比が40%を超える場合は、第1及び第2外部電極31、32が形成されるセラミック素体10一面のマージン部が小さすぎるため、デラミネーション(層間剥離)が発生して曲がりクラックが発生し得る。

【0082】

従って、セラミック素体10の一側面の広さに対する第1又は第2外部電極31、32の広さの比の範囲は、10〜40%にすることが好ましい。

【0083】

以下、具体的な実施例と比較例を挙げて本発明をより詳細に説明する。

【0084】

前述したように、第1又は第2外部電極31、32の広さをA、セラミック素体10の長さ及び幅をそれぞれL及びW、第1又は第2外部電極31、32とセラミック素体10の先端との間隔をaとし、下記表1〜3のように積層セラミックキャパシタの特性を測定した。

【0085】

厚さ2μmの成形シートに第1及び第2リード部23、24を有する第1及び第2内部電極21、22、並びに第1及び第2外部電極31、32を各サイズに印刷してチップを製作し、評価を行った。

【0086】

下記表1においては、セラミック素体10の一面の長さLを0.4mm、幅Wを0.2mmとし、第1又は第2外部電極31、32の広さAを様々に変更した。

【0087】

その後、複数のチップのうち、第1又は第2外部電極31、32と第1又は第2リード部23、24との電気的接続が切断されたり、デラミネーションが発生したチップの数と、固着強度数値をそれぞれ確認した。

【0088】

<セラミック素体及び外部電極のスペックによる積層セラミックキャパシタの特性>

【表1】

【0089】

表1を参照すると、サンプル1及びサンプル2は、比較例であって、セラミック素体10の一面の広さに対する第1又は第2外部電極31、32の広さの比が10%未満のものを示す。この場合、固着強度が低いため、第1又は第2外部電極31、32と第1又は第2リード部23、24との接続が切断された不良製品が多数発見されたことから、信頼性に問題があることが分かる。

【0090】

また、サンプル8及びサンプル9は、比較例であって、セラミック素体10の一面の広さに対する第1又は第2外部電極31、32の広さの比が40%を超えるものを示す。この場合、第1又は第2外部電極31、32と第1又は第2リード部23、24との接続に関する問題は発見されなかったが、セラミック素体10のマージン部が減少してデラミネーションが発生した不良製品が多数発見されたことから、信頼性に問題があることが分かる。

【0091】

<セラミック素体及び外部電極のスペックによる積層セラミックキャパシタの特性>

【表2】

【0092】

表2においては、セラミック素体10の一面の長さLを0.6mm、幅Wを0.3mmとする一方、第1又は第2外部電極31、32の広さAを様々なものに変更した。そして、これらの複数のチップのうち、第1又は第2外部電極31、32と第1又は第2リード部23、24との電気的接続が切断されたり、デラミネーションが発生したチップの数と、固着強度数値をそれぞれ確認した。

【0093】

表2を参照すると、サンプル1及びサンプル2は、比較例であって、セラミック素体10の一面の広さに対する第1又は第2外部電極31、32の広さの比が10%未満のものを示す。この場合、固着強度が低いため、第1又は第2外部電極31、32と第1又は第2リード部23、24との接続が切断された不良製品が多数発見されたことから、信頼性に問題があることが分かる。

【0094】

また、サンプル7及びサンプル8は、比較例であって、セラミック素体10の一面の広さに対する第1又は第2外部電極31、32の広さの比が40%を超えるものを示す。この場合、第1又は第2外部電極31、32と第1又は第2リード部23、24との接続に関する問題は発見されなかったが、セラミック素体10のマージン部が減少してデラミネーションが発生した不良製品が多数発見されたことから、信頼性に問題があることが分かる。

【0095】

<セラミック素体及び外部電極のスペックによる積層セラミックキャパシタの特性>

【表3】

【0096】

表3においては、セラミック素体10の一面の長さLを1.0mm、幅Wを0.5mmとし、第1又は第2外部電極31、32の広さAを様々に変更した。そして、複数のチップのうち、第1又は第2外部電極31、32と第1又は第2リード部23、24との電気的接続が切断されたり、デラミネーションが発生したチップの数と、固着強度数値をそれぞれ確認した。

【0097】

表3を参照すると、サンプル1及びサンプル2は、比較例であって、セラミック素体10の一面の広さに対する第1又は第2外部電極31、32の広さの比が10%未満のものを示す。この場合、固着強度が低いため、第1又は第2外部電極31、32と第1又は第2リード部23、24との接続が切断された不良製品が多数発見されたことから、信頼性に問題があることが分かる。

【0098】

また、サンプル9及び10は、比較例であって、セラミック素体10の一面の広さに対する第1又は第2外部電極31、32の広さの比が40%を超えるものを示す。この場合、第1又は第2外部電極31、32と第1又は第2リード部23、24との接続に関する問題は発見されなかったが、セラミック素体10のマージン部が減少してデラミネーションが発生した不良製品が多数発見されたことから、信頼性に問題があることが分かる。

【0099】

つまり、表1〜表3によれば、セラミック素体10の一面の広さに対する第1又は第2外部電極31、32の広さの比が10〜40%である場合、固着強度が維持されて外部電極とリード部との接続性が安定に維持され、セラミック素体10のマージン部を十分に確保してデラミネーションの発生を防止することができる。以上のことから、セラミック素体10の一面の広さに対する第1又は第2外部電極31、32の広さの比の数値範囲は、10〜40%であることが好ましいことが分かる。

【0100】

また、表1〜表3を参照すると、セラミック素体10の一面の長さに対する第1又は第2外部電極31、32とセラミック素体10の先端との間隔の比が4〜18%を維持する場合、マージン部を十分に確保してデラミネーションの発生を防止し、電極の露出面積を十分に確保して第1又は第2外部電極31、32と第1又は第2リード部23、24との接続性を安定に維持することができる。以上のことから、セラミック素体10の一面の長さに対する第1又は第2外部電極31、32とセラミック素体10の先端との間隔の比の数値範囲は、4〜18%であることが好ましい。

【0101】

以下、本発明の一実施形態による積層セラミックキャパシタの製造方法を説明する。

【0102】

まず、複数のセラミックグリーンシートを準備する。

【0103】

前記セラミックグリーンシートは、セラミック素体10の誘電体層を形成するためのものであり、セラミック粉末、ポリマー、及び溶剤を混合してスラリーを製造し、前記スラリーをドクターブレードなどの工法により数μm厚さのシート状に製作してもよい。

【0104】

その後、前記各セラミックグリーンシートの少なくとも一面に所定の厚さ、例えば0.2〜1.0μmの厚さを有するように導電性ペーストを印刷して、第1及び第2内部電極膜を形成する。

【0105】

ここで、前記導電性ペーストの印刷は、前記セラミックグリーンシートの縁部に沿って、その内部に前記第1及び第2内部電極膜と所定の幅のマージン部が形成されるように行ってもよい。

【0106】

その後、前記第1及び第2内部電極膜の形成と同様の方法により、前記各セラミックグリーンシートの正方向のマージン部に所定の厚さ、例えば0.2〜1.0μmの厚さを有するように導電性ペーストを印刷して、前記各セラミックグリーンシートの正方向の側面と前記第1及び第2内部電極膜とが互いに接続されるように、第1及び第2リード膜を形成する。

【0107】

ここで、前記第1及び第2リード膜は、前記第1及び第2内部電極膜が異なる極性を有するので、複数のセラミックグリーンシートを積層した際に前記第1及び第2内部電極膜の長側面に沿って重なる部分がないように交互に形成する。

【0108】

また、前記第1及び第2リード膜は、その幅が同じ幅になるように形成することが好ましいが、本発明がこれに限定されるものではなく、必要に応じて、前記第1及び第2リード膜の幅が異なる幅になるように形成してもよい。

【0109】

このような導電性ペーストの印刷方法としては、スクリーン印刷法又はグラビア印刷法などを用いてもよく、前記導電性ペーストは、金属粉末、セラミック粉末、及びシリカ(SiO2)粉末などを含んでもよい。

【0110】

前記導電性ペーストの平均粒径は50〜400nmでもよいが、本発明がこれに限定されるものではない。

【0111】

また、前記金属粉末としては、ニッケル(Ni)、マンガン(Mn)、クロム(Cr)、コバルト(Co)、及びアルミニウム(Al)のいずれか1つ又はこれらの合金を使用してもよい。

【0112】

その後、前記第1及び第2内部電極膜と前記第1及び第2リード膜が形成された複数のセラミックグリーンシートを積層し、積層方向から加圧することにより、積層された複数のセラミックグリーンシートとセラミックグリーンシート上に形成された導電性ペーストとを互いに圧着する。

【0113】

これにより、複数の誘電体層と複数の第1及び第2内部電極21、22が交互に積層され、第1及び第2リード部23、24が第1及び第2内部電極21、22の長側面の方向に沿って交互に配置された積層体を構成することができる。

【0114】

その後、前記積層体を1つのキャパシタに対応する領域毎に切断してチップ化し、高温で焼成することにより、セラミック素体10を完成する。

【0115】

その後、セラミック素体10の正方向の側面から露出した第1及び第2リード部23、24の端部を覆うように、第1及び第2外部電極31、32を形成する。

【0116】

すなわち、第1及び第2外部電極31、32は、第1及び第2リード部23、24にそれぞれ接続されて、第1及び第2内部電極21、22にそれぞれ電気的に接続されることができる。

【0117】

ここで、積層体の一面の広さに対する第1又は第2外部電極31、32の広さの比が10〜40%になるように形成してもよい。

【0118】

また、積層体の一面の長さに対する第1又は第2外部電極31、32と積層体の先端との間隔の比が4〜18%になるように形成してもよい。

【0119】

また、第1及び第2外部電極31、32の表面には、必要に応じてニッケル又はスズなどでめっき処理を施してもよい。

【0120】

本発明は、前述した実施形態及び添付された図面により限定されるものではなく、添付された請求の範囲により限定される。

【0121】

よって、請求の範囲に記載された本発明の技術的思想から外れない範囲内で当該技術分野における通常の知識を有する者により様々な形態の置換、変形、及び変更が可能であり、これも本発明の範囲に属するといえるであろう。

【符号の説明】

【0122】

1 積層セラミックキャパシタ

10 セラミック素体

21、22 第1及び第2内部電極

23、24 第1及び第2リード部

31、32 第1及び第2外部電極

【特許請求の範囲】

【請求項1】

複数の誘電体層が積層されたセラミック素体と、

前記セラミック素体内で前記複数の誘電体層の少なくとも一面に形成され、前記セラミック素体の一面から露出する第1及び第2内部電極と、

前記セラミック素体の一面に形成され、前記第1及び第2内部電極の露出部により前記第1及び第2内部電極とそれぞれ電気的に接続される第1及び第2外部電極とを含み、

前記セラミック素体の一面の広さに対する前記第1又は第2外部電極の広さの比が10〜40%である、積層セラミック電子部品。

【請求項2】

前記第1及び第2外部電極の広さが同じであることを特徴とする請求項1に記載の積層セラミック電子部品。

【請求項3】

前記第1及び第2外部電極の広さが異なっていることを特徴とする請求項1に記載の積層セラミック電子部品。

【請求項4】

前記第1外部電極と前記セラミック素体の一側先端との間隔が、前記第2外部電極と前記セラミック素体の対向する先端との間隔と同じであることを特徴とする請求項1に記載の積層セラミック電子部品。

【請求項5】

前記第1外部電極と前記セラミック素体の一側先端との間隔が、前記第2外部電極と前記セラミック素体の対向する先端との間隔と異なっていることを特徴とする請求項1に記載の積層セラミック電子部品。

【請求項6】

前記第1及び第2外部電極は、前記セラミック素体の長手方向に対して一方に偏って形成されていることを特徴とする請求項1に記載の積層セラミック電子部品。

【請求項7】

前記第1及び第2外部電極は、前記セラミック素体の中央に左右対称に形成されていることを特徴とする請求項1に記載の積層セラミック電子部品。

【請求項8】

前記第1及び第2外部電極は、前記セラミック素体の全てのマージン部が同じ幅で形成されていることを特徴とする請求項1に記載の積層セラミック電子部品。

【請求項9】

複数の誘電体層が積層されたセラミック素体と、

前記セラミック素体内で前記複数の誘電体層の少なくとも一面に形成され、前記セラミック素体の一面から露出する第1及び第2内部電極と、

前記セラミック素体の一面に形成され、前記第1及び第2内部電極の露出部により前記第1及び第2内部電極とそれぞれ電気的に接続される第1及び第2外部電極とを含み、

前記セラミック素体の一面の長さに対する前記第1又は第2外部電極と前記セラミック素体の先端との間隔の比が4〜18%である、積層セラミック電子部品。

【請求項10】

前記第1外部電極と前記セラミック素体の一側先端との間隔が、前記第2外部電極と前記セラミック素体の対向する先端との間隔と同じであることを特徴とする請求項9に記載の積層セラミック電子部品。

【請求項11】

前記第1外部電極と前記セラミック素体の一側先端との間隔が、前記第2外部電極と前記セラミック素体の対向する先端との間隔と異なっていることを特徴とする請求項9に記載の積層セラミック電子部品。

【請求項12】

前記第1及び第2外部電極は、前記セラミック素体の長手方向に対して一方に偏って形成されていることを特徴とする請求項9に記載の積層セラミック電子部品。

【請求項13】

前記第1及び第2外部電極は、前記セラミック素体の中央に左右対称に形成されていることを特徴とする請求項9に記載の積層セラミック電子部品。

【請求項14】

前記第1及び第2外部電極は、前記セラミック素体の全てのマージン部が同じ幅で形成されていることを特徴とする請求項9に記載の積層セラミック電子部品。

【請求項15】

第1及び第2セラミックシートの少なくとも一面に第1及び第2内部電極膜を形成する段階と、

前記第1及び第2内部電極膜がそれぞれ形成された前記第1及び第2セラミックシートを交互に積層して積層体を形成する段階と、

前記積層体を焼成する段階と、

前記第1及び第2内部電極膜と電気的に接続されるように、前記積層体の両側面に第1及び第2外部電極を形成する段階とを含み、

前記セラミック素体の一面の広さに対する前記第1又は第2外部電極の広さの比が10〜40%になるようにする、積層セラミック電子部品の製造方法。

【請求項16】

前記第1外部電極及び前記第2外部電極は、その広さが同じ広さになるように形成することを特徴とする請求項15に記載の積層セラミック電子部品の製造方法。

【請求項17】

前記第1外部電極及び前記第2外部電極は、その広さが異なる広さになるように形成することを特徴とする請求項15に記載の積層セラミック電子部品の製造方法。

【請求項18】

前記第1外部電極と前記セラミック素体の一側先端との間隔は、前記第2外部電極と前記セラミック素体の対向する先端との間隔と同じ間隔になるように形成することを特徴とする請求項15に記載の積層セラミック電子部品の製造方法。

【請求項19】

前記第1外部電極と前記セラミック素体の一側先端との間隔は、前記第2外部電極と前記セラミック素体の対向する先端との間隔と異なる間隔になるように形成することを特徴とする請求項15に記載の積層セラミック電子部品の製造方法。

【請求項20】

前記第1及び第2外部電極は、前記セラミック素体の長手方向に対して一方に偏るように形成することを特徴とする請求項15に記載の積層セラミック電子部品の製造方法。

【請求項21】

前記第1及び第2外部電極は、前記セラミック素体の中央に左右対称となるように形成することを特徴とする請求項15に記載の積層セラミック電子部品の製造方法。

【請求項22】

前記第1及び第2外部電極は、前記セラミック素体の全てのマージン部が同じ幅になるように形成することを特徴とする請求項15に記載の積層セラミック電子部品の製造方法。

【請求項23】

第1及び第2セラミックシートの少なくとも一面に第1及び第2内部電極膜を形成する段階と、

前記第1及び第2内部電極膜がそれぞれ形成された前記第1及び第2セラミックシートを交互に積層して積層体を形成する段階と、

前記積層体を焼成する段階と、

前記第1及び第2内部電極膜と電気的に接続されるように、前記積層体の両側面に第1及び第2外部電極を形成する段階とを含み、

前記セラミック素体の一面の長さに対する前記第1又は第2外部電極と前記セラミック素体の先端との間隔の比が4〜18%になるようにする、積層セラミック電子部品の製造方法。

【請求項24】

前記第1外部電極と前記セラミック素体の一側先端との間隔は、前記第2外部電極と前記セラミック素体の対向する先端との間隔と同じ間隔になるように形成することを特徴とする請求項23に記載の積層セラミック電子部品の製造方法。

【請求項25】

前記第1外部電極と前記セラミック素体の一側先端との間隔は、前記第2外部電極と前記セラミック素体の対向する先端との間隔と異なる間隔になるように形成することを特徴とする請求項23に記載の積層セラミック電子部品の製造方法。

【請求項26】

前記第1及び第2外部電極は、前記セラミック素体の長手方向に対して一方に偏るように形成することを特徴とする請求項23に記載の積層セラミック電子部品の製造方法。

【請求項27】

前記第1及び第2外部電極は、前記セラミック素体の中央に左右対称となるように形成することを特徴とする請求項23に記載の積層セラミック電子部品の製造方法。

【請求項28】

前記第1及び第2外部電極は、前記セラミック素体の全てのマージン部が同じ幅になるように形成することを特徴とする請求項23に記載の積層セラミック電子部品の製造方法。

【請求項1】

複数の誘電体層が積層されたセラミック素体と、

前記セラミック素体内で前記複数の誘電体層の少なくとも一面に形成され、前記セラミック素体の一面から露出する第1及び第2内部電極と、

前記セラミック素体の一面に形成され、前記第1及び第2内部電極の露出部により前記第1及び第2内部電極とそれぞれ電気的に接続される第1及び第2外部電極とを含み、

前記セラミック素体の一面の広さに対する前記第1又は第2外部電極の広さの比が10〜40%である、積層セラミック電子部品。

【請求項2】

前記第1及び第2外部電極の広さが同じであることを特徴とする請求項1に記載の積層セラミック電子部品。

【請求項3】

前記第1及び第2外部電極の広さが異なっていることを特徴とする請求項1に記載の積層セラミック電子部品。

【請求項4】

前記第1外部電極と前記セラミック素体の一側先端との間隔が、前記第2外部電極と前記セラミック素体の対向する先端との間隔と同じであることを特徴とする請求項1に記載の積層セラミック電子部品。

【請求項5】

前記第1外部電極と前記セラミック素体の一側先端との間隔が、前記第2外部電極と前記セラミック素体の対向する先端との間隔と異なっていることを特徴とする請求項1に記載の積層セラミック電子部品。

【請求項6】

前記第1及び第2外部電極は、前記セラミック素体の長手方向に対して一方に偏って形成されていることを特徴とする請求項1に記載の積層セラミック電子部品。

【請求項7】

前記第1及び第2外部電極は、前記セラミック素体の中央に左右対称に形成されていることを特徴とする請求項1に記載の積層セラミック電子部品。

【請求項8】

前記第1及び第2外部電極は、前記セラミック素体の全てのマージン部が同じ幅で形成されていることを特徴とする請求項1に記載の積層セラミック電子部品。

【請求項9】

複数の誘電体層が積層されたセラミック素体と、

前記セラミック素体内で前記複数の誘電体層の少なくとも一面に形成され、前記セラミック素体の一面から露出する第1及び第2内部電極と、

前記セラミック素体の一面に形成され、前記第1及び第2内部電極の露出部により前記第1及び第2内部電極とそれぞれ電気的に接続される第1及び第2外部電極とを含み、

前記セラミック素体の一面の長さに対する前記第1又は第2外部電極と前記セラミック素体の先端との間隔の比が4〜18%である、積層セラミック電子部品。

【請求項10】

前記第1外部電極と前記セラミック素体の一側先端との間隔が、前記第2外部電極と前記セラミック素体の対向する先端との間隔と同じであることを特徴とする請求項9に記載の積層セラミック電子部品。

【請求項11】

前記第1外部電極と前記セラミック素体の一側先端との間隔が、前記第2外部電極と前記セラミック素体の対向する先端との間隔と異なっていることを特徴とする請求項9に記載の積層セラミック電子部品。

【請求項12】

前記第1及び第2外部電極は、前記セラミック素体の長手方向に対して一方に偏って形成されていることを特徴とする請求項9に記載の積層セラミック電子部品。

【請求項13】

前記第1及び第2外部電極は、前記セラミック素体の中央に左右対称に形成されていることを特徴とする請求項9に記載の積層セラミック電子部品。

【請求項14】

前記第1及び第2外部電極は、前記セラミック素体の全てのマージン部が同じ幅で形成されていることを特徴とする請求項9に記載の積層セラミック電子部品。

【請求項15】

第1及び第2セラミックシートの少なくとも一面に第1及び第2内部電極膜を形成する段階と、

前記第1及び第2内部電極膜がそれぞれ形成された前記第1及び第2セラミックシートを交互に積層して積層体を形成する段階と、

前記積層体を焼成する段階と、

前記第1及び第2内部電極膜と電気的に接続されるように、前記積層体の両側面に第1及び第2外部電極を形成する段階とを含み、

前記セラミック素体の一面の広さに対する前記第1又は第2外部電極の広さの比が10〜40%になるようにする、積層セラミック電子部品の製造方法。

【請求項16】

前記第1外部電極及び前記第2外部電極は、その広さが同じ広さになるように形成することを特徴とする請求項15に記載の積層セラミック電子部品の製造方法。

【請求項17】

前記第1外部電極及び前記第2外部電極は、その広さが異なる広さになるように形成することを特徴とする請求項15に記載の積層セラミック電子部品の製造方法。

【請求項18】

前記第1外部電極と前記セラミック素体の一側先端との間隔は、前記第2外部電極と前記セラミック素体の対向する先端との間隔と同じ間隔になるように形成することを特徴とする請求項15に記載の積層セラミック電子部品の製造方法。

【請求項19】

前記第1外部電極と前記セラミック素体の一側先端との間隔は、前記第2外部電極と前記セラミック素体の対向する先端との間隔と異なる間隔になるように形成することを特徴とする請求項15に記載の積層セラミック電子部品の製造方法。

【請求項20】

前記第1及び第2外部電極は、前記セラミック素体の長手方向に対して一方に偏るように形成することを特徴とする請求項15に記載の積層セラミック電子部品の製造方法。

【請求項21】

前記第1及び第2外部電極は、前記セラミック素体の中央に左右対称となるように形成することを特徴とする請求項15に記載の積層セラミック電子部品の製造方法。

【請求項22】

前記第1及び第2外部電極は、前記セラミック素体の全てのマージン部が同じ幅になるように形成することを特徴とする請求項15に記載の積層セラミック電子部品の製造方法。

【請求項23】

第1及び第2セラミックシートの少なくとも一面に第1及び第2内部電極膜を形成する段階と、

前記第1及び第2内部電極膜がそれぞれ形成された前記第1及び第2セラミックシートを交互に積層して積層体を形成する段階と、

前記積層体を焼成する段階と、

前記第1及び第2内部電極膜と電気的に接続されるように、前記積層体の両側面に第1及び第2外部電極を形成する段階とを含み、

前記セラミック素体の一面の長さに対する前記第1又は第2外部電極と前記セラミック素体の先端との間隔の比が4〜18%になるようにする、積層セラミック電子部品の製造方法。

【請求項24】

前記第1外部電極と前記セラミック素体の一側先端との間隔は、前記第2外部電極と前記セラミック素体の対向する先端との間隔と同じ間隔になるように形成することを特徴とする請求項23に記載の積層セラミック電子部品の製造方法。

【請求項25】

前記第1外部電極と前記セラミック素体の一側先端との間隔は、前記第2外部電極と前記セラミック素体の対向する先端との間隔と異なる間隔になるように形成することを特徴とする請求項23に記載の積層セラミック電子部品の製造方法。

【請求項26】

前記第1及び第2外部電極は、前記セラミック素体の長手方向に対して一方に偏るように形成することを特徴とする請求項23に記載の積層セラミック電子部品の製造方法。

【請求項27】

前記第1及び第2外部電極は、前記セラミック素体の中央に左右対称となるように形成することを特徴とする請求項23に記載の積層セラミック電子部品の製造方法。

【請求項28】

前記第1及び第2外部電極は、前記セラミック素体の全てのマージン部が同じ幅になるように形成することを特徴とする請求項23に記載の積層セラミック電子部品の製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図2】

【図3】

【図4】

【図5】

【図6】

【公開番号】特開2013−106038(P2013−106038A)

【公開日】平成25年5月30日(2013.5.30)

【国際特許分類】

【出願番号】特願2012−176766(P2012−176766)

【出願日】平成24年8月9日(2012.8.9)

【出願人】(594023722)サムソン エレクトロ−メカニックス カンパニーリミテッド. (1,585)

【Fターム(参考)】

【公開日】平成25年5月30日(2013.5.30)

【国際特許分類】

【出願日】平成24年8月9日(2012.8.9)

【出願人】(594023722)サムソン エレクトロ−メカニックス カンパニーリミテッド. (1,585)

【Fターム(参考)】

[ Back to top ]