積層セラミック電子部品

【課題】本発明は、積層セラミック電子部品及びその製造方法に関する。

【解決手段】本発明は、誘電体層を含むセラミック本体と、上記セラミック本体内で上記誘電体層を介して対向するように配置される第1及び第2の内部電極と、上記第1及び第2の内部電極と電気的に連結された第1の外部電極及び当該第1の外部電極上に形成された第2の外部電極と、を含み、上記第1及び第2の外部電極は導電性金属とガラスとを含み、上記第2の外部電極を厚さ方向に3等分するとき、中央部領域の面積に対して上記ガラスが占める面積が30〜80%である積層セラミック電子部品及びその製造方法を提供する。

本発明によると、チップの密閉性を向上させることにより信頼性が改善された積層セラミック電子部品の具現が可能となる。

【解決手段】本発明は、誘電体層を含むセラミック本体と、上記セラミック本体内で上記誘電体層を介して対向するように配置される第1及び第2の内部電極と、上記第1及び第2の内部電極と電気的に連結された第1の外部電極及び当該第1の外部電極上に形成された第2の外部電極と、を含み、上記第1及び第2の外部電極は導電性金属とガラスとを含み、上記第2の外部電極を厚さ方向に3等分するとき、中央部領域の面積に対して上記ガラスが占める面積が30〜80%である積層セラミック電子部品及びその製造方法を提供する。

本発明によると、チップの密閉性を向上させることにより信頼性が改善された積層セラミック電子部品の具現が可能となる。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、チップの密閉性を向上させることにより信頼性が改善された積層セラミック電子部品に関する。

【背景技術】

【0002】

近年、電子製品の小型化に伴い、積層セラミック電子部品の小型化及び大容量化も求められており、これにより、当該積層セラミック電子部品の外部電極も薄層化されている。

【0003】

外部電極用ペーストは、主材料として銅(Cu)等の導電性金属を用いてチップの密閉性及び外部電極とチップとの電気的連結性を保障し、補助材料としてガラスを用いて上記導電性金属の焼結収縮時に空いている空間を充填すると共に外部電極とチップとの結合力を与える役割をする。

【0004】

しかしながら、外部電極用ペースト内のガラスの含量が不足する場合、チップの密閉性に問題があることがあり、これを補完するために過剰のガラスを添加する場合、金属の焼結後にガラスが外部電極の表面へ溶出されてメッキ不良が生じる問題がある。

【0005】

特に、外部電極の薄層化に伴い、所望の水準の緻密度を具現するのが困難となり、ガラスの高温挙動特性上、ガラスの不足又は過剰による不良発生の可能性が増加する。

【0006】

また、外部電極用ペーストの塗布厚さが薄い小型の積層セラミック電子部品では、コーナー部分の外部電極の厚さが薄いため、コーナーカバレッジ(corner coverage)性能が低下し、これにより、メッキ液が浸透する問題がある。

【発明の概要】

【発明が解決しようとする課題】

【0007】

本発明の目的は、チップの密閉性を向上させることにより信頼性が改善された積層セラミック電子部品を提供することである。

【課題を解決するための手段】

【0008】

本発明は、誘電体層を含むセラミック本体と、上記セラミック本体内で上記誘電体層を介して対向するように配置される第1及び第2の内部電極と、上記第1及び第2の内部電極と電気的に連結された第1の外部電極及び当該第1の外部電極上に形成された第2の外部電極と、を含み、上記第1及び第2の外部電極は導電性金属とガラスとを含み、上記第2の外部電極を厚さ方向に3等分するとき、中央部領域の面積に対して上記ガラスが占める面積が30〜80%である積層セラミック電子部品を提供する。

【0009】

上記第2の外部電極のガラスの含量に対する上記第1の外部電極のガラスの含量の比が0.5以下であることができる。

【0010】

上記第2の外部電極の中で上記ガラスが占める面積に対する上記第1の外部電極の中で上記ガラスが占める面積の比が0.5以下であることができる。

【0011】

上記第2の外部電極は、平均厚さが5μm以上であり、上記第2の外部電極に含まれるガラスは、絶縁性ガラスであることができる。

【0012】

上記導電性金属は、銅(Cu)、ニッケル(Ni)、銀(Ag)及び銀−パラジウム(Ag−Pd)からなる群から選択された一つ以上であることができる。

【0013】

本発明は、誘電体層を含むセラミック本体と、上記セラミック本体内で上記誘電体層を介して対向するように配置される第1及び第2の内部電極と、上記第1及び第2の内部電極と電気的に連結された第1の外部電極及び当該第1の外部電極上に形成された第2の外部電極と、を含み、上記第1及び第2の外部電極は導電性金属とガラスとを含み、上記第2の外部電極は上記導電性金属100重量部に対して35〜200重量部のガラスを含む積層セラミック電子部品を提供する。

【0014】

上記第2の外部電極のガラスの含量に対する上記第1の外部電極のガラスの含量の比が0.5以下であることができる。

【0015】

上記第2の外部電極の中で上記ガラスが占める面積に対する上記第1の外部電極の中で上記ガラスが占める面積の比が0.5以下であることができる。

【0016】

上記第2の外部電極は、平均厚さが5μm以上であり、上記第2の外部電極に含まれるガラスは、絶縁性ガラスであることができる。

【0017】

上記導電性金属は、銅(Cu)、ニッケル(Ni)、銀(Ag)及び銀−パラジウム(Ag−Pd)からなる群から選択された一つ以上であることができる。

【0018】

上記第2の外部電極を厚さ方向に3等分するとき、中央部領域の面積に対して上記ガラスが占める面積が30〜80%であることができる。

【0019】

本発明は、導電性金属とガラスとを含み、上記ガラスが上記導電性金属100重量部に対して35〜200重量部の含量を有する外部電極用導電性ペーストを提供する。

【0020】

上記ガラスは、絶縁性ガラスであることができる。

【0021】

上記導電性金属は、銅(Cu)、ニッケル(Ni)、銀(Ag)及び銀−パラジウム(Ag−Pd)からなる群から選択された一つ以上であることができる。

【0022】

本発明は、誘電体層と当該誘電体層を介して対向するように配置される第1及び第2の内部電極とを含むセラミック本体を設ける段階と、上記第1及び第2の内部電極と電気的に連結されるように第1の外部電極を上記セラミック本体の端部に形成する段階と、導電性金属と当該導電性金属100重量部に対して35〜200重量部の含量を有するガラスとを含む外部電極用導電性ペーストを製造する段階と、上記第1の外部電極上に上記外部電極用導電性ペーストを塗布する段階と、上記セラミック本体を焼成して上記第1の外部電極上に第2の外部電極を形成する段階と、を含む積層セラミック電子部品の製造方法を提供する。

【0023】

上記第2の外部電極を厚さ方向に3等分するとき、中央部領域の面積に対して上記ガラスが占める面積が30〜80%であることができる。

【0024】

上記第2の外部電極のガラスの含量に対する上記第1の外部電極のガラスの含量の比が0.5以下であることができる。

【0025】

上記第2の外部電極の中で上記ガラスが占める面積に対する上記第1の外部電極の中で上記ガラスが占める面積の比が0.5以下であることができる。

【0026】

上記第2の外部電極は、平均厚さが5μm以上であり、上記第2の外部電極に含まれるガラスは、絶縁性ガラスであることができる。

【0027】

上記導電性金属は、銅(Cu)、ニッケル(Ni)、銀(Ag)及び銀−パラジウム(Ag−Pd)からなる群から選択された一つ以上であることができる。

【0028】

上記セラミック本体を焼成する段階は、750℃以下で行われることができる。

【発明の効果】

【0029】

本発明によると、ガラスの含量が増加した外部電極用ペーストを用いて外部電極を形成することにより、チップの密閉性を向上させて信頼性が改善された積層セラミック電子部品を具現することができる。

【図面の簡単な説明】

【0030】

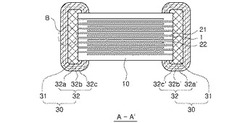

【図1】本発明の一実施形態による積層セラミックキャパシタを概略的に示す斜視図である。

【図2】図1のA−A’線に沿う断面図である。

【図3】図2のB部分の拡大図である。

【図4】本発明の他の実施形態による積層セラミックキャパシタの製造工程図である。

【図5】本発明の実施例(a)及び比較例(b)による積層セラミックキャパシタの外部電極の断面の走査電子顕微鏡(Scanning Electron Microscope、SEM)写真である。

【発明を実施するための形態】

【0031】

以下、添付の図面を参照して本発明の好ましい実施形態を説明する。但し、本発明の実施形態は、多様な他の形態に変形されることができ、本発明の範囲が後述する実施形態に限定されるものではない。また、本発明の実施形態は、当業界における通常の知識を有する者に本発明をより完全に説明するために提供されるものである。したがって、図面における要素の形状及びサイズ等は、より明確な説明のために誇張されることがある。なお、図面上において同一符号で表示される要素は、同一の要素である。

【0032】

図1は、本発明の一実施形態による積層セラミックキャパシタを概略的に示す斜視図であり、図2は、図1のA−A’線に沿う断面図であり、図3は、図2のB部分の拡大図である。

【0033】

図1から図3を参照すると、本発明の一実施形態による積層セラミック電子部品は、誘電体層1を含むセラミック本体10と、上記セラミック本体10内で上記誘電体層1を介して対向するように配置される第1及び第2の内部電極21、22と、上記第1及び第2の内部電極21、22と電気的に連結された第1の外部電極31及び当該第1の外部電極31上に形成された第2の外部電極32と、を含み、上記第1及び第2の外部電極31、32は導電性金属2とガラス3とを含み、上記第2の外部電極32を厚さ方向に3等分するとき、中央部領域32b、32b’の面積に対して上記ガラス3が占める面積が30〜80%であることができる。

【0034】

上記第2の外部電極のガラスの含量に対する上記第1の外部電極のガラスの含量の比が0.5以下であることができる。

【0035】

上記第2の外部電極の中で上記ガラスが占める面積に対する上記第1の外部電極の中で上記ガラスが占める面積の比が0.5以下であることができる。

【0036】

上記第2の外部電極は、平均厚さが5μm以上であり、上記第2の外部電極に含まれるガラスは、絶縁性ガラスであることができる。

【0037】

上記導電性金属は、銅(Cu)、ニッケル(Ni)、銀(Ag)及び銀−パラジウム(Ag−Pd)からなる群から選択された一つ以上であることができる。

【0038】

以下では、本発明の一実施形態による積層セラミック電子部品の一例として積層セラミックキャパシタを例に挙げて説明するが、これに制限されるものではない。

【0039】

図1を参照すると、本発明の一実施形態による積層セラミックキャパシタにおいて、「長さ方向」は「L方向」、「幅方向」は「W方向」、「厚さ方向」は「T方向」と定義される。ここで、「厚さ方向」は、誘電体層を積み重ねる方向、即ち、「積層方向」と同一の概念である。

【0040】

本発明の一実施形態によると、上記誘電体層1の原料は、十分な静電容量が得られるものであれば特に制限されず、例えば、チタン酸バリウム(BaTiO3)粉末であることができる。

【0041】

上記誘電体層1を形成する材料は、チタン酸バリウム(BaTiO3)等のパウダーに、本発明の目的に応じて多様なセラミック添加剤、有機溶剤、可塑剤、結合剤、分散剤等が添加されることができる。

【0042】

上記第1及び第2の内部電極21、22を形成する材料は、特に制限されず、例えば、銀(Ag)、鉛(Pb)、白金(Pt)、ニッケル(Ni)及び銅(Cu)の一つ以上の物質からなる導電性ペーストを用いて上記第1及び第2の内部電極21、22を形成することができる。

【0043】

本発明の一実施形態による積層セラミックキャパシタは、上記第1及び第2の内部電極21、22と電気的に連結された第1の外部電極31を含むことができる。

【0044】

上記第1の外部電極31は、静電容量の形成のために上記第1及び第2の内部電極21、22と電気的に連結されることができる。

【0045】

上記第1の外部電極31は、特に制限されず、例えば、導電性金属2とガラス3とを含むことができる。

【0046】

また、上記積層セラミックキャパシタは、上記第1の外部電極上に形成された第2の外部電極32を含み、上記第2の外部電極32は、導電性金属2とガラス3とを含むことができるが、これに制限されるものではない。

【0047】

上記第2の外部電極32を厚さ方向に3等分するとき、当該第2の外部電極32はそれぞれ三つの領域(32a、32b、32c又は32a’、32b’、32c’)に分けられ、中央部領域32b、32b’の面積に対して上記ガラス3が占める面積が30〜80%であることができる。

【0048】

上記ガラス3が占める面積の測定位置は、特に制限されず、例えば、上記第2の外部電極32を厚さ方向に3等分するとき、中央部領域32b、32b’であることができる。

【0049】

ここで、第2の外部電極の厚さとは、上記積層セラミックキャパシタの長さ方向の両端部から第2の外部電極が形成されている部分までの高さ、及び上記積層セラミックキャパシタの厚さ方向の上面及び下面から第2の外部電極が形成されている部分までの高さを意味することができる。

【0050】

上記ガラス3が占める面積の測定は、特に制限されず、例えば、上記中央部領域32b、32b’での150μm×10μm(横×縦)の面積に対して行われることができる。

【0051】

例えば、上記第2の外部電極32を厚さ方向に3等分するとき、中央部領域32b、32b’の面積に対して上記ガラス3が占める面積は、図2に示されるように積層セラミックキャパシタの長さ方向の断面を走査電子顕微鏡(SEM、Scanning Eletron Microscope)でイメージスキャンすることにより測定されることができる。

【0052】

具体的には、図2に示されるように積層セラミックキャパシタの幅(W)方向の中央部に沿う長さ及び厚さ(L−T)方向の断面を走査電子顕微鏡でスキャンしたイメージから取り出された外部電極領域において、中央部領域32b、32b’の面積に対してガラス3が占める面積を測定して求めることができる。

【0053】

本発明の一実施形態によると、上述したように、上記第1の外部電極31上に当該第1の外部電極31よりガラス3をさらに多く含む第2の外部電極32を形成して外部電極の緻密度を高めることにより、メッキ液の浸透を防止することができる。

【0054】

また、外部電極の焼結温度を低めて導電性金属の焼結を抑制することにより、過剰のガラスによるメッキ不良を防止することができる。

【0055】

上記第2の外部電極32の中央部領域32b、32b’の面積に対して上記ガラス3が占める面積が30%未満の場合は、ガラスの含量が少なくて外部電極の緻密度を高めることができないため、メッキ液が浸透する問題が発生することがある。

【0056】

逆に、上記第2の外部電極32の中央部領域32b、32b’の面積に対して上記ガラス3が占める面積が80%を超える場合は、ガラスが過剰に添加されてガラスの溶出によるメッキ不良が発生することがある。

【0057】

具体的には、本発明の一実施形態によると、上記第2の外部電極32の中で上記ガラスが占める面積に対する上記第1の外部電極31の中で上記ガラスが占める面積の比は、特に制限されず、例えば、0.5以下であることができる。

【0058】

上記第2の外部電極32の中で上記ガラスが占める面積に対する上記第1の外部電極31の中で上記ガラスが占める面積の比が0.5を超える場合は、第1の外部電極に含まれるガラスの含量と第2の外部電極に含まれるガラスの含量の差が大きくないため、外部電極の緻密度上昇及びメッキ不良防止の効果を具現することができない。

【0059】

上記第2の外部電極32は、特に制限されず、例えば、平均厚さが5μm以上であることができる。上記第2の外部電極の平均厚さが5μm未満の場合は、メッキ液が浸透して不良が発生する可能性がある。

【0060】

上記第2の外部電極32に含まれるガラス3は、特に制限されず、例えば、絶縁性ガラスであることができる。

【0061】

上記導電性金属2は、特に制限されず、例えば、銅(Cu)、ニッケル(Ni)、銀(Ag)及び銀−パラジウム(Ag−Pd)からなる群から選択された一つ以上であることができる。

【0062】

本発明の他の実施形態による積層セラミック電子部品は、誘電体層1を含むセラミック本体10と、上記セラミック本体10内で上記誘電体層1を介して対向するように配置される第1及び第2の内部電極21、22と、上記第1及び第2の内部電極21、22と電気的に連結された第1の外部電極31及び当該第1の外部電極31上に形成された第2の外部電極32と、を含み、上記第1及び第2の外部電極31、32は導電性金属とガラスとを含み、上記第2の外部電極32は上記導電性金属100重量部に対して35〜200重量部のガラスを含むことができる。

【0063】

以下、本実施形態による積層セラミック電子部品を説明する上で、前述した一実施形態による積層セラミック電子部品の説明と重複する説明は省略する。

【0064】

具体的には、本発明の一実施形態によると、上記第2の外部電極32は、導電性金属と、当該導電性金属100重量部に対して35〜200重量部の含量を有するガラスと、を含むことができる。

【0065】

上記導電性金属は、特に制限されず、例えば、銅(Cu)、ニッケル(Ni)、銀(Ag)及び銀−パラジウム(Ag−Pd)からなる群から選択された一つ以上であることができる。

【0066】

上記第2の外部電極32が上記導電性金属100重量部に対して35〜200重量部の含量を有するガラスを含むことにより、当該ガラスの含量が極端に増加して外部電極が薄層化しても上記セラミック本体10の密閉性に優れることができる。

【0067】

具体的には、上記ガラスは、導電性金属の焼結を促進させ、上記セラミック本体10と上記外部電極との接着剤の役割をし、特に、導電性金属が充填されない空いている空間に充填されてチップの密閉性を具現する役割をすることができる。

【0068】

本発明の一実施形態によると、上記第2の外部電極32内に含まれる上記ガラスの含量が極端に増加するため、上記セラミック本体10の密閉性に非常に優れることができる。

【0069】

これにより、本発明の一実施形態による積層セラミックキャパシタは、高温絶縁抵抗(Insulation Resistance、IR)特性が向上して信頼性に優れることができる。

【0070】

なお、外部電極の薄層化に伴い、当該外部電極のコーナー部の厚さも薄くなるため、緻密度が低下し、これにより、メッキ液がセラミック本体内に浸透する問題があった。

【0071】

しかしながら、本発明の一実施形態によると、上記外部電極のコーナー部の厚さが薄くなっても上記ガラスの含量が増加して当該コーナー部の緻密度を増加させることができるため、メッキ液の浸透による信頼性低下を防止することができる効果がある。

【0072】

上記ガラスの含量が上記導電性金属100重量部に対して35重量部未満の場合は、ガラスの含量が少ないため、本発明の目的によるセラミック本体の密閉性が得られない問題が生じることがある。

【0073】

また、上記ガラスの含量が上記導電性金属100重量部に対して200重量部を超える場合は、ガラスの含量が多すぎるため、ガラスの溶出によるメッキ不良の問題が生じることがある。

【0074】

図2を参照すると、上記第2の外部電極32を厚さ方向に3等分するとき、中央部領域32b、32b’の面積に対して上記ガラスが占める面積が30〜80%であることができる。

【0075】

本発明の一実施形態によると、上記第2の外部電極32は、増量されたガラスを含むため、当該第2の外部電極32の中央部領域32b、32b’の面積に対して上記ガラスが占める面積が30〜80%であることができる。

【0076】

本発明の他の実施形態による外部電極用導電性ペーストは、導電性金属2とガラス3とを含み、上記ガラスが上記導電性金属100重量部に対して35〜200重量部の含量を有することができる。

【0077】

本発明の一実施形態による積層セラミックキャパシタにおいて、上記第2の外部電極32は、上記外部電極用導電性ペーストで形成されることができる。

【0078】

上記外部電極用導電性ペーストは上記ガラスが上記導電性金属100重量部に対して35〜200重量部の含量を有することができるため、上記セラミック本体10の密閉性を向上させることができる。

【0079】

また、外部電極の焼結温度を低めて導電性金属の焼結を抑制することにより、過剰のガラスによるメッキ不良を防止することができる。

【0080】

図4は、本発明の他の実施形態による積層セラミックキャパシタの製造工程図である。

【0081】

図4を参照すると、本発明の他の実施形態による積層セラミック電子部品の製造方法は、誘電体層1と当該誘電体層1を介して対向するように配置される第1及び第2の内部電極21、22とを含むセラミック本体10を設ける段階と、上記第1及び第2の内部電極21、22と電気的に連結されるように第1の外部電極31を上記セラミック本体10の端部に形成する段階と、導電性金属2と当該導電性金属100重量部に対して35〜200重量部の含量を有するガラス3とを含む外部電極用導電性ペーストを製造する段階と、上記第1の外部電極31上に上記外部電極用導電性ペーストを塗布する段階と、上記セラミック本体を焼成して上記第1の外部電極31上に第2の外部電極32を形成する段階と、を含むことができる。

【0082】

以下、本実施形態による積層セラミック電子部品の製造方法を説明する上で、前述した一実施形態による積層セラミック電子部品と重複する説明は省略する。なお、積層セラミック電子部品の一例として積層セラミックキャパシタを例に挙げて説明するが、これに制限されるものではない。

【0083】

まず、誘電体層1と、当該誘電体層1を介して対向するように配置される第1及び第2の内部電極21、22と、を含むセラミック本体10を設けることができる。

【0084】

上記誘電体層1は、チタン酸バリウム(BaTiO3)等のパウダーをセラミック添加剤、有機溶剤、可塑剤、結合剤、分散剤と配合してバスケットミル(basket mill)を用いて形成されたスラリーをキャリアフィルム(carrier film)上に塗布し乾燥させることにより製造された数μmの厚さのセラミックグリーンシートで形成されることができる。

【0085】

その後、上記セラミックグリーンシート上に導電性ペーストをディスペンシング(dispensing)し、スクイージー(squeegee)を一側方向に進行させながら上記導電性ペーストによる内部電極層を形成することができる。

【0086】

この際、導電性ペーストは、銀(Ag)、鉛(Pb)、白金(Pt)等の貴金属材料及びニッケル(Ni)、銅(Cu)のうち一つの物質で形成されるか又は少なくとも二つの物質を混合して形成されることができる。

【0087】

このように内部電極層が形成されたセラミックグリーンシートをキャリアフィルムから分離した後、当該内部電極層が形成されたセラミックグリーンシートを複数積層して積層体を形成することができる。

【0088】

次いで、上記積層体を高温及び高圧で圧着し、圧着された当該積層体を切断工程により所定のサイズに切断してセラミック本体10を製造することができる。

【0089】

次に、上記第1及び第2の内部電極21、22と電気的に連結されるように第1の外部電極31を上記セラミック本体10の端部に形成することができる。

【0090】

次に、導電性金属2と、当該導電性金属100重量部に対して35〜200重量部の含量を有するガラス3と、を含む外部電極用導電性ペーストを製造することができる。

【0091】

上記導電性金属2は、銅(Cu)、ニッケル(Ni)、銀(Ag)及び銀−パラジウム(Ag−Pd)からなる群から選択された一つ以上であることができる。

【0092】

次に、上記第1の外部電極31上に上記外部電極用導電性ペーストを塗布することができる。

【0093】

最後に、上記セラミック本体10を焼成して上記第1の外部電極31上に第2の外部電極32を形成することができる。

【0094】

上記セラミック本体10を焼成する段階は、750℃以下で行われることができる。

【0095】

本発明の一実施形態によると、上記第2の外部電極32が増量されたガラスを含んでも、上記セラミック本体10を750℃以下の低い温度で焼成するため、ガラスの溶出によるメッキ不良を防止することができる。

【実施例】

【0096】

以下、実施例を挙げて本発明をより詳細に説明するが、本発明がこれに制限されるものではない。

【0097】

本実施例は、導電性金属とガラスとを含む第1の外部電極と、当該第1の外部電極上に形成された、導電性金属と当該導電性金属100重量部に対して35〜200重量部の含量を有するガラスとを含む第2の外部電極と、を含む積層セラミックキャパシタに対し、電極の連結性、メッキ不良の有無、チップ装着不良の有無及び信頼性を試験するために行われた。

【0098】

本実施例による積層セラミックキャパシタは、下記のような段階により製作された。

【0099】

まず、チタン酸バリウム(BaTiO3)等のパウダーを含んで形成されたスラリーをキャリアフィルム上に塗布し乾燥させて複数のセラミックグリーンシートを製造した。

【0100】

その後、ニッケル粒子の平均サイズが0.05〜0.2μmの内部電極用導電性ペーストを製造した。

【0101】

次いで、上記セラミックグリーンシート上に上記内部電極用導電性ペーストをスクリーン印刷工法により塗布して内部電極層を形成した後、当該内部電極層が形成されたセラミックグリーンシートを50層に積層して積層体を製造した。

【0102】

次に、上記積層体を圧着及び切断して2012規格のサイズのチップを製造し、当該チップをH20.1%以下の還元雰囲気下で1050〜1200℃の温度で焼成した。

【0103】

次に、チップの端部に第1の外部電極を形成し、その上に銅(Cu)金属に対するガラスの含量が20、35、70、100、200及び250重量部となるように第2の外部電極を形成した後、メッキ等の工程を経て積層セラミックキャパシタを製作した。

【0104】

下記表1は、積層セラミックキャパシタの外部電極の銅(Cu)金属に対するガラスの含量によるセラミック本体と外部電極との連結性、メッキ不良の有無、チップ装着不良の有無及び信頼性を比較したものである。

【0105】

【表1】

【0106】

表1を参照すると、比較例1は、銅(Cu)金属に対して20重量部の含量を有するガラスを含む場合で、チップ装着不良が発生し、高温絶縁抵抗(Insulation Resistance、IR)テストで問題があることが分かる。

【0107】

また、比較例2は、銅(Cu)金属に対して250重量部の含量を有するガラスを含む場合で、チップ装着不良の問題があることが分かる。

【0108】

これに対し、実施例1〜4は、本発明の数値範囲を満足する場合で、セラミック本体と外部電極との連結性、メッキ不良の有無、チップ装着不良の有無及び信頼性のテストにおいて全て良好な結果を示すことが分かる。

【0109】

図5は、本発明の実施例(a)及び比較例(b)による積層セラミックキャパシタの外部電極の断面の走査電子顕微鏡写真である。

【0110】

図5を参照すると、本発明の一実施形態による実施例(a)の場合、比較例(b)と比較して、第2の外部電極領域に対してガラスが占める面積が非常に大きいことが分かる。

【0111】

以上のように、本発明の一実施形態によると、第2の外部電極が導電性金属と当該導電性金属100重量部に対して35〜200重量部の含量を有するガラスとを含むことにより、セラミック本体と外部電極との連結性に優れ、メッキ不良及びチップ装着不良が発生せず、信頼性に優れた積層セラミック電子部品の具現が可能となる。

【0112】

即ち、本発明によると、チップの密閉性を向上させることにより信頼性が向上した積層セラミック電子部品の具現が可能となる。

【0113】

本発明は、上述した実施形態及び添付の図面によって限定されることなく添付の特許請求の範囲によって限定される。したがって、特許請求の範囲に記載された本発明の技術的思想を逸脱しない範囲内で本発明の属する技術分野における通常の知識を有する者による多様な形態の置換、変形及び変更が可能であり、これもまた本発明の範囲に属する。

【符号の説明】

【0114】

1 誘電体層

2 導電性金属

3 ガラス

10 セラミック本体

21 第1の内部電極

22 第2の内部電極

30 外部電極

31 第1の外部電極

32(32a、32b、32c、32a’、32b’、32c’) 第2の外部電極

【技術分野】

【0001】

本発明は、チップの密閉性を向上させることにより信頼性が改善された積層セラミック電子部品に関する。

【背景技術】

【0002】

近年、電子製品の小型化に伴い、積層セラミック電子部品の小型化及び大容量化も求められており、これにより、当該積層セラミック電子部品の外部電極も薄層化されている。

【0003】

外部電極用ペーストは、主材料として銅(Cu)等の導電性金属を用いてチップの密閉性及び外部電極とチップとの電気的連結性を保障し、補助材料としてガラスを用いて上記導電性金属の焼結収縮時に空いている空間を充填すると共に外部電極とチップとの結合力を与える役割をする。

【0004】

しかしながら、外部電極用ペースト内のガラスの含量が不足する場合、チップの密閉性に問題があることがあり、これを補完するために過剰のガラスを添加する場合、金属の焼結後にガラスが外部電極の表面へ溶出されてメッキ不良が生じる問題がある。

【0005】

特に、外部電極の薄層化に伴い、所望の水準の緻密度を具現するのが困難となり、ガラスの高温挙動特性上、ガラスの不足又は過剰による不良発生の可能性が増加する。

【0006】

また、外部電極用ペーストの塗布厚さが薄い小型の積層セラミック電子部品では、コーナー部分の外部電極の厚さが薄いため、コーナーカバレッジ(corner coverage)性能が低下し、これにより、メッキ液が浸透する問題がある。

【発明の概要】

【発明が解決しようとする課題】

【0007】

本発明の目的は、チップの密閉性を向上させることにより信頼性が改善された積層セラミック電子部品を提供することである。

【課題を解決するための手段】

【0008】

本発明は、誘電体層を含むセラミック本体と、上記セラミック本体内で上記誘電体層を介して対向するように配置される第1及び第2の内部電極と、上記第1及び第2の内部電極と電気的に連結された第1の外部電極及び当該第1の外部電極上に形成された第2の外部電極と、を含み、上記第1及び第2の外部電極は導電性金属とガラスとを含み、上記第2の外部電極を厚さ方向に3等分するとき、中央部領域の面積に対して上記ガラスが占める面積が30〜80%である積層セラミック電子部品を提供する。

【0009】

上記第2の外部電極のガラスの含量に対する上記第1の外部電極のガラスの含量の比が0.5以下であることができる。

【0010】

上記第2の外部電極の中で上記ガラスが占める面積に対する上記第1の外部電極の中で上記ガラスが占める面積の比が0.5以下であることができる。

【0011】

上記第2の外部電極は、平均厚さが5μm以上であり、上記第2の外部電極に含まれるガラスは、絶縁性ガラスであることができる。

【0012】

上記導電性金属は、銅(Cu)、ニッケル(Ni)、銀(Ag)及び銀−パラジウム(Ag−Pd)からなる群から選択された一つ以上であることができる。

【0013】

本発明は、誘電体層を含むセラミック本体と、上記セラミック本体内で上記誘電体層を介して対向するように配置される第1及び第2の内部電極と、上記第1及び第2の内部電極と電気的に連結された第1の外部電極及び当該第1の外部電極上に形成された第2の外部電極と、を含み、上記第1及び第2の外部電極は導電性金属とガラスとを含み、上記第2の外部電極は上記導電性金属100重量部に対して35〜200重量部のガラスを含む積層セラミック電子部品を提供する。

【0014】

上記第2の外部電極のガラスの含量に対する上記第1の外部電極のガラスの含量の比が0.5以下であることができる。

【0015】

上記第2の外部電極の中で上記ガラスが占める面積に対する上記第1の外部電極の中で上記ガラスが占める面積の比が0.5以下であることができる。

【0016】

上記第2の外部電極は、平均厚さが5μm以上であり、上記第2の外部電極に含まれるガラスは、絶縁性ガラスであることができる。

【0017】

上記導電性金属は、銅(Cu)、ニッケル(Ni)、銀(Ag)及び銀−パラジウム(Ag−Pd)からなる群から選択された一つ以上であることができる。

【0018】

上記第2の外部電極を厚さ方向に3等分するとき、中央部領域の面積に対して上記ガラスが占める面積が30〜80%であることができる。

【0019】

本発明は、導電性金属とガラスとを含み、上記ガラスが上記導電性金属100重量部に対して35〜200重量部の含量を有する外部電極用導電性ペーストを提供する。

【0020】

上記ガラスは、絶縁性ガラスであることができる。

【0021】

上記導電性金属は、銅(Cu)、ニッケル(Ni)、銀(Ag)及び銀−パラジウム(Ag−Pd)からなる群から選択された一つ以上であることができる。

【0022】

本発明は、誘電体層と当該誘電体層を介して対向するように配置される第1及び第2の内部電極とを含むセラミック本体を設ける段階と、上記第1及び第2の内部電極と電気的に連結されるように第1の外部電極を上記セラミック本体の端部に形成する段階と、導電性金属と当該導電性金属100重量部に対して35〜200重量部の含量を有するガラスとを含む外部電極用導電性ペーストを製造する段階と、上記第1の外部電極上に上記外部電極用導電性ペーストを塗布する段階と、上記セラミック本体を焼成して上記第1の外部電極上に第2の外部電極を形成する段階と、を含む積層セラミック電子部品の製造方法を提供する。

【0023】

上記第2の外部電極を厚さ方向に3等分するとき、中央部領域の面積に対して上記ガラスが占める面積が30〜80%であることができる。

【0024】

上記第2の外部電極のガラスの含量に対する上記第1の外部電極のガラスの含量の比が0.5以下であることができる。

【0025】

上記第2の外部電極の中で上記ガラスが占める面積に対する上記第1の外部電極の中で上記ガラスが占める面積の比が0.5以下であることができる。

【0026】

上記第2の外部電極は、平均厚さが5μm以上であり、上記第2の外部電極に含まれるガラスは、絶縁性ガラスであることができる。

【0027】

上記導電性金属は、銅(Cu)、ニッケル(Ni)、銀(Ag)及び銀−パラジウム(Ag−Pd)からなる群から選択された一つ以上であることができる。

【0028】

上記セラミック本体を焼成する段階は、750℃以下で行われることができる。

【発明の効果】

【0029】

本発明によると、ガラスの含量が増加した外部電極用ペーストを用いて外部電極を形成することにより、チップの密閉性を向上させて信頼性が改善された積層セラミック電子部品を具現することができる。

【図面の簡単な説明】

【0030】

【図1】本発明の一実施形態による積層セラミックキャパシタを概略的に示す斜視図である。

【図2】図1のA−A’線に沿う断面図である。

【図3】図2のB部分の拡大図である。

【図4】本発明の他の実施形態による積層セラミックキャパシタの製造工程図である。

【図5】本発明の実施例(a)及び比較例(b)による積層セラミックキャパシタの外部電極の断面の走査電子顕微鏡(Scanning Electron Microscope、SEM)写真である。

【発明を実施するための形態】

【0031】

以下、添付の図面を参照して本発明の好ましい実施形態を説明する。但し、本発明の実施形態は、多様な他の形態に変形されることができ、本発明の範囲が後述する実施形態に限定されるものではない。また、本発明の実施形態は、当業界における通常の知識を有する者に本発明をより完全に説明するために提供されるものである。したがって、図面における要素の形状及びサイズ等は、より明確な説明のために誇張されることがある。なお、図面上において同一符号で表示される要素は、同一の要素である。

【0032】

図1は、本発明の一実施形態による積層セラミックキャパシタを概略的に示す斜視図であり、図2は、図1のA−A’線に沿う断面図であり、図3は、図2のB部分の拡大図である。

【0033】

図1から図3を参照すると、本発明の一実施形態による積層セラミック電子部品は、誘電体層1を含むセラミック本体10と、上記セラミック本体10内で上記誘電体層1を介して対向するように配置される第1及び第2の内部電極21、22と、上記第1及び第2の内部電極21、22と電気的に連結された第1の外部電極31及び当該第1の外部電極31上に形成された第2の外部電極32と、を含み、上記第1及び第2の外部電極31、32は導電性金属2とガラス3とを含み、上記第2の外部電極32を厚さ方向に3等分するとき、中央部領域32b、32b’の面積に対して上記ガラス3が占める面積が30〜80%であることができる。

【0034】

上記第2の外部電極のガラスの含量に対する上記第1の外部電極のガラスの含量の比が0.5以下であることができる。

【0035】

上記第2の外部電極の中で上記ガラスが占める面積に対する上記第1の外部電極の中で上記ガラスが占める面積の比が0.5以下であることができる。

【0036】

上記第2の外部電極は、平均厚さが5μm以上であり、上記第2の外部電極に含まれるガラスは、絶縁性ガラスであることができる。

【0037】

上記導電性金属は、銅(Cu)、ニッケル(Ni)、銀(Ag)及び銀−パラジウム(Ag−Pd)からなる群から選択された一つ以上であることができる。

【0038】

以下では、本発明の一実施形態による積層セラミック電子部品の一例として積層セラミックキャパシタを例に挙げて説明するが、これに制限されるものではない。

【0039】

図1を参照すると、本発明の一実施形態による積層セラミックキャパシタにおいて、「長さ方向」は「L方向」、「幅方向」は「W方向」、「厚さ方向」は「T方向」と定義される。ここで、「厚さ方向」は、誘電体層を積み重ねる方向、即ち、「積層方向」と同一の概念である。

【0040】

本発明の一実施形態によると、上記誘電体層1の原料は、十分な静電容量が得られるものであれば特に制限されず、例えば、チタン酸バリウム(BaTiO3)粉末であることができる。

【0041】

上記誘電体層1を形成する材料は、チタン酸バリウム(BaTiO3)等のパウダーに、本発明の目的に応じて多様なセラミック添加剤、有機溶剤、可塑剤、結合剤、分散剤等が添加されることができる。

【0042】

上記第1及び第2の内部電極21、22を形成する材料は、特に制限されず、例えば、銀(Ag)、鉛(Pb)、白金(Pt)、ニッケル(Ni)及び銅(Cu)の一つ以上の物質からなる導電性ペーストを用いて上記第1及び第2の内部電極21、22を形成することができる。

【0043】

本発明の一実施形態による積層セラミックキャパシタは、上記第1及び第2の内部電極21、22と電気的に連結された第1の外部電極31を含むことができる。

【0044】

上記第1の外部電極31は、静電容量の形成のために上記第1及び第2の内部電極21、22と電気的に連結されることができる。

【0045】

上記第1の外部電極31は、特に制限されず、例えば、導電性金属2とガラス3とを含むことができる。

【0046】

また、上記積層セラミックキャパシタは、上記第1の外部電極上に形成された第2の外部電極32を含み、上記第2の外部電極32は、導電性金属2とガラス3とを含むことができるが、これに制限されるものではない。

【0047】

上記第2の外部電極32を厚さ方向に3等分するとき、当該第2の外部電極32はそれぞれ三つの領域(32a、32b、32c又は32a’、32b’、32c’)に分けられ、中央部領域32b、32b’の面積に対して上記ガラス3が占める面積が30〜80%であることができる。

【0048】

上記ガラス3が占める面積の測定位置は、特に制限されず、例えば、上記第2の外部電極32を厚さ方向に3等分するとき、中央部領域32b、32b’であることができる。

【0049】

ここで、第2の外部電極の厚さとは、上記積層セラミックキャパシタの長さ方向の両端部から第2の外部電極が形成されている部分までの高さ、及び上記積層セラミックキャパシタの厚さ方向の上面及び下面から第2の外部電極が形成されている部分までの高さを意味することができる。

【0050】

上記ガラス3が占める面積の測定は、特に制限されず、例えば、上記中央部領域32b、32b’での150μm×10μm(横×縦)の面積に対して行われることができる。

【0051】

例えば、上記第2の外部電極32を厚さ方向に3等分するとき、中央部領域32b、32b’の面積に対して上記ガラス3が占める面積は、図2に示されるように積層セラミックキャパシタの長さ方向の断面を走査電子顕微鏡(SEM、Scanning Eletron Microscope)でイメージスキャンすることにより測定されることができる。

【0052】

具体的には、図2に示されるように積層セラミックキャパシタの幅(W)方向の中央部に沿う長さ及び厚さ(L−T)方向の断面を走査電子顕微鏡でスキャンしたイメージから取り出された外部電極領域において、中央部領域32b、32b’の面積に対してガラス3が占める面積を測定して求めることができる。

【0053】

本発明の一実施形態によると、上述したように、上記第1の外部電極31上に当該第1の外部電極31よりガラス3をさらに多く含む第2の外部電極32を形成して外部電極の緻密度を高めることにより、メッキ液の浸透を防止することができる。

【0054】

また、外部電極の焼結温度を低めて導電性金属の焼結を抑制することにより、過剰のガラスによるメッキ不良を防止することができる。

【0055】

上記第2の外部電極32の中央部領域32b、32b’の面積に対して上記ガラス3が占める面積が30%未満の場合は、ガラスの含量が少なくて外部電極の緻密度を高めることができないため、メッキ液が浸透する問題が発生することがある。

【0056】

逆に、上記第2の外部電極32の中央部領域32b、32b’の面積に対して上記ガラス3が占める面積が80%を超える場合は、ガラスが過剰に添加されてガラスの溶出によるメッキ不良が発生することがある。

【0057】

具体的には、本発明の一実施形態によると、上記第2の外部電極32の中で上記ガラスが占める面積に対する上記第1の外部電極31の中で上記ガラスが占める面積の比は、特に制限されず、例えば、0.5以下であることができる。

【0058】

上記第2の外部電極32の中で上記ガラスが占める面積に対する上記第1の外部電極31の中で上記ガラスが占める面積の比が0.5を超える場合は、第1の外部電極に含まれるガラスの含量と第2の外部電極に含まれるガラスの含量の差が大きくないため、外部電極の緻密度上昇及びメッキ不良防止の効果を具現することができない。

【0059】

上記第2の外部電極32は、特に制限されず、例えば、平均厚さが5μm以上であることができる。上記第2の外部電極の平均厚さが5μm未満の場合は、メッキ液が浸透して不良が発生する可能性がある。

【0060】

上記第2の外部電極32に含まれるガラス3は、特に制限されず、例えば、絶縁性ガラスであることができる。

【0061】

上記導電性金属2は、特に制限されず、例えば、銅(Cu)、ニッケル(Ni)、銀(Ag)及び銀−パラジウム(Ag−Pd)からなる群から選択された一つ以上であることができる。

【0062】

本発明の他の実施形態による積層セラミック電子部品は、誘電体層1を含むセラミック本体10と、上記セラミック本体10内で上記誘電体層1を介して対向するように配置される第1及び第2の内部電極21、22と、上記第1及び第2の内部電極21、22と電気的に連結された第1の外部電極31及び当該第1の外部電極31上に形成された第2の外部電極32と、を含み、上記第1及び第2の外部電極31、32は導電性金属とガラスとを含み、上記第2の外部電極32は上記導電性金属100重量部に対して35〜200重量部のガラスを含むことができる。

【0063】

以下、本実施形態による積層セラミック電子部品を説明する上で、前述した一実施形態による積層セラミック電子部品の説明と重複する説明は省略する。

【0064】

具体的には、本発明の一実施形態によると、上記第2の外部電極32は、導電性金属と、当該導電性金属100重量部に対して35〜200重量部の含量を有するガラスと、を含むことができる。

【0065】

上記導電性金属は、特に制限されず、例えば、銅(Cu)、ニッケル(Ni)、銀(Ag)及び銀−パラジウム(Ag−Pd)からなる群から選択された一つ以上であることができる。

【0066】

上記第2の外部電極32が上記導電性金属100重量部に対して35〜200重量部の含量を有するガラスを含むことにより、当該ガラスの含量が極端に増加して外部電極が薄層化しても上記セラミック本体10の密閉性に優れることができる。

【0067】

具体的には、上記ガラスは、導電性金属の焼結を促進させ、上記セラミック本体10と上記外部電極との接着剤の役割をし、特に、導電性金属が充填されない空いている空間に充填されてチップの密閉性を具現する役割をすることができる。

【0068】

本発明の一実施形態によると、上記第2の外部電極32内に含まれる上記ガラスの含量が極端に増加するため、上記セラミック本体10の密閉性に非常に優れることができる。

【0069】

これにより、本発明の一実施形態による積層セラミックキャパシタは、高温絶縁抵抗(Insulation Resistance、IR)特性が向上して信頼性に優れることができる。

【0070】

なお、外部電極の薄層化に伴い、当該外部電極のコーナー部の厚さも薄くなるため、緻密度が低下し、これにより、メッキ液がセラミック本体内に浸透する問題があった。

【0071】

しかしながら、本発明の一実施形態によると、上記外部電極のコーナー部の厚さが薄くなっても上記ガラスの含量が増加して当該コーナー部の緻密度を増加させることができるため、メッキ液の浸透による信頼性低下を防止することができる効果がある。

【0072】

上記ガラスの含量が上記導電性金属100重量部に対して35重量部未満の場合は、ガラスの含量が少ないため、本発明の目的によるセラミック本体の密閉性が得られない問題が生じることがある。

【0073】

また、上記ガラスの含量が上記導電性金属100重量部に対して200重量部を超える場合は、ガラスの含量が多すぎるため、ガラスの溶出によるメッキ不良の問題が生じることがある。

【0074】

図2を参照すると、上記第2の外部電極32を厚さ方向に3等分するとき、中央部領域32b、32b’の面積に対して上記ガラスが占める面積が30〜80%であることができる。

【0075】

本発明の一実施形態によると、上記第2の外部電極32は、増量されたガラスを含むため、当該第2の外部電極32の中央部領域32b、32b’の面積に対して上記ガラスが占める面積が30〜80%であることができる。

【0076】

本発明の他の実施形態による外部電極用導電性ペーストは、導電性金属2とガラス3とを含み、上記ガラスが上記導電性金属100重量部に対して35〜200重量部の含量を有することができる。

【0077】

本発明の一実施形態による積層セラミックキャパシタにおいて、上記第2の外部電極32は、上記外部電極用導電性ペーストで形成されることができる。

【0078】

上記外部電極用導電性ペーストは上記ガラスが上記導電性金属100重量部に対して35〜200重量部の含量を有することができるため、上記セラミック本体10の密閉性を向上させることができる。

【0079】

また、外部電極の焼結温度を低めて導電性金属の焼結を抑制することにより、過剰のガラスによるメッキ不良を防止することができる。

【0080】

図4は、本発明の他の実施形態による積層セラミックキャパシタの製造工程図である。

【0081】

図4を参照すると、本発明の他の実施形態による積層セラミック電子部品の製造方法は、誘電体層1と当該誘電体層1を介して対向するように配置される第1及び第2の内部電極21、22とを含むセラミック本体10を設ける段階と、上記第1及び第2の内部電極21、22と電気的に連結されるように第1の外部電極31を上記セラミック本体10の端部に形成する段階と、導電性金属2と当該導電性金属100重量部に対して35〜200重量部の含量を有するガラス3とを含む外部電極用導電性ペーストを製造する段階と、上記第1の外部電極31上に上記外部電極用導電性ペーストを塗布する段階と、上記セラミック本体を焼成して上記第1の外部電極31上に第2の外部電極32を形成する段階と、を含むことができる。

【0082】

以下、本実施形態による積層セラミック電子部品の製造方法を説明する上で、前述した一実施形態による積層セラミック電子部品と重複する説明は省略する。なお、積層セラミック電子部品の一例として積層セラミックキャパシタを例に挙げて説明するが、これに制限されるものではない。

【0083】

まず、誘電体層1と、当該誘電体層1を介して対向するように配置される第1及び第2の内部電極21、22と、を含むセラミック本体10を設けることができる。

【0084】

上記誘電体層1は、チタン酸バリウム(BaTiO3)等のパウダーをセラミック添加剤、有機溶剤、可塑剤、結合剤、分散剤と配合してバスケットミル(basket mill)を用いて形成されたスラリーをキャリアフィルム(carrier film)上に塗布し乾燥させることにより製造された数μmの厚さのセラミックグリーンシートで形成されることができる。

【0085】

その後、上記セラミックグリーンシート上に導電性ペーストをディスペンシング(dispensing)し、スクイージー(squeegee)を一側方向に進行させながら上記導電性ペーストによる内部電極層を形成することができる。

【0086】

この際、導電性ペーストは、銀(Ag)、鉛(Pb)、白金(Pt)等の貴金属材料及びニッケル(Ni)、銅(Cu)のうち一つの物質で形成されるか又は少なくとも二つの物質を混合して形成されることができる。

【0087】

このように内部電極層が形成されたセラミックグリーンシートをキャリアフィルムから分離した後、当該内部電極層が形成されたセラミックグリーンシートを複数積層して積層体を形成することができる。

【0088】

次いで、上記積層体を高温及び高圧で圧着し、圧着された当該積層体を切断工程により所定のサイズに切断してセラミック本体10を製造することができる。

【0089】

次に、上記第1及び第2の内部電極21、22と電気的に連結されるように第1の外部電極31を上記セラミック本体10の端部に形成することができる。

【0090】

次に、導電性金属2と、当該導電性金属100重量部に対して35〜200重量部の含量を有するガラス3と、を含む外部電極用導電性ペーストを製造することができる。

【0091】

上記導電性金属2は、銅(Cu)、ニッケル(Ni)、銀(Ag)及び銀−パラジウム(Ag−Pd)からなる群から選択された一つ以上であることができる。

【0092】

次に、上記第1の外部電極31上に上記外部電極用導電性ペーストを塗布することができる。

【0093】

最後に、上記セラミック本体10を焼成して上記第1の外部電極31上に第2の外部電極32を形成することができる。

【0094】

上記セラミック本体10を焼成する段階は、750℃以下で行われることができる。

【0095】

本発明の一実施形態によると、上記第2の外部電極32が増量されたガラスを含んでも、上記セラミック本体10を750℃以下の低い温度で焼成するため、ガラスの溶出によるメッキ不良を防止することができる。

【実施例】

【0096】

以下、実施例を挙げて本発明をより詳細に説明するが、本発明がこれに制限されるものではない。

【0097】

本実施例は、導電性金属とガラスとを含む第1の外部電極と、当該第1の外部電極上に形成された、導電性金属と当該導電性金属100重量部に対して35〜200重量部の含量を有するガラスとを含む第2の外部電極と、を含む積層セラミックキャパシタに対し、電極の連結性、メッキ不良の有無、チップ装着不良の有無及び信頼性を試験するために行われた。

【0098】

本実施例による積層セラミックキャパシタは、下記のような段階により製作された。

【0099】

まず、チタン酸バリウム(BaTiO3)等のパウダーを含んで形成されたスラリーをキャリアフィルム上に塗布し乾燥させて複数のセラミックグリーンシートを製造した。

【0100】

その後、ニッケル粒子の平均サイズが0.05〜0.2μmの内部電極用導電性ペーストを製造した。

【0101】

次いで、上記セラミックグリーンシート上に上記内部電極用導電性ペーストをスクリーン印刷工法により塗布して内部電極層を形成した後、当該内部電極層が形成されたセラミックグリーンシートを50層に積層して積層体を製造した。

【0102】

次に、上記積層体を圧着及び切断して2012規格のサイズのチップを製造し、当該チップをH20.1%以下の還元雰囲気下で1050〜1200℃の温度で焼成した。

【0103】

次に、チップの端部に第1の外部電極を形成し、その上に銅(Cu)金属に対するガラスの含量が20、35、70、100、200及び250重量部となるように第2の外部電極を形成した後、メッキ等の工程を経て積層セラミックキャパシタを製作した。

【0104】

下記表1は、積層セラミックキャパシタの外部電極の銅(Cu)金属に対するガラスの含量によるセラミック本体と外部電極との連結性、メッキ不良の有無、チップ装着不良の有無及び信頼性を比較したものである。

【0105】

【表1】

【0106】

表1を参照すると、比較例1は、銅(Cu)金属に対して20重量部の含量を有するガラスを含む場合で、チップ装着不良が発生し、高温絶縁抵抗(Insulation Resistance、IR)テストで問題があることが分かる。

【0107】

また、比較例2は、銅(Cu)金属に対して250重量部の含量を有するガラスを含む場合で、チップ装着不良の問題があることが分かる。

【0108】

これに対し、実施例1〜4は、本発明の数値範囲を満足する場合で、セラミック本体と外部電極との連結性、メッキ不良の有無、チップ装着不良の有無及び信頼性のテストにおいて全て良好な結果を示すことが分かる。

【0109】

図5は、本発明の実施例(a)及び比較例(b)による積層セラミックキャパシタの外部電極の断面の走査電子顕微鏡写真である。

【0110】

図5を参照すると、本発明の一実施形態による実施例(a)の場合、比較例(b)と比較して、第2の外部電極領域に対してガラスが占める面積が非常に大きいことが分かる。

【0111】

以上のように、本発明の一実施形態によると、第2の外部電極が導電性金属と当該導電性金属100重量部に対して35〜200重量部の含量を有するガラスとを含むことにより、セラミック本体と外部電極との連結性に優れ、メッキ不良及びチップ装着不良が発生せず、信頼性に優れた積層セラミック電子部品の具現が可能となる。

【0112】

即ち、本発明によると、チップの密閉性を向上させることにより信頼性が向上した積層セラミック電子部品の具現が可能となる。

【0113】

本発明は、上述した実施形態及び添付の図面によって限定されることなく添付の特許請求の範囲によって限定される。したがって、特許請求の範囲に記載された本発明の技術的思想を逸脱しない範囲内で本発明の属する技術分野における通常の知識を有する者による多様な形態の置換、変形及び変更が可能であり、これもまた本発明の範囲に属する。

【符号の説明】

【0114】

1 誘電体層

2 導電性金属

3 ガラス

10 セラミック本体

21 第1の内部電極

22 第2の内部電極

30 外部電極

31 第1の外部電極

32(32a、32b、32c、32a’、32b’、32c’) 第2の外部電極

【特許請求の範囲】

【請求項1】

誘電体層を含むセラミック本体と、

前記セラミック本体内で前記誘電体層を介して対向するように配置される第1及び第2の内部電極と、

前記第1及び第2の内部電極と電気的に連結された第1の外部電極及び当該第1の外部電極上に形成された第2の外部電極と、

を含み、

前記第1及び第2の外部電極は導電性金属とガラスとを含み、前記第2の外部電極を厚さ方向に3等分するとき、中央部領域の面積に対して前記ガラスが占める面積が30〜80%である、積層セラミック電子部品。

【請求項2】

前記第2の外部電極のガラスの含量に対する前記第1の外部電極のガラスの含量の比が0.5以下である、請求項1に記載の積層セラミック電子部品。

【請求項3】

前記第2の外部電極の中で前記ガラスが占める面積に対する前記第1の外部電極の中で前記ガラスが占める面積の比が0.5以下である、請求項1に記載の積層セラミック電子部品。

【請求項4】

前記第2の外部電極は、平均厚さが5μm以上である、請求項1に記載の積層セラミック電子部品。

【請求項5】

前記第2の外部電極に含まれるガラスは、絶縁性ガラスである、請求項1に記載の積層セラミック電子部品。

【請求項6】

前記導電性金属は、銅(Cu)、ニッケル(Ni)、銀(Ag)及び銀−パラジウム(Ag−Pd)からなる群から選択された一つ以上である、請求項1に記載の積層セラミック電子部品。

【請求項7】

誘電体層を含むセラミック本体と、

前記セラミック本体内で前記誘電体層を介して対向するように配置される第1及び第2の内部電極と、

前記第1及び第2の内部電極と電気的に連結された第1の外部電極及び当該第1の外部電極上に形成された第2の外部電極と、

を含み、

前記第1及び第2の外部電極は導電性金属とガラスとを含み、前記第2の外部電極は前記導電性金属100重量部に対して35〜200重量部のガラスを含む、積層セラミック電子部品。

【請求項8】

前記第2の外部電極のガラスの含量に対する前記第1の外部電極のガラスの含量の比が0.5以下である、請求項7に記載の積層セラミック電子部品。

【請求項9】

前記第2の外部電極の中で前記ガラスが占める面積に対する前記第1の外部電極の中で前記ガラスが占める面積の比が0.5以下である、請求項7に記載の積層セラミック電子部品。

【請求項10】

前記第2の外部電極は、平均厚さが5μm以上である、請求項7に記載の積層セラミック電子部品。

【請求項11】

前記第2の外部電極に含まれるガラスは、絶縁性ガラスである、請求項7に記載の積層セラミック電子部品。

【請求項12】

前記導電性金属は、銅(Cu)、ニッケル(Ni)、銀(Ag)及び銀−パラジウム(Ag−Pd)からなる群から選択された一つ以上である、請求項7に記載の積層セラミック電子部品。

【請求項13】

前記第2の外部電極を厚さ方向に3等分するとき、中央部領域の面積に対して前記ガラスが占める面積が30〜80%である、請求項7に記載の積層セラミック電子部品。

【請求項14】

導電性金属とガラスとを含み、前記ガラスが前記導電性金属100重量部に対して35〜200重量部の含量を有する、外部電極用導電性ペースト。

【請求項15】

前記ガラスは、絶縁性ガラスである、請求項14に記載の外部電極用導電性ペースト。

【請求項16】

前記導電性金属は、銅(Cu)、ニッケル(Ni)、銀(Ag)及び銀−パラジウム(Ag−Pd)からなる群から選択された一つ以上である、請求項14に記載の外部電極用導電性ペースト。

【請求項17】

誘電体層と当該誘電体層を介して対向するように配置される第1及び第2の内部電極とを含むセラミック本体を設ける段階と、

前記第1及び第2の内部電極と電気的に連結されるように第1の外部電極を前記セラミック本体の端部に形成する段階と、

導電性金属と当該導電性金属100重量部に対して35〜200重量部の含量を有するガラスとを含む外部電極用導電性ペーストを製造する段階と、

前記第1の外部電極上に前記外部電極用導電性ペーストを塗布する段階と、

前記セラミック本体を焼成して前記第1の外部電極上に第2の外部電極を形成する段階と、

を含む、積層セラミック電子部品の製造方法。

【請求項18】

前記第2の外部電極を厚さ方向に3等分するとき、中央部領域の面積に対して前記ガラスが占める面積が30〜80%である、請求項17に記載の積層セラミック電子部品の製造方法。

【請求項19】

前記第2の外部電極のガラスの含量に対する前記第1の外部電極のガラスの含量の比が0.5以下である、請求項17に記載の積層セラミック電子部品の製造方法。

【請求項20】

前記第2の外部電極の中で前記ガラスが占める面積に対する前記第1の外部電極の中で前記ガラスが占める面積の比が0.5以下である、請求項17に記載の積層セラミック電子部品の製造方法。

【請求項21】

前記第2の外部電極は、平均厚さが5μm以上である、請求項17に記載の積層セラミック電子部品の製造方法。

【請求項22】

前記第2の外部電極に含まれるガラスは、絶縁性ガラスである、請求項17に記載の積層セラミック電子部品の製造方法。

【請求項23】

前記導電性金属は、銅(Cu)、ニッケル(Ni)、銀(Ag)及び銀−パラジウム(Ag−Pd)からなる群から選択された一つ以上である、請求項17に記載の積層セラミック電子部品の製造方法。

【請求項24】

前記セラミック本体を焼成する段階は、750℃以下で行われる、請求項17に記載の積層セラミック電子部品の製造方法。

【請求項1】

誘電体層を含むセラミック本体と、

前記セラミック本体内で前記誘電体層を介して対向するように配置される第1及び第2の内部電極と、

前記第1及び第2の内部電極と電気的に連結された第1の外部電極及び当該第1の外部電極上に形成された第2の外部電極と、

を含み、

前記第1及び第2の外部電極は導電性金属とガラスとを含み、前記第2の外部電極を厚さ方向に3等分するとき、中央部領域の面積に対して前記ガラスが占める面積が30〜80%である、積層セラミック電子部品。

【請求項2】

前記第2の外部電極のガラスの含量に対する前記第1の外部電極のガラスの含量の比が0.5以下である、請求項1に記載の積層セラミック電子部品。

【請求項3】

前記第2の外部電極の中で前記ガラスが占める面積に対する前記第1の外部電極の中で前記ガラスが占める面積の比が0.5以下である、請求項1に記載の積層セラミック電子部品。

【請求項4】

前記第2の外部電極は、平均厚さが5μm以上である、請求項1に記載の積層セラミック電子部品。

【請求項5】

前記第2の外部電極に含まれるガラスは、絶縁性ガラスである、請求項1に記載の積層セラミック電子部品。

【請求項6】

前記導電性金属は、銅(Cu)、ニッケル(Ni)、銀(Ag)及び銀−パラジウム(Ag−Pd)からなる群から選択された一つ以上である、請求項1に記載の積層セラミック電子部品。

【請求項7】

誘電体層を含むセラミック本体と、

前記セラミック本体内で前記誘電体層を介して対向するように配置される第1及び第2の内部電極と、

前記第1及び第2の内部電極と電気的に連結された第1の外部電極及び当該第1の外部電極上に形成された第2の外部電極と、

を含み、

前記第1及び第2の外部電極は導電性金属とガラスとを含み、前記第2の外部電極は前記導電性金属100重量部に対して35〜200重量部のガラスを含む、積層セラミック電子部品。

【請求項8】

前記第2の外部電極のガラスの含量に対する前記第1の外部電極のガラスの含量の比が0.5以下である、請求項7に記載の積層セラミック電子部品。

【請求項9】

前記第2の外部電極の中で前記ガラスが占める面積に対する前記第1の外部電極の中で前記ガラスが占める面積の比が0.5以下である、請求項7に記載の積層セラミック電子部品。

【請求項10】

前記第2の外部電極は、平均厚さが5μm以上である、請求項7に記載の積層セラミック電子部品。

【請求項11】

前記第2の外部電極に含まれるガラスは、絶縁性ガラスである、請求項7に記載の積層セラミック電子部品。

【請求項12】

前記導電性金属は、銅(Cu)、ニッケル(Ni)、銀(Ag)及び銀−パラジウム(Ag−Pd)からなる群から選択された一つ以上である、請求項7に記載の積層セラミック電子部品。

【請求項13】

前記第2の外部電極を厚さ方向に3等分するとき、中央部領域の面積に対して前記ガラスが占める面積が30〜80%である、請求項7に記載の積層セラミック電子部品。

【請求項14】

導電性金属とガラスとを含み、前記ガラスが前記導電性金属100重量部に対して35〜200重量部の含量を有する、外部電極用導電性ペースト。

【請求項15】

前記ガラスは、絶縁性ガラスである、請求項14に記載の外部電極用導電性ペースト。

【請求項16】

前記導電性金属は、銅(Cu)、ニッケル(Ni)、銀(Ag)及び銀−パラジウム(Ag−Pd)からなる群から選択された一つ以上である、請求項14に記載の外部電極用導電性ペースト。

【請求項17】

誘電体層と当該誘電体層を介して対向するように配置される第1及び第2の内部電極とを含むセラミック本体を設ける段階と、

前記第1及び第2の内部電極と電気的に連結されるように第1の外部電極を前記セラミック本体の端部に形成する段階と、

導電性金属と当該導電性金属100重量部に対して35〜200重量部の含量を有するガラスとを含む外部電極用導電性ペーストを製造する段階と、

前記第1の外部電極上に前記外部電極用導電性ペーストを塗布する段階と、

前記セラミック本体を焼成して前記第1の外部電極上に第2の外部電極を形成する段階と、

を含む、積層セラミック電子部品の製造方法。

【請求項18】

前記第2の外部電極を厚さ方向に3等分するとき、中央部領域の面積に対して前記ガラスが占める面積が30〜80%である、請求項17に記載の積層セラミック電子部品の製造方法。

【請求項19】

前記第2の外部電極のガラスの含量に対する前記第1の外部電極のガラスの含量の比が0.5以下である、請求項17に記載の積層セラミック電子部品の製造方法。

【請求項20】

前記第2の外部電極の中で前記ガラスが占める面積に対する前記第1の外部電極の中で前記ガラスが占める面積の比が0.5以下である、請求項17に記載の積層セラミック電子部品の製造方法。

【請求項21】

前記第2の外部電極は、平均厚さが5μm以上である、請求項17に記載の積層セラミック電子部品の製造方法。

【請求項22】

前記第2の外部電極に含まれるガラスは、絶縁性ガラスである、請求項17に記載の積層セラミック電子部品の製造方法。

【請求項23】

前記導電性金属は、銅(Cu)、ニッケル(Ni)、銀(Ag)及び銀−パラジウム(Ag−Pd)からなる群から選択された一つ以上である、請求項17に記載の積層セラミック電子部品の製造方法。

【請求項24】

前記セラミック本体を焼成する段階は、750℃以下で行われる、請求項17に記載の積層セラミック電子部品の製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図2】

【図3】

【図4】

【図5】

【公開番号】特開2013−106035(P2013−106035A)

【公開日】平成25年5月30日(2013.5.30)

【国際特許分類】

【出願番号】特願2012−164492(P2012−164492)

【出願日】平成24年7月25日(2012.7.25)

【出願人】(594023722)サムソン エレクトロ−メカニックス カンパニーリミテッド. (1,585)

【Fターム(参考)】

【公開日】平成25年5月30日(2013.5.30)

【国際特許分類】

【出願日】平成24年7月25日(2012.7.25)

【出願人】(594023722)サムソン エレクトロ−メカニックス カンパニーリミテッド. (1,585)

【Fターム(参考)】

[ Back to top ]