積層セラミック電子部品

【課題】アレイタイプの積層セラミックコンデンサでは、取り出す容量の個数に対応した数の内部電極を共通のセラミック層上に配置するため、1つの内部電極の面積を広げることに限界がある。

【解決手段】セラミック素体2の内部において、高さ方向に沿って隣接するように第1の機能部26と第2の機能部31とが配置され、第1の機能部26において、第1および第2の内部電極3,4がセラミック層21を介して対向し、第2の機能部において、第1および第2の内部電極3,4とは積層枚数が異なる第3および第4の内部電極5,6がセラミック層21を介して対向する。第1および/または第2の内部電極と同一の面上にマーク用内部導体が配置され、セラミック素体2の側面上において、露出した複数のマーク用内部導体を連結するようにマーク用外部導体を配置し、上下の方向性を認識可能とする。

【解決手段】セラミック素体2の内部において、高さ方向に沿って隣接するように第1の機能部26と第2の機能部31とが配置され、第1の機能部26において、第1および第2の内部電極3,4がセラミック層21を介して対向し、第2の機能部において、第1および第2の内部電極3,4とは積層枚数が異なる第3および第4の内部電極5,6がセラミック層21を介して対向する。第1および/または第2の内部電極と同一の面上にマーク用内部導体が配置され、セラミック素体2の側面上において、露出した複数のマーク用内部導体を連結するようにマーク用外部導体を配置し、上下の方向性を認識可能とする。

【発明の詳細な説明】

【技術分野】

【0001】

この発明は、積層セラミック電子部品に関するものであり、特に、アレイタイプの積層セラミック電子部品のように、1個の部品本体内に複数の機能部を有する積層セラミック電子部品に関するものである。

【背景技術】

【0002】

近年、携帯電話機や、携帯音楽プレイヤーなどをはじめとする電子機器の小型化が進むにつれて、電子機器に搭載される実装基板の小型化が進んできている。

【0003】

また、実装基板の小型化に伴い、当然のことながら、実装基板での実装面積も狭くなってきている。このため、実装基板に実装される電子部品に対する小型化の要求が強まってきており、複数の電子部品素子をワンチップ化したアレイタイプの電子部品もしばしば用いられるようになってきている。

【0004】

アレイタイプの電子部品を用いることにより、複数の電子部品を実装する場合と比べて、実装スペースを小さくできるだけでなく、実装コストも低減することができる。

【0005】

アレイタイプの電子部品、特に積層セラミック電子部品の代表例としては、コンデンサアレイを挙げることができる。一般的なコンデンサアレイでは、たとえば、1つの側面に4個ずつ外部電極が形成され、対向する外部電極間で4個の容量が取り出される。

【0006】

通常、コンデンサアレイから取り出される複数の容量は、互いに同じであることが多い。しかし、回路設計の都合上、これらの容量を互いに異ならせることが望まれる場合もある。これを受けて、特許文献1では、各容量部を構成する内部電極の面積を互いに異ならせることにより、互いに異なる容量を取り出すことが提案されている。

【先行技術文献】

【特許文献】

【0007】

【特許文献1】特開2003−257785号公報

【発明の概要】

【発明が解決しようとする課題】

【0008】

しかし、特許文献1に記載の構造では、取り出す容量の個数に対応した数の内部電極を共通のセラミック層上に配置するため、1つの内部電極の面積を広げることに限界がある。

【0009】

そこで、この発明の目的は、上記のような問題を解決し得る、積層セラミック電子部品を提供しようとすることである。

【課題を解決するための手段】

【0010】

この発明に係る積層セラミック電子部品は、複数の積層されたセラミック層からなり、互いに対向する1対の主面と主面間を結ぶ側面とを有する、セラミック素体と、セラミック素体の内部に配置された、第1ないし第4の内部電極と、セラミック素体の側面上に配置され、第1ないし第4の内部電極にそれぞれ電気的に接続された、第1ないし第4の外部電極と、を備えており、以下のような特徴を有している。

【0011】

セラミック素体の内部において、主面間を結ぶ高さ方向に沿って隣接するように、第1の機能部と第2の機能部とが配置されており、第1の機能部において、第1および第2の内部電極がセラミック層を介して高さ方向に対向し、第2の機能部において、第3および第4の内部電極がセラミック層を介して高さ方向に対向している。

【0012】

また、第1の機能部における第1および第2の内部電極の合計の積層枚数と、第2の機能部における第3および第4の内部電極の合計の積層枚数と、が異なっている。

【0013】

そして、この発明に係る積層セラミック電子部品は、第1および第2の内部電極のうち少なくとも一方と同一の面上に配置され、かつ側面に露出した、第1のマーク用内部導体と、側面上において、露出した複数の第1のマーク用内部導体を連結するようにして配置された、第1のマーク用外部導体と、をさらに備えている。

【0014】

この発明に係る積層セラミック電子部品は、好ましくは、第3および第4の内部電極のうち少なくとも一方と同一の面上に配置され、かつ側面に露出した、第2のマーク用内部導体と、側面上において、露出した複数の第2のマーク用内部導体を連結するようにして配置された、第2のマーク用外部導体とをさらに備え、第1の機能部における第1および第2の内部電極の合計の積層枚数が、第2の機能部における第3および第4の内部電極の合計の積層枚数よりも多く、高さ方向に沿った第1のマーク用外部導体の寸法が、高さ方向に沿った第2のマーク用外部導体の寸法よりも長い。

【0015】

なお、上述したように、この発明に係る積層セラミック電子部品は、第1および第2の機能部を備えるものであるが、第1および第2の機能部以外の少なくとも1個の機能部をさらに備えていてもよい。また、第1の機能部を構成するものが、第1および第2の内部電極ならびに第1および第2の外部電極であるが、第1の機能部において、第1および第2の内部電極以外の少なくとも1個の内部電極をさらに備えていても、第1および第2の外部電極以外の少なくとも1個の外部電極をさらに備えていてもよい。同様に、第2の機能部を構成するものが、第3および第4の内部電極ならびに第3および第4の外部電極であるが、第2の機能部において、第3および第4の内部電極以外の少なくとも1個の内部電極をさらに備えていても、第3および第4の外部電極以外の少なくとも1個の外部電極をさらに備えていてもよい。

【発明の効果】

【0016】

この発明に係る積層セラミック電子部品によれば、高さ方向に沿って複数の機能部が配置されるため、各機能部において、共通のセラミック層上に配置する内部電極の数を減らし、内部電極の各面積を広げることができる。

【0017】

また、この発明に係る積層セラミック電子部品においては、内部電極の合計の積層枚数の多少によって、各機能部の特性を異ならせることができる。このように、各機能部間で特性の差異が生じた場合、この積層セラミック電子部品では上下の方向性が生じるが、この方向性は少なくとも第1のマーク用外部導体を認識することによって識別することができる。

【0018】

この発明において、第2のマーク用外部導体をさらに備え、高さ方向に沿った第1のマーク用外部導体の寸法が、高さ方向に沿った第2のマーク用外部導体の寸法よりも長くされると、上述の方向性をより確実かつより容易に識別することができる。

【図面の簡単な説明】

【0019】

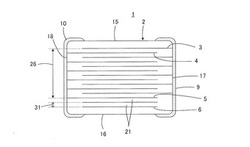

【図1】この発明の第1の実施形態による積層セラミック電子部品としての積層セラミックコンデンサ1の外観を示す斜視図である。

【図2】図1に示した積層セラミックコンデンサ1の上面図である。

【図3】図1に示した積層セラミックコンデンサ1の右側面図である。

【図4】図1に示した積層セラミックコンデンサ1の左側面図である。

【図5】図2の線A−Aに沿う断面図である。

【図6】図2の線B−Bに沿う断面図である。

【図7】図1に示した積層セラミックコンデンサ1の、セラミック素体2の主面15および16に平行な面に沿う切断部端面図であり、第1の内部電極3が延びる面を示す。

【図8】図1に示した積層セラミックコンデンサ1の、セラミック素体2の主面15および16に平行な面に沿う切断部端面図であり、第2の内部電極4が延びる面を示す。

【図9】図1に示した積層セラミックコンデンサ1の、セラミック素体2の主面15および16に平行な面に沿う切断部端面図であり、第3の内部電極5が延びる面を示す。

【図10】図1に示した積層セラミックコンデンサ1の、セラミック素体2の主面15および16に平行な面に沿う切断部端面図であり、第4の内部電極6が延びる面を示す。

【図11】図1に示した積層セラミックコンデンサ1の製造方法を説明するためのもので、内部電極3〜6ならびにマーク用内部導体7および8を得るための印刷パターンを示す図である。

【図12】この発明の第2の実施形態による積層セラミック電子部品としての積層セラミックコンデンサ1aの、セラミック素体2の主面に平行な面に沿う切断部端面図であり、第1の内部電極3が延びる面を示す。

【図13】図12に示した積層セラミックコンデンサ1aの、セラミック素体2の主面に平行な面に沿う切断部端面図であり、第2の内部電極3が延びる面を示す。

【図14】図12に示した積層セラミックコンデンサ1aの、セラミック素体2の主面に平行な面に沿う切断部端面図であり、第3の内部電極5が延びる面を示す。

【図15】図12に示した積層セラミックコンデンサ1aの、セラミック素体2の主面に平行な面に沿う切断部端面図であり、第4の内部電極6が延びる面を示す。

【図16】この発明の第3の実施形態による積層セラミック電子部品としての積層セラミックコンデンサ1bの右側面図である。

【図17】図16に示した積層セラミックコンデンサ1bの左側面図である。

【図18】図16に示した積層セラミックコンデンサ1bの、セラミック素体2の主面15および16に平行な面に沿う切断部端面図であり、第3の内部電極5が延びる面を示す。

【図19】図16に示した積層セラミックコンデンサ1bの、セラミック素体2の主面15および16に平行な面に沿う切断部端面図であり、第4の内部電極6が延びる面を示す。

【図20】この発明の第4の実施形態による積層セラミック電子部品としての積層セラミックコンデンサ1cの、セラミック素体2の主面9および10に平行な面に沿う切断部端面図であり、第1の内部電極3が延びる面を示す。

【図21】図20に示した積層セラミックコンデンサ1cの、セラミック素体2の主面に平行な面に沿う切断部端面図であり、第2の内部電極4が延びる面を示す。

【図22】図20に示した積層セラミックコンデンサ1cの、セラミック素体2の主面に平行な面に沿う切断部端面図であり、第3の内部電極5が延びる面を示す。

【図23】図20に示した積層セラミックコンデンサ1cの、セラミック素体2の主面に平行な面に沿う切断部端面図であり、第4の内部電極6が延びる面を示す。

【発明を実施するための形態】

【0020】

以下に、この発明を実施するための形態を説明するにあたり、積層セラミック電子部品として、積層セラミックコンデンサを例示する。

【0021】

[第1の実施形態]

図1ないし図11は、この発明の第1の実施形態を説明するためのものである。第1の実施形態による積層セラミックコンデンサ1は、2個のコンデンサ素子をワンチップ化したアレイタイプのコンデンサである。

【0022】

積層セラミックコンデンサ1は、セラミック素体2と、セラミック素体2の内部にそれぞれ配置された、第1、第2、第3および第4の内部電極3、4、5および6ならびに第1および第2のマーク用内部導体7および8と、セラミック素体2の外表面上に配置された、第1、第2、第3および第4の外部電極9、10、11および12ならびに第1および第2のマーク用外部導体13および14と、を備えている。

【0023】

以下、積層セラミックコンデンサ1の構造の詳細を、(1)セラミック素体、(2)内部電極、(3)マーク用内部導体、(4)外部電極、(5)マーク用外部導体に分けて説明し、その後、(6)製造方法について説明する。

【0024】

(1)セラミック素体

セラミック素体2は、互いに対向する第1および第2の主面15および16と、互いに対向する第1および第2の側面17および18と、互いに対向する第3および第4の側面19および20とを有している。第1ないし第4の側面17〜20は、第1および第2の主面15および16間を結んでいる。

【0025】

ここで、第1および第2の主面15および16間を結ぶ方向をH方向(高さ方向)、第1および第2の側面17および18間を結ぶ方向をW方向(幅方向)、第3および第4の側面19および20間を結ぶ方向をL方向(長さ方向)とそれぞれ定義する。

【0026】

セラミック素体2は、コーナー部および稜部に丸みがつけられていることが好ましい。

【0027】

セラミック素体2は、図5および図6に示すように、主面15および16の方向に延びかつH方向に積層された複数のセラミック層21からなる積層構造を有する。セラミック層21の各厚みは0.5〜10μmであることが好ましい。

【0028】

セラミック層21を構成するセラミック材料としては、たとえば、BaTiO3、CaTiO3、SrTiO3、CaZrO3などを主成分とする誘電体セラミックを用いることができる。また、これらの主成分に、Mn化合物、Mg化合物、Si化合物、Co化合物、Ni化合物、希土類元素化合物などの副成分を添加したものを用いてもよい。

【0029】

(2)内部電極

第1の内部電極3は、図7に示すように、第1の対向部22と、第1の対向部22から引き出されかつ第1の側面17に露出した第1の引出し部23と、を有する。第1の対向部22は、セラミック層21が与える面の主要部を占め、第1の対向部22が配置されたセラミック層21上には、他の内部電極の対向部が配置されていない。

【0030】

第2の内部電極4は、図8に示すように、第2の対向部24と、第2の対向部24から引き出されかつ第2の側面18に露出した第2の引出し部25と、を有する。第2の対向部24は、セラミック層21が与える面の主要部を占め、第2の対向部24が配置されたセラミック層21上には、他の内部電極の対向部が配置されていない。

【0031】

図5および図6に示すように、セラミック層21を介して、第1および第2の内部電極3および4が対向することにより、より特定的には、第1および第2の対向部22および24が対向することにより、第1の機能部26が形成される。第1の機能部26は、セラミック素体2におけるH方向での一方側に位置される。

【0032】

他方、第3の内部電極5は、図9に示すように、第3の対向部27と、第3の対向部27から引き出されかつ第1の側面17に露出した第3の引出し部28と、を有する。第3の対向部27は、セラミック層21が与える面の主要部を占め、第3の対向部27が配置されたセラミック層21上には、他の内部電極の対向部が配置されていない。

【0033】

第4の内部電極6は、図10に示すように、第4の対向部29と、第4の対向部29から引き出されかつ第2の側面18に露出した第4の引出し部30と、を有する。第4の対向部29は、セラミック層21が与える面の主要部を占め、第4の対向部29が配置されたセラミック層21上には、他の内部電極の対向部が配置されていない。

【0034】

図5および図6に示すように、セラミック層を介して、第3および第4の内部電極5および6が対向することにより、より特定的には、第3および第4の対向部27および29が対向することにより、第2の機能部31が形成される。第2の機能部31は、前述した第1の機能部26とH方向に沿って隣接している。

【0035】

第1および第2の機能部26および31の各々において、所定の電気的特性が発現する。この実施形態では、各々において静電容量が形成される。

【0036】

第1の機能部26における第1および第2の内部電極3および4の合計の積層枚数は、第2の機能部31における第3および第4の内部電極5および6の合計の積層枚数より多い。すなわち、この実施形態では、第1の機能部26が第2の機能部31に比べて静電容量が大きい。

【0037】

なお、クロストークを防止する観点からすると、図示しないが、第1の機能部26と第2の機能部31との間には、内部電極が形成されないセラミック層のみからなる緩衝領域が配置されていることが好ましい。

【0038】

内部電極3〜6を構成する導電材料としては、たとえば、Ni、Cu、Ag、Pd、Ag−Pd合金、Auなどを用いることができる。

【0039】

また、内部電極3〜6の各厚みは、0.3〜2.0μmであることが好ましい。

【0040】

(3)マーク用内部導体

第1のマーク用内部導体7は、図7に示すように、たとえば、第1の内部電極3と同一の面上に形成され、第4の側面20に露出している。第1のマーク用内部導体7は、第2の内部電極4と同一の面上に形成されても、後述する実施形態のように、第1および第2の内部電極3および4の双方と同一の面上に形成されてもよい。また、第1のマーク用内部導体7は、第4の側面20以外の側面に露出していてもよい。

【0041】

第2のマーク用内部導体8は、図10に示すように、たとえば、第4の内部電極6と同一の面上に形成され、第3の側面19に露出している。第2のマーク用内部導体8は、第3の内部電極5と同一の面上に形成されても、後述する実施形態のように、第3および第4の内部電極5および6の双方と同一の面上に形成されてもよい。また、第2のマーク用内部導体8は、第3の側面19以外の側面に露出していてもよい。

【0042】

第1のマーク用内部導体7は、側面17〜20のいずれかにおいてH方向に沿って複数箇所に分布するように露出していることが好ましいが、すべての第1の内部電極3、すべての第2の内部電極4、またはすべての第1および第2の内部電極3および4と同一の面上に形成されている必要はない。

【0043】

第2のマーク用内部導体8についても同様であり、側面17〜20のいずれかにおいてH方向に沿って複数箇所に分布するように露出していることが好ましいが、すべての第3の内部電極5、すべての第4の内部電極6、またはすべての第3および第4の内部電極5および6と同一の面上に形成されている必要はない。

【0044】

なお、この実施形態では、第1のマーク用内部導体7は、図7および図8からわかるように、第1および第2の引出し部23および25から遠ざけられ、第2のマーク用内部導体8は、図9および図10からわかるように、第3および第4の引出し部28および30から遠ざけられて配置されている。この技術的意義は、図11を参照しながら後述する印刷パターンを参照すると理解しやすい。すなわち、引出し部23および25とマーク用内部導体7とを遠ざけ、また、引出し部28および30とマーク用内部導体8とを遠ざけて配置することにより、両者の疎密のバランスが取れるため、マザー積層体のプレス状態のバランスが取れ、デラミネーションが抑制される。

【0045】

もっとも、マーク用内部導体7および8による方向性の選別という目的を重視するならば、引出し部とマーク用内部導体とを近づけて配置してもよい。

【0046】

マーク用内部導体7および8は、積層セラミックコンデンサ1の電気的特性の発現には寄与していない。

【0047】

マーク用内部導体7および8を構成し得る材料や厚みの条件については、内部電極3〜6と同様であるが、マーク用内部導体7および8は、内部電極3〜6と同じ材料で構成され、かつ同じ厚みであることが好ましい。

【0048】

(4)外部電極

主として、図1、図2、図7および図8を参照する。

【0049】

第1の外部電極9は、第1の側面17上に配置され、第1の内部電極3の第1の引出し部23と電気的に接続されている。第2の外部電極10は、第2の側面18上に配置され、第2の内部電極4の第2の引出し部25と電気的に接続されている。第3の外部電極11は、第1の側面17上に配置され、第3の内部電極5の第3の引出し部28と電気的に接続されている。第4の外部電極12は、第2の側面18上に配置され、第4の内部電極6の第4の引出し部30と電気的に接続されている。

【0050】

この実施形態では、4個の外部電極9〜12が配置されているが、機能部が3個、4個、…と増加すれば、それに応じて、外部電極の数は6個、8個、…と増加し得る。

【0051】

外部電極9〜12は、それぞれ、引出し部23、25、28および30と接続される下地層を有する。下地層は、焼結金属およびガラスを含む厚膜、金属フィラーおよび熱硬化性樹脂を含む導電性樹脂膜、またはめっき金属を含むめっき膜により構成され得る。上記厚膜上に導電性樹脂膜を形成してもよい。

【0052】

外部電極9〜12は、上記下地層を覆う上層を有することが好ましく、上層はめっき膜により構成され得る。

【0053】

下地層を厚膜で構成する場合、焼結金属としては、たとえば、Cu、Ni、Ag、Pd、Ag−Pd合金、Auなどを用いることができる。ガラスとしては、たとえば、Si、Bなどの酸化物を含むガラスを用いることができる。

【0054】

厚膜は、内部電極3〜6と同時焼成したものでもよく、焼結したセラミック素体2上に導電性ペーストを塗布して焼き付けたものでもよい。厚膜の厚みは、10〜50μmであることが好ましい。

【0055】

下地層を樹脂電極膜で構成する場合、金属フィラーとしては、たとえば、Ag、Pd、Ag−Pd合金などを用いることができる。熱硬化性樹脂としては、たとえば、エポキシ樹脂、フェノール樹脂などを用いることができる。導電性樹脂膜の厚みは、10〜50μmであることが好ましい。

【0056】

下地層および上層の各々を構成するめっき膜としては、たとえば、Cu、Ni、Sn、Pb、Au、Ag、Pd、BiおよびZnからなる群から選ばれる1種の金属または当該金属を含む合金を用いることができる。

【0057】

下地層および上層の各々を構成するめっき膜の厚みは、それぞれ1〜15μmであることが好ましい。

【0058】

上層を構成するめっき膜は、複数のめっき膜により構成してもよい。この場合、1層目がNi、2層目がSnであることが好ましい。

【0059】

(5)マーク用外部導体

第1のマーク用外部導体13は、図2、図4、図7および図8に示すように、第4の側面20上に配置され、露出した複数の第1のマーク用内部導体7を連結する。

【0060】

第2のマーク用外部導体14は、図1、図2、図3、図9および図10に示すように、第3の側面19上に配置され、露出した複数の第2のマーク用内部導体8を連結する。

【0061】

これらマーク用外部導体13および14は、実装基板(図示せず。)上のランドには接続されないことが好ましい。

【0062】

図3と図4とを対比すればわかるように、H方向に沿った第1のマーク用外部導体13の寸法は、H方向に沿った第2のマーク用外部導体14の寸法よりも長い。

【0063】

マーク用外部導体13および14は、機能部26および31の各々の領域を示すマークとして機能する。つまり、マーク用外部導体13および14の各寸法を比較すれば、H方向で見てどちらに大容量部、小容量部があるかを判別できる。具体的には、実装機(図示せず。)において、第1および第2のマーク用外部導体13および14を撮像し、それぞれの画像を処理して寸法の差異を比較すれば、H方向の方向性を選別できる。

【0064】

積層セラミックコンデンサ1の実装時には、第1ないし第4の外部電極9〜12のうち、どの外部電極が大容量部に対応しているかを予め実装機に記憶させておく。すなわち、この実施形態の場合、第1のマーク用外部導体13から遠い第1および第2の外部電極9および10が大容量部の入出力部となる旨、実装機に記憶させておく。

【0065】

また、マーク用外部導体13および14に基づいて積層セラミックコンデンサ1の方向性を揃えることにより、積層セラミックコンデンサ1の電気的特性を測定する測定工程や、積層セラミックコンデンサ1を、テープ状包装体を用いて包装する包装工程といった後工程を効率良く行なうことができる。

【0066】

なお、第1のマーク用内部導体7および第1のマーク用外部導体13を第3の側面19側に、ならびに、第2のマーク用内部導体8および第2のマーク用外部導体14を第4の側20側に、というように、それぞれ位置を入れ替えることも可能である。

【0067】

マーク用外部導体13および14は、めっき膜により構成されることが好ましい。この場合、マーク用内部導体7および8の各々の露出部を核としてめっきが成長するため、マーク用内部導体7および8の各々の露出状態を反映させやすい。

【0068】

めっき膜を構成する金属としては、外部電極9〜12において用いたのと同じものを用いることができる。好ましくは、マーク用外部導体13および14は、外部電極9〜12の下地層または上層と同じ材料で構成されることが好ましい。

【0069】

(6)製造方法

積層セラミックコンデンサ1は、たとえば、次のようにして製造される。

【0070】

(6)−1.

セラミック層21となるべきセラミックグリーンシート、および各種導電性ペーストを準備する。セラミックグリーンシートおよび各種導電性ペーストには、バインダおよび溶剤が含まれるが、公知の有機バインダや有機溶剤を用いることができる。

【0071】

(6)−2.

セラミックグリーンシート上に、たとえばスクリーン印刷などにより所定のパターンで導電性ペーストを印刷し、内部電極パターンおよびマーク用内部導体パターンを形成する。

【0072】

(6)−3.

内部電極パターンおよびマーク用内部導体パターンが印刷されていない外層用セラミックグリーンシートを所定枚数積層し、その上に内部電極パターンおよびマーク用内部導体パターンが印刷された内層用セラミックグリーンシートを所定の順序で積層し、その上に再び外層用セラミックグリーンシートを所定枚数積層し、マザー積層体を作製する。

【0073】

ここで、内層用セラミックグリーンシートの積層方法を説明するため、種々のパターンが印刷された内層用セラミックグリーンシート41を図11に示す。図11には、内層用セラミックグリーンシート41の一部が図示されていると理解すべきである。図11において、図7ないし図10に示す要素に対応する部分には、図7ないし図10において用いた参照符号を付している。

【0074】

図11に示した印刷パターンでは、第1および第2の引出し部23および25が連結され、第3および第4の引出し部28および30が連結され、第1および第2のマーク用内部導体7および8が連結されている。

【0075】

図11において、仮想カットライン42および43を点線で示している。仮想カットライン42および43で囲まれた領域が、積層セラミックコンデンサ1の1個分のセラミック層21を与える領域に相当し、各領域が所定のピッチで行列状に配置されている。

【0076】

この内層用セラミックグリーンシート41を複数枚準備し、1枚目の内層用セラミックグリーンシート41の上に、2枚目の内層用セラミックグリーンシート41をY方向に1ピッチ分ずらして積層する。これにより、パターン「P4」の上にパターン「P3」が積層され、前述した第2の機能部31が形成される。

【0077】

次に、3枚目の内層用セラミックグリーンシート41をX方向に1ピッチ分ずらして、パターン「P2」を積層し、さらに、4枚目の内層用セラミックグリーンシート41をX方向およびY方向にそれぞれ1ピッチ分ずらして、パターン「P1」を積層する。このように、パターン「P2」およびパターン「P1」を繰返し積層することにより、前述した第1の機能部26が形成される。

【0078】

ここでは、図11に示された9つの領域のうち、中央の領域に注目して、積層の過程を説明したが、パターン「P1」および「P2」とパターン「P3」および「P4」とは、マーク用内部導体7および8を除けば、鏡像の関係にあるため、他の領域でも、同時に第1および第2の機能部26および31が形成されることになる。

【0079】

また、パターン「P3」および「P4」とパターン「P1」および「P2」との間に、無地のセラミックグリーンシートを所定枚数積層すれば、緩衝領域を形成することができる。

【0080】

(6)−4.

マザー積層体を積層方向にプレスする。

【0081】

(6)−5.

マザー積層体を所定のサイズにカットし、生のセラミック素体を切り出す。

【0082】

(6)−6.

生のセラミック素体を焼成する。これによって、図示したセラミック素体2が得られる。焼成温度は、セラミックや内部電極等の材料にもよるが、900〜1300℃であることが好ましい。

【0083】

この後、必要に応じて、バレル研磨を行なう。これにより、セラミック素体2のコーナー部や稜部に丸みが付けられる。

【0084】

(6)−7.

外部電極9〜12の下地層を形成する。

【0085】

(6)−7a.外部電極の下地層を厚膜で構成する場合

セラミック素体2の側面17および18に導電性ペーストを塗布し、焼き付ける。焼付け温度は、700〜900℃であることが好ましい。

【0086】

(6)−7b.外部電極の下地層を導電性樹脂膜で構成する場合

セラミック素体2の側面17および18に樹脂ペーストを塗布し、熱硬化させる。硬化温度は、200〜300℃であることが好ましい。

【0087】

(6)−7c.外部電極の下地層をめっき膜で構成する場合

セラミック素体2にめっき処理を施す。これにより、外部電極9〜12の下地層とマーク用外部導体13および14とが同時に形成される。

【0088】

めっき処理を行なうにあたっては、電解めっき、無電解めっきのどちらを採用してもよいが、無電解めっきは、めっき析出速度を向上させるために、触媒などによる前処理が必要となり、工程が複雑化するというデメリットがある。したがって、通常は、電解めっきを採用することが好ましい。めっき処理には、バレルめっきを用いることが好ましい。

【0089】

(6)−8.

外部電極9〜12の下地層表面にめっき処理を施し、上層となるめっき膜を形成する。

【0090】

外部電極9〜12の下地層を厚膜で形成した場合には、この時点でマーク用外部導体13および14が形成される。

【0091】

以上のようにして、積層セラミックコンデンサ1が完成される。

【0092】

[第2の実施形態]

この発明の第2の実施形態が図12ないし図15に示されている。図12は図7に対応する図であり、図13は図8に対応する図であり、図14は図9に対応する図であり、図15は図10に対応する図である。図12ないし図15において、図7ないし図10に示す要素に相当する要素には同様の参照符号を付し、重複する説明は省略する。

【0093】

第2の実施形態による積層セラミックコンデンサ1aでは、第1のマーク用内部導体7が、図12に示した第1の内部電極3と同一の面上だけでなく、図13に示すように、第2の内部電極4と同一の面上にも形成されている。

【0094】

また、第2のマーク用内部導体8についても、図15に示した第4の内部電極6と同一の面上だけでなく、図14に示すように、第3の内部電極5と同一の面上にも形成されている。

【0095】

このように、マーク用内部導体7および8の数が増えることにより、特に、マーク用外部導体13および14をめっきにより構成する局面において、めっきの析出ポイントが増えるため、マーク用外部導体13および14を形成しやすくすることができる。

【0096】

[第3の実施形態]

この発明の第3の実施形態が図16ないし図19に示されている。図16は図3に対応する図であり、図17は図4に対応する図であり、図18は図9に対応する図であり、図19は図10に対応する図である。図16ないし図19において、図3、図4、図9または図10に示す要素に相当する要素には同様の参照符号を付し、重複する説明は省略する。

【0097】

第3の実施形態による積層セラミックコンデンサ1bでは、図18および図19からわかるように、第2のマーク用内部導体が形成されない。応じて、この実施形態では、図17に示すように、第1のマーク用外部導体13は形成されるが、図16からわかるように、第2のマーク用外部導体が形成されない。

【0098】

この実施形態の場合、マーク用外部導体の長さではなく、マーク用外部導体の有無により、方向性を選別することになる。

【0099】

[第4の実施形態]

この発明の第4の実施形態が図20ないし図23に示されている。図20は図7に対応する図であり、図21は図8に対応する図であり、図22は図9に対応する図であり、図23は図10に対応する図である。図20ないし図23において、図7ないし図10に示す要素に相当する要素には同様の参照符号を付し、重複する説明は省略する。

【0100】

第4の実施形態による積層セラミックコンデンサ1cでは、第1の実施形態と比較して、図21に示すように、第2の内部電極4が第1の側面17に引出され、また、図23に示すように、第4の内部電極6が第2の側面18に引出されている点で異なっている。

【0101】

また、図20に示すように、第1のマーク用内部導体7は第2の側面18に露出している。したがって、図20および図21に示すように、第1のマーク用外部導体13は第2の側面18に形成されている。

【0102】

他方、図22に示すように、第2のマーク用内部導体8は第1の側面17に露出している。したがって、図22および図23に示すように、第2のマーク用外部導体14は第1の側面17に形成されている。

【産業上の利用可能性】

【0103】

この発明は、以上説明した積層セラミックコンデンサに限らず、他の積層セラミック電子部品にも適用することができる。たとえば、セラミック素体を圧電体セラミックで構成した場合は、圧電部品として機能する積層セラミック電子部品とすることができる。セラミック素体をスピネル状セラミックなどの半導体セラミックで構成した場合は、サーミスタとして機能する積層セラミック電子部品とすることができる。セラミック素体をフェライトなどの磁性体セラミックで構成した場合は、インダクタとして機能する積層セラミック電子部品とすることができる。

【符号の説明】

【0104】

1,1a,1b,1c 積層セラミックコンデンサ

2 セラミック素体

3 第1の内部電極

4 第2の内部電極

5 第3の内部電極

6 第4の内部電極

7 第1のマーク用内部導体

8 第2のマーク用内部導体

9 第1の外部電極

10 第2の外部電極

11 第3の外部電極

12 第4の外部電極

13 第1のマーク用外部導体

14 第2のマーク用外部導体

15,16 主面

17〜20 側面

21 セラミック層

26 第1の機能部

31 第2の機能部

【技術分野】

【0001】

この発明は、積層セラミック電子部品に関するものであり、特に、アレイタイプの積層セラミック電子部品のように、1個の部品本体内に複数の機能部を有する積層セラミック電子部品に関するものである。

【背景技術】

【0002】

近年、携帯電話機や、携帯音楽プレイヤーなどをはじめとする電子機器の小型化が進むにつれて、電子機器に搭載される実装基板の小型化が進んできている。

【0003】

また、実装基板の小型化に伴い、当然のことながら、実装基板での実装面積も狭くなってきている。このため、実装基板に実装される電子部品に対する小型化の要求が強まってきており、複数の電子部品素子をワンチップ化したアレイタイプの電子部品もしばしば用いられるようになってきている。

【0004】

アレイタイプの電子部品を用いることにより、複数の電子部品を実装する場合と比べて、実装スペースを小さくできるだけでなく、実装コストも低減することができる。

【0005】

アレイタイプの電子部品、特に積層セラミック電子部品の代表例としては、コンデンサアレイを挙げることができる。一般的なコンデンサアレイでは、たとえば、1つの側面に4個ずつ外部電極が形成され、対向する外部電極間で4個の容量が取り出される。

【0006】

通常、コンデンサアレイから取り出される複数の容量は、互いに同じであることが多い。しかし、回路設計の都合上、これらの容量を互いに異ならせることが望まれる場合もある。これを受けて、特許文献1では、各容量部を構成する内部電極の面積を互いに異ならせることにより、互いに異なる容量を取り出すことが提案されている。

【先行技術文献】

【特許文献】

【0007】

【特許文献1】特開2003−257785号公報

【発明の概要】

【発明が解決しようとする課題】

【0008】

しかし、特許文献1に記載の構造では、取り出す容量の個数に対応した数の内部電極を共通のセラミック層上に配置するため、1つの内部電極の面積を広げることに限界がある。

【0009】

そこで、この発明の目的は、上記のような問題を解決し得る、積層セラミック電子部品を提供しようとすることである。

【課題を解決するための手段】

【0010】

この発明に係る積層セラミック電子部品は、複数の積層されたセラミック層からなり、互いに対向する1対の主面と主面間を結ぶ側面とを有する、セラミック素体と、セラミック素体の内部に配置された、第1ないし第4の内部電極と、セラミック素体の側面上に配置され、第1ないし第4の内部電極にそれぞれ電気的に接続された、第1ないし第4の外部電極と、を備えており、以下のような特徴を有している。

【0011】

セラミック素体の内部において、主面間を結ぶ高さ方向に沿って隣接するように、第1の機能部と第2の機能部とが配置されており、第1の機能部において、第1および第2の内部電極がセラミック層を介して高さ方向に対向し、第2の機能部において、第3および第4の内部電極がセラミック層を介して高さ方向に対向している。

【0012】

また、第1の機能部における第1および第2の内部電極の合計の積層枚数と、第2の機能部における第3および第4の内部電極の合計の積層枚数と、が異なっている。

【0013】

そして、この発明に係る積層セラミック電子部品は、第1および第2の内部電極のうち少なくとも一方と同一の面上に配置され、かつ側面に露出した、第1のマーク用内部導体と、側面上において、露出した複数の第1のマーク用内部導体を連結するようにして配置された、第1のマーク用外部導体と、をさらに備えている。

【0014】

この発明に係る積層セラミック電子部品は、好ましくは、第3および第4の内部電極のうち少なくとも一方と同一の面上に配置され、かつ側面に露出した、第2のマーク用内部導体と、側面上において、露出した複数の第2のマーク用内部導体を連結するようにして配置された、第2のマーク用外部導体とをさらに備え、第1の機能部における第1および第2の内部電極の合計の積層枚数が、第2の機能部における第3および第4の内部電極の合計の積層枚数よりも多く、高さ方向に沿った第1のマーク用外部導体の寸法が、高さ方向に沿った第2のマーク用外部導体の寸法よりも長い。

【0015】

なお、上述したように、この発明に係る積層セラミック電子部品は、第1および第2の機能部を備えるものであるが、第1および第2の機能部以外の少なくとも1個の機能部をさらに備えていてもよい。また、第1の機能部を構成するものが、第1および第2の内部電極ならびに第1および第2の外部電極であるが、第1の機能部において、第1および第2の内部電極以外の少なくとも1個の内部電極をさらに備えていても、第1および第2の外部電極以外の少なくとも1個の外部電極をさらに備えていてもよい。同様に、第2の機能部を構成するものが、第3および第4の内部電極ならびに第3および第4の外部電極であるが、第2の機能部において、第3および第4の内部電極以外の少なくとも1個の内部電極をさらに備えていても、第3および第4の外部電極以外の少なくとも1個の外部電極をさらに備えていてもよい。

【発明の効果】

【0016】

この発明に係る積層セラミック電子部品によれば、高さ方向に沿って複数の機能部が配置されるため、各機能部において、共通のセラミック層上に配置する内部電極の数を減らし、内部電極の各面積を広げることができる。

【0017】

また、この発明に係る積層セラミック電子部品においては、内部電極の合計の積層枚数の多少によって、各機能部の特性を異ならせることができる。このように、各機能部間で特性の差異が生じた場合、この積層セラミック電子部品では上下の方向性が生じるが、この方向性は少なくとも第1のマーク用外部導体を認識することによって識別することができる。

【0018】

この発明において、第2のマーク用外部導体をさらに備え、高さ方向に沿った第1のマーク用外部導体の寸法が、高さ方向に沿った第2のマーク用外部導体の寸法よりも長くされると、上述の方向性をより確実かつより容易に識別することができる。

【図面の簡単な説明】

【0019】

【図1】この発明の第1の実施形態による積層セラミック電子部品としての積層セラミックコンデンサ1の外観を示す斜視図である。

【図2】図1に示した積層セラミックコンデンサ1の上面図である。

【図3】図1に示した積層セラミックコンデンサ1の右側面図である。

【図4】図1に示した積層セラミックコンデンサ1の左側面図である。

【図5】図2の線A−Aに沿う断面図である。

【図6】図2の線B−Bに沿う断面図である。

【図7】図1に示した積層セラミックコンデンサ1の、セラミック素体2の主面15および16に平行な面に沿う切断部端面図であり、第1の内部電極3が延びる面を示す。

【図8】図1に示した積層セラミックコンデンサ1の、セラミック素体2の主面15および16に平行な面に沿う切断部端面図であり、第2の内部電極4が延びる面を示す。

【図9】図1に示した積層セラミックコンデンサ1の、セラミック素体2の主面15および16に平行な面に沿う切断部端面図であり、第3の内部電極5が延びる面を示す。

【図10】図1に示した積層セラミックコンデンサ1の、セラミック素体2の主面15および16に平行な面に沿う切断部端面図であり、第4の内部電極6が延びる面を示す。

【図11】図1に示した積層セラミックコンデンサ1の製造方法を説明するためのもので、内部電極3〜6ならびにマーク用内部導体7および8を得るための印刷パターンを示す図である。

【図12】この発明の第2の実施形態による積層セラミック電子部品としての積層セラミックコンデンサ1aの、セラミック素体2の主面に平行な面に沿う切断部端面図であり、第1の内部電極3が延びる面を示す。

【図13】図12に示した積層セラミックコンデンサ1aの、セラミック素体2の主面に平行な面に沿う切断部端面図であり、第2の内部電極3が延びる面を示す。

【図14】図12に示した積層セラミックコンデンサ1aの、セラミック素体2の主面に平行な面に沿う切断部端面図であり、第3の内部電極5が延びる面を示す。

【図15】図12に示した積層セラミックコンデンサ1aの、セラミック素体2の主面に平行な面に沿う切断部端面図であり、第4の内部電極6が延びる面を示す。

【図16】この発明の第3の実施形態による積層セラミック電子部品としての積層セラミックコンデンサ1bの右側面図である。

【図17】図16に示した積層セラミックコンデンサ1bの左側面図である。

【図18】図16に示した積層セラミックコンデンサ1bの、セラミック素体2の主面15および16に平行な面に沿う切断部端面図であり、第3の内部電極5が延びる面を示す。

【図19】図16に示した積層セラミックコンデンサ1bの、セラミック素体2の主面15および16に平行な面に沿う切断部端面図であり、第4の内部電極6が延びる面を示す。

【図20】この発明の第4の実施形態による積層セラミック電子部品としての積層セラミックコンデンサ1cの、セラミック素体2の主面9および10に平行な面に沿う切断部端面図であり、第1の内部電極3が延びる面を示す。

【図21】図20に示した積層セラミックコンデンサ1cの、セラミック素体2の主面に平行な面に沿う切断部端面図であり、第2の内部電極4が延びる面を示す。

【図22】図20に示した積層セラミックコンデンサ1cの、セラミック素体2の主面に平行な面に沿う切断部端面図であり、第3の内部電極5が延びる面を示す。

【図23】図20に示した積層セラミックコンデンサ1cの、セラミック素体2の主面に平行な面に沿う切断部端面図であり、第4の内部電極6が延びる面を示す。

【発明を実施するための形態】

【0020】

以下に、この発明を実施するための形態を説明するにあたり、積層セラミック電子部品として、積層セラミックコンデンサを例示する。

【0021】

[第1の実施形態]

図1ないし図11は、この発明の第1の実施形態を説明するためのものである。第1の実施形態による積層セラミックコンデンサ1は、2個のコンデンサ素子をワンチップ化したアレイタイプのコンデンサである。

【0022】

積層セラミックコンデンサ1は、セラミック素体2と、セラミック素体2の内部にそれぞれ配置された、第1、第2、第3および第4の内部電極3、4、5および6ならびに第1および第2のマーク用内部導体7および8と、セラミック素体2の外表面上に配置された、第1、第2、第3および第4の外部電極9、10、11および12ならびに第1および第2のマーク用外部導体13および14と、を備えている。

【0023】

以下、積層セラミックコンデンサ1の構造の詳細を、(1)セラミック素体、(2)内部電極、(3)マーク用内部導体、(4)外部電極、(5)マーク用外部導体に分けて説明し、その後、(6)製造方法について説明する。

【0024】

(1)セラミック素体

セラミック素体2は、互いに対向する第1および第2の主面15および16と、互いに対向する第1および第2の側面17および18と、互いに対向する第3および第4の側面19および20とを有している。第1ないし第4の側面17〜20は、第1および第2の主面15および16間を結んでいる。

【0025】

ここで、第1および第2の主面15および16間を結ぶ方向をH方向(高さ方向)、第1および第2の側面17および18間を結ぶ方向をW方向(幅方向)、第3および第4の側面19および20間を結ぶ方向をL方向(長さ方向)とそれぞれ定義する。

【0026】

セラミック素体2は、コーナー部および稜部に丸みがつけられていることが好ましい。

【0027】

セラミック素体2は、図5および図6に示すように、主面15および16の方向に延びかつH方向に積層された複数のセラミック層21からなる積層構造を有する。セラミック層21の各厚みは0.5〜10μmであることが好ましい。

【0028】

セラミック層21を構成するセラミック材料としては、たとえば、BaTiO3、CaTiO3、SrTiO3、CaZrO3などを主成分とする誘電体セラミックを用いることができる。また、これらの主成分に、Mn化合物、Mg化合物、Si化合物、Co化合物、Ni化合物、希土類元素化合物などの副成分を添加したものを用いてもよい。

【0029】

(2)内部電極

第1の内部電極3は、図7に示すように、第1の対向部22と、第1の対向部22から引き出されかつ第1の側面17に露出した第1の引出し部23と、を有する。第1の対向部22は、セラミック層21が与える面の主要部を占め、第1の対向部22が配置されたセラミック層21上には、他の内部電極の対向部が配置されていない。

【0030】

第2の内部電極4は、図8に示すように、第2の対向部24と、第2の対向部24から引き出されかつ第2の側面18に露出した第2の引出し部25と、を有する。第2の対向部24は、セラミック層21が与える面の主要部を占め、第2の対向部24が配置されたセラミック層21上には、他の内部電極の対向部が配置されていない。

【0031】

図5および図6に示すように、セラミック層21を介して、第1および第2の内部電極3および4が対向することにより、より特定的には、第1および第2の対向部22および24が対向することにより、第1の機能部26が形成される。第1の機能部26は、セラミック素体2におけるH方向での一方側に位置される。

【0032】

他方、第3の内部電極5は、図9に示すように、第3の対向部27と、第3の対向部27から引き出されかつ第1の側面17に露出した第3の引出し部28と、を有する。第3の対向部27は、セラミック層21が与える面の主要部を占め、第3の対向部27が配置されたセラミック層21上には、他の内部電極の対向部が配置されていない。

【0033】

第4の内部電極6は、図10に示すように、第4の対向部29と、第4の対向部29から引き出されかつ第2の側面18に露出した第4の引出し部30と、を有する。第4の対向部29は、セラミック層21が与える面の主要部を占め、第4の対向部29が配置されたセラミック層21上には、他の内部電極の対向部が配置されていない。

【0034】

図5および図6に示すように、セラミック層を介して、第3および第4の内部電極5および6が対向することにより、より特定的には、第3および第4の対向部27および29が対向することにより、第2の機能部31が形成される。第2の機能部31は、前述した第1の機能部26とH方向に沿って隣接している。

【0035】

第1および第2の機能部26および31の各々において、所定の電気的特性が発現する。この実施形態では、各々において静電容量が形成される。

【0036】

第1の機能部26における第1および第2の内部電極3および4の合計の積層枚数は、第2の機能部31における第3および第4の内部電極5および6の合計の積層枚数より多い。すなわち、この実施形態では、第1の機能部26が第2の機能部31に比べて静電容量が大きい。

【0037】

なお、クロストークを防止する観点からすると、図示しないが、第1の機能部26と第2の機能部31との間には、内部電極が形成されないセラミック層のみからなる緩衝領域が配置されていることが好ましい。

【0038】

内部電極3〜6を構成する導電材料としては、たとえば、Ni、Cu、Ag、Pd、Ag−Pd合金、Auなどを用いることができる。

【0039】

また、内部電極3〜6の各厚みは、0.3〜2.0μmであることが好ましい。

【0040】

(3)マーク用内部導体

第1のマーク用内部導体7は、図7に示すように、たとえば、第1の内部電極3と同一の面上に形成され、第4の側面20に露出している。第1のマーク用内部導体7は、第2の内部電極4と同一の面上に形成されても、後述する実施形態のように、第1および第2の内部電極3および4の双方と同一の面上に形成されてもよい。また、第1のマーク用内部導体7は、第4の側面20以外の側面に露出していてもよい。

【0041】

第2のマーク用内部導体8は、図10に示すように、たとえば、第4の内部電極6と同一の面上に形成され、第3の側面19に露出している。第2のマーク用内部導体8は、第3の内部電極5と同一の面上に形成されても、後述する実施形態のように、第3および第4の内部電極5および6の双方と同一の面上に形成されてもよい。また、第2のマーク用内部導体8は、第3の側面19以外の側面に露出していてもよい。

【0042】

第1のマーク用内部導体7は、側面17〜20のいずれかにおいてH方向に沿って複数箇所に分布するように露出していることが好ましいが、すべての第1の内部電極3、すべての第2の内部電極4、またはすべての第1および第2の内部電極3および4と同一の面上に形成されている必要はない。

【0043】

第2のマーク用内部導体8についても同様であり、側面17〜20のいずれかにおいてH方向に沿って複数箇所に分布するように露出していることが好ましいが、すべての第3の内部電極5、すべての第4の内部電極6、またはすべての第3および第4の内部電極5および6と同一の面上に形成されている必要はない。

【0044】

なお、この実施形態では、第1のマーク用内部導体7は、図7および図8からわかるように、第1および第2の引出し部23および25から遠ざけられ、第2のマーク用内部導体8は、図9および図10からわかるように、第3および第4の引出し部28および30から遠ざけられて配置されている。この技術的意義は、図11を参照しながら後述する印刷パターンを参照すると理解しやすい。すなわち、引出し部23および25とマーク用内部導体7とを遠ざけ、また、引出し部28および30とマーク用内部導体8とを遠ざけて配置することにより、両者の疎密のバランスが取れるため、マザー積層体のプレス状態のバランスが取れ、デラミネーションが抑制される。

【0045】

もっとも、マーク用内部導体7および8による方向性の選別という目的を重視するならば、引出し部とマーク用内部導体とを近づけて配置してもよい。

【0046】

マーク用内部導体7および8は、積層セラミックコンデンサ1の電気的特性の発現には寄与していない。

【0047】

マーク用内部導体7および8を構成し得る材料や厚みの条件については、内部電極3〜6と同様であるが、マーク用内部導体7および8は、内部電極3〜6と同じ材料で構成され、かつ同じ厚みであることが好ましい。

【0048】

(4)外部電極

主として、図1、図2、図7および図8を参照する。

【0049】

第1の外部電極9は、第1の側面17上に配置され、第1の内部電極3の第1の引出し部23と電気的に接続されている。第2の外部電極10は、第2の側面18上に配置され、第2の内部電極4の第2の引出し部25と電気的に接続されている。第3の外部電極11は、第1の側面17上に配置され、第3の内部電極5の第3の引出し部28と電気的に接続されている。第4の外部電極12は、第2の側面18上に配置され、第4の内部電極6の第4の引出し部30と電気的に接続されている。

【0050】

この実施形態では、4個の外部電極9〜12が配置されているが、機能部が3個、4個、…と増加すれば、それに応じて、外部電極の数は6個、8個、…と増加し得る。

【0051】

外部電極9〜12は、それぞれ、引出し部23、25、28および30と接続される下地層を有する。下地層は、焼結金属およびガラスを含む厚膜、金属フィラーおよび熱硬化性樹脂を含む導電性樹脂膜、またはめっき金属を含むめっき膜により構成され得る。上記厚膜上に導電性樹脂膜を形成してもよい。

【0052】

外部電極9〜12は、上記下地層を覆う上層を有することが好ましく、上層はめっき膜により構成され得る。

【0053】

下地層を厚膜で構成する場合、焼結金属としては、たとえば、Cu、Ni、Ag、Pd、Ag−Pd合金、Auなどを用いることができる。ガラスとしては、たとえば、Si、Bなどの酸化物を含むガラスを用いることができる。

【0054】

厚膜は、内部電極3〜6と同時焼成したものでもよく、焼結したセラミック素体2上に導電性ペーストを塗布して焼き付けたものでもよい。厚膜の厚みは、10〜50μmであることが好ましい。

【0055】

下地層を樹脂電極膜で構成する場合、金属フィラーとしては、たとえば、Ag、Pd、Ag−Pd合金などを用いることができる。熱硬化性樹脂としては、たとえば、エポキシ樹脂、フェノール樹脂などを用いることができる。導電性樹脂膜の厚みは、10〜50μmであることが好ましい。

【0056】

下地層および上層の各々を構成するめっき膜としては、たとえば、Cu、Ni、Sn、Pb、Au、Ag、Pd、BiおよびZnからなる群から選ばれる1種の金属または当該金属を含む合金を用いることができる。

【0057】

下地層および上層の各々を構成するめっき膜の厚みは、それぞれ1〜15μmであることが好ましい。

【0058】

上層を構成するめっき膜は、複数のめっき膜により構成してもよい。この場合、1層目がNi、2層目がSnであることが好ましい。

【0059】

(5)マーク用外部導体

第1のマーク用外部導体13は、図2、図4、図7および図8に示すように、第4の側面20上に配置され、露出した複数の第1のマーク用内部導体7を連結する。

【0060】

第2のマーク用外部導体14は、図1、図2、図3、図9および図10に示すように、第3の側面19上に配置され、露出した複数の第2のマーク用内部導体8を連結する。

【0061】

これらマーク用外部導体13および14は、実装基板(図示せず。)上のランドには接続されないことが好ましい。

【0062】

図3と図4とを対比すればわかるように、H方向に沿った第1のマーク用外部導体13の寸法は、H方向に沿った第2のマーク用外部導体14の寸法よりも長い。

【0063】

マーク用外部導体13および14は、機能部26および31の各々の領域を示すマークとして機能する。つまり、マーク用外部導体13および14の各寸法を比較すれば、H方向で見てどちらに大容量部、小容量部があるかを判別できる。具体的には、実装機(図示せず。)において、第1および第2のマーク用外部導体13および14を撮像し、それぞれの画像を処理して寸法の差異を比較すれば、H方向の方向性を選別できる。

【0064】

積層セラミックコンデンサ1の実装時には、第1ないし第4の外部電極9〜12のうち、どの外部電極が大容量部に対応しているかを予め実装機に記憶させておく。すなわち、この実施形態の場合、第1のマーク用外部導体13から遠い第1および第2の外部電極9および10が大容量部の入出力部となる旨、実装機に記憶させておく。

【0065】

また、マーク用外部導体13および14に基づいて積層セラミックコンデンサ1の方向性を揃えることにより、積層セラミックコンデンサ1の電気的特性を測定する測定工程や、積層セラミックコンデンサ1を、テープ状包装体を用いて包装する包装工程といった後工程を効率良く行なうことができる。

【0066】

なお、第1のマーク用内部導体7および第1のマーク用外部導体13を第3の側面19側に、ならびに、第2のマーク用内部導体8および第2のマーク用外部導体14を第4の側20側に、というように、それぞれ位置を入れ替えることも可能である。

【0067】

マーク用外部導体13および14は、めっき膜により構成されることが好ましい。この場合、マーク用内部導体7および8の各々の露出部を核としてめっきが成長するため、マーク用内部導体7および8の各々の露出状態を反映させやすい。

【0068】

めっき膜を構成する金属としては、外部電極9〜12において用いたのと同じものを用いることができる。好ましくは、マーク用外部導体13および14は、外部電極9〜12の下地層または上層と同じ材料で構成されることが好ましい。

【0069】

(6)製造方法

積層セラミックコンデンサ1は、たとえば、次のようにして製造される。

【0070】

(6)−1.

セラミック層21となるべきセラミックグリーンシート、および各種導電性ペーストを準備する。セラミックグリーンシートおよび各種導電性ペーストには、バインダおよび溶剤が含まれるが、公知の有機バインダや有機溶剤を用いることができる。

【0071】

(6)−2.

セラミックグリーンシート上に、たとえばスクリーン印刷などにより所定のパターンで導電性ペーストを印刷し、内部電極パターンおよびマーク用内部導体パターンを形成する。

【0072】

(6)−3.

内部電極パターンおよびマーク用内部導体パターンが印刷されていない外層用セラミックグリーンシートを所定枚数積層し、その上に内部電極パターンおよびマーク用内部導体パターンが印刷された内層用セラミックグリーンシートを所定の順序で積層し、その上に再び外層用セラミックグリーンシートを所定枚数積層し、マザー積層体を作製する。

【0073】

ここで、内層用セラミックグリーンシートの積層方法を説明するため、種々のパターンが印刷された内層用セラミックグリーンシート41を図11に示す。図11には、内層用セラミックグリーンシート41の一部が図示されていると理解すべきである。図11において、図7ないし図10に示す要素に対応する部分には、図7ないし図10において用いた参照符号を付している。

【0074】

図11に示した印刷パターンでは、第1および第2の引出し部23および25が連結され、第3および第4の引出し部28および30が連結され、第1および第2のマーク用内部導体7および8が連結されている。

【0075】

図11において、仮想カットライン42および43を点線で示している。仮想カットライン42および43で囲まれた領域が、積層セラミックコンデンサ1の1個分のセラミック層21を与える領域に相当し、各領域が所定のピッチで行列状に配置されている。

【0076】

この内層用セラミックグリーンシート41を複数枚準備し、1枚目の内層用セラミックグリーンシート41の上に、2枚目の内層用セラミックグリーンシート41をY方向に1ピッチ分ずらして積層する。これにより、パターン「P4」の上にパターン「P3」が積層され、前述した第2の機能部31が形成される。

【0077】

次に、3枚目の内層用セラミックグリーンシート41をX方向に1ピッチ分ずらして、パターン「P2」を積層し、さらに、4枚目の内層用セラミックグリーンシート41をX方向およびY方向にそれぞれ1ピッチ分ずらして、パターン「P1」を積層する。このように、パターン「P2」およびパターン「P1」を繰返し積層することにより、前述した第1の機能部26が形成される。

【0078】

ここでは、図11に示された9つの領域のうち、中央の領域に注目して、積層の過程を説明したが、パターン「P1」および「P2」とパターン「P3」および「P4」とは、マーク用内部導体7および8を除けば、鏡像の関係にあるため、他の領域でも、同時に第1および第2の機能部26および31が形成されることになる。

【0079】

また、パターン「P3」および「P4」とパターン「P1」および「P2」との間に、無地のセラミックグリーンシートを所定枚数積層すれば、緩衝領域を形成することができる。

【0080】

(6)−4.

マザー積層体を積層方向にプレスする。

【0081】

(6)−5.

マザー積層体を所定のサイズにカットし、生のセラミック素体を切り出す。

【0082】

(6)−6.

生のセラミック素体を焼成する。これによって、図示したセラミック素体2が得られる。焼成温度は、セラミックや内部電極等の材料にもよるが、900〜1300℃であることが好ましい。

【0083】

この後、必要に応じて、バレル研磨を行なう。これにより、セラミック素体2のコーナー部や稜部に丸みが付けられる。

【0084】

(6)−7.

外部電極9〜12の下地層を形成する。

【0085】

(6)−7a.外部電極の下地層を厚膜で構成する場合

セラミック素体2の側面17および18に導電性ペーストを塗布し、焼き付ける。焼付け温度は、700〜900℃であることが好ましい。

【0086】

(6)−7b.外部電極の下地層を導電性樹脂膜で構成する場合

セラミック素体2の側面17および18に樹脂ペーストを塗布し、熱硬化させる。硬化温度は、200〜300℃であることが好ましい。

【0087】

(6)−7c.外部電極の下地層をめっき膜で構成する場合

セラミック素体2にめっき処理を施す。これにより、外部電極9〜12の下地層とマーク用外部導体13および14とが同時に形成される。

【0088】

めっき処理を行なうにあたっては、電解めっき、無電解めっきのどちらを採用してもよいが、無電解めっきは、めっき析出速度を向上させるために、触媒などによる前処理が必要となり、工程が複雑化するというデメリットがある。したがって、通常は、電解めっきを採用することが好ましい。めっき処理には、バレルめっきを用いることが好ましい。

【0089】

(6)−8.

外部電極9〜12の下地層表面にめっき処理を施し、上層となるめっき膜を形成する。

【0090】

外部電極9〜12の下地層を厚膜で形成した場合には、この時点でマーク用外部導体13および14が形成される。

【0091】

以上のようにして、積層セラミックコンデンサ1が完成される。

【0092】

[第2の実施形態]

この発明の第2の実施形態が図12ないし図15に示されている。図12は図7に対応する図であり、図13は図8に対応する図であり、図14は図9に対応する図であり、図15は図10に対応する図である。図12ないし図15において、図7ないし図10に示す要素に相当する要素には同様の参照符号を付し、重複する説明は省略する。

【0093】

第2の実施形態による積層セラミックコンデンサ1aでは、第1のマーク用内部導体7が、図12に示した第1の内部電極3と同一の面上だけでなく、図13に示すように、第2の内部電極4と同一の面上にも形成されている。

【0094】

また、第2のマーク用内部導体8についても、図15に示した第4の内部電極6と同一の面上だけでなく、図14に示すように、第3の内部電極5と同一の面上にも形成されている。

【0095】

このように、マーク用内部導体7および8の数が増えることにより、特に、マーク用外部導体13および14をめっきにより構成する局面において、めっきの析出ポイントが増えるため、マーク用外部導体13および14を形成しやすくすることができる。

【0096】

[第3の実施形態]

この発明の第3の実施形態が図16ないし図19に示されている。図16は図3に対応する図であり、図17は図4に対応する図であり、図18は図9に対応する図であり、図19は図10に対応する図である。図16ないし図19において、図3、図4、図9または図10に示す要素に相当する要素には同様の参照符号を付し、重複する説明は省略する。

【0097】

第3の実施形態による積層セラミックコンデンサ1bでは、図18および図19からわかるように、第2のマーク用内部導体が形成されない。応じて、この実施形態では、図17に示すように、第1のマーク用外部導体13は形成されるが、図16からわかるように、第2のマーク用外部導体が形成されない。

【0098】

この実施形態の場合、マーク用外部導体の長さではなく、マーク用外部導体の有無により、方向性を選別することになる。

【0099】

[第4の実施形態]

この発明の第4の実施形態が図20ないし図23に示されている。図20は図7に対応する図であり、図21は図8に対応する図であり、図22は図9に対応する図であり、図23は図10に対応する図である。図20ないし図23において、図7ないし図10に示す要素に相当する要素には同様の参照符号を付し、重複する説明は省略する。

【0100】

第4の実施形態による積層セラミックコンデンサ1cでは、第1の実施形態と比較して、図21に示すように、第2の内部電極4が第1の側面17に引出され、また、図23に示すように、第4の内部電極6が第2の側面18に引出されている点で異なっている。

【0101】

また、図20に示すように、第1のマーク用内部導体7は第2の側面18に露出している。したがって、図20および図21に示すように、第1のマーク用外部導体13は第2の側面18に形成されている。

【0102】

他方、図22に示すように、第2のマーク用内部導体8は第1の側面17に露出している。したがって、図22および図23に示すように、第2のマーク用外部導体14は第1の側面17に形成されている。

【産業上の利用可能性】

【0103】

この発明は、以上説明した積層セラミックコンデンサに限らず、他の積層セラミック電子部品にも適用することができる。たとえば、セラミック素体を圧電体セラミックで構成した場合は、圧電部品として機能する積層セラミック電子部品とすることができる。セラミック素体をスピネル状セラミックなどの半導体セラミックで構成した場合は、サーミスタとして機能する積層セラミック電子部品とすることができる。セラミック素体をフェライトなどの磁性体セラミックで構成した場合は、インダクタとして機能する積層セラミック電子部品とすることができる。

【符号の説明】

【0104】

1,1a,1b,1c 積層セラミックコンデンサ

2 セラミック素体

3 第1の内部電極

4 第2の内部電極

5 第3の内部電極

6 第4の内部電極

7 第1のマーク用内部導体

8 第2のマーク用内部導体

9 第1の外部電極

10 第2の外部電極

11 第3の外部電極

12 第4の外部電極

13 第1のマーク用外部導体

14 第2のマーク用外部導体

15,16 主面

17〜20 側面

21 セラミック層

26 第1の機能部

31 第2の機能部

【特許請求の範囲】

【請求項1】

複数の積層されたセラミック層からなり、互いに対向する1対の主面と前記主面間を結ぶ側面とを有する、セラミック素体と、

前記セラミック素体の内部に配置された、第1ないし第4の内部電極と、

前記セラミック素体の前記側面上に配置され、前記第1ないし第4の内部電極にそれぞれ電気的に接続された、第1ないし第4の外部電極と、

を備え、

前記セラミック素体の内部において、前記主面間を結ぶ高さ方向に沿って隣接するように、第1の機能部と第2の機能部とが配置されており、

前記第1の機能部において、前記第1および第2の内部電極が前記セラミック層を介して前記高さ方向に対向し、

前記第2の機能部において、前記第3および第4の内部電極が前記セラミック層を介して前記高さ方向に対向し、

前記第1の機能部における前記第1および第2の内部電極の合計の積層枚数と、前記第2の機能部における前記第3および第4の内部電極の合計の積層枚数と、が異なり、

前記第1および第2の内部電極のうち少なくとも一方と同一の面上に配置され、かつ前記側面に露出した、第1のマーク用内部導体と、

前記側面上において、露出した複数の前記第1のマーク用内部導体を連結するようにして配置された、第1のマーク用外部導体と、

をさらに備える、

積層セラミック電子部品。

【請求項2】

前記第3および第4の内部電極のうち少なくとも一方と同一の面上に配置され、かつ前記側面に露出した、第2のマーク用内部導体と、

前記側面上において、露出した複数の前記第2のマーク用内部導体を連結するようにして配置された、第2のマーク用外部導体と、

をさらに備え、

前記第1の機能部における前記第1および第2の内部電極の合計の積層枚数が、前記第2の機能部における前記第3および第4の内部電極の合計の積層枚数よりも多く、

前記高さ方向に沿った前記第1のマーク用外部導体の寸法が、前記高さ方向に沿った前記第2のマーク用外部導体の寸法よりも長い、

請求項1に記載の積層セラミック電子部品。

【請求項1】

複数の積層されたセラミック層からなり、互いに対向する1対の主面と前記主面間を結ぶ側面とを有する、セラミック素体と、

前記セラミック素体の内部に配置された、第1ないし第4の内部電極と、

前記セラミック素体の前記側面上に配置され、前記第1ないし第4の内部電極にそれぞれ電気的に接続された、第1ないし第4の外部電極と、

を備え、

前記セラミック素体の内部において、前記主面間を結ぶ高さ方向に沿って隣接するように、第1の機能部と第2の機能部とが配置されており、

前記第1の機能部において、前記第1および第2の内部電極が前記セラミック層を介して前記高さ方向に対向し、

前記第2の機能部において、前記第3および第4の内部電極が前記セラミック層を介して前記高さ方向に対向し、

前記第1の機能部における前記第1および第2の内部電極の合計の積層枚数と、前記第2の機能部における前記第3および第4の内部電極の合計の積層枚数と、が異なり、

前記第1および第2の内部電極のうち少なくとも一方と同一の面上に配置され、かつ前記側面に露出した、第1のマーク用内部導体と、

前記側面上において、露出した複数の前記第1のマーク用内部導体を連結するようにして配置された、第1のマーク用外部導体と、

をさらに備える、

積層セラミック電子部品。

【請求項2】

前記第3および第4の内部電極のうち少なくとも一方と同一の面上に配置され、かつ前記側面に露出した、第2のマーク用内部導体と、

前記側面上において、露出した複数の前記第2のマーク用内部導体を連結するようにして配置された、第2のマーク用外部導体と、

をさらに備え、

前記第1の機能部における前記第1および第2の内部電極の合計の積層枚数が、前記第2の機能部における前記第3および第4の内部電極の合計の積層枚数よりも多く、

前記高さ方向に沿った前記第1のマーク用外部導体の寸法が、前記高さ方向に沿った前記第2のマーク用外部導体の寸法よりも長い、

請求項1に記載の積層セラミック電子部品。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【公開番号】特開2013−26323(P2013−26323A)

【公開日】平成25年2月4日(2013.2.4)

【国際特許分類】

【出願番号】特願2011−157875(P2011−157875)

【出願日】平成23年7月19日(2011.7.19)

【出願人】(000006231)株式会社村田製作所 (3,635)

【Fターム(参考)】

【公開日】平成25年2月4日(2013.2.4)

【国際特許分類】

【出願日】平成23年7月19日(2011.7.19)

【出願人】(000006231)株式会社村田製作所 (3,635)

【Fターム(参考)】

[ Back to top ]