積層セラミック電子部品

【課題】内部電極の露出部にめっき膜を析出させるにあたって、より確実なめっき成長を実現するため、いずれの内部電極も存在しない外層部にダミー導体を形成したとき、積層セラミック電子部品の信頼性、たとえばBDVが低下することがあった。

【解決手段】外層部24における外層ダミー導体7同士の間隔をd1、内層部における第1および第2の内部電極3および4の間隔をd2、としたとき、1.7d2≦d1を満足するようにする。このように、外層部24における外層ダミー導体7の密度を低減することにより、焼成前のプレス時において外層ダミー導体7による内部電極3,4の押圧が緩和され、それによって、局所的に内部電極間距離が短くなることを防止することができ、BDVの低下といった積層セラミック電子部品の信頼性の低下を効果的に抑制することができる。

【解決手段】外層部24における外層ダミー導体7同士の間隔をd1、内層部における第1および第2の内部電極3および4の間隔をd2、としたとき、1.7d2≦d1を満足するようにする。このように、外層部24における外層ダミー導体7の密度を低減することにより、焼成前のプレス時において外層ダミー導体7による内部電極3,4の押圧が緩和され、それによって、局所的に内部電極間距離が短くなることを防止することができ、BDVの低下といった積層セラミック電子部品の信頼性の低下を効果的に抑制することができる。

【発明の詳細な説明】

【技術分野】

【0001】

この発明は、積層セラミック電子部品に関するものであり、特に、セラミック素体の外表面上に直接形成されためっき膜を含む外部電極を備える積層セラミック電子部品に関するものである。

【背景技術】

【0002】

近年、携帯電話、ノートパソコン、デジタルカメラ、デジタルオーディオ機器等の電子機器は小型化が進んでおり、これら電子機器には、小型化かつ高性能化が可能な積層セラミック電子部品が多数用いられている。

【0003】

通常、積層セラミック電子部品は、複数の積層されたセラミック層を有するセラミック素体と、セラミック素体の内部に形成された内部電極と、セラミック素体の外表面上に形成された外部電極とを備える。そして、積層セラミック電子部品は、実装基板の導電ランド上に配置され、はんだなどの導電性接合材を介して基板上に実装される。

【0004】

現在、積層セラミック電子部品には、さらなる小型化の要求がある。

【0005】

しかしながら、積層セラミック電子部品を小型化すると、内部電極同士が対向する有効面積が小さくなるため、一般的に特性は低下する傾向にある。

【0006】

また、多端子型の積層セラミック電子部品においては、複数のストライプ状の外部電極を狭ピッチで形成する必要があるが、従来の厚膜ペーストの焼付けによる方法ではペースト塗布精度に限界があり、高精度に外部電極を形成することは困難である。

【0007】

これを受けて、外部電極を直接めっきにより形成する方法が提案されている。この方法によれば、薄くフラットな外部電極を形成することができるため、その分、内部電極の有効面積を広げることができる。また、内部電極の露出部にめっきが析出するため、狭ピッチであっても高精度に外部電極を形成することができる。

【0008】

このように外部電極を直接めっきにより形成する場合において、より確実なめっき成長を実現するため、ダミー導体(アンカータブ)を用いることが、たとえば特許文献1において提案されている。特許文献1に記載の技術によれば、内部電極の露出部だけでなくダミー導体の露出部にもめっき金属を析出させることが可能となり、より確実にめっきを成長させることができるとされている。

【先行技術文献】

【特許文献】

【0009】

【特許文献1】特開2004−327983号公報

【発明の概要】

【発明が解決しようとする課題】

【0010】

しかし、特許文献1に記載の方法では、積層セラミック電子部品の信頼性、たとえばBDV(破壊電圧)が低下することがあった。その原因を探るべく、本件発明者が鋭意研究を重ねた結果、信頼性(BDV)が低下するのは、ダミー導体の存在が原因となっていることがわかった。より詳細には、いずれの内部電極も存在しない外層部にダミー導体が存在するとき、このダミー導体と重なった内部電極が、焼成前のプレス時にダミー導体の存在により必要以上に押圧され、局所的に内部電極間距離が短くなることに起因することがわかった。

【0011】

そこで、この発明の目的は、上記のような問題を解決し得る構造を有する、積層セラミック電子部品を提供しようとすることである。

【課題を解決するための手段】

【0012】

この発明は、次のような構成を備える積層セラミック電子部品に向けられる。

【0013】

(1)複数のセラミック層が積層されてなるもので、外表面として、互いに対向する1対の主面と、互いに対向する1対の側面と、互いに対向する1対の端面と、を有し、1対の端面を結ぶ長さ方向に沿った側面の寸法が、1対の側面を結ぶ幅方向に沿った端面の寸法よりも長い、セラミック素体、

(2)セラミック素体の内部に配置され、長辺および短辺を有する長方形状の第1の対向部と、第1の対向部の長辺からセラミック素体の側面に引き出された第1の引出し部と、を有する第1の内部電極、

(3)セラミック素体の内部に配置され、第1の対向部と対向する第2の対向部と、第2の対向部からセラミック素体の外表面に引き出された第2の引出し部と、を有する第2の内部電極、

(4)セラミック素体の側面上に配置され、第1の引出し部の露出部を直接覆うめっき膜を有する、第1の外部電極、ならびに、

(5)セラミック素体の外表面上に配置され、第2の引出し部の露出部と電気的に接続され、第1の外部電極とは異なる電位に接続される、第2の外部電極。

【0014】

また、第1および第2の主面を結ぶ方向を高さ方向に沿って、第1の内部電極および第2の内部電極が存在する領域を内層部と定義し、高さ方向に沿って、第1の内部電極および第2の内部電極がいずれも存在しない領域を外層部と定義したとき、外層部には、セラミック素体を高さ方向に沿って投影した場合に第1の引出し部と重なるようにして側面に引き出され、第1の外部電極のめっき膜と接続された外層ダミー導体が高さ方向に沿って複数配置される。

【0015】

そして、この発明に係る積層セラミック電子部品は、前述した技術的課題を解決するため、次のような構成を備えることを特徴としている。

【0016】

すなわち、外層部における外層ダミー導体同士の間隔をd1、内層部における第1および第2の内部電極の間隔をd2、としたとき、

1.7d2≦d1

を満足することを特徴としている。

【0017】

さらに、d1≦6μmを満足することが好ましい。

【0018】

この発明に係る積層セラミック電子部品は、好ましい実施態様では、第1の引出し部は、長さ方向において、第1および第2の側面のうち少なくとも一方の中央にかかるように引き出されている。

【発明の効果】

【0019】

前述したように、外層部に外層ダミー導体が存在するとき、この外層ダミー導体と重なった内部電極が、焼成前のプレス時に外層ダミー導体の存在により必要以上に押圧され、局所的に内部電極間距離が短くなり、これが原因で積層セラミック電子部品の信頼性、たとえばBDV(破壊電圧)が低下することがあった。

【0020】

これは、プレス時に、外層ダミー導体が第1の内部電極の第1の引出し部を押圧し、押圧された第1の引出し部が第1の対向部を引きずり込むことにより、第1の引出し部の付け根の部分が沈み込むためであることがわかった。

【0021】

そして、本件発明者は、第1の引出し部が第1の対向部の長辺から引き出されている場合に、特に、この現象が生じやすいことを発見した。

【0022】

この発明によれば、第1の引出し部が第1の対向部の長辺から引き出された内部電極を有する積層セラミック電子部品において、外層部における外層ダミー導体の密度を低減することにより、焼成前のプレス時において外層ダミー導体による内部電極の押圧が緩和され、それによって、局所的に内部電極間距離が短くなることを防止することができる。したがって、このように局所的に内部電極間距離が短くなることに起因するBDVの低下といった積層セラミック電子部品の信頼性の低下を効果的に抑制することができる。

【0023】

この発明において、上述の信頼性の低下抑制の点からは、外層ダミー導体同士の間隔d1は長い方が好ましいと言えるが、d1がより長くなるほど、第1の外部電極のめっき膜の成長をより阻害する傾向が現れる。すなわち、外層ダミー導体の露出部を核として成長すべきめっき膜が高さ方向につながりにくくなるおそれがある。したがって、d1に関して、d1≦6μmを満足することが好ましく、この条件を満足すれば、第1の外部電極のめっき膜をより確実に成長させることができる。

【図面の簡単な説明】

【0024】

【図1】この発明の第1の実施形態による積層セラミック電子部品としての積層セラミックコンデンサ1の外観を示す斜視図である。

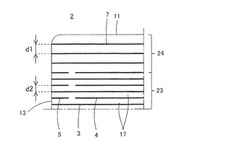

【図2】図1に示した積層セラミックコンデンサ1の、セラミック素体2の側面11および12に平行な面に沿う切断部端面図である。

【図3】図1に示した積層セラミックコンデンサ1の、セラミック素体2の端面13および14に平行な面に沿う切断部端面図である。

【図4】図1に示した積層セラミックコンデンサ1の、セラミック素体2の主面9および10に平行な面に沿う切断部端面図であり、第1の内部電極3が延びる面を示す。

【図5】図1に示した積層セラミックコンデンサ1の、セラミック素体2の主面9および10に平行な面に沿う切断部端面図であり、第2の内部電極4が延びる面を示す。

【図6】図1に示した積層セラミックコンデンサ1の、セラミック素体2の主面9および10に平行な面に沿う切断部端面図であり、外層ダミー導体7が延びる面を示す。

【図7】図3に示したセラミック素体2の一部を拡大して示す図であり、この発明の特徴を説明するためのものである。

【図8】この発明の第2の実施形態による積層セラミック電子部品としての積層セラミックコンデンサ1aの、セラミック素体2の端面13および14に平行な面に沿う切断部端面図である。

【図9】この発明の第3の実施形態による積層セラミック電子部品としての積層セラミックコンデンサ1bの外観を示す斜視図である。

【図10】図9に示した積層セラミックコンデンサ1bの、セラミック素体2の端面13および14に平行な面に沿う切断部端面図である。

【図11】この発明の第4の実施形態による積層セラミック電子部品としての積層セラミックコンデンサ1cの、セラミック素体2の側面11および12に平行な面に沿う切断部端面図である。

【図12】図11に示した積層セラミックコンデンサ1cの、セラミック素体2の主面9および10に平行な面に沿う切断部端面図であり、外層ダミー導体7および8が延びる面を示す。

【発明を実施するための形態】

【0025】

以下に、この発明を実施するための形態を説明するにあたり、積層セラミック電子部品として、積層セラミックコンデンサを例示する。

【0026】

[第1の実施形態]

図1ないし図7は、この発明の第1の実施形態を説明するためのものである。第1の実施形態による積層セラミックコンデンサ1は、セラミック素体2と、セラミック素体2の内部にそれぞれ配置された、第1および第2の内部電極3および4、第1および第2の内層ダミー導体5および6ならびに外層ダミー導体7と、セラミック素体2の外表面上に配置された第1および第2の外部電極9および10と、を備えている。以下、積層セラミックコンデンサ1の構造の詳細を、(1)セラミック素体、(2)内部電極、(3)内層ダミー導体、(4)外層ダミー導体、(5)外部電極に分けて説明し、その後、(6)製造方法について説明する。

【0027】

(1)セラミック素体

セラミック素体2は、その外表面として、互いに対向する第1および第2の主面11および12と、互いに対向する1対の側面13および14と、互いに対向する1対の端面15および16とを有する、ほぼ直方体状をなしている。

【0028】

ここで、主面11および12間を結ぶ方向を高さ方向、側面13および14間を結ぶ方向を幅方向、端面15および16間を結ぶ方向を長さ方向とそれぞれ定義する。この実施形態では、長さ方向の寸法が幅方向の寸法よりも長く、長さ方向の寸法は幅方向寸法のおよそ2倍である。

【0029】

セラミック素体2は、コーナー部および稜部に丸みがつけられていることが好ましい。

【0030】

セラミック素体2は、図2および図3に示すように、主面11および12の方向に延びかつ高さ方向に積層された複数のセラミック層17からなる積層構造を有する。セラミック層17の各厚みは0.5〜10μmであることが好ましく、特に0.7〜3.0μmであることが好ましい。セラミック層17を構成するセラミック材料としては、たとえば、BaTiO3、CaTiO3、SrTiO3、CaZrO3などを主成分とする誘電体セラミックを用いることができる。また、これらの主成分に、Mn化合物、Mg化合物、Si化合物、Co化合物、Ni化合物、希土類元素化合物などの副成分を添加したものを用いてもよい。

【0031】

(2)内部電極

内部電極は、図4に示した複数の第1の内部電極3および図5に示した複数の第2の内部電極4を備える。複数の第1の内部電極3および複数の第2の内部電極4は、図2および図3に示すように、セラミック素体2の積層方向に交互に配列される。

【0032】

(2)−1.第1の内部電極

第1の内部電極3は、図4に示すように、これと隣り合う第2の内部電極4に対向する第1の対向部19と、第1の対向部19からセラミック素体2の外表面に引き出された2つの第1の引出し部20とを有する。この実施形態においては、第1の内部電極3は十字形状に形成され、2つの第1の引出し部20の一方および他方は、それぞれ、第1および第2の側面13および14に引き出されている。言い換えると、第1の内部電極3は、第1の側面13から第2の側面14に至るようにして配置される。第1の対向部19は、長さ方向に沿った長辺および幅方向に沿った短辺を有する長方形状であり、第1の引出し部20は、第1の対向部19の長辺から側面13および14の各々の中央部にかかるように引き出されている。

【0033】

(2)−2.第2の内部電極

第2の内部電極4は、図5に示すように、これと隣り合う第1の内部電極3に対向する第2の対向部21と、第2の対向部21からセラミック素体2の外表面に引き出された第2の引出し部22とを有する。図5において、第2の内部電極4における第2の対向部21と第2の引出し部22との境界が破線で示されている。この実施形態においては、第2の内部電極4は長方形状に形成される。また、第2の内部電極4は、2つの第2の引出し部22を備え、2つの第2の引出し部22の一方および他方は、それぞれ、第1および第2の端面15および16に引き出されている。言い換えると、第2の内部電極4は、第1の端面15から第2の端面16に至るようにして配置される。

【0034】

(2)−3.その他

内部電極3および4を構成する導電材料としては、たとえば、Ni、Cu、Ag、Pd、Ag−Pd合金、Auなどを用いることができる。

【0035】

また、内部電極3および4の各厚みは、0.3〜2.0μmであることが好ましい。

【0036】

第1の内部電極3の第1の対向部19と第2の内部電極4の第2の対向部21とがセラミック層17を挟んで対向する領域において静電容量が生じる。この部分を含み、高さ方向に沿って、第1および第2の内部電極3および4が存在する領域を内層部23と定義する。

【0037】

一方、高さ方向に沿って、第1および第2の内部電極3および4がいずれも存在しない領域を外層部24と定義する。外層部24は、内層部23を挟むようにして、第1の主面11側および第2の主面12側にそれぞれ存在する。

【0038】

(3)内層ダミー導体

内層ダミー導体は、内層部23に配置されるもので、図5に示した複数の第1の内層ダミー導体5および図4に示した複数の第2の内層ダミー導体6を備える。

【0039】

(3)−1.第1の内層ダミー導体

第1の内層ダミー導体5は、この実施形態では、図5に示すように、第2の内部電極4と同一面上に配置されている。第1の内層ダミー導体5は、第1の外部電極9に接続される。

【0040】

(3)−2.第2の内層ダミー導体

第2の内層ダミー導体6は、この実施形態では、図4に示すように、第1の内部電極3と同一面上に配置されている。第2の内層ダミー導体6は、第2の外部電極10に接続される。

【0041】

(3)−3.その他

内層ダミー導体5および6は、第1および第2の外部電極9および10の下地層を構成するめっき膜の析出ポイントとして機能し、通電効率を向上させる。また、セラミック素体2の強度向上にも寄与する。

【0042】

内層ダミー導体5および6の材質および厚みの好ましい条件は、内部電極3および4の場合と同様である。内層ダミー導体5および6は、内部電極3および4と同じ材質および同じ厚みをもって構成されることが望ましい。

【0043】

なお、内層ダミー導体5および6は形成されていなくてもよい。

【0044】

(4)外層ダミー導体

図2および図3に示すように、外層ダミー導体7は外層部24に配置される。

【0045】

外層ダミー導体7は、セラミック素体2の外表面の少なくとも2箇所に引き出されることが好ましい。この実施形態において、外層ダミー導体7は、図6に示すように、長方形状に形成され、セラミック素体2の外表面の2箇所、すなわち、第1の側面13および第2の側面14にそれぞれ引き出される。言い換えると、外層ダミー導体7は、第1の側面13から第2の側面14に至るようにして配置される。

【0046】

外層ダミー導体7は、第1の外部電極9の下地層を構成するめっき膜の析出ポイントとして機能するものであるが、上述のように、2箇所に引き出されるため、めっき時において、スチールボールなどのメディアが外層ダミー導体7の一方の露出部に接触すれば、他方の露出部にも通電する。つまり、外層ダミー導体7が2箇所以上の露出部を有すると、メディアと接触する確率が高くなり、通電効率が高まる。これにより、後述する第1の外部電極9の下地層となるめっき膜を形成するために必要なめっき時間が短縮される。

【0047】

外層ダミー導体7は、図2および図3に示すように、セラミック層17の積層方向に沿って連続して複数枚積層されている。外層ダミー導体7は、各外層部24においてそれぞれ10〜100枚配置されていることが好ましい。

【0048】

外層ダミー導体7は、セラミック素体2を高さ方向に沿って投影した場合に、第1の引出し部20と重なるように配置される。そのため、外層ダミー導体7は、セラミック素体2の外表面において、第1の引出し部20の露出部と協働して列状の露出部グループを形成する。この実施形態においては、第1および第2の側面13および14において、それぞれ露出部グループが形成されている。

【0049】

図7を参照して、外層部24における外層ダミー導体7同士の間隔をd1、内層部23における第1および第2の内部電極3および4の間隔をd2、としたとき、

1.7d2≦d1

を満足するようにされる。

【0050】

このように、外層部24における外層ダミー導体7の密度を低減することにより、焼成前のプレス時において外層ダミー導体7による内部電極3および4の押圧が緩和され、それによって、局所的に内部電極間距離が短くなることを防止することができ、たとえばBDVの低下といった積層セラミック電子部品の信頼性の低下を効果的に抑制することができる。

【0051】

後述する実験例からわかるように、d1が1.7d2より小さい場合、信頼性が低下するおそれがある。

【0052】

この実施形態のように、第1の引出し部が、長さ方向において、1対の側面13および14のうち少なくとも一方の中央にかかるように引き出されている場合、第1の引出し部20の付け根の部分での沈み込みが大きくなるため、このような局面において、上述の効果が一層期待できる。

【0053】

なお、信頼性の低下抑制の点からは、上記d1は、長い方が好ましいと言えるが、d1がより長くなるほど、第1の外部電極9の下地層となるめっき膜の成長をより阻害する傾向が現れる。すなわち、外層ダミー導体7の露出部を核として成長すべきめっき膜が高さ方向につながりにくくなるおそれがある。この点から、d1≦6μmを満足することが好ましい。

【0054】

外層ダミー導体7は、内部電極3および4と同じ材料からなることが好ましく、外層ダミー導体7を構成する導電材料としては、前述したように、たとえば、Ni、Cu、Ag、Pd、Ag−Pd合金、Auなどを用いることができる。

【0055】

外層ダミー導体7の厚みは0.3〜2.0μmであることが好ましい。

【0056】

(5)外部電極

(5)−1.第1の外部電極

第1の外部電極9は、図3によく示されているように、セラミック素体2の第1および第2の側面13および14上にそれぞれ配置されている。この実施形態では、第1の外部電極9は、第1および第2の主面11および12にまで回り込んでいる。

【0057】

第1の外部電極9は、第1の内部電極3と電気的に接続される。第1の外部電極9は、図3ないし図6に示すように、下地層25およびその上に必要に応じて形成される上層26を含む。

【0058】

第1の外部電極9の下地層25は、めっき膜により構成される。第1の外部電極9の下地層25を構成するめっき膜は、第1の内部電極3の第1の引出し部20の露出部および第1の内層ダミー導体5の露出部を直接覆うとともに、外層ダミー導体7の露出部を直接覆う。下地層25となるめっき膜を構成する金属としては、たとえば、Cu、Ni、Ag、Pd、Ag−Pd合金、Au、Sn、Pb、Pd、Bi、Znなどを用いることができる。めっき膜は、ガラス成分を含まないことが好ましい。また、めっき膜の単位体積あたりの金属割合は99体積%以上であることが好ましい。めっき膜の厚みは、最も厚い部分において、1〜15μmであることが好ましい。第1の内層ダミー導体5および外層ダミー導体7は、下地層25となるめっき膜の析出および成長を促進するように作用する。

【0059】

第1の外部電極9において上層26が形成される場合、上層26は、たとえば、めっき膜により構成される。上層26となるめっき膜を構成する金属としては、たとえば、Cu、Ni、Ag、Pd、Ag−Pd合金、Au、Sn、Pb、Pd、Bi、Znなどを用いることができる。上層26のめっき膜は、複数層から構成されてもよい。上層26のめっき膜の厚みは、1層あたり、1〜10μmであることが好ましい。

【0060】

第1の外部電極9において上層26が形成される場合、好ましくは、下地層25がNiめっき膜から構成され、上層26がSnめっき膜から構成される。あるいは、上層26が複数層から構成される場合、好ましくは、Niめっき層およびその上のSnめっき層の2層構造とされる。

【0061】

(5)−2.第2の外部電極

第2の外部電極10は、第1の外部電極9とは異なる電位に接続されるもので、セラミック素体2の第1および第2の端面15および16上にそれぞれ配置されている。この実施形態では、第2の外部電極10は、第1および第2の主面11および12ならびに第1および第2の側面13および14にまで回り込んでいる。

【0062】

第2の外部電極10は、第2の内部電極4と電気的に接続されるようにして、第2の引出し部22の露出部を覆う。第2の外部電極10は、図2および図4ないし図6に示すように、第2の内部電極4の第2の引出し部22の露出部と接触する下地層27およびその上に必要に応じて形成される上層28を含む。下地層27は、めっき膜、焼結金属膜、および/または導電性樹脂膜などにより構成され得る。

【0063】

下地層27を構成するものとしてめっき膜が選択される場合、めっき膜を構成する金属としては、たとえば、Cu、Ni、Ag、Pd、Ag−Pd合金、Au、Sn、Pb、Pd、Bi、Znなどを用いることができる。めっき膜は、ガラス成分を含まないことが好ましい。また、下地層27の厚みは、最も厚い部分で、1〜20μmであることが好ましい。前述した第2の内層ダミー導体6は、下地層27となるめっき膜の析出および成長を促進するように作用する。

【0064】

下地層27を構成するものとして焼結金属膜が選択される場合、焼結金属膜を構成する金属としては、たとえば、Cu、Ni、Ag、Pd、Ag−Pd合金、Auなどを用いることができる。焼結金属膜には、ガラス成分が含まれ得る。また、焼結金属膜は、セラミック素体2ならびに内部電極3および4と同時焼成されたものでもよく、焼成後のセラミック素体2に導電性ペーストを塗布して焼き付けられたものでもよい。

【0065】

下地層27を構成するものとして導電性樹脂膜が選択される場合、熱硬化性樹脂および金属フィラーを混合したものを用いて導電性樹脂膜を形成することができる。

【0066】

上述した焼結金属膜または導電性樹脂膜が選択される場合、下地層27の厚みは、最も厚い部分で、10〜50μmであることが好ましい。

【0067】

図示の実施形態では、下地層27は、第2の内部電極4および第2の内層ダミー導体6の各露出部と接触するめっき膜29と、このめっき膜29上に形成される焼結金属膜30とから構成される。

【0068】

第2の外部電極10において、上記下地層27上に形成される上層28がさらに形成される場合、上層28は、たとえば、めっき膜により構成される。上層28となるめっき膜を構成する金属としては、たとえば、Cu、Ni、Ag、Pd、Ag−Pd合金、Au、Sn、Pb、Pd、Bi、Znなどを用いることができる。上層28のめっき膜は、複数層から構成されてもよい。この場合、好ましくは、Niめっき層およびその上のSnめっき層の2層構造とされる。上層28のめっき膜の厚みは、1層あたり、1〜10μmであることが好ましい。

【0069】

(6)製造方法

積層セラミックコンデンサ1は、たとえば、次のようにして製造される。

【0070】

(6)−1.

セラミック層17となるべきセラミックグリーンシート、内部電極用導電性ペースト、および外部電極用導電性ペーストを準備する。内部電極用導電性ペーストは、内層ダミー導体用導電性ペーストおよび外層ダミー導体用導電性ペーストを兼ねる。セラミックグリーンシートならびに内部電極用および外部電極用の各導電性ペーストには、バインダおよび溶剤が含まれるが、公知の有機バインダや有機溶剤を用いることができる。

【0071】

(6)−2.

セラミックグリーンシート上に、たとえばスクリーン印刷などにより所定のパターンで導電性ペーストを印刷し、内部電極パターン、内層ダミー導体パターンおよび外層ダミー導体パターンを形成する。

【0072】

(6)−3.

内部電極パターンが印刷されていない外層用セラミックグリーンシート、外層ダミー導体パターンが印刷されたセラミックグリーンシート、内部電極パターンおよび内層ダミー導体パターンが印刷されたセラミックグリーンシートを、それぞれ所定枚数かつ所定順序で積層し、マザー積層体を作製する。

【0073】

ここで、外層部において、外層ダミー導体パターンが印刷されていないセラミックグリーンシートの積層枚数を調整することにより、前述の距離d1を調整することができる。あるいは、外層用セラミックグリーンシートの厚みを調整することにより、距離d1を調整してもよい。

【0074】

なお、内層部において、内部電極パターンおよび内層ダミー導体パターンが印刷されていないセラミックグリーンシートの積層枚数を調整することにより、前述の距離d2を調整することも、あるいは、内層用セラミックグリーンシートの厚みを調整することにより、距離d2を調整することも可能である。

【0075】

(6)−4.

マザー積層体を積層方向にプレスする。

【0076】

(6)−5.

マザー積層体を所定のサイズにカットし、生のセラミック素体を切り出す。

【0077】

(6)−6.

生のセラミック素体を焼成する。これによって、図示したセラミック素体2が得られる。焼成温度は、セラミックや内部電極の材料にもよるが、900〜1300℃であることが好ましい。

【0078】

この後、必要に応じて、バレル研磨を行なう。これにより、セラミック素体2のコーナー部や稜部に丸みが付けられる。

【0079】

(6)−7.

研磨後のセラミック素体2に対して、めっき処理を行なう。

【0080】

これによって、第1の外部電極9の、めっき膜からなる下地層25が形成される。このとき、図3に示すように、第1の内部電極3ばかりでなく、第1の内層ダミー導体5および外層ダミー導体7が、側面13および14上に露出していて、これらの露出部分を起点にめっきが析出するため、第1の外部電極9の下地層25を能率的に形成することができる。

【0081】

めっき処理には、回転バレル法による電解めっきを適用することが好ましい。めっき方法は回転バレルめっきであることが好ましい。めっき処理には、スチールボールなどの導電性メディアが用いられる。

【0082】

外層ダミー導体7は、2つの露出部を有しているため、めっき工程において、導電性メディアが一方の露出部に接触すれば、他方の露出部にも通電する。つまり、メディアと接触する確率が高くなり、通電効率が高まる。これにより、下地層25の形成のためのめっき時間が短縮される。

【0083】

このめっき処理において、同時に、第2の内部電極4および第2の内層ダミー導体6の各露出部をめっき析出の起点として、第2の外部電極10の下地層27におけるめっき膜29も形成され得る。

【0084】

めっき処理後、600〜900℃の温度で熱処理を行なうことが好ましい。これにより、セラミック素体2に対するめっき膜の固着力が向上する。

【0085】

(6)−8.

第2の外部電極10の下地層27における焼結金属膜30が、導電性ペーストを塗布し、焼き付けることによって形成される。焼き付け温度は、700〜900℃であることが好ましい。

【0086】

(6)−9.

第1の外部電極9の上層26および第2の外部電極10の上層28を形成するため、めっき処理を行なう。

【0087】

以上のようにして、積層セラミックコンデンサ1が完成される。

【0088】

[第2の実施形態]

この発明の第2の実施形態が図8に示されている。図8は、図3に対応する図である。図8において、図3に示す要素に相当する要素には同様の参照符号を付し、重複する説明は省略する。

【0089】

第2の実施形態による積層セラミックコンデンサ1aでは、外層ダミー導体7aが、セラミック素体2を幅方向に貫通して形成されておらず、幅方向に沿って分離して形成されている。

【0090】

[第3の実施形態]

この発明の第3の実施形態が図9および図10に示されている。図9は、図1に対応する図であり、図10は、図3に対応する図である。図9および図10において、図1および図3に示す要素に相当する要素には同様の参照符号を付し、重複する説明は省略する。

【0091】

第3の実施形態による積層セラミックコンデンサ1bでは、第1の外部電極9bが、下地層25および上層26を含めて、セラミック素体2の第1および第2の側面13および14ならびに第1および第2の主面11および12を周回するように配置されていることを特徴としている。

【0092】

この実施形態では、主面11および12を与えるセラミック層17を前述した焼成後の研磨工程で削り取り、主面11および12の各々の少なくとも一部に外層ダミー導体7を露出させておくことが好ましい。これにより、主面11および12上にもめっきの析出ポイントが追加されるため、第1の外部電極9bの下地層25となるめっき膜を周回した状態で形成することが容易になる。

【0093】

なお、外層ダミー導体7は、主面11および12上に、その全面が露出している必要はなく、不連続状に(たとえば、まだら状に)分布して露出していてもよい。ただし、外層ダミー導体7の主面11および12における露出部分は、第1の側面13から第2の側面14にかけて一様に分布していることが好ましく、また、第1の側面13から第2の側面14にかけて途切れることなく露出していることが望ましい。このように、第1の側面13から第2の側面14にかけてわずかでも外層ダミー導体7が連続的に露出している部分がある場合、通電面積が主面11および12における第1の側面13側から第2の側面14側にまで及ぶことになるため、最も通電効率が高くなる。

【0094】

この実施形態によれば、第1の外部電極9bの下地層25を形成するためのめっき工程において生じるめっき成長の過程で、めっき膜がセラミック素体2を周回するようにつながることにより、めっきの析出ポイントとなり得る電極面積が大きくなるので、その時点から通電効率が向上し、単位時間で生成できる膜厚が厚くなる。つまり、この実施形態によれば、第1の外部電極9bの下地層25において、所定の膜厚を形成する時間が短くなり、コスト削減となる。

【0095】

前述した第1の実施形態では、セラミック素体2の主面11および12に第1の外部電極9の先端部分が存在する。当該積層セラミックコンデンサ1を実装する基板のたわみなどにより、第1の外部電極9の先端部分に応力が加わると、ここを起点に下地層25が剥がれる可能性が高い。しかし、この実施形態では、第1の外部電極9bがエンドレスであり、先端部分がなくなるため、剥がれの問題が起こりにくくなる。

【0096】

また、第1の実施形態では、主面11および12上に位置する第1の外部電極9の下地層25の先端部分が、上層26をめっきにより形成する際に用いられるめっき液の浸入の入り口となって、信頼性が低下する可能性がある。しかし、この実施形態では、第1の外部電極9bの下地層25には、先端部分が存在しないため、信頼性低下の問題も起こりにくくなる。

【0097】

また、第1の外部電極9bはセラミック素体2を周回するめっき膜から構成されるので、この第1の外部電極9bを、セラミック素体2の外表面に沿う平滑なものとすることができる。このため、積層セラミックコンデンサ1bは、その実装時に転がりにくく、姿勢を安定なものとすることができる。

【0098】

[第4の実施形態]

この発明の第4の実施形態が図11ないし図12に示されている。図11は、図2に対応する図であり、図12は、図6に対応する図である。図11および図12において、図2および図6に示す要素に相当する要素には同様の参照符号を付し、重複する説明は省略する。

【0099】

第4の実施形態による積層セラミックコンデンサ1cでは、外層ダミー導体7と同一面上に第2の外層ダミー導体8が配置されていることを特徴としている。

【0100】

また、第2の外部電極10cの下地層27全体がめっき膜により構成されている。これによって、第1および第2の外部電極9および10cの下地層25および27を同時に形成することができる。

【0101】

第2の外層ダミー導体8は、第2の外部電極10cの下地層27を構成するめっき膜の析出ポイントとして機能し、通電効率を向上させる。

【0102】

[その他の実施形態]

ダミー導体、特に外層ダミー導体は電気的特性の発現に寄与するものであってもよい。さらに、ダミー導体は、いかなる形状であってもよく、たとえば、外層ダミー導体は内部電極と同じ形状であってもよい。

【0103】

[実験例]

第1の実施形態に基づいて、次のような積層セラミックコンデンサを作製した。

【0104】

(1)セラミック素体の長さ方向寸法×幅方向寸法×高さ方向寸法:1.6mm×0.8mm×0.8mm

(2)第1の外部電極

下地層:厚み10μmのCuめっき膜

上層:厚み3μmのNiめっき膜およびその上の厚み3μmのSnめっき膜

(3)第2の外部電極

下地層:厚み10μmのCuめっき膜およびその上の厚み15μmのCu焼結金属膜

上層:厚み3μmのNiめっき膜およびその上の厚み3μmのSnめっき膜

(4)内部電極

内部電極間距離d2:表1のとおり

内部電極の厚み:0.56μm

内部電極の枚数:345枚

(5)内層ダミー導体

内部電極と同じ

(6)外層ダミー導体

外層ダミー導体間距離d1:表1のとおり

外層ダミー導体の厚み:0.56μm

外層ダミー導体の枚数:上下の外層部で各56枚ずつ

表1に示すように、d1およびd2を変えた各試料につき、BDVおよびめっき付き不良を評価した。

【0105】

なお、d1およびd2を測定するにあたって、各試料を3個ずつ準備し、セラミック素体を幅方向寸法の1/2程度まで研磨し、研磨面に、長さ方向寸法および厚み方向寸法によって規定される断面を露出させた。

【0106】

そして、d1については、上記断面において、長さ方向寸法の1/2程度に位置する第1の主面側の外層部にある外層ダミー導体間距離すべてを、電子顕微鏡により測定し、試料3個での平均値を求めた。

【0107】

他方、d2については、上記断面において、長さ方向寸法の1/2程度に位置する内層部の最上層に位置する15層分の内部電極間距離を、電子顕微鏡により測定し、試料3個での平均値を求めた。

【0108】

BDVについては、各試料を10個ずつ準備し、直流電圧破壊試験機により、昇圧速度100V/秒の条件で測定した。

【0109】

めっき付き不良については、第1の外部電極における下地層となるCuめっき膜を形成した段階での試料を1500個ずつ準備し、外層部と内層部との間でのCuめっき膜の状態を光学顕微鏡により確認し、めっき膜が切れているものをめっき付き不良とし、1500個の試料中において、めっき付き不良となった試料数を求めた。

【0110】

なお、上記の第1の外部電極における下地層となるCuめっき膜は、次のようにして形成した。まず、pH8.5で、浴温25℃とされた、14g/Lのピロリン酸銅、120g/Lのピロリン酸カリウム、および10g/Lの蓚酸カリウムを含むめっき浴を用いて、回転バレルめっきにより、電流密度0.1A/dm2の条件で、60分間、ストライクCuめっきを行ない、次に、pH8.8で、浴温55℃とされた、上村工業製ピロブライトプロセス用浴を用いて、回転バレルめっきにより、電流密度0.3A/dm2の条件で、60分間、厚付けCuめっきを行なうことによって、Cuめっき膜を形成した。

【0111】

【表1】

【0112】

表1からわかるように、1.7d2≦d1を満足する試料3〜9では、100V以上のBDVを達成した。

【0113】

これらの試料3〜9のうち、特に、d1≦6μmを満足する試料3〜6では、めっき付き性も良好であった。

【0114】

他方、試料1および2では、めっき付き性が良好であったが、1.7d2≦d1を満足しないため、BDVが100V未満となった。

【0115】

なお、表には記載していないが、上記実験例の条件の内部電極間距離d2を3.0μm付近または0.7μm付近のものに変えて同様の実験を行なったところ、上記実験結果と同様の効果が得られることが確認できている。

【産業上の利用可能性】

【0116】

この発明は、以上説明した積層セラミックコンデンサに限らず、他の積層セラミック電子部品にも適用することができる。たとえば、セラミック素体を圧電体セラミックで構成した場合は、圧電部品として機能する積層セラミック電子部品とすることができ、セラミック素体をスピネル状セラミックなどの半導体セラミックで構成した場合は、サーミスタとして機能する積層セラミック電子部品とすることができる。

【符号の説明】

【0117】

1,1a,1b,1c 積層セラミックコンデンサ

2 セラミック素体

3 第1の内部電極

4 第2の内部電極

7,7a 外層ダミー導体

9,9b 第1の外部電極

10,10c 第2の外部電極

11,12 主面

13,14 側面

15,16 端面

17 セラミック層

19 第1の対向部

20 第1の引出し部

21 第2の対向部

22 第2の引出し部

23 内層部

24 外層部

25 第1の外部電極の下地層

26 第1の外部電極の上層

27 第2の外部電極の下地層

28 第2の外部電極の上層

【技術分野】

【0001】

この発明は、積層セラミック電子部品に関するものであり、特に、セラミック素体の外表面上に直接形成されためっき膜を含む外部電極を備える積層セラミック電子部品に関するものである。

【背景技術】

【0002】

近年、携帯電話、ノートパソコン、デジタルカメラ、デジタルオーディオ機器等の電子機器は小型化が進んでおり、これら電子機器には、小型化かつ高性能化が可能な積層セラミック電子部品が多数用いられている。

【0003】

通常、積層セラミック電子部品は、複数の積層されたセラミック層を有するセラミック素体と、セラミック素体の内部に形成された内部電極と、セラミック素体の外表面上に形成された外部電極とを備える。そして、積層セラミック電子部品は、実装基板の導電ランド上に配置され、はんだなどの導電性接合材を介して基板上に実装される。

【0004】

現在、積層セラミック電子部品には、さらなる小型化の要求がある。

【0005】

しかしながら、積層セラミック電子部品を小型化すると、内部電極同士が対向する有効面積が小さくなるため、一般的に特性は低下する傾向にある。

【0006】

また、多端子型の積層セラミック電子部品においては、複数のストライプ状の外部電極を狭ピッチで形成する必要があるが、従来の厚膜ペーストの焼付けによる方法ではペースト塗布精度に限界があり、高精度に外部電極を形成することは困難である。

【0007】

これを受けて、外部電極を直接めっきにより形成する方法が提案されている。この方法によれば、薄くフラットな外部電極を形成することができるため、その分、内部電極の有効面積を広げることができる。また、内部電極の露出部にめっきが析出するため、狭ピッチであっても高精度に外部電極を形成することができる。

【0008】

このように外部電極を直接めっきにより形成する場合において、より確実なめっき成長を実現するため、ダミー導体(アンカータブ)を用いることが、たとえば特許文献1において提案されている。特許文献1に記載の技術によれば、内部電極の露出部だけでなくダミー導体の露出部にもめっき金属を析出させることが可能となり、より確実にめっきを成長させることができるとされている。

【先行技術文献】

【特許文献】

【0009】

【特許文献1】特開2004−327983号公報

【発明の概要】

【発明が解決しようとする課題】

【0010】

しかし、特許文献1に記載の方法では、積層セラミック電子部品の信頼性、たとえばBDV(破壊電圧)が低下することがあった。その原因を探るべく、本件発明者が鋭意研究を重ねた結果、信頼性(BDV)が低下するのは、ダミー導体の存在が原因となっていることがわかった。より詳細には、いずれの内部電極も存在しない外層部にダミー導体が存在するとき、このダミー導体と重なった内部電極が、焼成前のプレス時にダミー導体の存在により必要以上に押圧され、局所的に内部電極間距離が短くなることに起因することがわかった。

【0011】

そこで、この発明の目的は、上記のような問題を解決し得る構造を有する、積層セラミック電子部品を提供しようとすることである。

【課題を解決するための手段】

【0012】

この発明は、次のような構成を備える積層セラミック電子部品に向けられる。

【0013】

(1)複数のセラミック層が積層されてなるもので、外表面として、互いに対向する1対の主面と、互いに対向する1対の側面と、互いに対向する1対の端面と、を有し、1対の端面を結ぶ長さ方向に沿った側面の寸法が、1対の側面を結ぶ幅方向に沿った端面の寸法よりも長い、セラミック素体、

(2)セラミック素体の内部に配置され、長辺および短辺を有する長方形状の第1の対向部と、第1の対向部の長辺からセラミック素体の側面に引き出された第1の引出し部と、を有する第1の内部電極、

(3)セラミック素体の内部に配置され、第1の対向部と対向する第2の対向部と、第2の対向部からセラミック素体の外表面に引き出された第2の引出し部と、を有する第2の内部電極、

(4)セラミック素体の側面上に配置され、第1の引出し部の露出部を直接覆うめっき膜を有する、第1の外部電極、ならびに、

(5)セラミック素体の外表面上に配置され、第2の引出し部の露出部と電気的に接続され、第1の外部電極とは異なる電位に接続される、第2の外部電極。

【0014】

また、第1および第2の主面を結ぶ方向を高さ方向に沿って、第1の内部電極および第2の内部電極が存在する領域を内層部と定義し、高さ方向に沿って、第1の内部電極および第2の内部電極がいずれも存在しない領域を外層部と定義したとき、外層部には、セラミック素体を高さ方向に沿って投影した場合に第1の引出し部と重なるようにして側面に引き出され、第1の外部電極のめっき膜と接続された外層ダミー導体が高さ方向に沿って複数配置される。

【0015】

そして、この発明に係る積層セラミック電子部品は、前述した技術的課題を解決するため、次のような構成を備えることを特徴としている。

【0016】

すなわち、外層部における外層ダミー導体同士の間隔をd1、内層部における第1および第2の内部電極の間隔をd2、としたとき、

1.7d2≦d1

を満足することを特徴としている。

【0017】

さらに、d1≦6μmを満足することが好ましい。

【0018】

この発明に係る積層セラミック電子部品は、好ましい実施態様では、第1の引出し部は、長さ方向において、第1および第2の側面のうち少なくとも一方の中央にかかるように引き出されている。

【発明の効果】

【0019】

前述したように、外層部に外層ダミー導体が存在するとき、この外層ダミー導体と重なった内部電極が、焼成前のプレス時に外層ダミー導体の存在により必要以上に押圧され、局所的に内部電極間距離が短くなり、これが原因で積層セラミック電子部品の信頼性、たとえばBDV(破壊電圧)が低下することがあった。

【0020】

これは、プレス時に、外層ダミー導体が第1の内部電極の第1の引出し部を押圧し、押圧された第1の引出し部が第1の対向部を引きずり込むことにより、第1の引出し部の付け根の部分が沈み込むためであることがわかった。

【0021】

そして、本件発明者は、第1の引出し部が第1の対向部の長辺から引き出されている場合に、特に、この現象が生じやすいことを発見した。

【0022】

この発明によれば、第1の引出し部が第1の対向部の長辺から引き出された内部電極を有する積層セラミック電子部品において、外層部における外層ダミー導体の密度を低減することにより、焼成前のプレス時において外層ダミー導体による内部電極の押圧が緩和され、それによって、局所的に内部電極間距離が短くなることを防止することができる。したがって、このように局所的に内部電極間距離が短くなることに起因するBDVの低下といった積層セラミック電子部品の信頼性の低下を効果的に抑制することができる。

【0023】

この発明において、上述の信頼性の低下抑制の点からは、外層ダミー導体同士の間隔d1は長い方が好ましいと言えるが、d1がより長くなるほど、第1の外部電極のめっき膜の成長をより阻害する傾向が現れる。すなわち、外層ダミー導体の露出部を核として成長すべきめっき膜が高さ方向につながりにくくなるおそれがある。したがって、d1に関して、d1≦6μmを満足することが好ましく、この条件を満足すれば、第1の外部電極のめっき膜をより確実に成長させることができる。

【図面の簡単な説明】

【0024】

【図1】この発明の第1の実施形態による積層セラミック電子部品としての積層セラミックコンデンサ1の外観を示す斜視図である。

【図2】図1に示した積層セラミックコンデンサ1の、セラミック素体2の側面11および12に平行な面に沿う切断部端面図である。

【図3】図1に示した積層セラミックコンデンサ1の、セラミック素体2の端面13および14に平行な面に沿う切断部端面図である。

【図4】図1に示した積層セラミックコンデンサ1の、セラミック素体2の主面9および10に平行な面に沿う切断部端面図であり、第1の内部電極3が延びる面を示す。

【図5】図1に示した積層セラミックコンデンサ1の、セラミック素体2の主面9および10に平行な面に沿う切断部端面図であり、第2の内部電極4が延びる面を示す。

【図6】図1に示した積層セラミックコンデンサ1の、セラミック素体2の主面9および10に平行な面に沿う切断部端面図であり、外層ダミー導体7が延びる面を示す。

【図7】図3に示したセラミック素体2の一部を拡大して示す図であり、この発明の特徴を説明するためのものである。

【図8】この発明の第2の実施形態による積層セラミック電子部品としての積層セラミックコンデンサ1aの、セラミック素体2の端面13および14に平行な面に沿う切断部端面図である。

【図9】この発明の第3の実施形態による積層セラミック電子部品としての積層セラミックコンデンサ1bの外観を示す斜視図である。

【図10】図9に示した積層セラミックコンデンサ1bの、セラミック素体2の端面13および14に平行な面に沿う切断部端面図である。

【図11】この発明の第4の実施形態による積層セラミック電子部品としての積層セラミックコンデンサ1cの、セラミック素体2の側面11および12に平行な面に沿う切断部端面図である。

【図12】図11に示した積層セラミックコンデンサ1cの、セラミック素体2の主面9および10に平行な面に沿う切断部端面図であり、外層ダミー導体7および8が延びる面を示す。

【発明を実施するための形態】

【0025】

以下に、この発明を実施するための形態を説明するにあたり、積層セラミック電子部品として、積層セラミックコンデンサを例示する。

【0026】

[第1の実施形態]

図1ないし図7は、この発明の第1の実施形態を説明するためのものである。第1の実施形態による積層セラミックコンデンサ1は、セラミック素体2と、セラミック素体2の内部にそれぞれ配置された、第1および第2の内部電極3および4、第1および第2の内層ダミー導体5および6ならびに外層ダミー導体7と、セラミック素体2の外表面上に配置された第1および第2の外部電極9および10と、を備えている。以下、積層セラミックコンデンサ1の構造の詳細を、(1)セラミック素体、(2)内部電極、(3)内層ダミー導体、(4)外層ダミー導体、(5)外部電極に分けて説明し、その後、(6)製造方法について説明する。

【0027】

(1)セラミック素体

セラミック素体2は、その外表面として、互いに対向する第1および第2の主面11および12と、互いに対向する1対の側面13および14と、互いに対向する1対の端面15および16とを有する、ほぼ直方体状をなしている。

【0028】

ここで、主面11および12間を結ぶ方向を高さ方向、側面13および14間を結ぶ方向を幅方向、端面15および16間を結ぶ方向を長さ方向とそれぞれ定義する。この実施形態では、長さ方向の寸法が幅方向の寸法よりも長く、長さ方向の寸法は幅方向寸法のおよそ2倍である。

【0029】

セラミック素体2は、コーナー部および稜部に丸みがつけられていることが好ましい。

【0030】

セラミック素体2は、図2および図3に示すように、主面11および12の方向に延びかつ高さ方向に積層された複数のセラミック層17からなる積層構造を有する。セラミック層17の各厚みは0.5〜10μmであることが好ましく、特に0.7〜3.0μmであることが好ましい。セラミック層17を構成するセラミック材料としては、たとえば、BaTiO3、CaTiO3、SrTiO3、CaZrO3などを主成分とする誘電体セラミックを用いることができる。また、これらの主成分に、Mn化合物、Mg化合物、Si化合物、Co化合物、Ni化合物、希土類元素化合物などの副成分を添加したものを用いてもよい。

【0031】

(2)内部電極

内部電極は、図4に示した複数の第1の内部電極3および図5に示した複数の第2の内部電極4を備える。複数の第1の内部電極3および複数の第2の内部電極4は、図2および図3に示すように、セラミック素体2の積層方向に交互に配列される。

【0032】

(2)−1.第1の内部電極

第1の内部電極3は、図4に示すように、これと隣り合う第2の内部電極4に対向する第1の対向部19と、第1の対向部19からセラミック素体2の外表面に引き出された2つの第1の引出し部20とを有する。この実施形態においては、第1の内部電極3は十字形状に形成され、2つの第1の引出し部20の一方および他方は、それぞれ、第1および第2の側面13および14に引き出されている。言い換えると、第1の内部電極3は、第1の側面13から第2の側面14に至るようにして配置される。第1の対向部19は、長さ方向に沿った長辺および幅方向に沿った短辺を有する長方形状であり、第1の引出し部20は、第1の対向部19の長辺から側面13および14の各々の中央部にかかるように引き出されている。

【0033】

(2)−2.第2の内部電極

第2の内部電極4は、図5に示すように、これと隣り合う第1の内部電極3に対向する第2の対向部21と、第2の対向部21からセラミック素体2の外表面に引き出された第2の引出し部22とを有する。図5において、第2の内部電極4における第2の対向部21と第2の引出し部22との境界が破線で示されている。この実施形態においては、第2の内部電極4は長方形状に形成される。また、第2の内部電極4は、2つの第2の引出し部22を備え、2つの第2の引出し部22の一方および他方は、それぞれ、第1および第2の端面15および16に引き出されている。言い換えると、第2の内部電極4は、第1の端面15から第2の端面16に至るようにして配置される。

【0034】

(2)−3.その他

内部電極3および4を構成する導電材料としては、たとえば、Ni、Cu、Ag、Pd、Ag−Pd合金、Auなどを用いることができる。

【0035】

また、内部電極3および4の各厚みは、0.3〜2.0μmであることが好ましい。

【0036】

第1の内部電極3の第1の対向部19と第2の内部電極4の第2の対向部21とがセラミック層17を挟んで対向する領域において静電容量が生じる。この部分を含み、高さ方向に沿って、第1および第2の内部電極3および4が存在する領域を内層部23と定義する。

【0037】

一方、高さ方向に沿って、第1および第2の内部電極3および4がいずれも存在しない領域を外層部24と定義する。外層部24は、内層部23を挟むようにして、第1の主面11側および第2の主面12側にそれぞれ存在する。

【0038】

(3)内層ダミー導体

内層ダミー導体は、内層部23に配置されるもので、図5に示した複数の第1の内層ダミー導体5および図4に示した複数の第2の内層ダミー導体6を備える。

【0039】

(3)−1.第1の内層ダミー導体

第1の内層ダミー導体5は、この実施形態では、図5に示すように、第2の内部電極4と同一面上に配置されている。第1の内層ダミー導体5は、第1の外部電極9に接続される。

【0040】

(3)−2.第2の内層ダミー導体

第2の内層ダミー導体6は、この実施形態では、図4に示すように、第1の内部電極3と同一面上に配置されている。第2の内層ダミー導体6は、第2の外部電極10に接続される。

【0041】

(3)−3.その他

内層ダミー導体5および6は、第1および第2の外部電極9および10の下地層を構成するめっき膜の析出ポイントとして機能し、通電効率を向上させる。また、セラミック素体2の強度向上にも寄与する。

【0042】

内層ダミー導体5および6の材質および厚みの好ましい条件は、内部電極3および4の場合と同様である。内層ダミー導体5および6は、内部電極3および4と同じ材質および同じ厚みをもって構成されることが望ましい。

【0043】

なお、内層ダミー導体5および6は形成されていなくてもよい。

【0044】

(4)外層ダミー導体

図2および図3に示すように、外層ダミー導体7は外層部24に配置される。

【0045】

外層ダミー導体7は、セラミック素体2の外表面の少なくとも2箇所に引き出されることが好ましい。この実施形態において、外層ダミー導体7は、図6に示すように、長方形状に形成され、セラミック素体2の外表面の2箇所、すなわち、第1の側面13および第2の側面14にそれぞれ引き出される。言い換えると、外層ダミー導体7は、第1の側面13から第2の側面14に至るようにして配置される。

【0046】

外層ダミー導体7は、第1の外部電極9の下地層を構成するめっき膜の析出ポイントとして機能するものであるが、上述のように、2箇所に引き出されるため、めっき時において、スチールボールなどのメディアが外層ダミー導体7の一方の露出部に接触すれば、他方の露出部にも通電する。つまり、外層ダミー導体7が2箇所以上の露出部を有すると、メディアと接触する確率が高くなり、通電効率が高まる。これにより、後述する第1の外部電極9の下地層となるめっき膜を形成するために必要なめっき時間が短縮される。

【0047】

外層ダミー導体7は、図2および図3に示すように、セラミック層17の積層方向に沿って連続して複数枚積層されている。外層ダミー導体7は、各外層部24においてそれぞれ10〜100枚配置されていることが好ましい。

【0048】

外層ダミー導体7は、セラミック素体2を高さ方向に沿って投影した場合に、第1の引出し部20と重なるように配置される。そのため、外層ダミー導体7は、セラミック素体2の外表面において、第1の引出し部20の露出部と協働して列状の露出部グループを形成する。この実施形態においては、第1および第2の側面13および14において、それぞれ露出部グループが形成されている。

【0049】

図7を参照して、外層部24における外層ダミー導体7同士の間隔をd1、内層部23における第1および第2の内部電極3および4の間隔をd2、としたとき、

1.7d2≦d1

を満足するようにされる。

【0050】

このように、外層部24における外層ダミー導体7の密度を低減することにより、焼成前のプレス時において外層ダミー導体7による内部電極3および4の押圧が緩和され、それによって、局所的に内部電極間距離が短くなることを防止することができ、たとえばBDVの低下といった積層セラミック電子部品の信頼性の低下を効果的に抑制することができる。

【0051】

後述する実験例からわかるように、d1が1.7d2より小さい場合、信頼性が低下するおそれがある。

【0052】

この実施形態のように、第1の引出し部が、長さ方向において、1対の側面13および14のうち少なくとも一方の中央にかかるように引き出されている場合、第1の引出し部20の付け根の部分での沈み込みが大きくなるため、このような局面において、上述の効果が一層期待できる。

【0053】

なお、信頼性の低下抑制の点からは、上記d1は、長い方が好ましいと言えるが、d1がより長くなるほど、第1の外部電極9の下地層となるめっき膜の成長をより阻害する傾向が現れる。すなわち、外層ダミー導体7の露出部を核として成長すべきめっき膜が高さ方向につながりにくくなるおそれがある。この点から、d1≦6μmを満足することが好ましい。

【0054】

外層ダミー導体7は、内部電極3および4と同じ材料からなることが好ましく、外層ダミー導体7を構成する導電材料としては、前述したように、たとえば、Ni、Cu、Ag、Pd、Ag−Pd合金、Auなどを用いることができる。

【0055】

外層ダミー導体7の厚みは0.3〜2.0μmであることが好ましい。

【0056】

(5)外部電極

(5)−1.第1の外部電極

第1の外部電極9は、図3によく示されているように、セラミック素体2の第1および第2の側面13および14上にそれぞれ配置されている。この実施形態では、第1の外部電極9は、第1および第2の主面11および12にまで回り込んでいる。

【0057】

第1の外部電極9は、第1の内部電極3と電気的に接続される。第1の外部電極9は、図3ないし図6に示すように、下地層25およびその上に必要に応じて形成される上層26を含む。

【0058】

第1の外部電極9の下地層25は、めっき膜により構成される。第1の外部電極9の下地層25を構成するめっき膜は、第1の内部電極3の第1の引出し部20の露出部および第1の内層ダミー導体5の露出部を直接覆うとともに、外層ダミー導体7の露出部を直接覆う。下地層25となるめっき膜を構成する金属としては、たとえば、Cu、Ni、Ag、Pd、Ag−Pd合金、Au、Sn、Pb、Pd、Bi、Znなどを用いることができる。めっき膜は、ガラス成分を含まないことが好ましい。また、めっき膜の単位体積あたりの金属割合は99体積%以上であることが好ましい。めっき膜の厚みは、最も厚い部分において、1〜15μmであることが好ましい。第1の内層ダミー導体5および外層ダミー導体7は、下地層25となるめっき膜の析出および成長を促進するように作用する。

【0059】

第1の外部電極9において上層26が形成される場合、上層26は、たとえば、めっき膜により構成される。上層26となるめっき膜を構成する金属としては、たとえば、Cu、Ni、Ag、Pd、Ag−Pd合金、Au、Sn、Pb、Pd、Bi、Znなどを用いることができる。上層26のめっき膜は、複数層から構成されてもよい。上層26のめっき膜の厚みは、1層あたり、1〜10μmであることが好ましい。

【0060】

第1の外部電極9において上層26が形成される場合、好ましくは、下地層25がNiめっき膜から構成され、上層26がSnめっき膜から構成される。あるいは、上層26が複数層から構成される場合、好ましくは、Niめっき層およびその上のSnめっき層の2層構造とされる。

【0061】

(5)−2.第2の外部電極

第2の外部電極10は、第1の外部電極9とは異なる電位に接続されるもので、セラミック素体2の第1および第2の端面15および16上にそれぞれ配置されている。この実施形態では、第2の外部電極10は、第1および第2の主面11および12ならびに第1および第2の側面13および14にまで回り込んでいる。

【0062】

第2の外部電極10は、第2の内部電極4と電気的に接続されるようにして、第2の引出し部22の露出部を覆う。第2の外部電極10は、図2および図4ないし図6に示すように、第2の内部電極4の第2の引出し部22の露出部と接触する下地層27およびその上に必要に応じて形成される上層28を含む。下地層27は、めっき膜、焼結金属膜、および/または導電性樹脂膜などにより構成され得る。

【0063】

下地層27を構成するものとしてめっき膜が選択される場合、めっき膜を構成する金属としては、たとえば、Cu、Ni、Ag、Pd、Ag−Pd合金、Au、Sn、Pb、Pd、Bi、Znなどを用いることができる。めっき膜は、ガラス成分を含まないことが好ましい。また、下地層27の厚みは、最も厚い部分で、1〜20μmであることが好ましい。前述した第2の内層ダミー導体6は、下地層27となるめっき膜の析出および成長を促進するように作用する。

【0064】

下地層27を構成するものとして焼結金属膜が選択される場合、焼結金属膜を構成する金属としては、たとえば、Cu、Ni、Ag、Pd、Ag−Pd合金、Auなどを用いることができる。焼結金属膜には、ガラス成分が含まれ得る。また、焼結金属膜は、セラミック素体2ならびに内部電極3および4と同時焼成されたものでもよく、焼成後のセラミック素体2に導電性ペーストを塗布して焼き付けられたものでもよい。

【0065】

下地層27を構成するものとして導電性樹脂膜が選択される場合、熱硬化性樹脂および金属フィラーを混合したものを用いて導電性樹脂膜を形成することができる。

【0066】

上述した焼結金属膜または導電性樹脂膜が選択される場合、下地層27の厚みは、最も厚い部分で、10〜50μmであることが好ましい。

【0067】

図示の実施形態では、下地層27は、第2の内部電極4および第2の内層ダミー導体6の各露出部と接触するめっき膜29と、このめっき膜29上に形成される焼結金属膜30とから構成される。

【0068】

第2の外部電極10において、上記下地層27上に形成される上層28がさらに形成される場合、上層28は、たとえば、めっき膜により構成される。上層28となるめっき膜を構成する金属としては、たとえば、Cu、Ni、Ag、Pd、Ag−Pd合金、Au、Sn、Pb、Pd、Bi、Znなどを用いることができる。上層28のめっき膜は、複数層から構成されてもよい。この場合、好ましくは、Niめっき層およびその上のSnめっき層の2層構造とされる。上層28のめっき膜の厚みは、1層あたり、1〜10μmであることが好ましい。

【0069】

(6)製造方法

積層セラミックコンデンサ1は、たとえば、次のようにして製造される。

【0070】

(6)−1.

セラミック層17となるべきセラミックグリーンシート、内部電極用導電性ペースト、および外部電極用導電性ペーストを準備する。内部電極用導電性ペーストは、内層ダミー導体用導電性ペーストおよび外層ダミー導体用導電性ペーストを兼ねる。セラミックグリーンシートならびに内部電極用および外部電極用の各導電性ペーストには、バインダおよび溶剤が含まれるが、公知の有機バインダや有機溶剤を用いることができる。

【0071】

(6)−2.

セラミックグリーンシート上に、たとえばスクリーン印刷などにより所定のパターンで導電性ペーストを印刷し、内部電極パターン、内層ダミー導体パターンおよび外層ダミー導体パターンを形成する。

【0072】

(6)−3.

内部電極パターンが印刷されていない外層用セラミックグリーンシート、外層ダミー導体パターンが印刷されたセラミックグリーンシート、内部電極パターンおよび内層ダミー導体パターンが印刷されたセラミックグリーンシートを、それぞれ所定枚数かつ所定順序で積層し、マザー積層体を作製する。

【0073】

ここで、外層部において、外層ダミー導体パターンが印刷されていないセラミックグリーンシートの積層枚数を調整することにより、前述の距離d1を調整することができる。あるいは、外層用セラミックグリーンシートの厚みを調整することにより、距離d1を調整してもよい。

【0074】

なお、内層部において、内部電極パターンおよび内層ダミー導体パターンが印刷されていないセラミックグリーンシートの積層枚数を調整することにより、前述の距離d2を調整することも、あるいは、内層用セラミックグリーンシートの厚みを調整することにより、距離d2を調整することも可能である。

【0075】

(6)−4.

マザー積層体を積層方向にプレスする。

【0076】

(6)−5.

マザー積層体を所定のサイズにカットし、生のセラミック素体を切り出す。

【0077】

(6)−6.

生のセラミック素体を焼成する。これによって、図示したセラミック素体2が得られる。焼成温度は、セラミックや内部電極の材料にもよるが、900〜1300℃であることが好ましい。

【0078】

この後、必要に応じて、バレル研磨を行なう。これにより、セラミック素体2のコーナー部や稜部に丸みが付けられる。

【0079】

(6)−7.

研磨後のセラミック素体2に対して、めっき処理を行なう。

【0080】

これによって、第1の外部電極9の、めっき膜からなる下地層25が形成される。このとき、図3に示すように、第1の内部電極3ばかりでなく、第1の内層ダミー導体5および外層ダミー導体7が、側面13および14上に露出していて、これらの露出部分を起点にめっきが析出するため、第1の外部電極9の下地層25を能率的に形成することができる。

【0081】

めっき処理には、回転バレル法による電解めっきを適用することが好ましい。めっき方法は回転バレルめっきであることが好ましい。めっき処理には、スチールボールなどの導電性メディアが用いられる。

【0082】

外層ダミー導体7は、2つの露出部を有しているため、めっき工程において、導電性メディアが一方の露出部に接触すれば、他方の露出部にも通電する。つまり、メディアと接触する確率が高くなり、通電効率が高まる。これにより、下地層25の形成のためのめっき時間が短縮される。

【0083】

このめっき処理において、同時に、第2の内部電極4および第2の内層ダミー導体6の各露出部をめっき析出の起点として、第2の外部電極10の下地層27におけるめっき膜29も形成され得る。

【0084】

めっき処理後、600〜900℃の温度で熱処理を行なうことが好ましい。これにより、セラミック素体2に対するめっき膜の固着力が向上する。

【0085】

(6)−8.

第2の外部電極10の下地層27における焼結金属膜30が、導電性ペーストを塗布し、焼き付けることによって形成される。焼き付け温度は、700〜900℃であることが好ましい。

【0086】

(6)−9.

第1の外部電極9の上層26および第2の外部電極10の上層28を形成するため、めっき処理を行なう。

【0087】

以上のようにして、積層セラミックコンデンサ1が完成される。

【0088】

[第2の実施形態]

この発明の第2の実施形態が図8に示されている。図8は、図3に対応する図である。図8において、図3に示す要素に相当する要素には同様の参照符号を付し、重複する説明は省略する。

【0089】

第2の実施形態による積層セラミックコンデンサ1aでは、外層ダミー導体7aが、セラミック素体2を幅方向に貫通して形成されておらず、幅方向に沿って分離して形成されている。

【0090】

[第3の実施形態]

この発明の第3の実施形態が図9および図10に示されている。図9は、図1に対応する図であり、図10は、図3に対応する図である。図9および図10において、図1および図3に示す要素に相当する要素には同様の参照符号を付し、重複する説明は省略する。

【0091】

第3の実施形態による積層セラミックコンデンサ1bでは、第1の外部電極9bが、下地層25および上層26を含めて、セラミック素体2の第1および第2の側面13および14ならびに第1および第2の主面11および12を周回するように配置されていることを特徴としている。

【0092】

この実施形態では、主面11および12を与えるセラミック層17を前述した焼成後の研磨工程で削り取り、主面11および12の各々の少なくとも一部に外層ダミー導体7を露出させておくことが好ましい。これにより、主面11および12上にもめっきの析出ポイントが追加されるため、第1の外部電極9bの下地層25となるめっき膜を周回した状態で形成することが容易になる。

【0093】

なお、外層ダミー導体7は、主面11および12上に、その全面が露出している必要はなく、不連続状に(たとえば、まだら状に)分布して露出していてもよい。ただし、外層ダミー導体7の主面11および12における露出部分は、第1の側面13から第2の側面14にかけて一様に分布していることが好ましく、また、第1の側面13から第2の側面14にかけて途切れることなく露出していることが望ましい。このように、第1の側面13から第2の側面14にかけてわずかでも外層ダミー導体7が連続的に露出している部分がある場合、通電面積が主面11および12における第1の側面13側から第2の側面14側にまで及ぶことになるため、最も通電効率が高くなる。

【0094】

この実施形態によれば、第1の外部電極9bの下地層25を形成するためのめっき工程において生じるめっき成長の過程で、めっき膜がセラミック素体2を周回するようにつながることにより、めっきの析出ポイントとなり得る電極面積が大きくなるので、その時点から通電効率が向上し、単位時間で生成できる膜厚が厚くなる。つまり、この実施形態によれば、第1の外部電極9bの下地層25において、所定の膜厚を形成する時間が短くなり、コスト削減となる。

【0095】

前述した第1の実施形態では、セラミック素体2の主面11および12に第1の外部電極9の先端部分が存在する。当該積層セラミックコンデンサ1を実装する基板のたわみなどにより、第1の外部電極9の先端部分に応力が加わると、ここを起点に下地層25が剥がれる可能性が高い。しかし、この実施形態では、第1の外部電極9bがエンドレスであり、先端部分がなくなるため、剥がれの問題が起こりにくくなる。

【0096】

また、第1の実施形態では、主面11および12上に位置する第1の外部電極9の下地層25の先端部分が、上層26をめっきにより形成する際に用いられるめっき液の浸入の入り口となって、信頼性が低下する可能性がある。しかし、この実施形態では、第1の外部電極9bの下地層25には、先端部分が存在しないため、信頼性低下の問題も起こりにくくなる。

【0097】

また、第1の外部電極9bはセラミック素体2を周回するめっき膜から構成されるので、この第1の外部電極9bを、セラミック素体2の外表面に沿う平滑なものとすることができる。このため、積層セラミックコンデンサ1bは、その実装時に転がりにくく、姿勢を安定なものとすることができる。

【0098】

[第4の実施形態]

この発明の第4の実施形態が図11ないし図12に示されている。図11は、図2に対応する図であり、図12は、図6に対応する図である。図11および図12において、図2および図6に示す要素に相当する要素には同様の参照符号を付し、重複する説明は省略する。

【0099】

第4の実施形態による積層セラミックコンデンサ1cでは、外層ダミー導体7と同一面上に第2の外層ダミー導体8が配置されていることを特徴としている。

【0100】

また、第2の外部電極10cの下地層27全体がめっき膜により構成されている。これによって、第1および第2の外部電極9および10cの下地層25および27を同時に形成することができる。

【0101】

第2の外層ダミー導体8は、第2の外部電極10cの下地層27を構成するめっき膜の析出ポイントとして機能し、通電効率を向上させる。

【0102】

[その他の実施形態]

ダミー導体、特に外層ダミー導体は電気的特性の発現に寄与するものであってもよい。さらに、ダミー導体は、いかなる形状であってもよく、たとえば、外層ダミー導体は内部電極と同じ形状であってもよい。

【0103】

[実験例]

第1の実施形態に基づいて、次のような積層セラミックコンデンサを作製した。

【0104】

(1)セラミック素体の長さ方向寸法×幅方向寸法×高さ方向寸法:1.6mm×0.8mm×0.8mm

(2)第1の外部電極

下地層:厚み10μmのCuめっき膜

上層:厚み3μmのNiめっき膜およびその上の厚み3μmのSnめっき膜

(3)第2の外部電極

下地層:厚み10μmのCuめっき膜およびその上の厚み15μmのCu焼結金属膜

上層:厚み3μmのNiめっき膜およびその上の厚み3μmのSnめっき膜

(4)内部電極

内部電極間距離d2:表1のとおり

内部電極の厚み:0.56μm

内部電極の枚数:345枚

(5)内層ダミー導体

内部電極と同じ

(6)外層ダミー導体

外層ダミー導体間距離d1:表1のとおり

外層ダミー導体の厚み:0.56μm

外層ダミー導体の枚数:上下の外層部で各56枚ずつ

表1に示すように、d1およびd2を変えた各試料につき、BDVおよびめっき付き不良を評価した。

【0105】

なお、d1およびd2を測定するにあたって、各試料を3個ずつ準備し、セラミック素体を幅方向寸法の1/2程度まで研磨し、研磨面に、長さ方向寸法および厚み方向寸法によって規定される断面を露出させた。

【0106】

そして、d1については、上記断面において、長さ方向寸法の1/2程度に位置する第1の主面側の外層部にある外層ダミー導体間距離すべてを、電子顕微鏡により測定し、試料3個での平均値を求めた。

【0107】

他方、d2については、上記断面において、長さ方向寸法の1/2程度に位置する内層部の最上層に位置する15層分の内部電極間距離を、電子顕微鏡により測定し、試料3個での平均値を求めた。

【0108】

BDVについては、各試料を10個ずつ準備し、直流電圧破壊試験機により、昇圧速度100V/秒の条件で測定した。

【0109】

めっき付き不良については、第1の外部電極における下地層となるCuめっき膜を形成した段階での試料を1500個ずつ準備し、外層部と内層部との間でのCuめっき膜の状態を光学顕微鏡により確認し、めっき膜が切れているものをめっき付き不良とし、1500個の試料中において、めっき付き不良となった試料数を求めた。

【0110】

なお、上記の第1の外部電極における下地層となるCuめっき膜は、次のようにして形成した。まず、pH8.5で、浴温25℃とされた、14g/Lのピロリン酸銅、120g/Lのピロリン酸カリウム、および10g/Lの蓚酸カリウムを含むめっき浴を用いて、回転バレルめっきにより、電流密度0.1A/dm2の条件で、60分間、ストライクCuめっきを行ない、次に、pH8.8で、浴温55℃とされた、上村工業製ピロブライトプロセス用浴を用いて、回転バレルめっきにより、電流密度0.3A/dm2の条件で、60分間、厚付けCuめっきを行なうことによって、Cuめっき膜を形成した。

【0111】

【表1】

【0112】

表1からわかるように、1.7d2≦d1を満足する試料3〜9では、100V以上のBDVを達成した。

【0113】

これらの試料3〜9のうち、特に、d1≦6μmを満足する試料3〜6では、めっき付き性も良好であった。

【0114】

他方、試料1および2では、めっき付き性が良好であったが、1.7d2≦d1を満足しないため、BDVが100V未満となった。

【0115】

なお、表には記載していないが、上記実験例の条件の内部電極間距離d2を3.0μm付近または0.7μm付近のものに変えて同様の実験を行なったところ、上記実験結果と同様の効果が得られることが確認できている。

【産業上の利用可能性】

【0116】

この発明は、以上説明した積層セラミックコンデンサに限らず、他の積層セラミック電子部品にも適用することができる。たとえば、セラミック素体を圧電体セラミックで構成した場合は、圧電部品として機能する積層セラミック電子部品とすることができ、セラミック素体をスピネル状セラミックなどの半導体セラミックで構成した場合は、サーミスタとして機能する積層セラミック電子部品とすることができる。

【符号の説明】

【0117】

1,1a,1b,1c 積層セラミックコンデンサ

2 セラミック素体

3 第1の内部電極

4 第2の内部電極

7,7a 外層ダミー導体

9,9b 第1の外部電極

10,10c 第2の外部電極

11,12 主面

13,14 側面

15,16 端面

17 セラミック層

19 第1の対向部

20 第1の引出し部

21 第2の対向部

22 第2の引出し部

23 内層部

24 外層部

25 第1の外部電極の下地層

26 第1の外部電極の上層

27 第2の外部電極の下地層

28 第2の外部電極の上層

【特許請求の範囲】

【請求項1】

複数のセラミック層が積層されてなるもので、外表面として、互いに対向する1対の主面と、互いに対向する1対の側面と、互いに対向する1対の端面と、を有し、前記1対の端面を結ぶ長さ方向に沿った前記側面の寸法が、前記1対の側面を結ぶ幅方向に沿った前記端面の寸法よりも長い、セラミック素体と、

前記セラミック素体の内部に配置され、長辺および短辺を有する長方形状の第1の対向部と、前記第1の対向部の前記長辺から前記セラミック素体の前記側面に引き出された第1の引出し部と、を有する第1の内部電極と、

前記セラミック素体の内部に配置され、前記第1の対向部と対向する第2の対向部と、前記第2の対向部から前記セラミック素体の前記外表面に引き出された第2の引出し部と、を有する第2の内部電極と、

前記セラミック素体の前記側面上に配置され、前記第1の引出し部の露出部を直接覆うめっき膜を有する、第1の外部電極と、

前記セラミック素体の前記外表面上に配置され、前記第2の引出し部の露出部と電気的に接続され、前記第1の外部電極とは異なる電位に接続される、第2の外部電極と、

を備え、

前記1対の主面を結ぶ高さ方向に沿って、前記第1の内部電極および前記第2の内部電極が存在する領域を内層部と定義し、

前記高さ方向に沿って、前記第1の内部電極および前記第2の内部電極がいずれも存在しない領域を外層部と定義したとき、

前記外層部には、前記セラミック素体を前記高さ方向に沿って投影した場合に前記第1の引出し部と重なるようにして前記側面に引き出され、前記第1の外部電極の前記めっき膜と接続された外層ダミー導体が前記高さ方向に沿って複数配置され、

前記外層部における前記外層ダミー導体同士の間隔をd1、前記内層部における前記第1および第2の内部電極の間隔をd2、としたとき、

1.7d2≦d1

を満足する、積層セラミック電子部品。

【請求項2】

さらに、d1≦6μmを満足する、請求項1に記載の積層セラミック電子部品。

【請求項3】

前記第1の引出し部は、前記長さ方向において、前記1対の側面のうち少なくとも一方の中央にかかるように引き出されている、請求項1または2に記載の積層セラミック電子部品。

【請求項1】

複数のセラミック層が積層されてなるもので、外表面として、互いに対向する1対の主面と、互いに対向する1対の側面と、互いに対向する1対の端面と、を有し、前記1対の端面を結ぶ長さ方向に沿った前記側面の寸法が、前記1対の側面を結ぶ幅方向に沿った前記端面の寸法よりも長い、セラミック素体と、

前記セラミック素体の内部に配置され、長辺および短辺を有する長方形状の第1の対向部と、前記第1の対向部の前記長辺から前記セラミック素体の前記側面に引き出された第1の引出し部と、を有する第1の内部電極と、

前記セラミック素体の内部に配置され、前記第1の対向部と対向する第2の対向部と、前記第2の対向部から前記セラミック素体の前記外表面に引き出された第2の引出し部と、を有する第2の内部電極と、

前記セラミック素体の前記側面上に配置され、前記第1の引出し部の露出部を直接覆うめっき膜を有する、第1の外部電極と、

前記セラミック素体の前記外表面上に配置され、前記第2の引出し部の露出部と電気的に接続され、前記第1の外部電極とは異なる電位に接続される、第2の外部電極と、

を備え、

前記1対の主面を結ぶ高さ方向に沿って、前記第1の内部電極および前記第2の内部電極が存在する領域を内層部と定義し、

前記高さ方向に沿って、前記第1の内部電極および前記第2の内部電極がいずれも存在しない領域を外層部と定義したとき、

前記外層部には、前記セラミック素体を前記高さ方向に沿って投影した場合に前記第1の引出し部と重なるようにして前記側面に引き出され、前記第1の外部電極の前記めっき膜と接続された外層ダミー導体が前記高さ方向に沿って複数配置され、

前記外層部における前記外層ダミー導体同士の間隔をd1、前記内層部における前記第1および第2の内部電極の間隔をd2、としたとき、

1.7d2≦d1

を満足する、積層セラミック電子部品。

【請求項2】

さらに、d1≦6μmを満足する、請求項1に記載の積層セラミック電子部品。

【請求項3】

前記第1の引出し部は、前記長さ方向において、前記1対の側面のうち少なくとも一方の中央にかかるように引き出されている、請求項1または2に記載の積層セラミック電子部品。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【公開番号】特開2013−51392(P2013−51392A)

【公開日】平成25年3月14日(2013.3.14)

【国際特許分類】

【出願番号】特願2012−79714(P2012−79714)

【出願日】平成24年3月30日(2012.3.30)

【出願人】(000006231)株式会社村田製作所 (3,635)

【Fターム(参考)】

【公開日】平成25年3月14日(2013.3.14)

【国際特許分類】

【出願日】平成24年3月30日(2012.3.30)

【出願人】(000006231)株式会社村田製作所 (3,635)

【Fターム(参考)】

[ Back to top ]