積層型セラミック電子部品およびその製造方法

【課題】積層セラミックコンデンサの外部電極を、部品本体の所定の面上に直接めっきを施すことによって形成したとき、外部電極となるめっき膜の部品本体に対する固着力が低いことがある。

【解決手段】外部電極16として、各内部電極5の露出端を起点として析出しためっき析出物を部品本体2の少なくとも端面12上に成長させてなるもので、P含有率が9重量%以上のNi−Pめっき膜からなる第1のめっき層18をまず形成する。次いで、第1のめっき層18上に、Pを実質的に含まないNiめっき膜からなる第2のめっき層19を形成する。好ましくは、第1のめっき層18は無電解めっきにより形成され、第2のめっき層19は電解めっきにより形成される。

【解決手段】外部電極16として、各内部電極5の露出端を起点として析出しためっき析出物を部品本体2の少なくとも端面12上に成長させてなるもので、P含有率が9重量%以上のNi−Pめっき膜からなる第1のめっき層18をまず形成する。次いで、第1のめっき層18上に、Pを実質的に含まないNiめっき膜からなる第2のめっき層19を形成する。好ましくは、第1のめっき層18は無電解めっきにより形成され、第2のめっき層19は電解めっきにより形成される。

【発明の詳細な説明】

【技術分野】

【0001】

この発明は、積層型セラミック電子部品およびその製造方法に関するもので、特に、外部電極において、複数の内部電極と電気的に接続されるようにして直接めっきにより形成されためっき膜を備える、積層型セラミック電子部品およびその製造方法に関するものである。

【背景技術】

【0002】

図5に示すように、積層セラミックコンデンサに代表される積層型セラミック電子部品101は、一般に、たとえば誘電体セラミックからなる積層された複数のセラミック層102と、セラミック層102間の界面に沿って形成された複数の層状の内部電極103および104とを含む、積層構造の部品本体105を備えている。部品本体105の一方および他方端面106および107には、それぞれ、複数の内部電極103および複数の内部電極104の各端部が露出している。そして、これら内部電極103の各露出端および内部電極104の各露出端を、それぞれ、互いに電気的に接続するように、外部電極108および109が、部品本体105の一方および他方端面106および107上に形成されている。

【0003】

外部電極108および109の形成にあたっては、一般に、金属成分とガラス成分とを含む金属ペーストを部品本体105の端面106および107上に塗布し、次いで焼き付けることにより、ペースト電極層110がまず形成される。次に、ペースト電極層110上に、たとえばNiを主成分とする第1のめっき層111が形成され、さらにその上に、たとえばSnまたはAuを主成分とする第2のめっき層112が形成される。すなわち、外部電極108および109の各々は、ペースト電極層110、第1のめっき層111および第2のめっき層112の3層構造より構成される。

【0004】

外部電極108および109に対しては、積層型セラミック電子部品101がはんだを用いて基板に実装される際に、はんだとのぬれ性が良好であることが求められる。同時に、外部電極108に対しては、互いに電気的に絶縁された状態にある複数の内部電極103を互いに電気的に接続し、かつ、外部電極109に対しては、互いに電気的に絶縁された状態にある複数の内部電極104を互いに電気的に接続する役割が求められる。はんだぬれ性の確保の役割は、上述した第2のめっき層112が果たしており、内部電極103および104相互の電気的接続の役割は、ペースト電極層110が果たしている。第1のめっき層111は、はんだ接合時のはんだ喰われを防止する役割を果たしている。

【0005】

しかし、ペースト電極層110は、その厚みが数十μm〜数百μmと大きい。したがって、この積層型セラミック電子部品101の寸法を一定の規格値に収めるためには、このペースト電極層110の体積を確保する必要が生じる分、不所望にも、静電容量確保のための実効体積を減少させる必要が生じる。一方、めっき層111および112はその厚みが数μm程度であるため、仮に第1のめっき層111および第2のめっき層112のみで外部電極108および109を構成できれば、静電容量確保のための実効体積をより多く確保することができる。

【0006】

たとえば、特開昭63−169014号公報(特許文献1)には、部品本体の、内部電極が露出した側壁面の全面に対し、側壁面に露出した内部電極が短絡されるように、無電解Niめっきによって導電性金属層を析出させる、外部電極の形成方法が開示されている。

【0007】

しかしながら、部品本体の所定の面上への直接のめっきにより形成されためっき膜は、前述したペースト電極層の場合のようなガラス等を介さないため、めっき膜と部品本体との間での固着力が問題である。ここで、固着力は、部品本体におけるセラミック部分とめっき膜との間での固着力のみならず、内部電極露出端とめっき膜との間での固着力も重要である。

【0008】

また、一方では、めっき膜の皮膜強度(亀裂の入りにくさ)も重要である。そして、上述しためっき膜の固着力とこの皮膜強度とは、これらを両立させることが比較的難しい。

【0009】

より具体的に説明すると、積層型セラミック電子部品をはんだ実装すると、外部電極に応力が加わる。このとき、めっき膜がやわらかいと、めっき膜に亀裂が入りにくいが、上述の応力によってめっき膜が剥離して部品本体との間に隙間が生じやすく、そのため、隙間に水分が浸入することとなり、絶縁抵抗が劣化して、積層型セラミック電子部品の信頼性が低下するおそれがある。他方、めっき膜を硬くすると、固着力が向上するが、めっき膜が脆くなり、めっき膜に亀裂が入って、積層型セラミック電子部品の信頼性が低下する。

【先行技術文献】

【特許文献】

【0010】

【特許文献1】特開昭63−169014号公報

【発明の概要】

【発明が解決しようとする課題】

【0011】

この発明の目的は、上記のような問題点を解決し得る積層型セラミック電子部品およびその製造方法を提供しようとすることである。

【課題を解決するための手段】

【0012】

この発明は、積層された複数のセラミック層とセラミック層間の特定の界面に沿って形成された複数の内部電極とを備え、各内部電極が所定の面に露出する露出端を有している、部品本体と、各内部電極の露出端に電気的に接続されるように、部品本体の上記所定の面上に形成された、外部電極とを備える、積層型セラミック電子部品にまず向けられるものであって、上述した技術的課題を解決するため、上記外部電極は、上記所定の面上に直接形成されたもので、P含有率が9重量%以上のNi−Pめっき膜からなる第1のめっき層と、第1のめっき層上に形成されたもので、Pを実質的に含まないNiめっき膜からなる第2のめっき層とを含むことを特徴としている。

【0013】

この発明に係る積層型セラミック電子部品において、好ましくは、第1のめっき層は無電解めっきにより形成されたものであり、第2のめっき層は電解めっきにより形成されたものである。

【0014】

また、第1のめっき層を構成するNi−Pめっき膜は、非晶質であることが好ましい。

【0015】

この発明は、また、積層型セラミック電子部品の製造方法にも向けられる。この発明に係る積層型セラミック電子部品の製造方法は、積層された複数のセラミック層とセラミック層間の特定の界面に沿って形成された複数の内部電極とを備え、各内部電極が所定の面に露出する露出端を有している、部品本体を用意する工程と、各内部電極の露出端に電気的に接続されるように、部品本体の上記所定の面上に外部電極を形成する工程とを備えるもので、前述した技術的課題を解決するため、次のような構成を備えることを特徴としている。

【0016】

すなわち、外部電極を形成する工程は、無電解めっきを実施することにより、各内部電極の露出端を起点としてめっき析出物を析出させるとともに、当該めっき析出物を所定の面上に成長させることによって、P含有率が9重量%以上のNi−Pめっき膜からなる第1のめっき層を形成する工程と、電解めっきを実施することにより、第1のめっき層上に、Pを実質的に含まないNiめっき膜からなる第2のめっき層を形成する工程とを含むことを特徴としている。

【発明の効果】

【0017】

この発明に係る積層型セラミック電子部品によれば、まず、外部電極における第1のめっき層を、P含有率が9重量%以上のNi−Pめっき膜から構成しているので、固着力を向上させることができる。すなわち、P含有率を上げると、めっき膜の硬度が上がる。したがって、第1のめっき層の硬度を上げることができる。このように第1のめっき層の硬度が上がると、セラミックの微細な凹凸に追随したとき、皮膜応力が小さくなることから、アンカー効果が高くなる。よって、内部電極露出端に対する第1のめっき層の接合強度が全体的に向上するとともに、第1のめっき層と内部電極露出端の周縁部のセラミック部分との界面での剥離も生じにくくなるため、実装時の耐湿信頼性が向上する。

【0018】

また、P含有率が高いと、めっき膜の耐腐食性が向上する。したがって、第1のめっき層の耐腐食性が向上し、この点においても、耐湿信頼性を向上させることができる。

【0019】

第1のめっき層を構成するNi−Pめっき膜は、前述したように、非晶質であることが好ましい。非晶質であれば、前述したようなセラミックの凹凸に対する追随性が良好である。よって、前述のアンカー効果がより高くなり、固着力をより高めることができるとともに、第1のめっき層と内部電極との間の隙間を実質的になくすことができ、たとえば水蒸気に対するシール性を良好なものとし、耐湿信頼性をより向上させることができる。

【0020】

他方、第1のめっき層は、前述したように、硬度が高いので、割れやすいという欠点がある。すなわち、実装時および実装後に加わる応力や熱衝撃によって、第1のめっき層にクラックが入り、耐湿信頼性が低下することがある。この欠点を補うのが、Pを実質的に含まないNiめっき膜からなる第2のめっき層である。Pを含まないNiめっき膜は、比較的柔軟である。そのため、第1のめっき層を第2のめっき層によって保護することによって、第1のめっき層が割れにくくなり、第1のめっき層による耐湿信頼性を良好に維持することができる。

【0021】

以上のようにして、外部電極において、めっき膜の固着力とめっき膜の皮膜強度(亀裂の入りにくさ)とを両立させることができる。

【0022】

この発明に係る積層型セラミック電子部品の製造方法によれば、第1のめっき層を無電解めっきにより形成するので、所望のP含有量のめっき膜を安定して形成することができる。また、第2のめっき層を電解めっきにより形成するので、能率的に第2のめっき層を形成することができる。

【図面の簡単な説明】

【0023】

【図1】この発明の一実施形態による積層型セラミック電子部品としての積層セラミックコンデンサを製造するために用意される、内部電極が印刷された2種類のセラミックグリーンシートを示す平面図である。

【図2】図1に示したセラミックグリーンシートを用いて構成された積層セラミックコンデンサのための部品本体を示す斜視図である。

【図3】図2に示した部品本体にめっきを施すことによって外部電極が形成された積層セラミックコンデンサを示す斜視図である。

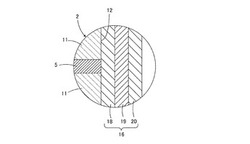

【図4】図3に示した積層セラミックコンデンサに形成された外部電極の断面を拡大して示す図である。

【図5】従来の積層型セラミック電子部品を示す断面図である。

【発明を実施するための形態】

【0024】

この発明の一実施形態による積層型セラミック電子部品としての積層セラミックコンデンサの構造を、図1ないし図4を参照しながら、その製造方法に従って説明する。

【0025】

図3に示した積層セラミックコンデンサ1を製造するため、図2に示した部品本体2が用意される。そして、図2に示した部品本体2を得るため、図1に示した2種類のセラミックグリーンシート3および4が用意される。

【0026】

図1(A)に示したセラミックグリーンシート3上には、第1の内部電極5が形成される。第1の内部電極5は、その主要部をなす容量形成部6と引出し部7とを有している。引出し部7は、セラミックグリーンシート3の一方の短辺とこれに隣接する2つの長辺の各一部にまで届くように延び、ここに露出端を構成する。

【0027】

他方、図1(B)に示したセラミックグリーンシート4上には、第2の内部電極8が形成される。第2の内部電極8は、その主要部をなす容量形成部9と引出し部10とを有している。引出し部10は、上述した第1の内部電極5の引出し部7とは逆側に形成される。引出し部10は、セラミックグリーンシート4の一方の短辺とこれに隣接する2つの長辺の各一部にまで届くように延び、ここに露出端を構成する。

【0028】

上述した内部電極5および8は、たとえばNiを主成分とする導電性ペーストを印刷することによって、セラミックグリーンシート3および4上にそれぞれ形成される。

【0029】

次に、各々複数のセラミックグリーンシート3および4が交互に積層されるとともに、その積層方向の両端部に、内部電極が形成されていない適当数のセラミックグリーンシートが外層部をなすように積層される。これによって、部品本体2の生の状態のものが得られる。

【0030】

なお、上述した積層工程が、複数の積層セラミックコンデンサを取り出すことができるマザー状態のセラミックグリーンシートについて実施され、積層工程の後、カット工程を実施して、個々の積層セラミックコンデンサのための部品本体2の生の状態のものを得るようにしてもよい。

【0031】

次に、焼成工程が実施される。これによって、図2に示すように、焼結した部品本体2が得られる。部品本体2は、積層された複数のセラミック層11を備えている。セラミック層11は、上述のセラミックグリーンシートの焼結によって得られたものである。また、前述した第1および第2の内部電極5および8は焼結した状態となっており、セラミック層11間の特定の界面に沿って位置している。第1の内部電極5の引出し部7は、部品本体2の一方の端面12ならびにそれに隣接する上面14および下面15の各一部において露出端を形成している。第2の内部電極8の引出し部10は、部品本体2の他方の端面13ならびにそれに隣接する上面14および下面15の各一部において露出端を形成している。

【0032】

次に、好ましくは、部品本体2に対して、バレル研磨工程が実施され、それによって、内部電極5および8の露出端をより確実に露出させるようにする。次いで、好ましくは、純水による洗浄工程が実施される。

【0033】

その後、図3に示した積層セラミックコンデンサ1を得るため、第1の内部電極5の露出端に電気的に接続される第1の外部電極16が、部品本体2の一方の端面12上ならびにそれに隣接する上面14および下面15の各一部上に形成され、また、第2の内部電極8の露出端に電気的に接続される第2の外部電極17が、部品本体2の他方の端面13上ならびにそれに隣接する上面14および下面15の各一部上に形成される。

【0034】

上述した第1の外部電極16と第2の外部電極17とは、同時に形成され、かつ互いに同じ断面構造を有しているので、図4に示した第1の外部電極16について、より詳細に説明し、第2の外部電極17については、詳細な説明は省略する。

【0035】

図4を参照して、第1の外部電極16は、各内部電極5の露出端を起点として析出しためっき析出物を、部品本体2の一方の端面12上ならびにそれに隣接する上面14および下面15(図2参照)の各一部上に成長させてなるもので、P含有率が9重量%以上のNi−Pめっき膜からなる第1のめっき層18と、第1のめっき層18上に形成されるもので、Pを実質的に含まないNiめっき膜からなる第2のめっき層19とを少なくとも備え、好ましくは、第2のめっき層19上に形成される第3のめっき層20をさらに備える。第3のめっき層20は、外部電極16のはんだぬれ性を向上させるためのものであり、たとえばSnめっき膜から構成される。

【0036】

上述した第1のめっき層18は、好ましくは、無電解めっきによって形成される。そのため、無電解めっき工程の前処理として、好ましくは、Pd触媒を付与する工程および純水による洗浄工程が実施され、その後、無電解Ni−Pめっきが実施され、P含有率が9重量%以上のNi−Pめっき膜からなる第1のめっき層18が形成される。ここで、第1のめっき層18を構成するNi−Pめっき膜は、隣り合う内部電極5の各露出端におけるめっき析出物を物理的に互いに接続した状態としながら、均質で緻密な膜を構成する。

【0037】

なお、上述のPd触媒を付与する工程において、内部電極5の露出端のNiがPdに置換され、無電解Ni−Pめっきの還元剤のための触媒能が向上するが、Ni自体に触媒性があるため、Pd触媒を付与する工程を省略することも可能である。

【0038】

上述のように、第1のめっき層18を無電解めっきにより形成すると、所望のP含有量のめっき膜を安定して形成することができる。しかし、このような利点を特に望まないならば、第1のめっき層18を電解めっきによって形成してもよい。

【0039】

上述の無電解Ni−Pめっき工程の後、純水による洗浄工程が実施される。

【0040】

その後、熱処理工程が実施されてもよい。熱処理温度としては、たとえば600℃以上、好ましくは800℃以上の温度が採用される。この熱処理によって、内部電極5と第1のめっき層18との間で相互拡散が生じる。そして、この相互拡散部分において、金属の体積膨張が起こるため、セラミック層11と内部電極5および第1のめっき層18の各々との界面に存在し得る隙間を有利に埋めることができ、その結果、部品本体2の内部への水分の浸入を防止する効果が奏される。

【0041】

次に、Pを実質的に含まないNiめっき膜からなる第2のめっき層19が形成される。第2のめっき層19は、好ましくは、電解めっきによって形成される。第2のめっき層19を電解めっきにより形成すると、能率的に第2のめっき層19を形成することができる。しかし、このような利点を特に望まないならば、第2のめっき層19を無電解めっきによって形成してもよい。

【0042】

上述の電解Niめっき工程の後、純水による洗浄工程が実施される。

【0043】

次に、たとえばSnめっき膜からなる第3のめっき層20が形成される。第3のめっき層20は、好ましくは、電解めっきによって形成される。

【0044】

上述の電解Snめっき工程の後、純水による洗浄工程が実施され、次いで、乾燥工程が実施される。

【0045】

このようにして、図3に示した積層セラミックコンデンサ1が完成される。

【0046】

以上説明した積層セラミックコンデンサ1では、セラミック層11が誘電体セラミックから構成される。しかし、この発明が向けられる積層型セラミック電子部品は、積層セラミックコンデンサに限らず、たとえば、インダクタ、サーミスタ、圧電部品などを構成するものであってもよい。したがって、積層型セラミック電子部品の機能に応じて、セラミック層は、誘電体セラミックの他、磁性体セラミック、半導体セラミック、圧電体セラミックなどから構成されてもよい。

【0047】

また、図示した積層セラミックコンデンサ1は、2個の外部電極16および17を備える2端子型のものであるが、この発明は3端子以上の多端子型の積層型セラミック電子部品にも適用することができる。

【0048】

以下に、この発明の効果を確認するために実施した実験例について説明する。この実験例では、この発明の範囲内の実施例としての試料1および2に係る各積層セラミックコンデンサ、ならびにこの発明の範囲外の比較例としての試料3〜5に係る各積層セラミックコンデンサを作製した。

【0049】

[試料1]

平面寸法が1.0mm×0.5mmの積層セラミックコンデンサ用部品本体であって、セラミック層がチタン酸バリウム系誘電体セラミックからなり、内部電極がNiを主成分とするものを用意した。この部品本体において、内部電極間のセラミック層の各厚みは1μmであり、各内部電極の厚みは1μmであり、内部電極が配置されない各外層部の厚みは50μmであった。また、後述するめっき処理の前処理として、部品本体にはバレル研磨を施し、内部電極の露出端を確実に露出させた状態としておき、次いで、純水による洗浄工程を実施しておいた。

【0050】

次に、部品本体に対して、Pd触媒付与工程を実施した。Pd触媒付与工程では、Pd濃度:100ppm、pH:2.5、温度:25℃の塩化パラジウム水溶液を用意し、そこに部品本体を3分間浸漬した。浸漬後、部品本体を塩化パラジウム水溶液から取り出し、純水による洗浄を行なった。

【0051】

次に、ドラム容積:300cc、直径:70mmの回転バレルを用意し、ここに部品本体を20ml投入した。そして、回転バレルを無電解Ni−Pめっき浴に浸漬し、バレル回転速度:20rpmで20分間、無電解めっき処理を実施した。ここで、無電解Ni−Pめっき浴として、P含有率:11重量%に設定された、硫酸ニッケル:0.1モル/L、次亜リン酸ナトリウム:0.2モル/L、クエン酸:0.5モル/L、および硫酸アンモニウム:0.5モル/Lを含むもの組成のものを用いた。また、この無電解Ni−Pめっき浴は、pH調整剤として硫酸および水酸化ナトリウムを用いて、pHを8.0に調整し、浴温を90℃に設定した。

【0052】

このようにして、P含有率が11重量%のNi−Pめっき膜からなる膜厚:1.5μmの第1のめっき層を形成した。

【0053】

上述の無電解Ni−Pめっき処理の後、純水による洗浄を実施した。

【0054】

次に、同じ回転バレルを用い、20mlの部品本体に加えて、直径:0.45mmのSn−Ag−Cu製メディア:40ml、および直径:8.0mmのナイロン被覆鉄球からなる攪拌玉:50ccを回転バレルに投入して、バレル回転速度:20rpmで、電解Niめっきを実施し、上記第1のめっき層上に、Pを実質的に含まない膜厚:2μmの電解Niめっき膜からなる第2のめっき層を形成した。ここで、電解Niめっき浴として、pH:4.0、浴温:55℃に設定されたワット浴(硫酸ニッケル:300g/L、塩化ニッケル:45g/L、ホウ酸:40mg/L)を用いた。

【0055】

上述の電解Niめっき処理の後、純水による洗浄を実施した。

【0056】

次に、上記のように、部品本体:20ml、メディア:40ml、および攪拌玉:50ccが投入されている同じ回転バレルを用い、バレル回転速度:20rpmで、電解Snめっきを実施し、上記第2のめっき層上に、膜厚:3μmの電解Snめっき膜からなる第3のめっき層を形成した。ここで、電解Snめっき浴として、中性Snめっき浴(石原産業株式会社製「NB−RZ」)を用いた。

【0057】

上述の電解Snめっき処理の後、純水による洗浄を実施し、次いで、空気中において、温度:80℃で15分間、乾燥を行なった。

【0058】

以上のようにして、試料1に係る積層セラミックコンデンサを作製した。

【0059】

[試料2]

試料1に係る積層セラミックコンデンサの作製のための無電解Ni−Pめっき処理において、無電解Ni−Pめっき浴のpHを8.5に調整し、P含有率を9重量%に設定したことを除いて、試料1の場合と同様の工程を経て、試料2に係る積層セラミックコンデンサを作製した。

【0060】

[試料3]

試料1に係る積層セラミックコンデンサの作製のための無電解Ni−Pめっき処理において、無電解Ni−Pめっき浴のpHを10に調整し、P含有率を5.5重量%に設定したことを除いて、試料1の場合と同様の工程を経て、試料3に係る積層セラミックコンデンサを作製した。

【0061】

[試料4]

試料1に係る積層セラミックコンデンサの作製のための無電解Ni−Pめっき処理において、無電解Ni−Pめっき浴のpHを9に調整し、P含有率を8重量%に設定したことを除いて、試料1の場合と同様の工程を経て、試料4に係る積層セラミックコンデンサを作製した。

【0062】

[試料5]

試料1に係る積層セラミックコンデンサの作製のための無電解Ni−Pめっき処理において、めっき時間を55分間と長くして、第1のめっき層としての無電解Ni−Pめっき膜の膜厚を4μmとしながら、その後の電解Niめっき処理を実施しなかったことを除いて、試料1の場合と同様の工程を経て、試料5に係る積層セラミックコンデンサを作製した。

【0063】

以上のようにして得られた試料1〜5に係る各積層セラミックコンデンサついて、シール性および電極固着力を評価した。

【0064】

シール性については、各試料に係る積層セラミックコンデンサを基板にはんだ実装した後、温度:125℃、湿度:95%RH、および印加電圧:6.3Vの条件で耐湿負荷試験を150時間実施し、絶縁抵抗IRが1×107Ω未満となったものを不良と判定し、試料数72個中での不良数を求めた。

【0065】

電極固着力については、各試料に係る積層セラミックコンデンサを基板にはんだ実装した後、積層セラミックコンデンサを横から基板と平行な方向に押す横押し試験を実施し、外部電極に剥離が生じる最大応力値を測定し、試料数20個での最大応力値の平均値を求めた。

【0066】

以下の表1には、第1のめっき層としての無電解Ni−Pめっき膜のP含有率とともに、上記シール性および電極固着力の評価結果が示されている。

【0067】

【表1】

【0068】

表1からわかるように、無電解Ni−Pめっき膜のP含有率が9重量%以上である試料1および2では、シール性不良数が0であり、電極固着力が12Nと高く、優れた結果を示した。

【0069】

これらに対して、試料3では、無電解Ni−Pめっき膜のP含有率が9重量%未満の5.5重量%と低く、そのため、シール性不良数が10と多く、また、電極固着力が5Nと極めて低かった。

【0070】

また、試料4では、無電解Ni−Pめっき膜のP含有率が9重量%未満の8重量%と低く、シール性不良数が0であったが、電極固着力が11Nと試料1および2に比べて低かった。

【0071】

また、試料5では、試料1の場合と同様、無電解Ni−Pめっき膜のP含有率が9重量%以上の11重量%であったが、Pを実質的に含まないNiめっき膜からなる第2のめっき層が形成されないため、電極固着力が12Nと高くなったが、シール性不良が2個生じた。

【0072】

上記試料5について、シール性不良が生じた積層セラミックコンデンサを解析したところ、無電解Ni−Pめっき膜に亀裂が確認された。

【符号の説明】

【0073】

1 積層セラミックコンデンサ

2 部品本体

3,4 セラミックグリーンシート

5,8 内部電極

11 セラミック層

16,17 外部電極

18 第1のめっき層

19 第2のめっき層

【技術分野】

【0001】

この発明は、積層型セラミック電子部品およびその製造方法に関するもので、特に、外部電極において、複数の内部電極と電気的に接続されるようにして直接めっきにより形成されためっき膜を備える、積層型セラミック電子部品およびその製造方法に関するものである。

【背景技術】

【0002】

図5に示すように、積層セラミックコンデンサに代表される積層型セラミック電子部品101は、一般に、たとえば誘電体セラミックからなる積層された複数のセラミック層102と、セラミック層102間の界面に沿って形成された複数の層状の内部電極103および104とを含む、積層構造の部品本体105を備えている。部品本体105の一方および他方端面106および107には、それぞれ、複数の内部電極103および複数の内部電極104の各端部が露出している。そして、これら内部電極103の各露出端および内部電極104の各露出端を、それぞれ、互いに電気的に接続するように、外部電極108および109が、部品本体105の一方および他方端面106および107上に形成されている。

【0003】

外部電極108および109の形成にあたっては、一般に、金属成分とガラス成分とを含む金属ペーストを部品本体105の端面106および107上に塗布し、次いで焼き付けることにより、ペースト電極層110がまず形成される。次に、ペースト電極層110上に、たとえばNiを主成分とする第1のめっき層111が形成され、さらにその上に、たとえばSnまたはAuを主成分とする第2のめっき層112が形成される。すなわち、外部電極108および109の各々は、ペースト電極層110、第1のめっき層111および第2のめっき層112の3層構造より構成される。

【0004】

外部電極108および109に対しては、積層型セラミック電子部品101がはんだを用いて基板に実装される際に、はんだとのぬれ性が良好であることが求められる。同時に、外部電極108に対しては、互いに電気的に絶縁された状態にある複数の内部電極103を互いに電気的に接続し、かつ、外部電極109に対しては、互いに電気的に絶縁された状態にある複数の内部電極104を互いに電気的に接続する役割が求められる。はんだぬれ性の確保の役割は、上述した第2のめっき層112が果たしており、内部電極103および104相互の電気的接続の役割は、ペースト電極層110が果たしている。第1のめっき層111は、はんだ接合時のはんだ喰われを防止する役割を果たしている。

【0005】

しかし、ペースト電極層110は、その厚みが数十μm〜数百μmと大きい。したがって、この積層型セラミック電子部品101の寸法を一定の規格値に収めるためには、このペースト電極層110の体積を確保する必要が生じる分、不所望にも、静電容量確保のための実効体積を減少させる必要が生じる。一方、めっき層111および112はその厚みが数μm程度であるため、仮に第1のめっき層111および第2のめっき層112のみで外部電極108および109を構成できれば、静電容量確保のための実効体積をより多く確保することができる。

【0006】

たとえば、特開昭63−169014号公報(特許文献1)には、部品本体の、内部電極が露出した側壁面の全面に対し、側壁面に露出した内部電極が短絡されるように、無電解Niめっきによって導電性金属層を析出させる、外部電極の形成方法が開示されている。

【0007】

しかしながら、部品本体の所定の面上への直接のめっきにより形成されためっき膜は、前述したペースト電極層の場合のようなガラス等を介さないため、めっき膜と部品本体との間での固着力が問題である。ここで、固着力は、部品本体におけるセラミック部分とめっき膜との間での固着力のみならず、内部電極露出端とめっき膜との間での固着力も重要である。

【0008】

また、一方では、めっき膜の皮膜強度(亀裂の入りにくさ)も重要である。そして、上述しためっき膜の固着力とこの皮膜強度とは、これらを両立させることが比較的難しい。

【0009】

より具体的に説明すると、積層型セラミック電子部品をはんだ実装すると、外部電極に応力が加わる。このとき、めっき膜がやわらかいと、めっき膜に亀裂が入りにくいが、上述の応力によってめっき膜が剥離して部品本体との間に隙間が生じやすく、そのため、隙間に水分が浸入することとなり、絶縁抵抗が劣化して、積層型セラミック電子部品の信頼性が低下するおそれがある。他方、めっき膜を硬くすると、固着力が向上するが、めっき膜が脆くなり、めっき膜に亀裂が入って、積層型セラミック電子部品の信頼性が低下する。

【先行技術文献】

【特許文献】

【0010】

【特許文献1】特開昭63−169014号公報

【発明の概要】

【発明が解決しようとする課題】

【0011】

この発明の目的は、上記のような問題点を解決し得る積層型セラミック電子部品およびその製造方法を提供しようとすることである。

【課題を解決するための手段】

【0012】

この発明は、積層された複数のセラミック層とセラミック層間の特定の界面に沿って形成された複数の内部電極とを備え、各内部電極が所定の面に露出する露出端を有している、部品本体と、各内部電極の露出端に電気的に接続されるように、部品本体の上記所定の面上に形成された、外部電極とを備える、積層型セラミック電子部品にまず向けられるものであって、上述した技術的課題を解決するため、上記外部電極は、上記所定の面上に直接形成されたもので、P含有率が9重量%以上のNi−Pめっき膜からなる第1のめっき層と、第1のめっき層上に形成されたもので、Pを実質的に含まないNiめっき膜からなる第2のめっき層とを含むことを特徴としている。

【0013】

この発明に係る積層型セラミック電子部品において、好ましくは、第1のめっき層は無電解めっきにより形成されたものであり、第2のめっき層は電解めっきにより形成されたものである。

【0014】

また、第1のめっき層を構成するNi−Pめっき膜は、非晶質であることが好ましい。

【0015】

この発明は、また、積層型セラミック電子部品の製造方法にも向けられる。この発明に係る積層型セラミック電子部品の製造方法は、積層された複数のセラミック層とセラミック層間の特定の界面に沿って形成された複数の内部電極とを備え、各内部電極が所定の面に露出する露出端を有している、部品本体を用意する工程と、各内部電極の露出端に電気的に接続されるように、部品本体の上記所定の面上に外部電極を形成する工程とを備えるもので、前述した技術的課題を解決するため、次のような構成を備えることを特徴としている。

【0016】

すなわち、外部電極を形成する工程は、無電解めっきを実施することにより、各内部電極の露出端を起点としてめっき析出物を析出させるとともに、当該めっき析出物を所定の面上に成長させることによって、P含有率が9重量%以上のNi−Pめっき膜からなる第1のめっき層を形成する工程と、電解めっきを実施することにより、第1のめっき層上に、Pを実質的に含まないNiめっき膜からなる第2のめっき層を形成する工程とを含むことを特徴としている。

【発明の効果】

【0017】

この発明に係る積層型セラミック電子部品によれば、まず、外部電極における第1のめっき層を、P含有率が9重量%以上のNi−Pめっき膜から構成しているので、固着力を向上させることができる。すなわち、P含有率を上げると、めっき膜の硬度が上がる。したがって、第1のめっき層の硬度を上げることができる。このように第1のめっき層の硬度が上がると、セラミックの微細な凹凸に追随したとき、皮膜応力が小さくなることから、アンカー効果が高くなる。よって、内部電極露出端に対する第1のめっき層の接合強度が全体的に向上するとともに、第1のめっき層と内部電極露出端の周縁部のセラミック部分との界面での剥離も生じにくくなるため、実装時の耐湿信頼性が向上する。

【0018】

また、P含有率が高いと、めっき膜の耐腐食性が向上する。したがって、第1のめっき層の耐腐食性が向上し、この点においても、耐湿信頼性を向上させることができる。

【0019】

第1のめっき層を構成するNi−Pめっき膜は、前述したように、非晶質であることが好ましい。非晶質であれば、前述したようなセラミックの凹凸に対する追随性が良好である。よって、前述のアンカー効果がより高くなり、固着力をより高めることができるとともに、第1のめっき層と内部電極との間の隙間を実質的になくすことができ、たとえば水蒸気に対するシール性を良好なものとし、耐湿信頼性をより向上させることができる。

【0020】

他方、第1のめっき層は、前述したように、硬度が高いので、割れやすいという欠点がある。すなわち、実装時および実装後に加わる応力や熱衝撃によって、第1のめっき層にクラックが入り、耐湿信頼性が低下することがある。この欠点を補うのが、Pを実質的に含まないNiめっき膜からなる第2のめっき層である。Pを含まないNiめっき膜は、比較的柔軟である。そのため、第1のめっき層を第2のめっき層によって保護することによって、第1のめっき層が割れにくくなり、第1のめっき層による耐湿信頼性を良好に維持することができる。

【0021】

以上のようにして、外部電極において、めっき膜の固着力とめっき膜の皮膜強度(亀裂の入りにくさ)とを両立させることができる。

【0022】

この発明に係る積層型セラミック電子部品の製造方法によれば、第1のめっき層を無電解めっきにより形成するので、所望のP含有量のめっき膜を安定して形成することができる。また、第2のめっき層を電解めっきにより形成するので、能率的に第2のめっき層を形成することができる。

【図面の簡単な説明】

【0023】

【図1】この発明の一実施形態による積層型セラミック電子部品としての積層セラミックコンデンサを製造するために用意される、内部電極が印刷された2種類のセラミックグリーンシートを示す平面図である。

【図2】図1に示したセラミックグリーンシートを用いて構成された積層セラミックコンデンサのための部品本体を示す斜視図である。

【図3】図2に示した部品本体にめっきを施すことによって外部電極が形成された積層セラミックコンデンサを示す斜視図である。

【図4】図3に示した積層セラミックコンデンサに形成された外部電極の断面を拡大して示す図である。

【図5】従来の積層型セラミック電子部品を示す断面図である。

【発明を実施するための形態】

【0024】

この発明の一実施形態による積層型セラミック電子部品としての積層セラミックコンデンサの構造を、図1ないし図4を参照しながら、その製造方法に従って説明する。

【0025】

図3に示した積層セラミックコンデンサ1を製造するため、図2に示した部品本体2が用意される。そして、図2に示した部品本体2を得るため、図1に示した2種類のセラミックグリーンシート3および4が用意される。

【0026】

図1(A)に示したセラミックグリーンシート3上には、第1の内部電極5が形成される。第1の内部電極5は、その主要部をなす容量形成部6と引出し部7とを有している。引出し部7は、セラミックグリーンシート3の一方の短辺とこれに隣接する2つの長辺の各一部にまで届くように延び、ここに露出端を構成する。

【0027】

他方、図1(B)に示したセラミックグリーンシート4上には、第2の内部電極8が形成される。第2の内部電極8は、その主要部をなす容量形成部9と引出し部10とを有している。引出し部10は、上述した第1の内部電極5の引出し部7とは逆側に形成される。引出し部10は、セラミックグリーンシート4の一方の短辺とこれに隣接する2つの長辺の各一部にまで届くように延び、ここに露出端を構成する。

【0028】

上述した内部電極5および8は、たとえばNiを主成分とする導電性ペーストを印刷することによって、セラミックグリーンシート3および4上にそれぞれ形成される。

【0029】

次に、各々複数のセラミックグリーンシート3および4が交互に積層されるとともに、その積層方向の両端部に、内部電極が形成されていない適当数のセラミックグリーンシートが外層部をなすように積層される。これによって、部品本体2の生の状態のものが得られる。

【0030】

なお、上述した積層工程が、複数の積層セラミックコンデンサを取り出すことができるマザー状態のセラミックグリーンシートについて実施され、積層工程の後、カット工程を実施して、個々の積層セラミックコンデンサのための部品本体2の生の状態のものを得るようにしてもよい。

【0031】

次に、焼成工程が実施される。これによって、図2に示すように、焼結した部品本体2が得られる。部品本体2は、積層された複数のセラミック層11を備えている。セラミック層11は、上述のセラミックグリーンシートの焼結によって得られたものである。また、前述した第1および第2の内部電極5および8は焼結した状態となっており、セラミック層11間の特定の界面に沿って位置している。第1の内部電極5の引出し部7は、部品本体2の一方の端面12ならびにそれに隣接する上面14および下面15の各一部において露出端を形成している。第2の内部電極8の引出し部10は、部品本体2の他方の端面13ならびにそれに隣接する上面14および下面15の各一部において露出端を形成している。

【0032】

次に、好ましくは、部品本体2に対して、バレル研磨工程が実施され、それによって、内部電極5および8の露出端をより確実に露出させるようにする。次いで、好ましくは、純水による洗浄工程が実施される。

【0033】

その後、図3に示した積層セラミックコンデンサ1を得るため、第1の内部電極5の露出端に電気的に接続される第1の外部電極16が、部品本体2の一方の端面12上ならびにそれに隣接する上面14および下面15の各一部上に形成され、また、第2の内部電極8の露出端に電気的に接続される第2の外部電極17が、部品本体2の他方の端面13上ならびにそれに隣接する上面14および下面15の各一部上に形成される。

【0034】

上述した第1の外部電極16と第2の外部電極17とは、同時に形成され、かつ互いに同じ断面構造を有しているので、図4に示した第1の外部電極16について、より詳細に説明し、第2の外部電極17については、詳細な説明は省略する。

【0035】

図4を参照して、第1の外部電極16は、各内部電極5の露出端を起点として析出しためっき析出物を、部品本体2の一方の端面12上ならびにそれに隣接する上面14および下面15(図2参照)の各一部上に成長させてなるもので、P含有率が9重量%以上のNi−Pめっき膜からなる第1のめっき層18と、第1のめっき層18上に形成されるもので、Pを実質的に含まないNiめっき膜からなる第2のめっき層19とを少なくとも備え、好ましくは、第2のめっき層19上に形成される第3のめっき層20をさらに備える。第3のめっき層20は、外部電極16のはんだぬれ性を向上させるためのものであり、たとえばSnめっき膜から構成される。

【0036】

上述した第1のめっき層18は、好ましくは、無電解めっきによって形成される。そのため、無電解めっき工程の前処理として、好ましくは、Pd触媒を付与する工程および純水による洗浄工程が実施され、その後、無電解Ni−Pめっきが実施され、P含有率が9重量%以上のNi−Pめっき膜からなる第1のめっき層18が形成される。ここで、第1のめっき層18を構成するNi−Pめっき膜は、隣り合う内部電極5の各露出端におけるめっき析出物を物理的に互いに接続した状態としながら、均質で緻密な膜を構成する。

【0037】

なお、上述のPd触媒を付与する工程において、内部電極5の露出端のNiがPdに置換され、無電解Ni−Pめっきの還元剤のための触媒能が向上するが、Ni自体に触媒性があるため、Pd触媒を付与する工程を省略することも可能である。

【0038】

上述のように、第1のめっき層18を無電解めっきにより形成すると、所望のP含有量のめっき膜を安定して形成することができる。しかし、このような利点を特に望まないならば、第1のめっき層18を電解めっきによって形成してもよい。

【0039】

上述の無電解Ni−Pめっき工程の後、純水による洗浄工程が実施される。

【0040】

その後、熱処理工程が実施されてもよい。熱処理温度としては、たとえば600℃以上、好ましくは800℃以上の温度が採用される。この熱処理によって、内部電極5と第1のめっき層18との間で相互拡散が生じる。そして、この相互拡散部分において、金属の体積膨張が起こるため、セラミック層11と内部電極5および第1のめっき層18の各々との界面に存在し得る隙間を有利に埋めることができ、その結果、部品本体2の内部への水分の浸入を防止する効果が奏される。

【0041】

次に、Pを実質的に含まないNiめっき膜からなる第2のめっき層19が形成される。第2のめっき層19は、好ましくは、電解めっきによって形成される。第2のめっき層19を電解めっきにより形成すると、能率的に第2のめっき層19を形成することができる。しかし、このような利点を特に望まないならば、第2のめっき層19を無電解めっきによって形成してもよい。

【0042】

上述の電解Niめっき工程の後、純水による洗浄工程が実施される。

【0043】

次に、たとえばSnめっき膜からなる第3のめっき層20が形成される。第3のめっき層20は、好ましくは、電解めっきによって形成される。

【0044】

上述の電解Snめっき工程の後、純水による洗浄工程が実施され、次いで、乾燥工程が実施される。

【0045】

このようにして、図3に示した積層セラミックコンデンサ1が完成される。

【0046】

以上説明した積層セラミックコンデンサ1では、セラミック層11が誘電体セラミックから構成される。しかし、この発明が向けられる積層型セラミック電子部品は、積層セラミックコンデンサに限らず、たとえば、インダクタ、サーミスタ、圧電部品などを構成するものであってもよい。したがって、積層型セラミック電子部品の機能に応じて、セラミック層は、誘電体セラミックの他、磁性体セラミック、半導体セラミック、圧電体セラミックなどから構成されてもよい。

【0047】

また、図示した積層セラミックコンデンサ1は、2個の外部電極16および17を備える2端子型のものであるが、この発明は3端子以上の多端子型の積層型セラミック電子部品にも適用することができる。

【0048】

以下に、この発明の効果を確認するために実施した実験例について説明する。この実験例では、この発明の範囲内の実施例としての試料1および2に係る各積層セラミックコンデンサ、ならびにこの発明の範囲外の比較例としての試料3〜5に係る各積層セラミックコンデンサを作製した。

【0049】

[試料1]

平面寸法が1.0mm×0.5mmの積層セラミックコンデンサ用部品本体であって、セラミック層がチタン酸バリウム系誘電体セラミックからなり、内部電極がNiを主成分とするものを用意した。この部品本体において、内部電極間のセラミック層の各厚みは1μmであり、各内部電極の厚みは1μmであり、内部電極が配置されない各外層部の厚みは50μmであった。また、後述するめっき処理の前処理として、部品本体にはバレル研磨を施し、内部電極の露出端を確実に露出させた状態としておき、次いで、純水による洗浄工程を実施しておいた。

【0050】

次に、部品本体に対して、Pd触媒付与工程を実施した。Pd触媒付与工程では、Pd濃度:100ppm、pH:2.5、温度:25℃の塩化パラジウム水溶液を用意し、そこに部品本体を3分間浸漬した。浸漬後、部品本体を塩化パラジウム水溶液から取り出し、純水による洗浄を行なった。

【0051】

次に、ドラム容積:300cc、直径:70mmの回転バレルを用意し、ここに部品本体を20ml投入した。そして、回転バレルを無電解Ni−Pめっき浴に浸漬し、バレル回転速度:20rpmで20分間、無電解めっき処理を実施した。ここで、無電解Ni−Pめっき浴として、P含有率:11重量%に設定された、硫酸ニッケル:0.1モル/L、次亜リン酸ナトリウム:0.2モル/L、クエン酸:0.5モル/L、および硫酸アンモニウム:0.5モル/Lを含むもの組成のものを用いた。また、この無電解Ni−Pめっき浴は、pH調整剤として硫酸および水酸化ナトリウムを用いて、pHを8.0に調整し、浴温を90℃に設定した。

【0052】

このようにして、P含有率が11重量%のNi−Pめっき膜からなる膜厚:1.5μmの第1のめっき層を形成した。

【0053】

上述の無電解Ni−Pめっき処理の後、純水による洗浄を実施した。

【0054】

次に、同じ回転バレルを用い、20mlの部品本体に加えて、直径:0.45mmのSn−Ag−Cu製メディア:40ml、および直径:8.0mmのナイロン被覆鉄球からなる攪拌玉:50ccを回転バレルに投入して、バレル回転速度:20rpmで、電解Niめっきを実施し、上記第1のめっき層上に、Pを実質的に含まない膜厚:2μmの電解Niめっき膜からなる第2のめっき層を形成した。ここで、電解Niめっき浴として、pH:4.0、浴温:55℃に設定されたワット浴(硫酸ニッケル:300g/L、塩化ニッケル:45g/L、ホウ酸:40mg/L)を用いた。

【0055】

上述の電解Niめっき処理の後、純水による洗浄を実施した。

【0056】

次に、上記のように、部品本体:20ml、メディア:40ml、および攪拌玉:50ccが投入されている同じ回転バレルを用い、バレル回転速度:20rpmで、電解Snめっきを実施し、上記第2のめっき層上に、膜厚:3μmの電解Snめっき膜からなる第3のめっき層を形成した。ここで、電解Snめっき浴として、中性Snめっき浴(石原産業株式会社製「NB−RZ」)を用いた。

【0057】

上述の電解Snめっき処理の後、純水による洗浄を実施し、次いで、空気中において、温度:80℃で15分間、乾燥を行なった。

【0058】

以上のようにして、試料1に係る積層セラミックコンデンサを作製した。

【0059】

[試料2]

試料1に係る積層セラミックコンデンサの作製のための無電解Ni−Pめっき処理において、無電解Ni−Pめっき浴のpHを8.5に調整し、P含有率を9重量%に設定したことを除いて、試料1の場合と同様の工程を経て、試料2に係る積層セラミックコンデンサを作製した。

【0060】

[試料3]

試料1に係る積層セラミックコンデンサの作製のための無電解Ni−Pめっき処理において、無電解Ni−Pめっき浴のpHを10に調整し、P含有率を5.5重量%に設定したことを除いて、試料1の場合と同様の工程を経て、試料3に係る積層セラミックコンデンサを作製した。

【0061】

[試料4]

試料1に係る積層セラミックコンデンサの作製のための無電解Ni−Pめっき処理において、無電解Ni−Pめっき浴のpHを9に調整し、P含有率を8重量%に設定したことを除いて、試料1の場合と同様の工程を経て、試料4に係る積層セラミックコンデンサを作製した。

【0062】

[試料5]

試料1に係る積層セラミックコンデンサの作製のための無電解Ni−Pめっき処理において、めっき時間を55分間と長くして、第1のめっき層としての無電解Ni−Pめっき膜の膜厚を4μmとしながら、その後の電解Niめっき処理を実施しなかったことを除いて、試料1の場合と同様の工程を経て、試料5に係る積層セラミックコンデンサを作製した。

【0063】

以上のようにして得られた試料1〜5に係る各積層セラミックコンデンサついて、シール性および電極固着力を評価した。

【0064】

シール性については、各試料に係る積層セラミックコンデンサを基板にはんだ実装した後、温度:125℃、湿度:95%RH、および印加電圧:6.3Vの条件で耐湿負荷試験を150時間実施し、絶縁抵抗IRが1×107Ω未満となったものを不良と判定し、試料数72個中での不良数を求めた。

【0065】

電極固着力については、各試料に係る積層セラミックコンデンサを基板にはんだ実装した後、積層セラミックコンデンサを横から基板と平行な方向に押す横押し試験を実施し、外部電極に剥離が生じる最大応力値を測定し、試料数20個での最大応力値の平均値を求めた。

【0066】

以下の表1には、第1のめっき層としての無電解Ni−Pめっき膜のP含有率とともに、上記シール性および電極固着力の評価結果が示されている。

【0067】

【表1】

【0068】

表1からわかるように、無電解Ni−Pめっき膜のP含有率が9重量%以上である試料1および2では、シール性不良数が0であり、電極固着力が12Nと高く、優れた結果を示した。

【0069】

これらに対して、試料3では、無電解Ni−Pめっき膜のP含有率が9重量%未満の5.5重量%と低く、そのため、シール性不良数が10と多く、また、電極固着力が5Nと極めて低かった。

【0070】

また、試料4では、無電解Ni−Pめっき膜のP含有率が9重量%未満の8重量%と低く、シール性不良数が0であったが、電極固着力が11Nと試料1および2に比べて低かった。

【0071】

また、試料5では、試料1の場合と同様、無電解Ni−Pめっき膜のP含有率が9重量%以上の11重量%であったが、Pを実質的に含まないNiめっき膜からなる第2のめっき層が形成されないため、電極固着力が12Nと高くなったが、シール性不良が2個生じた。

【0072】

上記試料5について、シール性不良が生じた積層セラミックコンデンサを解析したところ、無電解Ni−Pめっき膜に亀裂が確認された。

【符号の説明】

【0073】

1 積層セラミックコンデンサ

2 部品本体

3,4 セラミックグリーンシート

5,8 内部電極

11 セラミック層

16,17 外部電極

18 第1のめっき層

19 第2のめっき層

【特許請求の範囲】

【請求項1】

積層された複数のセラミック層と前記セラミック層間の特定の界面に沿って形成された複数の内部電極とを備え、各前記内部電極が所定の面に露出する露出端を有している、部品本体と、

各前記内部電極の前記露出端に電気的に接続されるように、前記部品本体の前記所定の面上に形成された、外部電極と

を備え、

前記外部電極は、

前記所定の面上に直接形成されたもので、P含有率が9重量%以上のNi−Pめっき膜からなる第1のめっき層と、

前記第1のめっき層上に形成されたもので、Pを実質的に含まないNiめっき膜からなる第2のめっき層と

を含む、

積層型セラミック電子部品。

【請求項2】

前記第1のめっき層は無電解めっきにより形成されたものであり、前記第2のめっき層は電解めっきにより形成されたものである、請求項1に記載の積層型セラミック電子部品。

【請求項3】

前記第1のめっき層を構成するNi−Pめっき膜は、非晶質である、請求項1または2に記載の積層型セラミック電子部品。

【請求項4】

積層された複数のセラミック層と前記セラミック層間の特定の界面に沿って形成された複数の内部電極とを備え、各前記内部電極が所定の面に露出する露出端を有している、部品本体を用意する工程と、

各前記内部電極の前記露出端に電気的に接続されるように、前記部品本体の前記所定の面上に外部電極を形成する工程と

を備え、

前記外部電極を形成する工程は、

無電解めっきを実施することにより、各前記内部電極の前記露出端を起点としてめっき析出物を析出させるとともに、当該めっき析出物を前記所定の面上に成長させることによって、P含有率が9重量%以上のNi−Pめっき膜からなる第1のめっき層を形成する工程と、

電解めっきを実施することにより、前記第1のめっき層上に、Pを実質的に含まないNiめっき膜からなる第2のめっき層を形成する工程と

を含む、

積層型セラミック電子部品の製造方法。

【請求項1】

積層された複数のセラミック層と前記セラミック層間の特定の界面に沿って形成された複数の内部電極とを備え、各前記内部電極が所定の面に露出する露出端を有している、部品本体と、

各前記内部電極の前記露出端に電気的に接続されるように、前記部品本体の前記所定の面上に形成された、外部電極と

を備え、

前記外部電極は、

前記所定の面上に直接形成されたもので、P含有率が9重量%以上のNi−Pめっき膜からなる第1のめっき層と、

前記第1のめっき層上に形成されたもので、Pを実質的に含まないNiめっき膜からなる第2のめっき層と

を含む、

積層型セラミック電子部品。

【請求項2】

前記第1のめっき層は無電解めっきにより形成されたものであり、前記第2のめっき層は電解めっきにより形成されたものである、請求項1に記載の積層型セラミック電子部品。

【請求項3】

前記第1のめっき層を構成するNi−Pめっき膜は、非晶質である、請求項1または2に記載の積層型セラミック電子部品。

【請求項4】

積層された複数のセラミック層と前記セラミック層間の特定の界面に沿って形成された複数の内部電極とを備え、各前記内部電極が所定の面に露出する露出端を有している、部品本体を用意する工程と、

各前記内部電極の前記露出端に電気的に接続されるように、前記部品本体の前記所定の面上に外部電極を形成する工程と

を備え、

前記外部電極を形成する工程は、

無電解めっきを実施することにより、各前記内部電極の前記露出端を起点としてめっき析出物を析出させるとともに、当該めっき析出物を前記所定の面上に成長させることによって、P含有率が9重量%以上のNi−Pめっき膜からなる第1のめっき層を形成する工程と、

電解めっきを実施することにより、前記第1のめっき層上に、Pを実質的に含まないNiめっき膜からなる第2のめっき層を形成する工程と

を含む、

積層型セラミック電子部品の製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図2】

【図3】

【図4】

【図5】

【公開番号】特開2012−43841(P2012−43841A)

【公開日】平成24年3月1日(2012.3.1)

【国際特許分類】

【出願番号】特願2010−181202(P2010−181202)

【出願日】平成22年8月13日(2010.8.13)

【出願人】(000006231)株式会社村田製作所 (3,635)

【Fターム(参考)】

【公開日】平成24年3月1日(2012.3.1)

【国際特許分類】

【出願日】平成22年8月13日(2010.8.13)

【出願人】(000006231)株式会社村田製作所 (3,635)

【Fターム(参考)】

[ Back to top ]