積層型電子部品及び電子部品の実装構造

【課題】低周波帯域において低インピーダンスを保ちつつ、高周波帯域において高インピーダンスとすることができる実装構造などに適した積層型電子部品を提供する。

【解決手段】フェライトビーズインダクタ12,13は、磁性体層24と内部電極25a〜25dとが積層されるフェライトビーズ素体18と、フェライトビーズ素体18の第1及び第2の側面18c,18dに配置される第1及び第2の外部電極19,20とを備えている。内部電極25a〜25dは、長辺よりも短い短辺の方向に伸びて第1及び第2の外部電極19,20に接続される。また、フェライトビーズ素体18は、磁性体層24上において内部電極を形成可能な内部電極領域S内に、積層方向に隣接する磁性体層24同士が接合するための空隙27a〜27c(接合部)を有している。

【解決手段】フェライトビーズインダクタ12,13は、磁性体層24と内部電極25a〜25dとが積層されるフェライトビーズ素体18と、フェライトビーズ素体18の第1及び第2の側面18c,18dに配置される第1及び第2の外部電極19,20とを備えている。内部電極25a〜25dは、長辺よりも短い短辺の方向に伸びて第1及び第2の外部電極19,20に接続される。また、フェライトビーズ素体18は、磁性体層24上において内部電極を形成可能な内部電極領域S内に、積層方向に隣接する磁性体層24同士が接合するための空隙27a〜27c(接合部)を有している。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、積層型電子部品及び当該積層型電子部品を含む電子部品の実装構造に関する。特に本発明は、積層ビーズインダクタ及び当該積層ビーズインダクタと積層コンデンサとの実装構造に関する。

【背景技術】

【0002】

電源や信号等の配線を介したノイズの漏洩や侵入を防止するためのノイズフィルタとして、例えば特許文献1に記載のインダクタとコンデンサとが組み合わされた電子部品が従来知られている。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開2007−234755号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

近年、電子機器の高周波化に伴い、電子機器に用いられる部品についても高周波化に対応することが求められている。しかしながら、上記特許文献1に記載された従来の電子部品では、高周波に対応すべく高周波帯域での抵抗成分を大きくすると、低周波帯域での直流抵抗も含め、全帯域での抵抗、ひいてはインピーダンスが大きくなってしまう。

【0005】

そこで、本願出願人は、例えば、特願2010−279010号において、低周波帯域において低インピーダンスを保ちつつ、高周波帯域において高インピーダンスとすることができる電子部品の実装構造を提案している。そして、このような実装構造に適した電子部品が望まれている。

【0006】

本発明は、低周波帯域において低インピーダンスを保ちつつ、高周波帯域において高インピーダンスとすることができる実装構造などに適した積層型電子部品、及び、当該積層型電子部品を含む電子部品の実装構造を提供することを目的とする。

【課題を解決するための手段】

【0007】

上記課題を解決するために、本発明に係る積層型電子部品は、磁性体層の間に内部電極が配置されるように磁性体層と内部電極とが積層され、且つ、互いに対向する略長方形状の第1及び第2の主面と、第1及び第2の主面間を連結するように第1及び第2の主面の長辺方向に伸び且つ互いに対向する第1及び第2の側面と、第1及び第2の主面間を連結するように第1及び第2の主面の短辺方向に伸び且つ互いに対向する第3及び第4の側面とを有する素体と、素体の第1の側面に配置される第1の外部電極と、素体の第2の側面に配置される第2の外部電極とを備えている。この積層型電子部品では、内部電極は、長辺よりも短い短辺の方向に伸びて第1及び第2の外部電極に接続され、素体は、磁性体層上において内部電極を形成可能な内部電極領域内に、積層方向に隣接する磁性体層同士が接合する接合部を有するようになっている。

【0008】

また、本発明に係る電子部品の実装構造は、電流を供給するための電源ラインに接続される電子部品の実装構造であって、電子部品として、コンデンサと上記構成の積層型電子部品であるビーズインダクタとを備え、電源ラインの間に、コンデンサとビーズインダクタとが直列となるように実装される。

【0009】

この実装構造によれば、コンデンサとビーズインダクタとが直列となるように電源ライン間に接続されるので、ビーズインダクタの抵抗成分がコンデンサの等価直列抵抗(ESR:Equivalent Series Resistance)として作用する。ビーズインダクタの抵抗成分は、直流抵抗成分と高周波帯域で増加する損失との和で構成される。よって、この実装構造によれば、高周波帯域でのインピーダンスを増加させることが可能になり、高周波ノイズを好適に除去することが可能となる。一方、ビーズインダクタは、低周波帯域では抵抗成分よりもむしろインダクタ成分が機能するため、上記実装構造によれば低周波帯域ではインピーダンスを小さく保つことが可能となる。そして、低周波ノイズに対しては、コンデンサを実装しているため、当該コンデンサでその低周波ノイズは吸収され好適に除去することができる。

【0010】

ところで、このビーズインダクタでは、第1及び第2の側面に両外部電極が配置されるので第1及び第2の外部電極の幅を広くでき、しかも、内部電極が短辺方向に伸びて両外部電極に接続する構成となっているので内部電極の長さを短くすることができる。このため、上記実装構造等に対して本発明に係るビーズインダクタを用いた場合、ビーズインダクタの抵抗成分の構成の1つである直流抵抗成分を小さくすることができる。つまり、このビーズインダクタを用いることにより、低周波帯域では更に低ESRとすることができ、高周波帯域では高ESRとすることができる。

【0011】

しかも、上記構成のビーズインダクタでは、内部電極を形成可能な内部電極領域内に、積層方向に隣接する磁性体層同士が接合する接合部を有する構成としている。このため、このビーズインダクタによれば、低周波帯域での低ESR等を実現できるだけでなく、更に、接合部の存在により磁性体層の層間はがれを防止してビーズインダクタの内部欠陥の発生を抑えることもできる。

【0012】

また、上記のビーズインダクタでは、磁性体層上における内部電極領域の面積をS0とし、磁性体層上における接合部の面積をS1とした場合において、内部電極領域と接合部との面積比であるS1/S0が0.20よりも大きく且つ0.67以下であることが好ましい。この場合、ビーズインダクタの直流抵抗を低めに抑えつつ、磁性体層同士の密着性を更に向上させて、層間はがれ等による内部欠陥の発生を一層抑えることができる。

【0013】

また、上記のビーズインダクタでは、内部電極は、磁性体層上において、複数の内部電極に分割されていることが好ましい。この場合、磁性体層同士の密着性を更に向上させて、層間はがれ等による内部欠陥の発生を一層抑えることができる。

【0014】

また、上記のビーズインダクタでは、異なる磁性体層上に配置された内部電極のそれぞれは、積層方向において、その間に位置する磁性体層を介して対向しないように配置されていることが好ましい。この場合、磁性体層同士の密着性を更に向上させて、層間はがれ等による内部欠陥の発生を一層抑えることができる。

【0015】

また、上記のビーズインダクタでは、第1及び第2の外部電極は、それぞれ一の外部電極からなることが好ましい。この場合、外部電極における抵抗値を更に下げることができるため、ビーズインダクタの直流抵抗成分を更に小さくすることができる。

【0016】

また、上記実装構造において、コンデンサは、誘電体層と内部電極とが積層され、且つ、互いに対向する略長方形状の第1及び第2の主面と、第1及び第2の主面間を連結するように第1及び第2の主面の長辺方向に伸び且つ互いに対向する第1及び第2の側面と、第1及び第2の主面間を連結するように第1及び第2の主面の短辺方向に伸び且つ互いに対向する第3及び第4の側面とを有するコンデンサ素体と、コンデンサ素体の第1の側面側に配置される第1のコンデンサ外部電極と、コンデンサ素体の第2の側面側に配置される第2のコンデンサ外部電極とを備えていることが好ましい。この場合、長辺方向に伸びる第1及び第2の側面にコンデンサ外部電極が配置されるので、等価直列インダクタンス(ESL:Equivalent Series Inductance)を低減させることができる。そして、低ESLとなることから、この実装構造によれば、不要ノイズをインダクタに確実に流すことが可能となり、不要ノイズを熱変換によって、より確実に除去できる。

【0017】

また、上記実装構造において、コンデンサの第1及び第2のコンデンサ外部電極の幅寸法は、ビーズインダクタの第1及び第2の外部電極の幅寸法と略同等であることが好ましい。コンデンサとビーズインダクタとの外部電極の幅寸法が異なる場合、高周波電流がコンデンサの外部電極とビーズインダクタの外部電極との間にて反射し、高周波電流がビーズインダクタの抵抗成分において熱に変換されないといった不具合が生じ、ノイズの除去効果が低下するといった問題がある。そこで、コンデンサとビーズインダクタとの外部電極の幅寸法を同等とすることで、高周波電流の反射を防止でき、ビーズインダクタにおけるノイズの除去効果の向上を図ることができる。

【0018】

また、上記実装構造において、ビーズインダクタを複数有し、各ビーズインダクタは、互いの磁界が相殺されるように実装されていることが好ましい。つまり、ビーズインダクタは、電流の流れる方向が互いに逆向きとなるように実装されていることが好ましい。この場合、ビーズインダクタにおけるESLが低減するため、高周波ノイズの反射を防止することが可能となり、高周波ノイズを抵抗成分で熱変換して好適に除去することが可能となる。

【発明の効果】

【0019】

本発明によれば、低周波帯域において低インピーダンスを保ちつつ、高周波帯域において高インピーダンスとすることができる実装構造などに適した積層型電子部品、及び、当該積層型電子部品を含む電子部品の実装構造を提供することができる。

【図面の簡単な説明】

【0020】

【図1】第1実施形態に係る電子部品の実装構造を概略的に示す図である。

【図2】図1に示す電子部品の実装構造の断面図である。

【図3】図1に示す実装構造に用いられるコンデンサを示す斜視図である。

【図4】図3に示すコンデンサの層構成を示す図である。

【図5】図1に示す実装構造に用いられるフェライトビーズインダクタを示す斜視図である。

【図6】図5に示すフェライトビーズインダクタのVI−VI線断面図である。

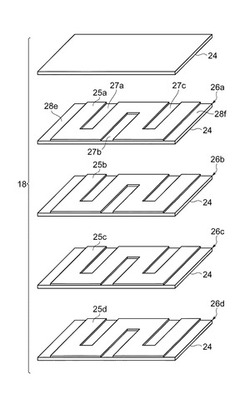

【図7】図5に示すフェライトビーズインダクタの層構成を示す図である。

【図8】フェライトビーズインダクタにおける内部電極領域や接合部を示す図である。

【図9】電子部品の実装構造の等価回路図である。

【図10】第2実施形態に係るフェライトビーズインダクタの層構成を示す図である。

【図11】第3実施形態に係るフェライトビーズインダクタの層構成を示す図である。

【図12】第4実施形態に係るフェライトビーズインダクタを示す図である。

【図13】図12に示すフェライトビーズインダクタの層構成を示す図である。

【図14】他の形態の電子部品の実装構造を概略的に示す図である。

【図15】他の形態の電子部品の実装構造を概略的に示す図である。

【発明を実施するための形態】

【0021】

以下、添付図面を参照して、本発明の好適な実施形態について詳細に説明する。なお、説明において、同一要素又は同一機能を有する要素には、同一符号を用いることとし、重複する説明は省略する。

【0022】

[第1実施形態]

まず、第1実施形態に係る電子部品の実装構造について説明する。図1は、第1実施形態に係る電子部品の実装構造を示す図である。図2は、図1に示す電子部品の実装構造の断面図である。各図に示すように、電子部品の実装構造では、電源供給用流路を形成する2本の電源ライン1,2、IC(Integrated Circuit)チップ3、第1〜第4のランド電極4〜7及び接続電極8,9が配置された回路に電子部品を実装する。電子部品の実装構造では、電源ライン1,2に接続される電子部品として、複数のコンデンサ(チップコンデンサ)10,11と、複数のフェライトビーズインダクタ12,13とを実装する。コンデンサ10,11及びフェライトビーズインダクタ12,13は、それぞれ2つ実装される。コンデンサ10,11とフェライトビーズインダクタ12,13とは、電源ライン1,2間に直列に接続されている。

【0023】

電源ライン1,2は、ICチップ3の端子電極3a,3bにそれぞれ接続されている。電源ライン1から分岐した配線1aは、第1のランド電極4に接続されており、電源ライン2から分岐した配線2aは、第2のランド電極5に接続されている。第1のランド電極4と第2のランド電極5とは、対向して配置されている。第1のランド電極4と第2のランド電極5との間には、配線1a,2aに接続されない接続電極8が設けられている。第1のランド電極4、第2のランド電極5及び接続電極8は、一直線上に配置されている。

【0024】

第1のランド電極4、接続電極8及び第2のランド電極5が配置された方向(以下、第1の方向)と面方向において略直角に交わる方向(以下、第2の方向)において、第1のランド電極4の隣(図示右側)には、所定の間隔をあけて第3のランド電極6が並設されている。また、第2のランド電極5の隣(図示右側)には、所定の間隔をあけて第4のランド電極7が並設されている。第3のランド電極6と第4のランド電極7との間には、接続電極8の隣に所定の間隔をあけて接続電極9が並設されている。なお、第1〜第4のランド電極4〜7及び接続電極8,9は、矩形状を呈している。

【0025】

図1及び図2に示すように、第4のランド電極7は、ビアホールH1を介して第1のランド電極4と電気的に接続される。第3のランド電極6は、ビアホールH2を介して第2のランド電極5と電気的に接続される。このような構成により、第1のランド電極4と第4のランド電極7とは、同極性(+極性)となり、第2のランド電極5と第3のランド電極6とは、同極性(−極性)となる。つまり、第2の方向において隣接する第1のランド電極4と第3のランド電極6、第2のランド電極5と第4のランド電極7は、異極性となる。

【0026】

コンデンサ10とコンデンサ11とは、同様の構成を有している。すなわち、コンデンサ10,11は、略直方体状のコンデンサ素体15と、コンデンサ素体15の側面15c,15d(図3参照)に形成された第1の外部電極16及び第2の外部電極17とを備えている。コンデンサ10は、第1のランド電極4及び接続電極8に跨って配置されている。コンデンサ11は、第3のランド電極6及び接続電極9に跨って配置されている。つまり、コンデンサ10の第1の外部電極16は、第1のランド電極4に接続されおり、第2の外部電極17は、接続電極8に接続されている。コンデンサ11の第1の外部電極16は、第3のランド電極6に接続されており、第2の外部電極17は、接続電極9に接続されている。コンデンサ10,11は、はんだ等によって第1及び第3のランド電極4,6、接続電極8,9に実装されている。

【0027】

コンデンサ10とコンデンサ11とは、上記のように配置されることにより、第2の方向において近接して実装されている。具体的には、コンデンサ10とコンデンサ11とは、第1の外部電極16と第2の外部電極17とが対向する方向(第1の方向と同じ方向)が略平行となる。また、コンデンサ10とコンデンサ11とは、実装面の面方向において第1の外部電極16と第2の外部電極17との対向方向に交わる方向、つまり第2の方向から見た場合に、重なるように実装されている。コンデンサ10の第1の外部電極16とコンデンサ11の第1の外部電極16とは、異なる極性に接続されている。

【0028】

フェライトビーズインダクタ12とフェライトビーズインダクタ13とは、同様の構成を有している。すなわち、フェライトビーズインダクタ12,13は、略直方体状のフェライトビーズ素体18と、フェライトビーズ素体18の側面18c,18d(図5参照)に形成された第1の外部電極19及び第2の外部電極20とを備えている。フェライトビーズインダクタ12は、接続電極8と第2のランド電極5とに跨って配置されている。フェライトビーズインダクタ13は、接続電極9と第4のランド電極7とに跨って配置されている。つまり、フェライトビーズインダクタ12の第1の外部電極19は、接続電極8に接続されており、第2の外部電極20は、第2のランド電極5に接続されている。フェライトビーズインダクタ13の第1の外部電極19は、接続電極9に接続されており、第2の外部電極20は、第4のランド電極7に接続されている。フェライトビーズインダクタ12,13は、はんだ等によって第2及び第4のランド電極5,7、接続電極8,9に実装されている。

【0029】

フェライトビーズインダクタ12とフェライトビーズインダクタ13とは、上記のように配置されることにより、第2の方向において近接して実装されている。具体的には、フェライトビーズインダクタ12とフェライトビーズインダクタ13とは、第1の外部電極19と第2の外部電極20とが対向する方向(第1の方向と同じ方向)が略平行となる。また、フェライトビーズインダクタ12とフェライトビーズインダクタ13とは、実装面の面方向において第1の外部電極19と第2の外部電極20との対向方向に交わる方向、つまり第2の方向から見た場合に、重なるように実装されている。フェライトビーズインダクタ12の第1の外部電極19とフェライトビーズインダクタ13の第1の外部電極19とは、異なる極性に接続されている。

【0030】

コンデンサ10,11とフェライトビーズインダクタ12,13とが上記のように配置されることにより、コンデンサ10の第2の外部電極17とフェライトビーズインダクタ12の第1の外部電極19とが対向すると共に、コンデンサ11の第2の外部電極17とフェライトビーズインダクタ13の第1の外部電極19とが対向する。この対向方向は、第1の方向と同方向となる。このように、コンデンサ10とフェライトビーズインダクタ12、及びコンデンサ11とフェライトビーズインダクタ13は、電源ライン1,2の間に直列に実装されている。そして、コンデンサ10,11及びフェライトビーズインダクタ12,13とICチップ3とは、並列接続の関係になる。

【0031】

電子部品の実装構造では、コンデンサ10,11及びフェライトビーズインダクタ12,13において、図1に示す矢印方向に電流がそれぞれ流れる。すなわち、コンデンサ10及びフェライトビーズインダクタ12においては、コンデンサ10側からフェライトビーズインダクタ12側に電流が流れる。コンデンサ11及びフェライトビーズインダクタ13においては、フェライトビーズインダクタ13側からコンデンサ11側に電流が流れる。このとき、隣接するコンデンサ10とコンデンサ11、及びフェライトビーズインダクタ12とフェライトビーズインダクタ13においては、電流が互いに逆向きに流れる。これにより、隣接するコンデンサ10とコンデンサ11、及びフェライトビーズインダクタ12とフェライトビーズインダクタ13とにおいて、磁界が相殺される。そのため、インダクタ成分のESL(Equivalent Series Inductance:等価直列インダクタンス)が低減する。

【0032】

続いて、上記のコンデンサ10,11及びフェライトビーズインダクタ12,13について詳細に説明する。まず、コンデンサ10,11について説明する。図3は、コンデンサを示す斜視図であり、図4は、図3に示すコンデンサの層構成を示す図である。

【0033】

図3,4に示すように、コンデンサ10,11は、積層チップコンデンサである。図3に示すように、コンデンサ10のコンデンサ素体15は、互いに対向する長方形状の第1及び第2の主面15a,15bと、第1及び第2の主面15a,15b間を連結するように第1及び第2の主面15a,15bの長辺方向に伸び且つ互いに対向する第1及び第2の側面15c,15dと、第1及び第2の主面15a,15b間を連結するように第1及び第2の主面15a,15bの短辺方向に伸び且つ互いに対向する第3及び第4の側面15e,15fとを有する。コンデンサ11のコンデンサ素体15も同様の構成を有している。

【0034】

第1の外部電極16は、コンデンサ素体15の第1の側面15c側に形成されている。第1の外部電極16は、第1の側面15c全面を覆うとともに、第1及び第2の主面15a,15b並びに第3及び第4の側面15e,15fの一部を連続して覆う。第2の外部電極17は、コンデンサ素体15の第2の側面15d側に形成されている。第2の外部電極17は、第2の側面15d全面を覆うとともに、第1及び第2の主面15a,15b並びに第3及び第4の側面15e,15fの一部を連続して覆う。すなわち、第1及び第2の外部電極16,17は、コンデンサ素体15の長手方向の側面15c,15dに配置されるように形成されている。

【0035】

コンデンサ素体15は、図4に示されるように、略長方形状の誘電体層21上に第1〜第4の内部電極22a〜22dがそれぞれ形成されてなる複数(ここでは4つ)の複合層23a〜23dと、複合層23a〜23dの最表層に積層され、保護層として機能する誘電体層21とによって形成されている。誘電体層21は、誘電体セラミックを含むセラミックグリーンシートの焼結体からなり、第1〜第4の内部電極22a〜22dは、導電性ペーストの焼結体からなる。実際のコンデンサ素体15では、誘電体層21間の境界が視認できない程度に一体化されている。

【0036】

複合層23aは、誘電体層21上に第1の内部電極22aが形成された層である。複合層23bは、誘電体層21上に第2の内部電極22bが形成された層である。複合層23cは、誘電体層21上に第3の内部電極22cが形成された層である。複合層23dは、誘電体層21上に第4の内部電極22dが形成された層である。第1〜第4の内部電極22a〜22dは、積層方向において誘電体層21を介して交互に配置されている。これにより、第1〜第4の内部電極22a〜22dは、コンデンサ素体15の一部である誘電体層21を間に挟んで対向する。

【0037】

第1の内部電極22aは、長方形状を呈し、コンデンサ素体15の第1及び第2の主面15a,15bの長辺方向とその長辺方向とが平行になるように、コンデンサ素体15内に配置される。第1の内部電極22aは、長方形状を保ったままコンデンサ素体15の第1の側面15cに引き出されるように伸び、第1の外部電極16に電気的且つ機械的に接続される。第1の内部電極22aは、第2〜第4の側面15d〜15fそれぞれからは所定距離離れて配置されている。第1の内部電極22aの第3及び第4の側面15e,15fの対向方向における長さは、第1及び第2の側面15c,15dの対向方向に沿って略一定である。第3の内部電極22cは、第1の内部電極22aと同様の構成を有している。

【0038】

第2の内部電極22bは、長方形状を呈し、コンデンサ素体15の第1及び第2の主面15a,15bの長辺方向とその長辺方向とが平行になるように、コンデンサ素体15内に配置される。第2の内部電極22bは、長方形状を保ったままコンデンサ素体15の第2の側面15dに引き出されるように伸び、第2の外部電極17に電気的且つ機械的に接続される。第2の内部電極22bは、第1、第3及び第4の側面15c,15e,15fそれぞれからは所定距離離れて配置されている。第2の内部電極22bの第3及び第4の側面15e,15fの対向方向における長さは、第1及び第2の側面15c,15dの対向方向に沿って略一定である。第4の内部電極22dは、第2の内部電極22bと同様の構成を有している。

【0039】

続いて、フェライトビーズインダクタ12,13について、図5〜図7を参照しながら詳細に説明する。図5は、フェライトビーズインダクタを示す斜視図であり、図6は、図5におけるVI−VI線断面図であり、図7は、図5に示すフェライトビーズインダクタの層構成を示す図である。

【0040】

図5〜図7に示すように、フェライトビーズインダクタ12,13は、積層チップフェライトビーズインダクタである。図5に示すように、フェライトビーズインダクタ12のフェライトビーズ素体18は、互いに対向する略長方形状の第1及び第2の主面18a,18bと、第1及び第2の主面18a,18b間を連結するように第1及び第2の主面18a,18bの長辺方向に伸び且つ互いに対向する第1及び第2の側面18c,18dと、第1及び第2の主面18a,18b間を連結するように第1及び第2の主面18a,18bの短辺方向に伸び且つ互いに対向する第3及び第4の側面18e,18fとを有する。フェライトビーズインダクタ13のフェライトビーズ素体18も同様の構成を有している。

【0041】

第1の外部電極19は、フェライトビーズ素体18の第1の側面18c側に形成されている。第1の外部電極19は、第1の側面18c全面を覆うとともに、第1及び第2の主面18a,18b並びに第3及び第4の側面18e,18fの一部を連続して覆う。第2の外部電極20は、フェライトビーズ素体18の第2の側面18d側に形成されている。第2の外部電極20は、第2の側面18d全面を覆うとともに、第1及び第2の主面18a,18b並びに第3及び第4の側面18e,18fの一部を連続して覆う。すなわち、第1及び第2の外部電極19,20は、フェライトビーズ素体18の長手方向の側面18c,18dに配置されるように形成されている。フェライトビーズインダクタ12,13の第1及び第2の外部電極19,20の幅寸法は、コンデンサ10,11の第1及び第2の外部電極16,17の幅寸法と同等となっている。

【0042】

図6及び図7に示すように、フェライトビーズ素体18は、略長方形状の磁性体層24上に第1〜第4の内部電極25a〜25dがそれぞれ形成されてなる複数(ここでは4つ)の複合層26a〜26dと、複合層26a〜26dの最表層に積層され、保護層として機能する磁性体層24とによって形成されている。磁性体層24は、主成分としてフェライト材料を含むシートの焼結体からなり、第1〜第4の内部電極25a〜25dは、導電性ペーストの焼結体からなる。実際のフェライトビーズ素体18では、磁性体層24間の境界が視認できない程度に一体化されている。

【0043】

複合層26aは、磁性体層24上に第1の内部電極25aが形成された層である。複合層26bは、磁性体層24上に第2の内部電極25bが形成された層である。複合層26cは、磁性体層24上に第3の内部電極25cが形成された層である。複合層26dは、磁性体層24上に第4の内部電極25dが形成された層である。第1〜第4の内部電極25a〜25dは、積層方向に磁性体層24を介して順に積層されている。これにより、第1〜第4の内部電極25a〜25dがフェライトビーズ素体18の一部である磁性体層24の間に挟まれるように配置される。

【0044】

第1の内部電極25aは、第1及び第2の側面18c,18dの対向方向(第1及び第2の主面18a,18bの短辺方向と平行)に伸びる長方形状の一部にスリット状の空隙27a〜27cを設けたものである。この第1の内部電極25aは、フェライトビーズ素体18の第1及び第2の側面18c,18dの両方に引き出されるように伸び、第1の外部電極19及び第2の外部電極20に電気的且つ機械的に接続される。第1の内部電極25aは、第3及び第4の側面18e,18fからは所定距離離れて配置されている。この離れた部分は、磁性体層24上におけるギャップ部分28e,28fに相当し、このギャップ部分28e,28f以外の部分が、磁性体層24上において内部電極の面積を最大限に形成することが可能な内部電極領域Sとなる(図8参照)。

【0045】

導電性ペーストが配置されていない空隙27a〜27cそれぞれは、第1及び第2の側面18c,18dの対向方向がその長手方向となる長方形状(短冊状)を呈しており、積層方向からみた際に、上述した内部電極領域S内に位置するように形成されている。空隙27a,27cは、その一端が第1の側面18c側に露出するように第1の側面18c寄りに形成され、空隙27bは、その一端が第2の側面18d側に露出するように第2の側面18d寄りに形成される。第2〜第4の内部電極25b〜25dは、第1の内部電極25aと同様の構成を有している。第1〜第4の内部電極25a〜25dの各空隙27a〜27cは、複合層26a〜26dと最表層の磁性体層24とが積層されてフェライトビーズインダクタ12,13が形成された際、積層方向に隣接する磁性体層24同士が接合する接合部となり、両者の密着性を向上させるように機能する。

【0046】

図9は、本実施形態における実装構造の等価回路図である。図9に示すように、コンデンサ10,11は、静電容量C1,C2を形成する。フェライトビーズインダクタ12,13は、直列に接続されたインダクタ成分L1,L2と抵抗成分R1,R2とを形成する。そして、インダクタ成分L1,L2及び抵抗成分R1,R2の合成成分は、コンデンサ10,11の静電容量C1,C2と直列に電源ライン1,2の間に接続される。フェライトビーズインダクタ12,13は、低周波帯域においてはインダクタ成分L1,L2が主として作用し、高周波帯域においては抵抗成分R1,R2が主として作用する。

【0047】

以上説明したように、本実施形態に係る電子部品の実装構造では、コンデンサ10,11とフェライトビーズインダクタ12,13とが直列となるように電源ライン1,2間に接続されるので、フェライトビーズインダクタ12,13の抵抗成分R1,R2がコンデンサ10,11の等価直列抵抗(ESR:Equivalent Series Resistance)として作用する。フェライトビーズインダクタ12,13の抵抗成分R1,R2は、直流抵抗成分と高周波帯域で増加する損失との和で構成される。したがって、この実装構造によれば、高周波帯域における抵抗成分を増加させることができる。

【0048】

また、この実装構造では、フェライトビーズインダクタ12,13は、電流の流れる方向が互いに逆向きとなるように実装されているため、磁界が相殺される。そのため、高周波帯域においてESLが更に低減するため、高周波ノイズの反射を防止することが可能となり、高周波ノイズを抵抗成分で熱変換して好適に除去することが可能となる。一方、フェライトビーズインダクタ12,13は、低周波帯域では抵抗成分よりもむしろインダクタ成分が機能するため、上記実装構造によって低周波帯域でインピーダンスを小さく保つことが可能となる。そして、低周波ノイズに対しては、コンデンサ10,11を実装しているため、このコンデンサ10,11でその低周波ノイズが吸収され、好適に除去することができる。

【0049】

また、この実装構造に用いられるフェライトビーズインダクタ12,13では、第1及び第2の外部電極19,20の幅を広くできると共に内部電極25a〜25dの長さを短くすることができるので、ビーズインダクタの抵抗成分の1つである直流抵抗成分を小さくすることができる。つまり、このフェライトビーズインダクタ12,13を用いることにより、低周波帯域では更に低ESRとすることができ、高周波帯域では高ESRとすることができる。

【0050】

しかも、これらフェライトビーズインダクタ12,13では、第1〜第4の内部電極25a〜25dを形成可能な内部電極領域S内に、積層方向に隣接する磁性体層24同士が接合する接合部のための空隙27a〜27cが形成されている。このため、上記構成のフェライトビーズインダクタ12,13によれば、低周波帯域での低ESRや高周波帯域での高ESRを実現しつつ、更に、磁性体層24の層間はがれを防止して、ビーズインダクタの内部欠陥の発生を抑えることもできる。

【0051】

ここで、上述したフェライトビーズインダクタ12,13の作用効果についてより具体的に説明する。図8に示すように、磁性体層24上における内部電極領域Sの面積をS0とし、磁性体層24上における空隙27a〜27cの総面積をS1とした場合において、内部電極領域Sと空隙27a〜27cとの面積比であるS1/S0がどの範囲にある場合に直流抵抗成分が小さくなり且つ内部構造欠陥の発生が抑えられるかについて、表1に示すように確認した。確認対象のサンプルとしては、外形寸法Lが0.8mm、Wが1.6mm(L0.8×W1.6、表1のNo.1〜No.7)のものと、外形寸法Lが1.2mm、Wが2.0mm(L1.2mm×W2.0mm、表1のNo.8〜No.14)のものとを用いた。

【0052】

【表1】

【0053】

この確認試験では、それぞれのサンプル数nを100個とし、面積比S1/S0を変更させた場合における、層間剥がれなどによる内部構造欠陥の発生数と直流抵抗Rdc(mΩ)とを求めた。その結果、表1に示すように、No.1〜No.14の何れのサンプルにおいても、内部構造欠陥の発生数を0個/100個〜数個/100個程度に抑えることができた。特に、面積比S1/S0が0.20よりも大きい場合には、内部構造結果の発生数が0個/100個、即ち内部構造欠陥がないといった顕著な効果を得ることができた。

【0054】

また、表1に示すように、No.1〜No.14の何れのサンプルにおいても、直流抵抗Rdcを低めに抑えることができたが、特に、面積比S1/S0が0.67以下の場合に、直流抵抗が低いと認定される指標の1つである「10mΩ」よりも更に低い直流抵抗Rdcを実現できるといった顕著な効果を得ることができた。

【0055】

このように、磁性体層24上における内部電極領域Sの面積をS0とし、磁性体層24上における空隙27a〜27cの総面積をS1とした場合において、特に、内部電極領域Sと空隙27a〜27cとの面積比であるS1/S0が0.20よりも大きく且つ0.67以下となるようにすることにより、低周波帯域での低ESRや高周波帯域での高ESRを実現でき、且つ、磁性体層24の層間はがれを防止してフェライトビーズインダクタ12,13の内部構造欠陥の発生を抑えることもできるといった顕著な効果を奏することができる。

【0056】

また、フェライトビーズインダクタ12,13では、第1及び第2の外部電極19,20は、それぞれ一の外部電極からなっている。このため、外部電極19,20における抵抗値を更に下げることができるため、フェライトビーズインダクタ12,13の直流抵抗成分を更に小さくすることができる。

【0057】

なお、コンデンサ10,11の第1及び第2の外部電極16,17の幅寸法は、フェライトビーズインダクタ12,13の第1及び第2の外部電極19,20の幅寸法と同等となっている。コンデンサ10,11の第1及び第2の外部電極16,17の幅寸法と、フェライトビーズインダクタ12,13の第1及び第2の外部電極19,20の幅寸法とが異なる場合、高周波電流が第1及び第2の外部電極16,17と第1及び第2の外部電極19,20との間にて反射し、高周波電流がフェライトビーズインダクタ12,13の抵抗成分R1,R2において熱に変換されないといった不具合が生じ、ノイズの除去効果が低下するといった問題があり得る。

【0058】

しかしながら、本実施形態では、第1及び第2の外部電極16,17と第1及び第2の外部電極19,20との幅寸法が同等となっていることにより、第1及び第2の外部電極16,17と第1及び第2の外部電極19,20との間の高周波電流の反射を防止でき、フェライトビーズインダクタ12,13におけるノイズの除去効果の向上を図ることができる。

【0059】

また、コンデンサ10,11において、第1及び第2の外部電極16,17がコンデンサ素体15の第1及び第2の側面15c,15d側に形成されている。第1及び第2の側面15c,15dは、コンデンサ素体15の長手方向の側面である。このため、コンデンサ10,11では、ESLをより低減させることができる。

【0060】

[第2実施形態]

次に、第2実施形態に係るフェライトビーズインダクタ12,13について説明する。本実施形態に係るフェライトビーズインダクタ12,13では、第1〜第4の内部電極35a〜35dの形状が第1実施形態の内部電極25a〜25dと異なっている。以下、第一実施形態と異なる点を中心に説明する。

【0061】

図10に示すように、フェライトビーズインダクタ12,13のフェライトビーズ素体18は、略長方形状の磁性体層24上に第1〜第4の内部電極35a〜35dがそれぞれ形成されてなる複数の複合層36a〜36dと、複合層36a〜36dの最表層に積層され、保護層として機能する磁性体層24とによって形成されている。複合層36a〜36dのそれぞれは、磁性体層24上に第1〜第4の内部電極35a〜35dそれぞれが形成された層である。第1〜第4の内部電極35a〜35dは、積層方向に磁性体層24を介して順に積層され、これにより、第1〜第4の内部電極35a〜35dのそれぞれが磁性体層24の間に挟まれるように配置される。

【0062】

第1の内部電極35aは、第1及び第2の側面18c,18dの対向方向に伸びる長方形状の一部に、それぞれ長方形状を呈する9つの空隙37a〜37iを設けて、梯子形状とした電極である。第1の内部電極35aは、フェライトビーズ素体18の第1及び第2の側面18c,18dの両方に引き出されるように伸び、第1実施形態と同様に、第1及び第2の外部電極19,20に電気的且つ機械的に接続される。第1の内部電極35aは、第3及び第4の側面18e,18fからは所定距離離れて配置されている。

【0063】

空隙37a〜37iは、第1の側面18cから第2の側面18dに向かって、空隙37a,37b,37cの順に、空隙37d,37e,37fの順に、空隙37g,37h,37iの順に、3列になるように配置されている。空隙37a〜37iは、第1実施形態と同様、積層方向からみて、内部電極領域S内に位置するように配置されている。空隙37a,37d,37gは、その一端が第1の側面18c側に露出するよう形成され、空隙37c,37f,37iは、その一端が第2の側面18d側に露出するよう形成され、空隙37b,37e,37hは、第1及び第2の側面18c,18dのいずれにも露出せずこれら側面18c,18dの対向方向の中央部に位置するように形成されている。第2〜第4の内部電極35b〜35dは、第1の内部電極35aと同様の構成を有している。

【0064】

以上説明したように、本実施形態に係るフェライトビーズインダクタ12,13では、第1実施形態と同様、ビーズインダクタの抵抗成分の1つである直流抵抗成分を小さくできることに加え、内部電極35a〜35dが、その形状が梯子状となるように内部電極領域S内に9つの空隙37a〜37iを有する構成となっているため、積層方向に隣接する磁性体層24同士をより確実に接合させることができる。その結果、本実施形態によれば、磁性体層24の層間はがれを防止して、ビーズインダクタの内部欠陥の発生を抑えることができる。

【0065】

[第3実施形態]

次に、第3実施形態に係るフェライトビーズインダクタ12,13について説明する。本実施形態に係るフェライトビーズインダクタ12,13では、第1〜第4の内部電極45a〜45dの形状が第1実施形態の内部電極25a〜25dと異なっている。以下、第一実施形態と異なる点を中心に説明する。

【0066】

図11に示すように、フェライトビーズインダクタ12,13のフェライトビーズ素体18は、略長方形状の磁性体層24上に第1〜第4の内部電極45a〜45dがそれぞれ形成されてなる複数の複合層46a〜46dと、複合層46a〜46dの最表層に積層され、保護層として機能する磁性体層24とによって形成されている。複合層46a〜46dのそれぞれは、各磁性体層24上に4つの第1〜第4の内部電極45a〜45dそれぞれが形成された層である。つまり、一の磁性体層24の上に分割された複数(4つ)の内部電極45a〜45dが配置されている。

【0067】

第1の内部電極45aのそれぞれは、第1及び第2の側面18c,18dの対向方向に伸びる長方形状(短冊状)を呈した電極である。第1の内部電極45aは、フェライトビーズ素体18の第1及び第2の側面18c,18dの両方に引き出されるように伸び、第1及び第2の外部電極19,20に電気的且つ機械的に接続される。第1の内部電極45aそれぞれの間には空隙47a〜47cが形成されており、また、第3及び第4の側面18e,18fの対向方向外側に位置する第1の内部電極45aは、第3及び第4の側面18e,18fからは所定距離離れて配置されている。

【0068】

空隙47a〜47cは、第1及び第2の側面18c,18dの対向方向に伸びる長方形状(短冊状)を呈したスリット状の空隙であり、第1実施形態等と同様、積層方向からみて、内部電極領域S内に位置するように配置されている。各空隙47a〜47cは、第1及び第2の側面18c,18d側に露出するよう形成されている。第2〜第4の内部電極45b〜45d及び内部電極間の空隙は、第1の内部電極45a及び第1の内部電極45a間の空隙47a〜47cと同様の構成となっている。

【0069】

以上説明したように、本実施形態に係るフェライトビーズインダクタ12,13では、第1実施形態等と同様、ビーズインダクタの抵抗成分の1つである直流抵抗成分を小さくできることに加え、内部電極45a〜45dの間に形成される空隙47a〜47cを内部電極領域S内に有する構成となっているため、積層方向に隣接する磁性体層24同士をより確実に接合させることができる。その結果、本実施形態によれば、磁性体層24の層間はがれを防止して、ビーズインダクタの内部欠陥の発生を抑えることができる。

【0070】

[第4実施形態]

次に、第4実施形態に係るフェライトビーズインダクタ12,13について説明する。本実施形態に係るフェライトビーズインダクタ12,13では、第1〜第4の内部電極53a〜53dの形状及び積層方向における配置箇所が第1実施形態の内部電極25a〜25dと異なっている。以下、第一実施形態と異なる点を中心に説明する。

【0071】

図12及び図13に示すように、本実施形態に係るフェライトビーズインダクタ12,13のフェライトビーズ素体18は、略長方形状の磁性体層24上に内部電極53a〜53dが形成されてなる複数の複合層54a〜54dと、複合層54a〜54dの最表層に積層され、保護層として機能する磁性体層24とによって形成されている。

【0072】

複合層54aは、磁性体層24上に複数(ここでは2つ)の内部電極53a,53bが形成された層である。内部電極53aは、長方形状を呈し、フェライトビーズ素体18の第1及び第2の主面18a,18bの短辺方向とその長辺方向とが平行になるように、磁性体層24上に形成されている。内部電極53aは、フェライトビーズ素体18の第1及び第2の側面18c,18dに引き出されるように伸び、第1及び第2の外部電極19,20に電気的且つ機械的に接続される。内部電極53bは、長方形状を呈し、フェライトビーズ素体18の第1及び第2の主面18a,18bの短辺方向とその長辺方向とが平行になるように、磁性体層24上に形成されている。

【0073】

内部電極53bは、内部電極53aよりもフェライトビーズ素体18の第1及び第2の主面18a,18bの長辺方向における幅寸法が大きい。内部電極53bは、フェライトビーズ素体18の第1及び第2の側面18c,18dに引き出されるように伸び、第1及び第2の外部電極19,20に電気的且つ機械的に接続される。内部電極53aと内部電極53bとの間には空隙57aが形成されており、また、内部電極53bとギャップ部分28fとの間には空隙57bが形成されている。複合層54cは、複合層54aと同様の構成を有している。

【0074】

複合層54bは、磁性体層24上に複数(ここでは2つ)の内部電極53c,53dが形成された層である。内部電極53cは、長方形状を呈し、フェライトビーズ素体18の第1及び第2の主面18a,18bの短辺方向とその長辺方向とが平行になるように、磁性体層24上に形成されている。内部電極53cは、フェライトビーズ素体18の第1及び第2の側面18c,18dに引き出されるように伸び、第1及び第2の外部電極19,20に電気的且つ機械的に接続される。内部電極53dは、長方形状を呈し、フェライトビーズ素体18の第1及び第2の主面18a,18bの短辺方向とその長辺方向とが平行になるように、磁性体層24上に形成されている。

【0075】

内部電極53dは、内部電極53cよりもフェライトビーズ素体18の第1及び第2の主面18a,18bの長辺方向における幅寸法が小さい。内部電極53dは、フェライトビーズ素体18の第1及び第2の側面18c,18dに引き出されるように伸び、第1及び第2の外部電極19,20に電気的且つ機械的に接続される。内部電極53cと内部電極53dとの間には空隙57dが形成されており、内部電極53cとギャップ部分28eとの間には空隙57cが形成されている。複合層54dは、複合層54bと同様の構成を有している。

【0076】

フェライトビーズ素体18において、内部電極53a,53bは、積層方向において磁性体層24を介して対向して配置されており、内部電極53c,53dは、積層方向において磁性体層24を介して対向して配置されている。つまり、複合層54a,54cの内部電極53a,53bは、積層方向において複合層54b,54dの内部電極53c,53dと重ならない位置に配置されている。

【0077】

以上説明したように、本実施形態に係るフェライトビーズインダクタ12,13では、このような構成により、積層方向において内部電極53a〜53dが磁性体層24を介して交互に積層されている。これにより、フェライトビーズインダクタ12,13では、第1実施形態等と同様、ビーズインダクタの抵抗成分の1つである直流抵抗成分を小さくできることに加え、内部電極53a〜53dの間等に形成される空隙57a〜57dを内部電極領域S内に有する構成となっているため、積層方向に隣接する磁性体層24同士をより確実に接合させることができる。その結果、本実施形態によれば、磁性体層24の層間はがれを防止して、ビーズインダクタの内部欠陥の発生を抑えることができる。

【0078】

本発明は、上記実施形態に限定されるものではない。例えば、上述したフェライトビーズインダクタ12,13では、4つの複合層からフェライトビーズ素体が構成される例を示したが、これに限定されるわけではなく、例えば6つの複合層から構成されるようにしてもよい。また、上述した電子部品の実装構造において、コンデンサ及びフェライトビーズインダクタの実装数は設計に応じて適宜変更することができる。例えば、図14に示すように、コンデンサ10,11及びフェライトビーズインダクタ12,13をそれぞれ4つずつ実装させることができる。このような構成においても、コンデンサ10,11及びフェライトビーズインダクタ12,13が電源ライン1,2間に直列に接続されていると共に、フェライトビーズインダクタ12,13において磁界が相殺されるため、ESLを低減することができる。したがって、低周波帯域において低インピーダンスを保ちつつ、高周波帯域において高インピーダンスとすることができる。

【0079】

また、図15に示すような実装構造を採用することもできる。すなわち、この実装構造では、電極パターンとして、配線1aが第1のランド電極60に接続され、配線2aが第2のランド電極61に接続され、第1のランド電極60と同一直線上に第3のランド電極62が設けられ、第2のランド電極61と同一直線上に第4のランド電極63が設けられる。第3のランド電極62は、ビアホールH3を介して第1のランド電極60と電気的に接続され、第4のランド電極63は、ビアホールH4を介して第2のランド電極61と電気的に接続される。また、第1及び第3のランド電極60,62の間や第2及び第4のランド電極61,63の間には接続電極64が設けられる。

【0080】

そして、このような電極パターンへの実装にあたり、コンデンサ10が第1のランド電極60及び接続電極64に跨って配置され、コンデンサ11が接続電極64及び第3のランド電極62に跨って配置される。また、フェライトビーズインダクタ12が第2のランド電極61と接続電極64とに跨って配置され、フェライトビーズインダクタ13が接続電極64と第4のランド電極63とに跨って配置される。この配置により、この実装構造においても、コンデンサ10,11とフェライトビーズインダクタ12,13とが電源ライン1,2の間に直列に実装され、コンデンサ10,11及びフェライトビーズインダクタ12,13とICチップ3とが並列接続の関係になるようにすることができる。しかも、この実装構造では、図15に示す矢印方向に電流が流れるため、フェライトビーズインダクタ12,13において磁界が相殺されるため、ESLを低減することができる。

【符号の説明】

【0081】

1,2…電源ライン、10,11…コンデンサ、12,13…フェライトビーズインダクタ、18…フェライトビーズ素体、18a,18b…第1及び第2の主面、18c〜18f…第1〜第4の側面、19…第1の外部電極、20…第2の外部電極、25a〜25d,35a〜35d,45a〜45d,53a〜53d…内部電極、27a〜27c,37a〜37i,47a〜47c,57a〜57d…空隙。

【技術分野】

【0001】

本発明は、積層型電子部品及び当該積層型電子部品を含む電子部品の実装構造に関する。特に本発明は、積層ビーズインダクタ及び当該積層ビーズインダクタと積層コンデンサとの実装構造に関する。

【背景技術】

【0002】

電源や信号等の配線を介したノイズの漏洩や侵入を防止するためのノイズフィルタとして、例えば特許文献1に記載のインダクタとコンデンサとが組み合わされた電子部品が従来知られている。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開2007−234755号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

近年、電子機器の高周波化に伴い、電子機器に用いられる部品についても高周波化に対応することが求められている。しかしながら、上記特許文献1に記載された従来の電子部品では、高周波に対応すべく高周波帯域での抵抗成分を大きくすると、低周波帯域での直流抵抗も含め、全帯域での抵抗、ひいてはインピーダンスが大きくなってしまう。

【0005】

そこで、本願出願人は、例えば、特願2010−279010号において、低周波帯域において低インピーダンスを保ちつつ、高周波帯域において高インピーダンスとすることができる電子部品の実装構造を提案している。そして、このような実装構造に適した電子部品が望まれている。

【0006】

本発明は、低周波帯域において低インピーダンスを保ちつつ、高周波帯域において高インピーダンスとすることができる実装構造などに適した積層型電子部品、及び、当該積層型電子部品を含む電子部品の実装構造を提供することを目的とする。

【課題を解決するための手段】

【0007】

上記課題を解決するために、本発明に係る積層型電子部品は、磁性体層の間に内部電極が配置されるように磁性体層と内部電極とが積層され、且つ、互いに対向する略長方形状の第1及び第2の主面と、第1及び第2の主面間を連結するように第1及び第2の主面の長辺方向に伸び且つ互いに対向する第1及び第2の側面と、第1及び第2の主面間を連結するように第1及び第2の主面の短辺方向に伸び且つ互いに対向する第3及び第4の側面とを有する素体と、素体の第1の側面に配置される第1の外部電極と、素体の第2の側面に配置される第2の外部電極とを備えている。この積層型電子部品では、内部電極は、長辺よりも短い短辺の方向に伸びて第1及び第2の外部電極に接続され、素体は、磁性体層上において内部電極を形成可能な内部電極領域内に、積層方向に隣接する磁性体層同士が接合する接合部を有するようになっている。

【0008】

また、本発明に係る電子部品の実装構造は、電流を供給するための電源ラインに接続される電子部品の実装構造であって、電子部品として、コンデンサと上記構成の積層型電子部品であるビーズインダクタとを備え、電源ラインの間に、コンデンサとビーズインダクタとが直列となるように実装される。

【0009】

この実装構造によれば、コンデンサとビーズインダクタとが直列となるように電源ライン間に接続されるので、ビーズインダクタの抵抗成分がコンデンサの等価直列抵抗(ESR:Equivalent Series Resistance)として作用する。ビーズインダクタの抵抗成分は、直流抵抗成分と高周波帯域で増加する損失との和で構成される。よって、この実装構造によれば、高周波帯域でのインピーダンスを増加させることが可能になり、高周波ノイズを好適に除去することが可能となる。一方、ビーズインダクタは、低周波帯域では抵抗成分よりもむしろインダクタ成分が機能するため、上記実装構造によれば低周波帯域ではインピーダンスを小さく保つことが可能となる。そして、低周波ノイズに対しては、コンデンサを実装しているため、当該コンデンサでその低周波ノイズは吸収され好適に除去することができる。

【0010】

ところで、このビーズインダクタでは、第1及び第2の側面に両外部電極が配置されるので第1及び第2の外部電極の幅を広くでき、しかも、内部電極が短辺方向に伸びて両外部電極に接続する構成となっているので内部電極の長さを短くすることができる。このため、上記実装構造等に対して本発明に係るビーズインダクタを用いた場合、ビーズインダクタの抵抗成分の構成の1つである直流抵抗成分を小さくすることができる。つまり、このビーズインダクタを用いることにより、低周波帯域では更に低ESRとすることができ、高周波帯域では高ESRとすることができる。

【0011】

しかも、上記構成のビーズインダクタでは、内部電極を形成可能な内部電極領域内に、積層方向に隣接する磁性体層同士が接合する接合部を有する構成としている。このため、このビーズインダクタによれば、低周波帯域での低ESR等を実現できるだけでなく、更に、接合部の存在により磁性体層の層間はがれを防止してビーズインダクタの内部欠陥の発生を抑えることもできる。

【0012】

また、上記のビーズインダクタでは、磁性体層上における内部電極領域の面積をS0とし、磁性体層上における接合部の面積をS1とした場合において、内部電極領域と接合部との面積比であるS1/S0が0.20よりも大きく且つ0.67以下であることが好ましい。この場合、ビーズインダクタの直流抵抗を低めに抑えつつ、磁性体層同士の密着性を更に向上させて、層間はがれ等による内部欠陥の発生を一層抑えることができる。

【0013】

また、上記のビーズインダクタでは、内部電極は、磁性体層上において、複数の内部電極に分割されていることが好ましい。この場合、磁性体層同士の密着性を更に向上させて、層間はがれ等による内部欠陥の発生を一層抑えることができる。

【0014】

また、上記のビーズインダクタでは、異なる磁性体層上に配置された内部電極のそれぞれは、積層方向において、その間に位置する磁性体層を介して対向しないように配置されていることが好ましい。この場合、磁性体層同士の密着性を更に向上させて、層間はがれ等による内部欠陥の発生を一層抑えることができる。

【0015】

また、上記のビーズインダクタでは、第1及び第2の外部電極は、それぞれ一の外部電極からなることが好ましい。この場合、外部電極における抵抗値を更に下げることができるため、ビーズインダクタの直流抵抗成分を更に小さくすることができる。

【0016】

また、上記実装構造において、コンデンサは、誘電体層と内部電極とが積層され、且つ、互いに対向する略長方形状の第1及び第2の主面と、第1及び第2の主面間を連結するように第1及び第2の主面の長辺方向に伸び且つ互いに対向する第1及び第2の側面と、第1及び第2の主面間を連結するように第1及び第2の主面の短辺方向に伸び且つ互いに対向する第3及び第4の側面とを有するコンデンサ素体と、コンデンサ素体の第1の側面側に配置される第1のコンデンサ外部電極と、コンデンサ素体の第2の側面側に配置される第2のコンデンサ外部電極とを備えていることが好ましい。この場合、長辺方向に伸びる第1及び第2の側面にコンデンサ外部電極が配置されるので、等価直列インダクタンス(ESL:Equivalent Series Inductance)を低減させることができる。そして、低ESLとなることから、この実装構造によれば、不要ノイズをインダクタに確実に流すことが可能となり、不要ノイズを熱変換によって、より確実に除去できる。

【0017】

また、上記実装構造において、コンデンサの第1及び第2のコンデンサ外部電極の幅寸法は、ビーズインダクタの第1及び第2の外部電極の幅寸法と略同等であることが好ましい。コンデンサとビーズインダクタとの外部電極の幅寸法が異なる場合、高周波電流がコンデンサの外部電極とビーズインダクタの外部電極との間にて反射し、高周波電流がビーズインダクタの抵抗成分において熱に変換されないといった不具合が生じ、ノイズの除去効果が低下するといった問題がある。そこで、コンデンサとビーズインダクタとの外部電極の幅寸法を同等とすることで、高周波電流の反射を防止でき、ビーズインダクタにおけるノイズの除去効果の向上を図ることができる。

【0018】

また、上記実装構造において、ビーズインダクタを複数有し、各ビーズインダクタは、互いの磁界が相殺されるように実装されていることが好ましい。つまり、ビーズインダクタは、電流の流れる方向が互いに逆向きとなるように実装されていることが好ましい。この場合、ビーズインダクタにおけるESLが低減するため、高周波ノイズの反射を防止することが可能となり、高周波ノイズを抵抗成分で熱変換して好適に除去することが可能となる。

【発明の効果】

【0019】

本発明によれば、低周波帯域において低インピーダンスを保ちつつ、高周波帯域において高インピーダンスとすることができる実装構造などに適した積層型電子部品、及び、当該積層型電子部品を含む電子部品の実装構造を提供することができる。

【図面の簡単な説明】

【0020】

【図1】第1実施形態に係る電子部品の実装構造を概略的に示す図である。

【図2】図1に示す電子部品の実装構造の断面図である。

【図3】図1に示す実装構造に用いられるコンデンサを示す斜視図である。

【図4】図3に示すコンデンサの層構成を示す図である。

【図5】図1に示す実装構造に用いられるフェライトビーズインダクタを示す斜視図である。

【図6】図5に示すフェライトビーズインダクタのVI−VI線断面図である。

【図7】図5に示すフェライトビーズインダクタの層構成を示す図である。

【図8】フェライトビーズインダクタにおける内部電極領域や接合部を示す図である。

【図9】電子部品の実装構造の等価回路図である。

【図10】第2実施形態に係るフェライトビーズインダクタの層構成を示す図である。

【図11】第3実施形態に係るフェライトビーズインダクタの層構成を示す図である。

【図12】第4実施形態に係るフェライトビーズインダクタを示す図である。

【図13】図12に示すフェライトビーズインダクタの層構成を示す図である。

【図14】他の形態の電子部品の実装構造を概略的に示す図である。

【図15】他の形態の電子部品の実装構造を概略的に示す図である。

【発明を実施するための形態】

【0021】

以下、添付図面を参照して、本発明の好適な実施形態について詳細に説明する。なお、説明において、同一要素又は同一機能を有する要素には、同一符号を用いることとし、重複する説明は省略する。

【0022】

[第1実施形態]

まず、第1実施形態に係る電子部品の実装構造について説明する。図1は、第1実施形態に係る電子部品の実装構造を示す図である。図2は、図1に示す電子部品の実装構造の断面図である。各図に示すように、電子部品の実装構造では、電源供給用流路を形成する2本の電源ライン1,2、IC(Integrated Circuit)チップ3、第1〜第4のランド電極4〜7及び接続電極8,9が配置された回路に電子部品を実装する。電子部品の実装構造では、電源ライン1,2に接続される電子部品として、複数のコンデンサ(チップコンデンサ)10,11と、複数のフェライトビーズインダクタ12,13とを実装する。コンデンサ10,11及びフェライトビーズインダクタ12,13は、それぞれ2つ実装される。コンデンサ10,11とフェライトビーズインダクタ12,13とは、電源ライン1,2間に直列に接続されている。

【0023】

電源ライン1,2は、ICチップ3の端子電極3a,3bにそれぞれ接続されている。電源ライン1から分岐した配線1aは、第1のランド電極4に接続されており、電源ライン2から分岐した配線2aは、第2のランド電極5に接続されている。第1のランド電極4と第2のランド電極5とは、対向して配置されている。第1のランド電極4と第2のランド電極5との間には、配線1a,2aに接続されない接続電極8が設けられている。第1のランド電極4、第2のランド電極5及び接続電極8は、一直線上に配置されている。

【0024】

第1のランド電極4、接続電極8及び第2のランド電極5が配置された方向(以下、第1の方向)と面方向において略直角に交わる方向(以下、第2の方向)において、第1のランド電極4の隣(図示右側)には、所定の間隔をあけて第3のランド電極6が並設されている。また、第2のランド電極5の隣(図示右側)には、所定の間隔をあけて第4のランド電極7が並設されている。第3のランド電極6と第4のランド電極7との間には、接続電極8の隣に所定の間隔をあけて接続電極9が並設されている。なお、第1〜第4のランド電極4〜7及び接続電極8,9は、矩形状を呈している。

【0025】

図1及び図2に示すように、第4のランド電極7は、ビアホールH1を介して第1のランド電極4と電気的に接続される。第3のランド電極6は、ビアホールH2を介して第2のランド電極5と電気的に接続される。このような構成により、第1のランド電極4と第4のランド電極7とは、同極性(+極性)となり、第2のランド電極5と第3のランド電極6とは、同極性(−極性)となる。つまり、第2の方向において隣接する第1のランド電極4と第3のランド電極6、第2のランド電極5と第4のランド電極7は、異極性となる。

【0026】

コンデンサ10とコンデンサ11とは、同様の構成を有している。すなわち、コンデンサ10,11は、略直方体状のコンデンサ素体15と、コンデンサ素体15の側面15c,15d(図3参照)に形成された第1の外部電極16及び第2の外部電極17とを備えている。コンデンサ10は、第1のランド電極4及び接続電極8に跨って配置されている。コンデンサ11は、第3のランド電極6及び接続電極9に跨って配置されている。つまり、コンデンサ10の第1の外部電極16は、第1のランド電極4に接続されおり、第2の外部電極17は、接続電極8に接続されている。コンデンサ11の第1の外部電極16は、第3のランド電極6に接続されており、第2の外部電極17は、接続電極9に接続されている。コンデンサ10,11は、はんだ等によって第1及び第3のランド電極4,6、接続電極8,9に実装されている。

【0027】

コンデンサ10とコンデンサ11とは、上記のように配置されることにより、第2の方向において近接して実装されている。具体的には、コンデンサ10とコンデンサ11とは、第1の外部電極16と第2の外部電極17とが対向する方向(第1の方向と同じ方向)が略平行となる。また、コンデンサ10とコンデンサ11とは、実装面の面方向において第1の外部電極16と第2の外部電極17との対向方向に交わる方向、つまり第2の方向から見た場合に、重なるように実装されている。コンデンサ10の第1の外部電極16とコンデンサ11の第1の外部電極16とは、異なる極性に接続されている。

【0028】

フェライトビーズインダクタ12とフェライトビーズインダクタ13とは、同様の構成を有している。すなわち、フェライトビーズインダクタ12,13は、略直方体状のフェライトビーズ素体18と、フェライトビーズ素体18の側面18c,18d(図5参照)に形成された第1の外部電極19及び第2の外部電極20とを備えている。フェライトビーズインダクタ12は、接続電極8と第2のランド電極5とに跨って配置されている。フェライトビーズインダクタ13は、接続電極9と第4のランド電極7とに跨って配置されている。つまり、フェライトビーズインダクタ12の第1の外部電極19は、接続電極8に接続されており、第2の外部電極20は、第2のランド電極5に接続されている。フェライトビーズインダクタ13の第1の外部電極19は、接続電極9に接続されており、第2の外部電極20は、第4のランド電極7に接続されている。フェライトビーズインダクタ12,13は、はんだ等によって第2及び第4のランド電極5,7、接続電極8,9に実装されている。

【0029】

フェライトビーズインダクタ12とフェライトビーズインダクタ13とは、上記のように配置されることにより、第2の方向において近接して実装されている。具体的には、フェライトビーズインダクタ12とフェライトビーズインダクタ13とは、第1の外部電極19と第2の外部電極20とが対向する方向(第1の方向と同じ方向)が略平行となる。また、フェライトビーズインダクタ12とフェライトビーズインダクタ13とは、実装面の面方向において第1の外部電極19と第2の外部電極20との対向方向に交わる方向、つまり第2の方向から見た場合に、重なるように実装されている。フェライトビーズインダクタ12の第1の外部電極19とフェライトビーズインダクタ13の第1の外部電極19とは、異なる極性に接続されている。

【0030】

コンデンサ10,11とフェライトビーズインダクタ12,13とが上記のように配置されることにより、コンデンサ10の第2の外部電極17とフェライトビーズインダクタ12の第1の外部電極19とが対向すると共に、コンデンサ11の第2の外部電極17とフェライトビーズインダクタ13の第1の外部電極19とが対向する。この対向方向は、第1の方向と同方向となる。このように、コンデンサ10とフェライトビーズインダクタ12、及びコンデンサ11とフェライトビーズインダクタ13は、電源ライン1,2の間に直列に実装されている。そして、コンデンサ10,11及びフェライトビーズインダクタ12,13とICチップ3とは、並列接続の関係になる。

【0031】

電子部品の実装構造では、コンデンサ10,11及びフェライトビーズインダクタ12,13において、図1に示す矢印方向に電流がそれぞれ流れる。すなわち、コンデンサ10及びフェライトビーズインダクタ12においては、コンデンサ10側からフェライトビーズインダクタ12側に電流が流れる。コンデンサ11及びフェライトビーズインダクタ13においては、フェライトビーズインダクタ13側からコンデンサ11側に電流が流れる。このとき、隣接するコンデンサ10とコンデンサ11、及びフェライトビーズインダクタ12とフェライトビーズインダクタ13においては、電流が互いに逆向きに流れる。これにより、隣接するコンデンサ10とコンデンサ11、及びフェライトビーズインダクタ12とフェライトビーズインダクタ13とにおいて、磁界が相殺される。そのため、インダクタ成分のESL(Equivalent Series Inductance:等価直列インダクタンス)が低減する。

【0032】

続いて、上記のコンデンサ10,11及びフェライトビーズインダクタ12,13について詳細に説明する。まず、コンデンサ10,11について説明する。図3は、コンデンサを示す斜視図であり、図4は、図3に示すコンデンサの層構成を示す図である。

【0033】

図3,4に示すように、コンデンサ10,11は、積層チップコンデンサである。図3に示すように、コンデンサ10のコンデンサ素体15は、互いに対向する長方形状の第1及び第2の主面15a,15bと、第1及び第2の主面15a,15b間を連結するように第1及び第2の主面15a,15bの長辺方向に伸び且つ互いに対向する第1及び第2の側面15c,15dと、第1及び第2の主面15a,15b間を連結するように第1及び第2の主面15a,15bの短辺方向に伸び且つ互いに対向する第3及び第4の側面15e,15fとを有する。コンデンサ11のコンデンサ素体15も同様の構成を有している。

【0034】

第1の外部電極16は、コンデンサ素体15の第1の側面15c側に形成されている。第1の外部電極16は、第1の側面15c全面を覆うとともに、第1及び第2の主面15a,15b並びに第3及び第4の側面15e,15fの一部を連続して覆う。第2の外部電極17は、コンデンサ素体15の第2の側面15d側に形成されている。第2の外部電極17は、第2の側面15d全面を覆うとともに、第1及び第2の主面15a,15b並びに第3及び第4の側面15e,15fの一部を連続して覆う。すなわち、第1及び第2の外部電極16,17は、コンデンサ素体15の長手方向の側面15c,15dに配置されるように形成されている。

【0035】

コンデンサ素体15は、図4に示されるように、略長方形状の誘電体層21上に第1〜第4の内部電極22a〜22dがそれぞれ形成されてなる複数(ここでは4つ)の複合層23a〜23dと、複合層23a〜23dの最表層に積層され、保護層として機能する誘電体層21とによって形成されている。誘電体層21は、誘電体セラミックを含むセラミックグリーンシートの焼結体からなり、第1〜第4の内部電極22a〜22dは、導電性ペーストの焼結体からなる。実際のコンデンサ素体15では、誘電体層21間の境界が視認できない程度に一体化されている。

【0036】

複合層23aは、誘電体層21上に第1の内部電極22aが形成された層である。複合層23bは、誘電体層21上に第2の内部電極22bが形成された層である。複合層23cは、誘電体層21上に第3の内部電極22cが形成された層である。複合層23dは、誘電体層21上に第4の内部電極22dが形成された層である。第1〜第4の内部電極22a〜22dは、積層方向において誘電体層21を介して交互に配置されている。これにより、第1〜第4の内部電極22a〜22dは、コンデンサ素体15の一部である誘電体層21を間に挟んで対向する。

【0037】

第1の内部電極22aは、長方形状を呈し、コンデンサ素体15の第1及び第2の主面15a,15bの長辺方向とその長辺方向とが平行になるように、コンデンサ素体15内に配置される。第1の内部電極22aは、長方形状を保ったままコンデンサ素体15の第1の側面15cに引き出されるように伸び、第1の外部電極16に電気的且つ機械的に接続される。第1の内部電極22aは、第2〜第4の側面15d〜15fそれぞれからは所定距離離れて配置されている。第1の内部電極22aの第3及び第4の側面15e,15fの対向方向における長さは、第1及び第2の側面15c,15dの対向方向に沿って略一定である。第3の内部電極22cは、第1の内部電極22aと同様の構成を有している。

【0038】

第2の内部電極22bは、長方形状を呈し、コンデンサ素体15の第1及び第2の主面15a,15bの長辺方向とその長辺方向とが平行になるように、コンデンサ素体15内に配置される。第2の内部電極22bは、長方形状を保ったままコンデンサ素体15の第2の側面15dに引き出されるように伸び、第2の外部電極17に電気的且つ機械的に接続される。第2の内部電極22bは、第1、第3及び第4の側面15c,15e,15fそれぞれからは所定距離離れて配置されている。第2の内部電極22bの第3及び第4の側面15e,15fの対向方向における長さは、第1及び第2の側面15c,15dの対向方向に沿って略一定である。第4の内部電極22dは、第2の内部電極22bと同様の構成を有している。

【0039】

続いて、フェライトビーズインダクタ12,13について、図5〜図7を参照しながら詳細に説明する。図5は、フェライトビーズインダクタを示す斜視図であり、図6は、図5におけるVI−VI線断面図であり、図7は、図5に示すフェライトビーズインダクタの層構成を示す図である。

【0040】

図5〜図7に示すように、フェライトビーズインダクタ12,13は、積層チップフェライトビーズインダクタである。図5に示すように、フェライトビーズインダクタ12のフェライトビーズ素体18は、互いに対向する略長方形状の第1及び第2の主面18a,18bと、第1及び第2の主面18a,18b間を連結するように第1及び第2の主面18a,18bの長辺方向に伸び且つ互いに対向する第1及び第2の側面18c,18dと、第1及び第2の主面18a,18b間を連結するように第1及び第2の主面18a,18bの短辺方向に伸び且つ互いに対向する第3及び第4の側面18e,18fとを有する。フェライトビーズインダクタ13のフェライトビーズ素体18も同様の構成を有している。

【0041】

第1の外部電極19は、フェライトビーズ素体18の第1の側面18c側に形成されている。第1の外部電極19は、第1の側面18c全面を覆うとともに、第1及び第2の主面18a,18b並びに第3及び第4の側面18e,18fの一部を連続して覆う。第2の外部電極20は、フェライトビーズ素体18の第2の側面18d側に形成されている。第2の外部電極20は、第2の側面18d全面を覆うとともに、第1及び第2の主面18a,18b並びに第3及び第4の側面18e,18fの一部を連続して覆う。すなわち、第1及び第2の外部電極19,20は、フェライトビーズ素体18の長手方向の側面18c,18dに配置されるように形成されている。フェライトビーズインダクタ12,13の第1及び第2の外部電極19,20の幅寸法は、コンデンサ10,11の第1及び第2の外部電極16,17の幅寸法と同等となっている。

【0042】

図6及び図7に示すように、フェライトビーズ素体18は、略長方形状の磁性体層24上に第1〜第4の内部電極25a〜25dがそれぞれ形成されてなる複数(ここでは4つ)の複合層26a〜26dと、複合層26a〜26dの最表層に積層され、保護層として機能する磁性体層24とによって形成されている。磁性体層24は、主成分としてフェライト材料を含むシートの焼結体からなり、第1〜第4の内部電極25a〜25dは、導電性ペーストの焼結体からなる。実際のフェライトビーズ素体18では、磁性体層24間の境界が視認できない程度に一体化されている。

【0043】

複合層26aは、磁性体層24上に第1の内部電極25aが形成された層である。複合層26bは、磁性体層24上に第2の内部電極25bが形成された層である。複合層26cは、磁性体層24上に第3の内部電極25cが形成された層である。複合層26dは、磁性体層24上に第4の内部電極25dが形成された層である。第1〜第4の内部電極25a〜25dは、積層方向に磁性体層24を介して順に積層されている。これにより、第1〜第4の内部電極25a〜25dがフェライトビーズ素体18の一部である磁性体層24の間に挟まれるように配置される。

【0044】

第1の内部電極25aは、第1及び第2の側面18c,18dの対向方向(第1及び第2の主面18a,18bの短辺方向と平行)に伸びる長方形状の一部にスリット状の空隙27a〜27cを設けたものである。この第1の内部電極25aは、フェライトビーズ素体18の第1及び第2の側面18c,18dの両方に引き出されるように伸び、第1の外部電極19及び第2の外部電極20に電気的且つ機械的に接続される。第1の内部電極25aは、第3及び第4の側面18e,18fからは所定距離離れて配置されている。この離れた部分は、磁性体層24上におけるギャップ部分28e,28fに相当し、このギャップ部分28e,28f以外の部分が、磁性体層24上において内部電極の面積を最大限に形成することが可能な内部電極領域Sとなる(図8参照)。

【0045】

導電性ペーストが配置されていない空隙27a〜27cそれぞれは、第1及び第2の側面18c,18dの対向方向がその長手方向となる長方形状(短冊状)を呈しており、積層方向からみた際に、上述した内部電極領域S内に位置するように形成されている。空隙27a,27cは、その一端が第1の側面18c側に露出するように第1の側面18c寄りに形成され、空隙27bは、その一端が第2の側面18d側に露出するように第2の側面18d寄りに形成される。第2〜第4の内部電極25b〜25dは、第1の内部電極25aと同様の構成を有している。第1〜第4の内部電極25a〜25dの各空隙27a〜27cは、複合層26a〜26dと最表層の磁性体層24とが積層されてフェライトビーズインダクタ12,13が形成された際、積層方向に隣接する磁性体層24同士が接合する接合部となり、両者の密着性を向上させるように機能する。

【0046】

図9は、本実施形態における実装構造の等価回路図である。図9に示すように、コンデンサ10,11は、静電容量C1,C2を形成する。フェライトビーズインダクタ12,13は、直列に接続されたインダクタ成分L1,L2と抵抗成分R1,R2とを形成する。そして、インダクタ成分L1,L2及び抵抗成分R1,R2の合成成分は、コンデンサ10,11の静電容量C1,C2と直列に電源ライン1,2の間に接続される。フェライトビーズインダクタ12,13は、低周波帯域においてはインダクタ成分L1,L2が主として作用し、高周波帯域においては抵抗成分R1,R2が主として作用する。

【0047】

以上説明したように、本実施形態に係る電子部品の実装構造では、コンデンサ10,11とフェライトビーズインダクタ12,13とが直列となるように電源ライン1,2間に接続されるので、フェライトビーズインダクタ12,13の抵抗成分R1,R2がコンデンサ10,11の等価直列抵抗(ESR:Equivalent Series Resistance)として作用する。フェライトビーズインダクタ12,13の抵抗成分R1,R2は、直流抵抗成分と高周波帯域で増加する損失との和で構成される。したがって、この実装構造によれば、高周波帯域における抵抗成分を増加させることができる。

【0048】

また、この実装構造では、フェライトビーズインダクタ12,13は、電流の流れる方向が互いに逆向きとなるように実装されているため、磁界が相殺される。そのため、高周波帯域においてESLが更に低減するため、高周波ノイズの反射を防止することが可能となり、高周波ノイズを抵抗成分で熱変換して好適に除去することが可能となる。一方、フェライトビーズインダクタ12,13は、低周波帯域では抵抗成分よりもむしろインダクタ成分が機能するため、上記実装構造によって低周波帯域でインピーダンスを小さく保つことが可能となる。そして、低周波ノイズに対しては、コンデンサ10,11を実装しているため、このコンデンサ10,11でその低周波ノイズが吸収され、好適に除去することができる。

【0049】

また、この実装構造に用いられるフェライトビーズインダクタ12,13では、第1及び第2の外部電極19,20の幅を広くできると共に内部電極25a〜25dの長さを短くすることができるので、ビーズインダクタの抵抗成分の1つである直流抵抗成分を小さくすることができる。つまり、このフェライトビーズインダクタ12,13を用いることにより、低周波帯域では更に低ESRとすることができ、高周波帯域では高ESRとすることができる。

【0050】

しかも、これらフェライトビーズインダクタ12,13では、第1〜第4の内部電極25a〜25dを形成可能な内部電極領域S内に、積層方向に隣接する磁性体層24同士が接合する接合部のための空隙27a〜27cが形成されている。このため、上記構成のフェライトビーズインダクタ12,13によれば、低周波帯域での低ESRや高周波帯域での高ESRを実現しつつ、更に、磁性体層24の層間はがれを防止して、ビーズインダクタの内部欠陥の発生を抑えることもできる。

【0051】

ここで、上述したフェライトビーズインダクタ12,13の作用効果についてより具体的に説明する。図8に示すように、磁性体層24上における内部電極領域Sの面積をS0とし、磁性体層24上における空隙27a〜27cの総面積をS1とした場合において、内部電極領域Sと空隙27a〜27cとの面積比であるS1/S0がどの範囲にある場合に直流抵抗成分が小さくなり且つ内部構造欠陥の発生が抑えられるかについて、表1に示すように確認した。確認対象のサンプルとしては、外形寸法Lが0.8mm、Wが1.6mm(L0.8×W1.6、表1のNo.1〜No.7)のものと、外形寸法Lが1.2mm、Wが2.0mm(L1.2mm×W2.0mm、表1のNo.8〜No.14)のものとを用いた。

【0052】

【表1】

【0053】

この確認試験では、それぞれのサンプル数nを100個とし、面積比S1/S0を変更させた場合における、層間剥がれなどによる内部構造欠陥の発生数と直流抵抗Rdc(mΩ)とを求めた。その結果、表1に示すように、No.1〜No.14の何れのサンプルにおいても、内部構造欠陥の発生数を0個/100個〜数個/100個程度に抑えることができた。特に、面積比S1/S0が0.20よりも大きい場合には、内部構造結果の発生数が0個/100個、即ち内部構造欠陥がないといった顕著な効果を得ることができた。

【0054】

また、表1に示すように、No.1〜No.14の何れのサンプルにおいても、直流抵抗Rdcを低めに抑えることができたが、特に、面積比S1/S0が0.67以下の場合に、直流抵抗が低いと認定される指標の1つである「10mΩ」よりも更に低い直流抵抗Rdcを実現できるといった顕著な効果を得ることができた。

【0055】

このように、磁性体層24上における内部電極領域Sの面積をS0とし、磁性体層24上における空隙27a〜27cの総面積をS1とした場合において、特に、内部電極領域Sと空隙27a〜27cとの面積比であるS1/S0が0.20よりも大きく且つ0.67以下となるようにすることにより、低周波帯域での低ESRや高周波帯域での高ESRを実現でき、且つ、磁性体層24の層間はがれを防止してフェライトビーズインダクタ12,13の内部構造欠陥の発生を抑えることもできるといった顕著な効果を奏することができる。

【0056】

また、フェライトビーズインダクタ12,13では、第1及び第2の外部電極19,20は、それぞれ一の外部電極からなっている。このため、外部電極19,20における抵抗値を更に下げることができるため、フェライトビーズインダクタ12,13の直流抵抗成分を更に小さくすることができる。

【0057】

なお、コンデンサ10,11の第1及び第2の外部電極16,17の幅寸法は、フェライトビーズインダクタ12,13の第1及び第2の外部電極19,20の幅寸法と同等となっている。コンデンサ10,11の第1及び第2の外部電極16,17の幅寸法と、フェライトビーズインダクタ12,13の第1及び第2の外部電極19,20の幅寸法とが異なる場合、高周波電流が第1及び第2の外部電極16,17と第1及び第2の外部電極19,20との間にて反射し、高周波電流がフェライトビーズインダクタ12,13の抵抗成分R1,R2において熱に変換されないといった不具合が生じ、ノイズの除去効果が低下するといった問題があり得る。

【0058】

しかしながら、本実施形態では、第1及び第2の外部電極16,17と第1及び第2の外部電極19,20との幅寸法が同等となっていることにより、第1及び第2の外部電極16,17と第1及び第2の外部電極19,20との間の高周波電流の反射を防止でき、フェライトビーズインダクタ12,13におけるノイズの除去効果の向上を図ることができる。

【0059】

また、コンデンサ10,11において、第1及び第2の外部電極16,17がコンデンサ素体15の第1及び第2の側面15c,15d側に形成されている。第1及び第2の側面15c,15dは、コンデンサ素体15の長手方向の側面である。このため、コンデンサ10,11では、ESLをより低減させることができる。

【0060】

[第2実施形態]

次に、第2実施形態に係るフェライトビーズインダクタ12,13について説明する。本実施形態に係るフェライトビーズインダクタ12,13では、第1〜第4の内部電極35a〜35dの形状が第1実施形態の内部電極25a〜25dと異なっている。以下、第一実施形態と異なる点を中心に説明する。

【0061】

図10に示すように、フェライトビーズインダクタ12,13のフェライトビーズ素体18は、略長方形状の磁性体層24上に第1〜第4の内部電極35a〜35dがそれぞれ形成されてなる複数の複合層36a〜36dと、複合層36a〜36dの最表層に積層され、保護層として機能する磁性体層24とによって形成されている。複合層36a〜36dのそれぞれは、磁性体層24上に第1〜第4の内部電極35a〜35dそれぞれが形成された層である。第1〜第4の内部電極35a〜35dは、積層方向に磁性体層24を介して順に積層され、これにより、第1〜第4の内部電極35a〜35dのそれぞれが磁性体層24の間に挟まれるように配置される。

【0062】

第1の内部電極35aは、第1及び第2の側面18c,18dの対向方向に伸びる長方形状の一部に、それぞれ長方形状を呈する9つの空隙37a〜37iを設けて、梯子形状とした電極である。第1の内部電極35aは、フェライトビーズ素体18の第1及び第2の側面18c,18dの両方に引き出されるように伸び、第1実施形態と同様に、第1及び第2の外部電極19,20に電気的且つ機械的に接続される。第1の内部電極35aは、第3及び第4の側面18e,18fからは所定距離離れて配置されている。

【0063】

空隙37a〜37iは、第1の側面18cから第2の側面18dに向かって、空隙37a,37b,37cの順に、空隙37d,37e,37fの順に、空隙37g,37h,37iの順に、3列になるように配置されている。空隙37a〜37iは、第1実施形態と同様、積層方向からみて、内部電極領域S内に位置するように配置されている。空隙37a,37d,37gは、その一端が第1の側面18c側に露出するよう形成され、空隙37c,37f,37iは、その一端が第2の側面18d側に露出するよう形成され、空隙37b,37e,37hは、第1及び第2の側面18c,18dのいずれにも露出せずこれら側面18c,18dの対向方向の中央部に位置するように形成されている。第2〜第4の内部電極35b〜35dは、第1の内部電極35aと同様の構成を有している。

【0064】

以上説明したように、本実施形態に係るフェライトビーズインダクタ12,13では、第1実施形態と同様、ビーズインダクタの抵抗成分の1つである直流抵抗成分を小さくできることに加え、内部電極35a〜35dが、その形状が梯子状となるように内部電極領域S内に9つの空隙37a〜37iを有する構成となっているため、積層方向に隣接する磁性体層24同士をより確実に接合させることができる。その結果、本実施形態によれば、磁性体層24の層間はがれを防止して、ビーズインダクタの内部欠陥の発生を抑えることができる。

【0065】

[第3実施形態]

次に、第3実施形態に係るフェライトビーズインダクタ12,13について説明する。本実施形態に係るフェライトビーズインダクタ12,13では、第1〜第4の内部電極45a〜45dの形状が第1実施形態の内部電極25a〜25dと異なっている。以下、第一実施形態と異なる点を中心に説明する。

【0066】

図11に示すように、フェライトビーズインダクタ12,13のフェライトビーズ素体18は、略長方形状の磁性体層24上に第1〜第4の内部電極45a〜45dがそれぞれ形成されてなる複数の複合層46a〜46dと、複合層46a〜46dの最表層に積層され、保護層として機能する磁性体層24とによって形成されている。複合層46a〜46dのそれぞれは、各磁性体層24上に4つの第1〜第4の内部電極45a〜45dそれぞれが形成された層である。つまり、一の磁性体層24の上に分割された複数(4つ)の内部電極45a〜45dが配置されている。

【0067】

第1の内部電極45aのそれぞれは、第1及び第2の側面18c,18dの対向方向に伸びる長方形状(短冊状)を呈した電極である。第1の内部電極45aは、フェライトビーズ素体18の第1及び第2の側面18c,18dの両方に引き出されるように伸び、第1及び第2の外部電極19,20に電気的且つ機械的に接続される。第1の内部電極45aそれぞれの間には空隙47a〜47cが形成されており、また、第3及び第4の側面18e,18fの対向方向外側に位置する第1の内部電極45aは、第3及び第4の側面18e,18fからは所定距離離れて配置されている。

【0068】

空隙47a〜47cは、第1及び第2の側面18c,18dの対向方向に伸びる長方形状(短冊状)を呈したスリット状の空隙であり、第1実施形態等と同様、積層方向からみて、内部電極領域S内に位置するように配置されている。各空隙47a〜47cは、第1及び第2の側面18c,18d側に露出するよう形成されている。第2〜第4の内部電極45b〜45d及び内部電極間の空隙は、第1の内部電極45a及び第1の内部電極45a間の空隙47a〜47cと同様の構成となっている。

【0069】

以上説明したように、本実施形態に係るフェライトビーズインダクタ12,13では、第1実施形態等と同様、ビーズインダクタの抵抗成分の1つである直流抵抗成分を小さくできることに加え、内部電極45a〜45dの間に形成される空隙47a〜47cを内部電極領域S内に有する構成となっているため、積層方向に隣接する磁性体層24同士をより確実に接合させることができる。その結果、本実施形態によれば、磁性体層24の層間はがれを防止して、ビーズインダクタの内部欠陥の発生を抑えることができる。

【0070】

[第4実施形態]

次に、第4実施形態に係るフェライトビーズインダクタ12,13について説明する。本実施形態に係るフェライトビーズインダクタ12,13では、第1〜第4の内部電極53a〜53dの形状及び積層方向における配置箇所が第1実施形態の内部電極25a〜25dと異なっている。以下、第一実施形態と異なる点を中心に説明する。

【0071】

図12及び図13に示すように、本実施形態に係るフェライトビーズインダクタ12,13のフェライトビーズ素体18は、略長方形状の磁性体層24上に内部電極53a〜53dが形成されてなる複数の複合層54a〜54dと、複合層54a〜54dの最表層に積層され、保護層として機能する磁性体層24とによって形成されている。

【0072】

複合層54aは、磁性体層24上に複数(ここでは2つ)の内部電極53a,53bが形成された層である。内部電極53aは、長方形状を呈し、フェライトビーズ素体18の第1及び第2の主面18a,18bの短辺方向とその長辺方向とが平行になるように、磁性体層24上に形成されている。内部電極53aは、フェライトビーズ素体18の第1及び第2の側面18c,18dに引き出されるように伸び、第1及び第2の外部電極19,20に電気的且つ機械的に接続される。内部電極53bは、長方形状を呈し、フェライトビーズ素体18の第1及び第2の主面18a,18bの短辺方向とその長辺方向とが平行になるように、磁性体層24上に形成されている。

【0073】

内部電極53bは、内部電極53aよりもフェライトビーズ素体18の第1及び第2の主面18a,18bの長辺方向における幅寸法が大きい。内部電極53bは、フェライトビーズ素体18の第1及び第2の側面18c,18dに引き出されるように伸び、第1及び第2の外部電極19,20に電気的且つ機械的に接続される。内部電極53aと内部電極53bとの間には空隙57aが形成されており、また、内部電極53bとギャップ部分28fとの間には空隙57bが形成されている。複合層54cは、複合層54aと同様の構成を有している。

【0074】

複合層54bは、磁性体層24上に複数(ここでは2つ)の内部電極53c,53dが形成された層である。内部電極53cは、長方形状を呈し、フェライトビーズ素体18の第1及び第2の主面18a,18bの短辺方向とその長辺方向とが平行になるように、磁性体層24上に形成されている。内部電極53cは、フェライトビーズ素体18の第1及び第2の側面18c,18dに引き出されるように伸び、第1及び第2の外部電極19,20に電気的且つ機械的に接続される。内部電極53dは、長方形状を呈し、フェライトビーズ素体18の第1及び第2の主面18a,18bの短辺方向とその長辺方向とが平行になるように、磁性体層24上に形成されている。

【0075】

内部電極53dは、内部電極53cよりもフェライトビーズ素体18の第1及び第2の主面18a,18bの長辺方向における幅寸法が小さい。内部電極53dは、フェライトビーズ素体18の第1及び第2の側面18c,18dに引き出されるように伸び、第1及び第2の外部電極19,20に電気的且つ機械的に接続される。内部電極53cと内部電極53dとの間には空隙57dが形成されており、内部電極53cとギャップ部分28eとの間には空隙57cが形成されている。複合層54dは、複合層54bと同様の構成を有している。

【0076】

フェライトビーズ素体18において、内部電極53a,53bは、積層方向において磁性体層24を介して対向して配置されており、内部電極53c,53dは、積層方向において磁性体層24を介して対向して配置されている。つまり、複合層54a,54cの内部電極53a,53bは、積層方向において複合層54b,54dの内部電極53c,53dと重ならない位置に配置されている。

【0077】

以上説明したように、本実施形態に係るフェライトビーズインダクタ12,13では、このような構成により、積層方向において内部電極53a〜53dが磁性体層24を介して交互に積層されている。これにより、フェライトビーズインダクタ12,13では、第1実施形態等と同様、ビーズインダクタの抵抗成分の1つである直流抵抗成分を小さくできることに加え、内部電極53a〜53dの間等に形成される空隙57a〜57dを内部電極領域S内に有する構成となっているため、積層方向に隣接する磁性体層24同士をより確実に接合させることができる。その結果、本実施形態によれば、磁性体層24の層間はがれを防止して、ビーズインダクタの内部欠陥の発生を抑えることができる。

【0078】

本発明は、上記実施形態に限定されるものではない。例えば、上述したフェライトビーズインダクタ12,13では、4つの複合層からフェライトビーズ素体が構成される例を示したが、これに限定されるわけではなく、例えば6つの複合層から構成されるようにしてもよい。また、上述した電子部品の実装構造において、コンデンサ及びフェライトビーズインダクタの実装数は設計に応じて適宜変更することができる。例えば、図14に示すように、コンデンサ10,11及びフェライトビーズインダクタ12,13をそれぞれ4つずつ実装させることができる。このような構成においても、コンデンサ10,11及びフェライトビーズインダクタ12,13が電源ライン1,2間に直列に接続されていると共に、フェライトビーズインダクタ12,13において磁界が相殺されるため、ESLを低減することができる。したがって、低周波帯域において低インピーダンスを保ちつつ、高周波帯域において高インピーダンスとすることができる。

【0079】

また、図15に示すような実装構造を採用することもできる。すなわち、この実装構造では、電極パターンとして、配線1aが第1のランド電極60に接続され、配線2aが第2のランド電極61に接続され、第1のランド電極60と同一直線上に第3のランド電極62が設けられ、第2のランド電極61と同一直線上に第4のランド電極63が設けられる。第3のランド電極62は、ビアホールH3を介して第1のランド電極60と電気的に接続され、第4のランド電極63は、ビアホールH4を介して第2のランド電極61と電気的に接続される。また、第1及び第3のランド電極60,62の間や第2及び第4のランド電極61,63の間には接続電極64が設けられる。

【0080】

そして、このような電極パターンへの実装にあたり、コンデンサ10が第1のランド電極60及び接続電極64に跨って配置され、コンデンサ11が接続電極64及び第3のランド電極62に跨って配置される。また、フェライトビーズインダクタ12が第2のランド電極61と接続電極64とに跨って配置され、フェライトビーズインダクタ13が接続電極64と第4のランド電極63とに跨って配置される。この配置により、この実装構造においても、コンデンサ10,11とフェライトビーズインダクタ12,13とが電源ライン1,2の間に直列に実装され、コンデンサ10,11及びフェライトビーズインダクタ12,13とICチップ3とが並列接続の関係になるようにすることができる。しかも、この実装構造では、図15に示す矢印方向に電流が流れるため、フェライトビーズインダクタ12,13において磁界が相殺されるため、ESLを低減することができる。

【符号の説明】

【0081】

1,2…電源ライン、10,11…コンデンサ、12,13…フェライトビーズインダクタ、18…フェライトビーズ素体、18a,18b…第1及び第2の主面、18c〜18f…第1〜第4の側面、19…第1の外部電極、20…第2の外部電極、25a〜25d,35a〜35d,45a〜45d,53a〜53d…内部電極、27a〜27c,37a〜37i,47a〜47c,57a〜57d…空隙。

【特許請求の範囲】

【請求項1】

磁性体層の間に内部電極が配置されるように前記磁性体層と前記内部電極とが積層され、且つ、互いに対向する略長方形状の第1及び第2の主面と、前記第1及び第2の主面間を連結するように前記第1及び第2の主面の長辺方向に伸び且つ互いに対向する第1及び第2の側面と、前記第1及び第2の主面間を連結するように前記第1及び第2の主面の短辺方向に伸び且つ互いに対向する第3及び第4の側面とを有する素体と、

前記素体の前記第1の側面に配置される第1の外部電極と、

前記素体の前記第2の側面に配置される第2の外部電極と、を備え、

前記内部電極は、前記長辺よりも短い前記短辺の方向に伸びて前記第1及び第2の外部電極に接続され、

前記素体は、前記磁性体層上において前記内部電極を形成可能な内部電極領域内に、積層方向に隣接する前記磁性体層同士が接合する接合部を有していることを特徴とする積層型電子部品。

【請求項2】

前記磁性体層上における前記内部電極領域の面積をS0とし、前記磁性体層上における前記接合部の面積をS1とした場合において、前記内部電極領域と前記接合部との面積比であるS1/S0が0.20よりも大きく且つ0.67以下であることを特徴とする請求項1に記載の積層型電子部品。

【請求項3】

前記内部電極は、前記磁性体層上において、複数の内部電極に分割されていることを特徴とする請求項1又は2に記載の積層型電子部品。

【請求項4】

異なる前記磁性体層上に配置された前記内部電極のそれぞれは、前記積層方向において、その間に位置する前記磁性体層を介して対向しないように配置されていることを特徴とする請求項1〜3の何れか一項に記載の積層型電子部品。

【請求項5】

前記第1及び第2の外部電極は、それぞれ一の外部電極からなることを特徴とする請求項1〜4の何れか一項に記載の積層型電子部品。

【請求項6】

電流を供給するための電源ラインに接続される電子部品の実装構造であって、

前記電子部品として、コンデンサと請求項1〜5の何れか1項に記載の積層型電子部品であるビーズインダクタとを備え、

前記電源ラインの間に、前記コンデンサと前記ビーズインダクタとが直列となるように実装されることを特徴とする電子部品の実装構造。

【請求項7】

前記コンデンサは、

誘電体層と内部電極とが積層され、且つ、互いに対向する略長方形状の第1及び第2の主面と、前記第1及び第2の主面間を連結するように前記第1及び第2の主面の長辺方向に伸び且つ互いに対向する第1及び第2の側面と、前記第1及び第2の主面間を連結するように前記第1及び第2の主面の短辺方向に伸び且つ互いに対向する第3及び第4の側面とを有するコンデンサ素体と、

前記コンデンサ素体の前記第1の側面側に配置される第1のコンデンサ外部電極と、

前記コンデンサ素体の前記第2の側面側に配置される第2のコンデンサ外部電極と、を備えていることを特徴とする請求項6に記載の電子部品の実装構造。

【請求項8】

前記コンデンサの前記第1及び第2のコンデンサ外部電極の幅寸法は、前記ビーズインダクタの前記第1及び第2の外部電極の幅寸法と略同等であることを特徴とする請求項7に記載の電子部品の実装構造。

【請求項9】

前記ビーズインダクタを複数有し、前記各ビーズインダクタは、互いの磁界が相殺されるように実装されていることを特徴とする請求項6〜8の何れか一項に記載の電子部品の実装構造。

【請求項1】

磁性体層の間に内部電極が配置されるように前記磁性体層と前記内部電極とが積層され、且つ、互いに対向する略長方形状の第1及び第2の主面と、前記第1及び第2の主面間を連結するように前記第1及び第2の主面の長辺方向に伸び且つ互いに対向する第1及び第2の側面と、前記第1及び第2の主面間を連結するように前記第1及び第2の主面の短辺方向に伸び且つ互いに対向する第3及び第4の側面とを有する素体と、

前記素体の前記第1の側面に配置される第1の外部電極と、

前記素体の前記第2の側面に配置される第2の外部電極と、を備え、

前記内部電極は、前記長辺よりも短い前記短辺の方向に伸びて前記第1及び第2の外部電極に接続され、

前記素体は、前記磁性体層上において前記内部電極を形成可能な内部電極領域内に、積層方向に隣接する前記磁性体層同士が接合する接合部を有していることを特徴とする積層型電子部品。

【請求項2】

前記磁性体層上における前記内部電極領域の面積をS0とし、前記磁性体層上における前記接合部の面積をS1とした場合において、前記内部電極領域と前記接合部との面積比であるS1/S0が0.20よりも大きく且つ0.67以下であることを特徴とする請求項1に記載の積層型電子部品。

【請求項3】

前記内部電極は、前記磁性体層上において、複数の内部電極に分割されていることを特徴とする請求項1又は2に記載の積層型電子部品。

【請求項4】

異なる前記磁性体層上に配置された前記内部電極のそれぞれは、前記積層方向において、その間に位置する前記磁性体層を介して対向しないように配置されていることを特徴とする請求項1〜3の何れか一項に記載の積層型電子部品。

【請求項5】

前記第1及び第2の外部電極は、それぞれ一の外部電極からなることを特徴とする請求項1〜4の何れか一項に記載の積層型電子部品。

【請求項6】

電流を供給するための電源ラインに接続される電子部品の実装構造であって、

前記電子部品として、コンデンサと請求項1〜5の何れか1項に記載の積層型電子部品であるビーズインダクタとを備え、

前記電源ラインの間に、前記コンデンサと前記ビーズインダクタとが直列となるように実装されることを特徴とする電子部品の実装構造。

【請求項7】

前記コンデンサは、

誘電体層と内部電極とが積層され、且つ、互いに対向する略長方形状の第1及び第2の主面と、前記第1及び第2の主面間を連結するように前記第1及び第2の主面の長辺方向に伸び且つ互いに対向する第1及び第2の側面と、前記第1及び第2の主面間を連結するように前記第1及び第2の主面の短辺方向に伸び且つ互いに対向する第3及び第4の側面とを有するコンデンサ素体と、

前記コンデンサ素体の前記第1の側面側に配置される第1のコンデンサ外部電極と、

前記コンデンサ素体の前記第2の側面側に配置される第2のコンデンサ外部電極と、を備えていることを特徴とする請求項6に記載の電子部品の実装構造。

【請求項8】

前記コンデンサの前記第1及び第2のコンデンサ外部電極の幅寸法は、前記ビーズインダクタの前記第1及び第2の外部電極の幅寸法と略同等であることを特徴とする請求項7に記載の電子部品の実装構造。

【請求項9】

前記ビーズインダクタを複数有し、前記各ビーズインダクタは、互いの磁界が相殺されるように実装されていることを特徴とする請求項6〜8の何れか一項に記載の電子部品の実装構造。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【公開番号】特開2012−156192(P2012−156192A)

【公開日】平成24年8月16日(2012.8.16)

【国際特許分類】

【出願番号】特願2011−12026(P2011−12026)

【出願日】平成23年1月24日(2011.1.24)

【出願人】(000003067)TDK株式会社 (7,238)

【Fターム(参考)】

【公開日】平成24年8月16日(2012.8.16)

【国際特許分類】

【出願日】平成23年1月24日(2011.1.24)

【出願人】(000003067)TDK株式会社 (7,238)

【Fターム(参考)】

[ Back to top ]