積層型電子部品

【課題】 DC−DCコンバータのICから出力される信号は、高電流、かつ高速の三角波が重畳されており、そのエネルギーの変化速度も数百MHzになるといわれ、このエネルギーによるノイズも発生し易くなっている。DC−DCコンバータのICに接続されるコイルやコンデンサを電子機器の配線基板上で接続した場合、配線基板の配線パターンによって、コイルとコンデンサの接続点に、それぞれ寄生インダクタンスが発生し、DC−DCコンバータの効率が悪化すると共に、ノイズが発生し易くなる。

【解決手段】 絶縁体層と導体パターンを積層し、絶縁体層間の導体パターンを螺旋状に接続してコイルが形成されたコイル部と、絶縁体層と導体パターンを積層してインピーダンス素子が形成されたインピーダンス部とが積層される。これらの積層体内には、入力端子と出力端子間に外部端子を介して直列に接続されたコイルとインピーダンス素子が形成される。

【解決手段】 絶縁体層と導体パターンを積層し、絶縁体層間の導体パターンを螺旋状に接続してコイルが形成されたコイル部と、絶縁体層と導体パターンを積層してインピーダンス素子が形成されたインピーダンス部とが積層される。これらの積層体内には、入力端子と出力端子間に外部端子を介して直列に接続されたコイルとインピーダンス素子が形成される。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、絶縁体層と導体パターンを積層し、素体内に回路素子が形成された積層型電子部品に関するものである。

【背景技術】

【0002】

各種電子機器において用いられる、リチウムイオンバッテリー等のバッテリーパックから供給される電圧を必要とする電圧に変換する同期整流タイプの降圧型DC−DCコンバータに、図6に示す様に、同期整流タイプの降圧型DC−DCコンバータを構成するIC60の出力端にコイルL5の一端を接続し、コイルL5の他端とアース間にコンデンサC3を接続し、コイルL5とコンデンサC3の接続点をIC60のフィードバック端に接続したものがある(例えば、特許文献1を参照。)。

この種の同期整流タイプの降圧型DC−DCコンバータは、電子機器の多機能化に伴い、低消費電力化、小型化が望まれている。この様な状況の中、この種の降圧型DC−DCコンバータでは、ICを低電圧で動作させて消費電力を小さくすると共に、DC−DCコンバータのICの出力側に接続されるコイルの形状が小さくなる様にICの制御方法を改良し、制御速度(fsw=スイッチング周波数)を高速化させて回路の小型化を実現している。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開2005-80419号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

この様なDC−DCコンバータのICから出力される信号は、高電流、かつ高速の三角波が重畳されており、そのエネルギーの変化速度も数百MHzになるといわれ、このエネルギーによるノイズも発生し易くなっている。例えば、6MHzで動作する同期整流タイプの降圧型DC−DCコンバータでは、200〜300MHz近傍でノイズが観測されている。この様なノイズを除去するために、現在、コンデンサC3の近傍に、ノイズの発生する周波数帯で大きな減衰効果が得られる高周波用のコンデンサを接続することが行われている。

また、この様なDC−DCコンバータのICに接続されるコイルL5やコンデンサC3を電子機器の配線基板上で接続した場合、配線基板に電子部品を配置するスペースや配線パターンを引き回すスペースを設ける必要があり、コイルL5とコンデンサC3を接続するための配線パターンが長くなりやすく、この配線基板の配線パターンによって、コイルL5とコンデンサC3の接続点に、図7に示す様に、それぞれ寄生インダクタンス71が発生し、DC−DCコンバータの効率が悪化すると共に、ノイズが発生し易くなるという問題があった。特に、従来のDC−DCコンバータのICが1MHz未満の速度でスイッチングされていたのに対し、近年のDC−DCコンバータのICでは6MHzを越える速度でスイッチングされており、数nHの誤差による位相差であっても波形制御に大きな影響を及ぼすという問題があった。

【0005】

本発明の積層型電子部品は、寄生インダクタンスを減少させ、コイル本来の性能を劣化させることなく、ノイズを低減させることができる積層型電子部品を提供することを目的とする。

【課題を解決するための手段】

【0006】

本発明は、絶縁体層と導体パターンを積層し、これらの積層体内に回路素子が形成された積層型電子部品において、絶縁体層と導体パターンを積層し、絶縁体層間の導体パターンを螺旋状に接続してコイルが形成されたコイル部と、絶縁体層と導体パターンを積層してインピーダンス素子が形成されたインピーダンス部とを積層し、これらの積層体内に、入力端子と出力端子間に外部端子を介して直列に接続されたコイルとインピーダンス素子が形成される。

【発明の効果】

【0007】

本発明の積層型電子部品は、絶縁体層と導体パターンを積層し、絶縁体層間の導体パターンを螺旋状に接続してコイルが形成されたコイル部と、絶縁体層と導体パターンを積層してインピーダンス素子が形成されたインピーダンス部とを積層し、これらの積層体内に、入力端子と出力端子間に外部端子を介して直列に接続されたコイルとインピーダンス素子が形成されるので、寄生インダクタンスを減少させ、コイル本来の性能を劣化させることなく、ノイズを低減させることができる。

【図面の簡単な説明】

【0008】

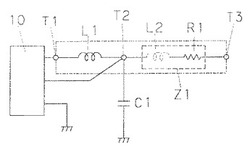

【図1】本発明の積層型電子部品の第1の実施例の回路図である。

【図2】本発明の積層型電子部品の第1の実施例を示す分解斜視図である。

【図3】本発明の積層型電子部品の第1の実施例を示す斜視図である。

【図4】本発明の積層型電子部品の第2の実施例の回路図である。

【図5】本発明の積層型電子部品の第2の実施例を示す分解斜視図である。

【図6】従来のDC−DCコンバータの回路図である。

【図7】従来のDC−DCコンバータを説明するための回路図である。

【発明を実施するための形態】

【0009】

本発明の積層型電子部品は、絶縁体層と導体パターンを積層し、絶縁体層間の導体パターンを螺旋状に接続してコイルが形成されたコイル部と、絶縁体層と導体パターンを積層してインピーダンス素子が形成されたインピーダンス部が積層される。これらの積層体内にはコイルとインピーダンスが形成され、入力端子と出力端子間に、DC−DCコンバータのICのフィードバック端に接続するための外部端子を介してコイルとインピーダンス素子が直列に接続される。このインピーダンス素子は、DC−DCコンバータのICから出力された信号が存在する低い周波数では低インダクタンスとして機能し、ノイズが存在する高い周波数では抵抗として機能する様に形成される。

従って、本発明の積層型電子部品は、DC−DCコンバータのICに接続されるコイルの出力端子の外側に、インピーダンス素子を一体に備えることができるので、DC−DCコンバータの負荷側の制御変動に伴って、コイルとこのコイルに接続されるコンデンサによって構成されるフィルタの周波数特性に影響を与えたり、コイルの出力端とDC−DCコンバータのICのフィードバック端間に寄生インダクタンスが発生したりすることもない。また、コイルとインピーダンス素子を電子機器の配線基板の配線パターンで接続する必要がないので、電子機器の配線基板における配線パターンの設計が簡単になると共に、配線基板の形状の小型化にも貢献できる。さらに、コイルとインピーダンス素子の配線距離を配線基板上で接続した場合よりも短くすることができる。

【実施例】

【0010】

以下、本発明の積層型電子部品の実施例を図1乃至図5を参照して説明する。

図1は本発明の積層型電子部品の第1の実施例の回路図である。

コイルL1は、一端が入力端子T1を介してDC−DCコンバータのIC10の出力端に接続され、他端が外部端子T2に接続される。インピーダンス素子Z1は、一端が外部端子T2に接続され、他端が出力端子T3に接続される。インピーダンス素子Z1は、DC−DCコンバータのICから出力された信号が存在する低い周波数で機能する低インダクタンスL2とノイズが存在する高い周波数で機能する抵抗R1からなる。コイルL1とインピーダンス素子Z1の接続点である外部端子T2は、コンデンサC1を介してアースされると共に、DC−DCコンバータのIC10のフィードバック端にも接続される。

【0011】

この様に形成された回路の一点鎖線で囲まれた部分が、図2のように絶縁体層と導体パターンを積層することにより、積層体内に形成される。

絶縁体層21A〜21Cと絶縁体層22A〜22Dは、磁性体、非磁性体、誘電体等絶縁性を有する材料を用いて形成される。

絶縁体層21Aの表面には、コイル用導体パターン23Aが形成される。コイル用導体パターン23Aは、線状に形成され、1ターン未満分が形成される。コイル用導体パターン23Aの一端は、絶縁体層21Aの端面まで引き出される。

絶縁体層21Bの表面には、コイル用導体パターン23Bが形成される。コイル用導体パターン23Bは、線状に形成され、1ターン未満分が形成される。コイル用導体パターン23Bの一端は、絶縁体層21Bに形成されたスルーホール内の導体を介してコイル用導体パターン23Aの他端に接続される。

絶縁体層21Cの表面には、コイル用導体パターン23Cが形成される。コイル用導体パターン23Cは、線状に形成され、1ターン未満分が形成される。コイル用導体パターン23Cの一端は、絶縁体層21Cに形成されたスルーホール内の導体を介してコイル用導体パターン23Bの他端に接続される。コイル用導体パターン23Cの他端は、絶縁体層21Cの側面まで引き出される。この様にコイル用導体パターン23A、コイル用導体パターン23B及び、コイル用導体パターン23Cを螺旋状に接続することにより、絶縁体層21A〜21Cとコイル用導体パターン23A〜23Cが積層されたコイル部内にコイルL1が形成される。また、このコイル部は、コイルL1の直流重畳特性が良くなる様に絶縁体層21A〜21Cやコイル用導体パターン23A〜23Cの材料が選択される。

絶縁体層22Aの表面には、導体パターン24Aが形成される。導体パターン24Aは、線状に形成され、1ターン未満分が形成される。導体パターン24Aの一端は、絶縁体層22Aの側面まで引き出される。

絶縁体層22Bの表面には、導体パターン24Bが形成される。導体パターン24Bは、線状に形成され、1ターン未満分が形成される。導体パターン24Bの一端は、絶縁体層22Bに形成されたスルーホール内の導体を介して導体パターン24Aの他端に接続される。

絶縁体層22Cの表面には、導体パターン24Cが形成される。導体パターン24Cは、線状に形成され、1ターン未満分が形成される。導体パターン24Cの一端は、絶縁体層22Cに形成されたスルーホール内の導体を介して導体パターン24Bの他端に接続される。導体パターン24Cの他端は、絶縁体層22Cの端面まで引き出される。この導体パターン24Cが形成された絶縁体層22C上には絶縁体層22Dが積層される。この様に導体パターン24A、導体パターン24B及び、導体パターン24Cを螺旋状に接続することにより、絶縁体層22A〜22Cと導体パターン24A〜24Cが積層されたインピーダンス部内にインピーダンス素子Z1が形成される。また、このインピーダンス部は、DC−DCコンバータのICから出力された信号が存在する低い周波数では低インダクタンスL2として機能し、ノイズが存在する高い周波数では抵抗R1として機能する様に、絶縁体層22A〜22Dや導体パターン24A〜24Cの材料が選択される。さらに、このインピーダンス素子Z1とコイルL1は、互いに磁気的に結合しない様に、インピーダンス素子Z1とコイルL1が離間して形成されたり、コイル部とインピーダンス部間に、コイル部やインピーダンス部と異なる材質の層や、グランド電極等の磁気結合防止層が形成されたりする。

この様に絶縁体層21A〜21C、コイル用導体パターン23A〜23C、絶縁体層22A〜22D及び、導体パターン24A〜24Cが積層された積層体には、図3に示す様に、積層体の端面に入力端子31と出力端子32が形成され、側面に外部端子が形成される。そして、コイル用導体パターン23Aが入力端子31に、導体パターン24Cが出力端子23に、コイル用導体パターン23Cと導体パターン24Aが外部端子33にそれぞれ接続される。

【0012】

この様に形成された積層型電子部品は、コイル用導体パターン23A、コイル用導体パターン23B及び、コイル用導体パターン23CによってコイルL1が、導体パターン24A、導体パターン24B及び、導体パターン24Cによってインピーダンス素子Z1が形成され、外部端子33によってコイルL1とインピーダンス素子Z1が接続される。

この積層型電子部品は、電子機器の配線基板に実装され、入力端子31が配線基板の配線パターンを介してDC−DCコンバータのIC10の出力端に接続され、出力端子32が配線基板の配線パターンを介して負荷に接続され、外部端子33が配線基板の配線パターンを介してコンデンサC1の一端とDC−DCコンバータのICのフィードバック端に接続される。コンデンサC1の他端はアースされる。

この様な積層型電子部品は、DC−DCコンバータのICから出力された信号が入力端子31から入力され、この入力された信号がコイルL1とインピーダンス素子Z1を介して出力端子32から負荷に出力されると共に、入力された信号の一部が外部端子33からDC−DCコンバータのICのフィードバック端とコンデンサC1に出力される。この時、入力された信号に混入したノイズはインピーダンス素子Z1の抵抗成分によって熱に変換されて除去され、出力端子32からはノイズの混入していない信号が出力される。

【0013】

図4は本発明の積層型電子部品の第2の実施例を示す回路図である。

コイルL3は、一端が入力端子T4を介してDC−DCコンバータのIC40の出力端に接続され、他端が外部端子T5に接続される。インピーダンス素子Z2は、一端が外部端子T5に接続され、他端が出力端子T6に接続される。インピーダンス素子Z2は、DC−DCコンバータのICから出力された信号が存在する低い周波数で機能する低インダクタンスL4とノイズが存在する高い周波数で機能する抵抗R2からなる。コイルL3とインピーダンス素子Z2の接続点である外部端子T5は、コンデンサC2を介してアースされると共に、DC−DCコンバータのIC40のフィードバック端にも接続される。

【0014】

この様に形成された回路の一点鎖線で囲まれた部分が、図5のように絶縁体層と導体パターンを積層することにより、積層体内に形成される。

絶縁体層51A〜51C、絶縁体層52A〜52C及び、絶縁体層55A〜55Cは、磁性体、非磁性体、誘電体等絶縁性を有する材料を用いて形成される。

絶縁体層51Aの表面にはコイル用導体パターン53Aが形成される。コイル用導体パターン53Aは1ターン未満分が形成される。コイル用導体パターン53Aの一端は、絶縁体層51Aの端面まで引き出される。

絶縁体層51Bの表面にはコイル用導体パターン53Bが形成される。コイル用導体パターン53Bは1ターン未満分が形成される。コイル用導体パターン53Bの一端は、絶縁体層51Bに形成されたスルーホール内の導体を介してコイル用導体パターン53Aの他端に接続される。

絶縁体層51Cの表面にはコイル用導体パターン53Cが形成される。コイル用導体パターン53Cは1ターン未満分が形成される。コイル用導体パターン53Cの一端は、絶縁体層51Cに形成されたスルーホール内の導体を介してコイル用導体パターン53Bの他端に接続される。コイル用導体パターン53Cの他端は、絶縁体層51Cの側面まで引き出される。この様にコイル用導体パターン53A、コイル用導体パターン53B及び、コイル用導体パターン53Cを螺旋状に接続することにより、絶縁体層51A〜51Cとコイル用導体パターン53A〜53Cが積層されたコイル部内にコイルL3が形成される。また、このコイル部は、コイルL3の直流重畳特性が良くなる様に絶縁体層51A〜51Cやコイル用導体パターン53A〜53Cの材料が選択される。

絶縁体層52Aの表面には、線状の導体パターン54Aが形成される。導体パターン54Aは1ターン未満分が形成される。導体パターン54Aの一端は、絶縁体層52Aの側面まで引き出される。

絶縁体層52Bの表面には、線状の導体パターン54Bが形成される。導体パターン54Bは1ターン未満分が形成される。導体パターン54Bの一端は、絶縁体層52Bに形成されたスルーホール内の導体を介して導体パターン54Aの他端に接続される。

絶縁体層52Cの表面には、線状の導体パターン54Cが形成される。導体パターン54Cは1ターン未満分が形成される。導体パターン54Cの一端は、絶縁体層52Cに形成されたスルーホール内の導体を介して導体パターン54Bの他端に接続される。導体パターン54Cの他端は、絶縁体層52Cの端面まで引き出される。この様に導体パターン54A、導体パターン54B及び、導体パターン54Cを螺旋状に接続することにより、絶縁体層52A〜52Cと導体パターン54A〜54Cが積層されたインピーダンス部内にインピーダンス素子Z2が形成される。また、このインピーダンス部は、DC−DCコンバータのICから出力された信号が存在する低い周波数では低インダクタンスL4として機能し、ノイズが存在する高い周波数では抵抗R2として機能する様に、絶縁体層52A〜52Dや導体パターン54A〜54Cの材料が選択される。さらに、このインピーダンス素子Z2とコイルL3は、互いに磁気的に結合しない様に、インピーダンス素子Z2とコイルL3が離間して形成されたり、コイル部とインピーダンス部間に、コイル部やインピーダンス部と異なる材質の層や、グランド電極等の磁気結合防止層が形成されたりする。

絶縁体層55Aの表面には、導体パターン56Aが形成される。導体パターン56Aは引出し端が絶縁体層55Aの側面まで引き出される。

絶縁体層55Bの表面には、導体パターン56Bが形成される。導体パターン56Bは、絶縁体層55Bの導体パターン55Aと対向する位置に形成され、引出し端が絶縁体層55Bの側面まで引き出される。この導体パターン56Bが形成された絶縁体層55B上には絶縁体層55Cが積層される。この様に導体パターン56Aと導体パターン56Bが絶縁体層55Bを介して対向することにより、絶縁体層55A〜55Cと導体パターン56A、56Bが積層されたコンデンサ部内にコンデンサC2が形成される。

この様に絶縁体層51A〜51C、コイル用導体パターン53A〜53C、絶縁体層52A〜52D、導体パターン54A〜54C、絶縁体層55A〜55C及び、導体パターン56A、56Bが積層された積層体には、積層体の端面に入力端子と出力端子が形成され、側面にそれぞれ外部端子が形成される。そして、コイル用導体パターン53Aが入力端子に、導体パターン54Cが出力端子に、コイル用導体パターン53Cと導体パターン54Aと導体パターン56Aが一方の外部端子に、導体パターン56Bが他方の外部端子にそれぞれ接続される。

【0015】

この様に形成された積層型電子部品は、コイル用導体パターン53A、コイル用導体パターン53B及び、コイル用導体パターン53CによってコイルL3が、導体パターン54A、導体パターン54B及び、導体パターン54Cによってインピーダンス素子Z2が、導体パターン56Aと導体パターン56B間に形成される容量によってコンデンサC2が形成され、外部端子によってコイルL3、インピーダンス素子Z2及び、コンデンサC2が接続される。

この積層型電子部品は、電子機器の配線基板に実装され、入力端子が配線基板の配線パターンを介してDC−DCコンバータのIC40の出力端に接続され、出力端子が配線基板の配線パターンを介して負荷に接続され、コイルL3とインピーダンス素子Z2が接続された外部端子が配線基板の配線パターンを介してDC−DCコンバータのICのフィードバック端に接続される。この積層型電子部品のもう一方の外部端子はアースされる。

この様な積層型電子部品は、DC−DCコンバータのICから出力された信号が入力端子から入力され、この入力された信号がコイルL3とインピーダンス素子Z2を介して出力端子から負荷に出力されると共に、入力された信号の一部が外部端子からDC−DCコンバータのICのフィードバック端とコンデンサC2に出力される。この時、入力された信号に混入したノイズはインピーダンス素子Z2の抵抗成分によって熱に変換されて除去され、出力端子からはノイズの混入していない信号が出力される。

この様に形成された本実施例の積層型電子部品は、コイルL3、インピーダンス素子Z2及び、コンデンサC2を電子機器の配線基板の配線パターンで接続する必要がないので、電子機器の配線基板の配線パターンの設計が簡単になると共に、配線基板の形状の小型化に貢献できる。また、コイルL3、インピーダンス素子Z2及びコンデンサC2の配線距離を配線基板上で接続した場合よりも短くすることができる。

【0016】

以上、本発明の積層型電子部品の実施例を述べたが、本発明はこれらの実施例に限定されるものではない。例えば、コイル部はコイル用導体パターンの形状を工夫してコイルの直流重畳特性を良くしてもよい。また、磁性体とコイル用導体パターンを積層して形成したコイル部内に非磁性体部分を形成してコイルの直流重畳特性を良くしてもよい。

また、第2の実施例において、DC−DCコンバータのICに接続される分圧用の抵抗を内蔵させても良い。さらに、第2の実施例において、積層体の上面に、DC−DCコンバータのICを実装し、DC−DCコンバータのICを積層体に形成された入力端子や外部端子に接続しても良い。

【符号の説明】

【0017】

L1 コイル

Z1 インピーダンス素子

C1 コンデンサ

21A〜21C、22A〜22D 絶縁体層

23A〜22C コイル用導体パターン

24A〜24C 導体パターン

【技術分野】

【0001】

本発明は、絶縁体層と導体パターンを積層し、素体内に回路素子が形成された積層型電子部品に関するものである。

【背景技術】

【0002】

各種電子機器において用いられる、リチウムイオンバッテリー等のバッテリーパックから供給される電圧を必要とする電圧に変換する同期整流タイプの降圧型DC−DCコンバータに、図6に示す様に、同期整流タイプの降圧型DC−DCコンバータを構成するIC60の出力端にコイルL5の一端を接続し、コイルL5の他端とアース間にコンデンサC3を接続し、コイルL5とコンデンサC3の接続点をIC60のフィードバック端に接続したものがある(例えば、特許文献1を参照。)。

この種の同期整流タイプの降圧型DC−DCコンバータは、電子機器の多機能化に伴い、低消費電力化、小型化が望まれている。この様な状況の中、この種の降圧型DC−DCコンバータでは、ICを低電圧で動作させて消費電力を小さくすると共に、DC−DCコンバータのICの出力側に接続されるコイルの形状が小さくなる様にICの制御方法を改良し、制御速度(fsw=スイッチング周波数)を高速化させて回路の小型化を実現している。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開2005-80419号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

この様なDC−DCコンバータのICから出力される信号は、高電流、かつ高速の三角波が重畳されており、そのエネルギーの変化速度も数百MHzになるといわれ、このエネルギーによるノイズも発生し易くなっている。例えば、6MHzで動作する同期整流タイプの降圧型DC−DCコンバータでは、200〜300MHz近傍でノイズが観測されている。この様なノイズを除去するために、現在、コンデンサC3の近傍に、ノイズの発生する周波数帯で大きな減衰効果が得られる高周波用のコンデンサを接続することが行われている。

また、この様なDC−DCコンバータのICに接続されるコイルL5やコンデンサC3を電子機器の配線基板上で接続した場合、配線基板に電子部品を配置するスペースや配線パターンを引き回すスペースを設ける必要があり、コイルL5とコンデンサC3を接続するための配線パターンが長くなりやすく、この配線基板の配線パターンによって、コイルL5とコンデンサC3の接続点に、図7に示す様に、それぞれ寄生インダクタンス71が発生し、DC−DCコンバータの効率が悪化すると共に、ノイズが発生し易くなるという問題があった。特に、従来のDC−DCコンバータのICが1MHz未満の速度でスイッチングされていたのに対し、近年のDC−DCコンバータのICでは6MHzを越える速度でスイッチングされており、数nHの誤差による位相差であっても波形制御に大きな影響を及ぼすという問題があった。

【0005】

本発明の積層型電子部品は、寄生インダクタンスを減少させ、コイル本来の性能を劣化させることなく、ノイズを低減させることができる積層型電子部品を提供することを目的とする。

【課題を解決するための手段】

【0006】

本発明は、絶縁体層と導体パターンを積層し、これらの積層体内に回路素子が形成された積層型電子部品において、絶縁体層と導体パターンを積層し、絶縁体層間の導体パターンを螺旋状に接続してコイルが形成されたコイル部と、絶縁体層と導体パターンを積層してインピーダンス素子が形成されたインピーダンス部とを積層し、これらの積層体内に、入力端子と出力端子間に外部端子を介して直列に接続されたコイルとインピーダンス素子が形成される。

【発明の効果】

【0007】

本発明の積層型電子部品は、絶縁体層と導体パターンを積層し、絶縁体層間の導体パターンを螺旋状に接続してコイルが形成されたコイル部と、絶縁体層と導体パターンを積層してインピーダンス素子が形成されたインピーダンス部とを積層し、これらの積層体内に、入力端子と出力端子間に外部端子を介して直列に接続されたコイルとインピーダンス素子が形成されるので、寄生インダクタンスを減少させ、コイル本来の性能を劣化させることなく、ノイズを低減させることができる。

【図面の簡単な説明】

【0008】

【図1】本発明の積層型電子部品の第1の実施例の回路図である。

【図2】本発明の積層型電子部品の第1の実施例を示す分解斜視図である。

【図3】本発明の積層型電子部品の第1の実施例を示す斜視図である。

【図4】本発明の積層型電子部品の第2の実施例の回路図である。

【図5】本発明の積層型電子部品の第2の実施例を示す分解斜視図である。

【図6】従来のDC−DCコンバータの回路図である。

【図7】従来のDC−DCコンバータを説明するための回路図である。

【発明を実施するための形態】

【0009】

本発明の積層型電子部品は、絶縁体層と導体パターンを積層し、絶縁体層間の導体パターンを螺旋状に接続してコイルが形成されたコイル部と、絶縁体層と導体パターンを積層してインピーダンス素子が形成されたインピーダンス部が積層される。これらの積層体内にはコイルとインピーダンスが形成され、入力端子と出力端子間に、DC−DCコンバータのICのフィードバック端に接続するための外部端子を介してコイルとインピーダンス素子が直列に接続される。このインピーダンス素子は、DC−DCコンバータのICから出力された信号が存在する低い周波数では低インダクタンスとして機能し、ノイズが存在する高い周波数では抵抗として機能する様に形成される。

従って、本発明の積層型電子部品は、DC−DCコンバータのICに接続されるコイルの出力端子の外側に、インピーダンス素子を一体に備えることができるので、DC−DCコンバータの負荷側の制御変動に伴って、コイルとこのコイルに接続されるコンデンサによって構成されるフィルタの周波数特性に影響を与えたり、コイルの出力端とDC−DCコンバータのICのフィードバック端間に寄生インダクタンスが発生したりすることもない。また、コイルとインピーダンス素子を電子機器の配線基板の配線パターンで接続する必要がないので、電子機器の配線基板における配線パターンの設計が簡単になると共に、配線基板の形状の小型化にも貢献できる。さらに、コイルとインピーダンス素子の配線距離を配線基板上で接続した場合よりも短くすることができる。

【実施例】

【0010】

以下、本発明の積層型電子部品の実施例を図1乃至図5を参照して説明する。

図1は本発明の積層型電子部品の第1の実施例の回路図である。

コイルL1は、一端が入力端子T1を介してDC−DCコンバータのIC10の出力端に接続され、他端が外部端子T2に接続される。インピーダンス素子Z1は、一端が外部端子T2に接続され、他端が出力端子T3に接続される。インピーダンス素子Z1は、DC−DCコンバータのICから出力された信号が存在する低い周波数で機能する低インダクタンスL2とノイズが存在する高い周波数で機能する抵抗R1からなる。コイルL1とインピーダンス素子Z1の接続点である外部端子T2は、コンデンサC1を介してアースされると共に、DC−DCコンバータのIC10のフィードバック端にも接続される。

【0011】

この様に形成された回路の一点鎖線で囲まれた部分が、図2のように絶縁体層と導体パターンを積層することにより、積層体内に形成される。

絶縁体層21A〜21Cと絶縁体層22A〜22Dは、磁性体、非磁性体、誘電体等絶縁性を有する材料を用いて形成される。

絶縁体層21Aの表面には、コイル用導体パターン23Aが形成される。コイル用導体パターン23Aは、線状に形成され、1ターン未満分が形成される。コイル用導体パターン23Aの一端は、絶縁体層21Aの端面まで引き出される。

絶縁体層21Bの表面には、コイル用導体パターン23Bが形成される。コイル用導体パターン23Bは、線状に形成され、1ターン未満分が形成される。コイル用導体パターン23Bの一端は、絶縁体層21Bに形成されたスルーホール内の導体を介してコイル用導体パターン23Aの他端に接続される。

絶縁体層21Cの表面には、コイル用導体パターン23Cが形成される。コイル用導体パターン23Cは、線状に形成され、1ターン未満分が形成される。コイル用導体パターン23Cの一端は、絶縁体層21Cに形成されたスルーホール内の導体を介してコイル用導体パターン23Bの他端に接続される。コイル用導体パターン23Cの他端は、絶縁体層21Cの側面まで引き出される。この様にコイル用導体パターン23A、コイル用導体パターン23B及び、コイル用導体パターン23Cを螺旋状に接続することにより、絶縁体層21A〜21Cとコイル用導体パターン23A〜23Cが積層されたコイル部内にコイルL1が形成される。また、このコイル部は、コイルL1の直流重畳特性が良くなる様に絶縁体層21A〜21Cやコイル用導体パターン23A〜23Cの材料が選択される。

絶縁体層22Aの表面には、導体パターン24Aが形成される。導体パターン24Aは、線状に形成され、1ターン未満分が形成される。導体パターン24Aの一端は、絶縁体層22Aの側面まで引き出される。

絶縁体層22Bの表面には、導体パターン24Bが形成される。導体パターン24Bは、線状に形成され、1ターン未満分が形成される。導体パターン24Bの一端は、絶縁体層22Bに形成されたスルーホール内の導体を介して導体パターン24Aの他端に接続される。

絶縁体層22Cの表面には、導体パターン24Cが形成される。導体パターン24Cは、線状に形成され、1ターン未満分が形成される。導体パターン24Cの一端は、絶縁体層22Cに形成されたスルーホール内の導体を介して導体パターン24Bの他端に接続される。導体パターン24Cの他端は、絶縁体層22Cの端面まで引き出される。この導体パターン24Cが形成された絶縁体層22C上には絶縁体層22Dが積層される。この様に導体パターン24A、導体パターン24B及び、導体パターン24Cを螺旋状に接続することにより、絶縁体層22A〜22Cと導体パターン24A〜24Cが積層されたインピーダンス部内にインピーダンス素子Z1が形成される。また、このインピーダンス部は、DC−DCコンバータのICから出力された信号が存在する低い周波数では低インダクタンスL2として機能し、ノイズが存在する高い周波数では抵抗R1として機能する様に、絶縁体層22A〜22Dや導体パターン24A〜24Cの材料が選択される。さらに、このインピーダンス素子Z1とコイルL1は、互いに磁気的に結合しない様に、インピーダンス素子Z1とコイルL1が離間して形成されたり、コイル部とインピーダンス部間に、コイル部やインピーダンス部と異なる材質の層や、グランド電極等の磁気結合防止層が形成されたりする。

この様に絶縁体層21A〜21C、コイル用導体パターン23A〜23C、絶縁体層22A〜22D及び、導体パターン24A〜24Cが積層された積層体には、図3に示す様に、積層体の端面に入力端子31と出力端子32が形成され、側面に外部端子が形成される。そして、コイル用導体パターン23Aが入力端子31に、導体パターン24Cが出力端子23に、コイル用導体パターン23Cと導体パターン24Aが外部端子33にそれぞれ接続される。

【0012】

この様に形成された積層型電子部品は、コイル用導体パターン23A、コイル用導体パターン23B及び、コイル用導体パターン23CによってコイルL1が、導体パターン24A、導体パターン24B及び、導体パターン24Cによってインピーダンス素子Z1が形成され、外部端子33によってコイルL1とインピーダンス素子Z1が接続される。

この積層型電子部品は、電子機器の配線基板に実装され、入力端子31が配線基板の配線パターンを介してDC−DCコンバータのIC10の出力端に接続され、出力端子32が配線基板の配線パターンを介して負荷に接続され、外部端子33が配線基板の配線パターンを介してコンデンサC1の一端とDC−DCコンバータのICのフィードバック端に接続される。コンデンサC1の他端はアースされる。

この様な積層型電子部品は、DC−DCコンバータのICから出力された信号が入力端子31から入力され、この入力された信号がコイルL1とインピーダンス素子Z1を介して出力端子32から負荷に出力されると共に、入力された信号の一部が外部端子33からDC−DCコンバータのICのフィードバック端とコンデンサC1に出力される。この時、入力された信号に混入したノイズはインピーダンス素子Z1の抵抗成分によって熱に変換されて除去され、出力端子32からはノイズの混入していない信号が出力される。

【0013】

図4は本発明の積層型電子部品の第2の実施例を示す回路図である。

コイルL3は、一端が入力端子T4を介してDC−DCコンバータのIC40の出力端に接続され、他端が外部端子T5に接続される。インピーダンス素子Z2は、一端が外部端子T5に接続され、他端が出力端子T6に接続される。インピーダンス素子Z2は、DC−DCコンバータのICから出力された信号が存在する低い周波数で機能する低インダクタンスL4とノイズが存在する高い周波数で機能する抵抗R2からなる。コイルL3とインピーダンス素子Z2の接続点である外部端子T5は、コンデンサC2を介してアースされると共に、DC−DCコンバータのIC40のフィードバック端にも接続される。

【0014】

この様に形成された回路の一点鎖線で囲まれた部分が、図5のように絶縁体層と導体パターンを積層することにより、積層体内に形成される。

絶縁体層51A〜51C、絶縁体層52A〜52C及び、絶縁体層55A〜55Cは、磁性体、非磁性体、誘電体等絶縁性を有する材料を用いて形成される。

絶縁体層51Aの表面にはコイル用導体パターン53Aが形成される。コイル用導体パターン53Aは1ターン未満分が形成される。コイル用導体パターン53Aの一端は、絶縁体層51Aの端面まで引き出される。

絶縁体層51Bの表面にはコイル用導体パターン53Bが形成される。コイル用導体パターン53Bは1ターン未満分が形成される。コイル用導体パターン53Bの一端は、絶縁体層51Bに形成されたスルーホール内の導体を介してコイル用導体パターン53Aの他端に接続される。

絶縁体層51Cの表面にはコイル用導体パターン53Cが形成される。コイル用導体パターン53Cは1ターン未満分が形成される。コイル用導体パターン53Cの一端は、絶縁体層51Cに形成されたスルーホール内の導体を介してコイル用導体パターン53Bの他端に接続される。コイル用導体パターン53Cの他端は、絶縁体層51Cの側面まで引き出される。この様にコイル用導体パターン53A、コイル用導体パターン53B及び、コイル用導体パターン53Cを螺旋状に接続することにより、絶縁体層51A〜51Cとコイル用導体パターン53A〜53Cが積層されたコイル部内にコイルL3が形成される。また、このコイル部は、コイルL3の直流重畳特性が良くなる様に絶縁体層51A〜51Cやコイル用導体パターン53A〜53Cの材料が選択される。

絶縁体層52Aの表面には、線状の導体パターン54Aが形成される。導体パターン54Aは1ターン未満分が形成される。導体パターン54Aの一端は、絶縁体層52Aの側面まで引き出される。

絶縁体層52Bの表面には、線状の導体パターン54Bが形成される。導体パターン54Bは1ターン未満分が形成される。導体パターン54Bの一端は、絶縁体層52Bに形成されたスルーホール内の導体を介して導体パターン54Aの他端に接続される。

絶縁体層52Cの表面には、線状の導体パターン54Cが形成される。導体パターン54Cは1ターン未満分が形成される。導体パターン54Cの一端は、絶縁体層52Cに形成されたスルーホール内の導体を介して導体パターン54Bの他端に接続される。導体パターン54Cの他端は、絶縁体層52Cの端面まで引き出される。この様に導体パターン54A、導体パターン54B及び、導体パターン54Cを螺旋状に接続することにより、絶縁体層52A〜52Cと導体パターン54A〜54Cが積層されたインピーダンス部内にインピーダンス素子Z2が形成される。また、このインピーダンス部は、DC−DCコンバータのICから出力された信号が存在する低い周波数では低インダクタンスL4として機能し、ノイズが存在する高い周波数では抵抗R2として機能する様に、絶縁体層52A〜52Dや導体パターン54A〜54Cの材料が選択される。さらに、このインピーダンス素子Z2とコイルL3は、互いに磁気的に結合しない様に、インピーダンス素子Z2とコイルL3が離間して形成されたり、コイル部とインピーダンス部間に、コイル部やインピーダンス部と異なる材質の層や、グランド電極等の磁気結合防止層が形成されたりする。

絶縁体層55Aの表面には、導体パターン56Aが形成される。導体パターン56Aは引出し端が絶縁体層55Aの側面まで引き出される。

絶縁体層55Bの表面には、導体パターン56Bが形成される。導体パターン56Bは、絶縁体層55Bの導体パターン55Aと対向する位置に形成され、引出し端が絶縁体層55Bの側面まで引き出される。この導体パターン56Bが形成された絶縁体層55B上には絶縁体層55Cが積層される。この様に導体パターン56Aと導体パターン56Bが絶縁体層55Bを介して対向することにより、絶縁体層55A〜55Cと導体パターン56A、56Bが積層されたコンデンサ部内にコンデンサC2が形成される。

この様に絶縁体層51A〜51C、コイル用導体パターン53A〜53C、絶縁体層52A〜52D、導体パターン54A〜54C、絶縁体層55A〜55C及び、導体パターン56A、56Bが積層された積層体には、積層体の端面に入力端子と出力端子が形成され、側面にそれぞれ外部端子が形成される。そして、コイル用導体パターン53Aが入力端子に、導体パターン54Cが出力端子に、コイル用導体パターン53Cと導体パターン54Aと導体パターン56Aが一方の外部端子に、導体パターン56Bが他方の外部端子にそれぞれ接続される。

【0015】

この様に形成された積層型電子部品は、コイル用導体パターン53A、コイル用導体パターン53B及び、コイル用導体パターン53CによってコイルL3が、導体パターン54A、導体パターン54B及び、導体パターン54Cによってインピーダンス素子Z2が、導体パターン56Aと導体パターン56B間に形成される容量によってコンデンサC2が形成され、外部端子によってコイルL3、インピーダンス素子Z2及び、コンデンサC2が接続される。

この積層型電子部品は、電子機器の配線基板に実装され、入力端子が配線基板の配線パターンを介してDC−DCコンバータのIC40の出力端に接続され、出力端子が配線基板の配線パターンを介して負荷に接続され、コイルL3とインピーダンス素子Z2が接続された外部端子が配線基板の配線パターンを介してDC−DCコンバータのICのフィードバック端に接続される。この積層型電子部品のもう一方の外部端子はアースされる。

この様な積層型電子部品は、DC−DCコンバータのICから出力された信号が入力端子から入力され、この入力された信号がコイルL3とインピーダンス素子Z2を介して出力端子から負荷に出力されると共に、入力された信号の一部が外部端子からDC−DCコンバータのICのフィードバック端とコンデンサC2に出力される。この時、入力された信号に混入したノイズはインピーダンス素子Z2の抵抗成分によって熱に変換されて除去され、出力端子からはノイズの混入していない信号が出力される。

この様に形成された本実施例の積層型電子部品は、コイルL3、インピーダンス素子Z2及び、コンデンサC2を電子機器の配線基板の配線パターンで接続する必要がないので、電子機器の配線基板の配線パターンの設計が簡単になると共に、配線基板の形状の小型化に貢献できる。また、コイルL3、インピーダンス素子Z2及びコンデンサC2の配線距離を配線基板上で接続した場合よりも短くすることができる。

【0016】

以上、本発明の積層型電子部品の実施例を述べたが、本発明はこれらの実施例に限定されるものではない。例えば、コイル部はコイル用導体パターンの形状を工夫してコイルの直流重畳特性を良くしてもよい。また、磁性体とコイル用導体パターンを積層して形成したコイル部内に非磁性体部分を形成してコイルの直流重畳特性を良くしてもよい。

また、第2の実施例において、DC−DCコンバータのICに接続される分圧用の抵抗を内蔵させても良い。さらに、第2の実施例において、積層体の上面に、DC−DCコンバータのICを実装し、DC−DCコンバータのICを積層体に形成された入力端子や外部端子に接続しても良い。

【符号の説明】

【0017】

L1 コイル

Z1 インピーダンス素子

C1 コンデンサ

21A〜21C、22A〜22D 絶縁体層

23A〜22C コイル用導体パターン

24A〜24C 導体パターン

【特許請求の範囲】

【請求項1】

絶縁体層と導体パターンを積層し、これらの積層体内に回路素子が形成された積層型電子部品において、

絶縁体層と導体パターンを積層し、絶縁体層間の導体パターンを螺旋状に接続してコイルが形成されたコイル部と、絶縁体層と導体パターンを積層してインピーダンス素子が形成されたインピーダンス部とを積層し、

これらの積層体内に、入力端子と出力端子間に外部端子を介して直列に接続された該コイルと該インピーダンス素子が形成されたことを特徴とする積層型電子部品。

【請求項2】

前記積層体の前記コイル部と前記インピーダンス部間に磁気結合防止層を設けた請求項1に記載の積層型電子部品。

【請求項3】

前記積層体内にコンデンサを形成し、前記コイルと前記インピーダンス素子の接続点とアース間に該コンデンサを接続した請求項1又は請求項2に記載の積層型電子部品。

【請求項4】

前記コイルと前記インピーダンス素子の接続点が接続された前記外部端子は半導体素子のフィードバック端に接続するための端子である請求項1乃至請求項3に記載の積層型電子部品。

【請求項1】

絶縁体層と導体パターンを積層し、これらの積層体内に回路素子が形成された積層型電子部品において、

絶縁体層と導体パターンを積層し、絶縁体層間の導体パターンを螺旋状に接続してコイルが形成されたコイル部と、絶縁体層と導体パターンを積層してインピーダンス素子が形成されたインピーダンス部とを積層し、

これらの積層体内に、入力端子と出力端子間に外部端子を介して直列に接続された該コイルと該インピーダンス素子が形成されたことを特徴とする積層型電子部品。

【請求項2】

前記積層体の前記コイル部と前記インピーダンス部間に磁気結合防止層を設けた請求項1に記載の積層型電子部品。

【請求項3】

前記積層体内にコンデンサを形成し、前記コイルと前記インピーダンス素子の接続点とアース間に該コンデンサを接続した請求項1又は請求項2に記載の積層型電子部品。

【請求項4】

前記コイルと前記インピーダンス素子の接続点が接続された前記外部端子は半導体素子のフィードバック端に接続するための端子である請求項1乃至請求項3に記載の積層型電子部品。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【公開番号】特開2011−243829(P2011−243829A)

【公開日】平成23年12月1日(2011.12.1)

【国際特許分類】

【出願番号】特願2010−116050(P2010−116050)

【出願日】平成22年5月20日(2010.5.20)

【出願人】(000003089)東光株式会社 (243)

【Fターム(参考)】

【公開日】平成23年12月1日(2011.12.1)

【国際特許分類】

【出願日】平成22年5月20日(2010.5.20)

【出願人】(000003089)東光株式会社 (243)

【Fターム(参考)】

[ Back to top ]