積層配線、該積層配線を用いた半導体装置及びその製造方法

【課題】マイクロクリスタルシリコン薄膜と金属薄膜との過剰なシリサイド化反応を抑制して、マイクロクリスタルシリコン薄膜の膜剥れを防止する。

【解決手段】半導体装置20の配線として備えられ、マイクロクリスタルシリコン薄膜8と該薄膜上に形成された金属薄膜9とから成る積層配線であって、マイクロクリスタルシリコン薄膜8の結晶組織を構成している結晶粒には、半導体装置の製造時の熱処理で生じた金属薄膜9とのシリサイド化反応に起因して膜厚方向に成長した柱状の結晶粒が含まれ、マイクロクリスタルシリコン薄膜8の膜厚方向の長さがマイクロクリスタルシリコン薄膜8の膜厚の60%以上である柱状の結晶粒が、マイクロクリスタルシリコン薄膜8の結晶粒の全数の6%以上15%以下となるように形成されている。

【解決手段】半導体装置20の配線として備えられ、マイクロクリスタルシリコン薄膜8と該薄膜上に形成された金属薄膜9とから成る積層配線であって、マイクロクリスタルシリコン薄膜8の結晶組織を構成している結晶粒には、半導体装置の製造時の熱処理で生じた金属薄膜9とのシリサイド化反応に起因して膜厚方向に成長した柱状の結晶粒が含まれ、マイクロクリスタルシリコン薄膜8の膜厚方向の長さがマイクロクリスタルシリコン薄膜8の膜厚の60%以上である柱状の結晶粒が、マイクロクリスタルシリコン薄膜8の結晶粒の全数の6%以上15%以下となるように形成されている。

【発明の詳細な説明】

【技術分野】

【0001】

この発明は、積層配線、該積層配線を用いた半導体装置及びその製造方法に係り、詳しくは、薄膜トランジスタのゲート電極等に適用されるマイクロクリスタルシリコン薄膜を含む積層配線、該積層配線を用いた半導体装置及びその製造方法に関する。

【背景技術】

【0002】

例えば、表示装置の代表として知られている液晶表示装置(Liquid Crystal Device:LCD)においては、アモルファス(非結晶)シリコン薄膜を活性層とするアモルファスシリコン薄膜トランジスタ(Thin Film Transistor:TFT)を用いることが主流となっている。しかしながら、アモルファスシリコン薄膜は移動度が低いので、LCDを高精細に実現することが困難であるため、より移動度の高いポリ(多結晶)シリコン薄膜を活性層とするポリシリコンTFTが注目されている。

【0003】

一方で、LCDにおける用途の多様化により、薄型化・小型化に対する要求も強く、その要求に応えるため、アクティブマトリクス基板上に駆動回路も同様にTFTで形成する試みがなされている。しかし、この駆動回路用のTFTをアモルファスシリコン薄膜を用いて形成することは、動作速度及び駆動能力の点で好ましくなく、より移動度の高いポリシリコン薄膜を用いて形成することが求められている。ポリシリコン薄膜の形成方法としては、プロセス温度の低温化、スループット向上及び低コスト化の点から、安価な低温ガラス基板上にポリシリコン薄膜を形成可能なレーザアニール法が主流となっている。

【0004】

しかしながら、ポリシリコンTFTはゲート電極の信頼性が低く、かつ低抵抗化が難しいので、LCDを高精細に実現するのが困難であるという問題がある。この問題を解決するために、例えば特許文献1、特許文献2、特許文献3あるいは特許文献4に開示されているように、ゲート電極をマイクロクリスタルシリコン薄膜(下層)と金属薄膜(上層)とから成る積層配線により構成するようにしたポリシリコンTFTが提供されている。

【0005】

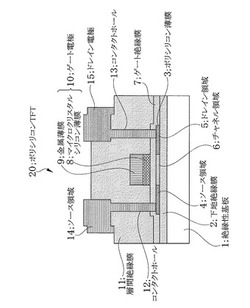

図11は、例えば、特許文献1に開示された上記のマイクロクリスタルシリコン薄膜を含む積層配線がゲート電極に適用された従来のポリシリコンTFTを示す断面図である。同ポリシリコンTFT100は、絶縁性基板101と、この絶縁性基板101上に形成された下地絶縁膜102と、この下地絶縁膜102上に形成されたポリシリコン薄膜103と、このポリシリコン薄膜103の両端領域にそれぞれ形成されたソース領域104及びドレイン領域105と、ポリシリコン薄膜103上に形成されたゲート絶縁膜106と、このゲート絶縁膜106上に形成されたマイクロクリスタルシリコン薄膜(下層)107と金属薄膜(上層)108とから成る積層配線により構成されたゲート電極109とを備えている。さらに、このポリシリコンTFT100は、ゲート電極109を含む全面に形成された層間絶縁膜110と、この層間絶縁膜110にそれぞれ開孔されたコンタクトホール111、112を通じて両領域104,105に接触するように形成されたソース電極113及びドレイン電極114とを備えている。

【0006】

ここで、ゲート電極109を構成しているマイクロクリスタルシリコン薄膜107は、プラズマCVD(Chemical Vapor Deposition)法によって形成されたシリコン薄膜であり、その結晶組織には極めて微細な結晶粒とアモルファスとが混在している。このマイクロクリスタルシリコン薄膜の成膜温度は300℃程度であり、従来のポリシリコン薄膜の成膜方法としての減圧CVD法や常圧CVD法のそれが600℃程度であるのに比較してかなり低い温度なので、成膜工程のスループット及び製造コストの点で極めて優れているため、生産性に富んでいるというメリットがある。また、マイクロクリスタルシリコン薄膜は、ゲート絶縁膜及び活性層のポリシリコン薄膜からの水素の過剰な離脱を防ぐこともできる。さらに、マイクロクリスタルシリコン薄膜には、微細な結晶粒が存在するために、ポリシリコン薄膜と同程度の低抵抗化が可能になっている。したがって、マイクロクリスタルシリコン薄膜上に金属薄膜を積層して形成した積層配線をTFTのゲート電極に適用することにより、ゲート電極の信頼性が高く、かつ低抵抗化が図れるので、LCDを高精細に実現するのが容易となる。

【先行技術文献】

【特許文献】

【0007】

【特許文献1】特許第3282582号公報

【特許文献2】特許第3613221号公報

【特許文献3】特開2004−336073号公報

【特許文献4】特開2004−281506号公報

【発明の概要】

【発明が解決しようとする課題】

【0008】

ところで、従来のマイクロクリスタルシリコン薄膜と金属薄膜とから成る積層配線では、熱処理時に下層のマイクロクリスタルシリコン薄膜と上層の金属薄膜との間でシリサイド化反応が起きるので、マイクロクリスタルシリコン薄膜に膜剥れが生ずる、という問題がある。

すなわち、上述したような積層配線がポリシリコンTFTのゲート電極に適用された場合、TFTの製造過程では、ポリシリコン薄膜中に予め導入したリンやボロン等の不純物を活性化するためのアニール工程(活性化工程)や、ポリシリコン薄膜中及びポリシリコン薄膜とゲート絶縁膜との界面に存在する未結合手(ダングリングボンド)を水素で終端するための水素化工程が必要になっている。そして、これら活性化工程及び水素化工程ではいずれも、マイクロクリスタルシリコン薄膜及び金属薄膜の成膜温度よりも高い温度での熱処理を伴うので、既に形成されているマイクロクリスタルシリコン薄膜がその熱処理の影響を受けて上述のシリサイド化反応が起きるのを回避できない。

【0009】

ところで、下層のマイクロクリスタルシリコン薄膜と上層の金属薄膜との間でシリサイド化反応が過剰に起きると、マイクロクリスタルシリコン薄膜の結晶組織を構成している結晶の形状が粒状から柱状へと変化する。そして、このように結晶の形状が変化する際に、マイクロクリスタルシリコン薄膜の体積に変化が生ずるので、マイクロクリスタルシリコン薄膜中や、下層のマイクロクリスタルシリコン薄膜と上層の金属薄膜との界面にボイドが発生して、このボイドの影響でマイクロクリスタルシリコン薄膜には最終的に膜剥れが起きるようになる。

【0010】

ここで、特許文献1に記載されているように、マイクロクリスタルシリコン薄膜をプラズマCVD法によって形成することは、減圧CVD法や常圧CVD法によりポリシリコン薄膜を形成する場合に比較して生産性に富んでいるというメリットがある。その一方で更なる生産性向上の要求に応えるには、プラズマCVD法によってより成膜速度の速い条件でマイクロクリスタルシリコン薄膜を形成する必要がある。しかしながら、一般に成膜速度の速い条件で形成した薄膜の膜質は悪くなり易いという傾向がある。したがって、マイクロクリスタルシリコン薄膜の膜質が悪くなると、この上に形成される金属薄膜との間で発生するシリサイド化反応がより加速されて、マイクロクリスタルシリコン薄膜の膜剥れが起き易くなるので、結果的に積層配線の膜剥れに結びつくことになる。

【0011】

この発明は、上述の事情に鑑みてなされたもので、マイクロクリスタルシリコン薄膜と金属薄膜との過剰なシリサイド化反応を抑制して、マイクロクリスタルシリコン薄膜の膜剥れを防止することができるようにした積層配線、該積層配線を用いた半導体装置及びその製造方法を提供することを目的としている。

【課題を解決するための手段】

【0012】

上記課題を解決するために、この発明の第1の構成は、電子部品の配線として備えられ、マイクロクリスタルシリコン薄膜と該薄膜上に形成された金属薄膜とから成る積層配線に係り、前記マイクロクリスタルシリコン薄膜の結晶組織を構成している結晶粒には、前記電子部品の製造時の熱処理で生じた前記金属薄膜とのシリサイド化反応に起因して膜厚方向に成長した柱状の結晶粒が含まれ、前記マイクロクリスタルシリコン薄膜の膜厚方向の長さが前記マイクロクリスタルシリコン薄膜の膜厚の60%以上である結晶粒が、前記マイクロクリスタルシリコン薄膜の結晶粒の全数の6%以上15%以下であることを特徴としている。

【0013】

また、この発明の第2の構成は、電子部品の配線として備えられ、マイクロクリスタルシリコン薄膜と該薄膜上に形成された金属薄膜とから成る積層配線に係り、前記マイクロクリスタルシリコン薄膜の結晶組織を構成している結晶粒には、前記電子部品の製造時の熱処理で生じた前記金属薄膜とのシリサイド化反応に起因して膜厚方向に成長した柱状の結晶粒が含まれ、前記マイクロクリスタルシリコン薄膜の膜厚方向の長さが前記マイクロクリスタルシリコン薄膜の膜厚の50%以下である結晶粒が、前記マイクロクリスタルシリコン薄膜の結晶粒の全数の85%以上91%以下であることを特徴としている。

【0014】

また、この発明の第3の構成は、半導体装置の製造方法に係り、絶縁性基板上に下地絶縁膜を介してアモルファスシリコン薄膜を形成する工程と、前記アモルファスシリコン薄膜にレーザアニール法を施して該アモルファスシリコン薄膜をポリシリコン薄膜に変質させる工程と、前記ポリシリコン薄膜をアイランド化した後、該ポリシリコン薄膜上にゲート絶縁膜を介してマイクロクリスタルシリコン薄膜及び金属薄膜を順次に堆積して積層膜を形成する工程と、前記積層膜を所望の形状にパターニングしてゲート電極を形成する工程と、前記ゲート電極が形成された上記絶縁性基板を熱処理する工程とを有し、前記熱処理後の前記マイクロクリスタルシリコン薄膜の結晶組織を構成している結晶粒には、前記熱処理の際に生じた前記金属薄膜とのシリサイド化反応に起因して膜厚方向に成長した柱状の結晶粒が含まれ、前記マイクロクリスタルシリコン薄膜の膜厚方向の長さが前記マイクロクリスタルシリコン薄膜の膜厚の60%以上である結晶粒が、前記マイクロクリスタルシリコン薄膜の結晶粒の全数の6%以上15%以下である薄膜、あるいは前記マイクロクリスタルシリコン薄膜の膜厚方向の長さが前記マイクロクリスタルシリコン薄膜の膜厚の50%以下である結晶粒が、前記マイクロクリスタルシリコン薄膜の結晶粒の全数の85%以上91%以下である薄膜を形成することを特徴としている。

【発明の効果】

【0015】

この発明の積層配線によれば、マイクロクリスタルシリコン薄膜の結晶組織を構成している結晶粒において、マイクロクリスタルシリコン薄膜の膜厚方向の長さがマイクロクリスタルシリコン薄膜の膜厚の60%以上である結晶粒が、マイクロクリスタルシリコン薄膜の結晶粒の全数の15%以下、あるいは膜厚方向の長さがマイクロクリスタルシリコン薄膜の膜厚の50%以下である結晶粒が、マイクロクリスタルシリコン薄膜の結晶粒の全数の85%以上になっている。したがって、マイクロクリスタルシリコン薄膜と金属薄膜との過剰なシリサイド化反応を抑制することができるので、膜剥れの発生を防止することができる。また、この発明の積層配線の製造方法によれば、少なくとも膜質が悪くならない成膜条件でマイクロクリスタルシリコン薄膜を形成するので、金属薄膜とのシリサイド化反応が抑制されるため膜剥れが発生しない。

【0016】

この発明の半導体装置の製造方法によれば、上記の組成のマイクロクリスタルシリコン薄膜を含む積層配線によりゲート電極を有する半導体装置を形成するようにしたので、ゲート電極の高信頼性及び低抵抗化を低コストで達成することができる。

【図面の簡単な説明】

【0017】

【図1】この発明の実施例1である積層配線を用いた半導体装置を示す断面図である。

【図2】この発明の実施例2である同半導体装置の製造方法を工程順に示す工程図である。

【図3】同半導体装置の製造方法を工程順に示す工程図である。

【図4】同半導体装置の製造方法を工程順に示す工程図である。

【図5】この発明の原理を示すもので、熱処理工程後でも膜剥れが生じなかったマイクロクリスタルシリコン薄膜の結晶組織の断面写真である。

【図6】この発明の原理を示すもので、熱処理工程後に膜剥れが生じたマイクロクリスタルシリコン薄膜の結晶組織の断面写真である。

【図7】マイクロクリスタルシリコン薄膜の結晶組織を構成している結晶粒の膜厚方向長さを定義する説明図である。

【図8】この発明の原理を示すもので、累積度数分布(縦軸)と(マイクロクリスタルシリコン薄膜の結晶粒の長さ)/(マイクロクリスタルシリコン薄膜の膜厚)(横軸)との関係を示す累積度数分布表である。

【図9】この発明の原理を示すもので、累積度数分布(縦軸)と(マイクロクリスタルシリコン薄膜の結晶粒の長さ)/(マイクロクリスタルシリコン薄膜の膜厚)(横軸)との関係を示す累積度数分布表である。

【図10】この発明の原理を示すもので、マイクロクリスタルシリコン薄膜の成膜条件と膜剥れとの対応関係を示す説明図である。

【図11】従来の積層配線を用いた半導体装置を示す断面図である。

【発明を実施するための形態】

【0018】

積層配線を構成するマイクロクリスタルシリコン薄膜8は、例えば100nmの膜厚のうち、下部の20nmについては成膜速度が13nm/minの成膜条件で形成し、残りの上部の80nmについては成膜速度が24nm/minの成膜条件で形成する。次に、450℃で4時間、窒素雰囲気中で活性化処理し、さらに400℃で30分間、水素化処理を行う。

【0019】

〔発明の原理〕

この発明の発明者らは鋭意研究を重ねた結果、活性化工程や水素化工程等の熱処理工程後に膜剥れが生じたマイクロクリスタルシリコン薄膜と、熱処理工程後でも膜剥れが生じなかったマイクロクリスタルシリコン薄膜とでは、この薄膜の結晶組織を構成している結晶粒の大きさが異なることを見い出した。

【0020】

図5は、熱処理工程後でも膜剥れが生じなかったマイクロクリスタルシリコン薄膜の結晶組織の断面写真、図6は熱処理工程後に膜剥れが生じたマイクロクリスタルシリコン薄膜の結晶組織の断面写真である。両図を比較すれば明らかなように、図5の膜剥れが生じなかったマイクロクリスタルシリコン薄膜の結晶組織の結晶粒は比較的小さなものが多く、一方図6の膜剥れが生じたマイクロクリスタルシリコン薄膜の結晶組織の結晶粒は比較的大きなものが多く、しかも膜厚方向に成長したものが多く観察された。このように膜剥れが生じたマイクロクリスタルシリコン薄膜は、熱処理工程中に上層の金属薄膜との間でシリサイド化反応を起こして、膜厚方向に成長した結晶粒が多くなっている。

【0021】

したがって、マイクロクリスタルシリコン薄膜の結晶組織を構成している結晶粒の大きさが膜剥れにどのような影響を与えるかを突き止めるべく、図5及び図6の断面写真から結晶粒の大きさを特定した。このように結晶粒の大きさを特定するために、図7に示すように、結晶粒の周囲部分に内接する四角形を描いて、この四角形の縦の長さLを求めて各結晶粒の膜厚方向の長さと定義した。

【0022】

次に、各結晶粒の長さを膜厚で規格化して、図8及び図9に示したような累積度数分布表を作成した。図8及び図9において、縦軸は累積度数分布(%)を示し、横軸は(マイクロクリスタルシリコン薄膜の結晶粒の長さ)/(マイクロクリスタルシリコン薄膜の膜厚)を示している。なお、□印は膜剥れ無、他は膜剥れ有を示している。

【0023】

図8は、マイクロクリスタルシリコン薄膜に膜剥れが生じない場合は、マイクロクリスタルシリコン薄膜の膜厚方向の長さがマイクロクリスタルシリコン薄膜の膜厚の60%以上である結晶粒が、マイクロクリスタルシリコン薄膜の結晶粒の全数の15%以下であることを示している。

【0024】

一方、図9は、マイクロクリスタルシリコン薄膜に膜剥れが生じない場合は、イクロクリスタルシリコン薄膜の膜厚方向の長さがマイクロクリスタルシリコン薄膜の膜厚の50%以下である結晶粒が、マイクロクリスタルシリコン薄膜の結晶粒の全数の85%以上であることを示している。したがって、図8あるいは図9の条件を満足するようにマイクロクリスタルシリコン薄膜を形成することにより、膜剥れの発生を防止することができるようになる。

【0025】

また、この発明の発明者らは、上述のように膜剥れの発生を防止できるマイクロクリスタルシリコン薄膜を形成できる成膜条件を見い出して、図10に示すような結果を得た。同図は、成膜条件と膜剥れとの対応関係を示す説明図で、前提として膜厚が100nmのマイクロクリスタルシリコン薄膜を形成する例で示している。

【0026】

同図において、No.1は、13nm/min(分)の成膜条件で100nmを形成した場合を示し、4時間の活性化及び30分の水素化を行っても、膜剥れが発生しなかった。No.2は、24nm/minの成膜条件で100nmを形成した場合を示し、4時間の活性化及び30分の水素化を行って、膜剥れが発生した。この膜剥れが発生した理由は、No.1と比較して生産性向上を図るため成膜速度を大きくしたことにより、膜質が悪くなり金属薄膜とのシリサイド化反応がより加速されたためである。

【0027】

また、No.3は、13nm/minの成膜条件で下部の20nmを形成した後、24nm/minの成膜条件で上部の80nmを形成した場合を示し、4時間の活性化及び30分の水素化を行っても、膜剥れが発生しなかった。この膜剥れが発生しなかった理由は、膜質が良くなる成膜条件で下部の20nmの膜厚を形成したことにより、金属薄膜とのシリサイド化反応が抑制されたためである。

【0028】

No.4はNo.3とは逆に、24nm/minの成膜条件で下部の80nmを形成した後、13nm/minの成膜条件で上部の20nmを形成した場合を示し、4時間の活性化及び30分の水素化を行っても、膜剥れが発生しなかった。この膜剥れが発生しなかった理由は、膜質が良くなる成膜条件で上部の20nmの膜厚を形成したことにより、金属薄膜とのシリサイド化反応が抑制されたためである。すなわち、No.3及びNo.4から明らかなように、膜質が良くなる成膜条件で膜厚を形成すればマイクロクリスタルシリコン薄膜の下部であっても、上部であっても金属薄膜とのシリサイド化反応が抑制されて膜剥れは発生しないことが確認された。

【0029】

また、No.5は、24nm/minの成膜条件で100nmを形成した後、短い1時間の活性化を行っても、膜剥れが発生しなかった。この膜剥れが発生しない理由は、活性化時間を短縮したことにより熱処理による影響を少なくできたためである。No.6は、24nm/minの成膜条件で100nmを形成した後、短い5分間の活性化を行っても、膜剥れが発生しなかった。

【0030】

この膜剥れが発生しない理由は、水素化時間を短縮したことにより熱処理による影響を少なくできたためである。すなわち、No.5及びNo.6から明らかなように、膜質が良くならない成膜条件で膜厚を形成しても活性化時間あるいは水素化時間を短縮すれば金属薄膜とのシリサイド化反応が抑制されて膜剥れは発生しないことが確認された。

【0031】

また、No.7は、24nm/minの成膜条件で100nmを形成した後、短い1時間の活性化及び5分間の水素化を行っても、膜剥れが発生しなかった。この膜剥れが発生しない理由は、活性化時間及び水素化を短縮したことにより熱処理による影響を少なくできたためである。このように、No.7から明らかなように、膜質が良くならない成膜条件で膜厚を形成しても活性化時間及び水素化時間を短縮すれば金属薄膜とのシリサイド化反応が抑制されて膜剥れは発生しないことが確認された。

【実施例1】

【0032】

以下、上述の原理を基に、図面を参照して、この発明の実施例1について説明する。

図1は、この発明の実施例1である積層配線を用いた半導体装置を示す断面図である。以下、図1を参照して同半導体装置の構成を説明する。なお、この例では半導体装置としてはポリシリコンTFTに適用した例で説明する。

【0033】

この例の積層配線を用いたポリシリコンTFT(半導体装置)20は、図1に示すように、ガラス、石英等から成る絶縁性基板1と、この絶縁性基板1上に形成された膜厚が150nmの二酸化シリコン膜から成る下地絶縁膜2と、この下地絶縁膜2上に形成された膜厚が50nmのポリシリコン薄膜3と、このポリシリコン薄膜3両端領域にそれぞれ形成されたソース領域4及びドレイン領域5と、両領域4、5間に形成されたチャネル領域6と、ポリシリコン薄膜3上に形成された膜厚が100nmの二酸化シリコン膜から成るゲート絶縁膜7と、このゲート絶縁膜7上に形成された膜厚が100nmのマイクロクリスタルシリコン薄膜(下層)8と膜厚が200nmのクロム薄膜(上層)から成る金属薄膜9との積層配線から構成されたゲート電極10とを備えている。

【0034】

ここで、ゲート電極10の下層を構成しているマイクロクリスタルシリコン薄膜8は、マイクロクリスタルシリコン薄膜8の膜厚方向の長さがマイクロクリスタルシリコン薄膜8の膜厚の60%以上(この例では、略60nm以上)である結晶粒が、マイクロクリスタルシリコン薄膜8の結晶粒の全数の15%以下となるように形成されている。あるいは、マイクロクリスタルシリコン薄膜8は、マイクロクリスタルシリコン薄膜8の膜厚方向の長さがマイクロクリスタルシリコン薄膜8の膜厚の50%以下(この例では、略50nm以下)である結晶粒が、マイクロクリスタルシリコン薄膜8の結晶粒の全数の85%以上となるように形成されている。

【0035】

さらに、このポリシリコンTFT20は、図1に示すように、ゲート電極10を含む全面に形成された膜厚が400nmの二酸化シリコン膜から成る層間絶縁膜11と、この層間絶縁膜11にそれぞれ開孔されたコンタクトホール12、13を通じてソース領域4及びドレイン領域5に接触するように形成された膜厚が500nmのアルミニウム膜から成るソース電極14及びドレイン電極15とを備えている。

【0036】

上述したようなこの例のポリシリコンTFT20によれば、ゲート電極10を構成しているマイクロクリスタルシリコン薄膜8は、前述の発明の原理の図8あるいは図9に基づいて、マイクロクリスタルシリコン薄膜8の膜厚方向の長さがマイクロクリスタルシリコン薄膜8の膜厚の60%以上である結晶粒が、マイクロクリスタルシリコン薄膜8の結晶粒の全数の15%以下となるように、あるいは、マイクロクリスタルシリコン薄膜8は、マイクロクリスタルシリコン薄膜8の膜厚方向の長さがマイクロクリスタルシリコン薄膜8の膜厚の50%以下である結晶粒が、マイクロクリスタルシリコン薄膜8の結晶粒の全数の85%以上となるように形成されている。

したがって、マイクロクリスタルシリコン薄膜8と金属薄膜9との過剰なシリサイド化反応を抑制することができるので、マイクロクリスタルシリコン薄膜8の膜剥れを防止することができる。

【実施例2】

【0037】

図2乃至図4は、この発明の実施例2であるポリシリコンTFTの製造方法(第1の製造方法)を工程順に示す工程図である。以下、図2乃至図4を参照して工程順に説明する。

まず、図2(a)に示すように、絶縁性基板1の一例のガラス基板として日本電気硝子社製OA−10を用意し、プラズマCVD法によりSiH4ガス及びN2Oガスを原料ガスとして、そのガラス基板上に膜厚が150nmの二酸化シリコン薄膜を堆積して下地絶縁膜2を形成した。次に、プラズマCVD法によりSiH4ガスを原料ガスとして、下地絶縁膜2上に膜厚が50nmのアモルファスシリコン薄膜16を堆積した。次に、アモルファスシリコン薄膜16中の水素を離脱させるために、約500℃で熱処理を行った。

【0038】

次に、図2(b)に示すように、レーザアニール法により、波長が308nmのXeCl(塩化キセノン)エキシマレーザ光をアモルファスシリコン薄膜16に照射してこの薄膜16を変質させて下地絶縁膜2上にポリシリコン薄膜3を形成した。次に、図2(c)に示すように、通常のフォトレジスト法により、ポリシリコン薄膜3の全面に塗布したレジストをパターニングして所望の形状のレジストマスク17を形成し、このレジストマスク17を用いてドライエッチング法によりCF4ガス及びO2ガスを原料ガスとして、ポリシリコン薄膜3をエッチングしてアイランド化した。

【0039】

次に、図3(d)に示すように、プラズマCVD法により、Si(OC2H5)4(テトラ・エチル・オルソ・シリケート:TEOS)ガス及びO2ガスを原料ガスとして、アイランド化されたポリシリコン薄膜3上に膜厚が100nmの二酸化シリコン薄膜を堆積してゲート絶縁膜7を形成した。次に、プラズマCVD法により、SiH4ガス、PH3(H2希釈5%)ガス及びH2ガスを原料ガスとして、ゲート絶縁膜7上に膜厚が100nmのマイクロクリスタルシリコン薄膜8を堆積した。このとき、前述の発明の原理の図10のNo.3の成膜条件に基づいて、マイクロクリスタルシリコン薄膜8の100nmの膜厚のうち、下部の20nmは成膜速度が13nm/minの成膜条件で形成し、上部の80nmは成膜速度が24nm/minの成膜条件で形成した。ここで、下部の20nmについては、SiH4 流量が20sccm(Standard cubic centimeter per minute)、PH3流量が65sccm、H2流量が2500sccm、圧力が260Pa(Pascal)、放電電力密度が1.25W/cm2、基板温度が350℃の条件で、95秒間放電して形成した。一方、上部の80nmについては、SiH4流量が40sccm、PH3流量が65sccm、H2流量が2500sccm、圧力が260Pa、放電電力密度が1.25W/cm2、基板温度が350℃の条件で、201秒間放電して形成した。

【0040】

このように、マイクロクリスタルシリコン薄膜8の膜厚100nmのうち、下部の20nmについては成膜速度が13nm/minの成膜条件で形成し、残りの上部の80nmについては成膜速度が24nm/minの成膜条件で形成したので、膜厚100nmをすべて13nm/minの成膜条件で形成した場合に比較して、生産性を大幅に向上させることができる。

【0041】

次に、スパッタリング法により、マイクロクリスタルシリコン薄膜8上に膜厚が200nmのクロム薄膜から成る金属薄膜9を形成した。次に、図3(e)に示すように、通常のフォトレジスト法により、金属薄膜9の全面に塗布したレジストをパターニングして所望の形状のレジストマスク18を形成し、このレジストマスク18を用いてドライエッチング法によりCl2ガス及びO2ガスを原料ガスとして、金属薄膜9及びマイクロクリスタルシリコン薄膜8をエッチング(パターニング)してゲート電極10を形成した。このゲート電極10は、膜厚が100nmのマイクロクリスタルシリコン薄膜(下層)8と、膜厚が200nmのクロム薄膜(上層)から成る金属薄膜9とから成る積層配線から構成されている。

【0042】

次に、レジストマスク18を除去した後、図3(f)に示すように、イオンドーピング法によりPH3(H2希釈5%)を用いて、加速電圧が50keV、ドーズ量が3×1015cm−2、圧力が0.02Paのドーピング条件で、ゲート電極10のパターンをマスクとした自己整合法により、不純物としてリン(P)をゲート絶縁膜7を通じてポリシリコン薄膜3に導入してソース領域4及びドレイン領域5を形成した。

【0043】

次に、図4(g)に示すように、プラズマCVD法により、TEOS及びO2ガスを原料ガスとして、全面に膜厚が400nmの二酸化シリコン薄膜を堆積して層間絶縁膜11を形成した。次に、ポリシリコン薄膜3中に導入したリンを活性化するために、450℃で4時間、窒素雰囲気中で熱処理を行った(活性化工程)。この活性化は例えば、アニール炉を用いたファーネスアニール法により行う。次に、ポリシリコン薄膜3及びポリシリコン薄膜3とゲート絶縁膜7との界面のダングリングボンドを終端させるために、400℃で30分間、水素プラズマ中で熱処理を行った(水素化工程)。

【0044】

このような活性化工程及び水素化工程の間に、マイクロクリスタルシリコン薄膜8はこの上層の金属薄膜9であるクロム薄膜とシリサイド化反応を起こすが、このシリサイド化反応が過剰になるとマイクロクリスタルシリコン薄膜8が膜剥れを起こす原因となる。しかしながら、前述したように、マイクロクリスタルシリコン薄膜8は100nmの膜厚のうち、下部の20nmは成膜速度が13nm/minの、膜質が良くなる成膜条件で形成されているため、マイクロクリスタルシリコン薄膜8はシリサイド化反応が抑制されるので、膜剥れを防止することができる。

【0045】

次に、図4(h)に示すように、プラズマCVD法により、通常のフォトレジスト法により、層間絶縁膜11の全面に塗布したレジストをパターニングして所望の形状のレジストマスク(図示せず)を形成し、このレジストマスクを用いてドライエッチング法によりCF4ガス及びO2ガスを原料ガスとして、層間絶縁膜11及びゲート絶縁膜7を選択的にエッチングしてそれぞれソース領域4及びドレイン領域5を露出させるコンタクトホール12、13を開孔する。

【0046】

次に、そのレジストマスクを除去した後、スパッタリング法により膜厚が500nmのアルミニウム薄膜を全面に堆積する。次に、通常のフォトレジスト法により形成したレジストマスク(図示せず)を用いて、ドライエッチング法によりCl2ガス及びBCl3ガスを原料ガスとして、アルミニウムをエッチングしてソース領域4及びドレイン領域5に接触するようにソース電極14及びドレイン電極15を形成する。次に、そのレジストマスクを除去することにより、図1に示したようなポリシリコンTFT20を完成させる。

【0047】

この例によって形成されたマイクロクリスタルシリコン薄膜8は、マイクロクリスタルシリコン薄膜8の膜厚方向の長さがマイクロクリスタルシリコン薄膜8の膜厚の60%以上である結晶粒が、マイクロクリスタルシリコン薄膜8の結晶粒の全数の6%であり、またマイクロクリスタルシリコン薄膜8の膜厚方向の長さがマイクロクリスタルシリコン薄膜8の膜厚の50%以下である結晶粒が、マイクロクリスタルシリコン薄膜8の結晶粒の全数の94%であった。

【0048】

上述したようなこの例のポリシリコンTFTの製造方法によれば、ゲート電極10を構成しているマイクロクリスタルシリコン薄膜8を、前述の発明の原理の図10のNo.3の成膜条件に基づいて、下部の20nmについては成膜速度が13nm/minの成膜条件で形成し、残りの上部の80nmについては成膜速度が24nm/minの成膜条件で形成したので、上述したような組成の結晶粒を得ることができるため、上層の金属薄膜9との過剰なシリサイド化反応を抑制できるので、マイクロクリスタルシリコン薄膜8の膜剥れを防止することができる。これによって、従来よりも生産性が高くて、信頼性の高いポリシリコンTFTを製造することができる。

【実施例3】

【0049】

次に、この発明の実施例3であるポリシリコンTFTの製造方法(第2の製造方法)を説明する。この実施例3のポリシリコンTFTの製造方法の構成が、上述の実施例2(第1の製造方法)のそれと大きく異なるところは、マイクロクリスタルシリコン薄膜を異なる成膜条件で形成するようにした点である。なお、この第2の製造方法では、工程図は第1の製造方法と略同じなので図示は省略する。

この第2の製造方法では、前述の発明の原理の図10のNo.4の成膜条件に基づいて、マイクロクリスタルシリコン薄膜8の100nmの膜厚のうち、下部の80nmは成膜速度が24nm/minの成膜条件で形成し、上部の20nmは成膜速度が13nm/minの成膜条件で形成した。ここで、下部の80nmについては、SiH4流量が40sccm、PH3流量が65sccm、H2流量が2500sccm、圧力が260Pa、放電電力密度が1.25W/cm2、基板温度が350℃の条件で、201秒間放電して形成した。一方、上部の20nmについては、SiH4流量が20sccm、PH3流量が65sccm、H2流量が2500sccm、圧力が260Pa、放電電力密度が1.25W/cm2、基板温度が350℃の条件で、95秒間放電して形成した。

これ以外は、上述した第1の製造方法と略同様である.それゆえ、説明を省略する。

【0050】

この例によって形成されたマイクロクリスタルシリコン薄膜8は、マイクロクリスタルシリコン薄膜8の膜厚方向の長さがマイクロクリスタルシリコン薄膜8の膜厚の60%以上である結晶粒が、マイクロクリスタルシリコン薄膜8の結晶粒の全数の13%であり、またマイクロクリスタルシリコン薄膜8の膜厚方向の長さがマイクロクリスタルシリコン薄膜8の膜厚の50%以下である結晶粒が、マイクロクリスタルシリコン薄膜8の結晶粒の全数の87%であった。

【0051】

上述したようなこの例のポリシリコンTFTの製造方法によれば、ゲート電極10を構成しているマイクロクリスタルシリコン薄膜8を、前述の発明の原理の図10のNo.4の成膜条件に基づいて、下部の80nmについては成膜速度が24nm/minの成膜条件で形成し、残りの上部の20nmについては成膜速度が13nm/minの成膜条件で形成したので、上述したような組成の結晶粒を得ることができるため、上層の金属薄膜9との過剰なシリサイド化反応を抑制できるので、マイクロクリスタルシリコン薄膜8の膜剥れを防止することができる。これによって、従来よりも生産性が高くて、信頼性の高いポリシリコンTFTを製造することができる。

【実施例4】

【0052】

次に、この発明の実施例4であるポリシリコンTFTの製造方法(第3の製造方法)を説明する。この実施例4のポリシリコンTFTの製造方法の構成が、上述の実施例2(第1の製造方法)のそれと大きく異なるところは、マイクロクリスタルシリコン薄膜を異なる成膜条件で形成するようにした点である。

この第3の製造方法では、前述の発明の原理の図10のNo.5の成膜条件に基づいて、マイクロクリスタルシリコン薄膜8の100nmを、成膜速度が24nm/minの成膜条件で形成した。そして、SiH4流量が40sccm、PH3流量が65sccm、H2流量が2500sccm、圧力が260Pa、放電電力密度が1.25W/cm2、基板温度が350℃の条件で、201秒間放電して形成した。一方、上部の20nmについては、SiH4流量が20sccm、PH3流量が65sccm、H2流量が2500sccm、圧力が260Pa、放電電力密度が1.25W/cm2、基板温度が350℃の条件で、251秒間放電して形成した。

【0053】

次に、ポリシリコン薄膜3中に導入したリンを活性化するために、450℃で1時間、窒素雰囲気中で熱処理を行った(活性化工程)。次に、ポリシリコン薄膜3及びポリシリコン薄膜3とゲート絶縁膜7との界面のダングリングボンドを終端させるために、第2の製造方法と同様に400℃で30分間、水素プラズマ中で熱処理を行った(水素化工程)。

【0054】

この例によって形成されたマイクロクリスタルシリコン薄膜8は、マイクロクリスタルシリコン薄膜8の膜厚方向の長さがマイクロクリスタルシリコン薄膜8の膜厚の60%以上である結晶粒が、マイクロクリスタルシリコン薄膜8の結晶粒の全数の9%であり、またマイクロクリスタルシリコン薄膜8の膜厚方向の長さがマイクロクリスタルシリコン薄膜8の膜厚の50%以下である結晶粒が、マイクロクリスタルシリコン薄膜8の結晶粒の全数の91%であった。

【0055】

上述したようなこの例のポリシリコンTFTの製造方法によれば、ゲート電極10を構成しているマイクロクリスタルシリコン薄膜8を、前述の発明の原理の図10のNo.5の成膜条件に基づいて、成膜速度が24nm/minの成膜条件でマイクロクリスタルシリコン薄膜8を100nm形成し、また450℃で1時間活性化した後、400℃で30分間水素化したので、上述したような組成の結晶粒を得ることができる。したがって、上層の金属薄膜9との過剰なシリサイド化反応を抑制できるので、マイクロクリスタルシリコン薄膜8の膜剥れを防止することができる。これによって、従来よりも生産性が高くて、信頼性の高いポリシリコンTFTを製造することができる。

【実施例5】

【0056】

次に、この発明の実施例5であるポリシリコンTFTの製造方法(第4の製造方法)を説明する。この実施例5のポリシリコンTFTの製造方法の構成が、上述の実施例2(第1の製造方法)のそれと大きく異なるところは、マイクロクリスタルシリコン薄膜を異なる成膜条件で形成するようにした点である。

この第4の製造方法では、前述の発明の原理の図10のNo.6の成膜条件に基づいて、マイクロクリスタルシリコン薄膜8の100nmを、成膜速度が24nm/minの成膜条件で形成した。次に、ポリシリコン薄膜3中に導入したリンを活性化するために、450℃で4時間、窒素雰囲気中で熱処理を行った(活性化工程)。次に、ポリシリコン薄膜3及びポリシリコン薄膜3とゲート絶縁膜7との界面のダングリングボンドを終端させるために、400℃で5分間、水素プラズマ中で熱処理を行った(水素化工程)。

【0057】

この例によって形成されたマイクロクリスタルシリコン薄膜8は、マイクロクリスタルシリコン薄膜8の膜厚方向の長さがマイクロクリスタルシリコン薄膜8の膜厚の60%以上である結晶粒が、マイクロクリスタルシリコン薄膜8の結晶粒の全数の9%であり、またマイクロクリスタルシリコン薄膜8の膜厚方向の長さがマイクロクリスタルシリコン薄膜8の膜厚の50%以下である結晶粒が、マイクロクリスタルシリコン薄膜8の結晶粒の全数の91%であった。

【0058】

上述したようなこの例のポリシリコンTFTの製造方法によれば、ゲート電極10を構成しているマイクロクリスタルシリコン薄膜8を、前述の発明の原理の図10のNo.6の成膜条件に基づいて、成膜速度が24nm/minの成膜条件でマイクロクリスタルシリコン薄膜8を100nm形成し、また450℃で4時間活性化した後、400℃で5分間水素化したので、上述したような組成の結晶粒を得ることができる。したがって、上層の金属薄膜9との過剰なシリサイド化反応を抑制できるので、マイクロクリスタルシリコン薄膜8の膜剥れを防止することができる。これによって、従来よりも生産性が高くて、信頼性の高いポリシリコンTFTを製造することができる。

【実施例6】

【0059】

次に、この発明の実施例6であるポリシリコンTFTの製造方法(第5の製造方法)を説明する。この実施例6のポリシリコンTFTの製造方法の構成が、上述の実施例2(第1の製造方法)のそれと大きく異なるところは、マイクロクリスタルシリコン薄膜を異なる成膜条件で形成するようにした点である。

この第5の製造方法では、マイクロクリスタルシリコン薄膜8の100nmを、成膜速度が24nm/minの成膜条件で形成した。次に、ポリシリコン薄膜3中に導入したリンを活性化するために、450℃で1時間、窒素雰囲気中で熱処理を行った(活性化工程)。次に、ポリシリコン薄膜3及びポリシリコン薄膜3とゲート絶縁膜7との界面のダングリングボンドを終端させるために、水素プラズマ中で熱処理を行った(水素化工程)。

【0060】

この例によって形成されたマイクロクリスタルシリコン薄膜8は、マイクロクリスタルシリコン薄膜8の膜厚方向の長さがマイクロクリスタルシリコン薄膜8の膜厚の60%以上である結晶粒が、マイクロクリスタルシリコン薄膜8の結晶粒の全数の13%であり、またマイクロクリスタルシリコン薄膜8の膜厚方向の長さがマイクロクリスタルシリコン薄膜8の膜厚の50%以下である結晶粒が、マイクロクリスタルシリコン薄膜8の結晶粒の全数の87%であった。

【0061】

上述したようなこの例のポリシリコンTFTの製造方法によれば、ゲート電極10を構成しているマイクロクリスタルシリコン薄膜8を、成膜速度が24nm/minの成膜条件でマイクロクリスタルシリコン薄膜8を100nm形成し、また450℃で1時間活性化した後、水素化したので、上述したような組成の結晶粒を得ることができる。したがって、上層の金属薄膜9との過剰なシリサイド化反応を抑制できるので、マイクロクリスタルシリコン薄膜8の膜剥れを防止することができる。これによって、従来よりも生産性が高くて、信頼性の高いポリシリコンTFTを製造することができる。

【0062】

以上のように、実施例1のポリシリコンTFT20を製造する第1乃至第5の製造方法(実施例2乃至実施例6)を述べたが、各製造方法を総合すると、マイクロクリスタルシリコン薄膜8の膜厚方向の長さがマイクロクリスタルシリコン薄膜8の膜厚の60%以上である結晶粒は、マイクロクリスタルシリコン薄膜8の結晶粒の全数の6〜9%となり、またマイクロクリスタルシリコン薄膜8の膜厚方向の長さがマイクロクリスタルシリコン薄膜8の膜厚の50%以下である結晶粒は、マイクロクリスタルシリコン薄膜8の結晶粒の全数の87〜91%となる。

【0063】

以上、この発明の実施例を図面により詳述してきたが、具体的な構成はこの実施例に限られるものではなく、この発明の要旨を逸脱しない範囲の設計の変更等があってもこの発明に含まれる。例えば、実施例では、マイクロクリスタルシリコン薄膜を含む積層配線をポリシリコンTFTのゲート電極に用いた例で説明したが、ゲート電極に限らずにあるいはTFTに限らずに各種電子部品の配線に適用することができる。また、活性化工程は400℃で行う例で説明したが、400℃以上で行っても略同様な効果を得ることができる。また、水素化工程は400℃で行う例で説明したが、350℃以上で行っても略同様な効果を得ることができる。

【0064】

また、下地絶縁膜、ゲート絶縁膜及び層間絶縁膜等をプラズマCVD法により形成する例で説明したが、プラズマCVD法に限ることなく、減圧CVD法によりSiH4ガス及びN2Oガスを原料ガスとして形成する場合にも同様に適用される。また、下地絶縁膜、ゲート絶縁膜及び層間絶縁膜等を二酸化シリコン薄膜により構成する例で説明したが、二酸化シリコン薄膜に限らずに窒化シリコン薄膜,酸窒化シリコン薄膜等の他の絶縁膜を用いることもできる。また、アモルファスシリコン薄膜をプラズマCVD法により形成する例で説明したが、減圧CVD法によりSi2H6を原料ガスとして形成する場合にも同様に適用される。また、ゲート電極の上層の金属薄膜としてはクロム薄膜を用いる例で説明したが、クロムに代えてアルミニウム、モリブデン、タングステン、ニオブ、あるいはこれらの合金等の他の金属を使用することもできる。また、活性化工程ではアニール炉を用いたファーネスアニール法により行う例で説明したが、これに代えてレーザ光を用いたレーザアニール法、あるいは高温窒素ガスを吹き付けるRTA(Rapid Thermal Anneal)法等を用いることができる。また、水素化工程では水素プラズマに代えて、水素雰囲気中に晒すようにしてもよい。また、層間絶縁膜の形成は水素化工程あるいは水素化工程の終了後に形成してもよい。

【産業上の利用可能性】

【0065】

この発明は、ゲート電極やTFTに限らず、各種電子部品の配線に適用することができる。

【符号の説明】

【0066】

1 絶縁性基板

2 下地絶縁膜

3 ポリシリコン薄膜

4 ソース領域

5 ドレイン領域

6 チャネル領域

7 ゲート絶縁膜

8 マイクロクリスタルシリコン薄膜

9 金属薄膜

10 ゲート電極

11 層間絶縁膜

12,13 コンタクトホール

14 ソース電極

15 ドレイン電極

16 アモルファスシリコン薄膜

17,18 レジストマスク

20 ポリシリコンTFT(半導体装置)

【技術分野】

【0001】

この発明は、積層配線、該積層配線を用いた半導体装置及びその製造方法に係り、詳しくは、薄膜トランジスタのゲート電極等に適用されるマイクロクリスタルシリコン薄膜を含む積層配線、該積層配線を用いた半導体装置及びその製造方法に関する。

【背景技術】

【0002】

例えば、表示装置の代表として知られている液晶表示装置(Liquid Crystal Device:LCD)においては、アモルファス(非結晶)シリコン薄膜を活性層とするアモルファスシリコン薄膜トランジスタ(Thin Film Transistor:TFT)を用いることが主流となっている。しかしながら、アモルファスシリコン薄膜は移動度が低いので、LCDを高精細に実現することが困難であるため、より移動度の高いポリ(多結晶)シリコン薄膜を活性層とするポリシリコンTFTが注目されている。

【0003】

一方で、LCDにおける用途の多様化により、薄型化・小型化に対する要求も強く、その要求に応えるため、アクティブマトリクス基板上に駆動回路も同様にTFTで形成する試みがなされている。しかし、この駆動回路用のTFTをアモルファスシリコン薄膜を用いて形成することは、動作速度及び駆動能力の点で好ましくなく、より移動度の高いポリシリコン薄膜を用いて形成することが求められている。ポリシリコン薄膜の形成方法としては、プロセス温度の低温化、スループット向上及び低コスト化の点から、安価な低温ガラス基板上にポリシリコン薄膜を形成可能なレーザアニール法が主流となっている。

【0004】

しかしながら、ポリシリコンTFTはゲート電極の信頼性が低く、かつ低抵抗化が難しいので、LCDを高精細に実現するのが困難であるという問題がある。この問題を解決するために、例えば特許文献1、特許文献2、特許文献3あるいは特許文献4に開示されているように、ゲート電極をマイクロクリスタルシリコン薄膜(下層)と金属薄膜(上層)とから成る積層配線により構成するようにしたポリシリコンTFTが提供されている。

【0005】

図11は、例えば、特許文献1に開示された上記のマイクロクリスタルシリコン薄膜を含む積層配線がゲート電極に適用された従来のポリシリコンTFTを示す断面図である。同ポリシリコンTFT100は、絶縁性基板101と、この絶縁性基板101上に形成された下地絶縁膜102と、この下地絶縁膜102上に形成されたポリシリコン薄膜103と、このポリシリコン薄膜103の両端領域にそれぞれ形成されたソース領域104及びドレイン領域105と、ポリシリコン薄膜103上に形成されたゲート絶縁膜106と、このゲート絶縁膜106上に形成されたマイクロクリスタルシリコン薄膜(下層)107と金属薄膜(上層)108とから成る積層配線により構成されたゲート電極109とを備えている。さらに、このポリシリコンTFT100は、ゲート電極109を含む全面に形成された層間絶縁膜110と、この層間絶縁膜110にそれぞれ開孔されたコンタクトホール111、112を通じて両領域104,105に接触するように形成されたソース電極113及びドレイン電極114とを備えている。

【0006】

ここで、ゲート電極109を構成しているマイクロクリスタルシリコン薄膜107は、プラズマCVD(Chemical Vapor Deposition)法によって形成されたシリコン薄膜であり、その結晶組織には極めて微細な結晶粒とアモルファスとが混在している。このマイクロクリスタルシリコン薄膜の成膜温度は300℃程度であり、従来のポリシリコン薄膜の成膜方法としての減圧CVD法や常圧CVD法のそれが600℃程度であるのに比較してかなり低い温度なので、成膜工程のスループット及び製造コストの点で極めて優れているため、生産性に富んでいるというメリットがある。また、マイクロクリスタルシリコン薄膜は、ゲート絶縁膜及び活性層のポリシリコン薄膜からの水素の過剰な離脱を防ぐこともできる。さらに、マイクロクリスタルシリコン薄膜には、微細な結晶粒が存在するために、ポリシリコン薄膜と同程度の低抵抗化が可能になっている。したがって、マイクロクリスタルシリコン薄膜上に金属薄膜を積層して形成した積層配線をTFTのゲート電極に適用することにより、ゲート電極の信頼性が高く、かつ低抵抗化が図れるので、LCDを高精細に実現するのが容易となる。

【先行技術文献】

【特許文献】

【0007】

【特許文献1】特許第3282582号公報

【特許文献2】特許第3613221号公報

【特許文献3】特開2004−336073号公報

【特許文献4】特開2004−281506号公報

【発明の概要】

【発明が解決しようとする課題】

【0008】

ところで、従来のマイクロクリスタルシリコン薄膜と金属薄膜とから成る積層配線では、熱処理時に下層のマイクロクリスタルシリコン薄膜と上層の金属薄膜との間でシリサイド化反応が起きるので、マイクロクリスタルシリコン薄膜に膜剥れが生ずる、という問題がある。

すなわち、上述したような積層配線がポリシリコンTFTのゲート電極に適用された場合、TFTの製造過程では、ポリシリコン薄膜中に予め導入したリンやボロン等の不純物を活性化するためのアニール工程(活性化工程)や、ポリシリコン薄膜中及びポリシリコン薄膜とゲート絶縁膜との界面に存在する未結合手(ダングリングボンド)を水素で終端するための水素化工程が必要になっている。そして、これら活性化工程及び水素化工程ではいずれも、マイクロクリスタルシリコン薄膜及び金属薄膜の成膜温度よりも高い温度での熱処理を伴うので、既に形成されているマイクロクリスタルシリコン薄膜がその熱処理の影響を受けて上述のシリサイド化反応が起きるのを回避できない。

【0009】

ところで、下層のマイクロクリスタルシリコン薄膜と上層の金属薄膜との間でシリサイド化反応が過剰に起きると、マイクロクリスタルシリコン薄膜の結晶組織を構成している結晶の形状が粒状から柱状へと変化する。そして、このように結晶の形状が変化する際に、マイクロクリスタルシリコン薄膜の体積に変化が生ずるので、マイクロクリスタルシリコン薄膜中や、下層のマイクロクリスタルシリコン薄膜と上層の金属薄膜との界面にボイドが発生して、このボイドの影響でマイクロクリスタルシリコン薄膜には最終的に膜剥れが起きるようになる。

【0010】

ここで、特許文献1に記載されているように、マイクロクリスタルシリコン薄膜をプラズマCVD法によって形成することは、減圧CVD法や常圧CVD法によりポリシリコン薄膜を形成する場合に比較して生産性に富んでいるというメリットがある。その一方で更なる生産性向上の要求に応えるには、プラズマCVD法によってより成膜速度の速い条件でマイクロクリスタルシリコン薄膜を形成する必要がある。しかしながら、一般に成膜速度の速い条件で形成した薄膜の膜質は悪くなり易いという傾向がある。したがって、マイクロクリスタルシリコン薄膜の膜質が悪くなると、この上に形成される金属薄膜との間で発生するシリサイド化反応がより加速されて、マイクロクリスタルシリコン薄膜の膜剥れが起き易くなるので、結果的に積層配線の膜剥れに結びつくことになる。

【0011】

この発明は、上述の事情に鑑みてなされたもので、マイクロクリスタルシリコン薄膜と金属薄膜との過剰なシリサイド化反応を抑制して、マイクロクリスタルシリコン薄膜の膜剥れを防止することができるようにした積層配線、該積層配線を用いた半導体装置及びその製造方法を提供することを目的としている。

【課題を解決するための手段】

【0012】

上記課題を解決するために、この発明の第1の構成は、電子部品の配線として備えられ、マイクロクリスタルシリコン薄膜と該薄膜上に形成された金属薄膜とから成る積層配線に係り、前記マイクロクリスタルシリコン薄膜の結晶組織を構成している結晶粒には、前記電子部品の製造時の熱処理で生じた前記金属薄膜とのシリサイド化反応に起因して膜厚方向に成長した柱状の結晶粒が含まれ、前記マイクロクリスタルシリコン薄膜の膜厚方向の長さが前記マイクロクリスタルシリコン薄膜の膜厚の60%以上である結晶粒が、前記マイクロクリスタルシリコン薄膜の結晶粒の全数の6%以上15%以下であることを特徴としている。

【0013】

また、この発明の第2の構成は、電子部品の配線として備えられ、マイクロクリスタルシリコン薄膜と該薄膜上に形成された金属薄膜とから成る積層配線に係り、前記マイクロクリスタルシリコン薄膜の結晶組織を構成している結晶粒には、前記電子部品の製造時の熱処理で生じた前記金属薄膜とのシリサイド化反応に起因して膜厚方向に成長した柱状の結晶粒が含まれ、前記マイクロクリスタルシリコン薄膜の膜厚方向の長さが前記マイクロクリスタルシリコン薄膜の膜厚の50%以下である結晶粒が、前記マイクロクリスタルシリコン薄膜の結晶粒の全数の85%以上91%以下であることを特徴としている。

【0014】

また、この発明の第3の構成は、半導体装置の製造方法に係り、絶縁性基板上に下地絶縁膜を介してアモルファスシリコン薄膜を形成する工程と、前記アモルファスシリコン薄膜にレーザアニール法を施して該アモルファスシリコン薄膜をポリシリコン薄膜に変質させる工程と、前記ポリシリコン薄膜をアイランド化した後、該ポリシリコン薄膜上にゲート絶縁膜を介してマイクロクリスタルシリコン薄膜及び金属薄膜を順次に堆積して積層膜を形成する工程と、前記積層膜を所望の形状にパターニングしてゲート電極を形成する工程と、前記ゲート電極が形成された上記絶縁性基板を熱処理する工程とを有し、前記熱処理後の前記マイクロクリスタルシリコン薄膜の結晶組織を構成している結晶粒には、前記熱処理の際に生じた前記金属薄膜とのシリサイド化反応に起因して膜厚方向に成長した柱状の結晶粒が含まれ、前記マイクロクリスタルシリコン薄膜の膜厚方向の長さが前記マイクロクリスタルシリコン薄膜の膜厚の60%以上である結晶粒が、前記マイクロクリスタルシリコン薄膜の結晶粒の全数の6%以上15%以下である薄膜、あるいは前記マイクロクリスタルシリコン薄膜の膜厚方向の長さが前記マイクロクリスタルシリコン薄膜の膜厚の50%以下である結晶粒が、前記マイクロクリスタルシリコン薄膜の結晶粒の全数の85%以上91%以下である薄膜を形成することを特徴としている。

【発明の効果】

【0015】

この発明の積層配線によれば、マイクロクリスタルシリコン薄膜の結晶組織を構成している結晶粒において、マイクロクリスタルシリコン薄膜の膜厚方向の長さがマイクロクリスタルシリコン薄膜の膜厚の60%以上である結晶粒が、マイクロクリスタルシリコン薄膜の結晶粒の全数の15%以下、あるいは膜厚方向の長さがマイクロクリスタルシリコン薄膜の膜厚の50%以下である結晶粒が、マイクロクリスタルシリコン薄膜の結晶粒の全数の85%以上になっている。したがって、マイクロクリスタルシリコン薄膜と金属薄膜との過剰なシリサイド化反応を抑制することができるので、膜剥れの発生を防止することができる。また、この発明の積層配線の製造方法によれば、少なくとも膜質が悪くならない成膜条件でマイクロクリスタルシリコン薄膜を形成するので、金属薄膜とのシリサイド化反応が抑制されるため膜剥れが発生しない。

【0016】

この発明の半導体装置の製造方法によれば、上記の組成のマイクロクリスタルシリコン薄膜を含む積層配線によりゲート電極を有する半導体装置を形成するようにしたので、ゲート電極の高信頼性及び低抵抗化を低コストで達成することができる。

【図面の簡単な説明】

【0017】

【図1】この発明の実施例1である積層配線を用いた半導体装置を示す断面図である。

【図2】この発明の実施例2である同半導体装置の製造方法を工程順に示す工程図である。

【図3】同半導体装置の製造方法を工程順に示す工程図である。

【図4】同半導体装置の製造方法を工程順に示す工程図である。

【図5】この発明の原理を示すもので、熱処理工程後でも膜剥れが生じなかったマイクロクリスタルシリコン薄膜の結晶組織の断面写真である。

【図6】この発明の原理を示すもので、熱処理工程後に膜剥れが生じたマイクロクリスタルシリコン薄膜の結晶組織の断面写真である。

【図7】マイクロクリスタルシリコン薄膜の結晶組織を構成している結晶粒の膜厚方向長さを定義する説明図である。

【図8】この発明の原理を示すもので、累積度数分布(縦軸)と(マイクロクリスタルシリコン薄膜の結晶粒の長さ)/(マイクロクリスタルシリコン薄膜の膜厚)(横軸)との関係を示す累積度数分布表である。

【図9】この発明の原理を示すもので、累積度数分布(縦軸)と(マイクロクリスタルシリコン薄膜の結晶粒の長さ)/(マイクロクリスタルシリコン薄膜の膜厚)(横軸)との関係を示す累積度数分布表である。

【図10】この発明の原理を示すもので、マイクロクリスタルシリコン薄膜の成膜条件と膜剥れとの対応関係を示す説明図である。

【図11】従来の積層配線を用いた半導体装置を示す断面図である。

【発明を実施するための形態】

【0018】

積層配線を構成するマイクロクリスタルシリコン薄膜8は、例えば100nmの膜厚のうち、下部の20nmについては成膜速度が13nm/minの成膜条件で形成し、残りの上部の80nmについては成膜速度が24nm/minの成膜条件で形成する。次に、450℃で4時間、窒素雰囲気中で活性化処理し、さらに400℃で30分間、水素化処理を行う。

【0019】

〔発明の原理〕

この発明の発明者らは鋭意研究を重ねた結果、活性化工程や水素化工程等の熱処理工程後に膜剥れが生じたマイクロクリスタルシリコン薄膜と、熱処理工程後でも膜剥れが生じなかったマイクロクリスタルシリコン薄膜とでは、この薄膜の結晶組織を構成している結晶粒の大きさが異なることを見い出した。

【0020】

図5は、熱処理工程後でも膜剥れが生じなかったマイクロクリスタルシリコン薄膜の結晶組織の断面写真、図6は熱処理工程後に膜剥れが生じたマイクロクリスタルシリコン薄膜の結晶組織の断面写真である。両図を比較すれば明らかなように、図5の膜剥れが生じなかったマイクロクリスタルシリコン薄膜の結晶組織の結晶粒は比較的小さなものが多く、一方図6の膜剥れが生じたマイクロクリスタルシリコン薄膜の結晶組織の結晶粒は比較的大きなものが多く、しかも膜厚方向に成長したものが多く観察された。このように膜剥れが生じたマイクロクリスタルシリコン薄膜は、熱処理工程中に上層の金属薄膜との間でシリサイド化反応を起こして、膜厚方向に成長した結晶粒が多くなっている。

【0021】

したがって、マイクロクリスタルシリコン薄膜の結晶組織を構成している結晶粒の大きさが膜剥れにどのような影響を与えるかを突き止めるべく、図5及び図6の断面写真から結晶粒の大きさを特定した。このように結晶粒の大きさを特定するために、図7に示すように、結晶粒の周囲部分に内接する四角形を描いて、この四角形の縦の長さLを求めて各結晶粒の膜厚方向の長さと定義した。

【0022】

次に、各結晶粒の長さを膜厚で規格化して、図8及び図9に示したような累積度数分布表を作成した。図8及び図9において、縦軸は累積度数分布(%)を示し、横軸は(マイクロクリスタルシリコン薄膜の結晶粒の長さ)/(マイクロクリスタルシリコン薄膜の膜厚)を示している。なお、□印は膜剥れ無、他は膜剥れ有を示している。

【0023】

図8は、マイクロクリスタルシリコン薄膜に膜剥れが生じない場合は、マイクロクリスタルシリコン薄膜の膜厚方向の長さがマイクロクリスタルシリコン薄膜の膜厚の60%以上である結晶粒が、マイクロクリスタルシリコン薄膜の結晶粒の全数の15%以下であることを示している。

【0024】

一方、図9は、マイクロクリスタルシリコン薄膜に膜剥れが生じない場合は、イクロクリスタルシリコン薄膜の膜厚方向の長さがマイクロクリスタルシリコン薄膜の膜厚の50%以下である結晶粒が、マイクロクリスタルシリコン薄膜の結晶粒の全数の85%以上であることを示している。したがって、図8あるいは図9の条件を満足するようにマイクロクリスタルシリコン薄膜を形成することにより、膜剥れの発生を防止することができるようになる。

【0025】

また、この発明の発明者らは、上述のように膜剥れの発生を防止できるマイクロクリスタルシリコン薄膜を形成できる成膜条件を見い出して、図10に示すような結果を得た。同図は、成膜条件と膜剥れとの対応関係を示す説明図で、前提として膜厚が100nmのマイクロクリスタルシリコン薄膜を形成する例で示している。

【0026】

同図において、No.1は、13nm/min(分)の成膜条件で100nmを形成した場合を示し、4時間の活性化及び30分の水素化を行っても、膜剥れが発生しなかった。No.2は、24nm/minの成膜条件で100nmを形成した場合を示し、4時間の活性化及び30分の水素化を行って、膜剥れが発生した。この膜剥れが発生した理由は、No.1と比較して生産性向上を図るため成膜速度を大きくしたことにより、膜質が悪くなり金属薄膜とのシリサイド化反応がより加速されたためである。

【0027】

また、No.3は、13nm/minの成膜条件で下部の20nmを形成した後、24nm/minの成膜条件で上部の80nmを形成した場合を示し、4時間の活性化及び30分の水素化を行っても、膜剥れが発生しなかった。この膜剥れが発生しなかった理由は、膜質が良くなる成膜条件で下部の20nmの膜厚を形成したことにより、金属薄膜とのシリサイド化反応が抑制されたためである。

【0028】

No.4はNo.3とは逆に、24nm/minの成膜条件で下部の80nmを形成した後、13nm/minの成膜条件で上部の20nmを形成した場合を示し、4時間の活性化及び30分の水素化を行っても、膜剥れが発生しなかった。この膜剥れが発生しなかった理由は、膜質が良くなる成膜条件で上部の20nmの膜厚を形成したことにより、金属薄膜とのシリサイド化反応が抑制されたためである。すなわち、No.3及びNo.4から明らかなように、膜質が良くなる成膜条件で膜厚を形成すればマイクロクリスタルシリコン薄膜の下部であっても、上部であっても金属薄膜とのシリサイド化反応が抑制されて膜剥れは発生しないことが確認された。

【0029】

また、No.5は、24nm/minの成膜条件で100nmを形成した後、短い1時間の活性化を行っても、膜剥れが発生しなかった。この膜剥れが発生しない理由は、活性化時間を短縮したことにより熱処理による影響を少なくできたためである。No.6は、24nm/minの成膜条件で100nmを形成した後、短い5分間の活性化を行っても、膜剥れが発生しなかった。

【0030】

この膜剥れが発生しない理由は、水素化時間を短縮したことにより熱処理による影響を少なくできたためである。すなわち、No.5及びNo.6から明らかなように、膜質が良くならない成膜条件で膜厚を形成しても活性化時間あるいは水素化時間を短縮すれば金属薄膜とのシリサイド化反応が抑制されて膜剥れは発生しないことが確認された。

【0031】

また、No.7は、24nm/minの成膜条件で100nmを形成した後、短い1時間の活性化及び5分間の水素化を行っても、膜剥れが発生しなかった。この膜剥れが発生しない理由は、活性化時間及び水素化を短縮したことにより熱処理による影響を少なくできたためである。このように、No.7から明らかなように、膜質が良くならない成膜条件で膜厚を形成しても活性化時間及び水素化時間を短縮すれば金属薄膜とのシリサイド化反応が抑制されて膜剥れは発生しないことが確認された。

【実施例1】

【0032】

以下、上述の原理を基に、図面を参照して、この発明の実施例1について説明する。

図1は、この発明の実施例1である積層配線を用いた半導体装置を示す断面図である。以下、図1を参照して同半導体装置の構成を説明する。なお、この例では半導体装置としてはポリシリコンTFTに適用した例で説明する。

【0033】

この例の積層配線を用いたポリシリコンTFT(半導体装置)20は、図1に示すように、ガラス、石英等から成る絶縁性基板1と、この絶縁性基板1上に形成された膜厚が150nmの二酸化シリコン膜から成る下地絶縁膜2と、この下地絶縁膜2上に形成された膜厚が50nmのポリシリコン薄膜3と、このポリシリコン薄膜3両端領域にそれぞれ形成されたソース領域4及びドレイン領域5と、両領域4、5間に形成されたチャネル領域6と、ポリシリコン薄膜3上に形成された膜厚が100nmの二酸化シリコン膜から成るゲート絶縁膜7と、このゲート絶縁膜7上に形成された膜厚が100nmのマイクロクリスタルシリコン薄膜(下層)8と膜厚が200nmのクロム薄膜(上層)から成る金属薄膜9との積層配線から構成されたゲート電極10とを備えている。

【0034】

ここで、ゲート電極10の下層を構成しているマイクロクリスタルシリコン薄膜8は、マイクロクリスタルシリコン薄膜8の膜厚方向の長さがマイクロクリスタルシリコン薄膜8の膜厚の60%以上(この例では、略60nm以上)である結晶粒が、マイクロクリスタルシリコン薄膜8の結晶粒の全数の15%以下となるように形成されている。あるいは、マイクロクリスタルシリコン薄膜8は、マイクロクリスタルシリコン薄膜8の膜厚方向の長さがマイクロクリスタルシリコン薄膜8の膜厚の50%以下(この例では、略50nm以下)である結晶粒が、マイクロクリスタルシリコン薄膜8の結晶粒の全数の85%以上となるように形成されている。

【0035】

さらに、このポリシリコンTFT20は、図1に示すように、ゲート電極10を含む全面に形成された膜厚が400nmの二酸化シリコン膜から成る層間絶縁膜11と、この層間絶縁膜11にそれぞれ開孔されたコンタクトホール12、13を通じてソース領域4及びドレイン領域5に接触するように形成された膜厚が500nmのアルミニウム膜から成るソース電極14及びドレイン電極15とを備えている。

【0036】

上述したようなこの例のポリシリコンTFT20によれば、ゲート電極10を構成しているマイクロクリスタルシリコン薄膜8は、前述の発明の原理の図8あるいは図9に基づいて、マイクロクリスタルシリコン薄膜8の膜厚方向の長さがマイクロクリスタルシリコン薄膜8の膜厚の60%以上である結晶粒が、マイクロクリスタルシリコン薄膜8の結晶粒の全数の15%以下となるように、あるいは、マイクロクリスタルシリコン薄膜8は、マイクロクリスタルシリコン薄膜8の膜厚方向の長さがマイクロクリスタルシリコン薄膜8の膜厚の50%以下である結晶粒が、マイクロクリスタルシリコン薄膜8の結晶粒の全数の85%以上となるように形成されている。

したがって、マイクロクリスタルシリコン薄膜8と金属薄膜9との過剰なシリサイド化反応を抑制することができるので、マイクロクリスタルシリコン薄膜8の膜剥れを防止することができる。

【実施例2】

【0037】

図2乃至図4は、この発明の実施例2であるポリシリコンTFTの製造方法(第1の製造方法)を工程順に示す工程図である。以下、図2乃至図4を参照して工程順に説明する。

まず、図2(a)に示すように、絶縁性基板1の一例のガラス基板として日本電気硝子社製OA−10を用意し、プラズマCVD法によりSiH4ガス及びN2Oガスを原料ガスとして、そのガラス基板上に膜厚が150nmの二酸化シリコン薄膜を堆積して下地絶縁膜2を形成した。次に、プラズマCVD法によりSiH4ガスを原料ガスとして、下地絶縁膜2上に膜厚が50nmのアモルファスシリコン薄膜16を堆積した。次に、アモルファスシリコン薄膜16中の水素を離脱させるために、約500℃で熱処理を行った。

【0038】

次に、図2(b)に示すように、レーザアニール法により、波長が308nmのXeCl(塩化キセノン)エキシマレーザ光をアモルファスシリコン薄膜16に照射してこの薄膜16を変質させて下地絶縁膜2上にポリシリコン薄膜3を形成した。次に、図2(c)に示すように、通常のフォトレジスト法により、ポリシリコン薄膜3の全面に塗布したレジストをパターニングして所望の形状のレジストマスク17を形成し、このレジストマスク17を用いてドライエッチング法によりCF4ガス及びO2ガスを原料ガスとして、ポリシリコン薄膜3をエッチングしてアイランド化した。

【0039】

次に、図3(d)に示すように、プラズマCVD法により、Si(OC2H5)4(テトラ・エチル・オルソ・シリケート:TEOS)ガス及びO2ガスを原料ガスとして、アイランド化されたポリシリコン薄膜3上に膜厚が100nmの二酸化シリコン薄膜を堆積してゲート絶縁膜7を形成した。次に、プラズマCVD法により、SiH4ガス、PH3(H2希釈5%)ガス及びH2ガスを原料ガスとして、ゲート絶縁膜7上に膜厚が100nmのマイクロクリスタルシリコン薄膜8を堆積した。このとき、前述の発明の原理の図10のNo.3の成膜条件に基づいて、マイクロクリスタルシリコン薄膜8の100nmの膜厚のうち、下部の20nmは成膜速度が13nm/minの成膜条件で形成し、上部の80nmは成膜速度が24nm/minの成膜条件で形成した。ここで、下部の20nmについては、SiH4 流量が20sccm(Standard cubic centimeter per minute)、PH3流量が65sccm、H2流量が2500sccm、圧力が260Pa(Pascal)、放電電力密度が1.25W/cm2、基板温度が350℃の条件で、95秒間放電して形成した。一方、上部の80nmについては、SiH4流量が40sccm、PH3流量が65sccm、H2流量が2500sccm、圧力が260Pa、放電電力密度が1.25W/cm2、基板温度が350℃の条件で、201秒間放電して形成した。

【0040】

このように、マイクロクリスタルシリコン薄膜8の膜厚100nmのうち、下部の20nmについては成膜速度が13nm/minの成膜条件で形成し、残りの上部の80nmについては成膜速度が24nm/minの成膜条件で形成したので、膜厚100nmをすべて13nm/minの成膜条件で形成した場合に比較して、生産性を大幅に向上させることができる。

【0041】

次に、スパッタリング法により、マイクロクリスタルシリコン薄膜8上に膜厚が200nmのクロム薄膜から成る金属薄膜9を形成した。次に、図3(e)に示すように、通常のフォトレジスト法により、金属薄膜9の全面に塗布したレジストをパターニングして所望の形状のレジストマスク18を形成し、このレジストマスク18を用いてドライエッチング法によりCl2ガス及びO2ガスを原料ガスとして、金属薄膜9及びマイクロクリスタルシリコン薄膜8をエッチング(パターニング)してゲート電極10を形成した。このゲート電極10は、膜厚が100nmのマイクロクリスタルシリコン薄膜(下層)8と、膜厚が200nmのクロム薄膜(上層)から成る金属薄膜9とから成る積層配線から構成されている。

【0042】

次に、レジストマスク18を除去した後、図3(f)に示すように、イオンドーピング法によりPH3(H2希釈5%)を用いて、加速電圧が50keV、ドーズ量が3×1015cm−2、圧力が0.02Paのドーピング条件で、ゲート電極10のパターンをマスクとした自己整合法により、不純物としてリン(P)をゲート絶縁膜7を通じてポリシリコン薄膜3に導入してソース領域4及びドレイン領域5を形成した。

【0043】

次に、図4(g)に示すように、プラズマCVD法により、TEOS及びO2ガスを原料ガスとして、全面に膜厚が400nmの二酸化シリコン薄膜を堆積して層間絶縁膜11を形成した。次に、ポリシリコン薄膜3中に導入したリンを活性化するために、450℃で4時間、窒素雰囲気中で熱処理を行った(活性化工程)。この活性化は例えば、アニール炉を用いたファーネスアニール法により行う。次に、ポリシリコン薄膜3及びポリシリコン薄膜3とゲート絶縁膜7との界面のダングリングボンドを終端させるために、400℃で30分間、水素プラズマ中で熱処理を行った(水素化工程)。

【0044】

このような活性化工程及び水素化工程の間に、マイクロクリスタルシリコン薄膜8はこの上層の金属薄膜9であるクロム薄膜とシリサイド化反応を起こすが、このシリサイド化反応が過剰になるとマイクロクリスタルシリコン薄膜8が膜剥れを起こす原因となる。しかしながら、前述したように、マイクロクリスタルシリコン薄膜8は100nmの膜厚のうち、下部の20nmは成膜速度が13nm/minの、膜質が良くなる成膜条件で形成されているため、マイクロクリスタルシリコン薄膜8はシリサイド化反応が抑制されるので、膜剥れを防止することができる。

【0045】

次に、図4(h)に示すように、プラズマCVD法により、通常のフォトレジスト法により、層間絶縁膜11の全面に塗布したレジストをパターニングして所望の形状のレジストマスク(図示せず)を形成し、このレジストマスクを用いてドライエッチング法によりCF4ガス及びO2ガスを原料ガスとして、層間絶縁膜11及びゲート絶縁膜7を選択的にエッチングしてそれぞれソース領域4及びドレイン領域5を露出させるコンタクトホール12、13を開孔する。

【0046】

次に、そのレジストマスクを除去した後、スパッタリング法により膜厚が500nmのアルミニウム薄膜を全面に堆積する。次に、通常のフォトレジスト法により形成したレジストマスク(図示せず)を用いて、ドライエッチング法によりCl2ガス及びBCl3ガスを原料ガスとして、アルミニウムをエッチングしてソース領域4及びドレイン領域5に接触するようにソース電極14及びドレイン電極15を形成する。次に、そのレジストマスクを除去することにより、図1に示したようなポリシリコンTFT20を完成させる。

【0047】

この例によって形成されたマイクロクリスタルシリコン薄膜8は、マイクロクリスタルシリコン薄膜8の膜厚方向の長さがマイクロクリスタルシリコン薄膜8の膜厚の60%以上である結晶粒が、マイクロクリスタルシリコン薄膜8の結晶粒の全数の6%であり、またマイクロクリスタルシリコン薄膜8の膜厚方向の長さがマイクロクリスタルシリコン薄膜8の膜厚の50%以下である結晶粒が、マイクロクリスタルシリコン薄膜8の結晶粒の全数の94%であった。

【0048】

上述したようなこの例のポリシリコンTFTの製造方法によれば、ゲート電極10を構成しているマイクロクリスタルシリコン薄膜8を、前述の発明の原理の図10のNo.3の成膜条件に基づいて、下部の20nmについては成膜速度が13nm/minの成膜条件で形成し、残りの上部の80nmについては成膜速度が24nm/minの成膜条件で形成したので、上述したような組成の結晶粒を得ることができるため、上層の金属薄膜9との過剰なシリサイド化反応を抑制できるので、マイクロクリスタルシリコン薄膜8の膜剥れを防止することができる。これによって、従来よりも生産性が高くて、信頼性の高いポリシリコンTFTを製造することができる。

【実施例3】

【0049】

次に、この発明の実施例3であるポリシリコンTFTの製造方法(第2の製造方法)を説明する。この実施例3のポリシリコンTFTの製造方法の構成が、上述の実施例2(第1の製造方法)のそれと大きく異なるところは、マイクロクリスタルシリコン薄膜を異なる成膜条件で形成するようにした点である。なお、この第2の製造方法では、工程図は第1の製造方法と略同じなので図示は省略する。

この第2の製造方法では、前述の発明の原理の図10のNo.4の成膜条件に基づいて、マイクロクリスタルシリコン薄膜8の100nmの膜厚のうち、下部の80nmは成膜速度が24nm/minの成膜条件で形成し、上部の20nmは成膜速度が13nm/minの成膜条件で形成した。ここで、下部の80nmについては、SiH4流量が40sccm、PH3流量が65sccm、H2流量が2500sccm、圧力が260Pa、放電電力密度が1.25W/cm2、基板温度が350℃の条件で、201秒間放電して形成した。一方、上部の20nmについては、SiH4流量が20sccm、PH3流量が65sccm、H2流量が2500sccm、圧力が260Pa、放電電力密度が1.25W/cm2、基板温度が350℃の条件で、95秒間放電して形成した。

これ以外は、上述した第1の製造方法と略同様である.それゆえ、説明を省略する。

【0050】

この例によって形成されたマイクロクリスタルシリコン薄膜8は、マイクロクリスタルシリコン薄膜8の膜厚方向の長さがマイクロクリスタルシリコン薄膜8の膜厚の60%以上である結晶粒が、マイクロクリスタルシリコン薄膜8の結晶粒の全数の13%であり、またマイクロクリスタルシリコン薄膜8の膜厚方向の長さがマイクロクリスタルシリコン薄膜8の膜厚の50%以下である結晶粒が、マイクロクリスタルシリコン薄膜8の結晶粒の全数の87%であった。

【0051】

上述したようなこの例のポリシリコンTFTの製造方法によれば、ゲート電極10を構成しているマイクロクリスタルシリコン薄膜8を、前述の発明の原理の図10のNo.4の成膜条件に基づいて、下部の80nmについては成膜速度が24nm/minの成膜条件で形成し、残りの上部の20nmについては成膜速度が13nm/minの成膜条件で形成したので、上述したような組成の結晶粒を得ることができるため、上層の金属薄膜9との過剰なシリサイド化反応を抑制できるので、マイクロクリスタルシリコン薄膜8の膜剥れを防止することができる。これによって、従来よりも生産性が高くて、信頼性の高いポリシリコンTFTを製造することができる。

【実施例4】

【0052】

次に、この発明の実施例4であるポリシリコンTFTの製造方法(第3の製造方法)を説明する。この実施例4のポリシリコンTFTの製造方法の構成が、上述の実施例2(第1の製造方法)のそれと大きく異なるところは、マイクロクリスタルシリコン薄膜を異なる成膜条件で形成するようにした点である。

この第3の製造方法では、前述の発明の原理の図10のNo.5の成膜条件に基づいて、マイクロクリスタルシリコン薄膜8の100nmを、成膜速度が24nm/minの成膜条件で形成した。そして、SiH4流量が40sccm、PH3流量が65sccm、H2流量が2500sccm、圧力が260Pa、放電電力密度が1.25W/cm2、基板温度が350℃の条件で、201秒間放電して形成した。一方、上部の20nmについては、SiH4流量が20sccm、PH3流量が65sccm、H2流量が2500sccm、圧力が260Pa、放電電力密度が1.25W/cm2、基板温度が350℃の条件で、251秒間放電して形成した。

【0053】

次に、ポリシリコン薄膜3中に導入したリンを活性化するために、450℃で1時間、窒素雰囲気中で熱処理を行った(活性化工程)。次に、ポリシリコン薄膜3及びポリシリコン薄膜3とゲート絶縁膜7との界面のダングリングボンドを終端させるために、第2の製造方法と同様に400℃で30分間、水素プラズマ中で熱処理を行った(水素化工程)。

【0054】

この例によって形成されたマイクロクリスタルシリコン薄膜8は、マイクロクリスタルシリコン薄膜8の膜厚方向の長さがマイクロクリスタルシリコン薄膜8の膜厚の60%以上である結晶粒が、マイクロクリスタルシリコン薄膜8の結晶粒の全数の9%であり、またマイクロクリスタルシリコン薄膜8の膜厚方向の長さがマイクロクリスタルシリコン薄膜8の膜厚の50%以下である結晶粒が、マイクロクリスタルシリコン薄膜8の結晶粒の全数の91%であった。

【0055】

上述したようなこの例のポリシリコンTFTの製造方法によれば、ゲート電極10を構成しているマイクロクリスタルシリコン薄膜8を、前述の発明の原理の図10のNo.5の成膜条件に基づいて、成膜速度が24nm/minの成膜条件でマイクロクリスタルシリコン薄膜8を100nm形成し、また450℃で1時間活性化した後、400℃で30分間水素化したので、上述したような組成の結晶粒を得ることができる。したがって、上層の金属薄膜9との過剰なシリサイド化反応を抑制できるので、マイクロクリスタルシリコン薄膜8の膜剥れを防止することができる。これによって、従来よりも生産性が高くて、信頼性の高いポリシリコンTFTを製造することができる。

【実施例5】

【0056】

次に、この発明の実施例5であるポリシリコンTFTの製造方法(第4の製造方法)を説明する。この実施例5のポリシリコンTFTの製造方法の構成が、上述の実施例2(第1の製造方法)のそれと大きく異なるところは、マイクロクリスタルシリコン薄膜を異なる成膜条件で形成するようにした点である。

この第4の製造方法では、前述の発明の原理の図10のNo.6の成膜条件に基づいて、マイクロクリスタルシリコン薄膜8の100nmを、成膜速度が24nm/minの成膜条件で形成した。次に、ポリシリコン薄膜3中に導入したリンを活性化するために、450℃で4時間、窒素雰囲気中で熱処理を行った(活性化工程)。次に、ポリシリコン薄膜3及びポリシリコン薄膜3とゲート絶縁膜7との界面のダングリングボンドを終端させるために、400℃で5分間、水素プラズマ中で熱処理を行った(水素化工程)。

【0057】

この例によって形成されたマイクロクリスタルシリコン薄膜8は、マイクロクリスタルシリコン薄膜8の膜厚方向の長さがマイクロクリスタルシリコン薄膜8の膜厚の60%以上である結晶粒が、マイクロクリスタルシリコン薄膜8の結晶粒の全数の9%であり、またマイクロクリスタルシリコン薄膜8の膜厚方向の長さがマイクロクリスタルシリコン薄膜8の膜厚の50%以下である結晶粒が、マイクロクリスタルシリコン薄膜8の結晶粒の全数の91%であった。

【0058】

上述したようなこの例のポリシリコンTFTの製造方法によれば、ゲート電極10を構成しているマイクロクリスタルシリコン薄膜8を、前述の発明の原理の図10のNo.6の成膜条件に基づいて、成膜速度が24nm/minの成膜条件でマイクロクリスタルシリコン薄膜8を100nm形成し、また450℃で4時間活性化した後、400℃で5分間水素化したので、上述したような組成の結晶粒を得ることができる。したがって、上層の金属薄膜9との過剰なシリサイド化反応を抑制できるので、マイクロクリスタルシリコン薄膜8の膜剥れを防止することができる。これによって、従来よりも生産性が高くて、信頼性の高いポリシリコンTFTを製造することができる。

【実施例6】

【0059】

次に、この発明の実施例6であるポリシリコンTFTの製造方法(第5の製造方法)を説明する。この実施例6のポリシリコンTFTの製造方法の構成が、上述の実施例2(第1の製造方法)のそれと大きく異なるところは、マイクロクリスタルシリコン薄膜を異なる成膜条件で形成するようにした点である。

この第5の製造方法では、マイクロクリスタルシリコン薄膜8の100nmを、成膜速度が24nm/minの成膜条件で形成した。次に、ポリシリコン薄膜3中に導入したリンを活性化するために、450℃で1時間、窒素雰囲気中で熱処理を行った(活性化工程)。次に、ポリシリコン薄膜3及びポリシリコン薄膜3とゲート絶縁膜7との界面のダングリングボンドを終端させるために、水素プラズマ中で熱処理を行った(水素化工程)。

【0060】

この例によって形成されたマイクロクリスタルシリコン薄膜8は、マイクロクリスタルシリコン薄膜8の膜厚方向の長さがマイクロクリスタルシリコン薄膜8の膜厚の60%以上である結晶粒が、マイクロクリスタルシリコン薄膜8の結晶粒の全数の13%であり、またマイクロクリスタルシリコン薄膜8の膜厚方向の長さがマイクロクリスタルシリコン薄膜8の膜厚の50%以下である結晶粒が、マイクロクリスタルシリコン薄膜8の結晶粒の全数の87%であった。

【0061】

上述したようなこの例のポリシリコンTFTの製造方法によれば、ゲート電極10を構成しているマイクロクリスタルシリコン薄膜8を、成膜速度が24nm/minの成膜条件でマイクロクリスタルシリコン薄膜8を100nm形成し、また450℃で1時間活性化した後、水素化したので、上述したような組成の結晶粒を得ることができる。したがって、上層の金属薄膜9との過剰なシリサイド化反応を抑制できるので、マイクロクリスタルシリコン薄膜8の膜剥れを防止することができる。これによって、従来よりも生産性が高くて、信頼性の高いポリシリコンTFTを製造することができる。

【0062】

以上のように、実施例1のポリシリコンTFT20を製造する第1乃至第5の製造方法(実施例2乃至実施例6)を述べたが、各製造方法を総合すると、マイクロクリスタルシリコン薄膜8の膜厚方向の長さがマイクロクリスタルシリコン薄膜8の膜厚の60%以上である結晶粒は、マイクロクリスタルシリコン薄膜8の結晶粒の全数の6〜9%となり、またマイクロクリスタルシリコン薄膜8の膜厚方向の長さがマイクロクリスタルシリコン薄膜8の膜厚の50%以下である結晶粒は、マイクロクリスタルシリコン薄膜8の結晶粒の全数の87〜91%となる。

【0063】

以上、この発明の実施例を図面により詳述してきたが、具体的な構成はこの実施例に限られるものではなく、この発明の要旨を逸脱しない範囲の設計の変更等があってもこの発明に含まれる。例えば、実施例では、マイクロクリスタルシリコン薄膜を含む積層配線をポリシリコンTFTのゲート電極に用いた例で説明したが、ゲート電極に限らずにあるいはTFTに限らずに各種電子部品の配線に適用することができる。また、活性化工程は400℃で行う例で説明したが、400℃以上で行っても略同様な効果を得ることができる。また、水素化工程は400℃で行う例で説明したが、350℃以上で行っても略同様な効果を得ることができる。

【0064】

また、下地絶縁膜、ゲート絶縁膜及び層間絶縁膜等をプラズマCVD法により形成する例で説明したが、プラズマCVD法に限ることなく、減圧CVD法によりSiH4ガス及びN2Oガスを原料ガスとして形成する場合にも同様に適用される。また、下地絶縁膜、ゲート絶縁膜及び層間絶縁膜等を二酸化シリコン薄膜により構成する例で説明したが、二酸化シリコン薄膜に限らずに窒化シリコン薄膜,酸窒化シリコン薄膜等の他の絶縁膜を用いることもできる。また、アモルファスシリコン薄膜をプラズマCVD法により形成する例で説明したが、減圧CVD法によりSi2H6を原料ガスとして形成する場合にも同様に適用される。また、ゲート電極の上層の金属薄膜としてはクロム薄膜を用いる例で説明したが、クロムに代えてアルミニウム、モリブデン、タングステン、ニオブ、あるいはこれらの合金等の他の金属を使用することもできる。また、活性化工程ではアニール炉を用いたファーネスアニール法により行う例で説明したが、これに代えてレーザ光を用いたレーザアニール法、あるいは高温窒素ガスを吹き付けるRTA(Rapid Thermal Anneal)法等を用いることができる。また、水素化工程では水素プラズマに代えて、水素雰囲気中に晒すようにしてもよい。また、層間絶縁膜の形成は水素化工程あるいは水素化工程の終了後に形成してもよい。

【産業上の利用可能性】

【0065】

この発明は、ゲート電極やTFTに限らず、各種電子部品の配線に適用することができる。

【符号の説明】

【0066】

1 絶縁性基板

2 下地絶縁膜

3 ポリシリコン薄膜

4 ソース領域

5 ドレイン領域

6 チャネル領域

7 ゲート絶縁膜

8 マイクロクリスタルシリコン薄膜

9 金属薄膜

10 ゲート電極

11 層間絶縁膜

12,13 コンタクトホール

14 ソース電極

15 ドレイン電極

16 アモルファスシリコン薄膜

17,18 レジストマスク

20 ポリシリコンTFT(半導体装置)

【特許請求の範囲】

【請求項1】

電子部品の配線として備えられ、マイクロクリスタルシリコン薄膜と該薄膜上に形成された金属薄膜とから成る積層配線であって、

前記マイクロクリスタルシリコン薄膜の結晶組織を構成している結晶粒には、前記電子部品の製造時の熱処理で生じた前記金属薄膜とのシリサイド化反応に起因して膜厚方向に成長した柱状の結晶粒が含まれ、前記マイクロクリスタルシリコン薄膜の膜厚方向の長さが前記マイクロクリスタルシリコン薄膜の膜厚の60%以上である結晶粒が、前記マイクロクリスタルシリコン薄膜の結晶粒の全数の6%以上15%以下であることを特徴とする積層配線。

【請求項2】

電子部品の配線として備えられ、マイクロクリスタルシリコン薄膜と該薄膜上に形成された金属薄膜とから成る積層配線であって、

前記マイクロクリスタルシリコン薄膜の結晶組織を構成している結晶粒には、前記電子部品の製造時の熱処理で生じた前記金属薄膜とのシリサイド化反応に起因して膜厚方向に成長した柱状の結晶粒が含まれ、前記マイクロクリスタルシリコン薄膜の膜厚方向の長さが前記マイクロクリスタルシリコン薄膜の膜厚の50%以下である結晶粒が、前記マイクロクリスタルシリコン薄膜の結晶粒の全数の85%以上91%以下であることを特徴とする積層配線。

【請求項3】

絶縁性基板上に下地絶縁膜を介してその両端領域にソース領域及びドレイン領域が形成されたポリシリコン薄膜を有し、該ポリシリコン薄膜上にゲート絶縁膜を介してゲート電極が形成された半導体装置であって、

前記ゲート電極が請求項1または2記載の積層配線から構成されていることを特徴とする半導体装置。

【請求項4】

絶縁性基板上に下地絶縁膜を介してアモルファスシリコン薄膜を形成する工程と、

前記アモルファスシリコン薄膜にレーザアニール法を施して該アモルファスシリコン薄膜をポリシリコン薄膜に変質させる工程と、

前記ポリシリコン薄膜をアイランド化した後、該ポリシリコン薄膜上にゲート絶縁膜を介してマイクロクリスタルシリコン薄膜及び金属薄膜を順次に堆積して積層膜を形成する工程と、

前記積層膜を所望の形状にパターニングしてゲート電極を形成する工程と、

前記ゲート電極が形成された上記絶縁性基板を熱処理する工程とを有し、

前記熱処理後の前記マイクロクリスタルシリコン薄膜の結晶組織を構成している結晶粒には、前記熱処理の際に生じた前記金属薄膜とのシリサイド化反応に起因して膜厚方向に成長した柱状の結晶粒が含まれ、前記マイクロクリスタルシリコン薄膜の膜厚方向の長さが前記マイクロクリスタルシリコン薄膜の膜厚の60%以上である結晶粒が、前記マイクロクリスタルシリコン薄膜の結晶粒の全数の6%以上15%以下である薄膜、

あるいは前記マイクロクリスタルシリコン薄膜の膜厚方向の長さが前記マイクロクリスタルシリコン薄膜の膜厚の50%以下である結晶粒が、前記マイクロクリスタルシリコン薄膜の結晶粒の全数の85%以上91%以下である薄膜

を形成することを特徴とする半導体装置の製造方法。

【請求項1】

電子部品の配線として備えられ、マイクロクリスタルシリコン薄膜と該薄膜上に形成された金属薄膜とから成る積層配線であって、

前記マイクロクリスタルシリコン薄膜の結晶組織を構成している結晶粒には、前記電子部品の製造時の熱処理で生じた前記金属薄膜とのシリサイド化反応に起因して膜厚方向に成長した柱状の結晶粒が含まれ、前記マイクロクリスタルシリコン薄膜の膜厚方向の長さが前記マイクロクリスタルシリコン薄膜の膜厚の60%以上である結晶粒が、前記マイクロクリスタルシリコン薄膜の結晶粒の全数の6%以上15%以下であることを特徴とする積層配線。

【請求項2】

電子部品の配線として備えられ、マイクロクリスタルシリコン薄膜と該薄膜上に形成された金属薄膜とから成る積層配線であって、

前記マイクロクリスタルシリコン薄膜の結晶組織を構成している結晶粒には、前記電子部品の製造時の熱処理で生じた前記金属薄膜とのシリサイド化反応に起因して膜厚方向に成長した柱状の結晶粒が含まれ、前記マイクロクリスタルシリコン薄膜の膜厚方向の長さが前記マイクロクリスタルシリコン薄膜の膜厚の50%以下である結晶粒が、前記マイクロクリスタルシリコン薄膜の結晶粒の全数の85%以上91%以下であることを特徴とする積層配線。

【請求項3】

絶縁性基板上に下地絶縁膜を介してその両端領域にソース領域及びドレイン領域が形成されたポリシリコン薄膜を有し、該ポリシリコン薄膜上にゲート絶縁膜を介してゲート電極が形成された半導体装置であって、

前記ゲート電極が請求項1または2記載の積層配線から構成されていることを特徴とする半導体装置。

【請求項4】

絶縁性基板上に下地絶縁膜を介してアモルファスシリコン薄膜を形成する工程と、

前記アモルファスシリコン薄膜にレーザアニール法を施して該アモルファスシリコン薄膜をポリシリコン薄膜に変質させる工程と、

前記ポリシリコン薄膜をアイランド化した後、該ポリシリコン薄膜上にゲート絶縁膜を介してマイクロクリスタルシリコン薄膜及び金属薄膜を順次に堆積して積層膜を形成する工程と、

前記積層膜を所望の形状にパターニングしてゲート電極を形成する工程と、

前記ゲート電極が形成された上記絶縁性基板を熱処理する工程とを有し、

前記熱処理後の前記マイクロクリスタルシリコン薄膜の結晶組織を構成している結晶粒には、前記熱処理の際に生じた前記金属薄膜とのシリサイド化反応に起因して膜厚方向に成長した柱状の結晶粒が含まれ、前記マイクロクリスタルシリコン薄膜の膜厚方向の長さが前記マイクロクリスタルシリコン薄膜の膜厚の60%以上である結晶粒が、前記マイクロクリスタルシリコン薄膜の結晶粒の全数の6%以上15%以下である薄膜、

あるいは前記マイクロクリスタルシリコン薄膜の膜厚方向の長さが前記マイクロクリスタルシリコン薄膜の膜厚の50%以下である結晶粒が、前記マイクロクリスタルシリコン薄膜の結晶粒の全数の85%以上91%以下である薄膜

を形成することを特徴とする半導体装置の製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【公開番号】特開2013−70100(P2013−70100A)

【公開日】平成25年4月18日(2013.4.18)

【国際特許分類】

【出願番号】特願2013−2177(P2013−2177)

【出願日】平成25年1月9日(2013.1.9)

【分割の表示】特願2006−78653(P2006−78653)の分割

【原出願日】平成18年3月22日(2006.3.22)

【出願人】(303018827)NLTテクノロジー株式会社 (547)

【Fターム(参考)】

【公開日】平成25年4月18日(2013.4.18)

【国際特許分類】

【出願日】平成25年1月9日(2013.1.9)

【分割の表示】特願2006−78653(P2006−78653)の分割

【原出願日】平成18年3月22日(2006.3.22)

【出願人】(303018827)NLTテクノロジー株式会社 (547)

【Fターム(参考)】

[ Back to top ]