積層電子部品およびその製造方法

【課題】外部電極に端子電極がめっき形成されるときに、多孔質素体の表面へのめっき付着を十分に抑止でき、製品の信頼性低下を防止することが可能な積層電子部品およびその製造方法を提供する。

【解決手段】積層電子部品1は、セラミックスからなり複数の空孔を有する多孔質素体2と、多孔質素体2内に形成された複数の内部電極3とを含む積層体4を有するPTCサーミスタであり、多孔質素体2と内部電極3が積層された単位構造10を少なくとも1つ備えたものである。内部電極2には、外部電極5,5が接続されており、更にその上に端子電極7,7がめっきにより形成されている。多孔質素体2の複数の空孔には、付加重合型の樹脂が充填されている。

【解決手段】積層電子部品1は、セラミックスからなり複数の空孔を有する多孔質素体2と、多孔質素体2内に形成された複数の内部電極3とを含む積層体4を有するPTCサーミスタであり、多孔質素体2と内部電極3が積層された単位構造10を少なくとも1つ備えたものである。内部電極2には、外部電極5,5が接続されており、更にその上に端子電極7,7がめっきにより形成されている。多孔質素体2の複数の空孔には、付加重合型の樹脂が充填されている。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、セラミックスからなる素体と内部電極の積層構造を備える積層電子部品およびその製造方法に関する。

【背景技術】

【0002】

一般に、セラミックス素体、内部電極、および外部電極を有するサーミスタ、コンデンサ、インダクタ、LTCC(Low Temperature Co-fired Ceramics)、バリスタやそれらの複合体からなる積層電子部品は、プリント配線基板等の配線基板に搭載され、外部電極が所定の接続位置にはんだ付けされる。その際、例えばAgからなる外部電極(下地電極)上に、めっきによりNi層およびSn層からなる端子電極を形成したものを用いると、はんだによる基板への接合性が高められ、生産性を向上させ得る。

【0003】

例えば、特許文献1には、かかる端子電極を形成するめっき工程において、めっき電解液が部品素体へ浸入してしまうことに起因して積層電子部品の電気特性が悪化してしまうことを防止すべく、電子部品のセラミック素体の表面部分に存在する全ての細孔に、シリコーン樹脂またはフェノール樹脂が含浸された電子部品が提案されている。

【0004】

【特許文献1】特許第270097号公報

【発明の開示】

【発明が解決しようとする課題】

【0005】

ところで、本発明者が、外部電極に端子電極がめっき形成された上記種々の積層電子部品の物性や電気特性について検討したところ、例えば、特にPTC(Positive Temperature Coefficient)サーミスタのような多孔質のセラッミク素体を有する積層電子部品では、素体の表面や表層部、さらには、素体の内部まで端子電極金属がめっきされることがあり、こうなると、外部電極間の絶縁特性の低下あるいは短絡が生じてしまい、ときには、めっきが内部電極にまで達してしまい、製品機能が失われるといった問題を生じ得ることが判明した。

【0006】

具体的には、PTCサーミスタの両端に外部電極(下地電極)を形成し、ベレルめっきによる電気めっきでNi/Sn端子電極の形成を行なったところ、セラミック素体の全面にめっきが付着した。この素体断面のNi及びSnの元素分布をEPMA(Electron-Probe Microanalyzer)で検査した結果、表層部に大量のNiが付着しており、更に深い部位にもNiが付着していることが判明した。このことから、内部電極に達するような開孔(オープンポア)の内部にめっき液が浸入し、内部電極から給電されることにより、めっきが素体内部から付着・成長していくものと推定される。このような素体へのめっき付着現象は、触媒を用いた無電解めっき、および、触媒を用いずに接触法で無電解めっきを開始する場合にも、同様に見られ、この場合にも、内部電極に達するような開孔(オープンポア)の内部から、めっきが付着・成長していくものと推定される。これに対し、上記特許文献1に開示された従来の方法を用いて、セラミック素体の全面にシリコーン樹脂を含浸したところ、樹脂の種類や樹脂の含浸条件によっては、セラミック素体へのめっきの付着を十分に抑制できないことが確認された。

【0007】

そこで、本発明はかかる事情に鑑みてなされたものであり、外部電極上にめっきにより端子電極が形成される場合でも、セラミックスからなる多孔質素体の表面へのめっき付着を十分に抑止でき、これにより、製品の信頼性低下を防止することが可能な積層電子部品およびその製造方法を提供することを目的とする。

【課題を解決するための手段】

【0008】

本発明者は、上記課題を解決すべく、積層電子部品の多孔質セラミック素体の表面にめっき付着が生じ得る素体材料の物性やそのときの条件、その素体の空孔に充填する樹脂の種類や性状との関係に着目し、鋭意研究を進めた結果、本発明を完成するに至った。すなわち、本発明による積層電子部品は、主としてセラミックスからなり、かつ、複数の空孔を含む多孔質素体(多孔質セラミック素体)と、その多孔質素体内に設けられた少なくとも1つの内部電極とを有する積層体と、内部電極に接続された外部電極と、外部電極上にめっきにより形成された端子電極とを備えるものであり、多孔質素体は、複数の空孔の少なくとも一部に付加重合型(付加重合性)の樹脂が充填されたものである。なお、本発明における多孔質素体に含まれる「空孔」とは、日本工業規格JIS Z2500および同2501に規定される「気孔」と同等のものである。

【0009】

また、後記の多孔質素体における樹脂の「充填率」とは、以下のとおり測定される値である。すなわち、まず、端子電極がめっきで形成される前の状態の積層電子部品を大気圧下150℃で1時間乾燥して水分を蒸発させたものの重量を測定する(重量m1)。次に、その積層電子部品を水中に浸漬させた状態で真空中30分間保持することにより、空孔内に水を含浸させたものの重量を測定する(重量m2)。さらに、その積層電子部品を大気圧下200℃で1時間乾燥した後、外部電極に樹脂が付着しないように、多孔質素体に未硬化の樹脂(重合性のものの場合はモノマー)を含浸させ、その樹脂を乾燥硬化(加熱硬化、重合)させたものの重量を測定する(重量m3)。そして、下記式(1);

充填率(%)=100×(m3−m1)/{(m2−m1)×ρ} …(1)、

で表される関係式に上記重量m1,m2,m3、および樹脂の乾燥硬化状態での密度ρを代入し、樹脂の「充填率」を算出する。

【0010】

このように構成された積層電子部品においては、多孔質素体の空孔に樹脂が充填されており、多孔質素体に開口した空孔(開孔:オープンポア)が樹脂によって閉塞されるので、外部電極上にめっきにより端子電極を形成するときに、そのような開孔からめっき液が多孔質素体の内部へ浸入することにより内部電極にめっき液が到達してめっきが付着・成長することが抑制される。このとき、樹脂による空孔の充填率が高いほど、多孔質素体へのめっき液の浸入を抑えることができると想定されるが、樹脂として例えば脱水縮合型のものを用いると、重合時に反応生成物として水が生じ、多孔質素体2の空孔の内部からその水が放出されることにより空隙が生起され、こうなると、多孔質素体の空孔への樹脂による充填が抑制され、樹脂の充填率を十分に高めることが困難となる。これに対し、付加重合型の樹脂を用いると、重合硬化時に水を生じないので、空隙の発生を抑え、脱水縮合型の樹脂を用いる場合に比して多孔質素体2の空孔の充填率をより高めることが可能となる。

【0011】

また、多孔質素体は、複数の空孔に付加重合型の樹脂が60%以上の充填率で充填されたものであると好適である。

【0012】

本発明者の知見によれば、多孔質素体への樹脂の充填率が60%以上であると、多孔質素体の表面へのめっき付着率(露出面積に対するめっき付着面積の割合)が略5%以下となるように十分に低く抑えられることが確認された。また、本発明による積層電子部品のように付加重合型の樹脂を用いることにより、60%以上の樹脂充填率を簡易かつ確実に達成しやすくなるので、多孔質素体2の内部へのめっき液の浸入をより確実に防止しつつ生産性をも向上させ得る。なお、多孔質素体の露出面上、好ましくはそのほぼ全体に樹脂層が形成されていると、そのバリア効果が一層高められるので好適である。

【0013】

また、上記特許文献1に開示された従来と同様の方法を用いて得られたPTCサーミスタが、リフローなどの加熱処理に供されたり、実装時の加熱や作動時のヒートアップなどによって高温環境に曝されたりした場合、樹脂の含浸条件によっては、高温での抵抗値が有意に低下するといったPTC特性の不良が生じ得ることが確認された。これは、おそらく、PTCサーミスタなどの電子部品のはんだ付けに使用されるフラックスが、加熱時に多孔質素体の開孔内部に流入し、その残留フラックスによってセラミックス製の素体が還元されてしまうことによるものと推測される。

【0014】

これに対し、特に、多孔質素体における樹脂の充填率が70%以上であると、積層電子部品を配線基板などに実装する際の、あるいは、その後に、フラックスが多孔質素体の内部へ流入することが十分に抑制され、特性不良の発生割合(頻度)を格段に低下させることができることが判明した。本発明による積層電子部品のように付加重合型の樹脂を用いれば、このような高い樹脂充填率でも簡易かつ確実に達成しやすい利点がある。

【0015】

さらに、上記従来方法を用いて得られたPTCサーミスタの温度特性の評価を行ったところ、樹脂の含浸条件によっては、セラッミク素体から発泡(いわゆる「爆ぜ」)を生じる個体が有意量発生することも確認された。これは、従来の方法では、セラミック素体の表面の細孔が閉塞されるものの、素体内部に空孔が残存することにより、高温に曝されたときに、空孔内部の空気が膨張し破裂することによって引き起こされるものと推定される。

【0016】

これに対し、殊に、多孔質素体における樹脂の充填率が80%以上であると、「爆ぜ」の発生割合(頻度)を格別に低減できることも判明した。本発明による積層電子部品のように付加重合型の樹脂を用いると、このような更に高い樹脂充填率をも簡易かつ確実に達成しやすいので、極めて有用である。

【0017】

また、多孔質素体が焼成されたもの(焼結体)であり、その焼結密度(実測密度/理論密度×100%)が90%以下のものである場合に、本発明は更に有用である。すなわち、本発明者の研究によれば、多孔質素体として、焼結密度が90%を超えるものを用いた場合には、端子電極のめっき形成時に多孔質素体の表面にめっきの付着がほとんど認められず、焼結密度が90%以下であると、焼結密度の低下に伴って、多孔質素体の表面へのめっきの付着率が急激に増大することが確認された。これは、多孔質素体の焼結密度が90%を超えると開孔(オープンポア)がほとんど生じることがなく、空孔が生成したとしても多くが閉孔(クローズドポア)であってめっき液が浸入しないのに対し、その焼結密度が90%以下になると、開孔の数量および全空孔に対する割合が急増することによるものと推測される。よって、そのような多量の開孔が形成され得る焼結密度90%以下の多孔質素体を備える積層電子部品に適用したときに、本発明の作用効果が一層好適に実現される。

【0018】

また、外部電極を被覆するオーバーコート層を更に有すると、外部電極の表面に端子電極をめっきするときに、めっき液による外部電極の腐食を確実に防止することができるので好適である。

【0019】

さらに、本発明による積層電子部品の製造方法は、本発明の積層電子部品を有効に製造するための方法であって、主としてセラミックスからなり、かつ、複数の空孔を含む多孔質素体内に、少なくとも1つの内部電極を設けて積層構造体を形成する工程と、積層構造体を焼成して積層体(焼結体)を形成する工程と、導電性ペーストを、積層体の内部電極と電気的に接続するように、積層体に塗布する工程と、導電性ペーストを焼成して外部電極を形成する工程と、多孔質素体に付加重合型の樹脂を得るためのモノマーを含浸させ、そのモノマーまたはプレポリマーを重合して複数の空孔に付加重合型の樹脂を、好ましくは60%以上、より好ましくは70%以上、特に好ましくは80%以上の充填率で充填する工程と、外部電極上にめっきにより端子電極を形成する工程とを有する。

【0020】

このとき、内部電極に金属成分としてNi、Cu、またはAlを主として含むものを用い、外部電極に金属成分としてAg、および、100質量部のAgに対して、好ましくは1質量部以上60質量部以下のAl等を含む導電性ペーストを用いると、導電性ペーストが、酸化されやすいCuを含まないので、大気焼成が可能となる。これにより、焼成時の雰囲気制御が簡易になり、金属成分としてCuを含む場合に必要とされる還元雰囲気下での焼成、および、その後の酸化雰囲気下での再焼成が不要となるので、製造コストの増大を防止することもできる。

【発明の効果】

【0021】

本発明の積層電子部品およびその製造方法によれば、多孔質素体に含まれる複数の空孔が、付加重合型の樹脂によって充填されているので、多孔質素体の空孔の充填率を高めやすくなり、端子電極をめっきで形成しても、多孔質素体の開孔からめっき液が浸入して内部電極まで流入することが抑制され、よって、多孔質素体へのめっきの付着が十分に抑止されるので、製品の信頼性が低下してしまうといった不都合を解消することができ、また、高温が印加されたときの特性不良の発生や高温下での「爆ぜ」の発生をも有効に防止することができる。

【発明を実施するための最良の形態】

【0022】

以下、本発明の実施の形態について、図面を参照して説明する。なお、図面中、同一の要素には同一の符号を付し、重複する説明を省略する。また、上下左右等の位置関係は、特に断らない限り、図面に示す位置関係に基づくものとする。さらに、図面の寸法比率は、図示の比率に限定されるものではない。また、以下の実施の形態は、本発明を説明するための例示であり、本発明をその実施の形態のみに限定する趣旨ではない。さらに、本発明は、その要旨を逸脱しない限り、さまざまな変形が可能である。

【0023】

<第1実施形態>

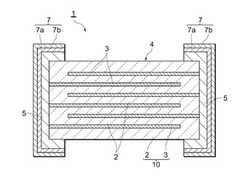

図1は、本発明による積層電子部品の第1実施形態の概略構造を示す断面図である。積層電子部品1は、セラミックスからなり複数の空孔を有する多孔質素体2と、多孔質素体2内に形成された複数の内部電極3とを含む積層体4を有するPTCサーミスタであり、換言すれば、多孔質素体2と内部電極3が積層された単位構造10を少なくとも1つ備えたものである。より具体的には、積層体4の一方の側面に露出した端部を有する内部電極3と、積層体4の他方の側面に露出した端部を有する内部電極3とが交互に積層されている。

【0024】

積層体4の両側面には、それらの側面を覆うように外部電極5,5が設けられており、各外部電極5は、積層体4の一方の側面から露出した内部電極3の群、あるいは積層体4の他方の面から露出した内部電極3の群に電気的に接続されている。

【0025】

さらに、外部電極5,5の外側には、めっきにより端子電極7,7が形成されている。これらの端子電極7,7と、例えば、配線基板(図示せず)上の電極とがはんだ等により接合される。各端子電極7は、例えば、外部電極5側から積層形成されたNi層7aおよびSn層7bを含む2層構造を有する。Ni層7aは、Sn層7bと外部電極5との接触を防止して、Snによる外部電極5の腐食を防止するバリアメタルとして機能するものであり、その厚さは例えば2μm程度である。また、Sn層7bは、はんだの濡れ性を向上させる機能を有するものであり、その厚さは例えば4μm程度とされる。

【0026】

本実施形態のように積層電子部品1としてPTCサーミスタを作製する場合には、先述のとおり、多孔質素体2はセラミックス、具体的には、半導体セラミックスからなる必要があり、より具体的には、例えば、チタン酸バリウム系セラミックスからなるものである。このチタン酸バリウム系セラミックスにおいて、必要に応じて、Baの一部をCa、Sr、Pbなどで置換しても、あるいは、Tiの一部をSn、Zrなどで置換してもよい。また、チタン酸バリウム系半導体セラミックスを得るために添加するドナー元素としては、La、Y、Sm、Ce、Dy、Gd等の希土類元素や、Nb、Ta、Bi、Sb、W等の遷移元素を用いることができる。さらにかかるチタン酸バリウム系半導体セラミックスに、必要に応じてSiO2やMn等を適宜添加して用いてもよい。

【0027】

このように多孔質素体2をチタン酸バリウム系半導体セラミックスで形成することにより、キュリー温度で電気抵抗が急上昇するというPTCサーミスタの特性(PTC特性)が良好に得られる。このようなPTCサーミスタの用途としては、過電流保護、定温度発熱体、過熱検知などが挙げられる。

【0028】

多孔質素体2を形成するために用いられるチタン酸バリウム系セラミックス粉末の合成方法としては、特に限定されるものではないが、例えば、水熱法、加水分解法、共沈法、固相法、ゾルゲル法等を用いることができ、必要に応じて仮焼が施されてもよい。

【0029】

また、多孔質素体2は、複数の空孔に樹脂が好ましくは60%以上、より好ましくは70%以上、更に好ましくは80%以上の充填率で充填されたものである。この樹脂の充填率が60%以上であると、端子電極7をめっきで形成する際に、多孔質素体2に含まれる開孔(オープンポア)からめっき液が多孔質素体2の内部へ浸入することにより内部電極にめっき液が到達してめっきが付着・成長してしまうことを十分に抑制できる。さらに、多孔質素体2への樹脂の充填率が70%以上であると、積層電子部品1の実装時などに懸念されるフラックスの多孔質素体内への流入・残留に起因する特性不良の発生割合を格段に低下させることができ、特に、樹脂の充填率が80%以上となると、積層電子部品1が高温に曝されたときに、空孔内部の空気が膨張し破裂することによって引き起こされるおそれがある「爆ぜ」の発生を格別に低く抑えることができる。

【0030】

また、多孔質素体2は、その露出面上、好ましくはそのほぼ全体に樹脂層が形成されていると、そのバリア効果が一層高められるので好適である。なお、多孔質素体2表面の樹脂層による被覆率は、ハンドリング上に特に不都合がなければ、より高い方が開孔(オープンポア)へのめっき液の浸入が防げられるので好適である。

【0031】

ここで、図2は、樹脂が60%以上の充填率で充填された多孔質素体2の実物の一例の表層断面を示す拡大写真である。多孔質素体2の内部には複数の空孔が形成されており、多くの開孔は内部空孔と連通していることが確認され、図示の如く、それらが樹脂で充填されるとともに、多孔質素体2の表面上に樹脂層が形成されていることがわかる。

【0032】

多孔質素体2の空孔充填に用いられる樹脂の種類は、特に制限されるものではなく、多孔質素体2に含浸させることができる付加重合型の樹脂であれば、種々のものを適宜選択して用いることができる。付加重合型の樹脂を得るためのモノマーまたはプレポリマー(オリゴマー)の種類も制限されず例えば、好ましくは、不飽和反応基を有するもの、特に好ましくは、(メタ)アクリロイル基、ビニル基、エポキシ基、または、それらの誘導基を有するものが挙げられる。また、付加重合型の樹脂の例としてポリジメチルシロキサンが挙げられる。ポリジメチルシロキサンは構造が単純で特性が安定しており、また安価であるので量産性を考慮すると好ましい。

【0033】

上述したとおり、樹脂として脱水縮合型のものを用いると、重合時に反応生成物として水が生じ、多孔質素体2の空孔の内部からその水が放出されることにより空隙が生起され得るのに対し、付加重合型の樹脂を用いると、重合硬化時に水を生じないので、空隙の発生を抑え、脱水縮合型の樹脂を用いる場合に比して多孔質素体2の空孔の充填率をより高めることができる。

【0034】

また、多孔質素体2は焼結体であり、その焼結密度は特に制限されないが、焼結密度が90%以下のものである場合に、上述した樹脂充填による効果が顕著に発現される。すなわち、多孔質素体2の焼結密度が90%を超える場合には、端子電極7のめっき形成時に多孔質素体2の表面に付着するめっきは有意量ではないのに対し、焼結密度が90%以下になると、焼結密度の低下につれて、多孔質素体2の開孔の量および割合が増大することに起因して、多孔質素体2の表面へのめっきの付着率が急増する傾向にある。したがって、多孔質素体2が、かかる多量の開孔が形成され得る焼結密度90%以下のものである場合、付加重合型の樹脂を用いることでその開孔を高い充填率で樹脂充填できるので、多孔質素体2の表面へのめっき付着を効果的に抑止できる。

【0035】

一方、内部電極3には、多孔質素体2との間での確実なオーミック接触を可能とする点から、例えば、Ni、Cu、またはAlを主成分とする材料が用いられ、これらの合金または複合材料であってもよく、低温焼成可能な多孔質素体2を用いることにより、Ni(融点:1450℃)に比べて融点の低いCu(融点1083℃)およびAl(融点660℃)を用いることができる。

【0036】

他方、外部電極5は、例えば、積層体4の側面への導電性ペーストの塗布および焼成により得られる。外部電極5を形成するための導電性ペーストとしては、主として、ガラス粉末と、有機ビヒクル(バインダー)と、金属粉末とを含むものが挙げられ、導電性ペーストの焼成により、有機ビヒクルは揮散し、最終的にガラス成分および金属成分を含む外部電極5が形成される。なお、導電性ペーストには、必要に応じて、粘度調整剤、無機結合剤、酸化剤等種々の添加剤を加えてもよい。

【0037】

本実施形態において、外部電極5は、例えば、金属成分としてAg、および、Al等を含むものであり、このAl等が、内部電極3の構成成分であるNi、Cu、またはAlと、外部電極5に含まれるAgとの接合部位に介在することにより、内部電極3と外部電極5との間の接合面積が増大され、これにより、接続抵抗を十分に低下させることができるとともに、内部電極3と外部電極5との機械的な接合強度をも高めることが可能となる。

【0038】

次に、上記の本実施形態に係る積層電子部品1の製造方法について、図3〜図7を参照して説明する。図3〜図7は、積層電子部品1を製造する手順の一例を示す工程図である。

【0039】

まず、出発原料として、BaCO3、TiO2および硝酸Sm溶液を所定量混合し、純水およびジルコニアボールとともにポリエチレン製ポットに入れて5時間粉砕混合した後、混合液を蒸発乾燥させて、得られた混合粉を1100度で仮焼成する。

【0040】

次に、仮焼粉に対して、再び、純水およびジルコニアボールを用いて、5〜30時間ボールミルによる粉砕を行なった後、蒸発乾燥を行い、チタン酸バリウム半導体セラミック粉末を得る。例えば、組成が(Ba0.9985Gd0.0015)0.995(Ti0.9985Nb0.0015)O3からなるチタン酸バリウム半導体セラミック粉末を得る。

【0041】

次いで、得られた粉末に、有機溶剤、有機バインダおよび可塑剤等を添加して、セラミックスラリーとした後、ドクターブレード法により成形して、図3に示すシート状の多孔質素体2、いわゆるセラミックグリーンシートを得る。

【0042】

さらに、図4に示すように、シート状の多孔質素体2上に、Ni、Cu、またはAlを金属成分として含有する導電性ペーストをスクリーン印刷することにより、内部電極3のパターンを形成する。

【0043】

次に、図5に示すように、内部電極3が形成された複数の多孔質素体2と内部電極3が形成されていない複数の多孔質素体2とを交互に積層し、それを更に加圧して積層構造体40を得る。

【0044】

それから、図6に示すように、積層構造体40を切断することにより個々の積層構造体41に分割する。切断後の積層構造体41の側面からは、内部電極3の端部が露出した状態とされている。

【0045】

次に、積層構造体41を、大気中で脱バインダ処理した後、H2/N2=3/100の強還元雰囲気中において1300℃で2時間焼成を行い、焼結された積層体4を得る。その後、大気中において600℃〜1000℃の温度で1時間再酸化処理を施す。

【0046】

次いで、図7に示すように、積層体4の側面に、Agと、Al等を含む導電性ペーストを塗布し、大気中において600℃〜1000℃の温度で1時間〜数時間で焼成して外部電極5を形成する。

【0047】

次に、多孔質素体2へ付加重合型の樹脂を充填する。充填方法としては、特に制限されず、(1)外部電極5,5の部分を適宜の部材で覆った状態で多孔質素体2全体を、付加重合型の樹脂を得るためのモノマーまたはプレポリマー液(重合開始材、安定化剤などの公知の添加剤が適宜添加されていてもよい)中に浸漬させ所定時間保持することにより、多孔質素体2の空孔内にそのモノマーまたはプレポリマーを含浸させ、その後、加熱し重合硬化させる方法、(2)外部電極5,5の部分を覆うことなく多孔質素体2全体を、付加重合型の樹脂を得るためのモノマーまたはプレポリマー液中に浸漬させて多孔質素体2の空孔内にそのモノマーまたはプレポリマーを含浸させ、外部電極5,5に付着した液を溶剤等で除去した後、加熱し重合硬化させる方法、(3)多孔質素体2の露出面から付加重合型の樹脂を得るためのモノマーまたはプレポリマー液を圧入した後、加熱し重合硬化する方法などを例示できる。

【0048】

なお、多孔質素体2への付加重合型樹脂の充填率は、その樹脂を得るためのモノマーまたはプレポリマー液の含浸を1回または複数回繰り返し、その回数を適宜調整することにより、調節することができ、含浸回数が多い方が、樹脂の充填率をより高めることが可能である。あるいは、モノマーまたはプレポリマー液の粘度を調整することによっても、多孔質素体2への樹脂の充填率を調節することができる。また、樹脂の種類にもよるが、例えば、シリコーン系樹脂の場合、加熱重合硬化条件としては、70℃で30分加熱後さらに180℃で1時間加熱するといった手法を例示できる。さらに、モノマーやプレポリマーを重合硬化させる際に、多孔質素体2の表面の樹脂層の架橋を促進するべく、紫外線硬化型を兼ねる樹脂であれば、紫外線照射と加熱を同時に行なってもよい。

【0049】

さらに、図2に示す如く、多孔質素体2の表面上に樹脂層を形成させるには、多孔質素体2に付加重合型の樹脂を得るためのモノマーまたはプレポリマーを含浸させた後、多孔質素体2を洗浄しないか、または、十分に洗浄しない状態で重合硬化させればよい。

【0050】

さらに、図1に示すように、外部電極5の表面に、電気めっきによりNi層7aおよびSn層7bを順次堆積させて端子電極7を形成する。例えば、Ni層7aの形成では、バレルめっき方式を採用し、ワット浴を用いてNiを2μm析出させる。また、Sn層7bの形成では、バレルめっき方式を採用し、中性錫めっき浴を用いて、Snを4μm析出させる。それから、端子電極7上または図示しない配線基板の電極上にはんだを形成し、そのはんだを溶融させて端子電極7と基板の電極とを電気的に接続する。

【0051】

かかる積層電子部品1の製造方法によれば、大気雰囲気にて外部電極5用の導電性ペーストを焼成できる。これにより、還元雰囲気で焼成する場合に比べて、雰囲気制御が簡易になるので、製造コストを低下させることができる。また、前記のとおり、特に、PTCサーミスタを作製する際には、外部電極形成用の導電性ペーストを還元雰囲気で焼成すると、積層体がPTC特性を発現しなくなるが、本発明によれば、積層体4のPTC特性を維持しつつ外部電極5を形成することができるので、たとえば薄膜法で端子電極を形成する場合と比べて量産性を向上できる。

【0052】

<第2実施形態>

図8は、本発明による積層電子部品の第2実施形態の概略構造を示す断面図である。積層電子部品9は、外部電極5の表面に、金属成分としてAgを含むオーバーコート層8が外部電極5を覆うように形成されていること以外は、図1に示す積層電子部品1と同様に構成されたものである。このオーバーコート層8は、例えば、Agを含む導電性ペーストを印刷・焼成することにより形成することができる。なお、図示を省略したが、図8においては、オーバーコート層8,8の外側に端子電極7,7が積層形成されている。

【0053】

かかる構造の積層電子部品9によれば、外部電極5の表面にオーバーコート層8が形成されていることにより、外部電極5に含まれるAl等が、図2に示すような端子電極7を形成するためのめっき液に腐食されることを、より一層確実に防止することができる。

【0054】

なお、上述したとおり、本発明は、上記各実施形態に限定されるものではなく、その要旨を逸脱しない範囲内において適宜変更を加えることが可能である。例えば、多孔質素体2へ含浸させる付加重合型樹脂のモノマーまたはポリマーは、それぞれ複数種のものを混合して用いてもとく、モノマーとプレポリマーをともに用いても構わない。また、積層電子部品1では、外部電極5を形成する前に、多孔質素体2へのモノマーまたはプレポリマーの含浸を行なってもよく、積層電子部品9では、外部電極5の形成前もしくは形成後またはオーバーコート層8の形成後に、多孔質素体2へのモノマーまたはプレポリマーの含浸を行なってもよい。またさらに、多孔質素体2はセラミックスであればよく、半導体セラミックスである必要はない。例えば、積層電子部品1,9として積層セラミックコンデンサを作製する場合には、多孔質素体2は、絶縁性のセラミックスからなるものを用いることができる。さらにまた、内部電極3は、少なくとも1つ以上形成すればよい。

【実施例】

【0055】

以下、本発明の実施例について説明するが、本発明はこれら実施例に限定されるものではない。

【0056】

(実施例1〜8)

上述した製造手順と同様にして、組成が(Ba0.9985Gd0.0015)0.995(Ti0.9985Nb0.0015)O3からなる多孔質素体2と、Niからなる複数の内部電極3を有する3.2mm×1.6mm×0.5mmサイズの積層体4を作製し、この積層体4の側面に、AlおよびAgの含有割合が種々異なる導電性ペーストを塗布し、大気雰囲気中において600℃で焼成して外部電極5を形成した。この多孔質素体2に付加重合型のシリコーン系モノマーを含浸させた後、70℃で30分加熱後さらに180℃で1時間加熱という加熱条件で樹脂を重合硬化させた。さらに、外部電極5,5上に端子電極7,7を、バレルめっきにてワット浴を用いてNiを2μmの厚さで、中性錫めっき浴を用いてSnを4μmの厚さで形成し、積層電子部品としてのPTCサーミスタを、複数製造した。なお、多孔質素体2として焼結密度が80%のものを用い、モノマーの含浸を1回または複数回繰り返し、その含浸回数を適宜調節することにより、多孔質素体2へ樹脂の充填率を種々変化させた。

【0057】

(比較例1)

多孔質素体に付加重合型のシリコーン系モノマーを含浸させず付加重合型の樹脂を充填しなかったこと以外は、上記実施例と同様にして、樹脂の充填率0%のPTCサーミスタを複数製造した。

【0058】

(試験評価1)

実施例1〜8および比較例1で得られたPTCサーミスタについて、多孔質素体の表面のめっき付着率(%)、PTCサーミスタの配線基板への実装後の特性不良発生率(%)、爆ぜ試験での不良発生率(%)を測定評価した。表面のめっき付着率(%)は、PTCサーミスタの多孔質素体の露出面積に対するめっきされた領域の面積から算出した。また、実装後の特性不良発生率(%)は、各PTCサーミスタにつき100体のサンプルを、リフロー処理で配線基板へ実装した後、200℃での抵抗値がリフロー前の抵抗値よりも10%低下したものの個体数の割合から算出した。さらに、爆ぜ試験での不良発生率(%)は、各PTCサーミスタにつき100体のサンプルを、260℃のシリコンオイルに浸漬し、多孔質素体から発泡があったものの個体数の割合から算出した。結果をまとめて表1に示す。また、図9は、表1のデータをグラフ化したものである。

【0059】

【表1】

【0060】

表1および図9より、実施例のPTCサーミスタでは、多孔質素体の表面のめっき付着率、PTCサーミスタの配線基板への実装後の特性不良発生率、および、爆ぜ試験での不良発生率が、比較例1のPTCサーミスタに比して十分に低減され、特に、多孔質素体2への樹脂の充填率が60%以上であると、多孔質素体の表面のめっき付着率を更に十分に抑制でき、また、その充填率が70%以上であると、PTCサーミスタの配線基板への実装後の特性不良発生率を更に十分に改善でき、さらに、その充填率が80%以上であると、爆ぜ試験での不良発生率を更に十分に低減できることが確認された。

【0061】

なお、図10および図11は、それぞれ、樹脂充填率0%(めっき付着率100%)の比較例のPTCサーミスタの多孔質素体の平面外観写真、および、その表層部の断面拡大写真であり、図12および図13は、その断面をEPMAで観察したときのそれぞれNiおよびSnの元素分布を示す図である。これらの結果より、多孔質素体に樹脂を含浸・充填していないPTCサーミスタでは、多孔質素体表面が金属光沢を有しており、また、多孔質素体の内部の深い領域までNiが浸入していることが判明した。

【0062】

また、図14および図15、図16および図17、図18および図19、図20および図21は、それぞれ、樹脂充填率42%(めっき付着率31%)、樹脂充填率56%(めっき付着率9.1%)の比較例のPTCサーミスタ、樹脂充填率82%(めっき付着率3.2%)、樹脂充填率98%(めっき付着率0.5%)の実施例のPTCサーミスタの各多孔質素体の平面外観写真、および、それらの表層部の断面拡大写真である。

【0063】

(参考例1〜6)

多孔質素体2の焼結密度を変化させ、比較例1と同様の手順でPTCサーミスタを製造し、焼結密度と多孔質素体の表面へのめっき付着率との関係を評価した。結果をまとめて表2に示す。また、図22は、表1のデータをグラフ化したものである。

【0064】

【表2】

【0065】

表2および図22より、多孔質素体の焼結密度が90%以下の場合にはめっき付着率が80%を超えてしまう程度にめっきの付着が顕著であるのに対し、焼結密度が90%を超えると、めっき付着率は急激に低下し、めっきの付着は、ほとんど不都合が生じない程度であることが判明した。

【産業上の利用可能性】

【0066】

本発明は、サーミスタ、コンデンサ、インダクタ、LTCC(Low Temperature Co-fired Ceramics)、バリスタ、それらの複合部品からなる積層電子部品等、および、それらを備える機器、装置、システム、設備等、ならびに、それらの製造に広く利用することができる。

【図面の簡単な説明】

【0067】

【図1】本発明による積層電子部品の第1実施形態の概略構造を示す断面図である。

【図2】樹脂が60%以上の充填率で充填された多孔質素体2の実物の一例の表層断面を示す拡大写真である。

【図3】積層電子部品を製造する手順の一例を示す工程図である。

【図4】積層電子部品を製造する手順の一例を示す工程図である。

【図5】積層電子部品を製造する手順の一例を示す工程図である。

【図6】積層電子部品を製造する手順の一例を示す工程図である。

【図7】積層電子部品を製造する手順の一例を示す工程図である。

【図8】本発明による積層電子部品の第2実施形態の概略構造を示す断面図である。

【図9】多孔質素体への樹脂の充填率に対する、表面のめっき付着率、実装後の特性不良発生率、爆ぜ試験での不良発生率を示すグラフである。

【図10】樹脂充填率0%(めっき付着率100%)の比較例のPTCサーミスタの多孔質素体の平面外観写真である。

【図11】樹脂充填率0%(めっき付着率100%)の比較例のPTCサーミスタの多孔質素体の表層部の断面拡大写真である。

【図12】樹脂充填率0%(めっき付着率100%)の比較例のPTCサーミスタの多孔質素体の表層部の断面をEPMAで観察したときのNiの元素分布を示す図である。

【図13】樹脂充填率0%(めっき付着率100%)の比較例のPTCサーミスタの多孔質素体の表層部の断面をEPMAで観察したときのSnの元素分布を示す図である。

【図14】樹脂充填率42%(めっき付着率31%)の比較例のPTCサーミスタの多孔質素体の平面外観写真である。

【図15】樹脂充填率42%(めっき付着率31%)の比較例のPTCサーミスタの多孔質素体の表層部の断面拡大写真である。

【図16】樹脂充填率56%(めっき付着率9.1%)の比較例のPTCサーミスタの多孔質素体の平面外観写真である。

【図17】樹脂充填率56%(めっき付着率9.1%)の比較例のPTCサーミスタの多孔質素体の表層部の断面拡大写真である。

【図18】樹脂充填率82%(めっき付着率3.2%)の比較例のPTCサーミスタの多孔質素体の平面外観写真である。

【図19】樹脂充填率82%(めっき付着率3.2%)の比較例のPTCサーミスタの多孔質素体の表層部の断面拡大写真である。

【図20】樹脂充填率98%(めっき付着率0.5%)の比較例のPTCサーミスタの多孔質素体の平面外観写真である。

【図21】樹脂充填率98%(めっき付着率0.5%)の比較例のPTCサーミスタの多孔質素体の表層部の断面拡大写真である。

【図22】多孔質素体の焼結密度に対する、多孔質素体の表面へのめっき付着率を示すグラフである。

【符号の説明】

【0068】

1,9…積層電子部品、2…多孔質素体、3…内部電極、4…積層体(焼結体)、5…外部電極、7…端子電極、7a…Ni層、7b…Sn層、8…オーバーコート層、10…単位構造、40,41…積層構造体。

【技術分野】

【0001】

本発明は、セラミックスからなる素体と内部電極の積層構造を備える積層電子部品およびその製造方法に関する。

【背景技術】

【0002】

一般に、セラミックス素体、内部電極、および外部電極を有するサーミスタ、コンデンサ、インダクタ、LTCC(Low Temperature Co-fired Ceramics)、バリスタやそれらの複合体からなる積層電子部品は、プリント配線基板等の配線基板に搭載され、外部電極が所定の接続位置にはんだ付けされる。その際、例えばAgからなる外部電極(下地電極)上に、めっきによりNi層およびSn層からなる端子電極を形成したものを用いると、はんだによる基板への接合性が高められ、生産性を向上させ得る。

【0003】

例えば、特許文献1には、かかる端子電極を形成するめっき工程において、めっき電解液が部品素体へ浸入してしまうことに起因して積層電子部品の電気特性が悪化してしまうことを防止すべく、電子部品のセラミック素体の表面部分に存在する全ての細孔に、シリコーン樹脂またはフェノール樹脂が含浸された電子部品が提案されている。

【0004】

【特許文献1】特許第270097号公報

【発明の開示】

【発明が解決しようとする課題】

【0005】

ところで、本発明者が、外部電極に端子電極がめっき形成された上記種々の積層電子部品の物性や電気特性について検討したところ、例えば、特にPTC(Positive Temperature Coefficient)サーミスタのような多孔質のセラッミク素体を有する積層電子部品では、素体の表面や表層部、さらには、素体の内部まで端子電極金属がめっきされることがあり、こうなると、外部電極間の絶縁特性の低下あるいは短絡が生じてしまい、ときには、めっきが内部電極にまで達してしまい、製品機能が失われるといった問題を生じ得ることが判明した。

【0006】

具体的には、PTCサーミスタの両端に外部電極(下地電極)を形成し、ベレルめっきによる電気めっきでNi/Sn端子電極の形成を行なったところ、セラミック素体の全面にめっきが付着した。この素体断面のNi及びSnの元素分布をEPMA(Electron-Probe Microanalyzer)で検査した結果、表層部に大量のNiが付着しており、更に深い部位にもNiが付着していることが判明した。このことから、内部電極に達するような開孔(オープンポア)の内部にめっき液が浸入し、内部電極から給電されることにより、めっきが素体内部から付着・成長していくものと推定される。このような素体へのめっき付着現象は、触媒を用いた無電解めっき、および、触媒を用いずに接触法で無電解めっきを開始する場合にも、同様に見られ、この場合にも、内部電極に達するような開孔(オープンポア)の内部から、めっきが付着・成長していくものと推定される。これに対し、上記特許文献1に開示された従来の方法を用いて、セラミック素体の全面にシリコーン樹脂を含浸したところ、樹脂の種類や樹脂の含浸条件によっては、セラミック素体へのめっきの付着を十分に抑制できないことが確認された。

【0007】

そこで、本発明はかかる事情に鑑みてなされたものであり、外部電極上にめっきにより端子電極が形成される場合でも、セラミックスからなる多孔質素体の表面へのめっき付着を十分に抑止でき、これにより、製品の信頼性低下を防止することが可能な積層電子部品およびその製造方法を提供することを目的とする。

【課題を解決するための手段】

【0008】

本発明者は、上記課題を解決すべく、積層電子部品の多孔質セラミック素体の表面にめっき付着が生じ得る素体材料の物性やそのときの条件、その素体の空孔に充填する樹脂の種類や性状との関係に着目し、鋭意研究を進めた結果、本発明を完成するに至った。すなわち、本発明による積層電子部品は、主としてセラミックスからなり、かつ、複数の空孔を含む多孔質素体(多孔質セラミック素体)と、その多孔質素体内に設けられた少なくとも1つの内部電極とを有する積層体と、内部電極に接続された外部電極と、外部電極上にめっきにより形成された端子電極とを備えるものであり、多孔質素体は、複数の空孔の少なくとも一部に付加重合型(付加重合性)の樹脂が充填されたものである。なお、本発明における多孔質素体に含まれる「空孔」とは、日本工業規格JIS Z2500および同2501に規定される「気孔」と同等のものである。

【0009】

また、後記の多孔質素体における樹脂の「充填率」とは、以下のとおり測定される値である。すなわち、まず、端子電極がめっきで形成される前の状態の積層電子部品を大気圧下150℃で1時間乾燥して水分を蒸発させたものの重量を測定する(重量m1)。次に、その積層電子部品を水中に浸漬させた状態で真空中30分間保持することにより、空孔内に水を含浸させたものの重量を測定する(重量m2)。さらに、その積層電子部品を大気圧下200℃で1時間乾燥した後、外部電極に樹脂が付着しないように、多孔質素体に未硬化の樹脂(重合性のものの場合はモノマー)を含浸させ、その樹脂を乾燥硬化(加熱硬化、重合)させたものの重量を測定する(重量m3)。そして、下記式(1);

充填率(%)=100×(m3−m1)/{(m2−m1)×ρ} …(1)、

で表される関係式に上記重量m1,m2,m3、および樹脂の乾燥硬化状態での密度ρを代入し、樹脂の「充填率」を算出する。

【0010】

このように構成された積層電子部品においては、多孔質素体の空孔に樹脂が充填されており、多孔質素体に開口した空孔(開孔:オープンポア)が樹脂によって閉塞されるので、外部電極上にめっきにより端子電極を形成するときに、そのような開孔からめっき液が多孔質素体の内部へ浸入することにより内部電極にめっき液が到達してめっきが付着・成長することが抑制される。このとき、樹脂による空孔の充填率が高いほど、多孔質素体へのめっき液の浸入を抑えることができると想定されるが、樹脂として例えば脱水縮合型のものを用いると、重合時に反応生成物として水が生じ、多孔質素体2の空孔の内部からその水が放出されることにより空隙が生起され、こうなると、多孔質素体の空孔への樹脂による充填が抑制され、樹脂の充填率を十分に高めることが困難となる。これに対し、付加重合型の樹脂を用いると、重合硬化時に水を生じないので、空隙の発生を抑え、脱水縮合型の樹脂を用いる場合に比して多孔質素体2の空孔の充填率をより高めることが可能となる。

【0011】

また、多孔質素体は、複数の空孔に付加重合型の樹脂が60%以上の充填率で充填されたものであると好適である。

【0012】

本発明者の知見によれば、多孔質素体への樹脂の充填率が60%以上であると、多孔質素体の表面へのめっき付着率(露出面積に対するめっき付着面積の割合)が略5%以下となるように十分に低く抑えられることが確認された。また、本発明による積層電子部品のように付加重合型の樹脂を用いることにより、60%以上の樹脂充填率を簡易かつ確実に達成しやすくなるので、多孔質素体2の内部へのめっき液の浸入をより確実に防止しつつ生産性をも向上させ得る。なお、多孔質素体の露出面上、好ましくはそのほぼ全体に樹脂層が形成されていると、そのバリア効果が一層高められるので好適である。

【0013】

また、上記特許文献1に開示された従来と同様の方法を用いて得られたPTCサーミスタが、リフローなどの加熱処理に供されたり、実装時の加熱や作動時のヒートアップなどによって高温環境に曝されたりした場合、樹脂の含浸条件によっては、高温での抵抗値が有意に低下するといったPTC特性の不良が生じ得ることが確認された。これは、おそらく、PTCサーミスタなどの電子部品のはんだ付けに使用されるフラックスが、加熱時に多孔質素体の開孔内部に流入し、その残留フラックスによってセラミックス製の素体が還元されてしまうことによるものと推測される。

【0014】

これに対し、特に、多孔質素体における樹脂の充填率が70%以上であると、積層電子部品を配線基板などに実装する際の、あるいは、その後に、フラックスが多孔質素体の内部へ流入することが十分に抑制され、特性不良の発生割合(頻度)を格段に低下させることができることが判明した。本発明による積層電子部品のように付加重合型の樹脂を用いれば、このような高い樹脂充填率でも簡易かつ確実に達成しやすい利点がある。

【0015】

さらに、上記従来方法を用いて得られたPTCサーミスタの温度特性の評価を行ったところ、樹脂の含浸条件によっては、セラッミク素体から発泡(いわゆる「爆ぜ」)を生じる個体が有意量発生することも確認された。これは、従来の方法では、セラミック素体の表面の細孔が閉塞されるものの、素体内部に空孔が残存することにより、高温に曝されたときに、空孔内部の空気が膨張し破裂することによって引き起こされるものと推定される。

【0016】

これに対し、殊に、多孔質素体における樹脂の充填率が80%以上であると、「爆ぜ」の発生割合(頻度)を格別に低減できることも判明した。本発明による積層電子部品のように付加重合型の樹脂を用いると、このような更に高い樹脂充填率をも簡易かつ確実に達成しやすいので、極めて有用である。

【0017】

また、多孔質素体が焼成されたもの(焼結体)であり、その焼結密度(実測密度/理論密度×100%)が90%以下のものである場合に、本発明は更に有用である。すなわち、本発明者の研究によれば、多孔質素体として、焼結密度が90%を超えるものを用いた場合には、端子電極のめっき形成時に多孔質素体の表面にめっきの付着がほとんど認められず、焼結密度が90%以下であると、焼結密度の低下に伴って、多孔質素体の表面へのめっきの付着率が急激に増大することが確認された。これは、多孔質素体の焼結密度が90%を超えると開孔(オープンポア)がほとんど生じることがなく、空孔が生成したとしても多くが閉孔(クローズドポア)であってめっき液が浸入しないのに対し、その焼結密度が90%以下になると、開孔の数量および全空孔に対する割合が急増することによるものと推測される。よって、そのような多量の開孔が形成され得る焼結密度90%以下の多孔質素体を備える積層電子部品に適用したときに、本発明の作用効果が一層好適に実現される。

【0018】

また、外部電極を被覆するオーバーコート層を更に有すると、外部電極の表面に端子電極をめっきするときに、めっき液による外部電極の腐食を確実に防止することができるので好適である。

【0019】

さらに、本発明による積層電子部品の製造方法は、本発明の積層電子部品を有効に製造するための方法であって、主としてセラミックスからなり、かつ、複数の空孔を含む多孔質素体内に、少なくとも1つの内部電極を設けて積層構造体を形成する工程と、積層構造体を焼成して積層体(焼結体)を形成する工程と、導電性ペーストを、積層体の内部電極と電気的に接続するように、積層体に塗布する工程と、導電性ペーストを焼成して外部電極を形成する工程と、多孔質素体に付加重合型の樹脂を得るためのモノマーを含浸させ、そのモノマーまたはプレポリマーを重合して複数の空孔に付加重合型の樹脂を、好ましくは60%以上、より好ましくは70%以上、特に好ましくは80%以上の充填率で充填する工程と、外部電極上にめっきにより端子電極を形成する工程とを有する。

【0020】

このとき、内部電極に金属成分としてNi、Cu、またはAlを主として含むものを用い、外部電極に金属成分としてAg、および、100質量部のAgに対して、好ましくは1質量部以上60質量部以下のAl等を含む導電性ペーストを用いると、導電性ペーストが、酸化されやすいCuを含まないので、大気焼成が可能となる。これにより、焼成時の雰囲気制御が簡易になり、金属成分としてCuを含む場合に必要とされる還元雰囲気下での焼成、および、その後の酸化雰囲気下での再焼成が不要となるので、製造コストの増大を防止することもできる。

【発明の効果】

【0021】

本発明の積層電子部品およびその製造方法によれば、多孔質素体に含まれる複数の空孔が、付加重合型の樹脂によって充填されているので、多孔質素体の空孔の充填率を高めやすくなり、端子電極をめっきで形成しても、多孔質素体の開孔からめっき液が浸入して内部電極まで流入することが抑制され、よって、多孔質素体へのめっきの付着が十分に抑止されるので、製品の信頼性が低下してしまうといった不都合を解消することができ、また、高温が印加されたときの特性不良の発生や高温下での「爆ぜ」の発生をも有効に防止することができる。

【発明を実施するための最良の形態】

【0022】

以下、本発明の実施の形態について、図面を参照して説明する。なお、図面中、同一の要素には同一の符号を付し、重複する説明を省略する。また、上下左右等の位置関係は、特に断らない限り、図面に示す位置関係に基づくものとする。さらに、図面の寸法比率は、図示の比率に限定されるものではない。また、以下の実施の形態は、本発明を説明するための例示であり、本発明をその実施の形態のみに限定する趣旨ではない。さらに、本発明は、その要旨を逸脱しない限り、さまざまな変形が可能である。

【0023】

<第1実施形態>

図1は、本発明による積層電子部品の第1実施形態の概略構造を示す断面図である。積層電子部品1は、セラミックスからなり複数の空孔を有する多孔質素体2と、多孔質素体2内に形成された複数の内部電極3とを含む積層体4を有するPTCサーミスタであり、換言すれば、多孔質素体2と内部電極3が積層された単位構造10を少なくとも1つ備えたものである。より具体的には、積層体4の一方の側面に露出した端部を有する内部電極3と、積層体4の他方の側面に露出した端部を有する内部電極3とが交互に積層されている。

【0024】

積層体4の両側面には、それらの側面を覆うように外部電極5,5が設けられており、各外部電極5は、積層体4の一方の側面から露出した内部電極3の群、あるいは積層体4の他方の面から露出した内部電極3の群に電気的に接続されている。

【0025】

さらに、外部電極5,5の外側には、めっきにより端子電極7,7が形成されている。これらの端子電極7,7と、例えば、配線基板(図示せず)上の電極とがはんだ等により接合される。各端子電極7は、例えば、外部電極5側から積層形成されたNi層7aおよびSn層7bを含む2層構造を有する。Ni層7aは、Sn層7bと外部電極5との接触を防止して、Snによる外部電極5の腐食を防止するバリアメタルとして機能するものであり、その厚さは例えば2μm程度である。また、Sn層7bは、はんだの濡れ性を向上させる機能を有するものであり、その厚さは例えば4μm程度とされる。

【0026】

本実施形態のように積層電子部品1としてPTCサーミスタを作製する場合には、先述のとおり、多孔質素体2はセラミックス、具体的には、半導体セラミックスからなる必要があり、より具体的には、例えば、チタン酸バリウム系セラミックスからなるものである。このチタン酸バリウム系セラミックスにおいて、必要に応じて、Baの一部をCa、Sr、Pbなどで置換しても、あるいは、Tiの一部をSn、Zrなどで置換してもよい。また、チタン酸バリウム系半導体セラミックスを得るために添加するドナー元素としては、La、Y、Sm、Ce、Dy、Gd等の希土類元素や、Nb、Ta、Bi、Sb、W等の遷移元素を用いることができる。さらにかかるチタン酸バリウム系半導体セラミックスに、必要に応じてSiO2やMn等を適宜添加して用いてもよい。

【0027】

このように多孔質素体2をチタン酸バリウム系半導体セラミックスで形成することにより、キュリー温度で電気抵抗が急上昇するというPTCサーミスタの特性(PTC特性)が良好に得られる。このようなPTCサーミスタの用途としては、過電流保護、定温度発熱体、過熱検知などが挙げられる。

【0028】

多孔質素体2を形成するために用いられるチタン酸バリウム系セラミックス粉末の合成方法としては、特に限定されるものではないが、例えば、水熱法、加水分解法、共沈法、固相法、ゾルゲル法等を用いることができ、必要に応じて仮焼が施されてもよい。

【0029】

また、多孔質素体2は、複数の空孔に樹脂が好ましくは60%以上、より好ましくは70%以上、更に好ましくは80%以上の充填率で充填されたものである。この樹脂の充填率が60%以上であると、端子電極7をめっきで形成する際に、多孔質素体2に含まれる開孔(オープンポア)からめっき液が多孔質素体2の内部へ浸入することにより内部電極にめっき液が到達してめっきが付着・成長してしまうことを十分に抑制できる。さらに、多孔質素体2への樹脂の充填率が70%以上であると、積層電子部品1の実装時などに懸念されるフラックスの多孔質素体内への流入・残留に起因する特性不良の発生割合を格段に低下させることができ、特に、樹脂の充填率が80%以上となると、積層電子部品1が高温に曝されたときに、空孔内部の空気が膨張し破裂することによって引き起こされるおそれがある「爆ぜ」の発生を格別に低く抑えることができる。

【0030】

また、多孔質素体2は、その露出面上、好ましくはそのほぼ全体に樹脂層が形成されていると、そのバリア効果が一層高められるので好適である。なお、多孔質素体2表面の樹脂層による被覆率は、ハンドリング上に特に不都合がなければ、より高い方が開孔(オープンポア)へのめっき液の浸入が防げられるので好適である。

【0031】

ここで、図2は、樹脂が60%以上の充填率で充填された多孔質素体2の実物の一例の表層断面を示す拡大写真である。多孔質素体2の内部には複数の空孔が形成されており、多くの開孔は内部空孔と連通していることが確認され、図示の如く、それらが樹脂で充填されるとともに、多孔質素体2の表面上に樹脂層が形成されていることがわかる。

【0032】

多孔質素体2の空孔充填に用いられる樹脂の種類は、特に制限されるものではなく、多孔質素体2に含浸させることができる付加重合型の樹脂であれば、種々のものを適宜選択して用いることができる。付加重合型の樹脂を得るためのモノマーまたはプレポリマー(オリゴマー)の種類も制限されず例えば、好ましくは、不飽和反応基を有するもの、特に好ましくは、(メタ)アクリロイル基、ビニル基、エポキシ基、または、それらの誘導基を有するものが挙げられる。また、付加重合型の樹脂の例としてポリジメチルシロキサンが挙げられる。ポリジメチルシロキサンは構造が単純で特性が安定しており、また安価であるので量産性を考慮すると好ましい。

【0033】

上述したとおり、樹脂として脱水縮合型のものを用いると、重合時に反応生成物として水が生じ、多孔質素体2の空孔の内部からその水が放出されることにより空隙が生起され得るのに対し、付加重合型の樹脂を用いると、重合硬化時に水を生じないので、空隙の発生を抑え、脱水縮合型の樹脂を用いる場合に比して多孔質素体2の空孔の充填率をより高めることができる。

【0034】

また、多孔質素体2は焼結体であり、その焼結密度は特に制限されないが、焼結密度が90%以下のものである場合に、上述した樹脂充填による効果が顕著に発現される。すなわち、多孔質素体2の焼結密度が90%を超える場合には、端子電極7のめっき形成時に多孔質素体2の表面に付着するめっきは有意量ではないのに対し、焼結密度が90%以下になると、焼結密度の低下につれて、多孔質素体2の開孔の量および割合が増大することに起因して、多孔質素体2の表面へのめっきの付着率が急増する傾向にある。したがって、多孔質素体2が、かかる多量の開孔が形成され得る焼結密度90%以下のものである場合、付加重合型の樹脂を用いることでその開孔を高い充填率で樹脂充填できるので、多孔質素体2の表面へのめっき付着を効果的に抑止できる。

【0035】

一方、内部電極3には、多孔質素体2との間での確実なオーミック接触を可能とする点から、例えば、Ni、Cu、またはAlを主成分とする材料が用いられ、これらの合金または複合材料であってもよく、低温焼成可能な多孔質素体2を用いることにより、Ni(融点:1450℃)に比べて融点の低いCu(融点1083℃)およびAl(融点660℃)を用いることができる。

【0036】

他方、外部電極5は、例えば、積層体4の側面への導電性ペーストの塗布および焼成により得られる。外部電極5を形成するための導電性ペーストとしては、主として、ガラス粉末と、有機ビヒクル(バインダー)と、金属粉末とを含むものが挙げられ、導電性ペーストの焼成により、有機ビヒクルは揮散し、最終的にガラス成分および金属成分を含む外部電極5が形成される。なお、導電性ペーストには、必要に応じて、粘度調整剤、無機結合剤、酸化剤等種々の添加剤を加えてもよい。

【0037】

本実施形態において、外部電極5は、例えば、金属成分としてAg、および、Al等を含むものであり、このAl等が、内部電極3の構成成分であるNi、Cu、またはAlと、外部電極5に含まれるAgとの接合部位に介在することにより、内部電極3と外部電極5との間の接合面積が増大され、これにより、接続抵抗を十分に低下させることができるとともに、内部電極3と外部電極5との機械的な接合強度をも高めることが可能となる。

【0038】

次に、上記の本実施形態に係る積層電子部品1の製造方法について、図3〜図7を参照して説明する。図3〜図7は、積層電子部品1を製造する手順の一例を示す工程図である。

【0039】

まず、出発原料として、BaCO3、TiO2および硝酸Sm溶液を所定量混合し、純水およびジルコニアボールとともにポリエチレン製ポットに入れて5時間粉砕混合した後、混合液を蒸発乾燥させて、得られた混合粉を1100度で仮焼成する。

【0040】

次に、仮焼粉に対して、再び、純水およびジルコニアボールを用いて、5〜30時間ボールミルによる粉砕を行なった後、蒸発乾燥を行い、チタン酸バリウム半導体セラミック粉末を得る。例えば、組成が(Ba0.9985Gd0.0015)0.995(Ti0.9985Nb0.0015)O3からなるチタン酸バリウム半導体セラミック粉末を得る。

【0041】

次いで、得られた粉末に、有機溶剤、有機バインダおよび可塑剤等を添加して、セラミックスラリーとした後、ドクターブレード法により成形して、図3に示すシート状の多孔質素体2、いわゆるセラミックグリーンシートを得る。

【0042】

さらに、図4に示すように、シート状の多孔質素体2上に、Ni、Cu、またはAlを金属成分として含有する導電性ペーストをスクリーン印刷することにより、内部電極3のパターンを形成する。

【0043】

次に、図5に示すように、内部電極3が形成された複数の多孔質素体2と内部電極3が形成されていない複数の多孔質素体2とを交互に積層し、それを更に加圧して積層構造体40を得る。

【0044】

それから、図6に示すように、積層構造体40を切断することにより個々の積層構造体41に分割する。切断後の積層構造体41の側面からは、内部電極3の端部が露出した状態とされている。

【0045】

次に、積層構造体41を、大気中で脱バインダ処理した後、H2/N2=3/100の強還元雰囲気中において1300℃で2時間焼成を行い、焼結された積層体4を得る。その後、大気中において600℃〜1000℃の温度で1時間再酸化処理を施す。

【0046】

次いで、図7に示すように、積層体4の側面に、Agと、Al等を含む導電性ペーストを塗布し、大気中において600℃〜1000℃の温度で1時間〜数時間で焼成して外部電極5を形成する。

【0047】

次に、多孔質素体2へ付加重合型の樹脂を充填する。充填方法としては、特に制限されず、(1)外部電極5,5の部分を適宜の部材で覆った状態で多孔質素体2全体を、付加重合型の樹脂を得るためのモノマーまたはプレポリマー液(重合開始材、安定化剤などの公知の添加剤が適宜添加されていてもよい)中に浸漬させ所定時間保持することにより、多孔質素体2の空孔内にそのモノマーまたはプレポリマーを含浸させ、その後、加熱し重合硬化させる方法、(2)外部電極5,5の部分を覆うことなく多孔質素体2全体を、付加重合型の樹脂を得るためのモノマーまたはプレポリマー液中に浸漬させて多孔質素体2の空孔内にそのモノマーまたはプレポリマーを含浸させ、外部電極5,5に付着した液を溶剤等で除去した後、加熱し重合硬化させる方法、(3)多孔質素体2の露出面から付加重合型の樹脂を得るためのモノマーまたはプレポリマー液を圧入した後、加熱し重合硬化する方法などを例示できる。

【0048】

なお、多孔質素体2への付加重合型樹脂の充填率は、その樹脂を得るためのモノマーまたはプレポリマー液の含浸を1回または複数回繰り返し、その回数を適宜調整することにより、調節することができ、含浸回数が多い方が、樹脂の充填率をより高めることが可能である。あるいは、モノマーまたはプレポリマー液の粘度を調整することによっても、多孔質素体2への樹脂の充填率を調節することができる。また、樹脂の種類にもよるが、例えば、シリコーン系樹脂の場合、加熱重合硬化条件としては、70℃で30分加熱後さらに180℃で1時間加熱するといった手法を例示できる。さらに、モノマーやプレポリマーを重合硬化させる際に、多孔質素体2の表面の樹脂層の架橋を促進するべく、紫外線硬化型を兼ねる樹脂であれば、紫外線照射と加熱を同時に行なってもよい。

【0049】

さらに、図2に示す如く、多孔質素体2の表面上に樹脂層を形成させるには、多孔質素体2に付加重合型の樹脂を得るためのモノマーまたはプレポリマーを含浸させた後、多孔質素体2を洗浄しないか、または、十分に洗浄しない状態で重合硬化させればよい。

【0050】

さらに、図1に示すように、外部電極5の表面に、電気めっきによりNi層7aおよびSn層7bを順次堆積させて端子電極7を形成する。例えば、Ni層7aの形成では、バレルめっき方式を採用し、ワット浴を用いてNiを2μm析出させる。また、Sn層7bの形成では、バレルめっき方式を採用し、中性錫めっき浴を用いて、Snを4μm析出させる。それから、端子電極7上または図示しない配線基板の電極上にはんだを形成し、そのはんだを溶融させて端子電極7と基板の電極とを電気的に接続する。

【0051】

かかる積層電子部品1の製造方法によれば、大気雰囲気にて外部電極5用の導電性ペーストを焼成できる。これにより、還元雰囲気で焼成する場合に比べて、雰囲気制御が簡易になるので、製造コストを低下させることができる。また、前記のとおり、特に、PTCサーミスタを作製する際には、外部電極形成用の導電性ペーストを還元雰囲気で焼成すると、積層体がPTC特性を発現しなくなるが、本発明によれば、積層体4のPTC特性を維持しつつ外部電極5を形成することができるので、たとえば薄膜法で端子電極を形成する場合と比べて量産性を向上できる。

【0052】

<第2実施形態>

図8は、本発明による積層電子部品の第2実施形態の概略構造を示す断面図である。積層電子部品9は、外部電極5の表面に、金属成分としてAgを含むオーバーコート層8が外部電極5を覆うように形成されていること以外は、図1に示す積層電子部品1と同様に構成されたものである。このオーバーコート層8は、例えば、Agを含む導電性ペーストを印刷・焼成することにより形成することができる。なお、図示を省略したが、図8においては、オーバーコート層8,8の外側に端子電極7,7が積層形成されている。

【0053】

かかる構造の積層電子部品9によれば、外部電極5の表面にオーバーコート層8が形成されていることにより、外部電極5に含まれるAl等が、図2に示すような端子電極7を形成するためのめっき液に腐食されることを、より一層確実に防止することができる。

【0054】

なお、上述したとおり、本発明は、上記各実施形態に限定されるものではなく、その要旨を逸脱しない範囲内において適宜変更を加えることが可能である。例えば、多孔質素体2へ含浸させる付加重合型樹脂のモノマーまたはポリマーは、それぞれ複数種のものを混合して用いてもとく、モノマーとプレポリマーをともに用いても構わない。また、積層電子部品1では、外部電極5を形成する前に、多孔質素体2へのモノマーまたはプレポリマーの含浸を行なってもよく、積層電子部品9では、外部電極5の形成前もしくは形成後またはオーバーコート層8の形成後に、多孔質素体2へのモノマーまたはプレポリマーの含浸を行なってもよい。またさらに、多孔質素体2はセラミックスであればよく、半導体セラミックスである必要はない。例えば、積層電子部品1,9として積層セラミックコンデンサを作製する場合には、多孔質素体2は、絶縁性のセラミックスからなるものを用いることができる。さらにまた、内部電極3は、少なくとも1つ以上形成すればよい。

【実施例】

【0055】

以下、本発明の実施例について説明するが、本発明はこれら実施例に限定されるものではない。

【0056】

(実施例1〜8)

上述した製造手順と同様にして、組成が(Ba0.9985Gd0.0015)0.995(Ti0.9985Nb0.0015)O3からなる多孔質素体2と、Niからなる複数の内部電極3を有する3.2mm×1.6mm×0.5mmサイズの積層体4を作製し、この積層体4の側面に、AlおよびAgの含有割合が種々異なる導電性ペーストを塗布し、大気雰囲気中において600℃で焼成して外部電極5を形成した。この多孔質素体2に付加重合型のシリコーン系モノマーを含浸させた後、70℃で30分加熱後さらに180℃で1時間加熱という加熱条件で樹脂を重合硬化させた。さらに、外部電極5,5上に端子電極7,7を、バレルめっきにてワット浴を用いてNiを2μmの厚さで、中性錫めっき浴を用いてSnを4μmの厚さで形成し、積層電子部品としてのPTCサーミスタを、複数製造した。なお、多孔質素体2として焼結密度が80%のものを用い、モノマーの含浸を1回または複数回繰り返し、その含浸回数を適宜調節することにより、多孔質素体2へ樹脂の充填率を種々変化させた。

【0057】

(比較例1)

多孔質素体に付加重合型のシリコーン系モノマーを含浸させず付加重合型の樹脂を充填しなかったこと以外は、上記実施例と同様にして、樹脂の充填率0%のPTCサーミスタを複数製造した。

【0058】

(試験評価1)

実施例1〜8および比較例1で得られたPTCサーミスタについて、多孔質素体の表面のめっき付着率(%)、PTCサーミスタの配線基板への実装後の特性不良発生率(%)、爆ぜ試験での不良発生率(%)を測定評価した。表面のめっき付着率(%)は、PTCサーミスタの多孔質素体の露出面積に対するめっきされた領域の面積から算出した。また、実装後の特性不良発生率(%)は、各PTCサーミスタにつき100体のサンプルを、リフロー処理で配線基板へ実装した後、200℃での抵抗値がリフロー前の抵抗値よりも10%低下したものの個体数の割合から算出した。さらに、爆ぜ試験での不良発生率(%)は、各PTCサーミスタにつき100体のサンプルを、260℃のシリコンオイルに浸漬し、多孔質素体から発泡があったものの個体数の割合から算出した。結果をまとめて表1に示す。また、図9は、表1のデータをグラフ化したものである。

【0059】

【表1】

【0060】

表1および図9より、実施例のPTCサーミスタでは、多孔質素体の表面のめっき付着率、PTCサーミスタの配線基板への実装後の特性不良発生率、および、爆ぜ試験での不良発生率が、比較例1のPTCサーミスタに比して十分に低減され、特に、多孔質素体2への樹脂の充填率が60%以上であると、多孔質素体の表面のめっき付着率を更に十分に抑制でき、また、その充填率が70%以上であると、PTCサーミスタの配線基板への実装後の特性不良発生率を更に十分に改善でき、さらに、その充填率が80%以上であると、爆ぜ試験での不良発生率を更に十分に低減できることが確認された。

【0061】

なお、図10および図11は、それぞれ、樹脂充填率0%(めっき付着率100%)の比較例のPTCサーミスタの多孔質素体の平面外観写真、および、その表層部の断面拡大写真であり、図12および図13は、その断面をEPMAで観察したときのそれぞれNiおよびSnの元素分布を示す図である。これらの結果より、多孔質素体に樹脂を含浸・充填していないPTCサーミスタでは、多孔質素体表面が金属光沢を有しており、また、多孔質素体の内部の深い領域までNiが浸入していることが判明した。

【0062】

また、図14および図15、図16および図17、図18および図19、図20および図21は、それぞれ、樹脂充填率42%(めっき付着率31%)、樹脂充填率56%(めっき付着率9.1%)の比較例のPTCサーミスタ、樹脂充填率82%(めっき付着率3.2%)、樹脂充填率98%(めっき付着率0.5%)の実施例のPTCサーミスタの各多孔質素体の平面外観写真、および、それらの表層部の断面拡大写真である。

【0063】

(参考例1〜6)

多孔質素体2の焼結密度を変化させ、比較例1と同様の手順でPTCサーミスタを製造し、焼結密度と多孔質素体の表面へのめっき付着率との関係を評価した。結果をまとめて表2に示す。また、図22は、表1のデータをグラフ化したものである。

【0064】

【表2】

【0065】

表2および図22より、多孔質素体の焼結密度が90%以下の場合にはめっき付着率が80%を超えてしまう程度にめっきの付着が顕著であるのに対し、焼結密度が90%を超えると、めっき付着率は急激に低下し、めっきの付着は、ほとんど不都合が生じない程度であることが判明した。

【産業上の利用可能性】

【0066】

本発明は、サーミスタ、コンデンサ、インダクタ、LTCC(Low Temperature Co-fired Ceramics)、バリスタ、それらの複合部品からなる積層電子部品等、および、それらを備える機器、装置、システム、設備等、ならびに、それらの製造に広く利用することができる。

【図面の簡単な説明】

【0067】

【図1】本発明による積層電子部品の第1実施形態の概略構造を示す断面図である。

【図2】樹脂が60%以上の充填率で充填された多孔質素体2の実物の一例の表層断面を示す拡大写真である。

【図3】積層電子部品を製造する手順の一例を示す工程図である。

【図4】積層電子部品を製造する手順の一例を示す工程図である。

【図5】積層電子部品を製造する手順の一例を示す工程図である。

【図6】積層電子部品を製造する手順の一例を示す工程図である。

【図7】積層電子部品を製造する手順の一例を示す工程図である。

【図8】本発明による積層電子部品の第2実施形態の概略構造を示す断面図である。

【図9】多孔質素体への樹脂の充填率に対する、表面のめっき付着率、実装後の特性不良発生率、爆ぜ試験での不良発生率を示すグラフである。

【図10】樹脂充填率0%(めっき付着率100%)の比較例のPTCサーミスタの多孔質素体の平面外観写真である。

【図11】樹脂充填率0%(めっき付着率100%)の比較例のPTCサーミスタの多孔質素体の表層部の断面拡大写真である。

【図12】樹脂充填率0%(めっき付着率100%)の比較例のPTCサーミスタの多孔質素体の表層部の断面をEPMAで観察したときのNiの元素分布を示す図である。

【図13】樹脂充填率0%(めっき付着率100%)の比較例のPTCサーミスタの多孔質素体の表層部の断面をEPMAで観察したときのSnの元素分布を示す図である。

【図14】樹脂充填率42%(めっき付着率31%)の比較例のPTCサーミスタの多孔質素体の平面外観写真である。

【図15】樹脂充填率42%(めっき付着率31%)の比較例のPTCサーミスタの多孔質素体の表層部の断面拡大写真である。

【図16】樹脂充填率56%(めっき付着率9.1%)の比較例のPTCサーミスタの多孔質素体の平面外観写真である。

【図17】樹脂充填率56%(めっき付着率9.1%)の比較例のPTCサーミスタの多孔質素体の表層部の断面拡大写真である。

【図18】樹脂充填率82%(めっき付着率3.2%)の比較例のPTCサーミスタの多孔質素体の平面外観写真である。

【図19】樹脂充填率82%(めっき付着率3.2%)の比較例のPTCサーミスタの多孔質素体の表層部の断面拡大写真である。

【図20】樹脂充填率98%(めっき付着率0.5%)の比較例のPTCサーミスタの多孔質素体の平面外観写真である。

【図21】樹脂充填率98%(めっき付着率0.5%)の比較例のPTCサーミスタの多孔質素体の表層部の断面拡大写真である。

【図22】多孔質素体の焼結密度に対する、多孔質素体の表面へのめっき付着率を示すグラフである。

【符号の説明】

【0068】

1,9…積層電子部品、2…多孔質素体、3…内部電極、4…積層体(焼結体)、5…外部電極、7…端子電極、7a…Ni層、7b…Sn層、8…オーバーコート層、10…単位構造、40,41…積層構造体。

【特許請求の範囲】

【請求項1】

主としてセラミックスからなり、かつ、複数の空孔を含む多孔質素体と、該多孔質素体内に設けられた少なくとも1つの内部電極と、を有する積層体と、

前記内部電極に接続された外部電極と、

前記外部電極上にめっきにより形成された端子電極と、

を備えており、

前記多孔質素体は、前記複数の空孔の少なくとも一部に付加重合型の樹脂が充填されたものである、

積層電子部品。

【請求項2】

前記多孔質素体は、前記複数の空孔に前記付加重合型の樹脂が60%以上の充填率で充填されたものである、

請求項1記載の積層電子部品。

【請求項3】

前記多孔質素体は、焼成されたものであり、焼結密度が90%以下のものである、

請求項1記載の積層電子部品。

【請求項4】

主としてセラミックスからなり、かつ、複数の空孔を含む多孔質素体内に、少なくとも1つの内部電極を設けて積層構造体を形成する工程と、

前記積層構造体を焼成して積層体を形成する工程と、

導電性ペーストを、前記積層体の内部電極と電気的に接続するように、前記積層体に塗布する工程と、

前記導電性ペーストを焼成して外部電極を形成する工程と、

前記多孔質素体に付加重合型の樹脂を得るためのモノマーまたはプレポリマーを含浸させ、該モノマーまたはプレポリマーを重合して前記複数の空孔の少なくとも一部に付加重合型の樹脂を充填する工程と、

前記外部電極上にめっきにより端子電極を形成する工程と、

を有する積層電子部品の製造方法。

【請求項1】

主としてセラミックスからなり、かつ、複数の空孔を含む多孔質素体と、該多孔質素体内に設けられた少なくとも1つの内部電極と、を有する積層体と、

前記内部電極に接続された外部電極と、

前記外部電極上にめっきにより形成された端子電極と、

を備えており、

前記多孔質素体は、前記複数の空孔の少なくとも一部に付加重合型の樹脂が充填されたものである、

積層電子部品。

【請求項2】

前記多孔質素体は、前記複数の空孔に前記付加重合型の樹脂が60%以上の充填率で充填されたものである、

請求項1記載の積層電子部品。

【請求項3】

前記多孔質素体は、焼成されたものであり、焼結密度が90%以下のものである、

請求項1記載の積層電子部品。

【請求項4】

主としてセラミックスからなり、かつ、複数の空孔を含む多孔質素体内に、少なくとも1つの内部電極を設けて積層構造体を形成する工程と、

前記積層構造体を焼成して積層体を形成する工程と、

導電性ペーストを、前記積層体の内部電極と電気的に接続するように、前記積層体に塗布する工程と、

前記導電性ペーストを焼成して外部電極を形成する工程と、

前記多孔質素体に付加重合型の樹脂を得るためのモノマーまたはプレポリマーを含浸させ、該モノマーまたはプレポリマーを重合して前記複数の空孔の少なくとも一部に付加重合型の樹脂を充填する工程と、

前記外部電極上にめっきにより端子電極を形成する工程と、

を有する積層電子部品の製造方法。

【図1】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図22】

【図2】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図22】

【図2】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【公開番号】特開2009−49360(P2009−49360A)

【公開日】平成21年3月5日(2009.3.5)

【国際特許分類】

【出願番号】特願2008−68166(P2008−68166)

【出願日】平成20年3月17日(2008.3.17)

【出願人】(000003067)TDK株式会社 (7,238)

【Fターム(参考)】

【公開日】平成21年3月5日(2009.3.5)

【国際特許分類】

【出願日】平成20年3月17日(2008.3.17)

【出願人】(000003067)TDK株式会社 (7,238)

【Fターム(参考)】

[ Back to top ]