積層電子部品用ビアペースト及びこれを用いた積層電子部品並びにその製造方法

【課題】 ビア導体部周辺のクラックを防止するビアペースト及びこれを用いた積層電子部品並びにその製造方法を提供する。

【解決手段】 本ビアペーストは、金属粉末とセラミック層と焼結できる共素地セラミック粉末とを含有し、共素地セラミック粉末は導電性金属粉末と共素地セラミック粉末との合計の10体積%以上含有される。本積層電子部品は、複数のセラミック層111と複数の導体層112とが交互に積層された積層部11と、積層部11の積層方向に延びて一部の導体層112と接続されたビア導体部12と、を備える積層電子部品1であり、ビア導体部12は、導電性金属相とセラミック層を構成するセラミック成分と焼結できる共素地セラミック成分からなる共素地セラミック相とを有し、共素地セラミック相は、ビア導体部全体の10体積%以上である。

【解決手段】 本ビアペーストは、金属粉末とセラミック層と焼結できる共素地セラミック粉末とを含有し、共素地セラミック粉末は導電性金属粉末と共素地セラミック粉末との合計の10体積%以上含有される。本積層電子部品は、複数のセラミック層111と複数の導体層112とが交互に積層された積層部11と、積層部11の積層方向に延びて一部の導体層112と接続されたビア導体部12と、を備える積層電子部品1であり、ビア導体部12は、導電性金属相とセラミック層を構成するセラミック成分と焼結できる共素地セラミック成分からなる共素地セラミック相とを有し、共素地セラミック相は、ビア導体部全体の10体積%以上である。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は積層電子部品用ビアペースト及びこれを用いた積層電子部品並びにその製造方法に関する。更に詳しくは、複数のセラミック層と複数の導体層とが交互に積層された構造を備える積層電子部品のビア導体部に用いる積層電子部品用ビアペースト及びこれを用いた積層電子部品並びにその製造方法に関する。

【背景技術】

【0002】

近年、集積回路の高速化、高密度化及び配線長の長化等に伴い高周波ノイズの増大が問題となっている。この高周波ノイズは、いわゆる同時スイッチングによる電源電圧の低下に起因する。この対策として、集積回路の直近に電力供給を目的とするコンデンサ(デカップリングコンデンサ)を配置する方法が知られている。このコンデンサでは、小さく、薄く(配線長を短く)、大容量であることが特に要求され、極めて微細且つ精度の高い構造が必要となる。

【0003】

従来、上記のような積層電子部品に設けられたビア導体において、ビア導体の外周縁部にクラックを生じる問題や、ビア導体と各内部電極層との接続不良を生じる問題が知られている。この問題を解決する方法として、下記特許文献1及び2が知られている

下記特許文献1及び2は、平均粒径の異なる2種類の導電性金属粉末を含有するビアホール用導電性ペーストを用いる技術である。

【0004】

【特許文献1】特開2004−273662号公報

【特許文献2】特開2004−228508号公報

【発明の開示】

【発明が解決しようとする課題】

【0005】

上記特許文献1及び2では、レーザー穿孔によりビアホールを形成すると、未焼成内部導体層がビアホールの内壁面から後退することに起因する内部導体層とビア導体との接続不良が改善される点において優れている。しかし、セラミック部分とビア導体との界面近傍に現れるクラックを防止することは困難である。

【0006】

本発明は上記問題を解決するものであり、複数のセラミック層と複数の導体層とが交互に積層された積層部の積層方向に延びて形成されたビア導体部と、セラミック層との間のクラックを確実に防止できる積層電子部品用ビアペースト及びこれを用いた積層電子部品並びにその製造方法を提供することを目的とする。

【課題を解決するための手段】

【0007】

即ち、本発明は以下に示す通りである。

(1)複数のセラミック層と複数の導体層とが交互に積層された積層部と、

該積層部の積層方向に延びて一部の該導体層と接続されたビア導体部と、を備える積層電子部品の該ビア導体部の形成に用いる積層電子部品用ビアペーストであって、

導電性金属粉末と、上記セラミック層を構成するセラミック成分と焼結できる共素地セラミック粉末と、を含有し、

該共素地セラミック粉末は、該導電性金属粉末と該共素地セラミック粉末との合計の10体積%以上含有されることを特徴とする積層電子部品用ビアペースト。

(2)上記導電性金属粉末は、上記共素地セラミック粉末の平均粒径よりも大きい粒径の大径導電性金属粒子を含有する上記(1)に記載の積層電子部品用ビアペースト。

(3)上記大径導電性金属粒子は、上記導電性金属粉末全体の40体積%以上含有される上記(1)又は(2)に記載の積層電子部品用ビアペースト。

(4)上記共素地セラミック粉末の平均粒径は、上記セラミック層となる未焼成セラミック層に含有されるセラミック粉末の平均粒径よりも大きい上記(1)乃至(3)のうちのいずれかに記載の積層電子部品用ビアペースト。

(5)複数のセラミック層と複数の導体層とが交互に積層された積層部と、

該積層部の積層方向に延びて一部の該導体層と接続されたビア導体部と、を備える積層電子部品の製造方法において、

上記積層部となるビアホールを有した未焼成積層部を得る未焼成積層部形成工程と、

該ビアホール内に請求項1乃至4のうちのいずれかに記載の積層電子部品用ビアペーストを充填する充填工程と、

該未焼成積層部及び該ビアホール内に充填されたビアペーストを一体焼成する焼成工程と、を備えることを特徴とする積層電子部品の製造方法。

(6)複数のセラミック層と複数の導体層とが交互に積層された積層部と、

該積層部の積層方向に延びて一部の該導体層と接続されたビア導体部と、を備える積層電子部品において、

上記ビア導体部は、導電性金属相と、上記セラミック層を構成するセラミック成分と焼結できる共素地セラミック成分からなる共素地セラミック相と、を有し、

該共素地セラミック相は、該ビア導体部全体の10体積%以上であることを特徴とする積層電子部品(以下、単に「本発明の積層電子部品」ともいう)。

(7)複数のセラミック層と複数の導体層とが交互に積層された積層部と、

該積層部の積層方向に延びて一部の該導体層と接続されたビア導体部と、を備える積層電子部品において、

上記ビア導体部は、導電性金属相と、上記セラミック層を構成するセラミック成分と焼結できる共素地セラミック成分からなる共素地セラミック相と、を有し、

上記セラミック層内における該ビア導体部を含む上記積層方向に対して垂直な断面に、該ビア導体部内側方向へ10μm以上入り込み、且つ該セラミック層と焼結された上記共素地セラミック相を5ヶ所以上有することを特徴とする積層電子部品(以下、単に「本発明の他の積層電子部品」ともいう)。

(8)上記積層部の積層方向に延びて一層おきの導体層と接続された第1ビア導体部と、

該積層部の積層方向に延びて該第1ビア導体部と接続されていない導体層と接続された第2ビア導体部と、

該第1ビア導体部の端部と接続されて該積層部の表面に導出された第1外部端子と、

該第2ビア導体部の端部と接続されて該積層部の表面に導出された第2外部端子と、を備える積層セラミックコンデンサである上記(6)又は(7)に記載の積層電子部品。

【発明の効果】

【0008】

本発明の積層電子部品用ビアペーストによると、ビア導体部とセラミック層との間のクラックを確実に防止できる。

導電性金属粉末が共素地セラミック粉末の平均粒径よりも大きい粒径の大径導電性金属粒子を含有する場合は、より確実に上記クラックを防止できる。

大径導電性金属粒子が導電性金属粉末全体の40体積%以上含有される場合は、更に確実に上記クラックを防止できる。

共素地セラミック粉末の平均粒径がセラミック層となる未焼成セラミック層に含有されるセラミック粉末の平均粒径よりも大きい場合は、ビア導体部とセラミック層との焼成収縮のタイミングを合わせ易く、ビア導体部とセラミック層との間のクラックを確実に防止できる。

本発明の製造方法によると、積層電子部品におけるビア導体部とセラミック層との間のクラックを確実に防止できる。

共素地セラミック相がビア導体部全体の10体積%以上である本発明の積層電子部品によると、ビア導体部とセラミック層との間のクラックが確実に防止され、信頼性及び耐久性に優れた電子部品が得られる。

ビア導体部内側方向へ入り込んでセラミック層と焼結された共素地セラミック相を所定ヶ所以上有する本発明の他の積層電子部品によると、ビア導体部とセラミック層との間のクラックが確実に防止され、信頼性及び耐久性に優れた電子部品が得られる。

第1ビア導体部と第2ビア導体部と第1外部端子と第2外部端子とを備える積層セラミックコンデンサである場合には、ビア導体部とセラミック層との間のクラックを確実に防止され、信頼性及び耐久性に優れた電子部品が得られる。

【発明を実施するための最良の形態】

【0009】

以下、本発明を詳細に説明する。

[1]積層電子部品用ビアペースト

(1)導電性金属粉末

本発明の積層部品用ビアペースト(以下、単に「ビアペースト」ともいう)は、導電性金属粉末と、共素地セラミック粉末と、を含有し、共素地セラミック粉末は、導電性金属粉末と共素地セラミック粉末との合計の10体積%以上含有されることを特徴とする。

【0010】

上記「導電性金属粉末」は、ニッケル、銅、貴金属(金、銀、白金、パラジウム、ロジウム、オスミニウム、ルテニウム及びイリジウム)、スズ、亜鉛、コバルト、クロム、チタン、タンタル、タングステン並びにインジウム等の金属(導電性金属成分)の粉末が挙げられる。更に、これらの金属のうちの2種以上からなる合金の粉末が挙げられる。これらのなかでも、ニッケル粉末、ニッケル合金(Ni−Cu等)粉末、表面処理が施されたニッケル粉末、貴金属粉末、及び銅粉末が好ましく、更には、ニッケル粉末及びニッケル合金粉末が好ましい。これらの導電性金属粉末は、1種のみを用いてもよく、2種以上を併用してもよい。

【0011】

また、導電性金属粉末の粒度分布は特に限定しない。即ち、例えば、測定される粒度分布においてピークが1つのみの粉末でもよく、ピークが2つ以上の粉末でもよい。また、粒度分布はシャープであってもよくブロードであってもよいが、累積質量が導電性金属粉末全体の90質量%となる粒径(D90)に対する累積質量が導電性金属粉末全体の10質量%となる粒径(D10)の割合(D90/D10)は1.3〜8.0(より好ましくは2.0〜7.8、更に好ましくは2.7〜7.5)であることが好ましい。この範囲であれば導電性金属相と共素地セラミック相とがより均一に分散して配置され、ビア導体部とセラミック層との間のクラックを確実に防止することができる。

【0012】

また、平均粒径は特に限定されないが、0.2〜3.5μmが好ましく、0.5〜3.0μmがより好ましく、0.8〜2.7μmが更に好ましく、1.0〜2.7μmが特に好ましい。平均粒径がこの範囲では、ビアペースト内における導電性金属粉末の凝集をより効果的に抑制でき好ましく、特に積層セラミックコンデンサとして機能させる電子部品において好適である。この平均粒径及び粒度分布はレーザー回折式粒度分布測定で測定できるが、この測定が困難である場合には後述する実施例の方法を用いることができる。

導電性金属粉末の含有量は、後述する共素地セラミック粉末との合計量を100体積%とした場合に、90体積%未満である。

【0013】

また、導電性金属粉末は、共素地セラミック粉末の平均粒径よりも大きい粒径の大径導電性金属粒子を含有することが好ましい。

この大径導電性金属粒子の含有量は特に限定されないが、導電性金属粉末全体の40体積%以上(好ましくは40〜100体積%、更に好ましくは50〜100体積%、75〜100体積%)であることが好ましい。

【0014】

また、上記導電性金属粉末は、共素地セラミック粉末の平均粒径よりも小さい小径導電性金属粒子を含有することができる。この小径導電性金属粒子の含有量は特に限定されないが、導電性金属粉末全体の10〜50体積%(好ましくは20〜50体積%)であることが好ましい。

【0015】

(2)共素地セラミック粉末

上記「共素地セラミック粉末」は、セラミック層を構成するセラミック成分と焼結できるセラミック粉末である。この共素地セラミック粉末を構成するセラミック成分(共素地セラミック成分)としては、誘電特性を有するセラミック成分が挙げられる。即ち、例えば、チタン酸塩系セラミック成分(チタン酸バリウム系、チタン酸ストロンチウム系、チタン酸カルシウム系、チタン酸マグネシウム系)、ニオブ酸塩系セラミック成分、タンタル酸塩系セラミック成分、酸化チタン、酸化タングステン、アルミナ、ジルコニア、シリカ、マグネシア、カルシア等が挙げられる。これらのセラミック成分は1種のみが含有されてもよく、2種以上が含有されてもよい。更に、2種以上が含有される場合には、2種以上の上記セラミック成分が混合された混合成分でもよく、2種以上の上記セラミック成分が複合化された複合成分(複合酸化物等)でもよい。

【0016】

更に、上記セラミック成分として誘電特性を有するガラス成分が挙げられる。このガラスは、通常、少なくともSi、Al及びOを含有する。更に、他の元素として、B、Ca、Mg、Sr、Ba、V、Cr、Mn、Co、Ni、Ga、Y、Zr、Nb、Mo、Tc、In、Sn、Ta、W、Re、Bi、各ランタノイド元素及び各アクチノイド元素等を含有できる。これらの他の元素は1種のみが含有されてもよく、2種以上が含有されてもよい。

【0017】

また、上記誘電特性を有するセラミック成分及び上記誘電特性を有するガラス成分は、各々単独で用いてもよく、併用してもよい。更に、積層電子部品のセラミック層を構成するセラミック成分と、ビアペースト内に含まれるセラミック粉末を構成するセラミック成分とは同じであってもよく、異なっていてもよいが、同一組成系であることが好ましい。即ち、共素地セラミック粉末は、上記積層電子部品のうちのセラミック層を構成するセラミック成分と、同一組成系のセラミック成分からなるセラミック粉末であることが好ましい。

【0018】

尚、同一組成系とは、セラミック成分に含まれる元素を含有量(酸化物換算)が多い順に積算した場合に70質量%を超えるまでに積算される元素種が同じであることを意味する。但し、40質量%を超えるまでに積算される元素種が同一であり、その他に共通して含有される元素種が2種以上あり、且つこれら2種以上の共通する元素種の各々の含有量差が両成分間で各々2N質量%以内(但し、N;共通する元素種の数)である場合には同一組成系である。尚、一方の成分に含有される元素の酸化物換算含有量が2種以上で同じである場合は各元素共、同一組成系を判断するための元素種に含むものとする。また、上記酸化物換算は各元素において最も安定な酸化物によるものとする。

【0019】

また、共素地セラミック粉末の粒度分布は特に限定しない。即ち、例えば、測定される粒度分布においてピークが1つのみの粉末でもよく、ピークが2つ以上の粉末でもよい。また、粒度分布はシャープであってもよくブロードであってもよいが、累積質量が共素地セラミック粉末全体の10質量%となる粒径(D10)と、累積質量が共素地セラミック粉末全体の10質量%となる粒径(D90)との比は1.3〜7.0(より好ましくは3.5〜4.4)であることが好ましい。この範囲であれば導電性金属相と共素地セラミック相とがより均一に分散して配置され、ビア導体部とセラミック層との間のクラックを確実に防止することができる。

【0020】

また、共素地セラミック粉末の平均粒径は特に限定されないが、0.3〜2.0μmが好ましく、0.3〜1.8μmがより好ましく、0.4〜1.5μmが更に好ましく、0.5〜1.3μmが特に好ましい。平均粒径がこの範囲では導電性金属相と共素地セラミック相とがより均一に分散して配置され、ビア導体部とセラミック層との間のクラックを確実に防止できために好ましく、特に積層セラミックコンデンサとして機能させる電子部品において好適である。

【0021】

この共素地セラミック粉末の平均粒径は、焼成されて上記セラミック層となる未焼成セラミック層に含有されるセラミック粉末の平均粒径よりも大きいことが好ましく、特に1.1倍以上であることが好ましい。この共素地セラミック粉末の平均粒径が、未焼成セラミック層に含有されるセラミック粉末の平均粒径よりも大きいことで、ビア導体部とセラミック層との焼成収縮のタイミングを合わせ易く、ビア導体部とセラミック層との間のクラックを確実に防止できる。

この平均粒径及び粒度分布はレーザー回折式粒度分布測定で測定できるが、この測定が困難である場合には後述する実施例の方法を用いることができる。

【0022】

上記共素地セラミック粉末の含有量は、導電性金属粉末と共素地セラミック粉末との合計の10体積%以上(通常49体積%以下)である。この含有量は10〜45体積%が好ましく、12〜40体積%がより好ましく、15〜35体積%が更に好ましい。この範囲であればビア導体部としての導電性を十分に確保しつつ、上記クラックの抑制をすることができる。

【0023】

また、ビアペースト全体に対する導電性金属粉末及び共素地セラミック粉末の含有量は特に限定されないが、通常、ビアペースト全体(100体積%)の30体積%以上(好ましくは40〜70体積%、より好ましくは45〜65体積%、通常70体積%以下)である。この範囲であればビアペーストとして最適な粘度(例えば、後述するように1,00,000Pa・s以下)に調整し易く好ましい。例えば、無機粉末(導電性金属粉末及び共素地セラミック粉末)と有機成分(後述する有機バインダ、溶媒、可塑剤及び消泡剤等)とからなるビアペースト全体を100体積%とした場合に、無機粉末は30体積%以上(好ましくは40〜70体積%、より好ましくは45〜65体積%、通常70体積%以下)とすることができる。

【0024】

(4)他の成分

本発明のビアペーストには、導電性金属粉末及び共素地セラミック粉末以外にも他の成分を含有することができる。他の成分としては、有機成分が挙げられる。即ち、例えば、有機バインダ、溶剤、可塑剤、消泡剤等が挙げられる。

このうち有機バインダとしては、アクリル系樹脂、アルキルセルロース(エチルセルロース、メチルセルロース)及びニトロセルロース等のセルロース類、ポリメチルメタクリレート等のアクリルエステル系樹脂、ポリビニルブチラール等のブチラール系樹脂、フェノール系樹脂、及びポリエステル系樹脂(アルキド樹脂等)などが挙げられる。これらは1種のみを用いてもよく、2種以上を併用してもよい。また、有機バインダの含有量は特に限定されないが、通常、ビアペースト全体の10体積%以下である。

【0025】

また、溶剤としては、ケトン系溶剤(アセトン及びメチルエチルケトン等)、炭化水素系溶剤(シクロヘキサン及びトルエン等)、1価アルコール(ターピネオール及びブチルカルビトール等)、並びに多価アルコール(エチレングリコール及びジエチレングリコール等)などが挙げられる。これらの溶剤は1種のみを用いてもよく、2種以上を併用してもよい。溶剤の含有量は特に限定されないが、有機バインダ全体を100質量部とした場合に45〜70質量部の割合で含有することが好ましい。

【0026】

更に、可塑剤は用いる有機バインダの種類に応じた適当な有機バインダを用いることが好ましい。更に、可塑剤は有機バインダ全体を100質量部とした場合に10〜30質量部の割合で含有することが好ましい。

また、消泡剤はビアペースト全体を100質量部とした場合に0.1〜10質量部の割合で含有することが好ましい。

【0027】

本ビアペーストの粘度は特に限定されないが、1,00,000Pa・s以下(より好ましくは10,000〜35,000Pa・s、通常5,000Pa・s以上)であることが好ましい。この範囲であればビアホールへの充填を確実に行うことができる。また、本ビアペーストを用いるのに適したビアホール径は特に限定されないが、50〜200μm(より好ましくは50〜150μm)が好ましい。更に、ビアホールのアスペクト比は特に限定されないが、50〜100(より好ましくは70〜110)が好ましい。

【0028】

本発明のビアペーストを用いる積層電子部品は、複数のセラミック層と複数の導体層とが交互に積層された積層部と、この積層部の積層方向に延びて一部の導体層と接続されたビア導体部と、を備える。この積層電子部品の構成については、後述する本発明の積層電子部品の構成をそのまま適用できる。

【0029】

[2]積層電子部品の製造方法

本発明の積層電子部品の製造方法は、未焼成積層部形成工程と、充填工程と、焼成工程とを備えることを特徴とする。

上記「未焼成積層部形成工程」は、積層部となるビアホールを有した未焼成積層部を得る工程である。

上記「未焼成積層部」は、焼成されて積層部となる未焼成体であり、ビアホールを備える。この未焼成積層部は、上記セラミック層となる未焼成セラミック層と、上記導体層となる未焼成導体層とが交互に積層された部分である。

【0030】

上記未焼成セラミック層の構成は特に限定されないが、通常、セラミック粉末を含有する。セラミック粉末は、本ビアペーストに含有される共素地セラミック粉末と焼結できるセラミック成分からなることが好ましい。また、この未焼成セラミック層を構成するセラミック粉末は、平均粒径が前記共素地セラミック粉末よりも小さいものであることが好ましい。このセラミック粉末を構成するセラミック成分としては、前記共素地セラミック粉末を構成するセラミック成分をそのまま適用できる。

【0031】

上記未焼成導体層の構成は特に限定されないが、通常、導電性金属粉末と有機成分とを含有する。このうち導電性金属粉末としては、本ビアペーストに含有される導電性金属粉末をそのまま適用できる。但し、未焼成導体層に含有される導電性金属粉末と、本ビアペーストに含有される導電性金属粉末とは、同成分からなってもよく、異なる成分からなってもよい。また、この未焼成導体層を構成する導電性金属粉末は、平均粒径が前記本ビアペーストを構成する導電性金属粉末よりも小さくても、大きくても、同じであってもよいが、小さいことが好ましい。有機成分としては、上記有機成分をそのまま適用できる。

【0032】

この未焼成積層部の形成方法は特に限定されず、未焼成セラミック層の表面に未焼成導体層を印刷形成した未焼成導体層付き未焼成セラミック層を一括的に積層して形成することができる。また、未焼成セラミック層と未焼成導体層とを交互に逐次的に積層して形成することができる。

【0033】

上記「ビアホール」は、未焼成積層体を貫通していてもよく、貫通していないものであってもよい。また、ビアホールの孔径(最大長さ)は特に限定されないが50〜200μm(更には50〜150μm)とすることができる。更に、ビアホールのアスペクト比は特に限定されないが、50〜100(更には70〜110)とすることができる。このビアホールの形成方法は特に限定されず、レーザー光及びドリル等を用いて形成できる。

【0034】

上記「充填工程」は、ビアホール内に本ビアペーストを充填する工程である。この充填工程における充填方法は特に限定されず、例えば、スクリーン印刷法及び圧入印刷法等を用いることができる。

【0035】

上記「焼成工程」は、未焼成積層部及びビアホール内に充填されたビアペーストを一体焼成する工程である。この焼成工程における焼成温度及び焼成雰囲気等は特に限定されないが、通常、焼成温度は1200〜1350℃であり、焼成雰囲気は不活性雰囲気又は酸化雰囲気である。特に導電性金属粉末がNi及びCu等を含有する場合には不活性雰囲気を用いる。

【0036】

[3]積層電子部品

本発明の積層電子部品は、積層部とビア導体部とを備え、ビア導体部は導電性金属相と共素地セラミック相とを有し、この共素地セラミック相はビア導体部全体の10体積%以上であることを特徴とする。

【0037】

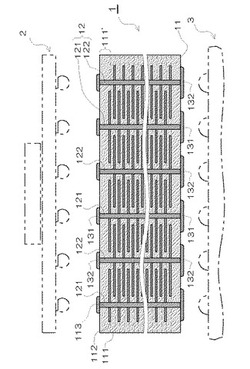

上記「積層部」は、複数のセラミック層と複数の導体層とが交互に積層された部分である。「交互に積層された」とは、セラミック層と導体層とが積層方向に向かって交互に配置されていることである。即ち、例えば、この積層部の構造としては、図1に示す構造が挙げられる。この図1の構造ではセラミック層111と導体層112とが順に各々交互に積層されていることが分かる。

【0038】

但し、この積層部では、結果的に交互の積層であればよく、例えば、連続して積層された複数層の未焼成セラミック層毎に1層又は2層以上の未焼成導体層が積層された構造が焼成されてなる構造も、本発明にいう交互に積層された構造である。

この積層部に含まれるセラミック層と導体層との数は特に限定されないが、通常、各々2層以上(更には10層以上、特に50層以上、通常100層以上)である。

【0039】

上記「セラミック層」は、導体層間に配置されて、導体層に対して絶縁層として機能する層である。また、特に積層コンデンサにおいては誘電体層として機能する。このセラミック層の絶縁性及び誘電性は特に限定されないが、通常、1010Ω・m以上の絶縁性を有する。更に、セラミック層の厚さは特に限定されないが、通常、5.0μm以下である。但し、これらの特性については、所望の絶縁性、静電容量及び耐電圧等の電気的特性、並びに、生産性などに応じて、更には、生産コストに応じて適宜選択することが好ましい。

【0040】

上記セラミック層を構成するセラミック成分は、共素地セラミック層を構成するセラミック成分と焼結されるセラミック成分であればよく、その他は特に限定されない。このセラミック層を構成するセラミック成分としては、前述の共素地セラミック層を構成するセラミック成分をそのまま適用できる。このセラミック層を構成するセラミック成分と、共素地セラミック層を構成するセラミック成分とは、同じであってもよく、異なっていてもよいが、前述のように同一組成系であることが好ましい。

【0041】

上記「導体層」は、導電性を有する層である。この導電性は特に限定されないが、通常、10μΩ・cm以下である。また、導体層は、コンデンサ用パターン、回路用パターン等の所定形状を有するパターン化された導体層であってもよく、グランド等のパターン化されていない導体層であってもよい。但し、導体層の各種特性については、所望の静電容量及び耐電圧等の電気的特性、並びに、生産性などに応じて、更には、生産コストに応じて適宜選択することが好ましい。

上記導体層を構成する導電性金属成分の種類は特に限定されず、前記導電性金属粉末を構成する成分(導電性金属成分)をそのまま適用できる。但し、導体層を構成する導電性金属成分と、ビア導体部を構成する導電性金属成分(即ち、ビアペーストに含有される導電性金属粉末を構成する成分)とは、同じであってもよく、異なっていてもよい。

【0042】

上記「ビア導体部」は、積層部の積層方向に延びて一部の導体層と接続された導体部分である。また、特に積層コンデンサにおいては、セラミック層及び導体層のうちの隣接された少なくとも2層を積層方向に貫通して配置され、貫通された導体層のうちの少なくとも1層と接続されている。

このビア導体部は、通常、少なくとも一端が積層部から露出又は導出されている。従って、ビア導体部は、積層部を貫通して設けられていてもよく、一端側のみが貫通して他端側が貫通しない状態で設けられていてもよい。

【0043】

このビア導体部の形状は特に限定されないが、通常、柱状形状であり、更には、円柱形状である。この形状はスルーホールに依存するものである。股、ビア導体部の大きさも特に限定されず、スルーホールに依存するものであるが、通常、最大径(最大長)が50〜200μm(更には50〜150μm)とすることができ、アスペクト比は50〜150(更には70〜110)とすることができる。

【0044】

また、このビア導体部は、導電性金属相と共素地セラミック相とを有する。即ち、例えば、図3〜6及び図9〜12に示すように導電性金属相125と共素地セラミック相123とを備える。

上記「導電性金属相」は、導電性金属成分からなる導電性を有する相である。この導電性金属成分としては、前記導電性金属粉末を構成する導電性金属成分をそのまま適用できる。

【0045】

上記「共素地セラミック相」は、セラミック層を構成するセラミック成分と焼結できる共素地セラミック成分からなる相である。この共素地セラミック成分としては、前記共素地セラミック粉末を構成する共素地セラミック成分をそのまま適用できる。

この共素地セラミック相は、ビア導体部全体の10体積%以上(通常49体積%以下)である。この含有量は10〜45体積%が好ましく、12〜40体積%がより好ましく、15〜35体積%が更に好ましい。

【0046】

本発明の他の積層電子部品積層部とビア導体部とを備え、ビア導体部は導電性金属相と共素地セラミック相とを有し、積層部のセラミック層内におけるビア導体部を含む積層方向に対して垂直な断面に、ビア導体部内側方向へ10μm以上入り込み、且つセラミック層と焼結された共素地セラミック相(以下、単に「接合相」という)を5ヶ所以上有することを特徴とする。

【0047】

即ち、図3〜5に示すように、ビア導体部の外周部に共素地セラミック相とセラミック層とが焼結された接合相が認められる。この接合相のうち、特にビア導体部内側方向へ10μm以上(ビアの中心に向かって10μm以上)入り込んだ形状の部分を少なくとも5ヶ所以上(更には10ヶ所以上、特に15ヶ所以上)有する。また、セラミック層から連続する接合相により取り囲まれた最大長さが3.0μm以上である導電性金属相(セラミック層から連続する接合相により取り囲まれて他の導電性金属相から孤立している導電性金属相、以下「孤立導電性金属相」という)を5ヶ所以上(更には10ヶ所以上、特に15ヶ所以上)有する。これらの接合相は、ビアペースト内に含有される共素地セラミック粉末がビアホールの内壁を構成するセラミック層と焼結されてなる相と考えられる。セラミック層及びビア導体部がこのような相形態を有することにより、本積層電子部品では、確実にビア導体部とビアホールとの界面におけるクラックが防止されているものと考えられる。更に、共素地セラミック相と導電性金属相とはバランス良く分散されて認められることが好ましい。

【0048】

尚、上記「積層部」、上記「セラミック層」及び上記「導体層」は、前記本発明の積層電子部品における各々をそのまま適用できる。上記「ビア導体部」は、共素地セラミック相の体積割合が限定されず、上記の所定の接合層が認められること以外は、前記本発明の積層電子部品におけるビア導体部をそのまま適用できる。

【0049】

本発明の積層電子部品及び本発明の他の積層電子部品は、積層コンデンサとして好適であり、更にビアアレイ型積層セラミックコンデンサとして特に好適である。この積層コンデンサにおける構成は、通常、積層部の積層方向に延びて一層おきの導体層と接続された第1ビア導体部と、積層部の積層方向に延びて第1ビア導体部と接続されていない導体層と接続された第2ビア導体部と、第1ビア導体部の端部と接続されて積層部の表面に導出された第1外部端子と、第2ビア導体部の端部と接続されて積層部の表面に導出された第2外部端子と、を備える。上記ビアアレイ型積層セラミックコンデンサは、例えば、実施例における図1の構造を有する。

【0050】

本発明の積層電子部品及び本発明の他の積層電子部品では、上記積層部及び上記ビア導体部以外にも他の部分を備えることができる。他の部分としては、外部端子部が挙げられる。このうち外部端子部は、通常、メッキ形成される部分であり、この部分を備える場合には、本発明の積層電子部品におけるように、ビアホール内壁とビア導体部と界面にクラックを有さないことによる優位性を特に享受できる。

【実施例】

【0051】

以下、本発明を実施例により具体的に説明する。

[1]積層電子部品の構成

図1は、積層電子部品1の一例である積層セラミックコンデンサの概略断面図である。この積層電子部品1は、ビアアレイ型積層セラミックコンデンサである。

積層電子部品1は、複数のセラミック層111と複数の導体層112とが交互に積層された積層部11と、積層部11の積層方向に延びて一部の導体層112と接続されたビア導体部12(121及び122)とを備える。

【0052】

積層部11を構成するセラミック層111は、チタン酸バリウムからなり、導体層112の層間に配置されて導体層112の誘電体(絶縁体)として機能する。セラミック層111の厚さは約5μmである。一方、導体層112はニッケルを主成分として形成された厚さ1.5μm〜1.8μmの層である。

【0053】

ビア導体部12は直径約100μm且つアスペクト比約90であり、ビアピッチ約400μmで格子状に多数配設されており、ビア導体部12のうちの一部は、積層部11の積層方向に延びて一層おきの導体層121と接続された第1ビア導体部121である。また、ビア導体部12のうちの他部は、積層部11の積層方向に延びて第1ビア導体部121と接続されていない導体層121と接続された第2ビア導体部122である。これらのビア導体部12は、ニッケルを導電性金属成分とし、チタン酸バリウムを共素地セラミック成分として形成されている。

【0054】

また、第1ビア導体部121及び第2ビア導体部122は、各々共通する導体層とは接続されていない。また、第1ビア導体部と接続された導体層121には、直径約300μmのクリアランスホールが形成されており、この導体層121のクリアランスホール内を直径約100μmの第2導体部が貫通し、この導体層121と絶縁されている。

【0055】

また、第1ビア導体部121の端部と接続されて積層部11の表面に導出された第1外部端子131と、第2ビア導体部122の端部と接続されて積層部11の表面に導出された第2外部端子132と、を備える。

【0056】

更に、積層部11の一面側は、この一面側に配置された第1外部端子131(ハンダバンプ)及び第2外部端子132(ハンダバンプ)と接続することで、他の電子部品2(半導体集積回路素子搭載基板)と接続可能となっている。一方、積層部11の他面側は、この他面側に配置された第1外部端子131(ハンダバンプ)及び第2外部端子132(ハンダバンプ)と接続することで、更に他の電子部品3(マザーボード)と接続可能となっている。上記第1外部端子131及び第2外部端子は、各々ニッケルを主成分として形成され、更に、その表面はニッケルメッキ層及び金メッキ層で被覆されている。

【0057】

[2]積層電子部品の製造

(1)未焼成積層部形成工程

(1−1)未焼成セラミック層の形成

キャリアフィルム上にチタン酸バリウム粉末を含有する未焼成セラミック層用スラリーを塗布し、乾燥させて、キャリアフィルム上に剥離可能に配置された未焼成セラミックグリーンシートを得た。未焼成セラミックグリーンシートは、その後、所望の形状に裁断されて未焼成セラミック層となる。

【0058】

(1−2)未焼成導体部の形成

上記(1−1)で得られた未焼成セラミックグリーンシート上にスクリーンマスクを配置し、導体層用ペーストをスクリーン印刷により印刷したのち乾燥させて、厚さ2〜3μmの未焼成導体層を形成した。

【0059】

(1−3)未焼成セラミック層及び未焼成導体層の積層圧着

上記(1−2)で得られた未焼成導体層が積層形成されたグリーンシート100〜120枚を、未焼成セラミック層と未焼成導体層とが交互に配置されるように積層した。更に、未焼成セラミックグリーンシートのみを3層積層して得られた未焼成カバー部を上記積層体の表裏に配置し、未焼成カバー部、未焼成セラミック層と未焼成導体層とが交互に配置された積層部、未焼成カバー部の順とした。次いで、ラミネート装置を用いて積層方向に温度60℃〜80℃で、押圧力300kg/cm2〜1000kg/cm2の条件で押圧して厚さ約1mmの未焼成積層体を得た。

【0060】

(1−4)ビアホールの形成

上記(1−3)で得られた未焼成積層体に、レーザー加工機を用いて直径約120μmのビアホールを規則的に穿孔した。

【0061】

(2)充填工程

上記(1−4)で形成されたビアホール内に、ペースト圧入充填装置を用いてビアペーストを2.0MPa〜7.5MPaの圧力で圧入充填し、未焼成ビア導体部を形成した。

【0062】

(3)未焼成外部端子の形成

上記(2)で得られた未焼成ビア導体の一端側(上記他の電子部品2を接続可能な側)に、未焼成積層体の一面に配置された厚さ約30μmのメタルマスクを通して外部端子用ペーストを印刷塗布して乾燥し、未焼成外部導体を形成した。

次いで、未焼成ビア導体の他端側(上記他の電子部品3を接続可能な側)に、未焼成積層体の他面に配置された厚さ約25μmのスクリーンマスクを通して外部端子用ペーストを印刷塗布して乾燥し、未焼成外部導体を形成した。

【0063】

(4)焼成工程

上記(3)までに得られた未焼成積層体にブレーク用の溝を格子状に入れた後、この未焼成積層体を脱脂し、その後焼成を行った。

【0064】

(5)外部端子を被覆するメッキ層の形成

上記(4)で得られた焼結体の第1外部端子131及び第2外部端子132の表面に無電解ニッケルメッキを厚さ約0.5μm〜3.0μmに形成した。その後、電解金メッキにより更に厚さ約0.1μm〜1.0μmのメッキ層を形成した。外部端子の表面にメッキを施すことで、外部端子に含まれる共素地セラミック相が端子表面に露出することを防止でき、端子部の濡れ性を向上させることができる。

【0065】

(6)焼結体の裁断

上記(4)で形成されたブレーク用の溝に沿って、焼結体をブレークして、複数の積層電子部品11を得た。

【0066】

[3]各種ペーストによる評価

上記[2]の製造方法において、未焼成セラミック層用スラリー及び導体層ペーストとして各々下記のスラリー及びペーストを用い、更に、ビアペーストとして下記ビアペーストA〜Dを用いて、得られるビア導体部の評価を行った。

【0067】

(1)未焼成セラミック層用スラリー

未焼成セラミック層用スラリー全体を100質量%とした場合に、60質量%のセラミック粉末と、40質量%の有機成分とを含有し、粘度0.5Pa・sである。

上記セラミック粉末は、チタン酸バリウムを主成分とし、平均粒径(D50)0.6μm(D10=0.3μm、D90=1.0μm)である。

【0068】

(2)導体層用ペースト

導体層用ペースト全体を100質量%とした場合に、55質量%の無機粉末と、45質量%の有機成分とを含有し、粘度20Pa・sである。

上記無機粉末は、共素地セラミック粉末とニッケル粉末とからなり、これらの合計を100体積%とした場合に、共素地セラミック粉末は15体積%、及びニッケル粉末85体積%が含有される。

上記共素地セラミック粉末は、純度99%以上のチタン酸バリウムであり、平均粒径(D50)0.1μmである。

ニッケル粉末は、純度99%以上のニッケル粉末であり、平均粒径(D50)0.4μmである。

【0069】

(3)ビアペーストA(実施例1)

ビアペースト全体を100質量%とした場合に、90質量%の無機粉末と10質量%の有機成分(ビアペースト全体を100体積%とした場合に、55体積%の無機粉末と45体積%の有機成分)とを含有し、粘度20,000Pa・s{回転円筒粘度計(東機産業製 RB−80U)により、ロータの回転数1rpm、温度25℃の条件で測定した値。以下同様)である。

上記無機粉末は、共素地セラミック粉末とニッケル粉末とからなり、これらの合計を100体積%とした場合に、共素地セラミック粉末は20体積%、及びニッケル粉末80体積%が含有される。

上記共素地セラミック粉末は、チタン酸バリウムであり、平均粒径(D50)0.64μm(D10=0.29μm、D90=1.15μm)である。

ニッケル粉末は、純度99%以上のニッケル粉末であり、平均粒径(D50)2.4μm(D10=0.5μm、D90=3.5μm)である。更に、大径導電性金属粉末はニッケル粉末全体の90体積%である。

有機成分は、有機バインダ(エチルセルロース)4.5質量%(ビアペースト全体に対する含有量)、有機溶剤(ターピネオール)、分散剤及び酸化防止剤を含む。

【0070】

(4)ビアペーストB(実施例2)

ビアペースト全体を100質量%とした場合に、90質量%の無機粉末と10質量%の有機成分(ビアペースト全体を100体積%とした場合に、50体積%の無機粉末と50体積%の有機成分)とを含有し、粘度30,000Pa・sである。

上記無機粉末は、共素地セラミック粉末とニッケル粉末とからなり、これらの合計を100体積%とした場合に、共素地セラミック粉末は30体積%、及びニッケル粉末70体積%が含有される。

上記共素地セラミック粉末は、チタン酸バリウムであり、平均粒径(D50)1.12μm(D10=0.65μm、D90=1.57μm)である。

ニッケル粉末は、純度99%以上のニッケル粉末であり、平均粒径(D50)1.5μm(D10=0.8μm、D90=2.0μm)である。更に、大径導電性金属粉末はニッケル粉末全体の75体積%である。

有機成分は、実施例1のビアペーストAと共通である。

【0071】

(5)ビアペーストC(比較例1)

ビアペースト全体を100質量%とした場合に、90質量%の無機粉末と10質量%の有機成分(ビアペースト全体を100体積%とした場合に、55体積%の無機粉末と45体積%の有機成分)とを含有し、粘度30,000Pa・sである。

上記無機粉末は、共素地セラミック粉末とニッケル粉末とからなり、これらの合計を100体積%とした場合に、共素地セラミック粉末は7.5体積%、及びニッケル粉末82.5体積%が含有される。

上記共素地セラミック粉末は、チタン酸バリウムであり、平均粒径(D50)0.64μm(D10=0.29μm、D90=1.15μm)である。

ニッケル粉末は、純度99%以上のニッケル粉末であり、平均粒径(D50)2.0μm(D10=0.5μm、D90=2.5μm)である。更に、大径導電性金属粉末はニッケル粉末全体の80体積%である。

有機成分は、実施例1のビアペーストAと共通である。

【0072】

(6)ビアペーストD(比較例2)

ビアペースト全体を100質量%とした場合に、90質量%の無機粉末と10質量%の有機成分(ビアペースト全体を100体積%とした場合に、55体積%の無機粉末と45体積%の有機成分)とを含有し、粘度20,000Pa・sである。

上記無機粉末は、共素地セラミック粉末とニッケル粉末とからなり、これらの合計を100体積%とした場合に、共素地セラミック粉末は2体積%、及びニッケル粉末98体積%が含有される。

上記共素地セラミック粉末は、チタン酸バリウムであり、平均粒径(D50)0.64μm(D10=0.29μm、D90=1.15μm)である。

ニッケル粉末は、純度99%以上のニッケル粉末であり、平均粒径(D50)0.3μm(D10=0.1μm、D90=0.6μm)である。更に、大径導電性金属粉末はニッケル粉末全体の5体積%である。

有機成分は、実施例1のビアペーストAと共通である。

【0073】

(7)実施例の結果

上記ビアペーストA(実施例1)を用いて得られたビア導体部を備える積層電子部品のセラミック層内におけるビア導体部を含む積層方向に対して垂直な断面を電子顕微鏡を用いて約700倍に拡大して得られた画像を図2に示した。また、この図2を上下に4分割し、各々の部分を更に拡大した画像を図3〜6に示した。尚、上記断面は、図1における積層電子部品において他の電子部品2が配置されることとなる側のカバー部111’内(実際には焼結されて一体化されている)におけるビア導体部の断面である。

同様に、ビアペーストB(実施例2)を用いて得られた積層電子部品による画像を図7に示した。

同様に、ビアペーストC(比較例1)を用いて得られた積層電子部品による画像を図8に、この図8を上下に4分割し、各々の部分を更に拡大した画像を図9〜12に示した。

同様に、ビアペーストD(比較例2)を用いて得られた積層電子部品による画像を図13に示した。

【0074】

(8)実施例の効果

比較例のビアペーストを用いて得られた図8〜図13では、ビア導体部の外周部にクラックが認められる。ビア導体部には導電性金属相125と共素地セラミック相123とが認められるものの、共素地セラミック相の割合は面積換算で約7.5%(即ち、体積換算でも約7.5%)と小さい。更に、セラミック層と接合相124はほとんど認められず、また接合相がいずれも小さいことが分かる。

更に、図8〜13では、ポアがビア導体部の共素地セラ部分にほとんど認められず、面積割合で1%であることが分かる。

【0075】

これに対して、実施例のビアペーストを用いて得られた図2〜7ではクラックが認められない。また、図2〜7では、ビア導体部に導電性金属相125と、共素地セラミック相123とが認められ、共素地セラミック相の割合は面積換算で約30%(即ち、体積換算でも約30%)と大きい。更に、これらの各相は、互いにバランスよく分散して配置されていることが分かる。

【0076】

また、図2〜7では、共素地セラミック層のうちのビア導体部の外周部には、積層体を構成するセラミック層と焼結された接合相124がほぼ全周にわたって認められる。更に、接合相は、ビア導体部内側方向へ10μm以上入り込んだ部分が図2では15ヶ所以上、図7では10ヶ所以上認められる。また、特に最大長さが3μm以上である孤立導電性金属相が図2で7ヶ所以上、図7では5ヶ所以上認められる。

【0077】

また、図2〜7では、ビア導体部の共素地セラ部に直径が5μm以下のポアが多数認められ、面積割合でビア導体部全体の5%である。また、ポアはセラミック層と同様なバランスでビア導体部内にも配置されていることが分かる。

これは、前記図8〜13と異なっている部分である。比較例のビアペーストを用いた場合には、焼成収縮がビアペーストと未焼成セラミック層とでは十分に調整ができず、ビアペーストから収縮が過度に早く始まるか、又は過度に早く収縮しているためであると考えられる。即ち、ビア導体部内部からポアが押し出されて、セラミック層との界面でクラックとして現れることが考えられる。

これに対して、実施例のビアペーストを用いた場合には、焼成収縮がセラミック層とほぼ同様なタイミングで始まるか、又は収縮挙動が近似しているためであると考えられる。即ち、クラックとして空隙が形成されず、ビア導体部内部にポアとして空隙が形成されることとなる。

【0078】

尚、本発明においては、上記の具体的実施例に示すものに限られず、目的、用途に応じて本発明の範囲内で種々変更した実施例とすることができる。

【産業上の利用可能性】

【0079】

本発明は電子部品分野において広く利用される。この積層電子部品としては、コンデンサ(特にビアアレイコンデンサ)、配線基板、インターポーザー、セラミック基板内にコンデンサを一体的に備える積層セラミック部品、コンデンサ及び/又は共振器とインダクタとを一体的に備える積層セラミック部品、汎用基板、各種機能部品が埋め込まれた機能基板(LTCC多層デバイス等)などの基板類、MPU及びSAW等のパッケージ類、これら個別部品類、基板類及びパッケージ類の少なくともいずれかを備えるモジュール類等が挙げられる。

【図面の簡単な説明】

【0080】

【図1】本発明の積層電子部品の一例の断面を模式的に示す説明図である。

【図2】実施例1のビアペーストAを用いたビア導体部の断面を拡大して示す説明図である。

【図3】図2の右上1/4部分を更に拡大して示す説明図である。

【図4】図2の右下1/4部分を更に拡大して示す説明図である。

【図5】図2の左上1/4部分を更に拡大して示す説明図である。

【図6】図2の左下1/4部分を更に拡大して示す説明図である。

【図7】実施例2のビアペーストBを用いたビア導体部の断面を拡大して示す説明図である。

【図8】比較例1のビアペーストCを用いたビア導体部の断面を拡大して示す説明図である。

【図9】図8の右上1/4部分を更に拡大して示す説明図である。

【図10】図8の右下1/4部分を更に拡大して示す説明図である。

【図11】図8の左上1/4部分を更に拡大して示す説明図である。

【図12】図8の左下1/4部分を更に拡大して示す説明図である。

【図13】比較例2のビアペーストDを用いたビア導体部の断面を拡大して示す説明図である。

【符号の説明】

【0081】

1;積層電子部品(ビアアレイ型積層セラミックコンデンサ)、11;積層部、111;セラミック層、111’;カバー部、112;導体層、113;ビアホール、12;ビア導体部、121;第1ビア導体部、122;第2ビア導体部、131;第1外部端子、132;第2外部端子、123;共素地セラミック相、124;接合相、125;導電性金属相、125’;孤立導電性金属相、126;ポア、127;クラック、2;他の電子部品、3;更に他の電子部品。

【技術分野】

【0001】

本発明は積層電子部品用ビアペースト及びこれを用いた積層電子部品並びにその製造方法に関する。更に詳しくは、複数のセラミック層と複数の導体層とが交互に積層された構造を備える積層電子部品のビア導体部に用いる積層電子部品用ビアペースト及びこれを用いた積層電子部品並びにその製造方法に関する。

【背景技術】

【0002】

近年、集積回路の高速化、高密度化及び配線長の長化等に伴い高周波ノイズの増大が問題となっている。この高周波ノイズは、いわゆる同時スイッチングによる電源電圧の低下に起因する。この対策として、集積回路の直近に電力供給を目的とするコンデンサ(デカップリングコンデンサ)を配置する方法が知られている。このコンデンサでは、小さく、薄く(配線長を短く)、大容量であることが特に要求され、極めて微細且つ精度の高い構造が必要となる。

【0003】

従来、上記のような積層電子部品に設けられたビア導体において、ビア導体の外周縁部にクラックを生じる問題や、ビア導体と各内部電極層との接続不良を生じる問題が知られている。この問題を解決する方法として、下記特許文献1及び2が知られている

下記特許文献1及び2は、平均粒径の異なる2種類の導電性金属粉末を含有するビアホール用導電性ペーストを用いる技術である。

【0004】

【特許文献1】特開2004−273662号公報

【特許文献2】特開2004−228508号公報

【発明の開示】

【発明が解決しようとする課題】

【0005】

上記特許文献1及び2では、レーザー穿孔によりビアホールを形成すると、未焼成内部導体層がビアホールの内壁面から後退することに起因する内部導体層とビア導体との接続不良が改善される点において優れている。しかし、セラミック部分とビア導体との界面近傍に現れるクラックを防止することは困難である。

【0006】

本発明は上記問題を解決するものであり、複数のセラミック層と複数の導体層とが交互に積層された積層部の積層方向に延びて形成されたビア導体部と、セラミック層との間のクラックを確実に防止できる積層電子部品用ビアペースト及びこれを用いた積層電子部品並びにその製造方法を提供することを目的とする。

【課題を解決するための手段】

【0007】

即ち、本発明は以下に示す通りである。

(1)複数のセラミック層と複数の導体層とが交互に積層された積層部と、

該積層部の積層方向に延びて一部の該導体層と接続されたビア導体部と、を備える積層電子部品の該ビア導体部の形成に用いる積層電子部品用ビアペーストであって、

導電性金属粉末と、上記セラミック層を構成するセラミック成分と焼結できる共素地セラミック粉末と、を含有し、

該共素地セラミック粉末は、該導電性金属粉末と該共素地セラミック粉末との合計の10体積%以上含有されることを特徴とする積層電子部品用ビアペースト。

(2)上記導電性金属粉末は、上記共素地セラミック粉末の平均粒径よりも大きい粒径の大径導電性金属粒子を含有する上記(1)に記載の積層電子部品用ビアペースト。

(3)上記大径導電性金属粒子は、上記導電性金属粉末全体の40体積%以上含有される上記(1)又は(2)に記載の積層電子部品用ビアペースト。

(4)上記共素地セラミック粉末の平均粒径は、上記セラミック層となる未焼成セラミック層に含有されるセラミック粉末の平均粒径よりも大きい上記(1)乃至(3)のうちのいずれかに記載の積層電子部品用ビアペースト。

(5)複数のセラミック層と複数の導体層とが交互に積層された積層部と、

該積層部の積層方向に延びて一部の該導体層と接続されたビア導体部と、を備える積層電子部品の製造方法において、

上記積層部となるビアホールを有した未焼成積層部を得る未焼成積層部形成工程と、

該ビアホール内に請求項1乃至4のうちのいずれかに記載の積層電子部品用ビアペーストを充填する充填工程と、

該未焼成積層部及び該ビアホール内に充填されたビアペーストを一体焼成する焼成工程と、を備えることを特徴とする積層電子部品の製造方法。

(6)複数のセラミック層と複数の導体層とが交互に積層された積層部と、

該積層部の積層方向に延びて一部の該導体層と接続されたビア導体部と、を備える積層電子部品において、

上記ビア導体部は、導電性金属相と、上記セラミック層を構成するセラミック成分と焼結できる共素地セラミック成分からなる共素地セラミック相と、を有し、

該共素地セラミック相は、該ビア導体部全体の10体積%以上であることを特徴とする積層電子部品(以下、単に「本発明の積層電子部品」ともいう)。

(7)複数のセラミック層と複数の導体層とが交互に積層された積層部と、

該積層部の積層方向に延びて一部の該導体層と接続されたビア導体部と、を備える積層電子部品において、

上記ビア導体部は、導電性金属相と、上記セラミック層を構成するセラミック成分と焼結できる共素地セラミック成分からなる共素地セラミック相と、を有し、

上記セラミック層内における該ビア導体部を含む上記積層方向に対して垂直な断面に、該ビア導体部内側方向へ10μm以上入り込み、且つ該セラミック層と焼結された上記共素地セラミック相を5ヶ所以上有することを特徴とする積層電子部品(以下、単に「本発明の他の積層電子部品」ともいう)。

(8)上記積層部の積層方向に延びて一層おきの導体層と接続された第1ビア導体部と、

該積層部の積層方向に延びて該第1ビア導体部と接続されていない導体層と接続された第2ビア導体部と、

該第1ビア導体部の端部と接続されて該積層部の表面に導出された第1外部端子と、

該第2ビア導体部の端部と接続されて該積層部の表面に導出された第2外部端子と、を備える積層セラミックコンデンサである上記(6)又は(7)に記載の積層電子部品。

【発明の効果】

【0008】

本発明の積層電子部品用ビアペーストによると、ビア導体部とセラミック層との間のクラックを確実に防止できる。

導電性金属粉末が共素地セラミック粉末の平均粒径よりも大きい粒径の大径導電性金属粒子を含有する場合は、より確実に上記クラックを防止できる。

大径導電性金属粒子が導電性金属粉末全体の40体積%以上含有される場合は、更に確実に上記クラックを防止できる。

共素地セラミック粉末の平均粒径がセラミック層となる未焼成セラミック層に含有されるセラミック粉末の平均粒径よりも大きい場合は、ビア導体部とセラミック層との焼成収縮のタイミングを合わせ易く、ビア導体部とセラミック層との間のクラックを確実に防止できる。

本発明の製造方法によると、積層電子部品におけるビア導体部とセラミック層との間のクラックを確実に防止できる。

共素地セラミック相がビア導体部全体の10体積%以上である本発明の積層電子部品によると、ビア導体部とセラミック層との間のクラックが確実に防止され、信頼性及び耐久性に優れた電子部品が得られる。

ビア導体部内側方向へ入り込んでセラミック層と焼結された共素地セラミック相を所定ヶ所以上有する本発明の他の積層電子部品によると、ビア導体部とセラミック層との間のクラックが確実に防止され、信頼性及び耐久性に優れた電子部品が得られる。

第1ビア導体部と第2ビア導体部と第1外部端子と第2外部端子とを備える積層セラミックコンデンサである場合には、ビア導体部とセラミック層との間のクラックを確実に防止され、信頼性及び耐久性に優れた電子部品が得られる。

【発明を実施するための最良の形態】

【0009】

以下、本発明を詳細に説明する。

[1]積層電子部品用ビアペースト

(1)導電性金属粉末

本発明の積層部品用ビアペースト(以下、単に「ビアペースト」ともいう)は、導電性金属粉末と、共素地セラミック粉末と、を含有し、共素地セラミック粉末は、導電性金属粉末と共素地セラミック粉末との合計の10体積%以上含有されることを特徴とする。

【0010】

上記「導電性金属粉末」は、ニッケル、銅、貴金属(金、銀、白金、パラジウム、ロジウム、オスミニウム、ルテニウム及びイリジウム)、スズ、亜鉛、コバルト、クロム、チタン、タンタル、タングステン並びにインジウム等の金属(導電性金属成分)の粉末が挙げられる。更に、これらの金属のうちの2種以上からなる合金の粉末が挙げられる。これらのなかでも、ニッケル粉末、ニッケル合金(Ni−Cu等)粉末、表面処理が施されたニッケル粉末、貴金属粉末、及び銅粉末が好ましく、更には、ニッケル粉末及びニッケル合金粉末が好ましい。これらの導電性金属粉末は、1種のみを用いてもよく、2種以上を併用してもよい。

【0011】

また、導電性金属粉末の粒度分布は特に限定しない。即ち、例えば、測定される粒度分布においてピークが1つのみの粉末でもよく、ピークが2つ以上の粉末でもよい。また、粒度分布はシャープであってもよくブロードであってもよいが、累積質量が導電性金属粉末全体の90質量%となる粒径(D90)に対する累積質量が導電性金属粉末全体の10質量%となる粒径(D10)の割合(D90/D10)は1.3〜8.0(より好ましくは2.0〜7.8、更に好ましくは2.7〜7.5)であることが好ましい。この範囲であれば導電性金属相と共素地セラミック相とがより均一に分散して配置され、ビア導体部とセラミック層との間のクラックを確実に防止することができる。

【0012】

また、平均粒径は特に限定されないが、0.2〜3.5μmが好ましく、0.5〜3.0μmがより好ましく、0.8〜2.7μmが更に好ましく、1.0〜2.7μmが特に好ましい。平均粒径がこの範囲では、ビアペースト内における導電性金属粉末の凝集をより効果的に抑制でき好ましく、特に積層セラミックコンデンサとして機能させる電子部品において好適である。この平均粒径及び粒度分布はレーザー回折式粒度分布測定で測定できるが、この測定が困難である場合には後述する実施例の方法を用いることができる。

導電性金属粉末の含有量は、後述する共素地セラミック粉末との合計量を100体積%とした場合に、90体積%未満である。

【0013】

また、導電性金属粉末は、共素地セラミック粉末の平均粒径よりも大きい粒径の大径導電性金属粒子を含有することが好ましい。

この大径導電性金属粒子の含有量は特に限定されないが、導電性金属粉末全体の40体積%以上(好ましくは40〜100体積%、更に好ましくは50〜100体積%、75〜100体積%)であることが好ましい。

【0014】

また、上記導電性金属粉末は、共素地セラミック粉末の平均粒径よりも小さい小径導電性金属粒子を含有することができる。この小径導電性金属粒子の含有量は特に限定されないが、導電性金属粉末全体の10〜50体積%(好ましくは20〜50体積%)であることが好ましい。

【0015】

(2)共素地セラミック粉末

上記「共素地セラミック粉末」は、セラミック層を構成するセラミック成分と焼結できるセラミック粉末である。この共素地セラミック粉末を構成するセラミック成分(共素地セラミック成分)としては、誘電特性を有するセラミック成分が挙げられる。即ち、例えば、チタン酸塩系セラミック成分(チタン酸バリウム系、チタン酸ストロンチウム系、チタン酸カルシウム系、チタン酸マグネシウム系)、ニオブ酸塩系セラミック成分、タンタル酸塩系セラミック成分、酸化チタン、酸化タングステン、アルミナ、ジルコニア、シリカ、マグネシア、カルシア等が挙げられる。これらのセラミック成分は1種のみが含有されてもよく、2種以上が含有されてもよい。更に、2種以上が含有される場合には、2種以上の上記セラミック成分が混合された混合成分でもよく、2種以上の上記セラミック成分が複合化された複合成分(複合酸化物等)でもよい。

【0016】

更に、上記セラミック成分として誘電特性を有するガラス成分が挙げられる。このガラスは、通常、少なくともSi、Al及びOを含有する。更に、他の元素として、B、Ca、Mg、Sr、Ba、V、Cr、Mn、Co、Ni、Ga、Y、Zr、Nb、Mo、Tc、In、Sn、Ta、W、Re、Bi、各ランタノイド元素及び各アクチノイド元素等を含有できる。これらの他の元素は1種のみが含有されてもよく、2種以上が含有されてもよい。

【0017】

また、上記誘電特性を有するセラミック成分及び上記誘電特性を有するガラス成分は、各々単独で用いてもよく、併用してもよい。更に、積層電子部品のセラミック層を構成するセラミック成分と、ビアペースト内に含まれるセラミック粉末を構成するセラミック成分とは同じであってもよく、異なっていてもよいが、同一組成系であることが好ましい。即ち、共素地セラミック粉末は、上記積層電子部品のうちのセラミック層を構成するセラミック成分と、同一組成系のセラミック成分からなるセラミック粉末であることが好ましい。

【0018】

尚、同一組成系とは、セラミック成分に含まれる元素を含有量(酸化物換算)が多い順に積算した場合に70質量%を超えるまでに積算される元素種が同じであることを意味する。但し、40質量%を超えるまでに積算される元素種が同一であり、その他に共通して含有される元素種が2種以上あり、且つこれら2種以上の共通する元素種の各々の含有量差が両成分間で各々2N質量%以内(但し、N;共通する元素種の数)である場合には同一組成系である。尚、一方の成分に含有される元素の酸化物換算含有量が2種以上で同じである場合は各元素共、同一組成系を判断するための元素種に含むものとする。また、上記酸化物換算は各元素において最も安定な酸化物によるものとする。

【0019】

また、共素地セラミック粉末の粒度分布は特に限定しない。即ち、例えば、測定される粒度分布においてピークが1つのみの粉末でもよく、ピークが2つ以上の粉末でもよい。また、粒度分布はシャープであってもよくブロードであってもよいが、累積質量が共素地セラミック粉末全体の10質量%となる粒径(D10)と、累積質量が共素地セラミック粉末全体の10質量%となる粒径(D90)との比は1.3〜7.0(より好ましくは3.5〜4.4)であることが好ましい。この範囲であれば導電性金属相と共素地セラミック相とがより均一に分散して配置され、ビア導体部とセラミック層との間のクラックを確実に防止することができる。

【0020】

また、共素地セラミック粉末の平均粒径は特に限定されないが、0.3〜2.0μmが好ましく、0.3〜1.8μmがより好ましく、0.4〜1.5μmが更に好ましく、0.5〜1.3μmが特に好ましい。平均粒径がこの範囲では導電性金属相と共素地セラミック相とがより均一に分散して配置され、ビア導体部とセラミック層との間のクラックを確実に防止できために好ましく、特に積層セラミックコンデンサとして機能させる電子部品において好適である。

【0021】

この共素地セラミック粉末の平均粒径は、焼成されて上記セラミック層となる未焼成セラミック層に含有されるセラミック粉末の平均粒径よりも大きいことが好ましく、特に1.1倍以上であることが好ましい。この共素地セラミック粉末の平均粒径が、未焼成セラミック層に含有されるセラミック粉末の平均粒径よりも大きいことで、ビア導体部とセラミック層との焼成収縮のタイミングを合わせ易く、ビア導体部とセラミック層との間のクラックを確実に防止できる。

この平均粒径及び粒度分布はレーザー回折式粒度分布測定で測定できるが、この測定が困難である場合には後述する実施例の方法を用いることができる。

【0022】

上記共素地セラミック粉末の含有量は、導電性金属粉末と共素地セラミック粉末との合計の10体積%以上(通常49体積%以下)である。この含有量は10〜45体積%が好ましく、12〜40体積%がより好ましく、15〜35体積%が更に好ましい。この範囲であればビア導体部としての導電性を十分に確保しつつ、上記クラックの抑制をすることができる。

【0023】

また、ビアペースト全体に対する導電性金属粉末及び共素地セラミック粉末の含有量は特に限定されないが、通常、ビアペースト全体(100体積%)の30体積%以上(好ましくは40〜70体積%、より好ましくは45〜65体積%、通常70体積%以下)である。この範囲であればビアペーストとして最適な粘度(例えば、後述するように1,00,000Pa・s以下)に調整し易く好ましい。例えば、無機粉末(導電性金属粉末及び共素地セラミック粉末)と有機成分(後述する有機バインダ、溶媒、可塑剤及び消泡剤等)とからなるビアペースト全体を100体積%とした場合に、無機粉末は30体積%以上(好ましくは40〜70体積%、より好ましくは45〜65体積%、通常70体積%以下)とすることができる。

【0024】

(4)他の成分

本発明のビアペーストには、導電性金属粉末及び共素地セラミック粉末以外にも他の成分を含有することができる。他の成分としては、有機成分が挙げられる。即ち、例えば、有機バインダ、溶剤、可塑剤、消泡剤等が挙げられる。

このうち有機バインダとしては、アクリル系樹脂、アルキルセルロース(エチルセルロース、メチルセルロース)及びニトロセルロース等のセルロース類、ポリメチルメタクリレート等のアクリルエステル系樹脂、ポリビニルブチラール等のブチラール系樹脂、フェノール系樹脂、及びポリエステル系樹脂(アルキド樹脂等)などが挙げられる。これらは1種のみを用いてもよく、2種以上を併用してもよい。また、有機バインダの含有量は特に限定されないが、通常、ビアペースト全体の10体積%以下である。

【0025】

また、溶剤としては、ケトン系溶剤(アセトン及びメチルエチルケトン等)、炭化水素系溶剤(シクロヘキサン及びトルエン等)、1価アルコール(ターピネオール及びブチルカルビトール等)、並びに多価アルコール(エチレングリコール及びジエチレングリコール等)などが挙げられる。これらの溶剤は1種のみを用いてもよく、2種以上を併用してもよい。溶剤の含有量は特に限定されないが、有機バインダ全体を100質量部とした場合に45〜70質量部の割合で含有することが好ましい。

【0026】

更に、可塑剤は用いる有機バインダの種類に応じた適当な有機バインダを用いることが好ましい。更に、可塑剤は有機バインダ全体を100質量部とした場合に10〜30質量部の割合で含有することが好ましい。

また、消泡剤はビアペースト全体を100質量部とした場合に0.1〜10質量部の割合で含有することが好ましい。

【0027】

本ビアペーストの粘度は特に限定されないが、1,00,000Pa・s以下(より好ましくは10,000〜35,000Pa・s、通常5,000Pa・s以上)であることが好ましい。この範囲であればビアホールへの充填を確実に行うことができる。また、本ビアペーストを用いるのに適したビアホール径は特に限定されないが、50〜200μm(より好ましくは50〜150μm)が好ましい。更に、ビアホールのアスペクト比は特に限定されないが、50〜100(より好ましくは70〜110)が好ましい。

【0028】

本発明のビアペーストを用いる積層電子部品は、複数のセラミック層と複数の導体層とが交互に積層された積層部と、この積層部の積層方向に延びて一部の導体層と接続されたビア導体部と、を備える。この積層電子部品の構成については、後述する本発明の積層電子部品の構成をそのまま適用できる。

【0029】

[2]積層電子部品の製造方法

本発明の積層電子部品の製造方法は、未焼成積層部形成工程と、充填工程と、焼成工程とを備えることを特徴とする。

上記「未焼成積層部形成工程」は、積層部となるビアホールを有した未焼成積層部を得る工程である。

上記「未焼成積層部」は、焼成されて積層部となる未焼成体であり、ビアホールを備える。この未焼成積層部は、上記セラミック層となる未焼成セラミック層と、上記導体層となる未焼成導体層とが交互に積層された部分である。

【0030】

上記未焼成セラミック層の構成は特に限定されないが、通常、セラミック粉末を含有する。セラミック粉末は、本ビアペーストに含有される共素地セラミック粉末と焼結できるセラミック成分からなることが好ましい。また、この未焼成セラミック層を構成するセラミック粉末は、平均粒径が前記共素地セラミック粉末よりも小さいものであることが好ましい。このセラミック粉末を構成するセラミック成分としては、前記共素地セラミック粉末を構成するセラミック成分をそのまま適用できる。

【0031】

上記未焼成導体層の構成は特に限定されないが、通常、導電性金属粉末と有機成分とを含有する。このうち導電性金属粉末としては、本ビアペーストに含有される導電性金属粉末をそのまま適用できる。但し、未焼成導体層に含有される導電性金属粉末と、本ビアペーストに含有される導電性金属粉末とは、同成分からなってもよく、異なる成分からなってもよい。また、この未焼成導体層を構成する導電性金属粉末は、平均粒径が前記本ビアペーストを構成する導電性金属粉末よりも小さくても、大きくても、同じであってもよいが、小さいことが好ましい。有機成分としては、上記有機成分をそのまま適用できる。

【0032】

この未焼成積層部の形成方法は特に限定されず、未焼成セラミック層の表面に未焼成導体層を印刷形成した未焼成導体層付き未焼成セラミック層を一括的に積層して形成することができる。また、未焼成セラミック層と未焼成導体層とを交互に逐次的に積層して形成することができる。

【0033】

上記「ビアホール」は、未焼成積層体を貫通していてもよく、貫通していないものであってもよい。また、ビアホールの孔径(最大長さ)は特に限定されないが50〜200μm(更には50〜150μm)とすることができる。更に、ビアホールのアスペクト比は特に限定されないが、50〜100(更には70〜110)とすることができる。このビアホールの形成方法は特に限定されず、レーザー光及びドリル等を用いて形成できる。

【0034】

上記「充填工程」は、ビアホール内に本ビアペーストを充填する工程である。この充填工程における充填方法は特に限定されず、例えば、スクリーン印刷法及び圧入印刷法等を用いることができる。

【0035】

上記「焼成工程」は、未焼成積層部及びビアホール内に充填されたビアペーストを一体焼成する工程である。この焼成工程における焼成温度及び焼成雰囲気等は特に限定されないが、通常、焼成温度は1200〜1350℃であり、焼成雰囲気は不活性雰囲気又は酸化雰囲気である。特に導電性金属粉末がNi及びCu等を含有する場合には不活性雰囲気を用いる。

【0036】

[3]積層電子部品

本発明の積層電子部品は、積層部とビア導体部とを備え、ビア導体部は導電性金属相と共素地セラミック相とを有し、この共素地セラミック相はビア導体部全体の10体積%以上であることを特徴とする。

【0037】

上記「積層部」は、複数のセラミック層と複数の導体層とが交互に積層された部分である。「交互に積層された」とは、セラミック層と導体層とが積層方向に向かって交互に配置されていることである。即ち、例えば、この積層部の構造としては、図1に示す構造が挙げられる。この図1の構造ではセラミック層111と導体層112とが順に各々交互に積層されていることが分かる。

【0038】

但し、この積層部では、結果的に交互の積層であればよく、例えば、連続して積層された複数層の未焼成セラミック層毎に1層又は2層以上の未焼成導体層が積層された構造が焼成されてなる構造も、本発明にいう交互に積層された構造である。

この積層部に含まれるセラミック層と導体層との数は特に限定されないが、通常、各々2層以上(更には10層以上、特に50層以上、通常100層以上)である。

【0039】

上記「セラミック層」は、導体層間に配置されて、導体層に対して絶縁層として機能する層である。また、特に積層コンデンサにおいては誘電体層として機能する。このセラミック層の絶縁性及び誘電性は特に限定されないが、通常、1010Ω・m以上の絶縁性を有する。更に、セラミック層の厚さは特に限定されないが、通常、5.0μm以下である。但し、これらの特性については、所望の絶縁性、静電容量及び耐電圧等の電気的特性、並びに、生産性などに応じて、更には、生産コストに応じて適宜選択することが好ましい。

【0040】

上記セラミック層を構成するセラミック成分は、共素地セラミック層を構成するセラミック成分と焼結されるセラミック成分であればよく、その他は特に限定されない。このセラミック層を構成するセラミック成分としては、前述の共素地セラミック層を構成するセラミック成分をそのまま適用できる。このセラミック層を構成するセラミック成分と、共素地セラミック層を構成するセラミック成分とは、同じであってもよく、異なっていてもよいが、前述のように同一組成系であることが好ましい。

【0041】

上記「導体層」は、導電性を有する層である。この導電性は特に限定されないが、通常、10μΩ・cm以下である。また、導体層は、コンデンサ用パターン、回路用パターン等の所定形状を有するパターン化された導体層であってもよく、グランド等のパターン化されていない導体層であってもよい。但し、導体層の各種特性については、所望の静電容量及び耐電圧等の電気的特性、並びに、生産性などに応じて、更には、生産コストに応じて適宜選択することが好ましい。

上記導体層を構成する導電性金属成分の種類は特に限定されず、前記導電性金属粉末を構成する成分(導電性金属成分)をそのまま適用できる。但し、導体層を構成する導電性金属成分と、ビア導体部を構成する導電性金属成分(即ち、ビアペーストに含有される導電性金属粉末を構成する成分)とは、同じであってもよく、異なっていてもよい。

【0042】

上記「ビア導体部」は、積層部の積層方向に延びて一部の導体層と接続された導体部分である。また、特に積層コンデンサにおいては、セラミック層及び導体層のうちの隣接された少なくとも2層を積層方向に貫通して配置され、貫通された導体層のうちの少なくとも1層と接続されている。

このビア導体部は、通常、少なくとも一端が積層部から露出又は導出されている。従って、ビア導体部は、積層部を貫通して設けられていてもよく、一端側のみが貫通して他端側が貫通しない状態で設けられていてもよい。

【0043】

このビア導体部の形状は特に限定されないが、通常、柱状形状であり、更には、円柱形状である。この形状はスルーホールに依存するものである。股、ビア導体部の大きさも特に限定されず、スルーホールに依存するものであるが、通常、最大径(最大長)が50〜200μm(更には50〜150μm)とすることができ、アスペクト比は50〜150(更には70〜110)とすることができる。

【0044】

また、このビア導体部は、導電性金属相と共素地セラミック相とを有する。即ち、例えば、図3〜6及び図9〜12に示すように導電性金属相125と共素地セラミック相123とを備える。

上記「導電性金属相」は、導電性金属成分からなる導電性を有する相である。この導電性金属成分としては、前記導電性金属粉末を構成する導電性金属成分をそのまま適用できる。

【0045】

上記「共素地セラミック相」は、セラミック層を構成するセラミック成分と焼結できる共素地セラミック成分からなる相である。この共素地セラミック成分としては、前記共素地セラミック粉末を構成する共素地セラミック成分をそのまま適用できる。

この共素地セラミック相は、ビア導体部全体の10体積%以上(通常49体積%以下)である。この含有量は10〜45体積%が好ましく、12〜40体積%がより好ましく、15〜35体積%が更に好ましい。

【0046】

本発明の他の積層電子部品積層部とビア導体部とを備え、ビア導体部は導電性金属相と共素地セラミック相とを有し、積層部のセラミック層内におけるビア導体部を含む積層方向に対して垂直な断面に、ビア導体部内側方向へ10μm以上入り込み、且つセラミック層と焼結された共素地セラミック相(以下、単に「接合相」という)を5ヶ所以上有することを特徴とする。

【0047】

即ち、図3〜5に示すように、ビア導体部の外周部に共素地セラミック相とセラミック層とが焼結された接合相が認められる。この接合相のうち、特にビア導体部内側方向へ10μm以上(ビアの中心に向かって10μm以上)入り込んだ形状の部分を少なくとも5ヶ所以上(更には10ヶ所以上、特に15ヶ所以上)有する。また、セラミック層から連続する接合相により取り囲まれた最大長さが3.0μm以上である導電性金属相(セラミック層から連続する接合相により取り囲まれて他の導電性金属相から孤立している導電性金属相、以下「孤立導電性金属相」という)を5ヶ所以上(更には10ヶ所以上、特に15ヶ所以上)有する。これらの接合相は、ビアペースト内に含有される共素地セラミック粉末がビアホールの内壁を構成するセラミック層と焼結されてなる相と考えられる。セラミック層及びビア導体部がこのような相形態を有することにより、本積層電子部品では、確実にビア導体部とビアホールとの界面におけるクラックが防止されているものと考えられる。更に、共素地セラミック相と導電性金属相とはバランス良く分散されて認められることが好ましい。

【0048】

尚、上記「積層部」、上記「セラミック層」及び上記「導体層」は、前記本発明の積層電子部品における各々をそのまま適用できる。上記「ビア導体部」は、共素地セラミック相の体積割合が限定されず、上記の所定の接合層が認められること以外は、前記本発明の積層電子部品におけるビア導体部をそのまま適用できる。

【0049】

本発明の積層電子部品及び本発明の他の積層電子部品は、積層コンデンサとして好適であり、更にビアアレイ型積層セラミックコンデンサとして特に好適である。この積層コンデンサにおける構成は、通常、積層部の積層方向に延びて一層おきの導体層と接続された第1ビア導体部と、積層部の積層方向に延びて第1ビア導体部と接続されていない導体層と接続された第2ビア導体部と、第1ビア導体部の端部と接続されて積層部の表面に導出された第1外部端子と、第2ビア導体部の端部と接続されて積層部の表面に導出された第2外部端子と、を備える。上記ビアアレイ型積層セラミックコンデンサは、例えば、実施例における図1の構造を有する。

【0050】

本発明の積層電子部品及び本発明の他の積層電子部品では、上記積層部及び上記ビア導体部以外にも他の部分を備えることができる。他の部分としては、外部端子部が挙げられる。このうち外部端子部は、通常、メッキ形成される部分であり、この部分を備える場合には、本発明の積層電子部品におけるように、ビアホール内壁とビア導体部と界面にクラックを有さないことによる優位性を特に享受できる。

【実施例】

【0051】

以下、本発明を実施例により具体的に説明する。

[1]積層電子部品の構成

図1は、積層電子部品1の一例である積層セラミックコンデンサの概略断面図である。この積層電子部品1は、ビアアレイ型積層セラミックコンデンサである。

積層電子部品1は、複数のセラミック層111と複数の導体層112とが交互に積層された積層部11と、積層部11の積層方向に延びて一部の導体層112と接続されたビア導体部12(121及び122)とを備える。

【0052】

積層部11を構成するセラミック層111は、チタン酸バリウムからなり、導体層112の層間に配置されて導体層112の誘電体(絶縁体)として機能する。セラミック層111の厚さは約5μmである。一方、導体層112はニッケルを主成分として形成された厚さ1.5μm〜1.8μmの層である。

【0053】

ビア導体部12は直径約100μm且つアスペクト比約90であり、ビアピッチ約400μmで格子状に多数配設されており、ビア導体部12のうちの一部は、積層部11の積層方向に延びて一層おきの導体層121と接続された第1ビア導体部121である。また、ビア導体部12のうちの他部は、積層部11の積層方向に延びて第1ビア導体部121と接続されていない導体層121と接続された第2ビア導体部122である。これらのビア導体部12は、ニッケルを導電性金属成分とし、チタン酸バリウムを共素地セラミック成分として形成されている。

【0054】

また、第1ビア導体部121及び第2ビア導体部122は、各々共通する導体層とは接続されていない。また、第1ビア導体部と接続された導体層121には、直径約300μmのクリアランスホールが形成されており、この導体層121のクリアランスホール内を直径約100μmの第2導体部が貫通し、この導体層121と絶縁されている。

【0055】

また、第1ビア導体部121の端部と接続されて積層部11の表面に導出された第1外部端子131と、第2ビア導体部122の端部と接続されて積層部11の表面に導出された第2外部端子132と、を備える。

【0056】

更に、積層部11の一面側は、この一面側に配置された第1外部端子131(ハンダバンプ)及び第2外部端子132(ハンダバンプ)と接続することで、他の電子部品2(半導体集積回路素子搭載基板)と接続可能となっている。一方、積層部11の他面側は、この他面側に配置された第1外部端子131(ハンダバンプ)及び第2外部端子132(ハンダバンプ)と接続することで、更に他の電子部品3(マザーボード)と接続可能となっている。上記第1外部端子131及び第2外部端子は、各々ニッケルを主成分として形成され、更に、その表面はニッケルメッキ層及び金メッキ層で被覆されている。

【0057】

[2]積層電子部品の製造

(1)未焼成積層部形成工程

(1−1)未焼成セラミック層の形成

キャリアフィルム上にチタン酸バリウム粉末を含有する未焼成セラミック層用スラリーを塗布し、乾燥させて、キャリアフィルム上に剥離可能に配置された未焼成セラミックグリーンシートを得た。未焼成セラミックグリーンシートは、その後、所望の形状に裁断されて未焼成セラミック層となる。

【0058】

(1−2)未焼成導体部の形成

上記(1−1)で得られた未焼成セラミックグリーンシート上にスクリーンマスクを配置し、導体層用ペーストをスクリーン印刷により印刷したのち乾燥させて、厚さ2〜3μmの未焼成導体層を形成した。

【0059】

(1−3)未焼成セラミック層及び未焼成導体層の積層圧着

上記(1−2)で得られた未焼成導体層が積層形成されたグリーンシート100〜120枚を、未焼成セラミック層と未焼成導体層とが交互に配置されるように積層した。更に、未焼成セラミックグリーンシートのみを3層積層して得られた未焼成カバー部を上記積層体の表裏に配置し、未焼成カバー部、未焼成セラミック層と未焼成導体層とが交互に配置された積層部、未焼成カバー部の順とした。次いで、ラミネート装置を用いて積層方向に温度60℃〜80℃で、押圧力300kg/cm2〜1000kg/cm2の条件で押圧して厚さ約1mmの未焼成積層体を得た。

【0060】

(1−4)ビアホールの形成

上記(1−3)で得られた未焼成積層体に、レーザー加工機を用いて直径約120μmのビアホールを規則的に穿孔した。

【0061】

(2)充填工程

上記(1−4)で形成されたビアホール内に、ペースト圧入充填装置を用いてビアペーストを2.0MPa〜7.5MPaの圧力で圧入充填し、未焼成ビア導体部を形成した。

【0062】

(3)未焼成外部端子の形成

上記(2)で得られた未焼成ビア導体の一端側(上記他の電子部品2を接続可能な側)に、未焼成積層体の一面に配置された厚さ約30μmのメタルマスクを通して外部端子用ペーストを印刷塗布して乾燥し、未焼成外部導体を形成した。

次いで、未焼成ビア導体の他端側(上記他の電子部品3を接続可能な側)に、未焼成積層体の他面に配置された厚さ約25μmのスクリーンマスクを通して外部端子用ペーストを印刷塗布して乾燥し、未焼成外部導体を形成した。

【0063】

(4)焼成工程

上記(3)までに得られた未焼成積層体にブレーク用の溝を格子状に入れた後、この未焼成積層体を脱脂し、その後焼成を行った。

【0064】

(5)外部端子を被覆するメッキ層の形成

上記(4)で得られた焼結体の第1外部端子131及び第2外部端子132の表面に無電解ニッケルメッキを厚さ約0.5μm〜3.0μmに形成した。その後、電解金メッキにより更に厚さ約0.1μm〜1.0μmのメッキ層を形成した。外部端子の表面にメッキを施すことで、外部端子に含まれる共素地セラミック相が端子表面に露出することを防止でき、端子部の濡れ性を向上させることができる。

【0065】

(6)焼結体の裁断

上記(4)で形成されたブレーク用の溝に沿って、焼結体をブレークして、複数の積層電子部品11を得た。

【0066】

[3]各種ペーストによる評価

上記[2]の製造方法において、未焼成セラミック層用スラリー及び導体層ペーストとして各々下記のスラリー及びペーストを用い、更に、ビアペーストとして下記ビアペーストA〜Dを用いて、得られるビア導体部の評価を行った。

【0067】

(1)未焼成セラミック層用スラリー

未焼成セラミック層用スラリー全体を100質量%とした場合に、60質量%のセラミック粉末と、40質量%の有機成分とを含有し、粘度0.5Pa・sである。

上記セラミック粉末は、チタン酸バリウムを主成分とし、平均粒径(D50)0.6μm(D10=0.3μm、D90=1.0μm)である。

【0068】

(2)導体層用ペースト

導体層用ペースト全体を100質量%とした場合に、55質量%の無機粉末と、45質量%の有機成分とを含有し、粘度20Pa・sである。

上記無機粉末は、共素地セラミック粉末とニッケル粉末とからなり、これらの合計を100体積%とした場合に、共素地セラミック粉末は15体積%、及びニッケル粉末85体積%が含有される。

上記共素地セラミック粉末は、純度99%以上のチタン酸バリウムであり、平均粒径(D50)0.1μmである。

ニッケル粉末は、純度99%以上のニッケル粉末であり、平均粒径(D50)0.4μmである。

【0069】

(3)ビアペーストA(実施例1)

ビアペースト全体を100質量%とした場合に、90質量%の無機粉末と10質量%の有機成分(ビアペースト全体を100体積%とした場合に、55体積%の無機粉末と45体積%の有機成分)とを含有し、粘度20,000Pa・s{回転円筒粘度計(東機産業製 RB−80U)により、ロータの回転数1rpm、温度25℃の条件で測定した値。以下同様)である。

上記無機粉末は、共素地セラミック粉末とニッケル粉末とからなり、これらの合計を100体積%とした場合に、共素地セラミック粉末は20体積%、及びニッケル粉末80体積%が含有される。

上記共素地セラミック粉末は、チタン酸バリウムであり、平均粒径(D50)0.64μm(D10=0.29μm、D90=1.15μm)である。

ニッケル粉末は、純度99%以上のニッケル粉末であり、平均粒径(D50)2.4μm(D10=0.5μm、D90=3.5μm)である。更に、大径導電性金属粉末はニッケル粉末全体の90体積%である。

有機成分は、有機バインダ(エチルセルロース)4.5質量%(ビアペースト全体に対する含有量)、有機溶剤(ターピネオール)、分散剤及び酸化防止剤を含む。

【0070】

(4)ビアペーストB(実施例2)

ビアペースト全体を100質量%とした場合に、90質量%の無機粉末と10質量%の有機成分(ビアペースト全体を100体積%とした場合に、50体積%の無機粉末と50体積%の有機成分)とを含有し、粘度30,000Pa・sである。

上記無機粉末は、共素地セラミック粉末とニッケル粉末とからなり、これらの合計を100体積%とした場合に、共素地セラミック粉末は30体積%、及びニッケル粉末70体積%が含有される。

上記共素地セラミック粉末は、チタン酸バリウムであり、平均粒径(D50)1.12μm(D10=0.65μm、D90=1.57μm)である。

ニッケル粉末は、純度99%以上のニッケル粉末であり、平均粒径(D50)1.5μm(D10=0.8μm、D90=2.0μm)である。更に、大径導電性金属粉末はニッケル粉末全体の75体積%である。

有機成分は、実施例1のビアペーストAと共通である。

【0071】

(5)ビアペーストC(比較例1)

ビアペースト全体を100質量%とした場合に、90質量%の無機粉末と10質量%の有機成分(ビアペースト全体を100体積%とした場合に、55体積%の無機粉末と45体積%の有機成分)とを含有し、粘度30,000Pa・sである。

上記無機粉末は、共素地セラミック粉末とニッケル粉末とからなり、これらの合計を100体積%とした場合に、共素地セラミック粉末は7.5体積%、及びニッケル粉末82.5体積%が含有される。

上記共素地セラミック粉末は、チタン酸バリウムであり、平均粒径(D50)0.64μm(D10=0.29μm、D90=1.15μm)である。

ニッケル粉末は、純度99%以上のニッケル粉末であり、平均粒径(D50)2.0μm(D10=0.5μm、D90=2.5μm)である。更に、大径導電性金属粉末はニッケル粉末全体の80体積%である。

有機成分は、実施例1のビアペーストAと共通である。

【0072】

(6)ビアペーストD(比較例2)

ビアペースト全体を100質量%とした場合に、90質量%の無機粉末と10質量%の有機成分(ビアペースト全体を100体積%とした場合に、55体積%の無機粉末と45体積%の有機成分)とを含有し、粘度20,000Pa・sである。

上記無機粉末は、共素地セラミック粉末とニッケル粉末とからなり、これらの合計を100体積%とした場合に、共素地セラミック粉末は2体積%、及びニッケル粉末98体積%が含有される。

上記共素地セラミック粉末は、チタン酸バリウムであり、平均粒径(D50)0.64μm(D10=0.29μm、D90=1.15μm)である。

ニッケル粉末は、純度99%以上のニッケル粉末であり、平均粒径(D50)0.3μm(D10=0.1μm、D90=0.6μm)である。更に、大径導電性金属粉末はニッケル粉末全体の5体積%である。

有機成分は、実施例1のビアペーストAと共通である。

【0073】

(7)実施例の結果

上記ビアペーストA(実施例1)を用いて得られたビア導体部を備える積層電子部品のセラミック層内におけるビア導体部を含む積層方向に対して垂直な断面を電子顕微鏡を用いて約700倍に拡大して得られた画像を図2に示した。また、この図2を上下に4分割し、各々の部分を更に拡大した画像を図3〜6に示した。尚、上記断面は、図1における積層電子部品において他の電子部品2が配置されることとなる側のカバー部111’内(実際には焼結されて一体化されている)におけるビア導体部の断面である。

同様に、ビアペーストB(実施例2)を用いて得られた積層電子部品による画像を図7に示した。

同様に、ビアペーストC(比較例1)を用いて得られた積層電子部品による画像を図8に、この図8を上下に4分割し、各々の部分を更に拡大した画像を図9〜12に示した。

同様に、ビアペーストD(比較例2)を用いて得られた積層電子部品による画像を図13に示した。

【0074】

(8)実施例の効果

比較例のビアペーストを用いて得られた図8〜図13では、ビア導体部の外周部にクラックが認められる。ビア導体部には導電性金属相125と共素地セラミック相123とが認められるものの、共素地セラミック相の割合は面積換算で約7.5%(即ち、体積換算でも約7.5%)と小さい。更に、セラミック層と接合相124はほとんど認められず、また接合相がいずれも小さいことが分かる。

更に、図8〜13では、ポアがビア導体部の共素地セラ部分にほとんど認められず、面積割合で1%であることが分かる。

【0075】

これに対して、実施例のビアペーストを用いて得られた図2〜7ではクラックが認められない。また、図2〜7では、ビア導体部に導電性金属相125と、共素地セラミック相123とが認められ、共素地セラミック相の割合は面積換算で約30%(即ち、体積換算でも約30%)と大きい。更に、これらの各相は、互いにバランスよく分散して配置されていることが分かる。

【0076】

また、図2〜7では、共素地セラミック層のうちのビア導体部の外周部には、積層体を構成するセラミック層と焼結された接合相124がほぼ全周にわたって認められる。更に、接合相は、ビア導体部内側方向へ10μm以上入り込んだ部分が図2では15ヶ所以上、図7では10ヶ所以上認められる。また、特に最大長さが3μm以上である孤立導電性金属相が図2で7ヶ所以上、図7では5ヶ所以上認められる。

【0077】

また、図2〜7では、ビア導体部の共素地セラ部に直径が5μm以下のポアが多数認められ、面積割合でビア導体部全体の5%である。また、ポアはセラミック層と同様なバランスでビア導体部内にも配置されていることが分かる。

これは、前記図8〜13と異なっている部分である。比較例のビアペーストを用いた場合には、焼成収縮がビアペーストと未焼成セラミック層とでは十分に調整ができず、ビアペーストから収縮が過度に早く始まるか、又は過度に早く収縮しているためであると考えられる。即ち、ビア導体部内部からポアが押し出されて、セラミック層との界面でクラックとして現れることが考えられる。

これに対して、実施例のビアペーストを用いた場合には、焼成収縮がセラミック層とほぼ同様なタイミングで始まるか、又は収縮挙動が近似しているためであると考えられる。即ち、クラックとして空隙が形成されず、ビア導体部内部にポアとして空隙が形成されることとなる。

【0078】

尚、本発明においては、上記の具体的実施例に示すものに限られず、目的、用途に応じて本発明の範囲内で種々変更した実施例とすることができる。

【産業上の利用可能性】

【0079】

本発明は電子部品分野において広く利用される。この積層電子部品としては、コンデンサ(特にビアアレイコンデンサ)、配線基板、インターポーザー、セラミック基板内にコンデンサを一体的に備える積層セラミック部品、コンデンサ及び/又は共振器とインダクタとを一体的に備える積層セラミック部品、汎用基板、各種機能部品が埋め込まれた機能基板(LTCC多層デバイス等)などの基板類、MPU及びSAW等のパッケージ類、これら個別部品類、基板類及びパッケージ類の少なくともいずれかを備えるモジュール類等が挙げられる。

【図面の簡単な説明】

【0080】

【図1】本発明の積層電子部品の一例の断面を模式的に示す説明図である。

【図2】実施例1のビアペーストAを用いたビア導体部の断面を拡大して示す説明図である。

【図3】図2の右上1/4部分を更に拡大して示す説明図である。

【図4】図2の右下1/4部分を更に拡大して示す説明図である。

【図5】図2の左上1/4部分を更に拡大して示す説明図である。

【図6】図2の左下1/4部分を更に拡大して示す説明図である。

【図7】実施例2のビアペーストBを用いたビア導体部の断面を拡大して示す説明図である。

【図8】比較例1のビアペーストCを用いたビア導体部の断面を拡大して示す説明図である。

【図9】図8の右上1/4部分を更に拡大して示す説明図である。

【図10】図8の右下1/4部分を更に拡大して示す説明図である。

【図11】図8の左上1/4部分を更に拡大して示す説明図である。

【図12】図8の左下1/4部分を更に拡大して示す説明図である。

【図13】比較例2のビアペーストDを用いたビア導体部の断面を拡大して示す説明図である。

【符号の説明】

【0081】

1;積層電子部品(ビアアレイ型積層セラミックコンデンサ)、11;積層部、111;セラミック層、111’;カバー部、112;導体層、113;ビアホール、12;ビア導体部、121;第1ビア導体部、122;第2ビア導体部、131;第1外部端子、132;第2外部端子、123;共素地セラミック相、124;接合相、125;導電性金属相、125’;孤立導電性金属相、126;ポア、127;クラック、2;他の電子部品、3;更に他の電子部品。

【特許請求の範囲】

【請求項1】

複数のセラミック層と複数の導体層とが交互に積層された積層部と、

該積層部の積層方向に延びて一部の該導体層と接続されたビア導体部と、を備える積層電子部品の該ビア導体部の形成に用いる積層電子部品用ビアペーストであって、

導電性金属粉末と、上記セラミック層を構成するセラミック成分と焼結できる共素地セラミック粉末と、を含有し、

該共素地セラミック粉末は、該導電性金属粉末と該共素地セラミック粉末との合計の10体積%以上含有されることを特徴とする積層電子部品用ビアペースト。

【請求項2】

上記導電性金属粉末は、上記共素地セラミック粉末の平均粒径よりも大きい粒径の大径導電性金属粒子を含有する請求項1に記載の積層電子部品用ビアペースト。

【請求項3】

上記大径導電性金属粒子は、上記導電性金属粉末全体の40体積%以上含有される請求項1又は2に記載の積層電子部品用ビアペースト。

【請求項4】

上記共素地セラミック粉末の平均粒径は、上記セラミック層となる未焼成セラミック層に含有されるセラミック粉末の平均粒径よりも大きい請求項1乃至3のうちのいずれかに記載の積層電子部品用ビアペースト。

【請求項5】

複数のセラミック層と複数の導体層とが交互に積層された積層部と、

該積層部の積層方向に延びて一部の該導体層と接続されたビア導体部と、を備える積層電子部品の製造方法において、

上記積層部となるビアホールを有した未焼成積層部を得る未焼成積層部形成工程と、

該ビアホール内に請求項1乃至4のうちのいずれかに記載の積層電子部品用ビアペーストを充填する充填工程と、

該未焼成積層部及び該ビアホール内に充填されたビアペーストを一体焼成する焼成工程と、を備えることを特徴とする積層電子部品の製造方法。

【請求項6】

複数のセラミック層と複数の導体層とが交互に積層された積層部と、

該積層部の積層方向に延びて一部の該導体層と接続されたビア導体部と、を備える積層電子部品において、

上記ビア導体部は、導電性金属相と、上記セラミック層を構成するセラミック成分と焼結できる共素地セラミック成分からなる共素地セラミック相と、を有し、

該共素地セラミック相は、該ビア導体部全体の10体積%以上であることを特徴とする積層電子部品。

【請求項7】

複数のセラミック層と複数の導体層とが交互に積層された積層部と、

該積層部の積層方向に延びて一部の該導体層と接続されたビア導体部と、を備える積層電子部品において、

上記ビア導体部は、導電性金属相と、上記セラミック層を構成するセラミック成分と焼結できる共素地セラミック成分からなる共素地セラミック相と、を有し、

上記セラミック層内における該ビア導体部を含む上記積層方向に対して垂直な断面に、該ビア導体部内側方向へ10μm以上入り込み、且つ該セラミック層と焼結された上記共素地セラミック相を5ヶ所以上有することを特徴とする積層電子部品。

【請求項8】

上記積層部の積層方向に延びて一層おきの導体層と接続された第1ビア導体部と、

該積層部の積層方向に延びて該第1ビア導体部と接続されていない導体層と接続された第2ビア導体部と、

該第1ビア導体部の端部と接続されて該積層部の表面に導出された第1外部端子と、

該第2ビア導体部の端部と接続されて該積層部の表面に導出された第2外部端子と、を備える積層セラミックコンデンサである請求項6又は7に記載の積層電子部品。

【請求項1】

複数のセラミック層と複数の導体層とが交互に積層された積層部と、

該積層部の積層方向に延びて一部の該導体層と接続されたビア導体部と、を備える積層電子部品の該ビア導体部の形成に用いる積層電子部品用ビアペーストであって、

導電性金属粉末と、上記セラミック層を構成するセラミック成分と焼結できる共素地セラミック粉末と、を含有し、

該共素地セラミック粉末は、該導電性金属粉末と該共素地セラミック粉末との合計の10体積%以上含有されることを特徴とする積層電子部品用ビアペースト。

【請求項2】

上記導電性金属粉末は、上記共素地セラミック粉末の平均粒径よりも大きい粒径の大径導電性金属粒子を含有する請求項1に記載の積層電子部品用ビアペースト。

【請求項3】

上記大径導電性金属粒子は、上記導電性金属粉末全体の40体積%以上含有される請求項1又は2に記載の積層電子部品用ビアペースト。

【請求項4】

上記共素地セラミック粉末の平均粒径は、上記セラミック層となる未焼成セラミック層に含有されるセラミック粉末の平均粒径よりも大きい請求項1乃至3のうちのいずれかに記載の積層電子部品用ビアペースト。

【請求項5】

複数のセラミック層と複数の導体層とが交互に積層された積層部と、

該積層部の積層方向に延びて一部の該導体層と接続されたビア導体部と、を備える積層電子部品の製造方法において、

上記積層部となるビアホールを有した未焼成積層部を得る未焼成積層部形成工程と、

該ビアホール内に請求項1乃至4のうちのいずれかに記載の積層電子部品用ビアペーストを充填する充填工程と、

該未焼成積層部及び該ビアホール内に充填されたビアペーストを一体焼成する焼成工程と、を備えることを特徴とする積層電子部品の製造方法。

【請求項6】

複数のセラミック層と複数の導体層とが交互に積層された積層部と、

該積層部の積層方向に延びて一部の該導体層と接続されたビア導体部と、を備える積層電子部品において、

上記ビア導体部は、導電性金属相と、上記セラミック層を構成するセラミック成分と焼結できる共素地セラミック成分からなる共素地セラミック相と、を有し、

該共素地セラミック相は、該ビア導体部全体の10体積%以上であることを特徴とする積層電子部品。

【請求項7】

複数のセラミック層と複数の導体層とが交互に積層された積層部と、

該積層部の積層方向に延びて一部の該導体層と接続されたビア導体部と、を備える積層電子部品において、

上記ビア導体部は、導電性金属相と、上記セラミック層を構成するセラミック成分と焼結できる共素地セラミック成分からなる共素地セラミック相と、を有し、

上記セラミック層内における該ビア導体部を含む上記積層方向に対して垂直な断面に、該ビア導体部内側方向へ10μm以上入り込み、且つ該セラミック層と焼結された上記共素地セラミック相を5ヶ所以上有することを特徴とする積層電子部品。

【請求項8】

上記積層部の積層方向に延びて一層おきの導体層と接続された第1ビア導体部と、

該積層部の積層方向に延びて該第1ビア導体部と接続されていない導体層と接続された第2ビア導体部と、

該第1ビア導体部の端部と接続されて該積層部の表面に導出された第1外部端子と、

該第2ビア導体部の端部と接続されて該積層部の表面に導出された第2外部端子と、を備える積層セラミックコンデンサである請求項6又は7に記載の積層電子部品。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【公開番号】特開2007−81351(P2007−81351A)

【公開日】平成19年3月29日(2007.3.29)

【国際特許分類】

【出願番号】特願2005−271126(P2005−271126)

【出願日】平成17年9月16日(2005.9.16)

【出願人】(000004547)日本特殊陶業株式会社 (2,912)

【Fターム(参考)】

【公開日】平成19年3月29日(2007.3.29)

【国際特許分類】

【出願日】平成17年9月16日(2005.9.16)

【出願人】(000004547)日本特殊陶業株式会社 (2,912)

【Fターム(参考)】

[ Back to top ]