窒化物半導体ダイオード

【課題】高耐圧、低逆方向リーク電流特性を有する二次元電子ガスを導電層とした性能の高い窒化物半導体ダイオードを提供する。

【解決手段】窒化物半導体積層膜の上面に塩素ガスを用いたドライエッチングにより形成した凹部6の底面および側面部に対して、所望の不純物を拡散させる、または所望の不純物を添加した窒化物半導体を再成長することにより、アノード電極7が接触する窒化物半導体積層膜の側面部を高抵抗化させ、逆方向リーク電流を低減する。

【解決手段】窒化物半導体積層膜の上面に塩素ガスを用いたドライエッチングにより形成した凹部6の底面および側面部に対して、所望の不純物を拡散させる、または所望の不純物を添加した窒化物半導体を再成長することにより、アノード電極7が接触する窒化物半導体積層膜の側面部を高抵抗化させ、逆方向リーク電流を低減する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、窒化物半導体ダイオードに関し、特に、バンドギャップエネルギーの異なる窒化物半導体層を積層したときのヘテロ接合によって生じる2次元電子ガス(2DEG)を導電層とし、前記窒化物半導体層の積層膜の側面に対してショットキー接合するアノード電極を備えた窒化物半導体ダイオードに適用して有効な技術に関する。

【背景技術】

【0002】

近年、SiC(炭化ケイ素)またはGaN(窒化ガリウム)などのワイドギャップ半導体を用いた電子デバイス素子が、パワーエレクトロニクス応用を目的として盛んに開発が進められている。

【0003】

GaN(窒化ガリウム)に代表される窒化物半導体を用いた装置では、例えばノンドープのAlGaN/GaNヘテロ接合を利用した横型デバイスの開発が盛んに行われている。

【0004】

特徴として、大きなバンドオフセットと、ヘテロ接合界面に生じる自然分極と、強いピエゾ分極との影響によって、接合界面近傍のGaN側にはノンドープながら2次元電子ガス(2 Dimensional Electron Gas:以降2DEGと略す)からなる導電層が発生する。

【0005】

この2DEG導電層は、高い電子移動度と高い電子濃度(1013cm−2オーダー)を有するため、AlGaN/GaNヘテロ構造を利用したHEMT(High Electron Mobility Transistor)素子は、高周波回路への搭載をはじめ、近年パワーエレクトロニクス向けにDC−DCコンバータ回路などに搭載され製品化されている。

【0006】

また、上記ヘテロ構造を用いた横型ダイオードに関しても、パワーエレクトロニクス応用を想定した開発が進められており、順方向特性を改善するため、ヘテロ接合を多層化することで、2DEGからなる導電層を縦方向(基板の主面に対して垂直な方向)に複数積層して、上方から見たときの単位面積あたりの電流密度を増大させる試みがなされている。

【0007】

これに関して、特許文献1(特開2009−117485号公報)には、多層化したヘテロ接合を有する横型ダイオードにおいて、アノード電極とカソード電極をヘテロ接合の側面部に形成することで、下層方向に位置する2DEG導電層に対してもアクセス抵抗を低く抑えることが記されている。

【0008】

また、非特許文献1には、3層の2DEG導電層に対して、リセス構造により前記3層の2DEG導電層側面部にアノード電極とカソード電極を形成することで、52mΩcm2のオン抵抗、および9400Vの逆方向ブレークダウン電圧を得ることが記載されている。

【先行技術文献】

【特許文献】

【0009】

【特許文献1】特開2009−117485号公報

【非特許文献】

【0010】

【非特許文献1】T. Ueda et al. Phys.Status Solid B 247,No.7 (2010)

【発明の概要】

【発明が解決しようとする課題】

【0011】

特許文献1および非特許文献1に記載された2DEG導電層側面部への電極形成は、複数の2DEG導電層をドリフト層とした窒化物半導体横型ダイオードにおいて順方向電流密度を増大させる上で有効な手法である。

【0012】

2DEG導電層の側面にアノード(ショットキー)電極を形成する際には、まず基板上にエピタキシャル成長したGaN、AlGaNなどのバンドギャップエネルギーが異なる複数の窒化物半導体からなる積層膜を用意する。続いて、前記積層膜のドリフト層以外の領域を、例えば塩素ガスを用いたドライエッチング法を用いて加工・除去して、2DEG導電層およびヘテロ接合部を含む前記積層膜の側面を露出させるように凹部を形成し、前記凹部に露出したヘテロ接合部を含む前記側面に接するアノード(ショットキー)電極を形成する。その後、前記積層膜を挟んで前記凹部の反対側に形成された他の凹部内の前記積層膜側面にカソード(オーミック)電極を形成することで横型ダイオードが完成する。

【0013】

しかしながら、上記工程により作製した横型ダイオードは、逆方向リーク電流が大きく、所望の耐圧特性が得られず、窒化物半導体ダイオードの性能が低下する課題がある。

【0014】

本発明の目的は、窒化物半導体ダイオードの性能を向上させることにある。

【0015】

本発明の前記の目的と新規な特徴は、本明細書の記述および添付図面から明らかになるであろう。

【課題を解決するための手段】

【0016】

代表的なものとして、基板と、前記基板上に形成された第1窒化物半導体層および前記第1窒化物半導体層よりもバンドギャップエネルギーが大きい第2窒化物半導体層が積層されたヘテロ接合型の積層膜と、前記積層膜の側面にオーミック接続されたカソード電極と、アノード電極とを備え、前記積層膜は、前記第1窒化物半導体層および前記第2窒化物半導体層の界面であるヘテロ接合面の深さに達する凹部を備え、前記凹部において、C(炭素)、Fe(鉄)、Zn(亜鉛)、Mg(マグネシウム)の群から選択された少なくとも1種類以上の不純物が注入された領域を備え、前記アノード電極は、前記領域に接して前記積層膜とショットキー接続していることを特徴とする窒化物半導体ダイオードがある。

【発明の効果】

【0017】

本発明によれば、窒化物半導体ダイオードの性能を向上させることができる。

【図面の簡単な説明】

【0018】

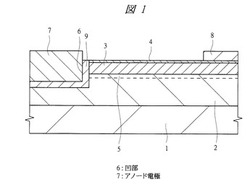

【図1】本発明の実施の形態1である窒化物半導体ダイオードを示す断面図である。

【図2】本発明の実施の形態2である窒化物半導体ダイオードを示す断面図である。

【図3】本発明の実施の形態2である窒化物半導体ダイオードを示す平面図である。

【図4】本発明の実施の形態2である窒化物半導体ダイオードの製造工程を示す断面図である。

【図5】図4に続く製造工程中の窒化物半導体ダイオードの断面図である。

【図6】図5に続く製造工程中の窒化物半導体ダイオードの断面図である。

【図7】図6に続く製造工程中の窒化物半導体ダイオードの断面図である。

【図8】本発明の実施の形態3である窒化物半導体ダイオードを示す断面図である。

【図9】GaN内における深さ方向のZnの濃度分布を示すグラフである。

【図10】窒化物半導体層内にZnまたはMgを拡散する熱処理条件に対する最大p型不純物濃度、p型不純物拡散深さ、最大酸素濃度、逆方向リーク電流、およびブレークダウン電圧を示す表である。

【図11】比較例として示すプレーナ構造の横型ダイオードの断面図である。

【図12】比較例として示すリセス構造の横型ダイオードの断面図である。

【図13】比較例として示すプレーナ構造の横型ダイオードの平面図である。

【図14】リセス構造およびプレーナ構造の横型ダイオードの逆方向特性を示すグラフである。

【図15】比較例として示す縦型ダイオードの断面図である。

【図16】縦型ダイオードの順方向特性を示すグラフである。

【図17】縦型ダイオードの順方向特性を示すグラフである。

【発明を実施するための形態】

【0019】

以下、本発明の実施の形態を図面に基づいて詳細に説明する。なお、実施の形態を説明するための全図において、同一の機能を有する部材には同一の符号を付し、その繰り返しの説明は省略する。また、以下の実施の形態では、特に必要なときを除き、同一または同様な部分の説明を原則として繰り返さない。

【0020】

また、以下の実施の形態で用いる図面においては、平面図であっても図面を見易くする

ために部分的にハッチングを付す場合がある。

【0021】

(実施の形態1)

はじめに、本発明者らが行った実験結果について説明する。本発明者らは、特許文献1および非特許文献1に記載されているような横型ダイオードの逆方向特性に関する知見を得るため、AlGaN/GaNシングルヘテロ構造を有するエピタキシャル基板を使って、図11および図12に示す構造を有する2種類の横型ダイオードを試作し、両者の逆方向特性を比較・評価した。なお、ここでいうリセス構造とは、基板表面に形成した凹部内に設けた電極を含む素子の構造を指すものとする。

【0022】

比較例のダイオードのエピタキシャル構造は、図11および図12の断面図に示すように、サファイアからなる基板1上にGaNからなる膜厚3.0μmの高抵抗バッファ層2と、アンドープのAlGaNからなる膜厚25nmのバリア層3と、アンドープGaNからなる膜厚5nmのキャップ層4とを有するものである。GaNからなる高抵抗バッファ層2上にはバリア層3が形成され、バリア層3上にはキャップ層4が形成されている。

【0023】

高抵抗バッファ層2とバリア層3とはヘテロ接合を有し、それらの界面を含む高抵抗バッファ層2内には2次元電子ガスからなる導電層5が存在している。

【0024】

導電層5はヘテロ接合部の高抵抗バッファ層2の上面近傍を含む高抵抗バッファ層2内において、二次元電子ガスが前記ヘテロ接合界面に沿う方向に広がることにより形成された層である。二次元電子ガスは、バンドギャップが小さい第1窒化物半導体層と、その上の、バンドギャップが第1窒化物半導体層よりも大きい第2窒化物半導体層とからなるヘテロ接合部において、第1窒化物半導体層内の上部の近傍に平面的に広がるように形成された、電子が多く溜まっている状態である。ショットキーバリアダイオードを動作させた際には、導電層5内を電流がアノード電極からカソード電極に向かって流れる。

【0025】

次に、試作した比較例である2種類の横型ダイオードについて図11、および図12を用いて説明する。

【0026】

図11は、前述したエピタキシャル層の表面上のみにショットキー電極であるアノード電極7aと、オーミック電極であるカソード電極8を形成したプレーナ構造の横型ダイオードの断面図であり、前記電極が設けられる領域のエピタキシャル層に対して、塩素ガスを用いたドライエッチングは施されていない。

【0027】

これに対して図12は、塩素ガスを用いたドライエッチングにより前記エピタキシャル層の一部を上面から加工して、2次元電子ガスからなる導電層5の側面を含む窒化物半導体の積層膜側面を露出させるように凹部6を前記積層膜を挟んで形成した後、当該積層膜側面に接触するように、一方の凹部6内にアノード電極7を形成し、もう一方の凹部6内にカソード電極8aを形成した、リセス構造の横型ダイオードである。

【0028】

図11および図12に示す構造において、アノード電極7、7aは300nm厚のPd(パラジウム)からなる電極であり、カソード電極8はTi/Al電極である。つまり、カソード電極8はTi(チタン)膜上にAl(アルミニウム)膜を形成した積層構造を有している。図12においても、図11と同様に導電層5の底部の輪郭を破線により示している。

【0029】

ここで、図11に示すダイオードの平面図を図13に示す。また、図12の平面図も図13と同様の構造となる。図13には、アノード電極7a、カソード電極8およびバリア層3を示しており、バリア層3上に形成されているキャップ層4(図11参照)などは図示していない。アノード電極7aおよびカソード電極8の寸法は、図13の平面図に示す通り、何れも300μm×1.0mmである。つまり、長手方向の長さWacは1.0mmであり、当該方向に直交する方向の長さL1、L2は何れも300μmである。このように長手方向に延在するアノード電極7aおよびカソード電極8が前記長手方向に直交する方向に並ぶようにそれぞれの電極を配置している。平面視において、バリア層3はアノード電極7aおよびカソード電極8の周囲を囲むように形成されている。なお、アノード電極7aおよびカソード電極8間の長さLacは150μmである。

【0030】

図14に、試作した比較例の横型ダイオードの逆方向特性を評価した実験の結果を示す。

【0031】

図14に示すように、特性線1(実線)で示したプレーナ構造のダイオード(図11参照)の場合、逆方向電圧を1kV以上印加した場合でもブレークダウンには至らず、逆方向リーク電流は1kVまで1〜2×10−5A/mmのほぼ一定な値であった。

【0032】

これに対して特性線2(破線)で示したリセス構造のダイオード(図12参照)の場合は、逆方向電圧の増加に伴いリーク電流も増加し、逆方向電圧を100V印加したところでブレークダウンしてしまった。

【0033】

この実験結果によれば、塩素ガスを用いたドライエッチングにより加工し露出させたヘテロ接合側面に対して、アノード電極、およびカソード電極をそれぞれ形成したリセス構造の横型ダイオードは、ドライエッチングを施さないプレーナ構造のダイオードに比べて逆方向特性の著しい劣化が観測された。

【0034】

この現象に関して、本発明者らは塩素ガスを用いたドライエッチングが窒化物半導体に与える影響について調べるため、縦型ショットキーバリアダイオードを用いた実験を行い検討した。

【0035】

当該実験には、図15に示すように、n型GaN基板16上に、Siドーピング濃度が2×1016cm−3であり、膜厚が12μmである低濃度n型GaN層17をエピタキシャル成長した基板を用いた。

【0036】

n型GaN基板裏面には、カソード(オーミック)電極8bとしてTi/Al電極を設け、表面側の低濃度n型GaN層17上には、膜厚が300nmのPd(パラジウム)からなるアノード(ショットキー)電極7a(電極サイズは300μmφ)を設けている。

【0037】

本実験では、アノード電極7a形成前の処理として、低濃度n型GaN層17の上面に対して塩素ガスを用いたドライエッチングを施したダイオード(A)と、前記ドライエッチングを行わずに、エピタキシャル成長後の低濃度n型GaN層17表面にアノード電極7を形成したダイオード(B)の2種類の縦型ダイオードを作製した。なお、前記ドライエッチングによるエッチング量は100nmとする。

【0038】

図16および図17に、図15に示す比較例の縦型ダイオードの順方向特性を評価した結果を示す。図16および図17に示すグラフでは、横軸を順方向電圧とし、縦軸を順方向電流としている。

【0039】

図16に示す結果によれば、微小電流領域での電流の立ち上がりは、ドライエッチングを行っていないダイオード(B)に比べて、ドライエッチングを行ったダイオード(A)の方が約0.5V程度低電圧側にシフトしており、ショットキー障壁高さφbは、ダイオード(B)が約1.2eVであるのに対して、ダイオード(A)は約0.65eVにまで低下していることが観測された。しかし、ショットキー接合の良否を表すn値は、ダイオード(B)が約1.02であるのに対して、ダイオード(A)は1.07とほぼ同等であり、ドライエッチングによるショットキー接合自体の劣化はほとんど観測されなかった。

【0040】

さらに図17に示す結果によれば、電流の立上り電圧は、図16と同様に、ダイオード(B)に比べてダイオード(A)は約0.5V程度低電圧側にシフトしているが、素子抵抗を示す電流の傾きには差異は見られなかった。

【0041】

以上の実験結果から鑑みて、塩素ガスを用いたドライエッチングの窒化物半導体に与える影響としては、図17のグラフに示すように、素子抵抗を示す立上り後の電流の傾きに差異が見られないことから、エッチングによって露出した窒化物半導体面が高抵抗化しているのではないことが推察される。

【0042】

また、図16のグラフに示すように、n値が良好なことから、窒化物半導体表面に対する物理的または化学的な損傷は小さく、比較的清浄な窒化物半導体表面を保持したままであることが分かる。ただし、φbが低下していることから、エッチングに曝された窒化物半導体の最表層にはドナー(キャリア)が生じて低抵抗化しているものと推察される。

【0043】

したがって、リセス構造の横型ダイオードの逆方向特性の劣化は、上記エッチングに曝された窒化物半導体の最表面に生じたドナー(キャリア)の影響によりアノード電極が接触する窒化物半導体面が低抵抗化し、アノード電極および窒化物半導体間のφbが低下したことで、アノード(ショットキー)電極からのリーク電流が増大し、十分な逆方向耐圧が得られないことが原因であると推測される。

【0044】

また、上記の2DEG(二次元電子ガス)を導電層とした横型ダイオードの場合、導電層には特にn型の不純物を添加していないため、逆方向特性は前記プレーナ型に見られたような、逆方向電圧に対してある一定のリーク電流をもって推移する傾向を示すことが正常であると考えられる。

【0045】

これに対して、本発明者らは、GaN、AlGaNなどのバンドギャップの異なる窒化物半導体積層膜のヘテロ接合界面に生じる2DEG(二次元電子ガス)導電層をドリフト層とし、周知のドライエッチング法を用いて前記積層膜を加工・除去することで露出した前記積層膜の側面に対してショットキー接合する電極を備えた横型ダイオードにおいて、被ドライエッチング面のドナー(キャリア)を補償して、上記した逆方向特性を向上させることを見出した。

【0046】

したがって、塩素ガスを用いたドライエッチングによって形成した凹部の側面部、すなわち2DEG導電層を含む窒化物半導体積層膜からなるヘテロ接合の側面にアノード(ショットキー)電極を形成しても、逆方向特性は前記プレーナ型と同等の傾向を示す構造を実現することが好ましい。

【0047】

これに対して、本発明者らは鋭意検討し、GaN、AlGaNなどのバンドギャップの異なる窒化物半導体積層膜のヘテロ接合界面に生じる2DEG導電層をドリフト層とし、周知のドライエッチング法を用いて前記窒化物半導体積層膜の所望の領域を加工・除去することで露出した二次元電子ガスからなる導電層側面を含む窒化物半導体積層膜の側面方向に対してショットキー接合する電極を備えた横型ダイオードにおいて、以下のことを見出した。すなわち、本発明者らは、上記ドライエッチングに曝された窒化物半導体積層膜凹部のアノード電極を形成する領域に対して、少なくともその側面部に(1)半絶縁性、もしくは高抵抗な窒化物半導体層を再成長する、および(2)p型不純物を拡散させる、ことで被ドライエッチング面のドナー(キャリア)を補償して、前記目標とした横型ダイオードの逆方向特性を実現できることを見出した。

【0048】

以下に本発明の実施の形態と効果について、図面を参照しながら説明する。

【0049】

まず、本発明の実施の形態である窒化物半導体ダイオードの構造について説明する。図1は、本実施の形態に係る窒化物半導体ダイオードの断面図である。

【0050】

図1に示す窒化物半導体ダイオードでは、比較例の窒化物半導体ダイオードと比較がしやすいように、図11および図12に示したエピタキシャル構造と同一のものを用いており、各電極の寸法、配置も図13に示す通りであるものとする。図1に示す窒化物半導体ダイオードは、図12に示す構造と同様に凹部6内に形成されたアノード電極7と、図11に示す構造と同様に積層膜上に形成されたカソード電極8とを有している。カソード電極8とアノード電極7とは互いに離間している。なお、凹部6の深さは積層膜の上面から例えば50nm程度であるものとする。

【0051】

図1に示すように、本実施の形態の特徴であるアノード電極7の形成領域に設けられた凹部6は、塩素ガスを用いたドライエッチングにより形成されており、凹部6の底面、および側面には、不純物であるC(炭素)を添加したGaNからなる再成長層(エピタキシャル成長層)9が形成されている。つまり、基板1上には高抵抗バッファ層2、バリア層3、キャップ層4が順次形成されており、高抵抗バッファ層2、バリア層3、キャップ層4からなる積層膜の上面をエッチングすることで形成された凹部6内にはアノード電極7が形成され、アノード電極7と前記積層膜との間には再成長層9が形成されている。図1では、導電層5の底部の輪郭を破線により示している。

【0052】

なお、カソード電極8はアノード電極7のようなエッチングにより形成した凹部側面ではなく、平面上に形成している。これは、二次元電子ガス層である導電層5が一層である場合、特にリセス構造としなくても、導電層に対して十分に低いオーム性接触を得ることが可能なためである。

【0053】

塩素ガスを用いたアノード電極形成領域の凹部形成からアノード電極形成に至るまでの工程では、SiO2膜をマスクとして塩素ガスを用いたドライエッチングによりアノード電極形成領域のみに凹部6を形成した後、そのまま前記SiO2膜をマスクとして、該凹部の底面、および側面にC(炭素)を添加したGaNからなる再成長層9を20nmの厚さで再成長(エピタキシャル成長)させる。この時、GaNからなる再成長層9は前記SiO2膜上に成長されないため、窒化物半導体面が露出した凹部6の内壁および底部のみに選択的に成長形成される。

【0054】

なお、窒化物半導体の結晶成長においてエピタキシャル層にC(炭素)を添加する方法としては、例えば周知のMOVPE(Metal-Organic Vapor Phase Epitaxy;有機金属化学気相エピタキシー)成長法を用い、その際に成長圧力を減圧する方法がある。また、MOVPE成長法を用いる際は、さらに成長圧力を制御することで、添加するC(炭素)の濃度を容易に調整することができる。本実施の形態の窒化物半導体ダイオードにおいて再成長層9を形成する際の再成長圧力は50kPaであり、GaNからなる再成長層9中のC濃度は4×1016cm−3である。

【0055】

その後、C(炭素)を添加したGaNからなる再成長層9が成長された当該凹部6を完全に埋込むようにPd(パラジウム)からなるアノード電極7を形成することで、アノード電極形成工程は完了する。アノード電極7は、例えばリフトオフにより形成することができる。アノード電極7は、例えばNi(ニッケル)膜上にAu(金)膜を形成した積層構造を有するものでもよい。

【0056】

そして、所望の平坦部にカソード電極8を形成して完成した本発明の横型ダイオードの逆方向特性を評価した結果、逆方向電圧を1kVまで印加した場合でもブレークダウンには至らず、前述したプレーナ構造のダイオードと同様にほぼ一定の逆方向リーク電流値を示しながら推移する傾向を示した。この時のリーク電流レベルは6.0×10−6〜7.0×10−6A/mmの範囲であり、前記プレーナ構造のダイオードよりもリーク電流は低減した。

【0057】

これは、不純物としてC(炭素)を添加したGaN層がもつ高抵抗特性と、再成長時に基板に加わる1000℃以上の熱との相乗効果により、ドライエッチング曝露面に生じたドナー(キャリア)が補償されるとともに、C添加GaN層によってヘテロ接合側面が適切な状態で保護されたことと、二次元電子ガスからなる導電層を含む積層膜の側面に対して、アノード電極が直接接触しない構造となったこととが原因として考えられる。ここでは、凹部近傍の積層膜内を高抵抗化することを目的としてC(炭素)などの不純物を添加しているため、当然カソード電極近傍よりもアノード電極近傍の積層膜内の前記不純物濃度は高くなる。

【0058】

このように、ドライエッチングにより加工して露出させた上記ヘテロ接合を含む積層膜の側面に対してショットキー接続するアノード電極を設けた窒化物半導体ダイオードにおいて、本実施の形態の窒化物半導体ダイオードは、C(炭素)などの不純物を導入しない場合のショットキーバリアダイオードに比べて逆方向リーク電流が小さく、かつ高い耐圧特性を有する窒化物半導体ダイオードを実現することができる。これにより、窒化物半導体ダイオードの性能を向上させることができる。

【0059】

なお、再成長層9の添加不純物を、C(炭素)に代えてFe(鉄)を添加したGaN層である再成長層9を形成して、上記と同様の横型ダイオードを作製した窒化物半導体ダイオードの実施形態について説明する。このときの再成長層9のFe濃度は5×1017cm−3、膜厚は100nmである。再成長したGaN層(再成長層)に添加する不純物、濃度および膜厚以外は、上記した図1に示す構造と同じ構造であるものとする。

【0060】

上記のようにFe(鉄)を導入した再成長層9を設けることで完成した横型ダイオードについて逆方向特性を評価した結果、Fe(鉄)を導入した構造においても、前記プレーナ型と同様に逆方向電圧を1kVまで印加した場合でもブレークダウンには至らず、リーク電流は8.0〜9.0×10−7A/mmと低く良好であった。

【0061】

また、上記した再成長層9の添加不純物を、C(炭素)またはFe(鉄)ではなくMg(マグネシウム)とした場合の窒化物半導体ダイオードの実施形態について説明する。このときの再成長層9のMg濃度は1×1017cm−3、膜厚は50nmである。なお、この場合の窒化物半導体ダイオードの構造も、再成長したGaN層(再成長層)に添加する不純物、濃度および膜厚以外は、図1を用いて説明した構造と同じである。

【0062】

完成した本発明の横型ダイオードについて逆方向特性を評した結果、再成長層9にMg(マグネシウム)を添加した当該構造において、逆方向電圧を1kVまで印加した場合にブレークダウンには至らなかったが、リーク電流は不安定な値を示した。

【0063】

詳細には、1回目の逆方向電圧印加では、リーク電流は3.0×10−5〜9.0×10−6A/mmの範囲で変動していたが、2回目以降は8.0〜9.0×10−6A/mmの範囲に安定した。

【0064】

これは、Mg(マグネシウム)を添加したGaN層(再成長層)中に含まれる高濃度の水素に関係しているものと考えられ、1回目の逆方向電圧印加によって生じた熱の影響により、Mg添加GaN層に含まれていた水素が半導体中を移動・脱離する現象を起こしたためにリーク電流が不安定となり、2回目以降はすでに水素脱離が完了しているため、リーク電流値が安定していたものと推測される。

【0065】

これに関して、本発明者らはMg添加GaN層再成長後に、窒素雰囲気中にて700℃、30分の熱処理を行い、続いてアノード電極を形成し、その後ダイオードを作製・評価したところ、逆方向リーク電流の変動は観測されなかったことを確認した。

【0066】

以上、再成長層に添加したC、FeおよびMgの前記3元素は、窒化物半導体結晶成長技術の分野において、すでに周知のものであるため、製法上適用しやすい材料である。本実施の形態の窒化物半導体ダイオードでは、ドライエッチングによって形成した窒化物半導体の凹部に露出したヘテロ接合体の側面に対して、前記C、FeおよびMgの3元素の中から選択された不純物を添加した窒化物半導体層を再成長することで、アノード電極からのリーク電流を低減し、ダイオードの逆方向耐圧を前記プレーナ構造並みに向上させることを可能としている。

【0067】

本発明者らの検討によれば、添加する不純物の濃度としては、CまたはFeを注入する場合は4×1016cm−3以上とし、また、不純物としてMgを添加する場合は、1×1017cm−3以上とすることが好ましい。これらの値未満の濃度で各不純物を導入して再成長層を形成すると、十分に真性度の高い再成長層、または低濃度かつ高抵抗なp型の導電型を有する再成長層が得られず、ショットキー接合すべき積層膜の側壁がn型化してしまい、ショットキーバリアダイオードの逆方向耐圧が低下する問題、または逆方向リーク電流が増大する問題などが発生する。

【0068】

また、上記不純物を添加した窒化物半導体層(再成長層)は非常に高抵抗であるため、必要以上に膜厚が厚いと、順方向における抵抗成分となり素子抵抗が増大する。本発明者らの検討によれば、再成長層の膜厚は150nm以下であることが望ましく、より好ましくは100nm以下であることが望ましい。

【0069】

言い換えれば、前記再成長層が1nmの薄い膜厚で存在するだけでも、再成長層が無い場合に比べてダイオードの逆方向特性を著しく改善することができる。

【0070】

本実施の形態では、再成長層としてGaNを用いたが、特にGaNである必要は無く、GaNの他、AlGaN、InAlN、InAlGaNまたはInGaNなどを用いてもよい。ただし、GaNよりもバンドギャップエネルギーの大きい窒化物半導体材料を用いた場合、再成長層と前記凹部に露出した窒化物半導体面の側面部との間で、2DEGが生じる可能性があるため、再成長層材料としては、GaNに比べてバンドギャップエネルギーがあまり大きくならない材料であることが望ましい。

【0071】

また、GaN以外の材料を選択した場合は、選択的にエピ成長することができないため、再成長後に不要な再成長層を除去する工程が増える。

【0072】

(実施の形態2)

次に、本発明の実施の形態2である窒化物半導体ダイオードの実施形態について説明する。図2および図3は、それぞれ本実施の形態に係る窒化物半導体ダイオードの断面図および平面図である。

【0073】

本実施の形態に係る窒化物半導体ダイオードの構造は、前記実施の形態1に述べた窒化物半導体ダイオードと同様に、アノード電極形成領域に塩素ガスを用いたドライエッチングを行い凹部を形成した横型ダイオードであり、AlGaN層とその下層のGaN層の積層膜からなるヘテロ接合数を3つとしたことで、二次元電子ガスからなる導電層が3層設けられているものである。

【0074】

これにより、図1に示す構造のように導電層が単層の場合に比べて、順方向特性における電流密度が増大するとともに、導電層のシート抵抗も低減するため、オン抵抗およびオン電圧の低減が可能となる。

【0075】

図2に示すように、本実施の形態の窒化物半導体ダイオードを構成するエピタキシャル層は、サファイアからなる基板1上に形成された高抵抗バッファ層2、バリア層3、中間GaN層11およびキャップ層4を有している。高抵抗バッファ層2は膜厚3.0μmのGaNからなりC(炭素)が2.0〜4.0×1016cm−3の濃度範囲でドープ(導入)されている。バリア層3は膜厚20nmのAlGaNからなりC(炭素)が2.0〜4.0×1016cm−3の濃度範囲でドープされている。中間GaN層11は膜厚100nmのGaNからなりC(炭素)が2.0〜4.0×1016cm−3の濃度範囲でドープされている。キャップ層4は膜厚5nmのGaNからなりC(炭素)が2.0〜4.0×1016cm−3の濃度範囲でドープされている。

【0076】

高抵抗バッファ層2、バリア層3、中間GaN層11およびキャップ層4はエピタキシャル層であり、高抵抗バッファ層2上にはバリア層3が形成され、当該バリア層3上には中間GaN層11およびバリア層3が交互に積層されている。つまり、高抵抗バッファ層2、バリア層3および中間GaN層11を含む積層膜は、GaN層(高抵抗バッファ層2または中間GaN層11)とその上にヘテロ接合されたAlGaN層(バリア層3)とからなるヘテロ接合部を複数層重ねた構造を有している。

【0077】

また、当該ヘテロ接合界面の下部におけるGaN層(高抵抗バッファ層2または中間GaN層11)内の上面近傍には、ヘテロ接合界面、すなわちGaN層とその上部のAlGaN層との界面に沿う二次元電子ガスからなる導電層5a、5bおよび5cが形成されている。ここでは、積層された三つのヘテロ接合部のうち、最も上に形成された中間GaN層11の上面に前述した二次元電子ガスからなる導電層5aが形成され、その下のヘテロ接合部の中間GaN層11の上面には導電層5bが形成され、その下のヘテロ接合部の高抵抗バッファ層2の上面には導電層5cが形成されているものとする。

【0078】

つまり、前記積層膜は、上面に導電層5cを有する高抵抗バッファ層2、バリア層3、上面に導電層5bを有する中間GaN層11、バリア層3、上面に導電層5aを有する中間GaN層11、バリア層3およびキャップ層4が基板側から順次形成されている構造を有している。図2では、導電層5a〜5cはそれぞれ破線を用いてその底部の輪郭を示している。つまり、導電層5a〜5cは、高抵抗バッファ層2内または中間GaN11内の上面からその下部の破線までの間の領域に形成されている。

【0079】

本実施の形態の横型ダイオードのエピタキシャル層には予めC(炭素)が添加されているため、各半導体層の真性度が向上し、アンドープの場合よりも寄生的なリーク電流が低減する効果がある。

【0080】

アノード電極7が形成されている領域には、塩素ガスを用いたドライエッチングにより形成された、エッチング深さが250nmの凹部6が設けられており、凹部6の底面および内壁には、膜厚が50nmであり、C(炭素)が8×1017cm−3の濃度で添加されたGaNからなる再成長層9が設けられている。

【0081】

凹部6内において、再成長層9上にはNi/Auからなるアノード(ショットキー)電極7が設けられている。

【0082】

カソード電極8が形成されている領域の高抵抗バッファ層2、バリア層3、中間GaN層11およびキャップ層4からなる積層膜中には、Si(シリコン)がイオン注入されたn型層12が設けられており、カソード(オーミック)電極8は、前記n型層12の直上に設けられている。このn型層12を設けることによって、カソード電極8と導電層5a〜5cとの接合抵抗は十分に低く抑えることができる。つまり、カソード電極8はn型層12を介して導電層5a〜5cを含む前記積層膜の側面に電気的に接続されている。図2では、n型層12の輪郭を点線で示しており、当該点線で囲まれた領域であってカソード電極8の直下の領域の積層膜上面にn型層12が形成されている。また、図3ではn型層12の輪郭を破線で示している。

【0083】

ここで、図3に本実施の形態の窒化物半導体ダイオードの平面図を示す。図3に示すように、アノード(ショットキー)電極7とカソード(オーミック)電極8はそれぞれ櫛型形状を有して対向しており、アノード電極7およびカソード電極8の離間長(ドリフト層長さ)は100μmである。

【0084】

アノード電極7およびカソード電極8のそれぞれの電極櫛部の長手方向の長さは1本あたり500μmであり、前記長手方向に直交する方向の電極の幅は100μmである。

【0085】

アノード電極7の櫛数は5本であり、アノード電極7の左右電極端部に対向する形でカソード電極8が設けられていることから、全体的な電極間の対向長さは0.5mm×2面×5本=5mmである。

【0086】

前記実施の形態1の窒化物半導体ダイオードである横型ダイオードの逆方向耐圧特性は、本実施の形態の作用、および効果を反映して、逆方向電圧を3kV印加した場合でもブレークダウンせず、逆方向リーク電流も3層の導電層5a〜5cを有しながら、1.0×10−7A/mm以下と低く良好であった。

【0087】

これは、前述の通りエピタキシャル層に予めC(炭素)を添加して各層の真性度を向上させたことによる効果であると考えられる。また、順方向特性においても3層の導電層の効果により、オン抵抗は80mΩcm2以下と良好であった。

【0088】

ここでは、再成長層に添加する不純物としてC(炭素)を選択したが、前記実施の形態1で述べたとおり、Fe(鉄)またはMg(マグネシウム)を用いた場合でも同様の効果が得られることは言うまでもない。

【0089】

また、ここではエピタキシャル層に予めC(炭素)を添加した例について述べたが、これは予めエピタキシャル層の真性度の向上させる、または高抵抗化させて、エピタキシャル層が持つ寄生リーク成分を排除することが目的であるため、C(炭素)の他、Fe(鉄)を添加しても同様の効果が得られることは言うまでもない。

【0090】

また、ここでは導電層の数、すなわちヘテロ接合部を3層としたが、これはAlGaN/GaNの積層数を変えることで、より多くの導電層を設けることは可能である。

【0091】

しかし、バンドギャップエネルギーが大きいバリア層(例えばAlGaN)に用いる半導体材料と、二次元電子ガス層からなる導電層が形成される側のバンドギャップエネルギーが小さい半導体材料(例えばGaN)との格子不整合差の大小によって、積層できるバリア層の膜厚には限界があるため、より多くの導電層を設けるためには、前記格子不整合差を考慮して各々の半導体材料の組成などを調整する必要がある。

【0092】

また、ここでは、カソード電極のオーミック接続確保のために、Siイオン注入によりn型層を形成した例について述べたが、凹部を形成してから、当該凹部側面にカソード電極を形成してもよいことは言うまでもなく、さらに両者を組み合せて、カソード電極形成領域に凹部を形成した後、当該凹部の底面および内壁に対してSiイオン注入して凹部全面にn型層を形成してからカソード電極を形成しても何ら問題はない。これは、カソード電極に必要とされる特性が、導電層との低オーム性接触であるためである。

【0093】

次に、本実施の形態の窒化物半導体ダイオードの主要部の作製工程について、図4〜図7を参照しながら以下に説明する。図4〜図7では、いずれもn型不純物拡散領域および導電層5a〜5cの輪郭をそれぞれ点線および破線で示している。

【0094】

まず、図4に示すように、サファイアからなる基板1上に高抵抗バッファ層2、バリア層3、中間GaN層11、バリア層3、中間GaN層11、バリア層3およびキャップ層4を順次エピタキシャル成長させる。続いて、キャップ層4上の全面に膜厚が30nmのSiN(図示せず)からなるスルー膜を被着した後、カソード電極形成領域を開口したフォトレジストパターンを形成する。開口された領域のエピタキシャル層中にn型の不純物であるSiイオンの注入を行い、前記フォトレジストパターンと前記スルー膜を除去した後、再度エピタキシャル層全面に膜厚が50nmのSiNからなるキャップ膜20を被着する。続いて、窒素雰囲気中にて、1100℃、30分間の活性化アニールを行って、n型層12を形成する。

【0095】

次に、図5に示すように、キャップ膜20を除去した後、エピタキシャル層全面に膜厚300nmのSiO2膜10を被着した後、n型層12を形成した領域およびドリフト層以外の全領域を開口したフォトレジストパターンをSiO2膜10上に形成する。前記フォトレジストパターンが開口された領域の直下のSiO2膜10を、フッ酸系溶液を用いたウェットエッチングにより除去して、不要なSiO2膜10を除去する。続いて、塩素ガスを用いたドライエッチングにより、高抵抗バッファ層2、バリア層3、バリア層3およびキャップ層4により構成された積層膜の表面から250nmの深さまでエッチングして凹部6を形成する。これにより、ドリフト層、およびカソード電極形成領域は、凹部6の底面に比べて上面高さが高い凸部15となる。

【0096】

次に、図6に示すように、MOVPE法により、C(炭素)を8×1017cm−3の濃度で添加したGaNからなる再成長層9を形成する。再成長層9の膜厚は50nmであり、再成長層9は、SiO2膜10上には成長されずに凹部6の底部および内壁のみに選択的に成長形成される。

【0097】

次に、図7に示すように、SiO2膜10を除去した後、再成長層9を形成した凹部6内にNi/Auからなるアノード電極7を形成して凹部6を完全に埋込み、n型層12が設けられた領域上にTi/Alからなるカソード電極8を形成する。カソード電極8は、例えば基板1上の全面にTi/Alからなる金属膜を形成した後に、フォトリソグラフィ技術およびドライエッチング法を用いて前記金属膜をパターニングすることで、n型層12の直上に形成することができる。以上の工程により、本実施の形態の窒化物半導体ダイオードが完成する。

【0098】

本実施の形態では、ヘテロ接合を有する窒化物半導体積層膜をドライエッチングにより加工・除去することで設けた凹部の、少なくとも側面に対してショットキー接合するアノード電極を形成する場合、アノード電極の形成前に、該凹部に露出した窒化物半導体面に対して不純物を添加した高抵抗な、または導電性が著しく低い半導体層を再成長することで、アノード電極からのリーク電流の増大を抑制し、耐圧を向上させることができる。

【0099】

(実施の形態3)

次に、本発明の実施の形態3である窒化物半導体ダイオードの実施形態について説明する。図8は、本実施の形態に係る窒化物半導体ダイオードの断面図である。

【0100】

ここでは、前記実施の形態1、2で述べたように再成長層を設けるのではなく、ドライエッチングに曝され低抵抗化したアノード電極形成領域の凹部の窒化物半導体の表面に、p型不純物を拡散させて窒化物半導体ダイオードを作製することで、当該窒化物半導体ダイオードの逆方向特性を向上させる構造について説明する。凹部の内壁および底部からエピタキシャル層からなる積層膜内に拡散させるp型不純物としては、プロセスの容易性から考えて、Zn(亜鉛)またはMg(マグネシウム)が好ましい。

【0101】

Zn、およびMgを導入する際は、ZnOまたはMgOなどの酸化膜を、拡散対象である窒化物半導体上の所望の領域上に直接被着形成した後、少なくとも600℃以上の熱処理を行うことで、容易に窒化物半導体中へZn、およびMgを積層膜内に拡散させることができる。

【0102】

本実施の形態の窒化物半導体ダイオードでは、比較例の窒化物半導体ダイオードとの比較がしやすいように、前記実施の形態1、2で述べたものと同じエピタキシャル構造の基板を用いている。半導体素子の構造としては、図8に示すように、本発明の特徴であるアノード電極7の形成領域に設けられた凹部6の底面、および側面に、p型不純物としてZnを拡散させたp型不純物拡散領域13を設けている。つまり、本実施の形態の窒化物半導体ダイオードの構造は図1の構造に似ているが、再成長層9が形成されておらず、凹部6の内壁および底面から凹部6近傍の積層膜内にかけてp型不純物拡散領域13が形成されている点で、本実施の形態は前記実施の形態1、2と異なる。

【0103】

図8に示すように、導電層5の底部の輪郭を破線で示しており、p型不純物拡散領域13の輪郭が積層膜内に点線で示されている。つまり、p型不純物拡散領域13は、凹部6の表面から前記破線にかけて形成されている。

【0104】

p型不純物拡散領域13を形成する工程では、積層膜上に形成したSiO2膜パターンをマスクとして、塩素ガスを用いたドライエッチングによりアノード電極形成領域に凹部6を形成した後、前記SiO2膜パターンを除去せずに基板上の全面にスパッタ法を用いてZnO膜を被着形成する。この時のZnO膜の厚さは100nmとする。その後、窒素雰囲気中において800℃、1時間の熱処理を行うことで当該凹部6の底面、および側面にZnが拡散し、p型不純物拡散領域13が形成される。

【0105】

次に、酸系およびアルカリ系エッチング液を用いて、不要なZnO膜およびSiO2膜パターンを除去した後、凹部6内にアノード電極7を形成し、続いて前記積層膜を挟んでアノード電極7と対向する所定の領域にカソード電極8を形成することで、本実施の形態の横型の窒化物半導体ダイオードが完成する。

【0106】

なお、アノード電極7、カソード電極8の寸法、配置、電極間距離については、図13を用いて説明したものと同じとする。本実施の形態においても、図8に示すようにカソード電極8は実施の形態1、2と同様に凹部の内壁ではなく積層膜上面の平面上に形成している。

【0107】

また、本発明者らは、Znの拡散による窒化物半導体中のZn濃度プロファイルを調べるため、別途サファイア基板上に膜厚が4μmであるアンドープGaN層をエピタキシャル成長した基板を用意し、アンドープGaN層上にスパッタ法を用いて上記と同じ条件でZnO膜を被着形成し、窒素雰囲気中において上記と同じ800℃、1時間の熱処理を行った。

【0108】

その後不要なZnO膜を除去し、続いてGaN中における深さ方向のZn濃度プロファイルをSIMS分析により調べた結果を図9に示す。図9に示す濃度分布のグラフでは、横軸を半導体表面からの深さ、縦軸をZn(亜鉛)の濃度としている。

【0109】

図9に示す濃度分布から、最もZn濃度が高いのはアンドープGaN層最表面近傍であり、その濃度は約1.0×1019cm−3程度であることが分かる。また、Zn拡散深さは約400nmにまで及んでおり、表面からの拡散のため、深さ方向に対してZn濃度は指数関数的に減少する傾向を示している。

【0110】

この拡散による不純物濃度プロファイルは、不純物拡散自体の原理から考えて、上記の平面上に限らず、ドライエッチングによって露出した窒化物半導体側面方向においても同様の傾向を示すと推定されることから、アノード電極7が形成された凹部6の側面方向のZn濃度も、上記濃度プロファイルが反映されていると推定される。

【0111】

上述した本発明の横型ダイオードの逆方向特性について評価した結果、前記プレーナ構造と同様に逆方向電圧を1kVまで印加した場合でもブレークダウンには至らなかった。これは、エッチングの影響により生じた半導体表面のキャリアをZnなどのp型不純物が補償することで、キャリアが消失したためであると考えられる。

【0112】

なお、このとき注入する不純物は、n型の導電型を有する不純物であってはならない。

【0113】

また、p型の不純物を過剰に注入すると、積層膜内においてアノード電極側とカソード電極側とでpn接合によるダイオードが形成されるため、注入する不純物は十分に低い濃度のp型不純物であることが望ましい。

【0114】

そこで、ZnO膜、およびMgO膜を用いた不純物拡散の効果と、拡散条件を探索するため、各不純物拡散条件に対する上記横型ダイオードにおける逆方向特性について調べた結果を図10にまとめて示す。

【0115】

なお、このときのZnO膜、およびMgO膜の膜厚は何れも100nmであり、熱処理時間は、1時間である。熱処理条件のパラメータは、温度が600℃、700℃または800℃である。また、熱処理雰囲気は常圧窒素雰囲気または減圧(100Pa)であり、ダイオードの逆方向特性としては、ブレークダウン電圧(最大1kV)と、逆方向リーク電流について図10に記している。

【0116】

図10より、何れの条件においても、ブレークダウン電圧は1kV以上となり高耐圧特性を示したが、熱処理雰囲気の違いによって、逆方向リーク電流に差異が現れた。

【0117】

常圧窒素雰囲気と減圧下(100Pa)とを比較すると、減圧下の方がリーク電流は低い傾向にある。また、熱処理温度についても低い方が、リーク電流は小さい傾向にある。

【0118】

そこで、最もリーク電流が小さかった減圧下、600熱処理条件を用いて、ZnO膜、およびMgO膜について、上記と同様に窒化物半導体中における不純物プロファイルを調べた結果、Zn(亜鉛)の最大不純物濃度は6.2×1017cm−3、Mg(マグネシウム)の最大不純物濃度は4.7×1017cm−3であった。

【0119】

以上のことから、本発明者らは、ドライエッチングによって設けたアノード電極形成領域の凹部にp型不純物を拡散させることで、前記プレーナ構造と同等の逆方向リーク電流の傾向を示し、ブレークダウン電圧を増大できることを見出した。このときのp型不純物濃度は、上記の内容から考えて少なくとも5×1017cm−3以上の濃度であることが望ましい。

【0120】

なお、窒化物半導体中に上記の熱処理温度範囲でp型不純物を拡散させただけでは、窒化物半導体がp型の導電型を示すことはなく、単純に拡散した領域は高抵抗化する。これは、本実施の形態で作製したダイオードの順方向特性を評価した限りでは、順方向の立上り電圧は1V前後の値であり、GaNのバンドギャップエネルギー(約3.3V程度)にはならなかったことからも言える。

【0121】

したがって、上記p型不純物を拡散させた領域と、アノード電極との間の接合はpn接合ではなくショットキー接合であり、p型不純物拡散を適用して作製した横型ダイオードは、何れもショットキーバリアダイオードである。

【0122】

本実施の形態では、導電層が単層である横型ダイオードに適用した場合について述べたが、前記実施の形態2で述べたように複数の導電層を持つ横型ダイオードに適用しても本発明の効果が得られることは言うまでもない。

【0123】

本実施の形態では、ヘテロ接合を有する窒化物半導体積層膜を、塩素ガスを用いたドライエッチングにより加工・除去して設けた凹部の少なくとも側面に対してショットキー接合するアノード電極を形成する場合、アノード電極を形成する前に、該凹部に露出した窒化物半導体面に対してp型不純物を拡散させることで、アノード電極からのリーク電流の増大を抑制し、耐圧を向上させることができる。

【0124】

以上、本発明者らによってなされた発明を実施の形態に基づき具体的に説明したが、本発明は前記実施の形態に限定されるものではなく、その要旨を逸脱しない範囲で種々変更可能であることはいうまでもない。

【0125】

例えば、前記実施の形態1〜3ではサファイア基板を用いた例について述べたが、この他に、SiC基板、Si基板、GaN基板を用いてもよい。

【0126】

また、前記実施の形態1、3では、基板上にエピタキシャル成長した第1の窒化物半導体層および第2の窒化物半導体層がアンドープである場合について述べたが、前記実施の形態2と同様に最初からエピタキシャル層にC(炭素)またはFe(鉄)などを適度にドーピングしてもよい。これにより。前記第1の窒化物半導体層および第2の窒化物半導体層の真性度がアンドープの場合よりも増すため、エピタキシャル層自体が有する寄生的な逆方向リーク電流レベルをさらに低減することができる。

【産業上の利用可能性】

【0127】

本発明は、横型のショットキーバリアダイオードの製造技術に適用して有効である。

【符号の説明】

【0128】

1 基板

2 高抵抗バッファ層

3 バリア層

4 キャップ層

5、5a〜5c 導電層

6 凹部

7、7a アノード(ショットキー)電極

8、8a、8b カソード(オーミック)電極

9 再成長層

10 SiO2膜

11 中間GaN層

12 n型層

13 p型不純物拡散領域

15 凸部

16 n型GaN基板

17 低濃度n型GaN層

20 キャップ膜

【技術分野】

【0001】

本発明は、窒化物半導体ダイオードに関し、特に、バンドギャップエネルギーの異なる窒化物半導体層を積層したときのヘテロ接合によって生じる2次元電子ガス(2DEG)を導電層とし、前記窒化物半導体層の積層膜の側面に対してショットキー接合するアノード電極を備えた窒化物半導体ダイオードに適用して有効な技術に関する。

【背景技術】

【0002】

近年、SiC(炭化ケイ素)またはGaN(窒化ガリウム)などのワイドギャップ半導体を用いた電子デバイス素子が、パワーエレクトロニクス応用を目的として盛んに開発が進められている。

【0003】

GaN(窒化ガリウム)に代表される窒化物半導体を用いた装置では、例えばノンドープのAlGaN/GaNヘテロ接合を利用した横型デバイスの開発が盛んに行われている。

【0004】

特徴として、大きなバンドオフセットと、ヘテロ接合界面に生じる自然分極と、強いピエゾ分極との影響によって、接合界面近傍のGaN側にはノンドープながら2次元電子ガス(2 Dimensional Electron Gas:以降2DEGと略す)からなる導電層が発生する。

【0005】

この2DEG導電層は、高い電子移動度と高い電子濃度(1013cm−2オーダー)を有するため、AlGaN/GaNヘテロ構造を利用したHEMT(High Electron Mobility Transistor)素子は、高周波回路への搭載をはじめ、近年パワーエレクトロニクス向けにDC−DCコンバータ回路などに搭載され製品化されている。

【0006】

また、上記ヘテロ構造を用いた横型ダイオードに関しても、パワーエレクトロニクス応用を想定した開発が進められており、順方向特性を改善するため、ヘテロ接合を多層化することで、2DEGからなる導電層を縦方向(基板の主面に対して垂直な方向)に複数積層して、上方から見たときの単位面積あたりの電流密度を増大させる試みがなされている。

【0007】

これに関して、特許文献1(特開2009−117485号公報)には、多層化したヘテロ接合を有する横型ダイオードにおいて、アノード電極とカソード電極をヘテロ接合の側面部に形成することで、下層方向に位置する2DEG導電層に対してもアクセス抵抗を低く抑えることが記されている。

【0008】

また、非特許文献1には、3層の2DEG導電層に対して、リセス構造により前記3層の2DEG導電層側面部にアノード電極とカソード電極を形成することで、52mΩcm2のオン抵抗、および9400Vの逆方向ブレークダウン電圧を得ることが記載されている。

【先行技術文献】

【特許文献】

【0009】

【特許文献1】特開2009−117485号公報

【非特許文献】

【0010】

【非特許文献1】T. Ueda et al. Phys.Status Solid B 247,No.7 (2010)

【発明の概要】

【発明が解決しようとする課題】

【0011】

特許文献1および非特許文献1に記載された2DEG導電層側面部への電極形成は、複数の2DEG導電層をドリフト層とした窒化物半導体横型ダイオードにおいて順方向電流密度を増大させる上で有効な手法である。

【0012】

2DEG導電層の側面にアノード(ショットキー)電極を形成する際には、まず基板上にエピタキシャル成長したGaN、AlGaNなどのバンドギャップエネルギーが異なる複数の窒化物半導体からなる積層膜を用意する。続いて、前記積層膜のドリフト層以外の領域を、例えば塩素ガスを用いたドライエッチング法を用いて加工・除去して、2DEG導電層およびヘテロ接合部を含む前記積層膜の側面を露出させるように凹部を形成し、前記凹部に露出したヘテロ接合部を含む前記側面に接するアノード(ショットキー)電極を形成する。その後、前記積層膜を挟んで前記凹部の反対側に形成された他の凹部内の前記積層膜側面にカソード(オーミック)電極を形成することで横型ダイオードが完成する。

【0013】

しかしながら、上記工程により作製した横型ダイオードは、逆方向リーク電流が大きく、所望の耐圧特性が得られず、窒化物半導体ダイオードの性能が低下する課題がある。

【0014】

本発明の目的は、窒化物半導体ダイオードの性能を向上させることにある。

【0015】

本発明の前記の目的と新規な特徴は、本明細書の記述および添付図面から明らかになるであろう。

【課題を解決するための手段】

【0016】

代表的なものとして、基板と、前記基板上に形成された第1窒化物半導体層および前記第1窒化物半導体層よりもバンドギャップエネルギーが大きい第2窒化物半導体層が積層されたヘテロ接合型の積層膜と、前記積層膜の側面にオーミック接続されたカソード電極と、アノード電極とを備え、前記積層膜は、前記第1窒化物半導体層および前記第2窒化物半導体層の界面であるヘテロ接合面の深さに達する凹部を備え、前記凹部において、C(炭素)、Fe(鉄)、Zn(亜鉛)、Mg(マグネシウム)の群から選択された少なくとも1種類以上の不純物が注入された領域を備え、前記アノード電極は、前記領域に接して前記積層膜とショットキー接続していることを特徴とする窒化物半導体ダイオードがある。

【発明の効果】

【0017】

本発明によれば、窒化物半導体ダイオードの性能を向上させることができる。

【図面の簡単な説明】

【0018】

【図1】本発明の実施の形態1である窒化物半導体ダイオードを示す断面図である。

【図2】本発明の実施の形態2である窒化物半導体ダイオードを示す断面図である。

【図3】本発明の実施の形態2である窒化物半導体ダイオードを示す平面図である。

【図4】本発明の実施の形態2である窒化物半導体ダイオードの製造工程を示す断面図である。

【図5】図4に続く製造工程中の窒化物半導体ダイオードの断面図である。

【図6】図5に続く製造工程中の窒化物半導体ダイオードの断面図である。

【図7】図6に続く製造工程中の窒化物半導体ダイオードの断面図である。

【図8】本発明の実施の形態3である窒化物半導体ダイオードを示す断面図である。

【図9】GaN内における深さ方向のZnの濃度分布を示すグラフである。

【図10】窒化物半導体層内にZnまたはMgを拡散する熱処理条件に対する最大p型不純物濃度、p型不純物拡散深さ、最大酸素濃度、逆方向リーク電流、およびブレークダウン電圧を示す表である。

【図11】比較例として示すプレーナ構造の横型ダイオードの断面図である。

【図12】比較例として示すリセス構造の横型ダイオードの断面図である。

【図13】比較例として示すプレーナ構造の横型ダイオードの平面図である。

【図14】リセス構造およびプレーナ構造の横型ダイオードの逆方向特性を示すグラフである。

【図15】比較例として示す縦型ダイオードの断面図である。

【図16】縦型ダイオードの順方向特性を示すグラフである。

【図17】縦型ダイオードの順方向特性を示すグラフである。

【発明を実施するための形態】

【0019】

以下、本発明の実施の形態を図面に基づいて詳細に説明する。なお、実施の形態を説明するための全図において、同一の機能を有する部材には同一の符号を付し、その繰り返しの説明は省略する。また、以下の実施の形態では、特に必要なときを除き、同一または同様な部分の説明を原則として繰り返さない。

【0020】

また、以下の実施の形態で用いる図面においては、平面図であっても図面を見易くする

ために部分的にハッチングを付す場合がある。

【0021】

(実施の形態1)

はじめに、本発明者らが行った実験結果について説明する。本発明者らは、特許文献1および非特許文献1に記載されているような横型ダイオードの逆方向特性に関する知見を得るため、AlGaN/GaNシングルヘテロ構造を有するエピタキシャル基板を使って、図11および図12に示す構造を有する2種類の横型ダイオードを試作し、両者の逆方向特性を比較・評価した。なお、ここでいうリセス構造とは、基板表面に形成した凹部内に設けた電極を含む素子の構造を指すものとする。

【0022】

比較例のダイオードのエピタキシャル構造は、図11および図12の断面図に示すように、サファイアからなる基板1上にGaNからなる膜厚3.0μmの高抵抗バッファ層2と、アンドープのAlGaNからなる膜厚25nmのバリア層3と、アンドープGaNからなる膜厚5nmのキャップ層4とを有するものである。GaNからなる高抵抗バッファ層2上にはバリア層3が形成され、バリア層3上にはキャップ層4が形成されている。

【0023】

高抵抗バッファ層2とバリア層3とはヘテロ接合を有し、それらの界面を含む高抵抗バッファ層2内には2次元電子ガスからなる導電層5が存在している。

【0024】

導電層5はヘテロ接合部の高抵抗バッファ層2の上面近傍を含む高抵抗バッファ層2内において、二次元電子ガスが前記ヘテロ接合界面に沿う方向に広がることにより形成された層である。二次元電子ガスは、バンドギャップが小さい第1窒化物半導体層と、その上の、バンドギャップが第1窒化物半導体層よりも大きい第2窒化物半導体層とからなるヘテロ接合部において、第1窒化物半導体層内の上部の近傍に平面的に広がるように形成された、電子が多く溜まっている状態である。ショットキーバリアダイオードを動作させた際には、導電層5内を電流がアノード電極からカソード電極に向かって流れる。

【0025】

次に、試作した比較例である2種類の横型ダイオードについて図11、および図12を用いて説明する。

【0026】

図11は、前述したエピタキシャル層の表面上のみにショットキー電極であるアノード電極7aと、オーミック電極であるカソード電極8を形成したプレーナ構造の横型ダイオードの断面図であり、前記電極が設けられる領域のエピタキシャル層に対して、塩素ガスを用いたドライエッチングは施されていない。

【0027】

これに対して図12は、塩素ガスを用いたドライエッチングにより前記エピタキシャル層の一部を上面から加工して、2次元電子ガスからなる導電層5の側面を含む窒化物半導体の積層膜側面を露出させるように凹部6を前記積層膜を挟んで形成した後、当該積層膜側面に接触するように、一方の凹部6内にアノード電極7を形成し、もう一方の凹部6内にカソード電極8aを形成した、リセス構造の横型ダイオードである。

【0028】

図11および図12に示す構造において、アノード電極7、7aは300nm厚のPd(パラジウム)からなる電極であり、カソード電極8はTi/Al電極である。つまり、カソード電極8はTi(チタン)膜上にAl(アルミニウム)膜を形成した積層構造を有している。図12においても、図11と同様に導電層5の底部の輪郭を破線により示している。

【0029】

ここで、図11に示すダイオードの平面図を図13に示す。また、図12の平面図も図13と同様の構造となる。図13には、アノード電極7a、カソード電極8およびバリア層3を示しており、バリア層3上に形成されているキャップ層4(図11参照)などは図示していない。アノード電極7aおよびカソード電極8の寸法は、図13の平面図に示す通り、何れも300μm×1.0mmである。つまり、長手方向の長さWacは1.0mmであり、当該方向に直交する方向の長さL1、L2は何れも300μmである。このように長手方向に延在するアノード電極7aおよびカソード電極8が前記長手方向に直交する方向に並ぶようにそれぞれの電極を配置している。平面視において、バリア層3はアノード電極7aおよびカソード電極8の周囲を囲むように形成されている。なお、アノード電極7aおよびカソード電極8間の長さLacは150μmである。

【0030】

図14に、試作した比較例の横型ダイオードの逆方向特性を評価した実験の結果を示す。

【0031】

図14に示すように、特性線1(実線)で示したプレーナ構造のダイオード(図11参照)の場合、逆方向電圧を1kV以上印加した場合でもブレークダウンには至らず、逆方向リーク電流は1kVまで1〜2×10−5A/mmのほぼ一定な値であった。

【0032】

これに対して特性線2(破線)で示したリセス構造のダイオード(図12参照)の場合は、逆方向電圧の増加に伴いリーク電流も増加し、逆方向電圧を100V印加したところでブレークダウンしてしまった。

【0033】

この実験結果によれば、塩素ガスを用いたドライエッチングにより加工し露出させたヘテロ接合側面に対して、アノード電極、およびカソード電極をそれぞれ形成したリセス構造の横型ダイオードは、ドライエッチングを施さないプレーナ構造のダイオードに比べて逆方向特性の著しい劣化が観測された。

【0034】

この現象に関して、本発明者らは塩素ガスを用いたドライエッチングが窒化物半導体に与える影響について調べるため、縦型ショットキーバリアダイオードを用いた実験を行い検討した。

【0035】

当該実験には、図15に示すように、n型GaN基板16上に、Siドーピング濃度が2×1016cm−3であり、膜厚が12μmである低濃度n型GaN層17をエピタキシャル成長した基板を用いた。

【0036】

n型GaN基板裏面には、カソード(オーミック)電極8bとしてTi/Al電極を設け、表面側の低濃度n型GaN層17上には、膜厚が300nmのPd(パラジウム)からなるアノード(ショットキー)電極7a(電極サイズは300μmφ)を設けている。

【0037】

本実験では、アノード電極7a形成前の処理として、低濃度n型GaN層17の上面に対して塩素ガスを用いたドライエッチングを施したダイオード(A)と、前記ドライエッチングを行わずに、エピタキシャル成長後の低濃度n型GaN層17表面にアノード電極7を形成したダイオード(B)の2種類の縦型ダイオードを作製した。なお、前記ドライエッチングによるエッチング量は100nmとする。

【0038】

図16および図17に、図15に示す比較例の縦型ダイオードの順方向特性を評価した結果を示す。図16および図17に示すグラフでは、横軸を順方向電圧とし、縦軸を順方向電流としている。

【0039】

図16に示す結果によれば、微小電流領域での電流の立ち上がりは、ドライエッチングを行っていないダイオード(B)に比べて、ドライエッチングを行ったダイオード(A)の方が約0.5V程度低電圧側にシフトしており、ショットキー障壁高さφbは、ダイオード(B)が約1.2eVであるのに対して、ダイオード(A)は約0.65eVにまで低下していることが観測された。しかし、ショットキー接合の良否を表すn値は、ダイオード(B)が約1.02であるのに対して、ダイオード(A)は1.07とほぼ同等であり、ドライエッチングによるショットキー接合自体の劣化はほとんど観測されなかった。

【0040】

さらに図17に示す結果によれば、電流の立上り電圧は、図16と同様に、ダイオード(B)に比べてダイオード(A)は約0.5V程度低電圧側にシフトしているが、素子抵抗を示す電流の傾きには差異は見られなかった。

【0041】

以上の実験結果から鑑みて、塩素ガスを用いたドライエッチングの窒化物半導体に与える影響としては、図17のグラフに示すように、素子抵抗を示す立上り後の電流の傾きに差異が見られないことから、エッチングによって露出した窒化物半導体面が高抵抗化しているのではないことが推察される。

【0042】

また、図16のグラフに示すように、n値が良好なことから、窒化物半導体表面に対する物理的または化学的な損傷は小さく、比較的清浄な窒化物半導体表面を保持したままであることが分かる。ただし、φbが低下していることから、エッチングに曝された窒化物半導体の最表層にはドナー(キャリア)が生じて低抵抗化しているものと推察される。

【0043】

したがって、リセス構造の横型ダイオードの逆方向特性の劣化は、上記エッチングに曝された窒化物半導体の最表面に生じたドナー(キャリア)の影響によりアノード電極が接触する窒化物半導体面が低抵抗化し、アノード電極および窒化物半導体間のφbが低下したことで、アノード(ショットキー)電極からのリーク電流が増大し、十分な逆方向耐圧が得られないことが原因であると推測される。

【0044】

また、上記の2DEG(二次元電子ガス)を導電層とした横型ダイオードの場合、導電層には特にn型の不純物を添加していないため、逆方向特性は前記プレーナ型に見られたような、逆方向電圧に対してある一定のリーク電流をもって推移する傾向を示すことが正常であると考えられる。

【0045】

これに対して、本発明者らは、GaN、AlGaNなどのバンドギャップの異なる窒化物半導体積層膜のヘテロ接合界面に生じる2DEG(二次元電子ガス)導電層をドリフト層とし、周知のドライエッチング法を用いて前記積層膜を加工・除去することで露出した前記積層膜の側面に対してショットキー接合する電極を備えた横型ダイオードにおいて、被ドライエッチング面のドナー(キャリア)を補償して、上記した逆方向特性を向上させることを見出した。

【0046】

したがって、塩素ガスを用いたドライエッチングによって形成した凹部の側面部、すなわち2DEG導電層を含む窒化物半導体積層膜からなるヘテロ接合の側面にアノード(ショットキー)電極を形成しても、逆方向特性は前記プレーナ型と同等の傾向を示す構造を実現することが好ましい。

【0047】

これに対して、本発明者らは鋭意検討し、GaN、AlGaNなどのバンドギャップの異なる窒化物半導体積層膜のヘテロ接合界面に生じる2DEG導電層をドリフト層とし、周知のドライエッチング法を用いて前記窒化物半導体積層膜の所望の領域を加工・除去することで露出した二次元電子ガスからなる導電層側面を含む窒化物半導体積層膜の側面方向に対してショットキー接合する電極を備えた横型ダイオードにおいて、以下のことを見出した。すなわち、本発明者らは、上記ドライエッチングに曝された窒化物半導体積層膜凹部のアノード電極を形成する領域に対して、少なくともその側面部に(1)半絶縁性、もしくは高抵抗な窒化物半導体層を再成長する、および(2)p型不純物を拡散させる、ことで被ドライエッチング面のドナー(キャリア)を補償して、前記目標とした横型ダイオードの逆方向特性を実現できることを見出した。

【0048】

以下に本発明の実施の形態と効果について、図面を参照しながら説明する。

【0049】

まず、本発明の実施の形態である窒化物半導体ダイオードの構造について説明する。図1は、本実施の形態に係る窒化物半導体ダイオードの断面図である。

【0050】

図1に示す窒化物半導体ダイオードでは、比較例の窒化物半導体ダイオードと比較がしやすいように、図11および図12に示したエピタキシャル構造と同一のものを用いており、各電極の寸法、配置も図13に示す通りであるものとする。図1に示す窒化物半導体ダイオードは、図12に示す構造と同様に凹部6内に形成されたアノード電極7と、図11に示す構造と同様に積層膜上に形成されたカソード電極8とを有している。カソード電極8とアノード電極7とは互いに離間している。なお、凹部6の深さは積層膜の上面から例えば50nm程度であるものとする。

【0051】

図1に示すように、本実施の形態の特徴であるアノード電極7の形成領域に設けられた凹部6は、塩素ガスを用いたドライエッチングにより形成されており、凹部6の底面、および側面には、不純物であるC(炭素)を添加したGaNからなる再成長層(エピタキシャル成長層)9が形成されている。つまり、基板1上には高抵抗バッファ層2、バリア層3、キャップ層4が順次形成されており、高抵抗バッファ層2、バリア層3、キャップ層4からなる積層膜の上面をエッチングすることで形成された凹部6内にはアノード電極7が形成され、アノード電極7と前記積層膜との間には再成長層9が形成されている。図1では、導電層5の底部の輪郭を破線により示している。

【0052】

なお、カソード電極8はアノード電極7のようなエッチングにより形成した凹部側面ではなく、平面上に形成している。これは、二次元電子ガス層である導電層5が一層である場合、特にリセス構造としなくても、導電層に対して十分に低いオーム性接触を得ることが可能なためである。

【0053】

塩素ガスを用いたアノード電極形成領域の凹部形成からアノード電極形成に至るまでの工程では、SiO2膜をマスクとして塩素ガスを用いたドライエッチングによりアノード電極形成領域のみに凹部6を形成した後、そのまま前記SiO2膜をマスクとして、該凹部の底面、および側面にC(炭素)を添加したGaNからなる再成長層9を20nmの厚さで再成長(エピタキシャル成長)させる。この時、GaNからなる再成長層9は前記SiO2膜上に成長されないため、窒化物半導体面が露出した凹部6の内壁および底部のみに選択的に成長形成される。

【0054】

なお、窒化物半導体の結晶成長においてエピタキシャル層にC(炭素)を添加する方法としては、例えば周知のMOVPE(Metal-Organic Vapor Phase Epitaxy;有機金属化学気相エピタキシー)成長法を用い、その際に成長圧力を減圧する方法がある。また、MOVPE成長法を用いる際は、さらに成長圧力を制御することで、添加するC(炭素)の濃度を容易に調整することができる。本実施の形態の窒化物半導体ダイオードにおいて再成長層9を形成する際の再成長圧力は50kPaであり、GaNからなる再成長層9中のC濃度は4×1016cm−3である。

【0055】

その後、C(炭素)を添加したGaNからなる再成長層9が成長された当該凹部6を完全に埋込むようにPd(パラジウム)からなるアノード電極7を形成することで、アノード電極形成工程は完了する。アノード電極7は、例えばリフトオフにより形成することができる。アノード電極7は、例えばNi(ニッケル)膜上にAu(金)膜を形成した積層構造を有するものでもよい。

【0056】

そして、所望の平坦部にカソード電極8を形成して完成した本発明の横型ダイオードの逆方向特性を評価した結果、逆方向電圧を1kVまで印加した場合でもブレークダウンには至らず、前述したプレーナ構造のダイオードと同様にほぼ一定の逆方向リーク電流値を示しながら推移する傾向を示した。この時のリーク電流レベルは6.0×10−6〜7.0×10−6A/mmの範囲であり、前記プレーナ構造のダイオードよりもリーク電流は低減した。

【0057】

これは、不純物としてC(炭素)を添加したGaN層がもつ高抵抗特性と、再成長時に基板に加わる1000℃以上の熱との相乗効果により、ドライエッチング曝露面に生じたドナー(キャリア)が補償されるとともに、C添加GaN層によってヘテロ接合側面が適切な状態で保護されたことと、二次元電子ガスからなる導電層を含む積層膜の側面に対して、アノード電極が直接接触しない構造となったこととが原因として考えられる。ここでは、凹部近傍の積層膜内を高抵抗化することを目的としてC(炭素)などの不純物を添加しているため、当然カソード電極近傍よりもアノード電極近傍の積層膜内の前記不純物濃度は高くなる。

【0058】

このように、ドライエッチングにより加工して露出させた上記ヘテロ接合を含む積層膜の側面に対してショットキー接続するアノード電極を設けた窒化物半導体ダイオードにおいて、本実施の形態の窒化物半導体ダイオードは、C(炭素)などの不純物を導入しない場合のショットキーバリアダイオードに比べて逆方向リーク電流が小さく、かつ高い耐圧特性を有する窒化物半導体ダイオードを実現することができる。これにより、窒化物半導体ダイオードの性能を向上させることができる。

【0059】

なお、再成長層9の添加不純物を、C(炭素)に代えてFe(鉄)を添加したGaN層である再成長層9を形成して、上記と同様の横型ダイオードを作製した窒化物半導体ダイオードの実施形態について説明する。このときの再成長層9のFe濃度は5×1017cm−3、膜厚は100nmである。再成長したGaN層(再成長層)に添加する不純物、濃度および膜厚以外は、上記した図1に示す構造と同じ構造であるものとする。

【0060】

上記のようにFe(鉄)を導入した再成長層9を設けることで完成した横型ダイオードについて逆方向特性を評価した結果、Fe(鉄)を導入した構造においても、前記プレーナ型と同様に逆方向電圧を1kVまで印加した場合でもブレークダウンには至らず、リーク電流は8.0〜9.0×10−7A/mmと低く良好であった。

【0061】

また、上記した再成長層9の添加不純物を、C(炭素)またはFe(鉄)ではなくMg(マグネシウム)とした場合の窒化物半導体ダイオードの実施形態について説明する。このときの再成長層9のMg濃度は1×1017cm−3、膜厚は50nmである。なお、この場合の窒化物半導体ダイオードの構造も、再成長したGaN層(再成長層)に添加する不純物、濃度および膜厚以外は、図1を用いて説明した構造と同じである。

【0062】

完成した本発明の横型ダイオードについて逆方向特性を評した結果、再成長層9にMg(マグネシウム)を添加した当該構造において、逆方向電圧を1kVまで印加した場合にブレークダウンには至らなかったが、リーク電流は不安定な値を示した。

【0063】

詳細には、1回目の逆方向電圧印加では、リーク電流は3.0×10−5〜9.0×10−6A/mmの範囲で変動していたが、2回目以降は8.0〜9.0×10−6A/mmの範囲に安定した。

【0064】

これは、Mg(マグネシウム)を添加したGaN層(再成長層)中に含まれる高濃度の水素に関係しているものと考えられ、1回目の逆方向電圧印加によって生じた熱の影響により、Mg添加GaN層に含まれていた水素が半導体中を移動・脱離する現象を起こしたためにリーク電流が不安定となり、2回目以降はすでに水素脱離が完了しているため、リーク電流値が安定していたものと推測される。

【0065】

これに関して、本発明者らはMg添加GaN層再成長後に、窒素雰囲気中にて700℃、30分の熱処理を行い、続いてアノード電極を形成し、その後ダイオードを作製・評価したところ、逆方向リーク電流の変動は観測されなかったことを確認した。

【0066】

以上、再成長層に添加したC、FeおよびMgの前記3元素は、窒化物半導体結晶成長技術の分野において、すでに周知のものであるため、製法上適用しやすい材料である。本実施の形態の窒化物半導体ダイオードでは、ドライエッチングによって形成した窒化物半導体の凹部に露出したヘテロ接合体の側面に対して、前記C、FeおよびMgの3元素の中から選択された不純物を添加した窒化物半導体層を再成長することで、アノード電極からのリーク電流を低減し、ダイオードの逆方向耐圧を前記プレーナ構造並みに向上させることを可能としている。

【0067】

本発明者らの検討によれば、添加する不純物の濃度としては、CまたはFeを注入する場合は4×1016cm−3以上とし、また、不純物としてMgを添加する場合は、1×1017cm−3以上とすることが好ましい。これらの値未満の濃度で各不純物を導入して再成長層を形成すると、十分に真性度の高い再成長層、または低濃度かつ高抵抗なp型の導電型を有する再成長層が得られず、ショットキー接合すべき積層膜の側壁がn型化してしまい、ショットキーバリアダイオードの逆方向耐圧が低下する問題、または逆方向リーク電流が増大する問題などが発生する。

【0068】

また、上記不純物を添加した窒化物半導体層(再成長層)は非常に高抵抗であるため、必要以上に膜厚が厚いと、順方向における抵抗成分となり素子抵抗が増大する。本発明者らの検討によれば、再成長層の膜厚は150nm以下であることが望ましく、より好ましくは100nm以下であることが望ましい。

【0069】

言い換えれば、前記再成長層が1nmの薄い膜厚で存在するだけでも、再成長層が無い場合に比べてダイオードの逆方向特性を著しく改善することができる。

【0070】

本実施の形態では、再成長層としてGaNを用いたが、特にGaNである必要は無く、GaNの他、AlGaN、InAlN、InAlGaNまたはInGaNなどを用いてもよい。ただし、GaNよりもバンドギャップエネルギーの大きい窒化物半導体材料を用いた場合、再成長層と前記凹部に露出した窒化物半導体面の側面部との間で、2DEGが生じる可能性があるため、再成長層材料としては、GaNに比べてバンドギャップエネルギーがあまり大きくならない材料であることが望ましい。

【0071】

また、GaN以外の材料を選択した場合は、選択的にエピ成長することができないため、再成長後に不要な再成長層を除去する工程が増える。

【0072】

(実施の形態2)

次に、本発明の実施の形態2である窒化物半導体ダイオードの実施形態について説明する。図2および図3は、それぞれ本実施の形態に係る窒化物半導体ダイオードの断面図および平面図である。

【0073】

本実施の形態に係る窒化物半導体ダイオードの構造は、前記実施の形態1に述べた窒化物半導体ダイオードと同様に、アノード電極形成領域に塩素ガスを用いたドライエッチングを行い凹部を形成した横型ダイオードであり、AlGaN層とその下層のGaN層の積層膜からなるヘテロ接合数を3つとしたことで、二次元電子ガスからなる導電層が3層設けられているものである。

【0074】

これにより、図1に示す構造のように導電層が単層の場合に比べて、順方向特性における電流密度が増大するとともに、導電層のシート抵抗も低減するため、オン抵抗およびオン電圧の低減が可能となる。

【0075】

図2に示すように、本実施の形態の窒化物半導体ダイオードを構成するエピタキシャル層は、サファイアからなる基板1上に形成された高抵抗バッファ層2、バリア層3、中間GaN層11およびキャップ層4を有している。高抵抗バッファ層2は膜厚3.0μmのGaNからなりC(炭素)が2.0〜4.0×1016cm−3の濃度範囲でドープ(導入)されている。バリア層3は膜厚20nmのAlGaNからなりC(炭素)が2.0〜4.0×1016cm−3の濃度範囲でドープされている。中間GaN層11は膜厚100nmのGaNからなりC(炭素)が2.0〜4.0×1016cm−3の濃度範囲でドープされている。キャップ層4は膜厚5nmのGaNからなりC(炭素)が2.0〜4.0×1016cm−3の濃度範囲でドープされている。

【0076】

高抵抗バッファ層2、バリア層3、中間GaN層11およびキャップ層4はエピタキシャル層であり、高抵抗バッファ層2上にはバリア層3が形成され、当該バリア層3上には中間GaN層11およびバリア層3が交互に積層されている。つまり、高抵抗バッファ層2、バリア層3および中間GaN層11を含む積層膜は、GaN層(高抵抗バッファ層2または中間GaN層11)とその上にヘテロ接合されたAlGaN層(バリア層3)とからなるヘテロ接合部を複数層重ねた構造を有している。

【0077】

また、当該ヘテロ接合界面の下部におけるGaN層(高抵抗バッファ層2または中間GaN層11)内の上面近傍には、ヘテロ接合界面、すなわちGaN層とその上部のAlGaN層との界面に沿う二次元電子ガスからなる導電層5a、5bおよび5cが形成されている。ここでは、積層された三つのヘテロ接合部のうち、最も上に形成された中間GaN層11の上面に前述した二次元電子ガスからなる導電層5aが形成され、その下のヘテロ接合部の中間GaN層11の上面には導電層5bが形成され、その下のヘテロ接合部の高抵抗バッファ層2の上面には導電層5cが形成されているものとする。

【0078】

つまり、前記積層膜は、上面に導電層5cを有する高抵抗バッファ層2、バリア層3、上面に導電層5bを有する中間GaN層11、バリア層3、上面に導電層5aを有する中間GaN層11、バリア層3およびキャップ層4が基板側から順次形成されている構造を有している。図2では、導電層5a〜5cはそれぞれ破線を用いてその底部の輪郭を示している。つまり、導電層5a〜5cは、高抵抗バッファ層2内または中間GaN11内の上面からその下部の破線までの間の領域に形成されている。

【0079】

本実施の形態の横型ダイオードのエピタキシャル層には予めC(炭素)が添加されているため、各半導体層の真性度が向上し、アンドープの場合よりも寄生的なリーク電流が低減する効果がある。

【0080】

アノード電極7が形成されている領域には、塩素ガスを用いたドライエッチングにより形成された、エッチング深さが250nmの凹部6が設けられており、凹部6の底面および内壁には、膜厚が50nmであり、C(炭素)が8×1017cm−3の濃度で添加されたGaNからなる再成長層9が設けられている。

【0081】

凹部6内において、再成長層9上にはNi/Auからなるアノード(ショットキー)電極7が設けられている。

【0082】

カソード電極8が形成されている領域の高抵抗バッファ層2、バリア層3、中間GaN層11およびキャップ層4からなる積層膜中には、Si(シリコン)がイオン注入されたn型層12が設けられており、カソード(オーミック)電極8は、前記n型層12の直上に設けられている。このn型層12を設けることによって、カソード電極8と導電層5a〜5cとの接合抵抗は十分に低く抑えることができる。つまり、カソード電極8はn型層12を介して導電層5a〜5cを含む前記積層膜の側面に電気的に接続されている。図2では、n型層12の輪郭を点線で示しており、当該点線で囲まれた領域であってカソード電極8の直下の領域の積層膜上面にn型層12が形成されている。また、図3ではn型層12の輪郭を破線で示している。

【0083】

ここで、図3に本実施の形態の窒化物半導体ダイオードの平面図を示す。図3に示すように、アノード(ショットキー)電極7とカソード(オーミック)電極8はそれぞれ櫛型形状を有して対向しており、アノード電極7およびカソード電極8の離間長(ドリフト層長さ)は100μmである。

【0084】

アノード電極7およびカソード電極8のそれぞれの電極櫛部の長手方向の長さは1本あたり500μmであり、前記長手方向に直交する方向の電極の幅は100μmである。

【0085】

アノード電極7の櫛数は5本であり、アノード電極7の左右電極端部に対向する形でカソード電極8が設けられていることから、全体的な電極間の対向長さは0.5mm×2面×5本=5mmである。

【0086】

前記実施の形態1の窒化物半導体ダイオードである横型ダイオードの逆方向耐圧特性は、本実施の形態の作用、および効果を反映して、逆方向電圧を3kV印加した場合でもブレークダウンせず、逆方向リーク電流も3層の導電層5a〜5cを有しながら、1.0×10−7A/mm以下と低く良好であった。

【0087】

これは、前述の通りエピタキシャル層に予めC(炭素)を添加して各層の真性度を向上させたことによる効果であると考えられる。また、順方向特性においても3層の導電層の効果により、オン抵抗は80mΩcm2以下と良好であった。

【0088】

ここでは、再成長層に添加する不純物としてC(炭素)を選択したが、前記実施の形態1で述べたとおり、Fe(鉄)またはMg(マグネシウム)を用いた場合でも同様の効果が得られることは言うまでもない。

【0089】

また、ここではエピタキシャル層に予めC(炭素)を添加した例について述べたが、これは予めエピタキシャル層の真性度の向上させる、または高抵抗化させて、エピタキシャル層が持つ寄生リーク成分を排除することが目的であるため、C(炭素)の他、Fe(鉄)を添加しても同様の効果が得られることは言うまでもない。

【0090】

また、ここでは導電層の数、すなわちヘテロ接合部を3層としたが、これはAlGaN/GaNの積層数を変えることで、より多くの導電層を設けることは可能である。

【0091】

しかし、バンドギャップエネルギーが大きいバリア層(例えばAlGaN)に用いる半導体材料と、二次元電子ガス層からなる導電層が形成される側のバンドギャップエネルギーが小さい半導体材料(例えばGaN)との格子不整合差の大小によって、積層できるバリア層の膜厚には限界があるため、より多くの導電層を設けるためには、前記格子不整合差を考慮して各々の半導体材料の組成などを調整する必要がある。

【0092】

また、ここでは、カソード電極のオーミック接続確保のために、Siイオン注入によりn型層を形成した例について述べたが、凹部を形成してから、当該凹部側面にカソード電極を形成してもよいことは言うまでもなく、さらに両者を組み合せて、カソード電極形成領域に凹部を形成した後、当該凹部の底面および内壁に対してSiイオン注入して凹部全面にn型層を形成してからカソード電極を形成しても何ら問題はない。これは、カソード電極に必要とされる特性が、導電層との低オーム性接触であるためである。

【0093】

次に、本実施の形態の窒化物半導体ダイオードの主要部の作製工程について、図4〜図7を参照しながら以下に説明する。図4〜図7では、いずれもn型不純物拡散領域および導電層5a〜5cの輪郭をそれぞれ点線および破線で示している。

【0094】

まず、図4に示すように、サファイアからなる基板1上に高抵抗バッファ層2、バリア層3、中間GaN層11、バリア層3、中間GaN層11、バリア層3およびキャップ層4を順次エピタキシャル成長させる。続いて、キャップ層4上の全面に膜厚が30nmのSiN(図示せず)からなるスルー膜を被着した後、カソード電極形成領域を開口したフォトレジストパターンを形成する。開口された領域のエピタキシャル層中にn型の不純物であるSiイオンの注入を行い、前記フォトレジストパターンと前記スルー膜を除去した後、再度エピタキシャル層全面に膜厚が50nmのSiNからなるキャップ膜20を被着する。続いて、窒素雰囲気中にて、1100℃、30分間の活性化アニールを行って、n型層12を形成する。

【0095】

次に、図5に示すように、キャップ膜20を除去した後、エピタキシャル層全面に膜厚300nmのSiO2膜10を被着した後、n型層12を形成した領域およびドリフト層以外の全領域を開口したフォトレジストパターンをSiO2膜10上に形成する。前記フォトレジストパターンが開口された領域の直下のSiO2膜10を、フッ酸系溶液を用いたウェットエッチングにより除去して、不要なSiO2膜10を除去する。続いて、塩素ガスを用いたドライエッチングにより、高抵抗バッファ層2、バリア層3、バリア層3およびキャップ層4により構成された積層膜の表面から250nmの深さまでエッチングして凹部6を形成する。これにより、ドリフト層、およびカソード電極形成領域は、凹部6の底面に比べて上面高さが高い凸部15となる。

【0096】

次に、図6に示すように、MOVPE法により、C(炭素)を8×1017cm−3の濃度で添加したGaNからなる再成長層9を形成する。再成長層9の膜厚は50nmであり、再成長層9は、SiO2膜10上には成長されずに凹部6の底部および内壁のみに選択的に成長形成される。

【0097】

次に、図7に示すように、SiO2膜10を除去した後、再成長層9を形成した凹部6内にNi/Auからなるアノード電極7を形成して凹部6を完全に埋込み、n型層12が設けられた領域上にTi/Alからなるカソード電極8を形成する。カソード電極8は、例えば基板1上の全面にTi/Alからなる金属膜を形成した後に、フォトリソグラフィ技術およびドライエッチング法を用いて前記金属膜をパターニングすることで、n型層12の直上に形成することができる。以上の工程により、本実施の形態の窒化物半導体ダイオードが完成する。

【0098】

本実施の形態では、ヘテロ接合を有する窒化物半導体積層膜をドライエッチングにより加工・除去することで設けた凹部の、少なくとも側面に対してショットキー接合するアノード電極を形成する場合、アノード電極の形成前に、該凹部に露出した窒化物半導体面に対して不純物を添加した高抵抗な、または導電性が著しく低い半導体層を再成長することで、アノード電極からのリーク電流の増大を抑制し、耐圧を向上させることができる。

【0099】

(実施の形態3)

次に、本発明の実施の形態3である窒化物半導体ダイオードの実施形態について説明する。図8は、本実施の形態に係る窒化物半導体ダイオードの断面図である。

【0100】

ここでは、前記実施の形態1、2で述べたように再成長層を設けるのではなく、ドライエッチングに曝され低抵抗化したアノード電極形成領域の凹部の窒化物半導体の表面に、p型不純物を拡散させて窒化物半導体ダイオードを作製することで、当該窒化物半導体ダイオードの逆方向特性を向上させる構造について説明する。凹部の内壁および底部からエピタキシャル層からなる積層膜内に拡散させるp型不純物としては、プロセスの容易性から考えて、Zn(亜鉛)またはMg(マグネシウム)が好ましい。

【0101】

Zn、およびMgを導入する際は、ZnOまたはMgOなどの酸化膜を、拡散対象である窒化物半導体上の所望の領域上に直接被着形成した後、少なくとも600℃以上の熱処理を行うことで、容易に窒化物半導体中へZn、およびMgを積層膜内に拡散させることができる。

【0102】

本実施の形態の窒化物半導体ダイオードでは、比較例の窒化物半導体ダイオードとの比較がしやすいように、前記実施の形態1、2で述べたものと同じエピタキシャル構造の基板を用いている。半導体素子の構造としては、図8に示すように、本発明の特徴であるアノード電極7の形成領域に設けられた凹部6の底面、および側面に、p型不純物としてZnを拡散させたp型不純物拡散領域13を設けている。つまり、本実施の形態の窒化物半導体ダイオードの構造は図1の構造に似ているが、再成長層9が形成されておらず、凹部6の内壁および底面から凹部6近傍の積層膜内にかけてp型不純物拡散領域13が形成されている点で、本実施の形態は前記実施の形態1、2と異なる。

【0103】

図8に示すように、導電層5の底部の輪郭を破線で示しており、p型不純物拡散領域13の輪郭が積層膜内に点線で示されている。つまり、p型不純物拡散領域13は、凹部6の表面から前記破線にかけて形成されている。

【0104】

p型不純物拡散領域13を形成する工程では、積層膜上に形成したSiO2膜パターンをマスクとして、塩素ガスを用いたドライエッチングによりアノード電極形成領域に凹部6を形成した後、前記SiO2膜パターンを除去せずに基板上の全面にスパッタ法を用いてZnO膜を被着形成する。この時のZnO膜の厚さは100nmとする。その後、窒素雰囲気中において800℃、1時間の熱処理を行うことで当該凹部6の底面、および側面にZnが拡散し、p型不純物拡散領域13が形成される。

【0105】

次に、酸系およびアルカリ系エッチング液を用いて、不要なZnO膜およびSiO2膜パターンを除去した後、凹部6内にアノード電極7を形成し、続いて前記積層膜を挟んでアノード電極7と対向する所定の領域にカソード電極8を形成することで、本実施の形態の横型の窒化物半導体ダイオードが完成する。

【0106】

なお、アノード電極7、カソード電極8の寸法、配置、電極間距離については、図13を用いて説明したものと同じとする。本実施の形態においても、図8に示すようにカソード電極8は実施の形態1、2と同様に凹部の内壁ではなく積層膜上面の平面上に形成している。

【0107】

また、本発明者らは、Znの拡散による窒化物半導体中のZn濃度プロファイルを調べるため、別途サファイア基板上に膜厚が4μmであるアンドープGaN層をエピタキシャル成長した基板を用意し、アンドープGaN層上にスパッタ法を用いて上記と同じ条件でZnO膜を被着形成し、窒素雰囲気中において上記と同じ800℃、1時間の熱処理を行った。

【0108】

その後不要なZnO膜を除去し、続いてGaN中における深さ方向のZn濃度プロファイルをSIMS分析により調べた結果を図9に示す。図9に示す濃度分布のグラフでは、横軸を半導体表面からの深さ、縦軸をZn(亜鉛)の濃度としている。

【0109】

図9に示す濃度分布から、最もZn濃度が高いのはアンドープGaN層最表面近傍であり、その濃度は約1.0×1019cm−3程度であることが分かる。また、Zn拡散深さは約400nmにまで及んでおり、表面からの拡散のため、深さ方向に対してZn濃度は指数関数的に減少する傾向を示している。

【0110】

この拡散による不純物濃度プロファイルは、不純物拡散自体の原理から考えて、上記の平面上に限らず、ドライエッチングによって露出した窒化物半導体側面方向においても同様の傾向を示すと推定されることから、アノード電極7が形成された凹部6の側面方向のZn濃度も、上記濃度プロファイルが反映されていると推定される。

【0111】

上述した本発明の横型ダイオードの逆方向特性について評価した結果、前記プレーナ構造と同様に逆方向電圧を1kVまで印加した場合でもブレークダウンには至らなかった。これは、エッチングの影響により生じた半導体表面のキャリアをZnなどのp型不純物が補償することで、キャリアが消失したためであると考えられる。

【0112】

なお、このとき注入する不純物は、n型の導電型を有する不純物であってはならない。

【0113】

また、p型の不純物を過剰に注入すると、積層膜内においてアノード電極側とカソード電極側とでpn接合によるダイオードが形成されるため、注入する不純物は十分に低い濃度のp型不純物であることが望ましい。

【0114】

そこで、ZnO膜、およびMgO膜を用いた不純物拡散の効果と、拡散条件を探索するため、各不純物拡散条件に対する上記横型ダイオードにおける逆方向特性について調べた結果を図10にまとめて示す。

【0115】

なお、このときのZnO膜、およびMgO膜の膜厚は何れも100nmであり、熱処理時間は、1時間である。熱処理条件のパラメータは、温度が600℃、700℃または800℃である。また、熱処理雰囲気は常圧窒素雰囲気または減圧(100Pa)であり、ダイオードの逆方向特性としては、ブレークダウン電圧(最大1kV)と、逆方向リーク電流について図10に記している。

【0116】

図10より、何れの条件においても、ブレークダウン電圧は1kV以上となり高耐圧特性を示したが、熱処理雰囲気の違いによって、逆方向リーク電流に差異が現れた。

【0117】

常圧窒素雰囲気と減圧下(100Pa)とを比較すると、減圧下の方がリーク電流は低い傾向にある。また、熱処理温度についても低い方が、リーク電流は小さい傾向にある。

【0118】

そこで、最もリーク電流が小さかった減圧下、600熱処理条件を用いて、ZnO膜、およびMgO膜について、上記と同様に窒化物半導体中における不純物プロファイルを調べた結果、Zn(亜鉛)の最大不純物濃度は6.2×1017cm−3、Mg(マグネシウム)の最大不純物濃度は4.7×1017cm−3であった。

【0119】

以上のことから、本発明者らは、ドライエッチングによって設けたアノード電極形成領域の凹部にp型不純物を拡散させることで、前記プレーナ構造と同等の逆方向リーク電流の傾向を示し、ブレークダウン電圧を増大できることを見出した。このときのp型不純物濃度は、上記の内容から考えて少なくとも5×1017cm−3以上の濃度であることが望ましい。

【0120】

なお、窒化物半導体中に上記の熱処理温度範囲でp型不純物を拡散させただけでは、窒化物半導体がp型の導電型を示すことはなく、単純に拡散した領域は高抵抗化する。これは、本実施の形態で作製したダイオードの順方向特性を評価した限りでは、順方向の立上り電圧は1V前後の値であり、GaNのバンドギャップエネルギー(約3.3V程度)にはならなかったことからも言える。

【0121】

したがって、上記p型不純物を拡散させた領域と、アノード電極との間の接合はpn接合ではなくショットキー接合であり、p型不純物拡散を適用して作製した横型ダイオードは、何れもショットキーバリアダイオードである。

【0122】

本実施の形態では、導電層が単層である横型ダイオードに適用した場合について述べたが、前記実施の形態2で述べたように複数の導電層を持つ横型ダイオードに適用しても本発明の効果が得られることは言うまでもない。

【0123】

本実施の形態では、ヘテロ接合を有する窒化物半導体積層膜を、塩素ガスを用いたドライエッチングにより加工・除去して設けた凹部の少なくとも側面に対してショットキー接合するアノード電極を形成する場合、アノード電極を形成する前に、該凹部に露出した窒化物半導体面に対してp型不純物を拡散させることで、アノード電極からのリーク電流の増大を抑制し、耐圧を向上させることができる。

【0124】

以上、本発明者らによってなされた発明を実施の形態に基づき具体的に説明したが、本発明は前記実施の形態に限定されるものではなく、その要旨を逸脱しない範囲で種々変更可能であることはいうまでもない。

【0125】

例えば、前記実施の形態1〜3ではサファイア基板を用いた例について述べたが、この他に、SiC基板、Si基板、GaN基板を用いてもよい。

【0126】

また、前記実施の形態1、3では、基板上にエピタキシャル成長した第1の窒化物半導体層および第2の窒化物半導体層がアンドープである場合について述べたが、前記実施の形態2と同様に最初からエピタキシャル層にC(炭素)またはFe(鉄)などを適度にドーピングしてもよい。これにより。前記第1の窒化物半導体層および第2の窒化物半導体層の真性度がアンドープの場合よりも増すため、エピタキシャル層自体が有する寄生的な逆方向リーク電流レベルをさらに低減することができる。

【産業上の利用可能性】

【0127】

本発明は、横型のショットキーバリアダイオードの製造技術に適用して有効である。

【符号の説明】

【0128】

1 基板

2 高抵抗バッファ層

3 バリア層

4 キャップ層

5、5a〜5c 導電層

6 凹部

7、7a アノード(ショットキー)電極

8、8a、8b カソード(オーミック)電極

9 再成長層

10 SiO2膜

11 中間GaN層

12 n型層

13 p型不純物拡散領域

15 凸部

16 n型GaN基板

17 低濃度n型GaN層

20 キャップ膜

【特許請求の範囲】

【請求項1】

基板と、

前記基板上に形成された第1窒化物半導体層および前記第1窒化物半導体層よりもバンドギャップエネルギーが大きい第2窒化物半導体層が積層されたヘテロ接合型の積層膜と、

前記積層膜の側面にオーミック接続されたカソード電極と、

アノード電極と、

を備え、

前記積層膜は、前記第1窒化物半導体層および前記第2窒化物半導体層の界面であるヘテロ接合面の深さに達する凹部を備え、

前記凹部において、C(炭素)、Fe(鉄)、Zn(亜鉛)、Mg(マグネシウム)の群から選択された少なくとも1種類以上の不純物が注入された領域を備え、

前記アノード電極は、前記領域に接して前記積層膜とショットキー接続していることを特徴とする窒化物半導体ダイオード。

【請求項2】

前記領域は、前記積層膜自体に前記不純物を注入するか、前記不純物を含む膜を成膜することにより形成されていることを特徴とする請求項1記載の窒化物半導体ダイオード。

【請求項3】

前記領域は、CもしくはFeが4×1016cm−3以上の濃度で含まれているか、またはMgが1×1017cm−3以上の濃度で含まれていることを特徴とする請求項1記載の窒化物半導体ダイオード。

【請求項4】

前記領域における前記不純物の濃度は、前記カソード電極と前記積層膜との界面の前記積層膜中の前記不純物の濃度よりも高いことを特徴とする請求項1記載の窒化物半導体ダイオード。

【請求項5】

前記第1窒化物半導体層はGaNを含み、

前記第2窒化物半導体層はAlGaN、InAlNまたはInAlGaNを含むことを特徴とする請求項1記載の窒化物半導体ダイオード。

【請求項6】

前記カソード電極に隣接する前記積層膜内にはSiが導入されていることを特徴とする請求項1記載の窒化物半導体ダイオード。

【請求項7】

前記基板はサファイア、Si、SiCまたはGaNを含むことを特徴とする請求項1記載の窒化物半導体ダイオード。

【請求項8】

前記積層膜の最上層に形成された前記第2窒化物半導体層上にはGaNを含むキャップ層が形成されていることを特徴とする請求項1記載の窒化物半導体ダイオード。

【請求項9】

前記領域はGaN、AlGaN、InGaN、InAlNまたはInAlGaNを含むことを特徴とする請求項2記載の窒化物半導体ダイオード。

【請求項10】

前記第1窒化物半導体層および前記第2窒化物半導体層にはCまたはFeが導入されていることを特徴とする請求項1記載の窒化物半導体ダイオード。

【請求項1】

基板と、

前記基板上に形成された第1窒化物半導体層および前記第1窒化物半導体層よりもバンドギャップエネルギーが大きい第2窒化物半導体層が積層されたヘテロ接合型の積層膜と、

前記積層膜の側面にオーミック接続されたカソード電極と、

アノード電極と、

を備え、

前記積層膜は、前記第1窒化物半導体層および前記第2窒化物半導体層の界面であるヘテロ接合面の深さに達する凹部を備え、

前記凹部において、C(炭素)、Fe(鉄)、Zn(亜鉛)、Mg(マグネシウム)の群から選択された少なくとも1種類以上の不純物が注入された領域を備え、

前記アノード電極は、前記領域に接して前記積層膜とショットキー接続していることを特徴とする窒化物半導体ダイオード。

【請求項2】

前記領域は、前記積層膜自体に前記不純物を注入するか、前記不純物を含む膜を成膜することにより形成されていることを特徴とする請求項1記載の窒化物半導体ダイオード。

【請求項3】

前記領域は、CもしくはFeが4×1016cm−3以上の濃度で含まれているか、またはMgが1×1017cm−3以上の濃度で含まれていることを特徴とする請求項1記載の窒化物半導体ダイオード。

【請求項4】

前記領域における前記不純物の濃度は、前記カソード電極と前記積層膜との界面の前記積層膜中の前記不純物の濃度よりも高いことを特徴とする請求項1記載の窒化物半導体ダイオード。

【請求項5】

前記第1窒化物半導体層はGaNを含み、

前記第2窒化物半導体層はAlGaN、InAlNまたはInAlGaNを含むことを特徴とする請求項1記載の窒化物半導体ダイオード。

【請求項6】

前記カソード電極に隣接する前記積層膜内にはSiが導入されていることを特徴とする請求項1記載の窒化物半導体ダイオード。

【請求項7】

前記基板はサファイア、Si、SiCまたはGaNを含むことを特徴とする請求項1記載の窒化物半導体ダイオード。

【請求項8】

前記積層膜の最上層に形成された前記第2窒化物半導体層上にはGaNを含むキャップ層が形成されていることを特徴とする請求項1記載の窒化物半導体ダイオード。

【請求項9】

前記領域はGaN、AlGaN、InGaN、InAlNまたはInAlGaNを含むことを特徴とする請求項2記載の窒化物半導体ダイオード。

【請求項10】

前記第1窒化物半導体層および前記第2窒化物半導体層にはCまたはFeが導入されていることを特徴とする請求項1記載の窒化物半導体ダイオード。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【公開番号】特開2013−115362(P2013−115362A)

【公開日】平成25年6月10日(2013.6.10)

【国際特許分類】

【出願番号】特願2011−262557(P2011−262557)

【出願日】平成23年11月30日(2011.11.30)

【出願人】(000005108)株式会社日立製作所 (27,607)

【Fターム(参考)】

【公開日】平成25年6月10日(2013.6.10)

【国際特許分類】

【出願日】平成23年11月30日(2011.11.30)

【出願人】(000005108)株式会社日立製作所 (27,607)

【Fターム(参考)】

[ Back to top ]