窒化物半導体発光素子及びその製造方法

【課題】

高抵抗領域と低抵抗領域が隣接して形成されると、境界部に電流集中が生じる。

【解決手段】

窒化物半導体発光素子は、基板と、基板上に配置され、p型層、活性層、n型層を含む窒化物半導体積層と、p型層と基板との間に形成されたp側電極と、n型層上の限定された領域に形成されたn側電極と、n側電極に対向する領域を含んで、p型層内、またはp型層表面に形成され、実質的に電流を流さない高抵抗領域と、高抵抗領域外側のp型層に形成され、p側電極との間に電流を流す低抵抗領域と、高抵抗領域と低抵抗領域の間に形成され、制限された電流を流すグレーデッド領域と、を有する。

高抵抗領域と低抵抗領域が隣接して形成されると、境界部に電流集中が生じる。

【解決手段】

窒化物半導体発光素子は、基板と、基板上に配置され、p型層、活性層、n型層を含む窒化物半導体積層と、p型層と基板との間に形成されたp側電極と、n型層上の限定された領域に形成されたn側電極と、n側電極に対向する領域を含んで、p型層内、またはp型層表面に形成され、実質的に電流を流さない高抵抗領域と、高抵抗領域外側のp型層に形成され、p側電極との間に電流を流す低抵抗領域と、高抵抗領域と低抵抗領域の間に形成され、制限された電流を流すグレーデッド領域と、を有する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明の実施例は、窒化物半導体発光素子及びその製造方法に関する。

【背景技術】

【0002】

GaN系窒化物半導体発光素子は、サファイア基板上にn型層、発光層、p型層の窒化物半導体層を成長して作成することが多い。例えば、p型層と発光層の一部をエッチングしてn型層を露出し、p型層、n型層表面に電極を形成する。III族元素として、GaにAl,Inを添加することによってバンドギャップを調整することができる。AlGaInNをIII族窒化物ないし窒化物半導体と呼ぶ。

【0003】

サファイアは絶縁物であり、熱伝導率は比較的低い。高出力発光素子を形成するためには熱伝導(放熱性)を改良することが望ましい。サファイア基板上にIII族窒化物半導体層を成長した後、p型層表面に電極を形成し、その上にSi等の熱伝導性のよい支持基板を結合した後、サファイア基板側からKrF等のエキシマレーザを照射してサファイア基板を除去するレーザリフトオフが行なわれる。Si支持基板は、例えば共晶によりp側電極に接合する。サファイア基板を除去して、露出したn型半導体層の上に、必要に応じて透明電極を介して、ボンディングメタルを形成する。

【0004】

ボンディングメタルは遮光性であるので、面積は制限される。狭い面積のボンディングメタル層を用いると電流集中が生じる。電流集中を緩和するためにボンディングメタルに対向するp型層表面に酸化シリコン等の絶縁膜を配置することが知られている。

【0005】

特開2007−180504号公報は、酸化シリコン等の絶縁膜は高い光吸収率を有し、実質的な発光効率を低下させる可能性が大きいと指摘し、ボンディングメタルと対向するp型層乃至n型層に窒化物単結晶が損傷された高抵抗層を形成することを提案する。

【0006】

例えば、p型窒化物半導体層上に開口を有するマスクを形成し、プラズマを利用して開口に露出した単結晶を故意に損傷させ、高抵抗領域を形成する。プラズマは、不要な反応を防止するために、不活性ガスプラズマを利用することが好ましく、このような不活性ガスとして、Ar、He、N2、CF4及びH2が使用できる;高抵抗領域の電極との接触抵抗は10−2Ωcm2以上となるように形成する;高抵抗領域の厚さは活性層まで損傷されないようにp型窒化物半導体層の厚さより薄いことが好ましく、より好ましくは10〜1000Å範囲の厚さに形成する、10Å未満の場合には十分な電流遮断効果を期待し難く、1000Åを超えると追加的な電流遮断効果なしにプラズマ処理工程の時間が無駄に消耗される、と指摘する。

【先行技術文献】

【特許文献】

【0007】

【特許文献1】特開2007−180504号公報

【発明の概要】

【発明が解決しようとする課題】

【0008】

ボンディングメタルと対向する領域に、接触抵抗10−2Ωcm2以上の高抵抗領域と低抵抗領域が隣接して形成されると、境界部に電流集中が生じる。

【課題を解決するための手段】

【0009】

実施例の1観点によれば、窒化物半導体発光素子は、

基板と、

前記基板上に配置され、p型層、活性層、n型層を含む窒化物半導体積層と、

前記p型層と前記基板との間に形成されたp側電極と、

前記n型層上の限定された領域に形成されたn側電極と、

前記n側電極に対向する領域を含んで、前記p型層内、または前記p型層表面に形成され、実質的に電流を流さない高抵抗領域と、

前記高抵抗領域外側の前記p型層に形成され、前記p側電極との間に電流を流す低抵抗領域と、

前記高抵抗領域と前記低抵抗領域の間に形成され、制限された電流を流すグレーデッド領域と、

を有する。

【0010】

実施例の他の観点によれば、窒化物半導体発光素子の製造方法は、

(a)サファイア基板上に窒化物半導体のn型層、活性層、p型層を成長する工程と、

(b)前記p型層表面のn側電極領域を含む領域に実質的に電流を遮断する高抵抗領域を形成し、その周囲に電流を制限するグレーデッド領域を形成する工程と、

(c)前記p型層表面にp側電極を形成する工程と、

(d)前記p側電極上に支持基板を接合する工程と、

(e)前記サファイア基板を除去する工程と、

(f)露出した前記n型層の前記n側電極領域上に面積を制限したn側電極を形成する工程と、

を含む。

【図面の簡単な説明】

【0011】

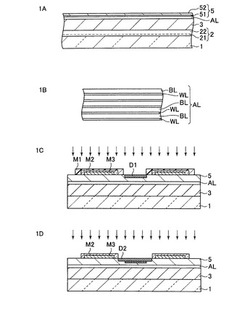

【図1−1】と、

【図1−2】と、

【図1−3】図1A〜1Mは、第1の実施例による窒化物半導体発光素子の製造方法を示す基板の断面図である。

【図2】図2A−2Cは、第2の実施例による窒化物半導体発光素子の製造方法を示す基板の断面図である。

【図3】図3A−3Cは、第3の実施例による窒化物半導体発光素子の製造方法を示す基板の断面図である。

【図4】図4A−4Fは、第4の実施例による窒化物半導体発光素子の製造方法を示す基板の断面図である。

【図5】図5A,5Bは窒化物半導体発光素子の平面図、図5C、5Dは高抵抗領域を設けた窒化物半導体発光素子の断面図である。

【発明を実施するための形態】

【0012】

図5Aは、大出力発光ダイオードの例を示す平面図である。角を丸めた1000μm×1000μm程度の正方形チップ40の表面に4本の横方向n側電極50を並べ、両端を2本の縦方向n側電極50で接続し、右側の上下角部にボンディングパッド60を形成している。車両用灯具等の用途に適する。n側電極50,60の面積は、全表面積の例えば約5%程度である。

【0013】

図5Bは、やや小型の発光ダイオードの例を示す平面図である。角を丸めた、横500μm、縦300μm程度の矩形チップ40の表面の上下方向中央部に横方向のn側電極50が形成され、その中央部上にボンディングパッド60が形成されている。一般的な照明用途に用いられる。n側電極50の面積は、全表面積の例えば約16%程度である。

【0014】

図5Cは電極を含む部分の断面図である。支持基板SS上にp型層5、活性層AL、n型層3が積層されたチップ40の上面にn側電極50が形成されている。n側電極50は遮光性であり、活性層で発光した光がn側電極に入射すると、透過できず、光取り出し効率を劣化させる。無効電力を低減するため、ほぼn側電極をカバーする形状の高抵抗領域70を形成することが望まれる。p型層5にn側電極50の直下の領域をカバーする形状の高抵抗領域70を形成し、その周囲はオーミックコンタクト領域80とすると、境界部90に電流集中が生じる。

【0015】

図5Dに示すように、本発明者は、n側電極に対応する形状の高抵抗領域70で電流を遮断するのみでなく、その周囲に電流密度を制限するグレーデッド領域75を形成し、高抵抗領域70の境界部における電流集中を緩和することを提案する。

【0016】

図1A−1Mを参照して、第1の実施例による半導体発光素子の製造方法を説明する。

【0017】

図1Aに示すように、c面サファイア基板1をMOCVD装置に投入し、水素雰囲気中で1000℃、10分の加熱(サーマルクリーニング)を行い、約500℃で、トリメチルガリウム(TMG)10.4μmol/min、アンモニアNH3 3.3LMを3分間供給してGaN低温バッファ層21を形成し、1000℃まで昇温して30秒間保持することにより低温バッファ層21を結晶化させる。温度1000℃のまま、TMG45μmol/min、NH3 4.4LMを20分間供給し下地GaN層22を約1μm形成する。なお、LMは、分当たりリットル(標準状態)の流量を表すものとする。

【0018】

温度1000℃でTMG45μmol/min、NH3 4.4LM、SiH42.7×10−9μmol/minを120分間供給し、Siドープのn型GaN層3を約7μm成長させる。温度を約700℃に降温し、活性層ALを成長する。活性層として多重量子井戸構造を形成する。

【0019】

図1Bに示すように、InGaNのウェル層WL/GaNのバリア層BLを1周期として5周期成長を行う。TMG3.6μmol/min、トリメチルインジウム(TMI)10μmol/min、NH34.4LMを33秒供給し、膜厚約2.2nmのInGaN井戸層WLを成長し、TMG3.6μmol/min、NH34.4LMを320秒供給し、膜厚約15nmのGaN障壁層BLを成長する。5周期分繰り返す。

【0020】

図1Aに戻り、温度を870℃まで上げ、TMG8.1μmol/min、トリメチルアルミニウム(TMA)7.5μmol/min、NH34.4LM、CP2Mg(ビスシクロペンタディエルマグネシウム)2.9×10−7μmol/minを5分間供給し、Mgドープのp型AlGaNクラッド層51を約40nmを成長する。同じ温度でTMG18μmol/min、NH3 4.4LM、CP2Mg2.9×10−7μmol/minを7分間供給しMgドープのp型GaN層52を約150nmを成長する。p型層51とp型層52を合わせてp型層5と呼ぶ。発光ダイオード用の化合物半導体積層が形成される。

【0021】

図1C〜図1Fは、1チップ分の工程を示す。図面上左右両端の領域は別チップとし、中央部のみに工程の変化を図示するが、実際には複数のチップに対して同時に工程が進んでいるものである。

【0022】

図1Cに示すように、p型層5の上に3重マスクM1,M2,M3を形成する。外側マスクM1はレジスト材料で形成され、後に形成するn側電極に対応する領域を含む開口を囲み、中間マスクM2を覆う形状を有する。中間マスクM2は酸化シリコンで形成され、外側マスクM1より拡げられた開口を有し、内側マスクM3を覆う形状を有する。内側マスクM3は、メタルで形成され、さらに拡げられた開口を有する。

【0023】

外側マスクM1の開口に露出したp型層5にプラズマを照射し、単結晶性を破壊するプラズマ処理を行う。プラズマは、Ar,He,N2,等の半導体層に対して不活性なガスのプラズマが好ましい。第1プラズマ処理領域D1が形成される。

【0024】

図1Dに示すように、外側マスクM1をアセトン等のレジストリムーバで除去し、中間マスクM2を露出する。中間マスクM2の開口内に露出したp型層5に対し、先のプラズマ処理と同等のガスを用い、程度を弱めたプラズマ処理を行う。新たに第2プラズマ処理領域D2が形成される。

【0025】

図1Eに示すように、中間マスクM2をバッファード弗酸で除去し、メタル内側マスクM3を露出する。内側マスクM3の開口内に露出したp型層5に対し、先のプラズマ処理と同等のガスを用い、さらに程度を弱めたプラズマ処理を行う。新たに第3プラズマ処理領域D3が形成される。

【0026】

図1Fに示すように、メタル内側マスクM3を酸等で除去する。プラズマダメージを受けていない低抵抗領域GCが露出する。低抵抗領域GCの接触抵抗は例えば、1×10−5Ωcm2〜1×10−3Ωcm2程度である。

【0027】

第1プラズマ処理領域D1は、第2、第3のプラズマ処理も受ける。第1プラズマ処理領域の接触抵抗が1×10−2Ωcm2以上になるようにする。実質的に電流を流さない高抵抗領域D1が形成される。

【0028】

第2プラズマ処理領域D2は第3のプラズマ処理も受ける。第2プラズマ処理領域の接触抵抗が、例えば5×10−3Ωcm2以上、10×10−3Ωcm2未満になるようにする。弱い電流は流せる第1グレーデッド領域D2が形成される。この第1グレーデッド領域D2は、高抵抗領域D1から5μm以上の幅を持って設けられることが好ましい。

【0029】

第3プラズマ処理領域D3は、第3のプラズマ処理のみを受ける。第3プラズマ処理領域の接触抵抗が、例えば1×10−3Ωcm2以上、5×10−3Ωcm2未満になるようにする。第1グレーデッド領域D2より強い電流を流せる第2グレーデッド領域D3が形成される。この第2グレーデッド領域D3は、第1グレーデッド領域D2から5μm以上の幅を持って設けられることが好ましい。低抵抗領域GCの電流密度を100%とすると、内側の第2グレーデッド領域D3の電流密度は50%〜90%程度、その内側の第1グレーデッド領域の電流密度は10%〜40%程度、更に内部の高抵抗領域(第1プラズマ処理領域)の電流密度は0%〜1%程度とするのが好ましい。

【0030】

なお、マスクM1,M2,M3のマスク材料とその層構成は、例示したものに限らない。但し、1つ内側のマスク材料とは、除去するための薬液が異なるものとなるように選択される。

【0031】

以下、第1プラズマ処理領域D1、第2プラズマ処理領域D2、第3プラズマ処理領域D3をまとめて、プラズマ処理領域Dとして図示する。

【0032】

図1Gに示すように、p型層5の上にp側電極7を形成する。例えば、電極形成領域を開口とするレジストマスクを形成し、Pt層1nm/Ag層150nm/Ti層100nm/Pt層100nm/Au層200nmをスパッタリングで積層し、レジストマスク上の金属層はリフトオフして除去する。厚さ1nmのPt層は透明電極として機能し、次の厚さ150nmのAg層は反射電極として機能する。

【0033】

図1Hに示すように、各チップ領域を囲むストリート8をエッチングする。例えば、ストリート部が露出するレジストマスクを形成し、Cl2プラズマを用いた反応性イオンエッチング(RIE)により、サファイア基板1が露出するまで半導体層のエッチングを行なう。

【0034】

図1Iに示すように、半導体チップ側面と上面のp側電極7周囲を覆う酸化シリコン膜9を形成する。例えば、酸化シリコン膜を形成しない領域を覆うレジストマスクを形成し、酸化シリコン膜をスパッタリングで堆積し、レジストマスク上の酸化シリコン膜は、リフトオフで除去する。別法として、酸化シリコン膜を形成した後、レジストマスクを形成し、露出部分をエッチングすることもできる。

【0035】

図1Jに示すように、表面にAuSn層またはAu層を有するシリコン基板SSをp側電極7に共晶により接合する。

【0036】

図1Kに示すように、ウエハを裏返してサファイア基板1を露出させ、波長248nmのKrFエキシマレーザ光を照射してサファイア基板をレーザリフトオフ(LLO)により剥離する。例えば、レーザパワーは約800mJ/cm2とする。

【0037】

図1Lに示すように、露出したn型層3の表面上にn側電極10を形成する。例えば、電極形成領域に開口を有するレジストマスクを形成し、Ti層1nm/Al層200nm/Ti層100nm/Pt層200nm/Au層3000nmを電子ビーム蒸着し、不要部の金属層はリフトオフで除去する。

【0038】

図1Mに示すように、各チップに分離する。例えばレーザスクライブによってストリートの支持基板SSを切断する。ダイヤモンドカッタでスクライブすることもできる。

【0039】

プラズマ処理領域Dは、図1Fに示すように、第1プラズマ処理領域D1、第2プラズマ処理領域D2、第3プラズマ処理領域D3で構成され、外側から徐々に電流を減衰させる構造となっている。高抵抗領域と低抵抗領域との間にグレーデッド領域を設けたことにより電流集中が緩和される。

【0040】

なお、窒化物半導体発光素子の構造は種々変更可能である。例えば多重量子井戸構造の変わりに、ダブルへテロ構造等を用いることもできる。

【0041】

図2A−2Cを参照して、第2の実施例による半導体発光素子の製造方法を説明する。図2A−2Cは基板の断面図を示す。第1の実施例同様に、図1A,1Bに示す半導体積層の形成を行なう。

【0042】

図2Aに示すように、p型半導体層5の上にn側電極に対応する領域を包含する開口を有する第1のレジストマスクRM1を形成し、開口内に露出したp型半導体層5に単結晶性を破壊するプラズマ処理を行う。プラズマ処理は図1Cに示すプラズマ処理同様である。第1プラズマ処理領域D1が形成される。

【0043】

図2Bに示すように、第1のレジストマスクRM1をレジストリムーバで除去し、より広い開口を有する第2のレジストマスクRM2を形成する。レジストマスクRM2の開口内に露出したp型半導体層5に程度を弱くしたプラズマ処理を行う。新たに第2プラズマ処理領域D2が形成される。この第2プラズマ処理領域D2は、第1プラズマ処理領域D1から5μm以上の幅を持って設けられることが好ましい。

【0044】

図2Cに示すように、第2のレジストマスクRM2はレジストリムーバで除去する。

【0045】

第1プラズマ処理領域D1は、第2のプラズマ処理も受ける。第1プラズマ処理領域の接触抵抗が1×10−2Ωcm2以上になるようにする。実質的に電流を流さない高抵抗領域D1が形成される。

【0046】

第2プラズマ処理領域の接触抵抗が、例えば5×10−3Ωcm2〜10×10−3Ωcm2になるようにする。弱い電流は流せるグレーデッド領域D2が形成される。

【0047】

第1のプラズマ処理と第2のプラズマ処理の順序は入れ替えてもよい。さらに広い開口を有する第3のレジストマスクを形成し、さらに程度を弱めた第3のプラズマ処理を行ってもよい。この場合は、3回のプラズマ処理の順序は任意である。

【0048】

その後、第1の実施例の図1G−1Mと同様の工程を行って、発光ダイオードチップを形成する。

【0049】

図3A−3Cを参照して、第3の実施例による半導体発光素子の製造方法を説明する。図3A−3Cは基板の断面図を示す。第1の実施例同様に、図1A,1Bに示す半導体積層の形成を行なう。

【0050】

図3Aに示すように、p型半導体層5の上にn側電極に対応する領域を包含するパターンの絶縁層DLを形成する。例えばCVDで酸化シリコン膜を形成し、レジストパターンを用いて不要部をエッチングする。絶縁層DLの外側に開口を残すように例えばレジストの第1のマスクM1,メタルの第2のマスクM2の複合構造を形成する。第1のマスクM1は第2のマスクを覆い、絶縁層の外側に第1の環状開口を画定する。第2のマスクM2は第1の環状開口より広い第2の環状開口を画定する。絶縁層DL,第1のマスクM1の画定する第1の環状開口にプラズマ処理を行って、ダメージ領域D2を形成する。

【0051】

図3Bに示すように、第1のマスクM1をレジストリムーバ等で除去し、絶縁層DLと第2のマスクM2が画定する第2の環状開口に程度を弱めたプラズマ処理を行って、ダメージ領域D3を形成する。

【0052】

図3Cに示すように、メタルマスクM2を酸化シリコンは溶解しない酸等で除去する。酸化シリコン等の絶縁層DLは残る。その後、第1の実施例の図1G−1Mと同様の工程を行って、発光ダイオードチップを形成する。

【0053】

絶縁層DLの領域は、完全に電流を遮断する。その周囲のダメージ領域D2は弱い電流を流す。その外側のダメージ領域D3は低抵抗領域より弱いが、ダメージ領域D2より強い電流を流す。第1の実施例同様、高抵抗領域の外側に2段のグレーデッド領域が形成される。

【0054】

第3の実施例においても、第1の実施例同様に、ダメージ領域D2の接触抵抗は5×10−3Ωcm2以上、10×10−3Ωcm2未満であり、ダメージ領域D3の接触抵抗は1×10−3Ωcm2以上、5×10−3Ωcm2未満となるよう形成される。また、ダメージ領域D2は、絶縁層DLから5μm以上、ダメージ領域D3はダメージ領域D2から5μm以上の幅を持って設けられることが好ましい。

【0055】

以上の実施例においては2段または3段のグレーデッド領域が形成された。連続的に変化するグレーデッド領域を形成することも可能である。

【0056】

図4Aに示すように、下地上にフォトレジスト層を塗布し、開口を有するパターンを露光現像して、フォトレジストパターンPRを形成する。開口に面するフォトレジストパターンの側面は下地表面に対してほぼ垂直である。

【0057】

図4Bに示すように、例えばレジストが軟化する温度、AZ6130の場合135℃程度で5分ほどポストベークを行なう。レジストパターンの端部が流れてなだらかな側面が形成される。

【0058】

図4Cは、別の方法を示す。フォトレジスト層PRに対して透過率Tが連続的に変化しているマスクMを用いて露光を行なう。連続的に変化する露光が行なわれ、現像すると、厚さが連続的に変化するレジストパターンが得られる。

【0059】

図4Dに示すように、n側電極に対向する領域を包含する開口を有し、厚さがなだらかに変化するレジストパターンVRを形成する。

【0060】

図4Eに示すように、レジストパターンVRを介してプラズマ処理を行う。プラズマ処理は徐々にレジストパターンVRを消費する。レジストパターンの画定する開口が次第に拡がる。プラズマ処理の終了後、レジストパターンVRは除去する。

【0061】

図4Fに示すように、n電極に対向する領域を包含する領域に強くダメージを受けた領域Dが形成され、その外側に徐々にダメージが弱くなるグレーデッド領域VDが形成される。その後、第1の実施例の図1G−1Mと同様の工程を行って、発光ダイオードチップを形成する。

【0062】

図4D〜4Fで説明した実施例においても、第1の実施例同様に、領域Dは1×10−2Ωcm2であり、グレーデッド領域VDは5×10−3Ωcm2以上、10×10−3Ωcm2未満となる領域と、1×10−3Ωcm2以上、5×10−3Ωcm2未満となる領域とが形成される。5×10−3Ωcm2以上、10×10−3Ωcm2未満となる領域と、1×10−3Ωcm2以上、5×10−3Ωcm2未満となる領域とは、それぞれ5μm以上の幅を持って設けられることが好ましい。

【0063】

以上、n側電極と対向する領域を含む領域に形成され実質的に電流を流さない高抵抗領域と、高抵抗領域の外側で積極的に電流を流す低抵抗領域と、高抵抗領域と低抵抗領域の間に形成され、制限された電流を流すグレーデッド領域を設ける実施例を説明した。

【0064】

図5Aに示す大出力型の素子の場合、n側電極の面積は半導体層面積の約5%であり、高抵抗領域の面積はn側電極の対向領域を含んで、半導体層面積の約5%〜10%であり、グレーデッド領域の面積は約5%〜10%が好ましい。高抵抗領域とグレーデッド領域の面積の和は、10%〜20%が好ましい。

【0065】

図5Bに示す一般用途用の素子の場合、n側電極の面積は半導体層面積の約16%であり、高抵抗領域の面積はn側電極の対向領域を含んで、半導体層面積の約16%〜32%であり、高抵抗領域とグレーデッド領域の面積の和は約32%〜50%が好ましい。

【0066】

いずれの場合も、グレーデッド領域の面積は高抵抗領域の面積の1/2〜2倍が好ましい。

【0067】

以上の実施例の説明における材料、数値は制限的なものではなく、種々変更可能である。例えばAlGaInN半導体層の組成は種々選択できる。その他、種々の変更、改良、組み合わせ等が可能なことは当業者に自明であろう。

【符号の説明】

【0068】

1 サファイア基板、

3 n型層、

AL 活性層、

5 p型層、

D1 高抵抗領域、

D2、D3 グレーデッド領域、

7 p側電極、

SS 支持基板、

10 n側電極。

【技術分野】

【0001】

本発明の実施例は、窒化物半導体発光素子及びその製造方法に関する。

【背景技術】

【0002】

GaN系窒化物半導体発光素子は、サファイア基板上にn型層、発光層、p型層の窒化物半導体層を成長して作成することが多い。例えば、p型層と発光層の一部をエッチングしてn型層を露出し、p型層、n型層表面に電極を形成する。III族元素として、GaにAl,Inを添加することによってバンドギャップを調整することができる。AlGaInNをIII族窒化物ないし窒化物半導体と呼ぶ。

【0003】

サファイアは絶縁物であり、熱伝導率は比較的低い。高出力発光素子を形成するためには熱伝導(放熱性)を改良することが望ましい。サファイア基板上にIII族窒化物半導体層を成長した後、p型層表面に電極を形成し、その上にSi等の熱伝導性のよい支持基板を結合した後、サファイア基板側からKrF等のエキシマレーザを照射してサファイア基板を除去するレーザリフトオフが行なわれる。Si支持基板は、例えば共晶によりp側電極に接合する。サファイア基板を除去して、露出したn型半導体層の上に、必要に応じて透明電極を介して、ボンディングメタルを形成する。

【0004】

ボンディングメタルは遮光性であるので、面積は制限される。狭い面積のボンディングメタル層を用いると電流集中が生じる。電流集中を緩和するためにボンディングメタルに対向するp型層表面に酸化シリコン等の絶縁膜を配置することが知られている。

【0005】

特開2007−180504号公報は、酸化シリコン等の絶縁膜は高い光吸収率を有し、実質的な発光効率を低下させる可能性が大きいと指摘し、ボンディングメタルと対向するp型層乃至n型層に窒化物単結晶が損傷された高抵抗層を形成することを提案する。

【0006】

例えば、p型窒化物半導体層上に開口を有するマスクを形成し、プラズマを利用して開口に露出した単結晶を故意に損傷させ、高抵抗領域を形成する。プラズマは、不要な反応を防止するために、不活性ガスプラズマを利用することが好ましく、このような不活性ガスとして、Ar、He、N2、CF4及びH2が使用できる;高抵抗領域の電極との接触抵抗は10−2Ωcm2以上となるように形成する;高抵抗領域の厚さは活性層まで損傷されないようにp型窒化物半導体層の厚さより薄いことが好ましく、より好ましくは10〜1000Å範囲の厚さに形成する、10Å未満の場合には十分な電流遮断効果を期待し難く、1000Åを超えると追加的な電流遮断効果なしにプラズマ処理工程の時間が無駄に消耗される、と指摘する。

【先行技術文献】

【特許文献】

【0007】

【特許文献1】特開2007−180504号公報

【発明の概要】

【発明が解決しようとする課題】

【0008】

ボンディングメタルと対向する領域に、接触抵抗10−2Ωcm2以上の高抵抗領域と低抵抗領域が隣接して形成されると、境界部に電流集中が生じる。

【課題を解決するための手段】

【0009】

実施例の1観点によれば、窒化物半導体発光素子は、

基板と、

前記基板上に配置され、p型層、活性層、n型層を含む窒化物半導体積層と、

前記p型層と前記基板との間に形成されたp側電極と、

前記n型層上の限定された領域に形成されたn側電極と、

前記n側電極に対向する領域を含んで、前記p型層内、または前記p型層表面に形成され、実質的に電流を流さない高抵抗領域と、

前記高抵抗領域外側の前記p型層に形成され、前記p側電極との間に電流を流す低抵抗領域と、

前記高抵抗領域と前記低抵抗領域の間に形成され、制限された電流を流すグレーデッド領域と、

を有する。

【0010】

実施例の他の観点によれば、窒化物半導体発光素子の製造方法は、

(a)サファイア基板上に窒化物半導体のn型層、活性層、p型層を成長する工程と、

(b)前記p型層表面のn側電極領域を含む領域に実質的に電流を遮断する高抵抗領域を形成し、その周囲に電流を制限するグレーデッド領域を形成する工程と、

(c)前記p型層表面にp側電極を形成する工程と、

(d)前記p側電極上に支持基板を接合する工程と、

(e)前記サファイア基板を除去する工程と、

(f)露出した前記n型層の前記n側電極領域上に面積を制限したn側電極を形成する工程と、

を含む。

【図面の簡単な説明】

【0011】

【図1−1】と、

【図1−2】と、

【図1−3】図1A〜1Mは、第1の実施例による窒化物半導体発光素子の製造方法を示す基板の断面図である。

【図2】図2A−2Cは、第2の実施例による窒化物半導体発光素子の製造方法を示す基板の断面図である。

【図3】図3A−3Cは、第3の実施例による窒化物半導体発光素子の製造方法を示す基板の断面図である。

【図4】図4A−4Fは、第4の実施例による窒化物半導体発光素子の製造方法を示す基板の断面図である。

【図5】図5A,5Bは窒化物半導体発光素子の平面図、図5C、5Dは高抵抗領域を設けた窒化物半導体発光素子の断面図である。

【発明を実施するための形態】

【0012】

図5Aは、大出力発光ダイオードの例を示す平面図である。角を丸めた1000μm×1000μm程度の正方形チップ40の表面に4本の横方向n側電極50を並べ、両端を2本の縦方向n側電極50で接続し、右側の上下角部にボンディングパッド60を形成している。車両用灯具等の用途に適する。n側電極50,60の面積は、全表面積の例えば約5%程度である。

【0013】

図5Bは、やや小型の発光ダイオードの例を示す平面図である。角を丸めた、横500μm、縦300μm程度の矩形チップ40の表面の上下方向中央部に横方向のn側電極50が形成され、その中央部上にボンディングパッド60が形成されている。一般的な照明用途に用いられる。n側電極50の面積は、全表面積の例えば約16%程度である。

【0014】

図5Cは電極を含む部分の断面図である。支持基板SS上にp型層5、活性層AL、n型層3が積層されたチップ40の上面にn側電極50が形成されている。n側電極50は遮光性であり、活性層で発光した光がn側電極に入射すると、透過できず、光取り出し効率を劣化させる。無効電力を低減するため、ほぼn側電極をカバーする形状の高抵抗領域70を形成することが望まれる。p型層5にn側電極50の直下の領域をカバーする形状の高抵抗領域70を形成し、その周囲はオーミックコンタクト領域80とすると、境界部90に電流集中が生じる。

【0015】

図5Dに示すように、本発明者は、n側電極に対応する形状の高抵抗領域70で電流を遮断するのみでなく、その周囲に電流密度を制限するグレーデッド領域75を形成し、高抵抗領域70の境界部における電流集中を緩和することを提案する。

【0016】

図1A−1Mを参照して、第1の実施例による半導体発光素子の製造方法を説明する。

【0017】

図1Aに示すように、c面サファイア基板1をMOCVD装置に投入し、水素雰囲気中で1000℃、10分の加熱(サーマルクリーニング)を行い、約500℃で、トリメチルガリウム(TMG)10.4μmol/min、アンモニアNH3 3.3LMを3分間供給してGaN低温バッファ層21を形成し、1000℃まで昇温して30秒間保持することにより低温バッファ層21を結晶化させる。温度1000℃のまま、TMG45μmol/min、NH3 4.4LMを20分間供給し下地GaN層22を約1μm形成する。なお、LMは、分当たりリットル(標準状態)の流量を表すものとする。

【0018】

温度1000℃でTMG45μmol/min、NH3 4.4LM、SiH42.7×10−9μmol/minを120分間供給し、Siドープのn型GaN層3を約7μm成長させる。温度を約700℃に降温し、活性層ALを成長する。活性層として多重量子井戸構造を形成する。

【0019】

図1Bに示すように、InGaNのウェル層WL/GaNのバリア層BLを1周期として5周期成長を行う。TMG3.6μmol/min、トリメチルインジウム(TMI)10μmol/min、NH34.4LMを33秒供給し、膜厚約2.2nmのInGaN井戸層WLを成長し、TMG3.6μmol/min、NH34.4LMを320秒供給し、膜厚約15nmのGaN障壁層BLを成長する。5周期分繰り返す。

【0020】

図1Aに戻り、温度を870℃まで上げ、TMG8.1μmol/min、トリメチルアルミニウム(TMA)7.5μmol/min、NH34.4LM、CP2Mg(ビスシクロペンタディエルマグネシウム)2.9×10−7μmol/minを5分間供給し、Mgドープのp型AlGaNクラッド層51を約40nmを成長する。同じ温度でTMG18μmol/min、NH3 4.4LM、CP2Mg2.9×10−7μmol/minを7分間供給しMgドープのp型GaN層52を約150nmを成長する。p型層51とp型層52を合わせてp型層5と呼ぶ。発光ダイオード用の化合物半導体積層が形成される。

【0021】

図1C〜図1Fは、1チップ分の工程を示す。図面上左右両端の領域は別チップとし、中央部のみに工程の変化を図示するが、実際には複数のチップに対して同時に工程が進んでいるものである。

【0022】

図1Cに示すように、p型層5の上に3重マスクM1,M2,M3を形成する。外側マスクM1はレジスト材料で形成され、後に形成するn側電極に対応する領域を含む開口を囲み、中間マスクM2を覆う形状を有する。中間マスクM2は酸化シリコンで形成され、外側マスクM1より拡げられた開口を有し、内側マスクM3を覆う形状を有する。内側マスクM3は、メタルで形成され、さらに拡げられた開口を有する。

【0023】

外側マスクM1の開口に露出したp型層5にプラズマを照射し、単結晶性を破壊するプラズマ処理を行う。プラズマは、Ar,He,N2,等の半導体層に対して不活性なガスのプラズマが好ましい。第1プラズマ処理領域D1が形成される。

【0024】

図1Dに示すように、外側マスクM1をアセトン等のレジストリムーバで除去し、中間マスクM2を露出する。中間マスクM2の開口内に露出したp型層5に対し、先のプラズマ処理と同等のガスを用い、程度を弱めたプラズマ処理を行う。新たに第2プラズマ処理領域D2が形成される。

【0025】

図1Eに示すように、中間マスクM2をバッファード弗酸で除去し、メタル内側マスクM3を露出する。内側マスクM3の開口内に露出したp型層5に対し、先のプラズマ処理と同等のガスを用い、さらに程度を弱めたプラズマ処理を行う。新たに第3プラズマ処理領域D3が形成される。

【0026】

図1Fに示すように、メタル内側マスクM3を酸等で除去する。プラズマダメージを受けていない低抵抗領域GCが露出する。低抵抗領域GCの接触抵抗は例えば、1×10−5Ωcm2〜1×10−3Ωcm2程度である。

【0027】

第1プラズマ処理領域D1は、第2、第3のプラズマ処理も受ける。第1プラズマ処理領域の接触抵抗が1×10−2Ωcm2以上になるようにする。実質的に電流を流さない高抵抗領域D1が形成される。

【0028】

第2プラズマ処理領域D2は第3のプラズマ処理も受ける。第2プラズマ処理領域の接触抵抗が、例えば5×10−3Ωcm2以上、10×10−3Ωcm2未満になるようにする。弱い電流は流せる第1グレーデッド領域D2が形成される。この第1グレーデッド領域D2は、高抵抗領域D1から5μm以上の幅を持って設けられることが好ましい。

【0029】

第3プラズマ処理領域D3は、第3のプラズマ処理のみを受ける。第3プラズマ処理領域の接触抵抗が、例えば1×10−3Ωcm2以上、5×10−3Ωcm2未満になるようにする。第1グレーデッド領域D2より強い電流を流せる第2グレーデッド領域D3が形成される。この第2グレーデッド領域D3は、第1グレーデッド領域D2から5μm以上の幅を持って設けられることが好ましい。低抵抗領域GCの電流密度を100%とすると、内側の第2グレーデッド領域D3の電流密度は50%〜90%程度、その内側の第1グレーデッド領域の電流密度は10%〜40%程度、更に内部の高抵抗領域(第1プラズマ処理領域)の電流密度は0%〜1%程度とするのが好ましい。

【0030】

なお、マスクM1,M2,M3のマスク材料とその層構成は、例示したものに限らない。但し、1つ内側のマスク材料とは、除去するための薬液が異なるものとなるように選択される。

【0031】

以下、第1プラズマ処理領域D1、第2プラズマ処理領域D2、第3プラズマ処理領域D3をまとめて、プラズマ処理領域Dとして図示する。

【0032】

図1Gに示すように、p型層5の上にp側電極7を形成する。例えば、電極形成領域を開口とするレジストマスクを形成し、Pt層1nm/Ag層150nm/Ti層100nm/Pt層100nm/Au層200nmをスパッタリングで積層し、レジストマスク上の金属層はリフトオフして除去する。厚さ1nmのPt層は透明電極として機能し、次の厚さ150nmのAg層は反射電極として機能する。

【0033】

図1Hに示すように、各チップ領域を囲むストリート8をエッチングする。例えば、ストリート部が露出するレジストマスクを形成し、Cl2プラズマを用いた反応性イオンエッチング(RIE)により、サファイア基板1が露出するまで半導体層のエッチングを行なう。

【0034】

図1Iに示すように、半導体チップ側面と上面のp側電極7周囲を覆う酸化シリコン膜9を形成する。例えば、酸化シリコン膜を形成しない領域を覆うレジストマスクを形成し、酸化シリコン膜をスパッタリングで堆積し、レジストマスク上の酸化シリコン膜は、リフトオフで除去する。別法として、酸化シリコン膜を形成した後、レジストマスクを形成し、露出部分をエッチングすることもできる。

【0035】

図1Jに示すように、表面にAuSn層またはAu層を有するシリコン基板SSをp側電極7に共晶により接合する。

【0036】

図1Kに示すように、ウエハを裏返してサファイア基板1を露出させ、波長248nmのKrFエキシマレーザ光を照射してサファイア基板をレーザリフトオフ(LLO)により剥離する。例えば、レーザパワーは約800mJ/cm2とする。

【0037】

図1Lに示すように、露出したn型層3の表面上にn側電極10を形成する。例えば、電極形成領域に開口を有するレジストマスクを形成し、Ti層1nm/Al層200nm/Ti層100nm/Pt層200nm/Au層3000nmを電子ビーム蒸着し、不要部の金属層はリフトオフで除去する。

【0038】

図1Mに示すように、各チップに分離する。例えばレーザスクライブによってストリートの支持基板SSを切断する。ダイヤモンドカッタでスクライブすることもできる。

【0039】

プラズマ処理領域Dは、図1Fに示すように、第1プラズマ処理領域D1、第2プラズマ処理領域D2、第3プラズマ処理領域D3で構成され、外側から徐々に電流を減衰させる構造となっている。高抵抗領域と低抵抗領域との間にグレーデッド領域を設けたことにより電流集中が緩和される。

【0040】

なお、窒化物半導体発光素子の構造は種々変更可能である。例えば多重量子井戸構造の変わりに、ダブルへテロ構造等を用いることもできる。

【0041】

図2A−2Cを参照して、第2の実施例による半導体発光素子の製造方法を説明する。図2A−2Cは基板の断面図を示す。第1の実施例同様に、図1A,1Bに示す半導体積層の形成を行なう。

【0042】

図2Aに示すように、p型半導体層5の上にn側電極に対応する領域を包含する開口を有する第1のレジストマスクRM1を形成し、開口内に露出したp型半導体層5に単結晶性を破壊するプラズマ処理を行う。プラズマ処理は図1Cに示すプラズマ処理同様である。第1プラズマ処理領域D1が形成される。

【0043】

図2Bに示すように、第1のレジストマスクRM1をレジストリムーバで除去し、より広い開口を有する第2のレジストマスクRM2を形成する。レジストマスクRM2の開口内に露出したp型半導体層5に程度を弱くしたプラズマ処理を行う。新たに第2プラズマ処理領域D2が形成される。この第2プラズマ処理領域D2は、第1プラズマ処理領域D1から5μm以上の幅を持って設けられることが好ましい。

【0044】

図2Cに示すように、第2のレジストマスクRM2はレジストリムーバで除去する。

【0045】

第1プラズマ処理領域D1は、第2のプラズマ処理も受ける。第1プラズマ処理領域の接触抵抗が1×10−2Ωcm2以上になるようにする。実質的に電流を流さない高抵抗領域D1が形成される。

【0046】

第2プラズマ処理領域の接触抵抗が、例えば5×10−3Ωcm2〜10×10−3Ωcm2になるようにする。弱い電流は流せるグレーデッド領域D2が形成される。

【0047】

第1のプラズマ処理と第2のプラズマ処理の順序は入れ替えてもよい。さらに広い開口を有する第3のレジストマスクを形成し、さらに程度を弱めた第3のプラズマ処理を行ってもよい。この場合は、3回のプラズマ処理の順序は任意である。

【0048】

その後、第1の実施例の図1G−1Mと同様の工程を行って、発光ダイオードチップを形成する。

【0049】

図3A−3Cを参照して、第3の実施例による半導体発光素子の製造方法を説明する。図3A−3Cは基板の断面図を示す。第1の実施例同様に、図1A,1Bに示す半導体積層の形成を行なう。

【0050】

図3Aに示すように、p型半導体層5の上にn側電極に対応する領域を包含するパターンの絶縁層DLを形成する。例えばCVDで酸化シリコン膜を形成し、レジストパターンを用いて不要部をエッチングする。絶縁層DLの外側に開口を残すように例えばレジストの第1のマスクM1,メタルの第2のマスクM2の複合構造を形成する。第1のマスクM1は第2のマスクを覆い、絶縁層の外側に第1の環状開口を画定する。第2のマスクM2は第1の環状開口より広い第2の環状開口を画定する。絶縁層DL,第1のマスクM1の画定する第1の環状開口にプラズマ処理を行って、ダメージ領域D2を形成する。

【0051】

図3Bに示すように、第1のマスクM1をレジストリムーバ等で除去し、絶縁層DLと第2のマスクM2が画定する第2の環状開口に程度を弱めたプラズマ処理を行って、ダメージ領域D3を形成する。

【0052】

図3Cに示すように、メタルマスクM2を酸化シリコンは溶解しない酸等で除去する。酸化シリコン等の絶縁層DLは残る。その後、第1の実施例の図1G−1Mと同様の工程を行って、発光ダイオードチップを形成する。

【0053】

絶縁層DLの領域は、完全に電流を遮断する。その周囲のダメージ領域D2は弱い電流を流す。その外側のダメージ領域D3は低抵抗領域より弱いが、ダメージ領域D2より強い電流を流す。第1の実施例同様、高抵抗領域の外側に2段のグレーデッド領域が形成される。

【0054】

第3の実施例においても、第1の実施例同様に、ダメージ領域D2の接触抵抗は5×10−3Ωcm2以上、10×10−3Ωcm2未満であり、ダメージ領域D3の接触抵抗は1×10−3Ωcm2以上、5×10−3Ωcm2未満となるよう形成される。また、ダメージ領域D2は、絶縁層DLから5μm以上、ダメージ領域D3はダメージ領域D2から5μm以上の幅を持って設けられることが好ましい。

【0055】

以上の実施例においては2段または3段のグレーデッド領域が形成された。連続的に変化するグレーデッド領域を形成することも可能である。

【0056】

図4Aに示すように、下地上にフォトレジスト層を塗布し、開口を有するパターンを露光現像して、フォトレジストパターンPRを形成する。開口に面するフォトレジストパターンの側面は下地表面に対してほぼ垂直である。

【0057】

図4Bに示すように、例えばレジストが軟化する温度、AZ6130の場合135℃程度で5分ほどポストベークを行なう。レジストパターンの端部が流れてなだらかな側面が形成される。

【0058】

図4Cは、別の方法を示す。フォトレジスト層PRに対して透過率Tが連続的に変化しているマスクMを用いて露光を行なう。連続的に変化する露光が行なわれ、現像すると、厚さが連続的に変化するレジストパターンが得られる。

【0059】

図4Dに示すように、n側電極に対向する領域を包含する開口を有し、厚さがなだらかに変化するレジストパターンVRを形成する。

【0060】

図4Eに示すように、レジストパターンVRを介してプラズマ処理を行う。プラズマ処理は徐々にレジストパターンVRを消費する。レジストパターンの画定する開口が次第に拡がる。プラズマ処理の終了後、レジストパターンVRは除去する。

【0061】

図4Fに示すように、n電極に対向する領域を包含する領域に強くダメージを受けた領域Dが形成され、その外側に徐々にダメージが弱くなるグレーデッド領域VDが形成される。その後、第1の実施例の図1G−1Mと同様の工程を行って、発光ダイオードチップを形成する。

【0062】

図4D〜4Fで説明した実施例においても、第1の実施例同様に、領域Dは1×10−2Ωcm2であり、グレーデッド領域VDは5×10−3Ωcm2以上、10×10−3Ωcm2未満となる領域と、1×10−3Ωcm2以上、5×10−3Ωcm2未満となる領域とが形成される。5×10−3Ωcm2以上、10×10−3Ωcm2未満となる領域と、1×10−3Ωcm2以上、5×10−3Ωcm2未満となる領域とは、それぞれ5μm以上の幅を持って設けられることが好ましい。

【0063】

以上、n側電極と対向する領域を含む領域に形成され実質的に電流を流さない高抵抗領域と、高抵抗領域の外側で積極的に電流を流す低抵抗領域と、高抵抗領域と低抵抗領域の間に形成され、制限された電流を流すグレーデッド領域を設ける実施例を説明した。

【0064】

図5Aに示す大出力型の素子の場合、n側電極の面積は半導体層面積の約5%であり、高抵抗領域の面積はn側電極の対向領域を含んで、半導体層面積の約5%〜10%であり、グレーデッド領域の面積は約5%〜10%が好ましい。高抵抗領域とグレーデッド領域の面積の和は、10%〜20%が好ましい。

【0065】

図5Bに示す一般用途用の素子の場合、n側電極の面積は半導体層面積の約16%であり、高抵抗領域の面積はn側電極の対向領域を含んで、半導体層面積の約16%〜32%であり、高抵抗領域とグレーデッド領域の面積の和は約32%〜50%が好ましい。

【0066】

いずれの場合も、グレーデッド領域の面積は高抵抗領域の面積の1/2〜2倍が好ましい。

【0067】

以上の実施例の説明における材料、数値は制限的なものではなく、種々変更可能である。例えばAlGaInN半導体層の組成は種々選択できる。その他、種々の変更、改良、組み合わせ等が可能なことは当業者に自明であろう。

【符号の説明】

【0068】

1 サファイア基板、

3 n型層、

AL 活性層、

5 p型層、

D1 高抵抗領域、

D2、D3 グレーデッド領域、

7 p側電極、

SS 支持基板、

10 n側電極。

【特許請求の範囲】

【請求項1】

基板と、

前記基板上に配置され、p型層、活性層、n型層を含む窒化物半導体積層と、

前記p型層と前記基板との間に形成されたp側電極と、

前記n型層上の限定された領域に形成されたn側電極と、

前記n側電極に対向する領域を含んで、前記p型層内、または前記p型層表面に形成され、実質的に電流を流さない高抵抗領域と、

前記高抵抗領域外側の前記p型層に形成され、前記p側電極との間に電流を流す低抵抗領域と、

前記高抵抗領域と前記低抵抗領域の間に形成され、制限された電流を流すグレーデッド領域と、

を有する窒化物半導体発光素子。

【請求項2】

前記窒化物半導体積層が、AlGaInN系半導体層の積層である、請求項1記載の窒化物半導体発光素子。

【請求項3】

前記高抵抗領域は、結晶性を破壊された領域または絶縁物層を形成した領域である請求項1または2記載の窒化物半導体発光素子。

【請求項4】

前記グレーデッド領域は、結晶性を損なう処理を受けた領域である請求項1〜3のいずれか1項に記載の窒化物半導体発光素子。

【請求項5】

前記グレーデッド領域の面積は前記高抵抗領域の面積の1/2〜2倍である請求項1〜4のいずれか1項に記載の窒化物半導体発光素子。

【請求項6】

(a)サファイア基板上に窒化物半導体のn型層、活性層、p型層を成長する工程と、

(b)前記p型層表面のn側電極領域を含む領域に実質的に電流を遮断する高抵抗領域を形成し、その周囲に電流を制限するグレーデッド領域を形成する工程と、

(c)前記p型層表面にp側電極を形成する工程と、

(d)前記p側電極上に支持基板を接合する工程と、

(e)前記サファイア基板を剥離する工程と、

(f)露出した前記n型層の前記n側電極領域上に面積を制限したn側電極を形成する工程と、

を含む窒化物半導体発光素子の製造方法。

【請求項7】

前記工程(b)がプラズマ処理で前記p型層の選択された面積の結晶性を破壊する工程を含む請求項6記載の窒化物半導体発光素子の製造方法。

【請求項8】

前記工程(b)が複数のマスクを用いる請求項7記載の窒化物半導体発光素子の製造方法。

【請求項9】

前記工程(b)が厚さ分布を有するマスクを用いる請求項7記載の窒化物半導体発光素子の製造方法。

【請求項10】

前記工程(b)が絶縁層パターンの形成を含む請求項7記載の窒化物半導体発光素子の製造方法。

【請求項1】

基板と、

前記基板上に配置され、p型層、活性層、n型層を含む窒化物半導体積層と、

前記p型層と前記基板との間に形成されたp側電極と、

前記n型層上の限定された領域に形成されたn側電極と、

前記n側電極に対向する領域を含んで、前記p型層内、または前記p型層表面に形成され、実質的に電流を流さない高抵抗領域と、

前記高抵抗領域外側の前記p型層に形成され、前記p側電極との間に電流を流す低抵抗領域と、

前記高抵抗領域と前記低抵抗領域の間に形成され、制限された電流を流すグレーデッド領域と、

を有する窒化物半導体発光素子。

【請求項2】

前記窒化物半導体積層が、AlGaInN系半導体層の積層である、請求項1記載の窒化物半導体発光素子。

【請求項3】

前記高抵抗領域は、結晶性を破壊された領域または絶縁物層を形成した領域である請求項1または2記載の窒化物半導体発光素子。

【請求項4】

前記グレーデッド領域は、結晶性を損なう処理を受けた領域である請求項1〜3のいずれか1項に記載の窒化物半導体発光素子。

【請求項5】

前記グレーデッド領域の面積は前記高抵抗領域の面積の1/2〜2倍である請求項1〜4のいずれか1項に記載の窒化物半導体発光素子。

【請求項6】

(a)サファイア基板上に窒化物半導体のn型層、活性層、p型層を成長する工程と、

(b)前記p型層表面のn側電極領域を含む領域に実質的に電流を遮断する高抵抗領域を形成し、その周囲に電流を制限するグレーデッド領域を形成する工程と、

(c)前記p型層表面にp側電極を形成する工程と、

(d)前記p側電極上に支持基板を接合する工程と、

(e)前記サファイア基板を剥離する工程と、

(f)露出した前記n型層の前記n側電極領域上に面積を制限したn側電極を形成する工程と、

を含む窒化物半導体発光素子の製造方法。

【請求項7】

前記工程(b)がプラズマ処理で前記p型層の選択された面積の結晶性を破壊する工程を含む請求項6記載の窒化物半導体発光素子の製造方法。

【請求項8】

前記工程(b)が複数のマスクを用いる請求項7記載の窒化物半導体発光素子の製造方法。

【請求項9】

前記工程(b)が厚さ分布を有するマスクを用いる請求項7記載の窒化物半導体発光素子の製造方法。

【請求項10】

前記工程(b)が絶縁層パターンの形成を含む請求項7記載の窒化物半導体発光素子の製造方法。

【図1−1】

【図1−2】

【図1−3】

【図2】

【図3】

【図4】

【図5】

【図1−2】

【図1−3】

【図2】

【図3】

【図4】

【図5】

【公開番号】特開2013−102068(P2013−102068A)

【公開日】平成25年5月23日(2013.5.23)

【国際特許分類】

【出願番号】特願2011−245235(P2011−245235)

【出願日】平成23年11月9日(2011.11.9)

【出願人】(000002303)スタンレー電気株式会社 (2,684)

【Fターム(参考)】

【公開日】平成25年5月23日(2013.5.23)

【国際特許分類】

【出願日】平成23年11月9日(2011.11.9)

【出願人】(000002303)スタンレー電気株式会社 (2,684)

【Fターム(参考)】

[ Back to top ]