窒化物半導体素子及びその製造方法

【課題】オン抵抗を低め、高電流で動作する半導体素子及び製造方法を提供する。

【解決手段】基板10上部に配設され、内部に2次元電子ガスチャネルを形成する窒化物半導体層30と、窒化物半導体層30にオーミック接合されたドレイン電極50と、ドレイン電極50と離間して配設され、窒化物半導体層30にショットキー接合されたソース電極60と、ドレイン電極50とソース電極60との間の窒化物半導体層30上及びソース電極60の少なくとも一部上にかけて形成され、ドレイン電極50とソース電極60との間にリセスを形成する誘電層40と、ドレイン電極50と離間して誘電層40上及びリセスに配設され、一部が誘電層40を挟んでソース電極60のドレイン方向へのエッジ部分上部に形成されたゲート電極70とを含む。

【解決手段】基板10上部に配設され、内部に2次元電子ガスチャネルを形成する窒化物半導体層30と、窒化物半導体層30にオーミック接合されたドレイン電極50と、ドレイン電極50と離間して配設され、窒化物半導体層30にショットキー接合されたソース電極60と、ドレイン電極50とソース電極60との間の窒化物半導体層30上及びソース電極60の少なくとも一部上にかけて形成され、ドレイン電極50とソース電極60との間にリセスを形成する誘電層40と、ドレイン電極50と離間して誘電層40上及びリセスに配設され、一部が誘電層40を挟んでソース電極60のドレイン方向へのエッジ部分上部に形成されたゲート電極70とを含む。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、窒化物半導体素子及びその製造方法に関し、詳しくは、ノーマリ−オフ動作する窒化物半導体素子及びその製造方法に関する。

【背景技術】

【0002】

グリーンエネルギ政策などによる電力消費の節減への関心が増加している。このため、電力変換効率の向上は、必須な要素となる。電力変換において、パワースイッチング素子の効率が全体電力変換の効率を左右する。

【0003】

現在、通常利用される電力素子は、シリコンを用いるパワーMOSFETやIGBTが大部分であるが、シリコンの材料的な限界によって素子の効率向上に限界が生ずるようになる。これを解決するために、窒化ガリウム(Galliumnitride:GaN)のような窒化物半導体を用いるトランジスタを製作して、変換効率を高めるような特許が出願されている。

【0004】

しかし、GaNを用いる、例えば、高電子移動度トランジスタ(HEMT)構造は、ゲート電圧が0V(ノーマル状態)の時、該ドレイン電極と該ソース電極との間の抵抗が低くて電流が流れるようになるオン状態になる。これによって、電流及び電力の消耗が発生し、これをオフ状態にするためには、ゲート電極に陰電圧(例えば、−5V)を加えなければならないという短所がある(ノーマリ−オン(normally−on)構造)。

【0005】

このようなノーマリ−オン構造の短所を解決するために、図6及び図7のような特許出願が従来に示されている。図6及び図7は、従来の高電子移動度HEMT構造を示す。

【0006】

図6は、米国特許出願公開第2007−0295993号明細書の図面を示す。図6では、AlGaN層でゲート(G)の下部領域と、ゲート(G)とドレイン(D)との間のゲート電極(G)に近い領域にイオンを打ち込み、AlGaN層133成長で形成されたチャネルの濃度を調節している。図6では、イオンインプラ(ion implantation)を用いて、ゲート(G)下部のチャネル領域131のキャリア濃度を調節してノーマリ−オフ(normally−off)動作を具現した。

【0007】

図7は、米国登録特許第7038253号明細書の図面であって、第1及び第2の電子共与層133a、133b間に形成されたチャネル層131上を絶縁層140で塗布し、絶縁層140上にゲート電極(G)を形成し、ゲート電極(G)下部で2DEGチャネル135が形成されないようにしている。図7では、ゲート(G)下部をリセス(recess)工程を用いてエッチングし、ノーマリ−オフ動作を具現した。

【先行技術文献】

【特許文献】

【0008】

【特許文献1】韓国公開特許10−2005−0010004号公報

【特許文献2】米国特許出願公開第2006−0102929号明細書

【発明の概要】

【発明が解決しようとする課題】

【0009】

前述のようなノーマリ−オン構造の問題を解決すると共にノーマリ−オフ動作する半導体素子を具現する必要がある。

【0010】

本発明は、上記の問題点に鑑みて成されたものであって、その目的は、半導体素子、例えばFETのソース領域にショットキー(Schottky)電極を形成し、ゲート電極をソース電極の一部領域と窒化物半導体の領域の一部に形成し、該ドレイン電極と該ソース電極との間の誘電層によって形成されたリセス(recess)上にゲート電極の一部を形成することによって、ノーマリ−オフ(Normally−off;N−off)またはエンハンスメントモード(Enhancement Mode)動作し、該リセス上に形成されたショットキーゲート電極を通じる電流供給を増加させてオン抵抗を低め、高電流で動作する半導体素子及び製造方法を提供することにある。

【課題を解決するための手段】

【0011】

上記目的を解決するために、本発明の好適な実施形態によれば、基板上部に配設され、内部に2次元電子ガス(2DEG)チャネルを形成する窒化物半導体層と、該窒化物半導体層にオーミック接合されたドレイン電極と、該ドレイン電極と離間して配設され、該窒化物半導体層にショットキー接合されたソース電極と、該ドレイン電極と該ソース電極との間の該窒化物半導体層上及び該ソース電極の少なくとも一部上にかけて形成され、該ドレイン電極と該ソース電極との間にリセスを形成する誘電層と、ドレイン電極と離間して誘電層上及びリセスに配設され、一部が誘電層を挟んでソース電極のドレイン方向へのエッジ部分上部に形成されたゲート電極と、を含む窒化物半導体素子が提供される。

【0012】

本発明によれば、ゲート電極は、リセスを通じて窒化物半導体層上にショットキー接合される。

【0013】

本発明によれば、ゲート電極は、リセスの底を成す誘電層とショットキー接合され、順方向バイアス電圧の印加時、リセスの底を挟む窒化物半導体層への電流の供給を増加させる。

【0014】

本発明によれば、ゲート電極は、リセスからドレイン方向へ延設されたフィールドプレート部を備え、該フィールドプレート部は、ドレイン方向の誘電層の一部を覆うように形成される。

【0015】

本発明によれば、窒化物半導体層は、基板上部に配設され、窒化ガリウム系列の材料を含む第1の窒化物層と、該第1の窒化物層上に異種接合され、該第1の窒化物層より広いエネルギバンドギャップを有する異種の窒化ガリウム系列の材料を含む第2の窒化物層と、を含む。望ましくは、第1の窒化物層は、窒化ガリウム(GaN)を含み、第2の窒化物層は、アルミニウム窒化ガリウム(AlGaN)、インジウム窒化ガリウム(InGaN)、インジウムアルミニウム窒化ガリウム(InAlGaN)のうちのいずれか一つを含む。

【0016】

また、上記目的を解決するために、本発明の他の実施形態によれば、基板上部に配設され、内部に2次元電子ガス(2DEG)チャネルを形成する窒化物半導体層と、該窒化物半導体層にオーミック接合されたドレイン電極と、該ドレイン電極と離間して配設され、窒化物半導体層にショットキー接合されたソース電極と、該ドレイン電極と該ソース電極との間の窒化物半導体層上及び該ソース電極の少なくとも一部上にかけて形成され、該ドレイン電極と該ソース電極との間にリセスを形成する誘電層と、該誘電層を挟んでソース電極のドレイン方向へのエッジ部分上部に形成された第1の領域、及び該ドレイン電極と該ソース電極との間の誘電層上にドレイン電極と離間し、リセスに形成された第2の領域を含むゲート電極と、を含む窒化物半導体素子が提供される。

【0017】

本発明によれば、ゲート電極は、第1の領域及び第2の領域に分離され、第2の領域は、フローティングゲートを形成する。

【0018】

望ましくは、ゲート電極の第2の領域は、リセスを通じて窒化物半導体層上にショットキー接合される。

【0019】

望ましくは、ゲート電極の第2の領域は、リセスの底を成す誘電層とショットキー接合され、順方向バイアス電圧の印加時、リセスの底を挟む窒化物半導体層への電流の供給を増加させる。

【0020】

望ましくは、ゲート電極の第2の領域は、リセスからドレイン方向へ延設されたフィールドプレート部を備え、該フィールドプレート部は、ドレイン方向の誘電層の一部を覆うように形成される。

【0021】

本発明によれば、窒化物半導体層は、基板上部に配設され、窒化ガリウム系列の材料を含む第1の窒化物層と、該第1の窒化物層上に異種接合され、該第1の窒化物層より広いエネルギバンドギャップを有する異種の窒化ガリウム系列の材料を含む第2の窒化物層と、を含む。

【0022】

本発明によれば、窒化物半導体素子は、基板と窒化物半導体層との間にバッファ層をさらに含む。

【0023】

本発明によれば、窒化物半導体素子は、パワートランジスタ素子である。

【0024】

また、上記目的を解決するために、本発明のさらに他の実施形態によれば、基板上部に、内部に2次元電子ガス(2DEG)チャネルを生成する窒化物半導体層を形成するステップと、該窒化物半導体層にオーミック接合されるドレイン電極と、該窒化物半導体層にドレイン電極と離間してショットキー接合されるソース電極を形成するステップと、該ドレイン電極と該ソース電極との間の窒化物半導体層上及び該ソース電極の少なくとも一部上にかけて誘電層を形成し、該ドレイン電極と該ソース電極との間にリセスを形成する誘電層を形成するステップと、該ドレイン電極と離間して誘電層上にゲート電極を形成し、ゲート電極の一部をソース電極のドレイン方向のエッジ部分上部の誘電層上に形成するステップと、を含む窒化物半導体素子の製造方法が提供される。

【0025】

本発明によれば、前記ゲート電極を形成するステップにおいて、ゲート電極は、リセスを通じて窒化物半導体層上にショットキー接合されるように形成される。

【0026】

本発明によれば、前記ゲート電極を形成するステップにおいて、順方向バイアス電圧の印加時、リセスの底を挟む窒化物半導体層への電流の供給を増加するように薄く形成されたリセスの底を成す誘電層とゲート電極とをショットキー接合させる。

【0027】

また、上記目的を解決するために、本発明のさらに他の実施形態によれば、基板上部に、内部に2次元電子ガス(2DEG)チャネルを生成する窒化物半導体層を形成するステップと、該窒化物半導体層にオーミック接合されるドレイン電極と、該窒化物半導体層にドレイン電極と離間してショットキー接合されるソース電極を形成するステップと、該ドレイン電極と該ソース電極との間の窒化物半導体層上及び該ソース電極の少なくとも一部上にかけて誘電層を形成し、該ドレイン電極と該ソース電極との間にリセスを形成する誘電層を形成するステップと、該誘電層を挟んでソース電極のドレイン方向へのエッジ部分上部に形成された第1の領域、及び該ドレイン電極と該ソース電極との間の誘電層上にドレイン電極と離間し、リセスに形成された第2の領域を含むゲート電極を形成するステップと、を含む窒化物半導体素子の製造方法が提供される。

【0028】

本発明によれば、前記ゲート電極を形成するステップにおいて、第1の領域及び第2の領域に分離してゲート電極を形成する。

【0029】

望ましくは、前記ゲート電極を形成するステップにおいて、該ゲート電極の第2の領域は、リセスを通じて窒化物半導体層上にショットキー接合されるように形成される。

【0030】

望ましくは、前記ゲート電極を形成するステップにおいて、順方向バイアス電圧の印加時、リセスの底を挟む窒化物半導体層への電流の供給が増加するように薄く形成されたリセスの底を成す誘電層とゲート電極の第2の領域とをショットキー接合させる。

【発明の効果】

【0031】

本発明によれば、半導体素子、例えばFETのソース領域にショットキー電極を形成し、ゲート電極をソース電極の一部領域及び窒化物半導体の領域の一部に形成し、該ドレイン電極と該ソース電極との間の誘電層によって形成されたリセス上にゲート電極の一部を形成することによって、ノーマリ−オフまたは、エンハンスメントモード動作し、リセス上に形成されたショットキーゲート電極を通じる電流供給を増加させ、オン抵抗を低め、高電流で動作する半導体素子を得ることができる。

【0032】

また、本発明によれば、既存のGaNノーマリ−オフ素子に比べて高耐圧動作が可能で、製造工程が簡単で、素子の製作が容易になる。すなわち、従来のノーマリ−オフHEMTのイオン注入、200〜300オングストロング厚さを有するAlGaN層に対するエッチングなどの高難易度の工程が必要ではなく、その製作が容易になる。

【0033】

また、本発明によれば、ソース電極のショットキー障壁によってリーク電流が防止される構造によって、既存のノーマリ−オフHEMTに比べてリーク電流が低く、耐圧が高くなるという効果が奏する。

【0034】

また、本発明によれば、ドレイン電極とソース電極との間の誘電層によって形成されるリセス領域に形成されたショットキーゲート電極によって、電流量が増加してオン抵抗を低くするという効果が奏する。それによって、高電流動作が可能になる。

【0035】

また、本発明によれば、ゲート構造によって、電界が分散して耐圧を高めることができる。また、ソース電極とゲート電極との間の距離が短く、トランスコンダクタンス(transconductance)の高くなる長所がある。

【図面の簡単な説明】

【0036】

【図1】本発明の一実施形態による窒化物半導体素子の概略的な断面図である。

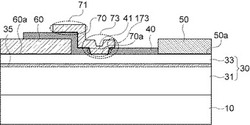

【図2】本発明の他の実施形態による窒化物半導体素子の概略的な断面図である。

【図3a】図1の窒化物半導体素子の製造方法を示す断面図である。

【図3b】図1の窒化物半導体素子の製造方法を示す断面図である。

【図3c】図1の窒化物半導体素子の製造方法を示す断面図である。

【図3d】図1の窒化物半導体素子の製造方法を示す断面図である。

【図3e】図1の窒化物半導体素子の製造方法を示す断面図である。

【図4a】本発明のさらに他の実施形態による窒化物半導体素子の概略的な断面図である。

【図4b】本発明のさらに他の実施形態による窒化物半導体素子の概略的な断面図である。

【図5a】本発明のさらに他の実施形態による窒化物半導体素子の概略的な断面図である。

【図5b】本発明のさらに他の実施形態による窒化物半導体素子の概略的な断面図である。

【図6】従来の高電子移動度HEMT構造を示す断面図である。

【図7】従来の高電子移動度HEMT構造を示す断面図である。

【発明を実施するための形態】

【0037】

以下、本発明の好適な実施の形態は、図面を参考にして詳細に説明する。次に示される各実施の形態は、当業者にとって本発明の思想が十分に伝達されることができるようにするために例として挙げられるものである。従って、本発明は、以下示している各実施の形態に限定されることなく他の形態で具体化されることができる。そして、図面において、装置の大きさ及び厚さなどは、便宜上誇張して表現されることができる。明細書全体に渡って同一の参照符号は、同一の構成要素を示している。

【0038】

本明細書で使われた用語は、実施形態を説明するためのものであって、本発明を制限しようとするものでは、ない。本明細書において、単数形は、文句で特別に言及しない限り複数形も含む。明細書で使われる「含む」とは、言及された構成要素、ステップ、動作及び/又は、素子は、一つ以上の他の構成要素、ステップ、動作及び/又は、素子の存在または、追加を排除しないことに理解されたい。

【0039】

図1は、本発明の一実施形態による窒化物半導体素子の概略的な断面図である。図2は、本発明の他の実施形態による窒化物半導体素子の概略的な断面図である。図3a〜図3eは、図1の窒化物半導体素子の製造方法を示す断面図である。図4a及び図4bは、本発明のさらに他の実施形態による窒化物半導体素子の概略的な断面図である。図5a及び図5bは、本発明のさらに他の実施形態による窒化物半導体素子の概略的な断面図である。

【0040】

まず、図1、図2、図4a及び図4b、図5a及び図5bを参照して、本発明の一実施形態による窒化物半導体素子を詳記する。

【0041】

図1、図2、図4a及び図4b、図5a及び図5bに示すように、本発明の一実施形態による窒化物半導体素子は、基板10上部に配設された窒化物半導体層30、ドレイン電極50、ソース電極60、誘電層40及びゲート電極70を含む。

【0042】

図1、図2、図4a及び図4b、図5a及び図5bに示すように、本実施形態において、窒化物半導体層30は、基板10上部に配設される。基板10は、一般に絶縁基板を用いて、実に絶縁性及び高抵抗性を有する基板を用いてもよい。望ましくは、基板10は、シリコン(Si)、シリコンカーバイド(SiC)及びサファイヤ(Al2O3)のうちの少なくともいずれか一つを用いて製造されてもよく、公知の他の基板材料を用いて製造されてもよい。

【0043】

窒化物半導体層30は、基板10上部に直接形成されてもよい。望ましくは、窒化物半導体層30は、単結晶薄膜をエピタキシャル成長させて形成する。窒化物半導体層30を形成するためのエピタキシャル成長工程としては、液相成長法(LPE:Liquid Phase Epitaxy)、化学気相蒸着法(CVD:Chemical Vapor Deposition)、分子ビーム成長法(MBE:Molecular Beam Epitaxy)、有機金属気相蒸着法(MOCVD:Metalorganic CVD)などが挙げられる。

【0044】

また、図4a及び図4bに示すように、本発明の他の実施形態によれば、基板10と窒化物半導体層30との間にバッファ層20を設け、窒化物半導体層30をバッファ層20上に形成する。バッファ層20は、基板10と窒化物半導体層30との格子不整合(lattice mismatch)による問題点を解決するために提供される。バッファ層20は、一つの層だけではなく、窒化ガリウム(GaN)、アルミニウム窒化ガリウム(AlGaN)、窒化アルミニウム(AlN)、インジウム窒化ガリウム(InGaN)、インジウムアルミニウム窒化ガリウム(InAlGaN)などを含む複数の層で形成されてもよい。また、バッファ層20は、窒化ガリウム以外の他の3−5族化合物半導体によって形成されてもよい。例えば、基板10がサファイヤ基板10の場合、窒化ガリウムを含む窒化物半導体層30との格子定数及び熱膨脹係数の差によって誤整合(mismatch)されることを防ぐため、バッファ層20の成長は重要である。

【0045】

図1、図2、図4a及び図4b、図5a及び図5bに示すように、窒化物半導体層30の内部には2次元電子ガス(2DEG)チャネル35が形成される。窒化物半導体素子のゲート電極70にバイアス電圧を印加すると、窒化物半導体層30内の2DEGチャネル35を通じて電子が移動し、電流がドレイン電極50とソース電極60との間に流れるようになる。窒化物半導体層30を成す窒化物としては、窒化ガリウム(GaN)、アルミニウム窒化ガリウム(AlGaN)、インジウム窒化ガリウム(InGaN)、インジウムアルミニウム窒化ガリウム(InAlGaN)などが挙げられる。

【0046】

本発明の実施形態によれば、窒化物半導体層30は、異種接合された窒化ガリウム系列の半導体層30であって、異種接合された界面でエネルギバンドギャップの差によって2次元電子ガスチャネル35が形成される。異種接合される窒化ガリウム系列の半導体層30で異種接合間の格子定数の差が小さいほど、バンドギャップとの極性の差が減るようになり、2DEGチャネル35の形成が抑制される。異種接合の時、エネルギバンドギャップの不連続性によって広いバンドギャップを有する材料から小さなバンドギャップを有する材料への自由電子が移動するようになる。このような電子は、異種接合界面に蓄積されて2DEGチャネル35を形成し、ドレイン電極50とソース電極60との間で電流が流れるようにする。

【0047】

より詳しくは、図1、図2、図4a及び図4b、図5a及び図5bに示すように、窒化物半導体層30は、第1の窒化物層31及び第2の窒化物層33を含む。第1の窒化物層31は、基板10上部に配設され、窒化ガリウム系列の材料を含む。第2の窒化物層33は、第1の窒化物層31上に異種接合され、該第1の窒化物層31より広いエネルギバンドギャップを有する異種の窒化ガリウム系列の材料を含む。この時、第2の窒化物層33は、第1の窒化物層31内に形成される2DEGチャネル35へ電子を供給する役割をする。一例として、電子を供与する第2の窒化物層33は、第1の窒化物層31より薄い厚さで形成されることが望ましい。

【0048】

望ましくは、本発明の他の実施形態によれば、第1の窒化物層31は、窒化ガリウム(GaN)を含み、第2の窒化物層33は、アルミニウム窒化ガリウム(AlGaN)、インジウム窒化ガリウム(InGaN)及びインジウムアルミニウム窒化ガリウム(InAlGaN)のうちのいずれか一つを含む。望ましくは、一例として、第1の窒化物層31は、窒化ガリウム(GaN)を含み、第2の窒化物層33は、アルミニウム窒化ガリウム(AlGaN)を含む。

【0049】

続いて、図1、図2、図4a及び図4b、図5a及び図5bを参照して、本発明の実施形態の構成がより詳しく説明する。

【0050】

図1、図2、図4a及び図4b、図5a及び図5bに示すように、本実施形態による窒化物半導体素子のドレイン電極50及びソース電極60が窒化物半導体層30に形成される。ドレイン電極50は、窒化物半導体層30にオーミック接合50aされている。

【0051】

ソース電極60は、ドレイン電極50と離間して配設され、窒化物半導体層30にショットキー接合60aされる。ショットキーソース電極60によって、逆方向に駆動される時、ソース電極60のショットキー接合領域60aで生成される空乏領域によって2次元電子ガス(2DEG)による電流の流れを安定して遮断することができる。そのため、逆方向電流の流れを遮断することができ、ノーマリ−オフ状態を具現することができるようになる。より詳しくは、逆方向バイアス電圧が印加された場合、ソース電極60のショットキー接合領域60aで生成される空乏領域が2DEGチャネル35領域まで拡張され、2DEGチャネル35を遮断し、逆方向の降伏電圧を増加させるようになる。特に、逆方向バイアス電圧の印加時、ソース電極60のドレイン側のコーナー寄りのショットキー接合領域60aで空乏領域が大きく拡張される。一方、順方向バイアス電圧をかけると、ソース電極60のショットキー接合領域60aで生成される空乏領域が小さくなり、2DEGチャネル35を通じてドレイン電極50とソース電極60との間に電流が流れるようになる。

【0052】

続いて、図1、図2、図4a及び図4b、図5a及び図5bに示すように、本発明の一実施形態による窒化物半導体素子の誘電層40は、ドレイン電極50とソース電極60との間の窒化物半導体層30上及びソース電極60の少なくとも一部上にかけて形成される。この時、誘電層40は、ドレイン電極50とソース電極60との間でリセスを形成する。望ましくは、図1、図4a及び図5aに示すように、リセス領域41は、誘電層40を貫いて窒化物半導体層30の底を成すように形成されてもよい。または、図2、図4b及び図5bに示すように、リセス領域42は、誘電層40の一部領域を、例えばエッチングして形成し、窒化物半導体層30上に薄い膜を残して形成されてもよい。望ましくは、誘電層40は、酸化膜からなり、一実施形態によれば、SiN、SiO2、Al2O3のうちの少なくともいずれか一つを含むことができる。

【0053】

続いて、図1、図2、図4a及び図4b、図5a及び図5bに示すように、本実施形態による窒化物半導体素子のゲート電極70は、ドレイン電極50と離間して誘電層40上に配設される。また、ゲート電極70の一部71、71’が誘電層40を挟んでソース電極60のドレイン方向へのエッジ部分上部に形成される。望ましくは、ゲート電極70は、誘電層40上にショットキー接合70aされる。ゲート電極70に順方向バイアスの電圧が印加されると、ソース電極60のドレイン側のコーナー寄りのショットキー接合領域60aで形成される空乏領域が小さくなり、2DEGチャネル35を通じてドレイン電極50とソース電極60との間に電流が流れるようになる。

【0054】

なお、ゲート電極70の一部73、73’は、誘電層40によって形成されたリセス領域41、42に配設されるように形成される。これによって、リセス領域41、42に形成されたショットキーゲート電極70を通じて窒化物半導体層30との電流キャリアの移動が容易になり、電流量が増加し、オン抵抗が低くなる。

【0055】

また、図1、図2、図4a及び図4bに示すように、ゲート構造がソース電極60のエッジ部分上部及びドレイン電極50とソース電極60との間の誘電層40上に亘っており、電界が分散するという効果があり、ドレイン電極50とソース電極60との間の誘電層40上に掛っているゲート構造自体が耐圧を高めるフィールドプレートの役割を果たすようになる。

【0056】

望ましくは、図1及び図4aを参照して、本発明の他の実施形態において、ゲート電極70は、リセス41を通じて窒化物半導体30層上にショットキー接合70aされる。これによって、ゲート電極70に閾値電圧以上のバイアス電圧を印加すると、開放された誘電層40の領域に形成されたショットキーゲート電極70を通じて電流キャリアの移動が容易になり、電流量が増加するようになる。よって、オン抵抗が低くなり、高電流動作が可能になる。

【0057】

また、望ましくは、図2及び図4bに示すように、本発明のさらに他の実施形態において、ゲート電極70は、リセス42の底を成す誘電層40とショットキー接合70aされて、順方向バイアス電圧の印加時、リセス42の底を挟む窒化物半導体層30への電流の供給を増加させる。これによって、ゲート電極70に閾値電圧以上のバイアス電圧を印加すると、薄いリセス42の底を成す誘電層40とショットキー接合70aされたゲート電極70を通じて窒化物半導体層30との電流キャリアの移動が容易になり、電流量が増加するようになる。よって、オン抵抗が低くなり、高電流動作が可能になる。

【0058】

また、望ましくは、図1、図2、図4a及び図4bに示すように、本発明の他の実施形態において、ゲート電極70は、リセス41、42からドレイン方向で延設されたフィールドプレート部173を備える。フィールドプレート部173は、ドレイン方向の誘電層40の一部を覆うように形成される。フィールドプレート部173は、ゲート電極70のリセス領域41、42に形成された縁部に集中される電界を分散させるという効果が奏する。

【0059】

また、図1、図2、図4a及び図4b、図5a及び図5bを参照して、本発明の他の実施形態について説明する。

【0060】

図1、図2、図4a及び図4b、図5a及び図5bに示すように、本発明の一実施形態による窒化物半導体素子は、基板10上部に配設された窒化物半導体層30、ドレイン電極50、ソース電極60、誘電層40及びゲート電極70を含む。窒化物半導体層30、ドレイン電極50、ソース電極60及び誘電層40については、前述のようである。

【0061】

本実施形態において、ゲート電極70は、第1の領域71、71’及び第2の領域73、73’を備える。第1の領域71、71’は、誘電層40を挟んでソース電極60のドレイン方向へのエッジ部分上部に形成されている。第2の領域73、73’は、ドレイン電極50とソース電極60との間の誘電層40上にドレイン電極50と離間して配設される。この時、第2の領域73、73’は、誘電層40によってドレイン電極50とソース電極60との間で形成されるリセス領域41、42上にも配設されるように形成される。第1の領域と第2の領域とは、図1、図2、図4a及び図4bに示すように、一体に形成されてもよく、図5a、図5bに示すように分離されてもよい。

【0062】

望ましくは、図5a及び図5bに示すように、本発明の他の実施形態によれば、ゲート電極70の第1の領域71’及び第2の領域73’は、分離されている。第2の領域73’によって電界が分散されるという効果が奏する。望ましくは、第2の領域73’は、ドレイン電極50よりソース電極60に近く配設される。

【0063】

図5a及び図5bに示されていないが、本発明の他の実施形態によれば、図4a及び図4bと同様に、基板10と窒化物半導体層30との間にバッファ層20を設け、窒化物半導体層30を該バッファ層20上に形成してもよい。

【0064】

望ましくは、図5aに示すように、他の実施形態によれば、ゲート電極70の第2の領域73’は、リセス41を通じて窒化物半導体30層上にショットキー接合70aされる。これによって、ゲート電極70に閾値電圧以上のバイアス電圧を印加すると、開放された誘電層40の領域に形成されたショットキーゲート電極の第2の領域73’を通じて電流キャリアの移動が容易になり電流量が増加し、オン抵抗が低くなるようになる。

【0065】

また、望ましくは、図5bに示すように、他の実施形態によれば、ゲート電極70の第2の領域73’は、リセス42の底を成す誘電層40とショットキー接合70aされ、順方向バイアス電圧の印加時、リセス42の底を挟む窒化物半導体層30への電流の供給を増加させる。これによって、閾値電圧以上のバイアス電圧を印加すると、薄いリセス42の底を成す誘電層40とショットキー接合70aされたゲート電極の第2の領域73’を通じて窒化物半導体層30との電流キャリアの移動が容易になり、電流量が増加し、オン抵抗が低くなるようになる。

【0066】

また、望ましくは、図5a及び図5bに示すように、他の実施形態によれば、ゲート電極70の第2の領域73’は、リセス41、42からドレイン方向へ延設されたフィールドプレート部173を備える。該フィールドプレート部173は、ドレイン方向の誘電層40の一部を覆うように形成される。これによって、フィールドプレート部173は、ゲート電極の第2の領域73’のリセス領域41、42に形成された縁部に集中される電界を分散させるという効果が奏する。

【0067】

図1、図2、図4a及び図4b、図5a及び図5bに示す本発明の実施形態によれば、ゲート電極70に0Vの電圧を印加すると、ドレイン電極50とソース電極60との間に2DEGチャネル35を通じる電流の流れがソース電極60領域のショットキー障壁によって遮られる。そして、ゲート電極70に閾値電圧以上を印加すると、ソース電極60のドレイン方向のエッジ領域にキャリア(電子)の濃度が高くなり、トンネリング(tunneling)現象によって電流が流れるようになる。この時、ゲートの閾値電圧は、誘電層40の厚さなどによって決まる。これによって、既存のノーマリ−オフHEMT構造に比べて製作が容易で、リーク電流が少なく、高い耐圧特性を現わすようになる。

【0068】

また、誘電層40によって形成されたリセス領域41、42にゲート電極70の一部を形成させ、ゲート電極70に閾値電圧以上のバイアス電圧を印加すると、リセス領域41、42に形成されたショットキーゲート電極70を通じて窒化物半導体層30との電流キャリアの移動が容易になり、電流量が増加するようになる。よって、オン抵抗が低くなり、高電流動作が可能になる。

【0069】

本発明の他の実施形態によれば、前述の実施形態による窒化物半導体素子は、パワートランジスタ素子である。本発明の実施形態によるパワートランジスタは、水平型HEMT構造を備える。

【0070】

次に、本発明の他の実施形態による窒化物半導体製造方法を図面を参照して説明する。本発明による窒化物半導体製造方法を説明するに当たって、図3a〜図3eの他に、前述の実施形態による窒化物半導体素子及び図1、図2、図4a及び図4b、図5a及び図5bを参照する。反対の場合も同様である。本発明の窒化物半導体素子の製造方法に関する具体的な実施形態に対して、以下説明されないことは、前述と同様であるため、重複する説明は省略する。

【0071】

図3a〜図3eは、本発明の他の実施形態による窒化物半導体の製造方法を示す。

【0072】

望ましくは、本発明の実施形態によれば、窒化物半導体素子の製造方法によって製造される素子は、パワートランジスタである。

【0073】

まず、図3aに示すように、基板10上部に、内部に2次元電子ガス(2DEG)チャネル35を生成する窒化物半導体層30を形成する。望ましくは、基板10は、シリコン(Si)、シリコンカーバイド(SiC)、サファイヤ(Al2O3)のうちの少なくともいずれか一つを用いて製造されてもよい。窒化物半導体層30を成す窒化物としては、窒化ガリウム(GaN)、アルミニウム窒化ガリウム(AlGaN)、インジウム窒化ガリウム(InGaN)、インジウムアルミニウム窒化ガリウム(InAlGaN)などが挙げられる。

【0074】

望ましくは、窒化物半導体層30は、窒化物単結晶薄膜をエピタキシャル成長させて形成される。望ましくは、エピタキシャル成長の時、選択的に成長させて過成長されないように調節する。仮に、過成長された場合には、エッチバック(etchback)工程やCMP(Chemical Mechanical Polishing)工程を用いて平坦化する過程を追加してもよい。

【0075】

望ましくは、本発明の実施形態によれば、図3aに示された第1の窒化物層31及び第2の窒化物層33は、エピタキシャル成長工程(Epitaxial Growth Precess)によって形成される。まず、第1の窒化物層31は、基板10上部に窒化ガリウム系列単結晶薄膜をエピタキシャル成長させて形成する。望ましくは、本発明の他の実施形態によれば、第1の窒化物層31は、窒化ガリウム(GaN)をエピタキシャル成長させて形成する。続いて、第2の窒化物層33は、第1の窒化物層31をシード層として第1の窒化物層31より広いエネルギバンドギャップを有する異種の窒化ガリウム系列の材料を含む窒化物層をエピタキシャル成長させて形成する。望ましくは、本発明の他の実施形態によれば、第2の窒化物層33は、アルミニウム窒化ガリウム(AlGaN)、インジウム窒化ガリウム(InGaN)及びインジウムアルミニウム窒化ガリウム(InAlGaN)のうちのいずれか一つを含む窒化ガリウム系列単結晶をエピタキシャル成長させて形成する。望ましくは、第2の窒化物層33は、アルミニウム窒化ガリウム(AlGaN)をエピタキシャル成長させて形成する。一例として、電子を供与する第2の窒化物層33は、第1の窒化物層31より薄い厚さで形成されることが望ましい。

【0076】

第1及び第2の窒化物層33を形成するためのエピタキシャル成長工程としては、液相成長法、化学気相蒸着法、分子ビーム成長法、有機金属気相蒸着法などが挙げられる。

【0077】

次に、図3bに示すように、窒化物半導体層30にドレイン電極50とソース電極60とを形成する。図3bにおいて、ドレイン電極50は、窒化物半導体層30にオーミック接合50されるように形成する。該オーミック接合を完成するために熱処理を行ってもよい。窒化膜半導体層30上に金(Au)、ニッケル(Ni)、白金(Pt)、チタン(Ti)、アルミニウム(Al)、パラジウム(Pd)、イリジウム(Ir)、ロジウム(Rh)、コバルト(Co)、タングステン(W)、モリブデン(Mo)、タンタル(Ta)、銅(Cu)及び亜鉛(Zn)のうちの少なくともいずれか一つの金属、金属シリサイド及びこれらの合金を用いてドレイン金属電極を形成してもよい。ドレイン電極50は、多層構造で形成されてもよい。

【0078】

ソース電極60は、ドレイン電極50と離間して窒化物半導体層30にショットキー接合60aされるように形成する。ショットキー接合60aされるソース電極60は、窒化膜半導体層30とショットキー接合可能な材料、例えば、アルミニウム(Al)、モリブデン(Mo)、金(Au)、ニッケル(Ni)、白金(Pt)、チタン(Ti)、パラジウム(Pd)、イリジウム(Ir)、ロジウム(Rh)、コバルト(Co)、タングステン(W)、タンタル(Ta)、銅(Cu)及び亜鉛(Zn)のうちの少なくともいずれか一つの金属、金属シリサイド及びこれらの合金を用いて形成されてもよい。ソース電極60は、多層構造で形成されてもよい。ソース電極60で金属と半導体接合を有するショットキー接合60aを用いて、ドレイン電極50とソース電極60との間に2DEGチャネル35を通じる逆方向の電流を遮断することができる。

【0079】

一例として、ドレイン電極50及びソース電極60の形成過程について説明する。基板10上部にエピタキシャル成長によって形成された窒化物半導体層30上に電極を形成するための金属層を、電子ビーム蒸着器などによって蒸着形成し、該金属層上にフォトレジストパターンを形成する。続いて、該フォトレジストパターンをエッチングマスクとして金属層をエッチングし、フォトレジストパターンを取り除いて金属電極50、60を形成する。

【0080】

図3cに示すように、本発明の一実施形態によれば、ドレイン電極50及びソース電極60を形成した後、ドレイン電極50とソース電極60との間の窒化物半導体層30上に誘電層40を形成する。この時、誘電層40は、少なくともソース電極60の一部上に、望ましくは、ドレイン電極50方のソース電極60の一部上にかけて形成される。望ましくは、誘電層40は、酸化膜からなってもよく、SiN、SiO2及びAl2O3のうちの少なくともいずれか一つからなってもよい。

【0081】

また、図3dに示すように、ドレイン電極50とソース電極60との間に塗布形成された誘電層40にリセス41を形成する。例えば、リセス41はエッチング工程によって設けられる。望ましくは、リセス領域41は、誘電層40を貫いて窒化物半導体層30が底を成すように形成されてもよく、リセス領域42は、誘電層40の一部領域をエッチングして形成するものの、窒化物半導体層30上に薄い膜を残しておくように形成されてもよい。

【0082】

図3eに示すように、本発明の一実施形態によれば、図3c及び図3dの誘電層40を形成した後、ドレイン電極50と離間して誘電層40上にゲート電極70を形成する。そして、ゲート電極70の一部がソース電極60のドレイン方向のエッジ部分上部の誘電層40上に形成されるようにする。ゲート電極70は、アルミニウム(Al)、モリブデン(Mo)、金(Au)、ニッケル(Ni)、白金(Pt)、チタン(Ti)、パラジウム(Pd)、イリジウム(Ir)、ロジウム(Rh)、コバルト(Co)、タングステン(W)、タンタル(Ta)、銅(Cu)及び亜鉛(Zn)のうちの少なくともいずれか一つの金属、金属シリサイド及びこれらの合金を用いて形成されてもよい。ゲート電極70は、ドレイン電極50及び/またはソース電極60と異なる金属を使ってもよく、多層構造に形成されてもよい。望ましくは、ゲート電極70は、誘電層40上にショットキー接合70aされる。

【0083】

なお、ゲート電極70の一部73、73’は、誘電層40によって形成されたリセス領域41、42に配設されるように形成される。これによって、リセス領域41、42に形成されたショットキーゲート電極70を通じて窒化物半導体層30との電流キャリアの移動が容易になり、電流量が増加し、オン抵抗が低くなるようになる。

【0084】

ゲート電極70の形成過程について説明する、誘電層40上に電極を形成するための金属層を電子ビーム蒸着器などによって蒸着形成し、該金属層上にフォトレジストパターンを形成する。そして、該フォトレジストパターンをエッチングマスクとして金属層をエッチングする。エッチング後、フォトレジストパターンを取り除いて金属電極を形成する。

【0085】

望ましくは、図3e、図1、図4a及び図5aに示すように、ゲート電極70の一部73または第2の領域73’は、リセス41を通じて窒化物半導体30層上にショットキー接合70aされるように形成される。これによって、ゲート閾値電圧以上のバイアス電圧を印加すると、開放された誘電層40の領域に形成されたショットキーゲート電極部分73、73’を通じて電流キャリアの移動が容易になり、電流量が増加し、オン抵抗が低くなるようになる。

【0086】

また、さらに他の実施形態によれば、図2、図4b及び図5bに示すように、ゲート順方向のバイアス電圧を印加すると、リセス42の底を挟む窒化物半導体層30への電流の供給が増加するように、ゲート電極の一部73または第2の領域73’は、リセス42の底を成す誘電層40とショットキー接合70aされるように形成する。これによって、閾値電圧以上のバイアス電圧を印加すると、薄いリセス42の底を成す誘電層40とショットキー接合70aされたゲート電極部分73、73’を通じて窒化物半導体層30との電流キャリアの移動が容易になり、電流量が増加し、オン抵抗が低くなるようになる。

【0087】

また、望ましくは、ゲート電極70の一部領域73または第2の領域73’は、リセス41、42からドレイン方向へ延設されたフィールドプレート部173を備える。この時、フィールドプレート部173は、ドレイン方向の誘電層40の一部を覆うように形成される。これによって、フィールドプレート部173は、ゲート電極近隣73、73’のリセス領域41、42に形成された縁部に集中される電界を分散させるという効果が奏する。

【0088】

また、図3e、図1、図2、図4a及び図4b、図5a及び図5bに示すように、他の実施形態によれば、ゲート電極70は、第領域71、71’及び第2の領域73、73’を備える。ゲート電極70の第1の領域71、71’は、ソース電極60のドレイン方向のエッジ部分上部で誘電層40を挟み、第2の領域73、73’は、ドレイン電極50とソース電極60との間の誘電層40上にドレイン電極50と離間して配設されるようにゲート電極70を形成する。この時、第2の領域73、73’は、誘電層40によってドレイン電極50とソース電極60との間で形成されるリセス領域41、42上にも配設される。第1の領域及び第2の領域は、図1、図2、図4a及び図4bに示すように、一体に形成されてもよく、図5a及び図5bに示すように分離されて形成されてもよい。

【0089】

図5a及び図5bに示すように、ゲート電極70を形成するステップにおいて、第1の領域71’及び第2の領域73’を分離してゲート電極70を形成する。

【0090】

図5a及び図5bに示す追加的な実施形態に対する説明は、前述と同様である。

【0091】

望ましくは、他の実施形態によれば、図3aの基板10上部に窒化物半導体層30を形成する前に、基板10上部にバッファ層20を形成するステップをさらに含む。該バッファ層20は、基板10と窒化物半導体層30との格子不整合による問題点を解決するために提供される。バッファ層20は、一つの層だけではなく、窒化ガリウム(GaN)、アルミニウム窒化ガリウム(AlGaN)、窒化アルミニウム(AlN)、インジウム窒化ガリウム(InGaN)、インジウムアルミニウム窒化ガリウム(InAlGaN)などを含む複数の層で形成されてもよい。

【0092】

今回開示された実施の形態は、すべての点で例示であって制限的なものでは、ないと考えられるべきである。本発明の範囲は、前記した実施の形態の説明では、なくて特許請求の範囲によって示され、特許請求の範囲と均等の意味及び範囲内でのすべての変更が含まれることが意図される。

【符号の説明】

【0093】

10 基板

20 バッファ層

30 窒化物半導体層

31 第1の窒化物層

33 第2の窒化物層

35 2DEGチャネル

40 誘電層

41、42 リセス領域

50 ドレイン電極

60 ソース電極

70 ゲート電極

【技術分野】

【0001】

本発明は、窒化物半導体素子及びその製造方法に関し、詳しくは、ノーマリ−オフ動作する窒化物半導体素子及びその製造方法に関する。

【背景技術】

【0002】

グリーンエネルギ政策などによる電力消費の節減への関心が増加している。このため、電力変換効率の向上は、必須な要素となる。電力変換において、パワースイッチング素子の効率が全体電力変換の効率を左右する。

【0003】

現在、通常利用される電力素子は、シリコンを用いるパワーMOSFETやIGBTが大部分であるが、シリコンの材料的な限界によって素子の効率向上に限界が生ずるようになる。これを解決するために、窒化ガリウム(Galliumnitride:GaN)のような窒化物半導体を用いるトランジスタを製作して、変換効率を高めるような特許が出願されている。

【0004】

しかし、GaNを用いる、例えば、高電子移動度トランジスタ(HEMT)構造は、ゲート電圧が0V(ノーマル状態)の時、該ドレイン電極と該ソース電極との間の抵抗が低くて電流が流れるようになるオン状態になる。これによって、電流及び電力の消耗が発生し、これをオフ状態にするためには、ゲート電極に陰電圧(例えば、−5V)を加えなければならないという短所がある(ノーマリ−オン(normally−on)構造)。

【0005】

このようなノーマリ−オン構造の短所を解決するために、図6及び図7のような特許出願が従来に示されている。図6及び図7は、従来の高電子移動度HEMT構造を示す。

【0006】

図6は、米国特許出願公開第2007−0295993号明細書の図面を示す。図6では、AlGaN層でゲート(G)の下部領域と、ゲート(G)とドレイン(D)との間のゲート電極(G)に近い領域にイオンを打ち込み、AlGaN層133成長で形成されたチャネルの濃度を調節している。図6では、イオンインプラ(ion implantation)を用いて、ゲート(G)下部のチャネル領域131のキャリア濃度を調節してノーマリ−オフ(normally−off)動作を具現した。

【0007】

図7は、米国登録特許第7038253号明細書の図面であって、第1及び第2の電子共与層133a、133b間に形成されたチャネル層131上を絶縁層140で塗布し、絶縁層140上にゲート電極(G)を形成し、ゲート電極(G)下部で2DEGチャネル135が形成されないようにしている。図7では、ゲート(G)下部をリセス(recess)工程を用いてエッチングし、ノーマリ−オフ動作を具現した。

【先行技術文献】

【特許文献】

【0008】

【特許文献1】韓国公開特許10−2005−0010004号公報

【特許文献2】米国特許出願公開第2006−0102929号明細書

【発明の概要】

【発明が解決しようとする課題】

【0009】

前述のようなノーマリ−オン構造の問題を解決すると共にノーマリ−オフ動作する半導体素子を具現する必要がある。

【0010】

本発明は、上記の問題点に鑑みて成されたものであって、その目的は、半導体素子、例えばFETのソース領域にショットキー(Schottky)電極を形成し、ゲート電極をソース電極の一部領域と窒化物半導体の領域の一部に形成し、該ドレイン電極と該ソース電極との間の誘電層によって形成されたリセス(recess)上にゲート電極の一部を形成することによって、ノーマリ−オフ(Normally−off;N−off)またはエンハンスメントモード(Enhancement Mode)動作し、該リセス上に形成されたショットキーゲート電極を通じる電流供給を増加させてオン抵抗を低め、高電流で動作する半導体素子及び製造方法を提供することにある。

【課題を解決するための手段】

【0011】

上記目的を解決するために、本発明の好適な実施形態によれば、基板上部に配設され、内部に2次元電子ガス(2DEG)チャネルを形成する窒化物半導体層と、該窒化物半導体層にオーミック接合されたドレイン電極と、該ドレイン電極と離間して配設され、該窒化物半導体層にショットキー接合されたソース電極と、該ドレイン電極と該ソース電極との間の該窒化物半導体層上及び該ソース電極の少なくとも一部上にかけて形成され、該ドレイン電極と該ソース電極との間にリセスを形成する誘電層と、ドレイン電極と離間して誘電層上及びリセスに配設され、一部が誘電層を挟んでソース電極のドレイン方向へのエッジ部分上部に形成されたゲート電極と、を含む窒化物半導体素子が提供される。

【0012】

本発明によれば、ゲート電極は、リセスを通じて窒化物半導体層上にショットキー接合される。

【0013】

本発明によれば、ゲート電極は、リセスの底を成す誘電層とショットキー接合され、順方向バイアス電圧の印加時、リセスの底を挟む窒化物半導体層への電流の供給を増加させる。

【0014】

本発明によれば、ゲート電極は、リセスからドレイン方向へ延設されたフィールドプレート部を備え、該フィールドプレート部は、ドレイン方向の誘電層の一部を覆うように形成される。

【0015】

本発明によれば、窒化物半導体層は、基板上部に配設され、窒化ガリウム系列の材料を含む第1の窒化物層と、該第1の窒化物層上に異種接合され、該第1の窒化物層より広いエネルギバンドギャップを有する異種の窒化ガリウム系列の材料を含む第2の窒化物層と、を含む。望ましくは、第1の窒化物層は、窒化ガリウム(GaN)を含み、第2の窒化物層は、アルミニウム窒化ガリウム(AlGaN)、インジウム窒化ガリウム(InGaN)、インジウムアルミニウム窒化ガリウム(InAlGaN)のうちのいずれか一つを含む。

【0016】

また、上記目的を解決するために、本発明の他の実施形態によれば、基板上部に配設され、内部に2次元電子ガス(2DEG)チャネルを形成する窒化物半導体層と、該窒化物半導体層にオーミック接合されたドレイン電極と、該ドレイン電極と離間して配設され、窒化物半導体層にショットキー接合されたソース電極と、該ドレイン電極と該ソース電極との間の窒化物半導体層上及び該ソース電極の少なくとも一部上にかけて形成され、該ドレイン電極と該ソース電極との間にリセスを形成する誘電層と、該誘電層を挟んでソース電極のドレイン方向へのエッジ部分上部に形成された第1の領域、及び該ドレイン電極と該ソース電極との間の誘電層上にドレイン電極と離間し、リセスに形成された第2の領域を含むゲート電極と、を含む窒化物半導体素子が提供される。

【0017】

本発明によれば、ゲート電極は、第1の領域及び第2の領域に分離され、第2の領域は、フローティングゲートを形成する。

【0018】

望ましくは、ゲート電極の第2の領域は、リセスを通じて窒化物半導体層上にショットキー接合される。

【0019】

望ましくは、ゲート電極の第2の領域は、リセスの底を成す誘電層とショットキー接合され、順方向バイアス電圧の印加時、リセスの底を挟む窒化物半導体層への電流の供給を増加させる。

【0020】

望ましくは、ゲート電極の第2の領域は、リセスからドレイン方向へ延設されたフィールドプレート部を備え、該フィールドプレート部は、ドレイン方向の誘電層の一部を覆うように形成される。

【0021】

本発明によれば、窒化物半導体層は、基板上部に配設され、窒化ガリウム系列の材料を含む第1の窒化物層と、該第1の窒化物層上に異種接合され、該第1の窒化物層より広いエネルギバンドギャップを有する異種の窒化ガリウム系列の材料を含む第2の窒化物層と、を含む。

【0022】

本発明によれば、窒化物半導体素子は、基板と窒化物半導体層との間にバッファ層をさらに含む。

【0023】

本発明によれば、窒化物半導体素子は、パワートランジスタ素子である。

【0024】

また、上記目的を解決するために、本発明のさらに他の実施形態によれば、基板上部に、内部に2次元電子ガス(2DEG)チャネルを生成する窒化物半導体層を形成するステップと、該窒化物半導体層にオーミック接合されるドレイン電極と、該窒化物半導体層にドレイン電極と離間してショットキー接合されるソース電極を形成するステップと、該ドレイン電極と該ソース電極との間の窒化物半導体層上及び該ソース電極の少なくとも一部上にかけて誘電層を形成し、該ドレイン電極と該ソース電極との間にリセスを形成する誘電層を形成するステップと、該ドレイン電極と離間して誘電層上にゲート電極を形成し、ゲート電極の一部をソース電極のドレイン方向のエッジ部分上部の誘電層上に形成するステップと、を含む窒化物半導体素子の製造方法が提供される。

【0025】

本発明によれば、前記ゲート電極を形成するステップにおいて、ゲート電極は、リセスを通じて窒化物半導体層上にショットキー接合されるように形成される。

【0026】

本発明によれば、前記ゲート電極を形成するステップにおいて、順方向バイアス電圧の印加時、リセスの底を挟む窒化物半導体層への電流の供給を増加するように薄く形成されたリセスの底を成す誘電層とゲート電極とをショットキー接合させる。

【0027】

また、上記目的を解決するために、本発明のさらに他の実施形態によれば、基板上部に、内部に2次元電子ガス(2DEG)チャネルを生成する窒化物半導体層を形成するステップと、該窒化物半導体層にオーミック接合されるドレイン電極と、該窒化物半導体層にドレイン電極と離間してショットキー接合されるソース電極を形成するステップと、該ドレイン電極と該ソース電極との間の窒化物半導体層上及び該ソース電極の少なくとも一部上にかけて誘電層を形成し、該ドレイン電極と該ソース電極との間にリセスを形成する誘電層を形成するステップと、該誘電層を挟んでソース電極のドレイン方向へのエッジ部分上部に形成された第1の領域、及び該ドレイン電極と該ソース電極との間の誘電層上にドレイン電極と離間し、リセスに形成された第2の領域を含むゲート電極を形成するステップと、を含む窒化物半導体素子の製造方法が提供される。

【0028】

本発明によれば、前記ゲート電極を形成するステップにおいて、第1の領域及び第2の領域に分離してゲート電極を形成する。

【0029】

望ましくは、前記ゲート電極を形成するステップにおいて、該ゲート電極の第2の領域は、リセスを通じて窒化物半導体層上にショットキー接合されるように形成される。

【0030】

望ましくは、前記ゲート電極を形成するステップにおいて、順方向バイアス電圧の印加時、リセスの底を挟む窒化物半導体層への電流の供給が増加するように薄く形成されたリセスの底を成す誘電層とゲート電極の第2の領域とをショットキー接合させる。

【発明の効果】

【0031】

本発明によれば、半導体素子、例えばFETのソース領域にショットキー電極を形成し、ゲート電極をソース電極の一部領域及び窒化物半導体の領域の一部に形成し、該ドレイン電極と該ソース電極との間の誘電層によって形成されたリセス上にゲート電極の一部を形成することによって、ノーマリ−オフまたは、エンハンスメントモード動作し、リセス上に形成されたショットキーゲート電極を通じる電流供給を増加させ、オン抵抗を低め、高電流で動作する半導体素子を得ることができる。

【0032】

また、本発明によれば、既存のGaNノーマリ−オフ素子に比べて高耐圧動作が可能で、製造工程が簡単で、素子の製作が容易になる。すなわち、従来のノーマリ−オフHEMTのイオン注入、200〜300オングストロング厚さを有するAlGaN層に対するエッチングなどの高難易度の工程が必要ではなく、その製作が容易になる。

【0033】

また、本発明によれば、ソース電極のショットキー障壁によってリーク電流が防止される構造によって、既存のノーマリ−オフHEMTに比べてリーク電流が低く、耐圧が高くなるという効果が奏する。

【0034】

また、本発明によれば、ドレイン電極とソース電極との間の誘電層によって形成されるリセス領域に形成されたショットキーゲート電極によって、電流量が増加してオン抵抗を低くするという効果が奏する。それによって、高電流動作が可能になる。

【0035】

また、本発明によれば、ゲート構造によって、電界が分散して耐圧を高めることができる。また、ソース電極とゲート電極との間の距離が短く、トランスコンダクタンス(transconductance)の高くなる長所がある。

【図面の簡単な説明】

【0036】

【図1】本発明の一実施形態による窒化物半導体素子の概略的な断面図である。

【図2】本発明の他の実施形態による窒化物半導体素子の概略的な断面図である。

【図3a】図1の窒化物半導体素子の製造方法を示す断面図である。

【図3b】図1の窒化物半導体素子の製造方法を示す断面図である。

【図3c】図1の窒化物半導体素子の製造方法を示す断面図である。

【図3d】図1の窒化物半導体素子の製造方法を示す断面図である。

【図3e】図1の窒化物半導体素子の製造方法を示す断面図である。

【図4a】本発明のさらに他の実施形態による窒化物半導体素子の概略的な断面図である。

【図4b】本発明のさらに他の実施形態による窒化物半導体素子の概略的な断面図である。

【図5a】本発明のさらに他の実施形態による窒化物半導体素子の概略的な断面図である。

【図5b】本発明のさらに他の実施形態による窒化物半導体素子の概略的な断面図である。

【図6】従来の高電子移動度HEMT構造を示す断面図である。

【図7】従来の高電子移動度HEMT構造を示す断面図である。

【発明を実施するための形態】

【0037】

以下、本発明の好適な実施の形態は、図面を参考にして詳細に説明する。次に示される各実施の形態は、当業者にとって本発明の思想が十分に伝達されることができるようにするために例として挙げられるものである。従って、本発明は、以下示している各実施の形態に限定されることなく他の形態で具体化されることができる。そして、図面において、装置の大きさ及び厚さなどは、便宜上誇張して表現されることができる。明細書全体に渡って同一の参照符号は、同一の構成要素を示している。

【0038】

本明細書で使われた用語は、実施形態を説明するためのものであって、本発明を制限しようとするものでは、ない。本明細書において、単数形は、文句で特別に言及しない限り複数形も含む。明細書で使われる「含む」とは、言及された構成要素、ステップ、動作及び/又は、素子は、一つ以上の他の構成要素、ステップ、動作及び/又は、素子の存在または、追加を排除しないことに理解されたい。

【0039】

図1は、本発明の一実施形態による窒化物半導体素子の概略的な断面図である。図2は、本発明の他の実施形態による窒化物半導体素子の概略的な断面図である。図3a〜図3eは、図1の窒化物半導体素子の製造方法を示す断面図である。図4a及び図4bは、本発明のさらに他の実施形態による窒化物半導体素子の概略的な断面図である。図5a及び図5bは、本発明のさらに他の実施形態による窒化物半導体素子の概略的な断面図である。

【0040】

まず、図1、図2、図4a及び図4b、図5a及び図5bを参照して、本発明の一実施形態による窒化物半導体素子を詳記する。

【0041】

図1、図2、図4a及び図4b、図5a及び図5bに示すように、本発明の一実施形態による窒化物半導体素子は、基板10上部に配設された窒化物半導体層30、ドレイン電極50、ソース電極60、誘電層40及びゲート電極70を含む。

【0042】

図1、図2、図4a及び図4b、図5a及び図5bに示すように、本実施形態において、窒化物半導体層30は、基板10上部に配設される。基板10は、一般に絶縁基板を用いて、実に絶縁性及び高抵抗性を有する基板を用いてもよい。望ましくは、基板10は、シリコン(Si)、シリコンカーバイド(SiC)及びサファイヤ(Al2O3)のうちの少なくともいずれか一つを用いて製造されてもよく、公知の他の基板材料を用いて製造されてもよい。

【0043】

窒化物半導体層30は、基板10上部に直接形成されてもよい。望ましくは、窒化物半導体層30は、単結晶薄膜をエピタキシャル成長させて形成する。窒化物半導体層30を形成するためのエピタキシャル成長工程としては、液相成長法(LPE:Liquid Phase Epitaxy)、化学気相蒸着法(CVD:Chemical Vapor Deposition)、分子ビーム成長法(MBE:Molecular Beam Epitaxy)、有機金属気相蒸着法(MOCVD:Metalorganic CVD)などが挙げられる。

【0044】

また、図4a及び図4bに示すように、本発明の他の実施形態によれば、基板10と窒化物半導体層30との間にバッファ層20を設け、窒化物半導体層30をバッファ層20上に形成する。バッファ層20は、基板10と窒化物半導体層30との格子不整合(lattice mismatch)による問題点を解決するために提供される。バッファ層20は、一つの層だけではなく、窒化ガリウム(GaN)、アルミニウム窒化ガリウム(AlGaN)、窒化アルミニウム(AlN)、インジウム窒化ガリウム(InGaN)、インジウムアルミニウム窒化ガリウム(InAlGaN)などを含む複数の層で形成されてもよい。また、バッファ層20は、窒化ガリウム以外の他の3−5族化合物半導体によって形成されてもよい。例えば、基板10がサファイヤ基板10の場合、窒化ガリウムを含む窒化物半導体層30との格子定数及び熱膨脹係数の差によって誤整合(mismatch)されることを防ぐため、バッファ層20の成長は重要である。

【0045】

図1、図2、図4a及び図4b、図5a及び図5bに示すように、窒化物半導体層30の内部には2次元電子ガス(2DEG)チャネル35が形成される。窒化物半導体素子のゲート電極70にバイアス電圧を印加すると、窒化物半導体層30内の2DEGチャネル35を通じて電子が移動し、電流がドレイン電極50とソース電極60との間に流れるようになる。窒化物半導体層30を成す窒化物としては、窒化ガリウム(GaN)、アルミニウム窒化ガリウム(AlGaN)、インジウム窒化ガリウム(InGaN)、インジウムアルミニウム窒化ガリウム(InAlGaN)などが挙げられる。

【0046】

本発明の実施形態によれば、窒化物半導体層30は、異種接合された窒化ガリウム系列の半導体層30であって、異種接合された界面でエネルギバンドギャップの差によって2次元電子ガスチャネル35が形成される。異種接合される窒化ガリウム系列の半導体層30で異種接合間の格子定数の差が小さいほど、バンドギャップとの極性の差が減るようになり、2DEGチャネル35の形成が抑制される。異種接合の時、エネルギバンドギャップの不連続性によって広いバンドギャップを有する材料から小さなバンドギャップを有する材料への自由電子が移動するようになる。このような電子は、異種接合界面に蓄積されて2DEGチャネル35を形成し、ドレイン電極50とソース電極60との間で電流が流れるようにする。

【0047】

より詳しくは、図1、図2、図4a及び図4b、図5a及び図5bに示すように、窒化物半導体層30は、第1の窒化物層31及び第2の窒化物層33を含む。第1の窒化物層31は、基板10上部に配設され、窒化ガリウム系列の材料を含む。第2の窒化物層33は、第1の窒化物層31上に異種接合され、該第1の窒化物層31より広いエネルギバンドギャップを有する異種の窒化ガリウム系列の材料を含む。この時、第2の窒化物層33は、第1の窒化物層31内に形成される2DEGチャネル35へ電子を供給する役割をする。一例として、電子を供与する第2の窒化物層33は、第1の窒化物層31より薄い厚さで形成されることが望ましい。

【0048】

望ましくは、本発明の他の実施形態によれば、第1の窒化物層31は、窒化ガリウム(GaN)を含み、第2の窒化物層33は、アルミニウム窒化ガリウム(AlGaN)、インジウム窒化ガリウム(InGaN)及びインジウムアルミニウム窒化ガリウム(InAlGaN)のうちのいずれか一つを含む。望ましくは、一例として、第1の窒化物層31は、窒化ガリウム(GaN)を含み、第2の窒化物層33は、アルミニウム窒化ガリウム(AlGaN)を含む。

【0049】

続いて、図1、図2、図4a及び図4b、図5a及び図5bを参照して、本発明の実施形態の構成がより詳しく説明する。

【0050】

図1、図2、図4a及び図4b、図5a及び図5bに示すように、本実施形態による窒化物半導体素子のドレイン電極50及びソース電極60が窒化物半導体層30に形成される。ドレイン電極50は、窒化物半導体層30にオーミック接合50aされている。

【0051】

ソース電極60は、ドレイン電極50と離間して配設され、窒化物半導体層30にショットキー接合60aされる。ショットキーソース電極60によって、逆方向に駆動される時、ソース電極60のショットキー接合領域60aで生成される空乏領域によって2次元電子ガス(2DEG)による電流の流れを安定して遮断することができる。そのため、逆方向電流の流れを遮断することができ、ノーマリ−オフ状態を具現することができるようになる。より詳しくは、逆方向バイアス電圧が印加された場合、ソース電極60のショットキー接合領域60aで生成される空乏領域が2DEGチャネル35領域まで拡張され、2DEGチャネル35を遮断し、逆方向の降伏電圧を増加させるようになる。特に、逆方向バイアス電圧の印加時、ソース電極60のドレイン側のコーナー寄りのショットキー接合領域60aで空乏領域が大きく拡張される。一方、順方向バイアス電圧をかけると、ソース電極60のショットキー接合領域60aで生成される空乏領域が小さくなり、2DEGチャネル35を通じてドレイン電極50とソース電極60との間に電流が流れるようになる。

【0052】

続いて、図1、図2、図4a及び図4b、図5a及び図5bに示すように、本発明の一実施形態による窒化物半導体素子の誘電層40は、ドレイン電極50とソース電極60との間の窒化物半導体層30上及びソース電極60の少なくとも一部上にかけて形成される。この時、誘電層40は、ドレイン電極50とソース電極60との間でリセスを形成する。望ましくは、図1、図4a及び図5aに示すように、リセス領域41は、誘電層40を貫いて窒化物半導体層30の底を成すように形成されてもよい。または、図2、図4b及び図5bに示すように、リセス領域42は、誘電層40の一部領域を、例えばエッチングして形成し、窒化物半導体層30上に薄い膜を残して形成されてもよい。望ましくは、誘電層40は、酸化膜からなり、一実施形態によれば、SiN、SiO2、Al2O3のうちの少なくともいずれか一つを含むことができる。

【0053】

続いて、図1、図2、図4a及び図4b、図5a及び図5bに示すように、本実施形態による窒化物半導体素子のゲート電極70は、ドレイン電極50と離間して誘電層40上に配設される。また、ゲート電極70の一部71、71’が誘電層40を挟んでソース電極60のドレイン方向へのエッジ部分上部に形成される。望ましくは、ゲート電極70は、誘電層40上にショットキー接合70aされる。ゲート電極70に順方向バイアスの電圧が印加されると、ソース電極60のドレイン側のコーナー寄りのショットキー接合領域60aで形成される空乏領域が小さくなり、2DEGチャネル35を通じてドレイン電極50とソース電極60との間に電流が流れるようになる。

【0054】

なお、ゲート電極70の一部73、73’は、誘電層40によって形成されたリセス領域41、42に配設されるように形成される。これによって、リセス領域41、42に形成されたショットキーゲート電極70を通じて窒化物半導体層30との電流キャリアの移動が容易になり、電流量が増加し、オン抵抗が低くなる。

【0055】

また、図1、図2、図4a及び図4bに示すように、ゲート構造がソース電極60のエッジ部分上部及びドレイン電極50とソース電極60との間の誘電層40上に亘っており、電界が分散するという効果があり、ドレイン電極50とソース電極60との間の誘電層40上に掛っているゲート構造自体が耐圧を高めるフィールドプレートの役割を果たすようになる。

【0056】

望ましくは、図1及び図4aを参照して、本発明の他の実施形態において、ゲート電極70は、リセス41を通じて窒化物半導体30層上にショットキー接合70aされる。これによって、ゲート電極70に閾値電圧以上のバイアス電圧を印加すると、開放された誘電層40の領域に形成されたショットキーゲート電極70を通じて電流キャリアの移動が容易になり、電流量が増加するようになる。よって、オン抵抗が低くなり、高電流動作が可能になる。

【0057】

また、望ましくは、図2及び図4bに示すように、本発明のさらに他の実施形態において、ゲート電極70は、リセス42の底を成す誘電層40とショットキー接合70aされて、順方向バイアス電圧の印加時、リセス42の底を挟む窒化物半導体層30への電流の供給を増加させる。これによって、ゲート電極70に閾値電圧以上のバイアス電圧を印加すると、薄いリセス42の底を成す誘電層40とショットキー接合70aされたゲート電極70を通じて窒化物半導体層30との電流キャリアの移動が容易になり、電流量が増加するようになる。よって、オン抵抗が低くなり、高電流動作が可能になる。

【0058】

また、望ましくは、図1、図2、図4a及び図4bに示すように、本発明の他の実施形態において、ゲート電極70は、リセス41、42からドレイン方向で延設されたフィールドプレート部173を備える。フィールドプレート部173は、ドレイン方向の誘電層40の一部を覆うように形成される。フィールドプレート部173は、ゲート電極70のリセス領域41、42に形成された縁部に集中される電界を分散させるという効果が奏する。

【0059】

また、図1、図2、図4a及び図4b、図5a及び図5bを参照して、本発明の他の実施形態について説明する。

【0060】

図1、図2、図4a及び図4b、図5a及び図5bに示すように、本発明の一実施形態による窒化物半導体素子は、基板10上部に配設された窒化物半導体層30、ドレイン電極50、ソース電極60、誘電層40及びゲート電極70を含む。窒化物半導体層30、ドレイン電極50、ソース電極60及び誘電層40については、前述のようである。

【0061】

本実施形態において、ゲート電極70は、第1の領域71、71’及び第2の領域73、73’を備える。第1の領域71、71’は、誘電層40を挟んでソース電極60のドレイン方向へのエッジ部分上部に形成されている。第2の領域73、73’は、ドレイン電極50とソース電極60との間の誘電層40上にドレイン電極50と離間して配設される。この時、第2の領域73、73’は、誘電層40によってドレイン電極50とソース電極60との間で形成されるリセス領域41、42上にも配設されるように形成される。第1の領域と第2の領域とは、図1、図2、図4a及び図4bに示すように、一体に形成されてもよく、図5a、図5bに示すように分離されてもよい。

【0062】

望ましくは、図5a及び図5bに示すように、本発明の他の実施形態によれば、ゲート電極70の第1の領域71’及び第2の領域73’は、分離されている。第2の領域73’によって電界が分散されるという効果が奏する。望ましくは、第2の領域73’は、ドレイン電極50よりソース電極60に近く配設される。

【0063】

図5a及び図5bに示されていないが、本発明の他の実施形態によれば、図4a及び図4bと同様に、基板10と窒化物半導体層30との間にバッファ層20を設け、窒化物半導体層30を該バッファ層20上に形成してもよい。

【0064】

望ましくは、図5aに示すように、他の実施形態によれば、ゲート電極70の第2の領域73’は、リセス41を通じて窒化物半導体30層上にショットキー接合70aされる。これによって、ゲート電極70に閾値電圧以上のバイアス電圧を印加すると、開放された誘電層40の領域に形成されたショットキーゲート電極の第2の領域73’を通じて電流キャリアの移動が容易になり電流量が増加し、オン抵抗が低くなるようになる。

【0065】

また、望ましくは、図5bに示すように、他の実施形態によれば、ゲート電極70の第2の領域73’は、リセス42の底を成す誘電層40とショットキー接合70aされ、順方向バイアス電圧の印加時、リセス42の底を挟む窒化物半導体層30への電流の供給を増加させる。これによって、閾値電圧以上のバイアス電圧を印加すると、薄いリセス42の底を成す誘電層40とショットキー接合70aされたゲート電極の第2の領域73’を通じて窒化物半導体層30との電流キャリアの移動が容易になり、電流量が増加し、オン抵抗が低くなるようになる。

【0066】

また、望ましくは、図5a及び図5bに示すように、他の実施形態によれば、ゲート電極70の第2の領域73’は、リセス41、42からドレイン方向へ延設されたフィールドプレート部173を備える。該フィールドプレート部173は、ドレイン方向の誘電層40の一部を覆うように形成される。これによって、フィールドプレート部173は、ゲート電極の第2の領域73’のリセス領域41、42に形成された縁部に集中される電界を分散させるという効果が奏する。

【0067】

図1、図2、図4a及び図4b、図5a及び図5bに示す本発明の実施形態によれば、ゲート電極70に0Vの電圧を印加すると、ドレイン電極50とソース電極60との間に2DEGチャネル35を通じる電流の流れがソース電極60領域のショットキー障壁によって遮られる。そして、ゲート電極70に閾値電圧以上を印加すると、ソース電極60のドレイン方向のエッジ領域にキャリア(電子)の濃度が高くなり、トンネリング(tunneling)現象によって電流が流れるようになる。この時、ゲートの閾値電圧は、誘電層40の厚さなどによって決まる。これによって、既存のノーマリ−オフHEMT構造に比べて製作が容易で、リーク電流が少なく、高い耐圧特性を現わすようになる。

【0068】

また、誘電層40によって形成されたリセス領域41、42にゲート電極70の一部を形成させ、ゲート電極70に閾値電圧以上のバイアス電圧を印加すると、リセス領域41、42に形成されたショットキーゲート電極70を通じて窒化物半導体層30との電流キャリアの移動が容易になり、電流量が増加するようになる。よって、オン抵抗が低くなり、高電流動作が可能になる。

【0069】

本発明の他の実施形態によれば、前述の実施形態による窒化物半導体素子は、パワートランジスタ素子である。本発明の実施形態によるパワートランジスタは、水平型HEMT構造を備える。

【0070】

次に、本発明の他の実施形態による窒化物半導体製造方法を図面を参照して説明する。本発明による窒化物半導体製造方法を説明するに当たって、図3a〜図3eの他に、前述の実施形態による窒化物半導体素子及び図1、図2、図4a及び図4b、図5a及び図5bを参照する。反対の場合も同様である。本発明の窒化物半導体素子の製造方法に関する具体的な実施形態に対して、以下説明されないことは、前述と同様であるため、重複する説明は省略する。

【0071】

図3a〜図3eは、本発明の他の実施形態による窒化物半導体の製造方法を示す。

【0072】

望ましくは、本発明の実施形態によれば、窒化物半導体素子の製造方法によって製造される素子は、パワートランジスタである。

【0073】

まず、図3aに示すように、基板10上部に、内部に2次元電子ガス(2DEG)チャネル35を生成する窒化物半導体層30を形成する。望ましくは、基板10は、シリコン(Si)、シリコンカーバイド(SiC)、サファイヤ(Al2O3)のうちの少なくともいずれか一つを用いて製造されてもよい。窒化物半導体層30を成す窒化物としては、窒化ガリウム(GaN)、アルミニウム窒化ガリウム(AlGaN)、インジウム窒化ガリウム(InGaN)、インジウムアルミニウム窒化ガリウム(InAlGaN)などが挙げられる。

【0074】

望ましくは、窒化物半導体層30は、窒化物単結晶薄膜をエピタキシャル成長させて形成される。望ましくは、エピタキシャル成長の時、選択的に成長させて過成長されないように調節する。仮に、過成長された場合には、エッチバック(etchback)工程やCMP(Chemical Mechanical Polishing)工程を用いて平坦化する過程を追加してもよい。

【0075】

望ましくは、本発明の実施形態によれば、図3aに示された第1の窒化物層31及び第2の窒化物層33は、エピタキシャル成長工程(Epitaxial Growth Precess)によって形成される。まず、第1の窒化物層31は、基板10上部に窒化ガリウム系列単結晶薄膜をエピタキシャル成長させて形成する。望ましくは、本発明の他の実施形態によれば、第1の窒化物層31は、窒化ガリウム(GaN)をエピタキシャル成長させて形成する。続いて、第2の窒化物層33は、第1の窒化物層31をシード層として第1の窒化物層31より広いエネルギバンドギャップを有する異種の窒化ガリウム系列の材料を含む窒化物層をエピタキシャル成長させて形成する。望ましくは、本発明の他の実施形態によれば、第2の窒化物層33は、アルミニウム窒化ガリウム(AlGaN)、インジウム窒化ガリウム(InGaN)及びインジウムアルミニウム窒化ガリウム(InAlGaN)のうちのいずれか一つを含む窒化ガリウム系列単結晶をエピタキシャル成長させて形成する。望ましくは、第2の窒化物層33は、アルミニウム窒化ガリウム(AlGaN)をエピタキシャル成長させて形成する。一例として、電子を供与する第2の窒化物層33は、第1の窒化物層31より薄い厚さで形成されることが望ましい。

【0076】

第1及び第2の窒化物層33を形成するためのエピタキシャル成長工程としては、液相成長法、化学気相蒸着法、分子ビーム成長法、有機金属気相蒸着法などが挙げられる。

【0077】

次に、図3bに示すように、窒化物半導体層30にドレイン電極50とソース電極60とを形成する。図3bにおいて、ドレイン電極50は、窒化物半導体層30にオーミック接合50されるように形成する。該オーミック接合を完成するために熱処理を行ってもよい。窒化膜半導体層30上に金(Au)、ニッケル(Ni)、白金(Pt)、チタン(Ti)、アルミニウム(Al)、パラジウム(Pd)、イリジウム(Ir)、ロジウム(Rh)、コバルト(Co)、タングステン(W)、モリブデン(Mo)、タンタル(Ta)、銅(Cu)及び亜鉛(Zn)のうちの少なくともいずれか一つの金属、金属シリサイド及びこれらの合金を用いてドレイン金属電極を形成してもよい。ドレイン電極50は、多層構造で形成されてもよい。

【0078】

ソース電極60は、ドレイン電極50と離間して窒化物半導体層30にショットキー接合60aされるように形成する。ショットキー接合60aされるソース電極60は、窒化膜半導体層30とショットキー接合可能な材料、例えば、アルミニウム(Al)、モリブデン(Mo)、金(Au)、ニッケル(Ni)、白金(Pt)、チタン(Ti)、パラジウム(Pd)、イリジウム(Ir)、ロジウム(Rh)、コバルト(Co)、タングステン(W)、タンタル(Ta)、銅(Cu)及び亜鉛(Zn)のうちの少なくともいずれか一つの金属、金属シリサイド及びこれらの合金を用いて形成されてもよい。ソース電極60は、多層構造で形成されてもよい。ソース電極60で金属と半導体接合を有するショットキー接合60aを用いて、ドレイン電極50とソース電極60との間に2DEGチャネル35を通じる逆方向の電流を遮断することができる。

【0079】

一例として、ドレイン電極50及びソース電極60の形成過程について説明する。基板10上部にエピタキシャル成長によって形成された窒化物半導体層30上に電極を形成するための金属層を、電子ビーム蒸着器などによって蒸着形成し、該金属層上にフォトレジストパターンを形成する。続いて、該フォトレジストパターンをエッチングマスクとして金属層をエッチングし、フォトレジストパターンを取り除いて金属電極50、60を形成する。

【0080】

図3cに示すように、本発明の一実施形態によれば、ドレイン電極50及びソース電極60を形成した後、ドレイン電極50とソース電極60との間の窒化物半導体層30上に誘電層40を形成する。この時、誘電層40は、少なくともソース電極60の一部上に、望ましくは、ドレイン電極50方のソース電極60の一部上にかけて形成される。望ましくは、誘電層40は、酸化膜からなってもよく、SiN、SiO2及びAl2O3のうちの少なくともいずれか一つからなってもよい。

【0081】

また、図3dに示すように、ドレイン電極50とソース電極60との間に塗布形成された誘電層40にリセス41を形成する。例えば、リセス41はエッチング工程によって設けられる。望ましくは、リセス領域41は、誘電層40を貫いて窒化物半導体層30が底を成すように形成されてもよく、リセス領域42は、誘電層40の一部領域をエッチングして形成するものの、窒化物半導体層30上に薄い膜を残しておくように形成されてもよい。

【0082】

図3eに示すように、本発明の一実施形態によれば、図3c及び図3dの誘電層40を形成した後、ドレイン電極50と離間して誘電層40上にゲート電極70を形成する。そして、ゲート電極70の一部がソース電極60のドレイン方向のエッジ部分上部の誘電層40上に形成されるようにする。ゲート電極70は、アルミニウム(Al)、モリブデン(Mo)、金(Au)、ニッケル(Ni)、白金(Pt)、チタン(Ti)、パラジウム(Pd)、イリジウム(Ir)、ロジウム(Rh)、コバルト(Co)、タングステン(W)、タンタル(Ta)、銅(Cu)及び亜鉛(Zn)のうちの少なくともいずれか一つの金属、金属シリサイド及びこれらの合金を用いて形成されてもよい。ゲート電極70は、ドレイン電極50及び/またはソース電極60と異なる金属を使ってもよく、多層構造に形成されてもよい。望ましくは、ゲート電極70は、誘電層40上にショットキー接合70aされる。

【0083】

なお、ゲート電極70の一部73、73’は、誘電層40によって形成されたリセス領域41、42に配設されるように形成される。これによって、リセス領域41、42に形成されたショットキーゲート電極70を通じて窒化物半導体層30との電流キャリアの移動が容易になり、電流量が増加し、オン抵抗が低くなるようになる。

【0084】

ゲート電極70の形成過程について説明する、誘電層40上に電極を形成するための金属層を電子ビーム蒸着器などによって蒸着形成し、該金属層上にフォトレジストパターンを形成する。そして、該フォトレジストパターンをエッチングマスクとして金属層をエッチングする。エッチング後、フォトレジストパターンを取り除いて金属電極を形成する。

【0085】

望ましくは、図3e、図1、図4a及び図5aに示すように、ゲート電極70の一部73または第2の領域73’は、リセス41を通じて窒化物半導体30層上にショットキー接合70aされるように形成される。これによって、ゲート閾値電圧以上のバイアス電圧を印加すると、開放された誘電層40の領域に形成されたショットキーゲート電極部分73、73’を通じて電流キャリアの移動が容易になり、電流量が増加し、オン抵抗が低くなるようになる。

【0086】

また、さらに他の実施形態によれば、図2、図4b及び図5bに示すように、ゲート順方向のバイアス電圧を印加すると、リセス42の底を挟む窒化物半導体層30への電流の供給が増加するように、ゲート電極の一部73または第2の領域73’は、リセス42の底を成す誘電層40とショットキー接合70aされるように形成する。これによって、閾値電圧以上のバイアス電圧を印加すると、薄いリセス42の底を成す誘電層40とショットキー接合70aされたゲート電極部分73、73’を通じて窒化物半導体層30との電流キャリアの移動が容易になり、電流量が増加し、オン抵抗が低くなるようになる。

【0087】

また、望ましくは、ゲート電極70の一部領域73または第2の領域73’は、リセス41、42からドレイン方向へ延設されたフィールドプレート部173を備える。この時、フィールドプレート部173は、ドレイン方向の誘電層40の一部を覆うように形成される。これによって、フィールドプレート部173は、ゲート電極近隣73、73’のリセス領域41、42に形成された縁部に集中される電界を分散させるという効果が奏する。

【0088】

また、図3e、図1、図2、図4a及び図4b、図5a及び図5bに示すように、他の実施形態によれば、ゲート電極70は、第領域71、71’及び第2の領域73、73’を備える。ゲート電極70の第1の領域71、71’は、ソース電極60のドレイン方向のエッジ部分上部で誘電層40を挟み、第2の領域73、73’は、ドレイン電極50とソース電極60との間の誘電層40上にドレイン電極50と離間して配設されるようにゲート電極70を形成する。この時、第2の領域73、73’は、誘電層40によってドレイン電極50とソース電極60との間で形成されるリセス領域41、42上にも配設される。第1の領域及び第2の領域は、図1、図2、図4a及び図4bに示すように、一体に形成されてもよく、図5a及び図5bに示すように分離されて形成されてもよい。

【0089】

図5a及び図5bに示すように、ゲート電極70を形成するステップにおいて、第1の領域71’及び第2の領域73’を分離してゲート電極70を形成する。

【0090】

図5a及び図5bに示す追加的な実施形態に対する説明は、前述と同様である。

【0091】

望ましくは、他の実施形態によれば、図3aの基板10上部に窒化物半導体層30を形成する前に、基板10上部にバッファ層20を形成するステップをさらに含む。該バッファ層20は、基板10と窒化物半導体層30との格子不整合による問題点を解決するために提供される。バッファ層20は、一つの層だけではなく、窒化ガリウム(GaN)、アルミニウム窒化ガリウム(AlGaN)、窒化アルミニウム(AlN)、インジウム窒化ガリウム(InGaN)、インジウムアルミニウム窒化ガリウム(InAlGaN)などを含む複数の層で形成されてもよい。

【0092】

今回開示された実施の形態は、すべての点で例示であって制限的なものでは、ないと考えられるべきである。本発明の範囲は、前記した実施の形態の説明では、なくて特許請求の範囲によって示され、特許請求の範囲と均等の意味及び範囲内でのすべての変更が含まれることが意図される。

【符号の説明】

【0093】

10 基板

20 バッファ層

30 窒化物半導体層

31 第1の窒化物層

33 第2の窒化物層

35 2DEGチャネル

40 誘電層

41、42 リセス領域

50 ドレイン電極

60 ソース電極

70 ゲート電極

【特許請求の範囲】

【請求項1】

基板上部に配設され、内部に2次元電子ガスチャネルを形成する窒化物半導体層と、

前記窒化物半導体層にオーミック接合されたドレイン電極と、

前記ドレイン電極と離間して配設され、前記窒化物半導体層にショットキー接合されたソース電極と、

前記ドレイン電極と前記ソース電極との間の前記窒化物半導体層上及び前記ソース電極の少なくとも一部上にかけて形成され、前記ドレイン電極と前記ソース電極との間にリセスを形成する誘電層と、

前記ドレイン電極と離間して前記誘電層上及び前記リセスに配設され、一部が前記誘電層を挟んで前記ソース電極のドレイン方向へのエッジ部分上部に形成されたゲート電極と

を含む窒化物半導体素子。

【請求項2】

前記ゲート電極は、前記リセスを通じて前記窒化物半導体層上にショットキー接合されることを特徴とする請求項1に記載の窒化物半導体素子。

【請求項3】

前記ゲート電極は、前記リセスの底を成す前記誘電層とショットキー接合され、順方向バイアス電圧の印加時、前記リセスの底を挟む前記窒化物半導体層への電流の供給を増加させることを特徴とする請求項1に記載の窒化物半導体素子。

【請求項4】

前記ゲート電極は、前記リセスからドレイン方向へ延設されたフィールドプレート部を備え、該フィールドプレート部は、前記ドレイン方向の前記誘電層の一部を覆うように形成されたことを特徴とする請求項1に記載の窒化物半導体素子。

【請求項5】

前記窒化物半導体層は、

前記基板上部に配設され、窒化ガリウム系列の材料を含む第1の窒化物層と、

前記第1の窒化物層上に異種接合され、前記第1の窒化物層より広いエネルギバンドギャップを有する異種の窒化ガリウム系列の材料を含む第2の窒化物層と、を含むことを特徴とする請求項1に記載の窒化物半導体素子。

【請求項6】

基板上部に配設され、内部に2次元電子ガスチャネルを形成する窒化物半導体層と、

前記窒化物半導体層にオーミック接合されたドレイン電極と、

前記ドレイン電極と離間して配設され、前記窒化物半導体層にショットキー接合されたソース電極と、

前記ドレイン電極と前記ソース電極との間の前記窒化物半導体層上及び前記ソース電極の少なくとも一部上にかけて形成され、前記ドレイン電極と前記ソース電極との間にリセスを形成する誘電層と、

前記誘電層を挟んで前記ソース電極のドレイン方向へのエッジ部分上部に形成された第1の領域、及び前記ドレイン電極と前記ソース電極との間の前記誘電層上で前記ドレイン電極と離間して、前記リセスに形成された第2の領域を含むゲート電極と

を含む窒化物半導体素子。

【請求項7】

前記ゲート電極は、前記第1の領域と前記第2の領域とに分離形成されることを特徴とする請求項6に記載の窒化物半導体素子。

【請求項8】

前記ゲート電極の第2の領域は、前記リセスを通じて前記窒化物半導体層上にショットキー接合されることを特徴とする請求項7に記載の窒化物半導体素子。

【請求項9】

前記ゲート電極の第2の領域は、前記リセスの底を成す前記誘電層とショットキー接合され、順方向バイアス電圧の印加時、前記リセスの底を挟む前記窒化物半導体層への電流の供給を増加させることを特徴とする請求項7に記載の窒化物半導体素子。

【請求項10】

前記ゲート電極の第2の領域は、前記リセスからドレイン方向へ延設されたフィールドプレート部を備え、該フィールドプレート部は、前記ドレイン方向の前記誘電層の一部を覆うように形成されたことを特徴とする請求項7に記載の窒化物半導体素子。

【請求項11】

前記窒化物半導体層は、

前記基板上部に配設され、窒化ガリウム系列の材料を含む第1の窒化物層と、

前記第1の窒化物層上に異種接合され、前記第1の窒化物層より広いエネルギバンドギャップを有する異種の窒化ガリウム系列の材料を含む第2の窒化物層とを含むことを特徴とする請求項6に記載の窒化物半導体素子。

【請求項12】

前記窒化物半導体素子は、前記基板と前記窒化物半導体層との間にバッファ層をさらに含むことを特徴とする請求項1〜11のうちの少なくともいずれか一つに記載の窒化物半導体素子。

【請求項13】

前記窒化物半導体素子は、パワートランジスタ素子であることを特徴とする請求項1〜11のうちの少なくともいずれか一つに記載の窒化物半導体素子。

【請求項14】

基板上部に、内部に2次元電子ガスチャネルを生成する窒化物半導体層を形成するステップと、

前記窒化物半導体層にオーミック接合されるドレイン電極と、前記窒化物半導体層に前記ドレイン電極と離間してショットキー接合されるソース電極を形成するステップと、

前記ドレイン電極と前記ソース電極との間の前記窒化物半導体層上及び前記ソース電極の少なくとも一部上にかけて誘電層を形成し、前記ドレイン電極と前記ソース電極との間でリセスを形成する前記誘電層を形成するステップと、

前記ドレイン電極と離間して前記誘電層上及び前記リセスにゲート電極を形成し、前記ゲート電極の一部を前記ソース電極のドレイン方向のエッジ部分上部の前記誘電層上に形成するステップと

を含む窒化物半導体素子の製造方法。

【請求項15】

前記ゲート電極を形成するステップにおいて、前記ゲート電極は、前記リセスを通じて前記窒化物半導体層上にショットキー接合されるように形成されることを特徴とする請求項14に記載の窒化物半導体素子の製造方法。

【請求項16】

前記ゲート電極を形成するステップにおいて、順方向バイアス電圧の印加時、前記リセスの底を挟む前記窒化物半導体層への電流の供給を増加させるように薄く形成された前記リセスの底を成す前記誘電層と前記ゲート電極とをショットキー接合させることを特徴とする請求項14に記載の窒化物半導体素子の製造方法。

【請求項17】

基板上部に、内部に2次元電子ガスチャネルを生成する窒化物半導体層を形成するステップと、

前記窒化物半導体層にオーミック接合されるドレイン電極と、前記窒化物半導体層に前記ドレイン電極と離間してショットキー接合されるソース電極を形成するステップと、

前記ドレイン電極と前記ソース電極との間の前記窒化物半導体層上及び前記ソース電極の少なくとも一部上にかけて誘電層を形成し、前記ドレイン電極と前記ソース電極との間にリセスを形成する前記誘電層を形成するステップと、

前記誘電層を挟んで前記ソース電極のドレイン方向へのエッジ部分上部に形成された第1の領域、及び前記ドレイン電極と前記ソース電極との間の前記誘電層上に前記ドレイン電極と離間し、前記リセスに形成された第2の領域を含むゲート電極を形成するステップと

を含む窒化物半導体素子の製造方法。

【請求項18】

前記ゲート電極を形成するステップにおいて、前記第1の領域と前記第2の領域とを分離して前記ゲート電極を形成することを特徴とする請求項17に記載の窒化物半導体素子の製造方法。

【請求項19】

前記ゲート電極を形成するステップにおいて、前記ゲート電極の第2の領域は、前記リセスを通じて前記窒化物半導体層上にショットキー接合されるように形成されることを特徴とする請求項18に記載の窒化物半導体素子の製造方法。

【請求項20】

前記ゲート電極を形成するステップにおいて、順方向バイアス電圧の印加時、前記リセスの底を挟む前記窒化物半導体層への電流の供給を増加させるように薄く形成された前記リセスの底を成す前記誘電層と前記ゲート電極の第2の領域とをショットキー接合させることを特徴とする請求項18に記載の窒化物半導体素子の製造方法。

【請求項1】

基板上部に配設され、内部に2次元電子ガスチャネルを形成する窒化物半導体層と、

前記窒化物半導体層にオーミック接合されたドレイン電極と、

前記ドレイン電極と離間して配設され、前記窒化物半導体層にショットキー接合されたソース電極と、

前記ドレイン電極と前記ソース電極との間の前記窒化物半導体層上及び前記ソース電極の少なくとも一部上にかけて形成され、前記ドレイン電極と前記ソース電極との間にリセスを形成する誘電層と、

前記ドレイン電極と離間して前記誘電層上及び前記リセスに配設され、一部が前記誘電層を挟んで前記ソース電極のドレイン方向へのエッジ部分上部に形成されたゲート電極と

を含む窒化物半導体素子。

【請求項2】

前記ゲート電極は、前記リセスを通じて前記窒化物半導体層上にショットキー接合されることを特徴とする請求項1に記載の窒化物半導体素子。

【請求項3】

前記ゲート電極は、前記リセスの底を成す前記誘電層とショットキー接合され、順方向バイアス電圧の印加時、前記リセスの底を挟む前記窒化物半導体層への電流の供給を増加させることを特徴とする請求項1に記載の窒化物半導体素子。

【請求項4】

前記ゲート電極は、前記リセスからドレイン方向へ延設されたフィールドプレート部を備え、該フィールドプレート部は、前記ドレイン方向の前記誘電層の一部を覆うように形成されたことを特徴とする請求項1に記載の窒化物半導体素子。

【請求項5】

前記窒化物半導体層は、

前記基板上部に配設され、窒化ガリウム系列の材料を含む第1の窒化物層と、

前記第1の窒化物層上に異種接合され、前記第1の窒化物層より広いエネルギバンドギャップを有する異種の窒化ガリウム系列の材料を含む第2の窒化物層と、を含むことを特徴とする請求項1に記載の窒化物半導体素子。

【請求項6】

基板上部に配設され、内部に2次元電子ガスチャネルを形成する窒化物半導体層と、

前記窒化物半導体層にオーミック接合されたドレイン電極と、

前記ドレイン電極と離間して配設され、前記窒化物半導体層にショットキー接合されたソース電極と、

前記ドレイン電極と前記ソース電極との間の前記窒化物半導体層上及び前記ソース電極の少なくとも一部上にかけて形成され、前記ドレイン電極と前記ソース電極との間にリセスを形成する誘電層と、

前記誘電層を挟んで前記ソース電極のドレイン方向へのエッジ部分上部に形成された第1の領域、及び前記ドレイン電極と前記ソース電極との間の前記誘電層上で前記ドレイン電極と離間して、前記リセスに形成された第2の領域を含むゲート電極と

を含む窒化物半導体素子。

【請求項7】

前記ゲート電極は、前記第1の領域と前記第2の領域とに分離形成されることを特徴とする請求項6に記載の窒化物半導体素子。

【請求項8】

前記ゲート電極の第2の領域は、前記リセスを通じて前記窒化物半導体層上にショットキー接合されることを特徴とする請求項7に記載の窒化物半導体素子。

【請求項9】

前記ゲート電極の第2の領域は、前記リセスの底を成す前記誘電層とショットキー接合され、順方向バイアス電圧の印加時、前記リセスの底を挟む前記窒化物半導体層への電流の供給を増加させることを特徴とする請求項7に記載の窒化物半導体素子。

【請求項10】

前記ゲート電極の第2の領域は、前記リセスからドレイン方向へ延設されたフィールドプレート部を備え、該フィールドプレート部は、前記ドレイン方向の前記誘電層の一部を覆うように形成されたことを特徴とする請求項7に記載の窒化物半導体素子。

【請求項11】

前記窒化物半導体層は、

前記基板上部に配設され、窒化ガリウム系列の材料を含む第1の窒化物層と、

前記第1の窒化物層上に異種接合され、前記第1の窒化物層より広いエネルギバンドギャップを有する異種の窒化ガリウム系列の材料を含む第2の窒化物層とを含むことを特徴とする請求項6に記載の窒化物半導体素子。

【請求項12】

前記窒化物半導体素子は、前記基板と前記窒化物半導体層との間にバッファ層をさらに含むことを特徴とする請求項1〜11のうちの少なくともいずれか一つに記載の窒化物半導体素子。

【請求項13】

前記窒化物半導体素子は、パワートランジスタ素子であることを特徴とする請求項1〜11のうちの少なくともいずれか一つに記載の窒化物半導体素子。

【請求項14】

基板上部に、内部に2次元電子ガスチャネルを生成する窒化物半導体層を形成するステップと、

前記窒化物半導体層にオーミック接合されるドレイン電極と、前記窒化物半導体層に前記ドレイン電極と離間してショットキー接合されるソース電極を形成するステップと、

前記ドレイン電極と前記ソース電極との間の前記窒化物半導体層上及び前記ソース電極の少なくとも一部上にかけて誘電層を形成し、前記ドレイン電極と前記ソース電極との間でリセスを形成する前記誘電層を形成するステップと、

前記ドレイン電極と離間して前記誘電層上及び前記リセスにゲート電極を形成し、前記ゲート電極の一部を前記ソース電極のドレイン方向のエッジ部分上部の前記誘電層上に形成するステップと

を含む窒化物半導体素子の製造方法。

【請求項15】

前記ゲート電極を形成するステップにおいて、前記ゲート電極は、前記リセスを通じて前記窒化物半導体層上にショットキー接合されるように形成されることを特徴とする請求項14に記載の窒化物半導体素子の製造方法。

【請求項16】

前記ゲート電極を形成するステップにおいて、順方向バイアス電圧の印加時、前記リセスの底を挟む前記窒化物半導体層への電流の供給を増加させるように薄く形成された前記リセスの底を成す前記誘電層と前記ゲート電極とをショットキー接合させることを特徴とする請求項14に記載の窒化物半導体素子の製造方法。

【請求項17】

基板上部に、内部に2次元電子ガスチャネルを生成する窒化物半導体層を形成するステップと、

前記窒化物半導体層にオーミック接合されるドレイン電極と、前記窒化物半導体層に前記ドレイン電極と離間してショットキー接合されるソース電極を形成するステップと、

前記ドレイン電極と前記ソース電極との間の前記窒化物半導体層上及び前記ソース電極の少なくとも一部上にかけて誘電層を形成し、前記ドレイン電極と前記ソース電極との間にリセスを形成する前記誘電層を形成するステップと、

前記誘電層を挟んで前記ソース電極のドレイン方向へのエッジ部分上部に形成された第1の領域、及び前記ドレイン電極と前記ソース電極との間の前記誘電層上に前記ドレイン電極と離間し、前記リセスに形成された第2の領域を含むゲート電極を形成するステップと

を含む窒化物半導体素子の製造方法。

【請求項18】

前記ゲート電極を形成するステップにおいて、前記第1の領域と前記第2の領域とを分離して前記ゲート電極を形成することを特徴とする請求項17に記載の窒化物半導体素子の製造方法。

【請求項19】

前記ゲート電極を形成するステップにおいて、前記ゲート電極の第2の領域は、前記リセスを通じて前記窒化物半導体層上にショットキー接合されるように形成されることを特徴とする請求項18に記載の窒化物半導体素子の製造方法。

【請求項20】

前記ゲート電極を形成するステップにおいて、順方向バイアス電圧の印加時、前記リセスの底を挟む前記窒化物半導体層への電流の供給を増加させるように薄く形成された前記リセスの底を成す前記誘電層と前記ゲート電極の第2の領域とをショットキー接合させることを特徴とする請求項18に記載の窒化物半導体素子の製造方法。

【図1】

【図2】

【図3a】

【図3b】

【図3c】

【図3d】

【図3e】

【図4a】

【図4b】

【図5a】

【図5b】

【図6】

【図7】

【図2】

【図3a】

【図3b】

【図3c】

【図3d】

【図3e】

【図4a】

【図4b】

【図5a】

【図5b】

【図6】

【図7】

【公開番号】特開2012−231106(P2012−231106A)

【公開日】平成24年11月22日(2012.11.22)

【国際特許分類】

【出願番号】特願2011−190744(P2011−190744)

【出願日】平成23年9月1日(2011.9.1)

【出願人】(594023722)サムソン エレクトロ−メカニックス カンパニーリミテッド. (1,585)

【Fターム(参考)】

【公開日】平成24年11月22日(2012.11.22)

【国際特許分類】

【出願日】平成23年9月1日(2011.9.1)

【出願人】(594023722)サムソン エレクトロ−メカニックス カンパニーリミテッド. (1,585)

【Fターム(参考)】

[ Back to top ]