窒化物半導体素子

【課題】低Vf化を図りながら、逆バイアス印加時の漏洩電流を確実に防止することができ、高輝度及び高光束を有する信頼性の高い窒化物半導体素子を提供することを目的とする。

【解決手段】n側窒化物半導体層、活性層及びp側窒化物半導体層がこの順に積層された窒化物半導体素子であって、前記n側窒化物半導体は、n型コンタクト層、アンドープ半導体層及びn型多層膜層がこの順に積層されてなり、該n型多層膜層が、50nm以上500nm以下の総膜厚を有し、前記活性層は90nm以上200nm以下の総膜厚を有する窒化物半導体素子。

【解決手段】n側窒化物半導体層、活性層及びp側窒化物半導体層がこの順に積層された窒化物半導体素子であって、前記n側窒化物半導体は、n型コンタクト層、アンドープ半導体層及びn型多層膜層がこの順に積層されてなり、該n型多層膜層が、50nm以上500nm以下の総膜厚を有し、前記活性層は90nm以上200nm以下の総膜厚を有する窒化物半導体素子。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、窒化物半導体素子に関する。

【背景技術】

【0002】

窒化物半導体は、例えば、高輝度青色LED、純緑色LEDの材料として、フルカラーLEDディスプレイ、交通信号灯、イメージスキャナー光源等の各種光源で実用化されている。LEDの構造としては種々知られており、例えば、n側窒化物半導体層及びp側窒化物半導体層が、それぞれ組成の異なる多層膜によって形成された構造などがある(例えば、特許文献1)。

ここに記載された窒化物半導体素子では、活性層に接して又は近接して、互いに異なる組成等のn型多層膜層及びp型多層膜層を形成することにより、Vf(素子の順方向電圧)の低下及び静電耐圧を向上させることができる。

【0003】

しかし、上記活性層に接した又は近接したn型多層膜層はn型不純物がドーピングされているため、アンドープである場合と比べ、逆バイアス印加時に漏洩電流が発生しやすくなるという問題が依然として存在する。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2000−232237号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

本発明は、上記課題に鑑みなされたものであり、低Vf化を図りながら、逆バイアス印加時の漏洩電流を確実に防止することができ、高輝度及び高光束を有する信頼性の高い窒化物半導体素子を提供することを目的とする。

【課題を解決するための手段】

【0006】

本発明の窒化物半導体素子は、

n側窒化物半導体層、活性層及びp側窒化物半導体層がこの順に積層された窒化物半導体素子であって、

前記n側窒化物半導体は、n型コンタクト層、アンドープ半導体層及びn型多層膜層がこの順に積層されてなり、

該n型多層膜層が、20層以上の層からなり、50nm以上500nm以下の総膜厚を有することを特徴とする。

この窒化物半導体素子では、以下の1以上を備えることが好ましい。

活性層が、90nm以上200nm以下の総膜厚を有する。

前記n側窒化物半導体層側に基板を備え、かつ該基板とn型コンタクト層との間に、転位密度が1×107〜5×109cm−2である第1窒化物半導体層を備え、該第1窒化物半導体層が、1μm以上10μm以下の膜厚を有する。

前記第1窒化物半導体層は、前記基板側よりも前記n型コンタクト層側において転位密度が低い。

前記第1窒化物半導体層は、異なる成膜温度で形成された少なくとも2層を有する。

前記第1窒化物半導体層は、全ガス流量に対するNH3流量の割合が異なる条件下で形成された少なくとも2層を有する。

前記アンドープ半導体層は、アンドープGaN層である。

前記アンドープ半導体層は、アンドープ層とSiドープ層とが交互に積層されてなる。

【発明の効果】

【0007】

本発明によれば、低Vf化を図りながら、逆バイアス印加時の漏洩電流を確実に防止することができ、高輝度及び高光束を有する信頼性の高い窒化物半導体素子を提供することができる。

【図面の簡単な説明】

【0008】

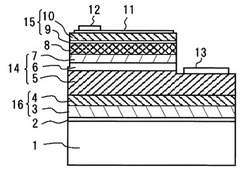

【図1】本発明の一実施の形態に係る半導体発光素子の構造を説明するための概略断面図である。

【図2】本発明の実施例1の半導体発光素子の順方向電圧(Vf)及び出力に関する結果を示すグラフである。

【図3】本発明の実施例1の半導体発光素子のVfに関する結果を示すグラフである。

【図4】本発明の実施例1の半導体発光素子のIrに関する結果を示すグラフである。

【発明を実施するための形態】

【0009】

以下、本件発明の好ましい実施形態について図面を参照しながら説明する。ただし、以下に示す実施形態は、本発明の技術思想を具体化するための窒化物半導体素子を例示するものであって、本発明は窒化物半導体素子を以下のものに特定しない。さらに以下の説明において、同一の名称、符号については同一もしくは同質の部材を示しており、詳細説明を適宜省略する。

【0010】

本発明の窒化物半導体素子は、いわゆるLEDと称されるものであり、図1に示すように、主として、基板1上に、n側窒化物半導体層14、活性層8及びp側窒化物半導体層15がこの順に積層されて構成されている。なお、基板1は、最終形態においては存在しなくてもよい。

さらに、p側窒化物半導体層15は、その上面の略全面に接続された全面電極11及びこの全面電極の一部に接続されたp電極12を有している。n型コンタクト層5は、その上に積層されたn側窒化物半導体層、活性層8、p側窒化物半導体層15の各一部が除去されて、露出しており、その露出した面にn電極13が接続されている。

なお、図示されないが、基板1、半導体層の側面及び上面の一部、任意に、電極上の側面及び上面の一部には、保護膜が形成されている。

ここでの「一部」とは、面内における一部(領域の一部)及び膜厚方向の一部の双方を含む。

【0011】

n側及びp側窒化物半導体層14、15並びに活性層8は、例えば、式(A)

InxAlyGa1−x−yN(0≦x≦1、0≦y≦1、0≦x+y≦1) (A)

で示される化合物半導体によって形成さすることができる。これに加えて、III族元素としてBが一部に置換されたものを用いてもよいし、V族元素としてNの一部をP、Asで置換されたものを用いてもよい。

n側窒化物半導体層は、活性層に対して、n型不純物として、Si、Ge、Sn、S、O、Ti、Zr、CdなどのIV族元素又はVI族元素等を1種類以上含有している層が配置されている側の積層層の総称である。なかでも、n型不純物としては、Si、Snが好ましい。

p側窒化物半導体層は、活性層に対して、p型不純物として、Mg、Zn、Be、Mn、Ca、Sr等層が配置されている側の積層層の総称である。

これらのn型及びp型不純物は、例えば、5×1016/cm3〜1×1021/cm3程度の濃度範囲で含有されていることが好ましい。ただし、n側及びp側窒化物半導体層の全ての層が必ずしもn型又はp型の不純物を含有していなくてもよい。

【0012】

〔n側窒化物半導体層14〕

n側窒化物半導体層14は、基板1側から、n型コンタクト層5、アンドープ半導体層6及びn型多層膜層7がこの順に積層されている。

【0013】

(n型コンタクト層5)

n型コンタクト層5としては、その組成は特に限定されるものではなく、例えば、Al比率が0.2以下のAlGaN又はGaNからなる層が好ましく、単一層からなる層がより好ましい。このような組成にすると、結晶欠陥の少ない窒化物半導体層が得やすい。

n型コンタクト層5の膜厚は特に限定されるものではなく、例えば、1μm程度以上、好ましくは3μm程度以上とすることができる。

n型コンタクト層5は、n型不純物を含有しており、その濃度は、窒化物半導体の結晶性を悪化しない程度に高いことが好ましい。例えば、1×1018/cm3以上、5×1021/cm3以下が挙げられる。

【0014】

(アンドープ半導体層6)

アンドープ半導体層6としては、例えば、上述した式(A)からなる層が挙げられる。なかでも、アンドープ半導体層6は、GaN、x及び/又はyが0.2以下のAlyGa1−x−yN、InxGa1−x−yNが好ましく、さらに、GaNからなる層を含むことが好ましい。このような組成により、結晶欠陥の少ない窒化物半導体層が容易に得られる。アンドープ半導体層6は、単層で形成されていてもよいが、多層膜によって形成されていることが好ましい。

アンドープ半導体層6が多層膜で形成される場合、その全ての層の組成が同じでなくもよく、部分的に、傾斜的に、段階的に又は交互にその組成が変化してもよい。

また、アンドープ半導体層6が多層膜で形成される場合、その全ての層が、n型不純物を含有しない、アンドープ層とすることは必要ではなく、少なくとも1層がアンドープ層であればよい。

不純物が含有されている層が2層以上含まれる場合、その不純物濃度は必ずしも同じでなく、互いに又は少なくとも1層が異なっていてもよい。例えば、その不純物濃度は、3×1018/cm3以上が挙げられ、5×1018/cm3以上が好ましい。n型不純物濃度の上限は特に限定されないが、結晶性が悪くなりすぎない程度、例えば、5×1021/cm3以下が好ましい。このような不純物濃度とすることにより、発光出力の向上とVfの低下との双方を向上させることができる。

特に、アンドープ半導体層6が多層膜で形成される場合、同じ組成のアンドープ層とドープ層とが交互に積層された層であることが好ましい。これらの交互の積層層は、例えば、3層以上であることが好ましく、5層程度以下であることが適しており、アンドープ層とドープ層とのいずれが最下層及び/又は最上層であってもよい。

【0015】

なお、本明細書において「アンドープ」とは、成膜時に、上述したp型又はn型の不純物を導入することなく形成された層であって、成膜後及び/又は製造工程における熱処理等によって上下層から拡散されて不純物が混入された層を意味するのではない。つまり、不純物濃度が1×1017/cm3程度以下に留められている層を、実質的に「アンドープ」の層と称する。

【0016】

アンドープ半導体層6を、比較的高濃度の不純物がドープされたn型コンタクト層5上に配置することにより、下地の結晶性が良くなるため、次に成長させるn型多層膜層7が成長し易くなり、さらにn型多層膜層7上に、結晶性の良好な活性層8を成長させることが可能となる。これにより、窒化物半導体素子として、Vfを低下させることが可能となる。

【0017】

アンドープ半導体層6は、例えば、膜厚が5nm程度以上であることが好ましい。これによって、静電耐圧を向上させることができる。好ましくは、100nm程度以上、さらに好ましくは、300nm程度以上である。また、製造効率と静電耐圧とのバランスを考慮すると、500nm程度以下であることが適している。

アンドープ半導体層6が多層膜で形成される場合、例えば、アンドープ層及びn型不純物ドープ層の膜厚は、それぞれ同じであってもよいし、少なくとも1層が異なっていてもよい。多層膜を構成する個々の層の膜厚は、特に限定されないが、例えば、5〜500nmが適しており、好ましくは5〜300nmであり、より好ましくは5〜200nmである。多層膜の膜厚をこの範囲とすることにより、Vfの最適化と静電耐圧の向上との双方を良好にバランスさせることができる。

【0018】

この多層膜は、その組成及び/又は膜厚及び/又は不純物濃度等によって、積層される位置により、素子の諸特性に与える影響が異なる場合がある。そのために、これらの要因と、各層が大きく関与するであろう素子特性を考慮して、アンドープ層又はドープ層の組成及び/又は膜厚及び/又は不純物濃度を段階的に変化させるなどして、良好な特性に調整することが好ましい。このような調整を行なうことにより、全体として種々の素子特性を良好に維持させながら、特に発光出力及び静電耐圧を著しく向上させることが可能となる(例えば、特開2000−232237号公報参照)。

【0019】

(n型多層膜層7)

n型多層膜層7は、組成の異なる少なくとも2種類以上の元素からなる窒化物半導体、例えば、上述した式(A)からなる層が挙げられる。特に、n型多層膜層7は、超格子多層膜によって形成されていることが好ましく、AlzGa1−zN(0≦z<1)(第1層)とInpGa1−pN(0<p<1)(第2層)との2種類の組成からなる層が交互に積層された超格子層がより好ましい。第1層及び第2層は、いずれが最下層及び/又は最上層であってもよい。ただし、必ずしも第1層同士、第2層同士、第1層及び第2層の全ての層の組成が同じでなくもよく、部分的に、傾斜的に、段階的に又は交互にその組成が変化してもよい。なかでも、第1層同士及び第2層同士が、同じ組成の層であることが好ましい。

【0020】

第1層は、zが小さいほど、つまりアルミニウム含量が小さいほど、結晶性が良好になるため、z=0であるGaNからなる層が好ましい。

第2層は、pが0.5以下の層が好ましく、pが0.2以下の層がより好ましい。

なかでも、n型多層膜層7としては、第1層がGaNであり、第2層においてpが0.2以下のInpGa1−pNである超格子多層膜が好ましい。

【0021】

n型多層膜層7は、組成の異なる層(好ましくは上述した第1層及び第2層)をそれぞれ10層以上積層した、合計20層以上の積層膜であることが適しており、それぞれ20層以上(合計で40層以上)の積層膜であることが好ましい。第1層と第2層との積層数の上限は特に限定されないが、例えば、500層以下が適しており、200層以下、100層以下が好ましい。このようなn型多層膜層を配置することにより、Vfの効果的な低下を実現することができる。

n型多層膜層7を構成する単一層(つまり、第1層又は第2層)の膜厚は特に限定されないが、少なくとも1種類の単一層の膜厚を、10nm以下とすることが適しており、7nm以下が好ましく、5nm以下がより好ましい。このように単一層の膜厚を薄くすることにより、多層膜層が超格子構造となるとともに、弾性臨界膜厚以下となり、多層膜層における各単一層の結晶性が良好となる。よって、積層が進むにつれて、より結晶性を向上させることができ、さらなる光出力の向上を実現させることができる。

さらに、n型多層膜層7を構成する全ての単一層、好ましくは、上述した第1層及び第2層は、両方とも10nm以下とすることが好ましく、7nm以下がより好ましく、5nm以下がさらに好ましい。n型多層膜層6を構成する層の膜厚をこの範囲とすることにより、上述した結晶性をより向上させることができる。

【0022】

n型多層膜層7は、特に限定されないが、総膜厚が、50nm程度以上とすることが適しており、65nm程度以上が好ましく、75nm程度以上、80nm程度以上がより好ましく、さらに、90nm程度以上がより一層好ましい。総膜厚の上限は特に限定されないが、製造効率と特性の向上を考慮して、500nm程度以下が挙げられ、400nm程度以下が好ましい。総膜厚をこの範囲とすることにより、結晶性が良好となり、素子の出力を向上させることができる。

【0023】

n型多層膜層7は、その全ての層にn型不純物が含有されていなくてもよく、少なくとも1層にn型不純物が含有されていればよい。例えば、上述した第1層及び第2層のいずれか一方のみにn型不純物が含有されていなくてもよいし、全ての層にn型不純物が含有されていてもよい。この場合、不純物の種類及び濃度は、いずれも、全ての層において同一でなくてもよく、互いに又は少なくとも1層が異なっていてもよい。例えば、上述した第1層及び第2層の双方にn型不純物がドープされ、隣接する窒化物半導体層同士で濃度が異なる変調ドープを採用することにより、光出力をより向上させることができる傾向がある。

不純物濃度は、5×1016/cm3以上、3×1018/cm3以上が挙げられ、5×1018/cm3以上が好ましい。n型不純物濃度の上限は特に限定されないが、結晶性が悪くなりすぎない程度、例えば、5×1021/cm3以下又は1×1020/cm3以下が好ましい。このような不純物濃度とすることにより、よりVfを低下させることができる。

【0024】

n型多層膜層7の成膜方法は、特に限定されず、公知の成膜方法、例えば、MOVPE、有機金属気相成長法(MOCVD)、ハイドライド気相成長法(HVPE)、分子線エピタキシャル成長法(MBE)等のいずれを利用してもよい。成膜温度は、特に限定されないが、好ましくは850℃以上、より好ましくは900℃以上である。これにより、より結晶性を良好とすることができる。

【0025】

〔活性層8〕

活性層8としては、少なくともInを含んでなる窒化物半導体、好ましくはInjGa1-jN(0≦j<1)を含む井戸層と、障壁層とを有する単一量子井戸構造又は多重量子井戸構造のものが挙げられる。特に、井戸層は、iが0.1〜0.2程度が好ましく、障壁層は、jが0が好ましい。活性層8では、井戸層及び障壁層は、いずれが最下層及び/又は最上層であってもよい。

活性層8は、例えば、90nm程度以上の総膜厚であることが適しており、100〜200nm程度であることが好ましい。この厚みの範囲内で、窒化物半導体素子における所望の波長等を考慮して、障壁層及び井戸層の各積層数、積層順等を調整することにより、逆バイアス印加時の漏洩電流を効果的に低減することができる。

【0026】

〔p側窒化物半導体層15〕

p側窒化物半導体層15は、例えば、活性層側から順に、p側クラッド層9、p型コンタクト層10を含むことが好ましい。

(p側クラッド層9)

p側クラッド層9としては、p型不純物を含有する、上述した式(A)からなる単一層又はバンドギャップエネルギーの異なる少なくとも2層の積層層又は超格子多層膜が挙げられる。なかでも、AlbGa1-b N(0≦b≦1)からなる単一層又はバンドギャップエネルギーの異なる少なくとも2層の半導体層の積層層が好ましい。

p側クラッド層9は、p型不純物濃度が、例えば、1×1022/cm3程度以下が好ましく、5×1020/cm3程度以下がより好ましい。p型不純物濃度の下限は特に限定されないが、5×1016/cm3程度以上が適している。

積層層又は超格子多層膜においては、全ての層にp型不純物が含有されていなくてもよい。また、各層又は一部の層においてp型不純物濃度が異なっていてもよいし、同じでもよい。

p側クラッド層9の膜厚は特に限定されるものではなく、10nm程度以上が挙げられる。また、積層層又は超格子多層膜では、単一の窒化物半導体層の膜厚を、10nm程度以下とすることが好ましく、7nm程度以下、5nm程度以下とすることがより好ましい。薄膜で形成することにより、多層膜層が超格子構造となり、多層膜層の結晶性を向上させることができる。その結果、p型不純物を添加した場合にキャリア濃度が大きく抵抗率の小さい層が得られ、素子のVf及びしきい値等が低下し易い傾向がある。これによって、低消費電力で良好な発光出力を得ることができる。

【0027】

(p型コンタクト層10)

p型コンタクト層10は、例えば、上述した式(A)で表される窒化物半導体からなる層が挙げられ、なかでも、GaN、Al比率0.2以下のAlGaN、In比率0.2以下のInGaNからなる層が好ましく、GaNからなる層がより好ましい。これらの組成は、電極材料と良好なオーミックコンタクトを得ることができる。

p型コンタクト層10の膜厚は特に限定されるものではなく、例えば、50nm程度以上であることが好ましく、60nm程度以上であることがより好ましい。

不純物濃度は、例えば、1×1018/cm3以上、5×1021/cm3以下が挙げられる。

【0028】

〔基板1〕

上述した窒化物半導体層は、通常、基板1上に形成されている。

基板1としては、C面、R面又はA面を主面とするサファイア、その他、スピネル(MgA12O4)のような絶縁性の基板の他、SiC(6H、4H、3Cを含む)、Si、ZnO、GaAs、GaN等の半導体基板を用いることができる。

【0029】

基板1上には、バッファ層2が形成されていることが好ましい。

バッファ層2としては、例えば、GadAl1−dN(0<d≦1)からなる窒化物半導体が挙げられ、Al混晶比が0.3以下が好ましく、Al混晶比が0.2以下の層がより好ましい。Alの割合が小さい組成ほど結晶性の改善が顕著となる。より好ましくはGaNからなるバッファ層2が挙げられる。また、バッファ層2は最終的に除去することもできるし、それ自体省略することもできる。

バッファ層2は、0.002〜0.5μm程度の膜厚であることが好ましく、0.05〜0.2μm程度、さらに0.01〜0.02μm程度の膜厚であることが好ましい。この範囲とすることにより、窒化物半導体の結晶モフォロジーが良好となり、バッファ層2上に成長させる窒化物半導体の結晶性が改善される。バッファ層2を成長させる場合の温度は、200〜900℃とすることが適しており、400〜800℃の範囲に調整することが好ましい。これにより、良好な多結晶を形成することができ、この多結晶を種結晶として、バッファ層2上に成長させる窒化物半導体の結晶性を良好にすることができる。

【0030】

〔第1窒化物半導体層16〕

基板1とn型コンタクト層5との間、特に、上述したバッファ層2を形成する場合には、バッファ層2とn型コンタクト層5との間に、転位密度が1×107〜5×109cm−2である第1窒化物半導体層16を備えていることが適している。第1窒化物半導体層16はGaN層であることが好ましいが、Al1−xGaxN層(0<x<1)としてもよい。

この第1窒化物半導体層16は、単一層でなくてもよく、例えば、2層以上の積層構造であってもよい。積層構造としては、基板側から、転位密度が低減された低転位層3、ピットを減少させるためのピット埋込層4と称する層が積層された積層構造が挙げられる。また、この積層構造の上又は下に、任意の中間層が配置していてもよい。第1窒化物半導体層16は、いずれの層構造であっても、成膜が進むにつれて、結晶性が良好となり、成膜初期よりも成膜終期に成膜された側(又は層)の転位密度が低い。従って、概して、ピット埋込層4が、低転位層3よりも転位密度が低く、低転位層3内ではピット埋込層4側においてより転位密度が低く、ピット埋込層4内では、低転位層3側においてより転位密度が高い。

【0031】

第1窒化物半導体層16は、積層構造として形成される場合、双方とも組成は同一であるが、例えば、成膜方法の違いによって、両者を区別することができる。例えば、上述したような公知の成膜方法において、低転位層3とピット埋込層4とが、さらに任意の層が、異なる成膜温度で形成された層が挙げられる。成膜温度は、成膜初期よりも成膜終期において高くすることが適している。従って、低転位層3の成膜温度よりも、ピット埋込層4の成膜温度を高くすることが好ましい。

また、成膜時における全ガス流量に対するNH3流量の割合が異なる条件下で形成された層が挙げられる。全ガス流量に対するNH3流量の割合は、成膜初期よりも成膜終期において高くすることが適している。従って、低転位層3のNH3流量の割合よりも、ピット埋込層4のNH3流量の割合を高くすることが好ましい。

なお、第1窒化物半導体層16は、実質的に不純物を含有していない。

【0032】

第1窒化物半導体層16の厚みは、例えば、1μm程度以上であることが好ましく、2μm程度以上、3μm程度以上であることがより好ましく、10μm程度以下であることが好ましく、5μm程度以下であることがより好ましい。

【0033】

低転位層3は、例えば、膜厚が500〜5000nm程度が挙げられ、1000〜3000nm程度が好ましい。特に、低転位層は、その終端(活性層側)の転位密度が1×107〜5×108cm−2であることが好ましく、5×10〜3×108cm−2であることがより好ましい。

この低転位層を成膜する方法としては、当該分野で公知の方法にいずれを利用してもよい。例えば、成長中の全供給ガス流量に対するNH3ガスの割合を、30%程度以下に制御し及び/又は成長速度を200nm/分程度以下と制御する方法が挙げられる。さらに、成膜時の温度を、800〜1400℃程度の温度範囲とすることが好ましい。

【0034】

ピット埋込層4は、例えば、膜厚が500〜5000nm程度が挙げられ、1000〜3000nm程度が好ましい。特に、ピット埋込層は、低転位層よりも転位密度が低く、かつ、ピットの発生が極力低減された層である。

このピット埋込層を成膜する方法としては、当該分野で公知の方法にいずれを利用してもよい。さらに、成膜時の温度を、低転位層の成膜温度よりも高い温度、例えば、850〜1450℃程度の温度範囲とすることが好ましい。

【0035】

〔電極11、12、13〕

本発明の窒化物半導体素子において用いられる全面電極、p電極及びn電極は、その単一層の組成、積層構造の組成及び積層順序、膜厚等、特に限定されず、当該分野で公知のもののいずれをも採用することができる。

特に、全面電極は、光の取出効率を考慮して、活性層から出射される光を吸収しない材料によって形成されることが好ましく、例えば、導電性酸化物(ITO等)等が挙げられる。

〔保護膜〕

保護膜としては、特にその材料及び膜厚は限定されないが、例えば、SiO2、ZrO2、TiO2、Al2O3、Nb2O5、AlN、AlGaN等からなる単層膜又は多層膜等が挙げられる。その膜厚は適宜調整することが好ましい。

【0036】

以下に、本発明の窒化物半導体素子の実施例を説明するが、本発明は以下の実施例に限定されるものではない。

実施例1

この実施例の窒化物半導体素子は、サファイアからなる基板1上に、

アンドープAlGaNからなるバッファ層2(膜厚:約15nm)、

アンドープGaNからなる低転位層3(膜厚:約1.5μm)、

アンドープGaNからなるピット埋込層4(膜厚:約2.0μm)、

下から順に、Siを9×1018/cm3ドープしたGaNからなるn型コンタクト層(膜厚:4.2μm)、アンドープGaN層(膜厚:145nm)、Siを2×1018/cm3ドープしたGaN層(膜厚:10nm)、アンドープGaN層(膜厚:145nm)、Siを1.5×1019/cm3ドープしたGaN層(膜厚:30nm)、アンドープGaN層(膜厚:5nm)が順に積層されたアンドープ半導体層6、

Siを2.5×1018/cm3ドープしたGaN層p(膜厚:4nm)を積層した上に、アンドープIn0.02Ga0.98N層q(膜厚:2nm)、Siを2.5×1018/cm3ドープしたGaN層p(膜厚:4nm)がこの順で、GaN層qとGaN層pの積層を繰り返した合計121層の超格子構造からなるn型多層膜層7(膜厚:364nm)、

Siを5×1018/cm3ドープしたGaNからなる障壁層e(膜厚:約4nm)、アンドープGaNからなる障壁層f(膜厚:約3.5nm)を積層した上に、アンドープIn0.2Ga0.8Nからなる井戸層g(膜厚:約3.3nm)及びアンドープGaNからなる障壁層h(膜厚:約4.4nm)の積層構造において井戸層fを15層及び障壁層hを15層交互に積層した多重量子井戸構造よりなる活性層8(膜厚:膜厚123nm)、

Mgを1×1020/cm3ドープしたp型Al0.2Ga0.8Nからなるp側クラッド層9(膜厚:約25nm)及び

下から順に、アンドープGaNからなる層(膜厚:約50nm)、Mgを1×1020/cm3ドープしたp型GaNからなる層(膜厚:約50nm)及びMgを5×1020/cm3ドープしたp型GaNからなる層(膜厚:約15nm)が順に積層されたp型コンタクト層10がこの順に積層されて構成されており、一部のp側窒化物半導体層、活性層及びn側窒化物半導体層が除去されて、n型コンタクト層5の表面が露出されている。

p型コンタクト層10上のほぼ全面には、ITOからなる透光性の全面電極11と、その上に形成されたTi、Rh及びAuを含むp電極12が形成されており、露出したn型コンタクト層5上の表面にはp電極12と同じ積層材料からなるn電極13が形成されている。

【0037】

このような窒化物半導体素子は、以下の方法によって製造することができる。

(基板1)

サファイア(C面)からなる基板1をMOCVDの反応容器内にセットし、水素を流しながら、基板1の温度を900℃〜1200℃程度まで上昇させ、基板のクリーニングを行う。

(バッファ層2)

続いて、温度を400℃〜800℃まで下げ、キャリアガスに水素、原料ガスにアンモニア、TMG(トリメチルガリウム)及びTMA(トリメチルアルミニウム)を用い、基板上にアンドープAlGaNからなるバッファ層2を約15nmの膜厚で成長させる。

【0038】

(第1窒化物半導体層16)

以下のように、低転位層3及びピット埋込層4からなる第1窒化物半導体層16を形成する。

(低転位層3)

バッファ層2成長後、TMGのみ止めて、温度を800℃〜1400℃程度まで上昇させる。原料ガスにTMG、アンモニアガスを用い、アンドープGaNからなる低転位層3を約1.5μmの膜厚で成長させる。このとき全ガス流量に対するアンモニアガス流量の割合を約30%にする。

(ピット埋込層4)

続いて、温度850℃〜1450℃程度で、原料ガスにTMG、アンモニアガスを用い、アンドープGaNからなるピット埋込層4を約2.0μmの膜厚で成長させる。このとき全ガス流量に対するアンモニアガス流量の割合を約60%にする。

【0039】

(nコンタクト層5)

次に、同じく原料ガスにTMG、アンモニアガス、不純物ガスにシランガスを用い、Siを9×1018/cm3ドープしたGaNからなるn型コンタクト層5を約4.2μmの膜厚で成長させる。

【0040】

(アンドープ半導体層6)

次いで、800℃〜1400℃程度で、原料ガスにTMG、アンモニアガス、不純物ガスの有無をシランガスの有無により制御して、アンドープGaN層(膜厚:145nm)、Siを2.5×1018/cm3ドープしたGaN層(膜厚:10nm)、アンドープGaN層(膜厚:145nm)、Siを1.5×1019/cm3ドープしたGaN層(膜厚:30nm)、アンドープGaN層(膜厚:5nm)を順に成長させる。

【0041】

(n型多層膜層7)

続いて、温度800℃〜1000℃程度で、TMG、TMI(トリメチルインジウム)、アンモニアを用い、Siを2.5×1018/cm3ドープしたGaN層p(膜厚:4nm)を積層した上に、アンドープIn0.02Ga0.98N層q(膜厚:2nm)、Siを2.5×1018/cm3ドープしたGaN層p(膜厚:4nm)がこの順で、GaN層pとGaN層qの積層を繰り返した合計121層の超格子構造からなるn型多層膜層7(膜厚:364nm)を成長させる。

【0042】

(活性層8)

次に、Siを含むGaNよりなる障壁層eを約4nm成長させ、アンドープGaNよりなる障壁層fを約3.5nmの膜厚で成長させる。その後、TMG、TMI、アンモニアを用いアンドープIn0.2Ga0.8Nよりなる井戸層gを約3.3nm及びアンドープGaNよりなる障壁層hを約4.4nmの膜厚でそれぞれ15層交互に積層して、総膜厚123nmの多重量子井戸構造よりなる活性層8を成長させる。

【0043】

(p側クラッド層9)

次に、TMG、TMA、アンモニア、Cp2 Mg(シクロペンタジエニルマグネシウム)を用い、Mgを1×1020/cm3ドープしたp型Al0.2Ga0.8Nからなるp側クラッド層9を約25nmの膜厚で成長させる。

(p型コンタクト層10)

続いて、温度900℃〜1000℃程度で、TMG、TMA、アンモニアを用い、アンドープのGaNからなる層を約50nmの膜厚で成長させ、この上に、TMG、アンモニア、Cp2Mgを用い、Mgを1×1020/cm3ドープしたp型GaNからなる層を約50nmの膜厚で、さらにその上にMgを5×1020/cm3ドープしたp型GaNからなる層を約15nmの膜厚で成長させる。

【0044】

反応終了後、温度を室温まで下げ、さらに窒素雰囲気中、ウエハを反応容器内において、300℃〜700℃でアニールし、p側層をさらに低抵抗化する。

その後、ウエハを反応容器から取り出し、最上層のp型コンタクト層10の表面に所定の形状のマスクを形成し、RIE(反応性イオンエッチング)装置でp型コンタクト層側10からエッチングを行い、図1に示すようにn型コンタクト層5の表面を露出させる。

続いて、最上層にあるp型コンタクト層10のほぼ全面にITOよりなる透光性の全面電極11を形成する。

全面電極11上pエッチングにより露出させたn型コンタクト層の上に、Ti、Rh、Auを含む積層膜を成膜し、パターニングすることにより、p電極12及びn電極13をそれぞれ形成する。

得られた積層構造を各チップに切断し、窒化物半導体素子を得る。

【0045】

得られた窒化物半導体素子について、順方向電圧と出力とを測定した。評価は500×290μmサイズのチップに順電流60mAをパルスで印加した状態で行った。

また、窒化物半導体素子に100mA印加し、120℃の環境で動作させることにより、リークを発生しやすくした場合の漏洩電流を評価した。漏洩電流の有無の指標として、IrとVfとの推移を示す。Irが上昇し及びVf低下が大きくなると漏洩電流が発生しているとみなすことができる。

なお、上述した実施例において、n型多層膜層にSiドーピングを行なわず、合計41層の超格子構造からなるn型多層膜層7(膜厚:124nm)とした以外、上述した実施例と同様に、窒化物半導体素子を製造し、比較例とした。

これらの結果を図2から図4に示す。

【0046】

図2に示したように、実施例の素子(n=5)では、比較例に対して、平均2.3%程度のVfの低下が認められ、さらに平均4.2%の出力の増加が認められた。なお、これらのVfの低下及び出力の増加傾向は、n=5個の素子の全てにおいて確認された。

また、図3及び4に示すように、n型多層膜層にSiをドーピングしても、同層にSiをドーピングしない素子と同様に、過酷条件下で1000時間動作させた後においても、Irを上昇も、Vfの低下の増大も認められず、漏洩電流が有効に防止されたことが確認された。

【産業上の利用可能性】

【0047】

本発明の窒化物半導体素子は、例えば、高輝度青色LED、純緑色LED等として、フルカラーLEDディスプレイ、交通信号灯、イメージスキャナー光源等の各種光源に利用することができる。

【符号の説明】

【0048】

1 サファイア基板

2 バッファ層

3 低転位GaN層

4 ピット減少GaN層

5 n型コンタクト層

6 アンドープ半導体層

7 n型多層膜層

8 活性層

9 p型単一層

10 p型コンタクト層

11 全面電極

12 p電極

13 n電極

14 n側窒化物半導体層

15 p側窒化物半導体層

16 第1窒化物半導体層

【技術分野】

【0001】

本発明は、窒化物半導体素子に関する。

【背景技術】

【0002】

窒化物半導体は、例えば、高輝度青色LED、純緑色LEDの材料として、フルカラーLEDディスプレイ、交通信号灯、イメージスキャナー光源等の各種光源で実用化されている。LEDの構造としては種々知られており、例えば、n側窒化物半導体層及びp側窒化物半導体層が、それぞれ組成の異なる多層膜によって形成された構造などがある(例えば、特許文献1)。

ここに記載された窒化物半導体素子では、活性層に接して又は近接して、互いに異なる組成等のn型多層膜層及びp型多層膜層を形成することにより、Vf(素子の順方向電圧)の低下及び静電耐圧を向上させることができる。

【0003】

しかし、上記活性層に接した又は近接したn型多層膜層はn型不純物がドーピングされているため、アンドープである場合と比べ、逆バイアス印加時に漏洩電流が発生しやすくなるという問題が依然として存在する。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2000−232237号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

本発明は、上記課題に鑑みなされたものであり、低Vf化を図りながら、逆バイアス印加時の漏洩電流を確実に防止することができ、高輝度及び高光束を有する信頼性の高い窒化物半導体素子を提供することを目的とする。

【課題を解決するための手段】

【0006】

本発明の窒化物半導体素子は、

n側窒化物半導体層、活性層及びp側窒化物半導体層がこの順に積層された窒化物半導体素子であって、

前記n側窒化物半導体は、n型コンタクト層、アンドープ半導体層及びn型多層膜層がこの順に積層されてなり、

該n型多層膜層が、20層以上の層からなり、50nm以上500nm以下の総膜厚を有することを特徴とする。

この窒化物半導体素子では、以下の1以上を備えることが好ましい。

活性層が、90nm以上200nm以下の総膜厚を有する。

前記n側窒化物半導体層側に基板を備え、かつ該基板とn型コンタクト層との間に、転位密度が1×107〜5×109cm−2である第1窒化物半導体層を備え、該第1窒化物半導体層が、1μm以上10μm以下の膜厚を有する。

前記第1窒化物半導体層は、前記基板側よりも前記n型コンタクト層側において転位密度が低い。

前記第1窒化物半導体層は、異なる成膜温度で形成された少なくとも2層を有する。

前記第1窒化物半導体層は、全ガス流量に対するNH3流量の割合が異なる条件下で形成された少なくとも2層を有する。

前記アンドープ半導体層は、アンドープGaN層である。

前記アンドープ半導体層は、アンドープ層とSiドープ層とが交互に積層されてなる。

【発明の効果】

【0007】

本発明によれば、低Vf化を図りながら、逆バイアス印加時の漏洩電流を確実に防止することができ、高輝度及び高光束を有する信頼性の高い窒化物半導体素子を提供することができる。

【図面の簡単な説明】

【0008】

【図1】本発明の一実施の形態に係る半導体発光素子の構造を説明するための概略断面図である。

【図2】本発明の実施例1の半導体発光素子の順方向電圧(Vf)及び出力に関する結果を示すグラフである。

【図3】本発明の実施例1の半導体発光素子のVfに関する結果を示すグラフである。

【図4】本発明の実施例1の半導体発光素子のIrに関する結果を示すグラフである。

【発明を実施するための形態】

【0009】

以下、本件発明の好ましい実施形態について図面を参照しながら説明する。ただし、以下に示す実施形態は、本発明の技術思想を具体化するための窒化物半導体素子を例示するものであって、本発明は窒化物半導体素子を以下のものに特定しない。さらに以下の説明において、同一の名称、符号については同一もしくは同質の部材を示しており、詳細説明を適宜省略する。

【0010】

本発明の窒化物半導体素子は、いわゆるLEDと称されるものであり、図1に示すように、主として、基板1上に、n側窒化物半導体層14、活性層8及びp側窒化物半導体層15がこの順に積層されて構成されている。なお、基板1は、最終形態においては存在しなくてもよい。

さらに、p側窒化物半導体層15は、その上面の略全面に接続された全面電極11及びこの全面電極の一部に接続されたp電極12を有している。n型コンタクト層5は、その上に積層されたn側窒化物半導体層、活性層8、p側窒化物半導体層15の各一部が除去されて、露出しており、その露出した面にn電極13が接続されている。

なお、図示されないが、基板1、半導体層の側面及び上面の一部、任意に、電極上の側面及び上面の一部には、保護膜が形成されている。

ここでの「一部」とは、面内における一部(領域の一部)及び膜厚方向の一部の双方を含む。

【0011】

n側及びp側窒化物半導体層14、15並びに活性層8は、例えば、式(A)

InxAlyGa1−x−yN(0≦x≦1、0≦y≦1、0≦x+y≦1) (A)

で示される化合物半導体によって形成さすることができる。これに加えて、III族元素としてBが一部に置換されたものを用いてもよいし、V族元素としてNの一部をP、Asで置換されたものを用いてもよい。

n側窒化物半導体層は、活性層に対して、n型不純物として、Si、Ge、Sn、S、O、Ti、Zr、CdなどのIV族元素又はVI族元素等を1種類以上含有している層が配置されている側の積層層の総称である。なかでも、n型不純物としては、Si、Snが好ましい。

p側窒化物半導体層は、活性層に対して、p型不純物として、Mg、Zn、Be、Mn、Ca、Sr等層が配置されている側の積層層の総称である。

これらのn型及びp型不純物は、例えば、5×1016/cm3〜1×1021/cm3程度の濃度範囲で含有されていることが好ましい。ただし、n側及びp側窒化物半導体層の全ての層が必ずしもn型又はp型の不純物を含有していなくてもよい。

【0012】

〔n側窒化物半導体層14〕

n側窒化物半導体層14は、基板1側から、n型コンタクト層5、アンドープ半導体層6及びn型多層膜層7がこの順に積層されている。

【0013】

(n型コンタクト層5)

n型コンタクト層5としては、その組成は特に限定されるものではなく、例えば、Al比率が0.2以下のAlGaN又はGaNからなる層が好ましく、単一層からなる層がより好ましい。このような組成にすると、結晶欠陥の少ない窒化物半導体層が得やすい。

n型コンタクト層5の膜厚は特に限定されるものではなく、例えば、1μm程度以上、好ましくは3μm程度以上とすることができる。

n型コンタクト層5は、n型不純物を含有しており、その濃度は、窒化物半導体の結晶性を悪化しない程度に高いことが好ましい。例えば、1×1018/cm3以上、5×1021/cm3以下が挙げられる。

【0014】

(アンドープ半導体層6)

アンドープ半導体層6としては、例えば、上述した式(A)からなる層が挙げられる。なかでも、アンドープ半導体層6は、GaN、x及び/又はyが0.2以下のAlyGa1−x−yN、InxGa1−x−yNが好ましく、さらに、GaNからなる層を含むことが好ましい。このような組成により、結晶欠陥の少ない窒化物半導体層が容易に得られる。アンドープ半導体層6は、単層で形成されていてもよいが、多層膜によって形成されていることが好ましい。

アンドープ半導体層6が多層膜で形成される場合、その全ての層の組成が同じでなくもよく、部分的に、傾斜的に、段階的に又は交互にその組成が変化してもよい。

また、アンドープ半導体層6が多層膜で形成される場合、その全ての層が、n型不純物を含有しない、アンドープ層とすることは必要ではなく、少なくとも1層がアンドープ層であればよい。

不純物が含有されている層が2層以上含まれる場合、その不純物濃度は必ずしも同じでなく、互いに又は少なくとも1層が異なっていてもよい。例えば、その不純物濃度は、3×1018/cm3以上が挙げられ、5×1018/cm3以上が好ましい。n型不純物濃度の上限は特に限定されないが、結晶性が悪くなりすぎない程度、例えば、5×1021/cm3以下が好ましい。このような不純物濃度とすることにより、発光出力の向上とVfの低下との双方を向上させることができる。

特に、アンドープ半導体層6が多層膜で形成される場合、同じ組成のアンドープ層とドープ層とが交互に積層された層であることが好ましい。これらの交互の積層層は、例えば、3層以上であることが好ましく、5層程度以下であることが適しており、アンドープ層とドープ層とのいずれが最下層及び/又は最上層であってもよい。

【0015】

なお、本明細書において「アンドープ」とは、成膜時に、上述したp型又はn型の不純物を導入することなく形成された層であって、成膜後及び/又は製造工程における熱処理等によって上下層から拡散されて不純物が混入された層を意味するのではない。つまり、不純物濃度が1×1017/cm3程度以下に留められている層を、実質的に「アンドープ」の層と称する。

【0016】

アンドープ半導体層6を、比較的高濃度の不純物がドープされたn型コンタクト層5上に配置することにより、下地の結晶性が良くなるため、次に成長させるn型多層膜層7が成長し易くなり、さらにn型多層膜層7上に、結晶性の良好な活性層8を成長させることが可能となる。これにより、窒化物半導体素子として、Vfを低下させることが可能となる。

【0017】

アンドープ半導体層6は、例えば、膜厚が5nm程度以上であることが好ましい。これによって、静電耐圧を向上させることができる。好ましくは、100nm程度以上、さらに好ましくは、300nm程度以上である。また、製造効率と静電耐圧とのバランスを考慮すると、500nm程度以下であることが適している。

アンドープ半導体層6が多層膜で形成される場合、例えば、アンドープ層及びn型不純物ドープ層の膜厚は、それぞれ同じであってもよいし、少なくとも1層が異なっていてもよい。多層膜を構成する個々の層の膜厚は、特に限定されないが、例えば、5〜500nmが適しており、好ましくは5〜300nmであり、より好ましくは5〜200nmである。多層膜の膜厚をこの範囲とすることにより、Vfの最適化と静電耐圧の向上との双方を良好にバランスさせることができる。

【0018】

この多層膜は、その組成及び/又は膜厚及び/又は不純物濃度等によって、積層される位置により、素子の諸特性に与える影響が異なる場合がある。そのために、これらの要因と、各層が大きく関与するであろう素子特性を考慮して、アンドープ層又はドープ層の組成及び/又は膜厚及び/又は不純物濃度を段階的に変化させるなどして、良好な特性に調整することが好ましい。このような調整を行なうことにより、全体として種々の素子特性を良好に維持させながら、特に発光出力及び静電耐圧を著しく向上させることが可能となる(例えば、特開2000−232237号公報参照)。

【0019】

(n型多層膜層7)

n型多層膜層7は、組成の異なる少なくとも2種類以上の元素からなる窒化物半導体、例えば、上述した式(A)からなる層が挙げられる。特に、n型多層膜層7は、超格子多層膜によって形成されていることが好ましく、AlzGa1−zN(0≦z<1)(第1層)とInpGa1−pN(0<p<1)(第2層)との2種類の組成からなる層が交互に積層された超格子層がより好ましい。第1層及び第2層は、いずれが最下層及び/又は最上層であってもよい。ただし、必ずしも第1層同士、第2層同士、第1層及び第2層の全ての層の組成が同じでなくもよく、部分的に、傾斜的に、段階的に又は交互にその組成が変化してもよい。なかでも、第1層同士及び第2層同士が、同じ組成の層であることが好ましい。

【0020】

第1層は、zが小さいほど、つまりアルミニウム含量が小さいほど、結晶性が良好になるため、z=0であるGaNからなる層が好ましい。

第2層は、pが0.5以下の層が好ましく、pが0.2以下の層がより好ましい。

なかでも、n型多層膜層7としては、第1層がGaNであり、第2層においてpが0.2以下のInpGa1−pNである超格子多層膜が好ましい。

【0021】

n型多層膜層7は、組成の異なる層(好ましくは上述した第1層及び第2層)をそれぞれ10層以上積層した、合計20層以上の積層膜であることが適しており、それぞれ20層以上(合計で40層以上)の積層膜であることが好ましい。第1層と第2層との積層数の上限は特に限定されないが、例えば、500層以下が適しており、200層以下、100層以下が好ましい。このようなn型多層膜層を配置することにより、Vfの効果的な低下を実現することができる。

n型多層膜層7を構成する単一層(つまり、第1層又は第2層)の膜厚は特に限定されないが、少なくとも1種類の単一層の膜厚を、10nm以下とすることが適しており、7nm以下が好ましく、5nm以下がより好ましい。このように単一層の膜厚を薄くすることにより、多層膜層が超格子構造となるとともに、弾性臨界膜厚以下となり、多層膜層における各単一層の結晶性が良好となる。よって、積層が進むにつれて、より結晶性を向上させることができ、さらなる光出力の向上を実現させることができる。

さらに、n型多層膜層7を構成する全ての単一層、好ましくは、上述した第1層及び第2層は、両方とも10nm以下とすることが好ましく、7nm以下がより好ましく、5nm以下がさらに好ましい。n型多層膜層6を構成する層の膜厚をこの範囲とすることにより、上述した結晶性をより向上させることができる。

【0022】

n型多層膜層7は、特に限定されないが、総膜厚が、50nm程度以上とすることが適しており、65nm程度以上が好ましく、75nm程度以上、80nm程度以上がより好ましく、さらに、90nm程度以上がより一層好ましい。総膜厚の上限は特に限定されないが、製造効率と特性の向上を考慮して、500nm程度以下が挙げられ、400nm程度以下が好ましい。総膜厚をこの範囲とすることにより、結晶性が良好となり、素子の出力を向上させることができる。

【0023】

n型多層膜層7は、その全ての層にn型不純物が含有されていなくてもよく、少なくとも1層にn型不純物が含有されていればよい。例えば、上述した第1層及び第2層のいずれか一方のみにn型不純物が含有されていなくてもよいし、全ての層にn型不純物が含有されていてもよい。この場合、不純物の種類及び濃度は、いずれも、全ての層において同一でなくてもよく、互いに又は少なくとも1層が異なっていてもよい。例えば、上述した第1層及び第2層の双方にn型不純物がドープされ、隣接する窒化物半導体層同士で濃度が異なる変調ドープを採用することにより、光出力をより向上させることができる傾向がある。

不純物濃度は、5×1016/cm3以上、3×1018/cm3以上が挙げられ、5×1018/cm3以上が好ましい。n型不純物濃度の上限は特に限定されないが、結晶性が悪くなりすぎない程度、例えば、5×1021/cm3以下又は1×1020/cm3以下が好ましい。このような不純物濃度とすることにより、よりVfを低下させることができる。

【0024】

n型多層膜層7の成膜方法は、特に限定されず、公知の成膜方法、例えば、MOVPE、有機金属気相成長法(MOCVD)、ハイドライド気相成長法(HVPE)、分子線エピタキシャル成長法(MBE)等のいずれを利用してもよい。成膜温度は、特に限定されないが、好ましくは850℃以上、より好ましくは900℃以上である。これにより、より結晶性を良好とすることができる。

【0025】

〔活性層8〕

活性層8としては、少なくともInを含んでなる窒化物半導体、好ましくはInjGa1-jN(0≦j<1)を含む井戸層と、障壁層とを有する単一量子井戸構造又は多重量子井戸構造のものが挙げられる。特に、井戸層は、iが0.1〜0.2程度が好ましく、障壁層は、jが0が好ましい。活性層8では、井戸層及び障壁層は、いずれが最下層及び/又は最上層であってもよい。

活性層8は、例えば、90nm程度以上の総膜厚であることが適しており、100〜200nm程度であることが好ましい。この厚みの範囲内で、窒化物半導体素子における所望の波長等を考慮して、障壁層及び井戸層の各積層数、積層順等を調整することにより、逆バイアス印加時の漏洩電流を効果的に低減することができる。

【0026】

〔p側窒化物半導体層15〕

p側窒化物半導体層15は、例えば、活性層側から順に、p側クラッド層9、p型コンタクト層10を含むことが好ましい。

(p側クラッド層9)

p側クラッド層9としては、p型不純物を含有する、上述した式(A)からなる単一層又はバンドギャップエネルギーの異なる少なくとも2層の積層層又は超格子多層膜が挙げられる。なかでも、AlbGa1-b N(0≦b≦1)からなる単一層又はバンドギャップエネルギーの異なる少なくとも2層の半導体層の積層層が好ましい。

p側クラッド層9は、p型不純物濃度が、例えば、1×1022/cm3程度以下が好ましく、5×1020/cm3程度以下がより好ましい。p型不純物濃度の下限は特に限定されないが、5×1016/cm3程度以上が適している。

積層層又は超格子多層膜においては、全ての層にp型不純物が含有されていなくてもよい。また、各層又は一部の層においてp型不純物濃度が異なっていてもよいし、同じでもよい。

p側クラッド層9の膜厚は特に限定されるものではなく、10nm程度以上が挙げられる。また、積層層又は超格子多層膜では、単一の窒化物半導体層の膜厚を、10nm程度以下とすることが好ましく、7nm程度以下、5nm程度以下とすることがより好ましい。薄膜で形成することにより、多層膜層が超格子構造となり、多層膜層の結晶性を向上させることができる。その結果、p型不純物を添加した場合にキャリア濃度が大きく抵抗率の小さい層が得られ、素子のVf及びしきい値等が低下し易い傾向がある。これによって、低消費電力で良好な発光出力を得ることができる。

【0027】

(p型コンタクト層10)

p型コンタクト層10は、例えば、上述した式(A)で表される窒化物半導体からなる層が挙げられ、なかでも、GaN、Al比率0.2以下のAlGaN、In比率0.2以下のInGaNからなる層が好ましく、GaNからなる層がより好ましい。これらの組成は、電極材料と良好なオーミックコンタクトを得ることができる。

p型コンタクト層10の膜厚は特に限定されるものではなく、例えば、50nm程度以上であることが好ましく、60nm程度以上であることがより好ましい。

不純物濃度は、例えば、1×1018/cm3以上、5×1021/cm3以下が挙げられる。

【0028】

〔基板1〕

上述した窒化物半導体層は、通常、基板1上に形成されている。

基板1としては、C面、R面又はA面を主面とするサファイア、その他、スピネル(MgA12O4)のような絶縁性の基板の他、SiC(6H、4H、3Cを含む)、Si、ZnO、GaAs、GaN等の半導体基板を用いることができる。

【0029】

基板1上には、バッファ層2が形成されていることが好ましい。

バッファ層2としては、例えば、GadAl1−dN(0<d≦1)からなる窒化物半導体が挙げられ、Al混晶比が0.3以下が好ましく、Al混晶比が0.2以下の層がより好ましい。Alの割合が小さい組成ほど結晶性の改善が顕著となる。より好ましくはGaNからなるバッファ層2が挙げられる。また、バッファ層2は最終的に除去することもできるし、それ自体省略することもできる。

バッファ層2は、0.002〜0.5μm程度の膜厚であることが好ましく、0.05〜0.2μm程度、さらに0.01〜0.02μm程度の膜厚であることが好ましい。この範囲とすることにより、窒化物半導体の結晶モフォロジーが良好となり、バッファ層2上に成長させる窒化物半導体の結晶性が改善される。バッファ層2を成長させる場合の温度は、200〜900℃とすることが適しており、400〜800℃の範囲に調整することが好ましい。これにより、良好な多結晶を形成することができ、この多結晶を種結晶として、バッファ層2上に成長させる窒化物半導体の結晶性を良好にすることができる。

【0030】

〔第1窒化物半導体層16〕

基板1とn型コンタクト層5との間、特に、上述したバッファ層2を形成する場合には、バッファ層2とn型コンタクト層5との間に、転位密度が1×107〜5×109cm−2である第1窒化物半導体層16を備えていることが適している。第1窒化物半導体層16はGaN層であることが好ましいが、Al1−xGaxN層(0<x<1)としてもよい。

この第1窒化物半導体層16は、単一層でなくてもよく、例えば、2層以上の積層構造であってもよい。積層構造としては、基板側から、転位密度が低減された低転位層3、ピットを減少させるためのピット埋込層4と称する層が積層された積層構造が挙げられる。また、この積層構造の上又は下に、任意の中間層が配置していてもよい。第1窒化物半導体層16は、いずれの層構造であっても、成膜が進むにつれて、結晶性が良好となり、成膜初期よりも成膜終期に成膜された側(又は層)の転位密度が低い。従って、概して、ピット埋込層4が、低転位層3よりも転位密度が低く、低転位層3内ではピット埋込層4側においてより転位密度が低く、ピット埋込層4内では、低転位層3側においてより転位密度が高い。

【0031】

第1窒化物半導体層16は、積層構造として形成される場合、双方とも組成は同一であるが、例えば、成膜方法の違いによって、両者を区別することができる。例えば、上述したような公知の成膜方法において、低転位層3とピット埋込層4とが、さらに任意の層が、異なる成膜温度で形成された層が挙げられる。成膜温度は、成膜初期よりも成膜終期において高くすることが適している。従って、低転位層3の成膜温度よりも、ピット埋込層4の成膜温度を高くすることが好ましい。

また、成膜時における全ガス流量に対するNH3流量の割合が異なる条件下で形成された層が挙げられる。全ガス流量に対するNH3流量の割合は、成膜初期よりも成膜終期において高くすることが適している。従って、低転位層3のNH3流量の割合よりも、ピット埋込層4のNH3流量の割合を高くすることが好ましい。

なお、第1窒化物半導体層16は、実質的に不純物を含有していない。

【0032】

第1窒化物半導体層16の厚みは、例えば、1μm程度以上であることが好ましく、2μm程度以上、3μm程度以上であることがより好ましく、10μm程度以下であることが好ましく、5μm程度以下であることがより好ましい。

【0033】

低転位層3は、例えば、膜厚が500〜5000nm程度が挙げられ、1000〜3000nm程度が好ましい。特に、低転位層は、その終端(活性層側)の転位密度が1×107〜5×108cm−2であることが好ましく、5×10〜3×108cm−2であることがより好ましい。

この低転位層を成膜する方法としては、当該分野で公知の方法にいずれを利用してもよい。例えば、成長中の全供給ガス流量に対するNH3ガスの割合を、30%程度以下に制御し及び/又は成長速度を200nm/分程度以下と制御する方法が挙げられる。さらに、成膜時の温度を、800〜1400℃程度の温度範囲とすることが好ましい。

【0034】

ピット埋込層4は、例えば、膜厚が500〜5000nm程度が挙げられ、1000〜3000nm程度が好ましい。特に、ピット埋込層は、低転位層よりも転位密度が低く、かつ、ピットの発生が極力低減された層である。

このピット埋込層を成膜する方法としては、当該分野で公知の方法にいずれを利用してもよい。さらに、成膜時の温度を、低転位層の成膜温度よりも高い温度、例えば、850〜1450℃程度の温度範囲とすることが好ましい。

【0035】

〔電極11、12、13〕

本発明の窒化物半導体素子において用いられる全面電極、p電極及びn電極は、その単一層の組成、積層構造の組成及び積層順序、膜厚等、特に限定されず、当該分野で公知のもののいずれをも採用することができる。

特に、全面電極は、光の取出効率を考慮して、活性層から出射される光を吸収しない材料によって形成されることが好ましく、例えば、導電性酸化物(ITO等)等が挙げられる。

〔保護膜〕

保護膜としては、特にその材料及び膜厚は限定されないが、例えば、SiO2、ZrO2、TiO2、Al2O3、Nb2O5、AlN、AlGaN等からなる単層膜又は多層膜等が挙げられる。その膜厚は適宜調整することが好ましい。

【0036】

以下に、本発明の窒化物半導体素子の実施例を説明するが、本発明は以下の実施例に限定されるものではない。

実施例1

この実施例の窒化物半導体素子は、サファイアからなる基板1上に、

アンドープAlGaNからなるバッファ層2(膜厚:約15nm)、

アンドープGaNからなる低転位層3(膜厚:約1.5μm)、

アンドープGaNからなるピット埋込層4(膜厚:約2.0μm)、

下から順に、Siを9×1018/cm3ドープしたGaNからなるn型コンタクト層(膜厚:4.2μm)、アンドープGaN層(膜厚:145nm)、Siを2×1018/cm3ドープしたGaN層(膜厚:10nm)、アンドープGaN層(膜厚:145nm)、Siを1.5×1019/cm3ドープしたGaN層(膜厚:30nm)、アンドープGaN層(膜厚:5nm)が順に積層されたアンドープ半導体層6、

Siを2.5×1018/cm3ドープしたGaN層p(膜厚:4nm)を積層した上に、アンドープIn0.02Ga0.98N層q(膜厚:2nm)、Siを2.5×1018/cm3ドープしたGaN層p(膜厚:4nm)がこの順で、GaN層qとGaN層pの積層を繰り返した合計121層の超格子構造からなるn型多層膜層7(膜厚:364nm)、

Siを5×1018/cm3ドープしたGaNからなる障壁層e(膜厚:約4nm)、アンドープGaNからなる障壁層f(膜厚:約3.5nm)を積層した上に、アンドープIn0.2Ga0.8Nからなる井戸層g(膜厚:約3.3nm)及びアンドープGaNからなる障壁層h(膜厚:約4.4nm)の積層構造において井戸層fを15層及び障壁層hを15層交互に積層した多重量子井戸構造よりなる活性層8(膜厚:膜厚123nm)、

Mgを1×1020/cm3ドープしたp型Al0.2Ga0.8Nからなるp側クラッド層9(膜厚:約25nm)及び

下から順に、アンドープGaNからなる層(膜厚:約50nm)、Mgを1×1020/cm3ドープしたp型GaNからなる層(膜厚:約50nm)及びMgを5×1020/cm3ドープしたp型GaNからなる層(膜厚:約15nm)が順に積層されたp型コンタクト層10がこの順に積層されて構成されており、一部のp側窒化物半導体層、活性層及びn側窒化物半導体層が除去されて、n型コンタクト層5の表面が露出されている。

p型コンタクト層10上のほぼ全面には、ITOからなる透光性の全面電極11と、その上に形成されたTi、Rh及びAuを含むp電極12が形成されており、露出したn型コンタクト層5上の表面にはp電極12と同じ積層材料からなるn電極13が形成されている。

【0037】

このような窒化物半導体素子は、以下の方法によって製造することができる。

(基板1)

サファイア(C面)からなる基板1をMOCVDの反応容器内にセットし、水素を流しながら、基板1の温度を900℃〜1200℃程度まで上昇させ、基板のクリーニングを行う。

(バッファ層2)

続いて、温度を400℃〜800℃まで下げ、キャリアガスに水素、原料ガスにアンモニア、TMG(トリメチルガリウム)及びTMA(トリメチルアルミニウム)を用い、基板上にアンドープAlGaNからなるバッファ層2を約15nmの膜厚で成長させる。

【0038】

(第1窒化物半導体層16)

以下のように、低転位層3及びピット埋込層4からなる第1窒化物半導体層16を形成する。

(低転位層3)

バッファ層2成長後、TMGのみ止めて、温度を800℃〜1400℃程度まで上昇させる。原料ガスにTMG、アンモニアガスを用い、アンドープGaNからなる低転位層3を約1.5μmの膜厚で成長させる。このとき全ガス流量に対するアンモニアガス流量の割合を約30%にする。

(ピット埋込層4)

続いて、温度850℃〜1450℃程度で、原料ガスにTMG、アンモニアガスを用い、アンドープGaNからなるピット埋込層4を約2.0μmの膜厚で成長させる。このとき全ガス流量に対するアンモニアガス流量の割合を約60%にする。

【0039】

(nコンタクト層5)

次に、同じく原料ガスにTMG、アンモニアガス、不純物ガスにシランガスを用い、Siを9×1018/cm3ドープしたGaNからなるn型コンタクト層5を約4.2μmの膜厚で成長させる。

【0040】

(アンドープ半導体層6)

次いで、800℃〜1400℃程度で、原料ガスにTMG、アンモニアガス、不純物ガスの有無をシランガスの有無により制御して、アンドープGaN層(膜厚:145nm)、Siを2.5×1018/cm3ドープしたGaN層(膜厚:10nm)、アンドープGaN層(膜厚:145nm)、Siを1.5×1019/cm3ドープしたGaN層(膜厚:30nm)、アンドープGaN層(膜厚:5nm)を順に成長させる。

【0041】

(n型多層膜層7)

続いて、温度800℃〜1000℃程度で、TMG、TMI(トリメチルインジウム)、アンモニアを用い、Siを2.5×1018/cm3ドープしたGaN層p(膜厚:4nm)を積層した上に、アンドープIn0.02Ga0.98N層q(膜厚:2nm)、Siを2.5×1018/cm3ドープしたGaN層p(膜厚:4nm)がこの順で、GaN層pとGaN層qの積層を繰り返した合計121層の超格子構造からなるn型多層膜層7(膜厚:364nm)を成長させる。

【0042】

(活性層8)

次に、Siを含むGaNよりなる障壁層eを約4nm成長させ、アンドープGaNよりなる障壁層fを約3.5nmの膜厚で成長させる。その後、TMG、TMI、アンモニアを用いアンドープIn0.2Ga0.8Nよりなる井戸層gを約3.3nm及びアンドープGaNよりなる障壁層hを約4.4nmの膜厚でそれぞれ15層交互に積層して、総膜厚123nmの多重量子井戸構造よりなる活性層8を成長させる。

【0043】

(p側クラッド層9)

次に、TMG、TMA、アンモニア、Cp2 Mg(シクロペンタジエニルマグネシウム)を用い、Mgを1×1020/cm3ドープしたp型Al0.2Ga0.8Nからなるp側クラッド層9を約25nmの膜厚で成長させる。

(p型コンタクト層10)

続いて、温度900℃〜1000℃程度で、TMG、TMA、アンモニアを用い、アンドープのGaNからなる層を約50nmの膜厚で成長させ、この上に、TMG、アンモニア、Cp2Mgを用い、Mgを1×1020/cm3ドープしたp型GaNからなる層を約50nmの膜厚で、さらにその上にMgを5×1020/cm3ドープしたp型GaNからなる層を約15nmの膜厚で成長させる。

【0044】

反応終了後、温度を室温まで下げ、さらに窒素雰囲気中、ウエハを反応容器内において、300℃〜700℃でアニールし、p側層をさらに低抵抗化する。

その後、ウエハを反応容器から取り出し、最上層のp型コンタクト層10の表面に所定の形状のマスクを形成し、RIE(反応性イオンエッチング)装置でp型コンタクト層側10からエッチングを行い、図1に示すようにn型コンタクト層5の表面を露出させる。

続いて、最上層にあるp型コンタクト層10のほぼ全面にITOよりなる透光性の全面電極11を形成する。

全面電極11上pエッチングにより露出させたn型コンタクト層の上に、Ti、Rh、Auを含む積層膜を成膜し、パターニングすることにより、p電極12及びn電極13をそれぞれ形成する。

得られた積層構造を各チップに切断し、窒化物半導体素子を得る。

【0045】

得られた窒化物半導体素子について、順方向電圧と出力とを測定した。評価は500×290μmサイズのチップに順電流60mAをパルスで印加した状態で行った。

また、窒化物半導体素子に100mA印加し、120℃の環境で動作させることにより、リークを発生しやすくした場合の漏洩電流を評価した。漏洩電流の有無の指標として、IrとVfとの推移を示す。Irが上昇し及びVf低下が大きくなると漏洩電流が発生しているとみなすことができる。

なお、上述した実施例において、n型多層膜層にSiドーピングを行なわず、合計41層の超格子構造からなるn型多層膜層7(膜厚:124nm)とした以外、上述した実施例と同様に、窒化物半導体素子を製造し、比較例とした。

これらの結果を図2から図4に示す。

【0046】

図2に示したように、実施例の素子(n=5)では、比較例に対して、平均2.3%程度のVfの低下が認められ、さらに平均4.2%の出力の増加が認められた。なお、これらのVfの低下及び出力の増加傾向は、n=5個の素子の全てにおいて確認された。

また、図3及び4に示すように、n型多層膜層にSiをドーピングしても、同層にSiをドーピングしない素子と同様に、過酷条件下で1000時間動作させた後においても、Irを上昇も、Vfの低下の増大も認められず、漏洩電流が有効に防止されたことが確認された。

【産業上の利用可能性】

【0047】

本発明の窒化物半導体素子は、例えば、高輝度青色LED、純緑色LED等として、フルカラーLEDディスプレイ、交通信号灯、イメージスキャナー光源等の各種光源に利用することができる。

【符号の説明】

【0048】

1 サファイア基板

2 バッファ層

3 低転位GaN層

4 ピット減少GaN層

5 n型コンタクト層

6 アンドープ半導体層

7 n型多層膜層

8 活性層

9 p型単一層

10 p型コンタクト層

11 全面電極

12 p電極

13 n電極

14 n側窒化物半導体層

15 p側窒化物半導体層

16 第1窒化物半導体層

【特許請求の範囲】

【請求項1】

n側窒化物半導体層、活性層及びp側窒化物半導体層がこの順に積層された窒化物半導体素子であって、

前記n側窒化物半導体は、n型コンタクト層、アンドープ半導体層及びn型多層膜層がこの順に積層されてなり、

該n型多層膜層が、20層以上の層からなり、50nm以上500nm以下の総膜厚を有することを特徴とする窒化物半導体素子。

【請求項2】

活性層が、90nm以上200nm以下の総膜厚を有する請求項1に記載の窒化物半導体素子。

【請求項3】

前記n側窒化物半導体層側に基板を備え、かつ該基板とn型コンタクト層との間に、転位密度が1×107〜5×109cm−2である第1窒化物半導体層を備え、該第1窒化物半導体層が、1μm以上10μm以下の膜厚を有する請求項1又は2に記載の窒化物半導体素子。

【請求項4】

前記第1窒化物半導体層は、前記基板側よりも前記n型コンタクト層側において転位密度が低い請求項3に記載の窒化物半導体素子。

【請求項5】

前記第1窒化物半導体層は、異なる成膜温度で形成された少なくとも2層を有する請求項3又は4に記載の窒化物半導体素子。

【請求項6】

前記第1窒化物半導体層は、全ガス流量に対するNH3流量の割合が異なる条件下で形成された少なくとも2層を有する請求項3〜5のいずれか1つに記載の窒化物半導体素子。

【請求項7】

前記アンドープ半導体層は、アンドープGaN層である請求項1〜6のいずれか1つに記載の窒化物半導体素子。

【請求項8】

前記アンドープ半導体層は、アンドープ層とSiドープ層とが交互に積層されてなる請求項1〜7のいずれか1つに記載の窒化物半導体素子。

【請求項1】

n側窒化物半導体層、活性層及びp側窒化物半導体層がこの順に積層された窒化物半導体素子であって、

前記n側窒化物半導体は、n型コンタクト層、アンドープ半導体層及びn型多層膜層がこの順に積層されてなり、

該n型多層膜層が、20層以上の層からなり、50nm以上500nm以下の総膜厚を有することを特徴とする窒化物半導体素子。

【請求項2】

活性層が、90nm以上200nm以下の総膜厚を有する請求項1に記載の窒化物半導体素子。

【請求項3】

前記n側窒化物半導体層側に基板を備え、かつ該基板とn型コンタクト層との間に、転位密度が1×107〜5×109cm−2である第1窒化物半導体層を備え、該第1窒化物半導体層が、1μm以上10μm以下の膜厚を有する請求項1又は2に記載の窒化物半導体素子。

【請求項4】

前記第1窒化物半導体層は、前記基板側よりも前記n型コンタクト層側において転位密度が低い請求項3に記載の窒化物半導体素子。

【請求項5】

前記第1窒化物半導体層は、異なる成膜温度で形成された少なくとも2層を有する請求項3又は4に記載の窒化物半導体素子。

【請求項6】

前記第1窒化物半導体層は、全ガス流量に対するNH3流量の割合が異なる条件下で形成された少なくとも2層を有する請求項3〜5のいずれか1つに記載の窒化物半導体素子。

【請求項7】

前記アンドープ半導体層は、アンドープGaN層である請求項1〜6のいずれか1つに記載の窒化物半導体素子。

【請求項8】

前記アンドープ半導体層は、アンドープ層とSiドープ層とが交互に積層されてなる請求項1〜7のいずれか1つに記載の窒化物半導体素子。

【図1】

【図2】

【図3】

【図4】

【図2】

【図3】

【図4】

【公開番号】特開2012−248656(P2012−248656A)

【公開日】平成24年12月13日(2012.12.13)

【国際特許分類】

【出願番号】特願2011−118837(P2011−118837)

【出願日】平成23年5月27日(2011.5.27)

【出願人】(000226057)日亜化学工業株式会社 (993)

【Fターム(参考)】

【公開日】平成24年12月13日(2012.12.13)

【国際特許分類】

【出願日】平成23年5月27日(2011.5.27)

【出願人】(000226057)日亜化学工業株式会社 (993)

【Fターム(参考)】

[ Back to top ]