窒化物半導体装置

【課題】活性層の上に電極パッドを形成する場合に生じる問題を解決し、オン抵抗の上昇を抑えた窒化物半導体装置を実現できるようにする。

【解決手段】窒化物半導体装置は、活性領域102Aを有する窒化物半導体層積層体102と、活性領域の上に互いに間隔をおいて形成されたフィンガー状の第1の電極131及び第2の電極132とを備えている。第1の電極の上に接して第1の電極配線151が形成され、第2の電極の上に第2の電極配線152が接して形成されている。第1の電極配線及び第2の電極配線を覆うように第2の絶縁膜が形成され、第2の絶縁膜の上に第1の金属層161が形成されている。第1の金属層は、第2の絶縁膜を介して活性領域の上に形成され、第1の電極配線と接続されている。

【解決手段】窒化物半導体装置は、活性領域102Aを有する窒化物半導体層積層体102と、活性領域の上に互いに間隔をおいて形成されたフィンガー状の第1の電極131及び第2の電極132とを備えている。第1の電極の上に接して第1の電極配線151が形成され、第2の電極の上に第2の電極配線152が接して形成されている。第1の電極配線及び第2の電極配線を覆うように第2の絶縁膜が形成され、第2の絶縁膜の上に第1の金属層161が形成されている。第1の金属層は、第2の絶縁膜を介して活性領域の上に形成され、第1の電極配線と接続されている。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、窒化物半導体装置に関し、特に活性領域の上に形成された電極パッドを有する窒化物半導体装置に関する。

【背景技術】

【0002】

III−V族窒化物半導体(以下、窒化物半導体という。)は、III族元素であるガリウム(Ga)、アルミニウム(Al)及びインジウム(In)等と、V族元素である窒素(N)との化合物であり、一般式がAlxGa1-x-yInyN(但し、0≦x≦1、0≦y ≦1、x+y≦1)で表される混晶を形成する。窒化物半導体は、広いバンドギャップを有しており、バンド構造は直接遷移型である。このため、短波長光学素子へ応用されている。また、高い破壊電界と飽和電子速度という特長を有するため、電子デバイスへ応用することも検討されている。特に、半絶縁性基板の上に順次エピタキシャル成長したAlxGa1-xN層(但し、0<x≦1)とGaN層との界面に現れる2次元電子ガス(2Dimensional Electron Gas:以下、2DEGという。)を利用したヘテロ接合電界効果トランジスタ(Hetero-junction Field Effect Transistor:以下、HFETという)は、高出力デバイス及び高周波デバイスとして開発が進められている。

【0003】

HFETにおいては、キャリア供給層であるAlGaNショットキー層から電子が供給されるだけでなく、自発分極及びピエゾ分極からなる分極効果により電荷が供給される。このため、窒化物半導体を用いたHFETの電子密度は1013cm-2を超える。これは、砒化アルミニウムガリウム(AlGaAs)と砒化ガリウム(GaAs)とを用いたHFETと比べて1桁程度も大きい。このように、窒化物半導体を用いたHFETは、GaAsを用いたHFETと比べて高いドレイン電流密度が期待でき、最大ドレイン電流が1A/mmを超える素子が報告されている(例えば、非特許文献1を参照。)。さらに、窒化物半導体は広いバンドギャップ(例えばGaNのバンドギャップは3.4eV)を有するため高い耐圧特性をも示し、窒化物半導体を用いたHFETではゲート電極とドレイン電極との間の耐圧を100V以上とすることが可能である。このため、窒化物半導体を用いたHFET等の電子デバイスは、高周波素子及び従来よりも小さい設計寸法で大電力を扱える素子として応用が検討されている。

【0004】

窒化物半導体装置は、活性領域のサイズをシリコン(Si)半導体装置の3分の1〜10分の1程度に縮小可能である。しかし、大電流を流すパワーデバイスの用途では、電極パッドに接続するワイヤ径やリボンサイズは大きい方が望ましく、活性領域を縮小しても窒化物半導体装置のサイズを小さくする効果は小さい。窒化物半導体装置のサイズを縮小する方法として、活性領域の上に電極パッドを形成する、いわゆるパッドオンエレメント構造が検討されている(例えば、特許文献1を参照。)。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2008−177527号公報

【非特許文献】

【0006】

【非特許文献1】安藤祐二、岡本康宏、宮本広信、中山達峰、井上隆、葛原正明著「高耐圧AlGaN/GaNヘテロ接合FETの評価」信学技報、ED2002-214, CPM2002-105(2002-10), p.29-34

【発明の概要】

【発明が解決しようとする課題】

【0007】

しかしながら、前記従来のパッドオンエレメント構造には以下のような問題がある。ドレイン電極パッドは活性層の上に形成し、ソース電極パッドは基板の裏面に形成すれば、最も効率良くパッドを配置することができる。しかし、ソース電極パッドを基板の裏面に形成するためには、窒化物半導体層及び基板を貫通するビアを形成する必要があり、コストが上昇するという問題がある。このため、製造方法の容易さの観点及びサイズの縮小の観点から、ドレイン電極パッドとソース電極パッドとを活性層の上に形成することが好ましい。しかし、ドレイン電極パッドとソース電極パッドとの両方を活性層の上に形成する場合には、電極フィンガーの一部しか電極パッドと直接接触させることができない。電極フィンガーの幅はデバイスのサイズによって制限されるため、広くすることは困難である。また、電極フィンガーはリフトオフ法により形成することが一般的であり、電極フィンガーの膜厚を厚くすることは困難である。このため、電極フィンガーは配線抵抗が大きく、電極フィンガーの一部しか電極パッドと直接接していない場合には、デバイスのオン抵抗が上昇するという問題がある。

【0008】

また、活性層の上に例えば一方の電極パッドだけを形成する場合においても、電極フィンガーの全体が電極パッドと直接接するように大きな開口部を形成する必要があり、電極パッドの平坦性が低下するという問題もある。

【0009】

これらの問題は、HFETだけでなくショットキーダイオード等の他の窒化物半導体装置においても生じる。

【0010】

本発明は、活性層の上に電極パッドを形成する場合に生じる問題を解決し、オン抵抗の上昇を抑えた窒化物半導体装置を実現できるようにすることを目的とする。

【課題を解決するための手段】

【0011】

前記の目的を達成するため、本発明は半導体装置を、活性領域の上に形成された電極パッドが電極配線を介して電極と接続されている構成とする。

【0012】

具体的に、本発明に係る窒化物半導体装置は、基板の上に形成され、素子分離領域に囲まれた活性領域を有する窒化物半導体層積層体と、活性領域の上に互いに間隔をおいて形成されたフィンガー状の第1の電極及び第2の電極と、第1の電極及び第2の電極を覆い、第1の電極の上面を露出する第1の開口部及び第2の電極の上面を露出する第2の開口部を有する第1の絶縁膜と、第1の電極の上に形成され、第1の開口部において第1の電極と接する第1の電極配線と、第2の電極の上に形成され、第2の開口部において第2の電極と接する第2の電極配線と、第1の電極配線及び第2の電極配線を覆う第2の絶縁膜と、第2の絶縁膜を介して活性領域の上に形成され、第1の電極配線と接続された第1の金属層とを備えている。

【0013】

本発明の窒化物半導体装置は、電極パッドである第1の金属層が第2の絶縁膜を介して活性領域の上に形成され、第1の電極配線と接続されている。活性領域の上に形成された第1の金属層と第1の電極とをビア等により直接接続した場合には、第1の電極の配線抵抗が大きいため、窒化物半導体装置のオン抵抗が上昇するおそれがある。しかし、例示の第1の金属層と第1の電極とは、第1の電極配線を介して接続されている。第1の電極配線は第1の電極よりも配線抵抗を小さくすることができるので、第1の金属層と第1の電極配線との接触面積が小さい場合においても、窒化物半導体装置のオン抵抗の上昇を抑えることができる。

【0014】

本発明に係る窒化物半導体装置は、第2の絶縁膜の上に第1の金属層と間隔をおいて形成された第2の金属層をさらに備え、第2の金属層は、活性領域の上に形成され、第2の電極配線と接続されていてもよい。

【0015】

本発明の窒化物半導体装置において、第1の金属層と第1の電極配線とを接続する第1のビアと、第2の金属層と第2の電極配線とを接続する第2のビアとをさらに備え、第1のビア及び第2のビアは活性領域の上に形成されていてもよい。また、第1の金属層と第1の電極配線とを接続する第1のビアと、第2の金属層と第2の電極配線とを接続する第2のビアとをさらに備え、第1のビア及び第2のビアは、素子分離領域の上に形成されていてもよい。

【0016】

本発明の窒化物半導体装置において、第2の絶縁膜は、シリコン窒化膜又はシリコン酸化膜である第1の膜と、該第1の膜の上に形成された有機絶縁膜である第2の膜とを有し、第1のビア及び第2のビアの開口部は、第2の膜の下端部における開口部の面積が、第1の膜の上端部における開口部の面積よりも大よりも大きくてもよい。

【0017】

本発明の窒化物半導体装置において、第1の電極配線と第2の電極配線との最短距離、第1の電極配線と第2の金属層との最短距離及び第2の電極配線と第1の金属層との最短距離のうちの最小の距離と、第2の絶縁膜の絶縁破壊電圧との積は、600V以上であることが好ましい。

【0018】

本発明の窒化物半導体装置において、第1の電極は、カソード電極であり、第2の電極は、アノード電極である構成としてもよい。

【0019】

本発明の窒化物半導体装置において、第1の電極と、第2の電極との間に形成されたフィンガー状の第1のゲート電極と、第2の絶縁膜の上に、第1の金属層及び第2の金属層と間隔をおいて形成され且つ第1のゲート電極と接続された第3の金属層とをさらに備え、第3の金属層と第2の金属層との間隔は、第3の金属層と第1の金属層との間隔以上であり、第1の電極は、ソース電極であり、第2の電極は、ドレイン電極である構成としてもよい。

【0020】

この場合において、基板に垂直で且つ第1の電極配線及び第2の電極配線を垂直に横切る断面において、第1の電極配線の第2の電極側の端部は、第1のゲート電極よりも第2の電極側に位置していてもよい。

【0021】

また、第1のゲート電極と窒化物半導体層積層体との間に形成されたp型の窒化物半導体層をさらに備えていてもよい。

【0022】

本発明の窒化物半導体装置は、第1の電極と、第2の電極との間に、第1の電極側から順次形成されたフィンガー状の第1のゲート電極及び第2のゲート電極と、第2の絶縁膜の上に、第1の金属層及び第2の金属層と間隔をおいて形成され且つ第1のゲート電極と接続された第3の金属層及び第2のゲート電極と接続された第4の金属層とをさらに備え、第3の金属層と第2の金属層との間隔は、第3の金属層と第1の金属層との間隔以上であり、第1の電極は、第1のオーミック電極であり、第2の電極は、第2のオーミック電極である構成としてもよい。

【0023】

この場合において、基板に垂直で且つ第1の電極配線及び第2の電極配線を垂直に横切る断面において、第1の電極配線の第2の電極側の端部は、第1のゲート電極よりも第2の電極側で且つ第2のゲート電極よりも第1のゲート電極側に位置し、第2の電極配線の第1の電極側の端部は、第2のゲート電極よりも第1の電極側で且つ第1のゲート電極よりも第2のゲート電極側に位置していてもよい。

【0024】

また、第1のゲート電極及び第2のゲート電極と窒化物半導体層積層体との間にそれぞれ形成されたp型の窒化物半導体層をさらに備えていてもよい。

【発明の効果】

【0025】

本発明に係る窒化物半導体装置によれば、活性層の上に電極パッドを形成する場合に生じる問題を解決し、オン抵抗の上昇を抑えた窒化物半導体装置を実現できる。

【図面の簡単な説明】

【0026】

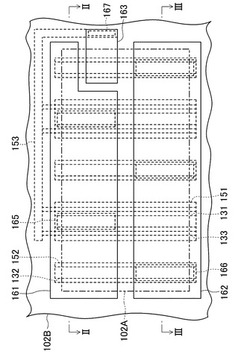

【図1】一実施形態に係る窒化物半導体装置を示す平面図である。

【図2】一実施形態に係る窒化物半導体装置を示す断面図である。

【図3】一実施形態に係る窒化物半導体装置を示す断面図である。

【図4】一実施形態に係る窒化物半導体装置の変形例を示す平面図である。

【図5】一実施形態に係る窒化物半導体装置の変形例を示す平面図である。

【図6】一実施形態に係る窒化物半導体装置の変形例を示す断面図である。

【図7】一実施形態に係る窒化物半導体装置の変形例を示す平面図である。

【発明を実施するための形態】

【0027】

図1〜図3は、一実施形態に係る窒化物半導体装置であり、図1は平面構成を示し、図2は図1のII−II線における断面構成を示し、図3は図1のIII−III線における断面構成を示している。本実施形態の窒化物半導体装置は、Si基板101の上に形成された窒化物半導体層積層体102を備えている。窒化物半導体層積層体102は、例えば、基板101側から順次形成されたバッファ層120、膜厚が2.5μmのアンドープのGaNからなる第1の窒化物半導体層121及び膜厚が50nmのアンドープのAlGaNからなる第2の窒化物半導体層122を有している。窒化物半導体層積層体102は、活性領域102Aと、活性領域102Aを囲む素子分離領域102Bとを有している。素子分離領域102Bはイオン注入等により高抵抗化された領域である。活性領域102Aにおいては、第1の窒化物半導体層121における第2の窒化物半導体層122との界面近傍には、2次元電子ガス(2DEG)からなるチャネルが形成されている。

【0028】

窒化物半導体層積層体102の上には、活性領域102Aを横切るようにフィンガー状の第1のオーミック電極131と第2のオーミック電極132とが、互いに間隔をおいて交互に形成されている。第1のオーミック電極131と第2のオーミック電極132との間には、p型の第3の窒化物半導体層134を介在させてゲート電極133が形成されている。本実施形態においては、第1のオーミック電極131はソース電極であり、第2のオーミック電極132はドレイン電極である。図1においては、第1のオーミック電極131が2本、第2のオーミック電極132が3本の構成を示しているが、第1のオーミック電極131及び第2のオーミック電極132の数は何本であってもよい。

【0029】

第1のオーミック電極131及び第2のオーミック電極132は、チタン(Ti)とアルミニウム(Al)とからなり、チャネルとオーミック接触している。本実施形態においては、コンタクト抵抗を低減するために、第2の窒化物半導体層122と第1の窒化物半導体層121との界面よりも下側に達する凹部に形成されている。第1のオーミック電極131及び第2のオーミック電極132は、最も厚い部分における膜厚が250nm程度であり、幅は数μm程度である。幅を大きくするとオーミック電極の配線抵抗を低減できるが、チップ面積におけるチャネル領域の割合が減少するため、大きくとることは好ましくない。チャネル領域が大きいほどオン抵抗は小さくなり、大電流を流すことができるので、チャネル領域は大きい方が望ましい。第1のオーミック電極131及び第2のオーミック電極132はニッケル(Ni)、金(Au)又はバナジウム(V)等により形成してもよい。第1のオーミック電極131及び第2のオーミック電極132はリフトオフ法を用いれば容易に形成することができる。

【0030】

p型の第3の窒化物半導体層134は、膜厚が200nm程度のマグネシウム(Mg)がドープされたGaNからなる。ゲート電極133は、パラジウム(Pd)及びAuからなり、p型の第3の窒化物半導体層134とオーミック接触している。p型の第3の窒化物半導体層134と第2の窒化物半導体層122とによりPN接合が形成される。これにより、ゲート電極133に印加する電圧が0Vの場合においても、p型の第3の窒化物半導体層134から基板101側及び第2のオーミック電極132側に向かって、第2の窒化物半導体層122及び第1の窒化物半導体層121中に空乏層が広がる。従って、ゲート電極133に印加する電圧が0Vの場合においてもチャネルを流れる電流が遮断される、ノーマリオフ動作を行わせることが可能となる。本実施形態においては、閾値電圧を調整するために、p型の第3の窒化物半導体層134及びゲート電極133は、第2の窒化物半導体層122の膜厚が他の部分よりも薄いゲートリセス部(図示せず)に形成されている。ゲート電極133は、Ni、Ti、銀(Ag)又は白金(Pt)等により形成することも可能である。p型の第3の窒化物半導体層134を用いてノーマリオフ動作をするノーマリオフ型としたが、ゲートリセス構造等によりノーマリオフ型を実現してもよい。また、ノーマリオン型とすることも可能である。

【0031】

窒化物半導体層積層体102の上には、第1のオーミック電極131、第2のオーミック電極132及びゲート電極133を覆うように、膜厚が300nm程度のシリコン窒化膜(SiN膜)である第1の絶縁膜141が形成されている。第1の絶縁膜141は、窒化物半導体層積層体102の表面を安定化すると共に、後述する第2の絶縁膜142から窒化物半導体層積層体102への水分の侵入を低減する機能を有する。第1の絶縁膜141は、第1のオーミック電極131の上面を露出するストライプ状の第1の開口部及び第2のオーミック電極132の上面を露出するストライプ状の第2の開口部を有している。

【0032】

第1の絶縁膜141の上には、第1のオーミック電極配線151及び第2のオーミック電極配線152が形成されている。第1のオーミック電極配線151は、第1の開口部において第1のオーミック電極131と接続され、第2のオーミック電極配線152は第2の開口部において第2のオーミック電極132と接続されている。第1のオーミック電極配線151及び第2のオーミック電極配線152は、TiとAuとの積層膜となっており、Tiは第1のオーミック電極131及び第2のオーミック電極132との密着性を向上させる密着層である。第1のオーミック電極配線151及び第2のオーミック電極配線152の膜厚は5μm程度とすればよく、幅はそれぞれ第1のオーミック電極131及び第2のオーミック電極132の幅と同じ又はそれよりも広くすることが好ましい。

【0033】

第1のオーミック電極配線151及び第2のオーミック電極配線152を覆うように、第2の絶縁膜142が形成されている。本実施形態において第2の絶縁膜142は、膜厚が400nm程度のSiNからなる第1の膜142Aと、膜厚が10μm程度のポリベンズオキサゾール(PBO)からなる第2の膜142Bとの積層膜である。第1の膜142Aは、第2の膜142Bから窒化物半導体層積層体102への水分の侵入を低減する機能と、第2の膜142Bと下側の層との密着性を向上させる機能とを有する。

【0034】

第2の絶縁膜142の上には、電極パッドである第1の金属層161、第2の金属層162及び第3の金属層163が形成されている。本実施形態において第1の金属層161及び第2の金属層162は、活性領域102Aの上に形成されている。第1の金属層161と第2の金属層162とは、ゲート電極133が延びる方向(ゲート幅方向)と交差する辺同士が相対するように、互いに間隔をおいて配置されている。第2の絶縁膜142は、第1の金属層161の下側において第1のオーミック電極配線151の上面を露出する第3の開口部を有している。第3の開口部を埋めるように第1の金属層161と一体となった第1のビア165が形成されており、第1のビア165により第1の金属層161と第1のオーミック電極配線151とは接続されている。また、第2の金属層162の下側において第2のオーミック電極配線152の上面を露出する第2の開口部を有している。第2の開口部を埋めるように第2の金属層162と一体となった第2のビア166が形成されており、第2のビア166により第2の金属層162と第2のオーミック電極配線152とは接続されている。

【0035】

第1の金属層161、第2の金属層162及び第3の金属層163は、Ti、銅(Cu)及びNiの積層膜とすればよい。シート抵抗を低く抑えるためにCu膜の厚さは5μm程度とすることが好ましい。最上層にNi膜を設けることにより、Alワイヤ又はAlリボン等との密着性が向上し、信頼性が高い半導体装置を実現することができる。Ni膜の膜厚は1μm程度とすることが好ましい。Niに代えてAgを用いることも可能である。Au又はCu等からなるワイヤ、リボン又はクリップ等を用いる場合には最表面をAu層としてもよい。

【0036】

本実施形態において、第3の金属層163は活性領域102Aの上の第1の金属層161側の領域に形成されている。このような構成とすることにより、第3の金属層163と第2の金属層162との間の耐圧を確保しつつ、半導体装置のサイズを小さくすることができる。第3の金属層163は、素子分離領域102Bの上に形成されたゲート電極配線153と第3のビア167を介して接続されている。ゲート電極配線153は、活性領域102Aの外周を迂回して配置され、ゲート電極133と接続されている。本実施形態においては、第1のオーミック電極配線151及び第2のオーミック電極配線152を素子分離領域102Bに引き出して束ねていないため、ゲート電極配線153が第1のオーミック電極配線151及び第2のオーミック電極配線152を横切ることがない。活性領域が複数形成されている場合には、活性領域の間の素子分離領域において、複数のゲート電極を束ねるようにゲート電極配線を形成してもよい。

【0037】

第1の金属層161及び第2の金属層162を、活性領域102Aの上に形成する場合には、第1のオーミック電極131の一部は第2の金属層162の下側に位置し、第2のオーミック電極132の一部は第1の金属層161の下側に位置する。仮に、第1のオーミック電極配線151を形成せずに、第1の金属層161と第1のオーミック電極131とをビアにより直接接続する場合、ビアと接するのは第1のオーミック電極131の第1の金属層161の下側に形成された部分だけである。第1のオーミック電極131は、膜厚が薄く幅も狭いため、配線抵抗が大きい。このため、第1のオーミック電極131の第2の金属層162の下側に形成されている部分においては、第1の金属層161と第1のオーミック電極131との間の抵抗を無視できなくなる。第2の金属層162と第2のオーミック電極132との間にも同じ問題が生じる。第1のオーミック電極131及び第2のオーミック電極132は、一般にリフトオフ法により形成するため、膜厚を厚くして配線抵抗を低減することは困難である。また、第1のオーミック電極131及び第2のオーミック電極132の幅は、デバイスのサイズによって制限されるため、幅を広くすることにより配線抵抗を低減することも困難である。

【0038】

本実施形態の半導体装置は、第1のオーミック電極131の上を覆うように第1のオーミック電極配線151が形成され、第2のオーミック電極132の上を覆うように第2のオーミック電極配線152が形成されている。第1のオーミック電極配線151及び第2のオーミック電極配線152は、第1のオーミック電極131及び第2のオーミック電極132よりも膜厚を厚くすることができるので、配線抵抗を小さくすることが容易である。このため、第1のオーミック電極配線151の第1の金属層161の下側の部分のみにビアが接続されていたとしても、第1の金属層161と第1のオーミック電極131との間の抵抗を小さく抑えることができる。第2の金属層162と第2のオーミック電極132との間においても同様である。本実施形態の半導体装置は、第1の金属層及び第2の金属層を第1のオーミック電極配線及び第2のオーミック電極配線を介さずに、第1のオーミック電極及び第2のオーミック電極と直接接続した場合と比べて、配線抵抗を約半分に低減することができる。

【0039】

配線抵抗を効果的に抑えるためには、第1のオーミック電極配線151及び第2のオーミック電極配線152は、ゲート幅方向と交差する方向の断面積が第1のオーミック電極131及び第2のオーミック電極132よりも大きくなるようにすればよい。第1のオーミック電極配線151及び第2のオーミック電極配線152をめっき法により形成すれば、膜厚を厚くすることが容易にできる。また、第1のオーミック電極配線151及び第2のオーミック電極配線152は、できるだけ電気抵抗が小さい材料を用いることが好ましく、Au若しくはCu又はこれらの合金等とすればよい。Al、Ni若しくはTi又はこれらの合金等を用いることも可能である。また、第1のオーミック電極131及び第2のオーミック電極132との密着性を向上するため、積層膜としてもよい。この場合には、密着層である下層は、Ti若しくはTa又はこれらの窒化物等を用いればよい。

【0040】

図1は第1のオーミック電極配線151がゲート電極133の上を覆うように形成された例を示している。第1のオーミック電極配線151をゲート電極133よりも第2のオーミック電極132側に張り出した構造とすることにより、第1のオーミック電極配線151の断面積を大きくすることができるだけでなく、第1のオーミック電極配線151をフィールドプレートとして機能させることが可能となる。さらに、第1の金属層161及び第2の金属層162が活性領域102Aの上に形成されている。これにより、半導体装置がオフの状態において、ゲート電極133の端部及び第1のオーミック電極配線151からなるフィールドプレートの端部における電界集中を緩和することができる。従って、パッドオンエレメント構造ではない場合と比べて、電流コラプスを抑制することができる。

【0041】

本実施形態においては、第2の絶縁膜142をSiNからなる第1の膜142AとPBOからなる第2の膜142Bとの積層膜とした。PBO膜等の有機膜はスピン塗布により形成できるため、凹部への埋め込みが容易であり、第2の絶縁膜142の上面を容易に平坦化できる。第2の絶縁膜142の上面を平坦にすることにより、第2の絶縁膜142の上に形成する電極パッドである金属層を平坦にすることができる。電極パッドを平坦にすることにより電極パッド面とワイヤとの接触面積を大きくなるため、配線の抵抗を低減したり、ワイヤボンディングの歩留まりを向上させたりすることができる。

【0042】

PBOはAuとの密着性に劣る。このため、最上層がAuである第1のオーミック電極配線151及び第2のオーミック電極配線152と、第2の絶縁膜142との密着性を向上させるために、第2の膜142Bと第1のオーミック電極配線151及び第2のオーミック電極配線152との間に、SiNからなる第1の膜142Aを設けている。第1の膜142AはSiO2膜等とすることも可能であるが、SiN膜は耐水性が高いため、下層への水分の透過を抑える効果が得られる。第1の膜142Aは例えばプラズマ化学気相堆積層(CVD)法等により形成すればよい。

【0043】

第1の金属層161と第1のオーミック電極配線151とを接続するための第3の開口部及び第2の金属層162と第2のオーミック電極配線152とを接続するための第4の開口部は、第1の膜142Aの上端部における幅よりも、第2の膜142Bの下端部における幅が広い形状とすることが好ましい。これにより、第1のビア165及び第2のビア166は、第2の膜142Bの下端部における面積が第1の膜142Aの上端部における面積より大きくなる。このような構成とすれば、Auとの密着性が悪い第2の膜142Bが第1のオーミック電極配線151及び第2のオーミック電極配線152の上面と直接接することがなく、第2の絶縁膜142の剥がれ等を抑えることができる。第1の膜142Aに形成する開口部は、ドライエッチングにより形成すればよい。第2の膜142Bに形成する開口部は、第2の膜142Bを感光性樹脂とする場合にはフォトリソグラフィーにより形成すればよい。また、SiO2膜等をハードマスクとして用いたドライエッチングにより形成してもよい。

【0044】

第2の膜142Bは、PBOに代えて、ポリイミド、ベンゾシクロブテン(BCB)、エポキシ系の感光性樹脂(例えば、化薬マイクロケム社製SU−8)又はフッ素系の感光性樹脂(例えば、旭硝子社製AL−X2)等の有機膜としてもよい。但し、ポリイミド等の吸湿性を有する材料を用いる場合には、吸湿により第2の膜142Bが膨張し、第2の膜142Bに亀裂が発生したり、下層への水分の透過が生じたりするおそれがある。このため、第2の膜142Bの上にさらに耐水性の第3の膜を形成することが好ましい。

【0045】

Al−X2等のAuとの密着性に優れた材料を用いた場合には、第1の膜142Aを省略してもよい。また、第1のオーミック電極配線151及び第2のオーミック電極配線152の最上層をTi又はCu等の有機膜と比較的密着しやすい材料とした場合にも、第1の膜142Aを省略することが可能である。

【0046】

また、第2の膜142Bにガラス系材料を用いてもよい。この場合には、リンを含有することが望ましい。このようにすることにより、第2の絶縁膜142の膜応力を緩和し、膜剥がれの発生を抑えることができる。また、リンのゲッタリング効果により、活性領域102Aへのアルカリ性不純物の侵入を防ぐ効果も得られるため、半導体装置の信頼性を向上させることができる。

【0047】

本実施形態においては、第3の金属層163の面積を、第1の金属層161及び第2の金属層162よりも小さくしている。これは、ゲート電極には高い電圧を印加する必要がないため、第3の金属層163には細いワイヤを接続するためである。また、第3の金属層163を第1の金属層161よりに形成している。これは、ドレイン電極パッドである第2の金属層162には、より高い電圧を印加するためである。但し、必要な絶縁破壊耐圧を確保できれば、第3の金属層163の位置は特に限定されない。

【0048】

第1の金属層161と第2の金属層162及び第3の金属層163と第2の金属層162との最小の間隔をS1とし、半導体装置全体を封止する樹脂封止の絶縁破壊耐圧をA1とすると、S1とA1との積が必要とする絶縁耐圧よりも大きくなるようにすればよい。

【0049】

また、絶縁破壊耐圧を確保するためには、電極パッドである金属層同士の間隔だけでなく、第1のオーミック電極配線151と第2のオーミック電極配線152との間隔、第1のオーミック電極配線151と第2の金属層162との間隔、第2のオーミック電極配線152と第1の金属層161との間隔も重要である。これらの間隔のうちの最も狭いものをS2とし、第2の絶縁膜142の絶縁破壊電圧をA2とすると、S2とA2との積が必要とする絶縁破壊耐圧よりも大きくなるようにすればよい。例えば、PBOの絶縁破壊電圧は250V/μmである。このため、必要とする絶縁破壊耐圧が600Vの場合には、最小の間隔S1を2.4μm以上とし、1000Vの場合には4μm以上とすればよい。本実施形態においては、S1を5μmとなるように設計した。

【0050】

本実施形態の半導体装置は、基板101における窒化物半導体層積層体102と反対側の面(裏面)には、例えばAu、スズ(Sn)、クロム(Cr)若しくはNi又はこれらの合金等からなる裏面電極164を形成した例を示している。裏面電極164を形成することにより外部から基板101に電位を与えることが可能となる。また、裏面電極164と第1のオーミック電極131とを電気的に接続してもよい。この場合には、裏面電極164をソース電極パッドとすることも可能である。裏面電極164と第1のオーミック電極131との接続には貫通ビアを用いてもよい。裏面電極164は例えば、スパッタ法又は蒸着法等により形成すればよい。

【0051】

本実施形態の半導体装置は、第1の金属層161と第1のオーミック電極配線151とを接続する第1のビア165は、活性領域102Aの上に複数形成されている。第2の金属層162と第2のオーミック電極配線152とを接続する第2のビア166も同様である。このため、ワイヤボンディングの際の圧力から活性領域を保護する効果が得られる。しかし、第1の金属層161と第1のオーミック電極配線151とを接続する第1のビア165及び第2の金属層162と第2のオーミック電極配線152とを接続する第2のビア166は、素子分離領域102Bの上に形成してもよい。この場合には、図4に示すように、第1のオーミック電極配線151を互いに接続する配線155を素子分離領域102Bに形成し、配線155と第1の金属層161とを第1のビア165により接続すればよい。また、第2のオーミック電極配線152を互いに接続する配線156を活性領域102Aを挟んで配線155と反対側に形成し、配線156と第2の金属層162とを第2のビア166により接続すればよい。

【0052】

本実施形態において、シングルゲートの半導体装置について説明したが、インバータ又はマトリックスコンバータ等に用いることができるダブルゲートの半導体装置においても同様の構成としてかまわない。図5及び図6は、ダブルゲートの半導体装置の例であり、図5は平面構成を示し、図6は図5のVI−VI線における断面構成を示している。

【0053】

ダブルゲートの半導体装置は、第1のオーミック電極131と第2のオーミック電極132との間に、第1のゲート電極133Aと第2のゲート電極133Bとが、第1のオーミック電極131側から順に形成されている。図6は、ノーマリオフ型とするため第1のゲート電極133A及び第2のゲート電極133Bを、それぞれp型の第3の窒化物半導体層134の上に形成した例を示している。但し、ゲートリセス構造によりノーマリオフ型にしたり、ノーマリオン型にしたりすることも可能である。

【0054】

第1のゲート電極133A及び第2のゲート電極133Bに所定のバイアスを印加することにより、双方向スイッチとしても、ダイオードとしても動作させることができる。例えば、第1のゲート電極133Aと第2のゲート電極133Bとに、それぞれ、第1のオーミック電極131を基準として第1のゲート電極133Aの閾値電圧以上の電圧を印加し、第2のオーミック電極132を基準として第2のゲート電極133Bの閾値電圧以上の電圧を印加することにより、第1のオーミック電極131と第2のオーミック電極132との間に双方向に電流が流れる双方向通電動作をさせることができる。一方、第1のゲート電極133A及び第2のゲート電極133Bに印加するバイアス電圧をそれぞれ閾値電圧以下の電圧とすることにより第1のオーミック電極131と第2のオーミック電極132との間に双方向に電流が流れない双方向遮断動作をさせることができる。

【0055】

また、第1のゲート電極133Aに閾値電圧以上の電圧を印加し、第2のゲート電極133Bに閾値電圧以下の電圧を印加することにより、第1のオーミック電極131から第2のオーミック電極132へは電流が流れないが、第2のオーミック電極132から第1のオーミック電極131へは電流が流れるダイオード動作をさせることができる。第1のゲート電極133Aに閾値電圧以下の電圧を印加し、第2のゲート電極133Bに閾値電圧以上の電圧を印加することにより、第1のオーミック電極131から第2のオーミック電極132へは電流が流れるが、第2のオーミック電極132から第1のオーミック電極131へは電流が流れないダイオード動作をさせることができる。

【0056】

図5は、第1のオーミック電極配線151が第1のゲート電極133Aよりも第2のゲート電極133B側に広がり、第2のオーミック電極配線152が第2のゲート電極133Bよりも第1のゲート電極133A側に広がっている例を示している。このようにすれば、第1のオーミック電極配線151及び第2のオーミック電極配線152が、それぞれフィールドプレートとして機能する。また、第1のゲート電極133Aと第2のゲート電極133Bとの間に発生する電気力線の一部を、第1のオーミック電極配線151及び第2のオーミック電極配線152により切断することができる。これにより、第1のゲート電極133Aと第2のゲート電極133Bとの間の寄生抵抗Cggを低減することが可能となり、ゲートノイズを抑制することができる。

【0057】

図5に示すように、第1のゲート電極133A同士を接続する第1のゲート電極配線153Aと第2のゲート電極同士を接続する第2のゲート電極配線153Bとを、活性領域102Aを挟んで反対側に形成することにより、配線の形成が容易となる。第3の金属層163Aは、第1の金属層161側に形成し、第4の金属層163Bは、第2の金属層162側に形成することが好ましい。

【0058】

図7に示すように、ショットキーダイオードにおいても同様の構成とすることができる。この場合には、2DEGとオーミック接触したカソード電極である第1の電極231と、ショットキー接触したアノード電極である第2の電極232とを設ければよい。第1の電極231は、第1の電極配線251を介して第1の金属層261と接続し、第2の電極232は、第2の電極配線252を介して第2の金属層262と接続すればよい。

【0059】

図7では、第1の金属層261と第1の電極配線251とを接続する第1のビア265及び第2の金属層262と第2の電極配線252とを接続する第2のビア266を活性領域102Aの上に形成する例を示した。しかし、第1の電極配線251を互いに接続する配線及び第2の電極配線252を互いに接続する配線を素子分離領域102Bに形成し、電極パッドである金属層と配線とを接続するビアを素子分離領域102Bの上に形成してもよい。

【0060】

第1の電極231は、TiとNiとの積層体等とすればよく、第2の電極232はPd及びAuの合金等とすればよい。

【産業上の利用可能性】

【0061】

本発明に係る窒化物半導体装置は、活性層の上に電極パッドを形成する場合に生じる問題を解決し、オン抵抗の上昇を抑えることができ、電源回路用のパワーデバイス等を含む窒化物半導体装置として有用である。

【符号の説明】

【0062】

101 基板

102 窒化物半導体層積層体

102A 活性領域

102B 素子分離領域

120 バッファ層

121 第1の窒化物半導体層

122 第2の窒化物半導体層

131 第1のオーミック電極

132 第2のオーミック電極

133 ゲート電極

133A 第1のゲート電極

133B 第2のゲート電極

134 第3の窒化物半導体層

141 第1の絶縁膜

142 第2の絶縁膜

142A 第1の膜

142B 第2の膜

151 第1のオーミック電極配線

152 第2のオーミック電極配線

153 ゲート電極配線

153A 第1のゲート電極配線

153B 第2のゲート電極配線

155 配線

156 配線

161 第1の金属層

162 第2の金属層

163 第3の金属層

163A 第3の金属層

163B 第4の金属層

164 裏面電極

165 第1のビア

166 第2のビア

167 第3のビア

231 第1の電極

232 第2の電極

251 第1の電極配線

252 第2の電極配線

261 第1の金属層

262 第2の金属層

265 第1のビア

266 第2のビア

【技術分野】

【0001】

本発明は、窒化物半導体装置に関し、特に活性領域の上に形成された電極パッドを有する窒化物半導体装置に関する。

【背景技術】

【0002】

III−V族窒化物半導体(以下、窒化物半導体という。)は、III族元素であるガリウム(Ga)、アルミニウム(Al)及びインジウム(In)等と、V族元素である窒素(N)との化合物であり、一般式がAlxGa1-x-yInyN(但し、0≦x≦1、0≦y ≦1、x+y≦1)で表される混晶を形成する。窒化物半導体は、広いバンドギャップを有しており、バンド構造は直接遷移型である。このため、短波長光学素子へ応用されている。また、高い破壊電界と飽和電子速度という特長を有するため、電子デバイスへ応用することも検討されている。特に、半絶縁性基板の上に順次エピタキシャル成長したAlxGa1-xN層(但し、0<x≦1)とGaN層との界面に現れる2次元電子ガス(2Dimensional Electron Gas:以下、2DEGという。)を利用したヘテロ接合電界効果トランジスタ(Hetero-junction Field Effect Transistor:以下、HFETという)は、高出力デバイス及び高周波デバイスとして開発が進められている。

【0003】

HFETにおいては、キャリア供給層であるAlGaNショットキー層から電子が供給されるだけでなく、自発分極及びピエゾ分極からなる分極効果により電荷が供給される。このため、窒化物半導体を用いたHFETの電子密度は1013cm-2を超える。これは、砒化アルミニウムガリウム(AlGaAs)と砒化ガリウム(GaAs)とを用いたHFETと比べて1桁程度も大きい。このように、窒化物半導体を用いたHFETは、GaAsを用いたHFETと比べて高いドレイン電流密度が期待でき、最大ドレイン電流が1A/mmを超える素子が報告されている(例えば、非特許文献1を参照。)。さらに、窒化物半導体は広いバンドギャップ(例えばGaNのバンドギャップは3.4eV)を有するため高い耐圧特性をも示し、窒化物半導体を用いたHFETではゲート電極とドレイン電極との間の耐圧を100V以上とすることが可能である。このため、窒化物半導体を用いたHFET等の電子デバイスは、高周波素子及び従来よりも小さい設計寸法で大電力を扱える素子として応用が検討されている。

【0004】

窒化物半導体装置は、活性領域のサイズをシリコン(Si)半導体装置の3分の1〜10分の1程度に縮小可能である。しかし、大電流を流すパワーデバイスの用途では、電極パッドに接続するワイヤ径やリボンサイズは大きい方が望ましく、活性領域を縮小しても窒化物半導体装置のサイズを小さくする効果は小さい。窒化物半導体装置のサイズを縮小する方法として、活性領域の上に電極パッドを形成する、いわゆるパッドオンエレメント構造が検討されている(例えば、特許文献1を参照。)。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2008−177527号公報

【非特許文献】

【0006】

【非特許文献1】安藤祐二、岡本康宏、宮本広信、中山達峰、井上隆、葛原正明著「高耐圧AlGaN/GaNヘテロ接合FETの評価」信学技報、ED2002-214, CPM2002-105(2002-10), p.29-34

【発明の概要】

【発明が解決しようとする課題】

【0007】

しかしながら、前記従来のパッドオンエレメント構造には以下のような問題がある。ドレイン電極パッドは活性層の上に形成し、ソース電極パッドは基板の裏面に形成すれば、最も効率良くパッドを配置することができる。しかし、ソース電極パッドを基板の裏面に形成するためには、窒化物半導体層及び基板を貫通するビアを形成する必要があり、コストが上昇するという問題がある。このため、製造方法の容易さの観点及びサイズの縮小の観点から、ドレイン電極パッドとソース電極パッドとを活性層の上に形成することが好ましい。しかし、ドレイン電極パッドとソース電極パッドとの両方を活性層の上に形成する場合には、電極フィンガーの一部しか電極パッドと直接接触させることができない。電極フィンガーの幅はデバイスのサイズによって制限されるため、広くすることは困難である。また、電極フィンガーはリフトオフ法により形成することが一般的であり、電極フィンガーの膜厚を厚くすることは困難である。このため、電極フィンガーは配線抵抗が大きく、電極フィンガーの一部しか電極パッドと直接接していない場合には、デバイスのオン抵抗が上昇するという問題がある。

【0008】

また、活性層の上に例えば一方の電極パッドだけを形成する場合においても、電極フィンガーの全体が電極パッドと直接接するように大きな開口部を形成する必要があり、電極パッドの平坦性が低下するという問題もある。

【0009】

これらの問題は、HFETだけでなくショットキーダイオード等の他の窒化物半導体装置においても生じる。

【0010】

本発明は、活性層の上に電極パッドを形成する場合に生じる問題を解決し、オン抵抗の上昇を抑えた窒化物半導体装置を実現できるようにすることを目的とする。

【課題を解決するための手段】

【0011】

前記の目的を達成するため、本発明は半導体装置を、活性領域の上に形成された電極パッドが電極配線を介して電極と接続されている構成とする。

【0012】

具体的に、本発明に係る窒化物半導体装置は、基板の上に形成され、素子分離領域に囲まれた活性領域を有する窒化物半導体層積層体と、活性領域の上に互いに間隔をおいて形成されたフィンガー状の第1の電極及び第2の電極と、第1の電極及び第2の電極を覆い、第1の電極の上面を露出する第1の開口部及び第2の電極の上面を露出する第2の開口部を有する第1の絶縁膜と、第1の電極の上に形成され、第1の開口部において第1の電極と接する第1の電極配線と、第2の電極の上に形成され、第2の開口部において第2の電極と接する第2の電極配線と、第1の電極配線及び第2の電極配線を覆う第2の絶縁膜と、第2の絶縁膜を介して活性領域の上に形成され、第1の電極配線と接続された第1の金属層とを備えている。

【0013】

本発明の窒化物半導体装置は、電極パッドである第1の金属層が第2の絶縁膜を介して活性領域の上に形成され、第1の電極配線と接続されている。活性領域の上に形成された第1の金属層と第1の電極とをビア等により直接接続した場合には、第1の電極の配線抵抗が大きいため、窒化物半導体装置のオン抵抗が上昇するおそれがある。しかし、例示の第1の金属層と第1の電極とは、第1の電極配線を介して接続されている。第1の電極配線は第1の電極よりも配線抵抗を小さくすることができるので、第1の金属層と第1の電極配線との接触面積が小さい場合においても、窒化物半導体装置のオン抵抗の上昇を抑えることができる。

【0014】

本発明に係る窒化物半導体装置は、第2の絶縁膜の上に第1の金属層と間隔をおいて形成された第2の金属層をさらに備え、第2の金属層は、活性領域の上に形成され、第2の電極配線と接続されていてもよい。

【0015】

本発明の窒化物半導体装置において、第1の金属層と第1の電極配線とを接続する第1のビアと、第2の金属層と第2の電極配線とを接続する第2のビアとをさらに備え、第1のビア及び第2のビアは活性領域の上に形成されていてもよい。また、第1の金属層と第1の電極配線とを接続する第1のビアと、第2の金属層と第2の電極配線とを接続する第2のビアとをさらに備え、第1のビア及び第2のビアは、素子分離領域の上に形成されていてもよい。

【0016】

本発明の窒化物半導体装置において、第2の絶縁膜は、シリコン窒化膜又はシリコン酸化膜である第1の膜と、該第1の膜の上に形成された有機絶縁膜である第2の膜とを有し、第1のビア及び第2のビアの開口部は、第2の膜の下端部における開口部の面積が、第1の膜の上端部における開口部の面積よりも大よりも大きくてもよい。

【0017】

本発明の窒化物半導体装置において、第1の電極配線と第2の電極配線との最短距離、第1の電極配線と第2の金属層との最短距離及び第2の電極配線と第1の金属層との最短距離のうちの最小の距離と、第2の絶縁膜の絶縁破壊電圧との積は、600V以上であることが好ましい。

【0018】

本発明の窒化物半導体装置において、第1の電極は、カソード電極であり、第2の電極は、アノード電極である構成としてもよい。

【0019】

本発明の窒化物半導体装置において、第1の電極と、第2の電極との間に形成されたフィンガー状の第1のゲート電極と、第2の絶縁膜の上に、第1の金属層及び第2の金属層と間隔をおいて形成され且つ第1のゲート電極と接続された第3の金属層とをさらに備え、第3の金属層と第2の金属層との間隔は、第3の金属層と第1の金属層との間隔以上であり、第1の電極は、ソース電極であり、第2の電極は、ドレイン電極である構成としてもよい。

【0020】

この場合において、基板に垂直で且つ第1の電極配線及び第2の電極配線を垂直に横切る断面において、第1の電極配線の第2の電極側の端部は、第1のゲート電極よりも第2の電極側に位置していてもよい。

【0021】

また、第1のゲート電極と窒化物半導体層積層体との間に形成されたp型の窒化物半導体層をさらに備えていてもよい。

【0022】

本発明の窒化物半導体装置は、第1の電極と、第2の電極との間に、第1の電極側から順次形成されたフィンガー状の第1のゲート電極及び第2のゲート電極と、第2の絶縁膜の上に、第1の金属層及び第2の金属層と間隔をおいて形成され且つ第1のゲート電極と接続された第3の金属層及び第2のゲート電極と接続された第4の金属層とをさらに備え、第3の金属層と第2の金属層との間隔は、第3の金属層と第1の金属層との間隔以上であり、第1の電極は、第1のオーミック電極であり、第2の電極は、第2のオーミック電極である構成としてもよい。

【0023】

この場合において、基板に垂直で且つ第1の電極配線及び第2の電極配線を垂直に横切る断面において、第1の電極配線の第2の電極側の端部は、第1のゲート電極よりも第2の電極側で且つ第2のゲート電極よりも第1のゲート電極側に位置し、第2の電極配線の第1の電極側の端部は、第2のゲート電極よりも第1の電極側で且つ第1のゲート電極よりも第2のゲート電極側に位置していてもよい。

【0024】

また、第1のゲート電極及び第2のゲート電極と窒化物半導体層積層体との間にそれぞれ形成されたp型の窒化物半導体層をさらに備えていてもよい。

【発明の効果】

【0025】

本発明に係る窒化物半導体装置によれば、活性層の上に電極パッドを形成する場合に生じる問題を解決し、オン抵抗の上昇を抑えた窒化物半導体装置を実現できる。

【図面の簡単な説明】

【0026】

【図1】一実施形態に係る窒化物半導体装置を示す平面図である。

【図2】一実施形態に係る窒化物半導体装置を示す断面図である。

【図3】一実施形態に係る窒化物半導体装置を示す断面図である。

【図4】一実施形態に係る窒化物半導体装置の変形例を示す平面図である。

【図5】一実施形態に係る窒化物半導体装置の変形例を示す平面図である。

【図6】一実施形態に係る窒化物半導体装置の変形例を示す断面図である。

【図7】一実施形態に係る窒化物半導体装置の変形例を示す平面図である。

【発明を実施するための形態】

【0027】

図1〜図3は、一実施形態に係る窒化物半導体装置であり、図1は平面構成を示し、図2は図1のII−II線における断面構成を示し、図3は図1のIII−III線における断面構成を示している。本実施形態の窒化物半導体装置は、Si基板101の上に形成された窒化物半導体層積層体102を備えている。窒化物半導体層積層体102は、例えば、基板101側から順次形成されたバッファ層120、膜厚が2.5μmのアンドープのGaNからなる第1の窒化物半導体層121及び膜厚が50nmのアンドープのAlGaNからなる第2の窒化物半導体層122を有している。窒化物半導体層積層体102は、活性領域102Aと、活性領域102Aを囲む素子分離領域102Bとを有している。素子分離領域102Bはイオン注入等により高抵抗化された領域である。活性領域102Aにおいては、第1の窒化物半導体層121における第2の窒化物半導体層122との界面近傍には、2次元電子ガス(2DEG)からなるチャネルが形成されている。

【0028】

窒化物半導体層積層体102の上には、活性領域102Aを横切るようにフィンガー状の第1のオーミック電極131と第2のオーミック電極132とが、互いに間隔をおいて交互に形成されている。第1のオーミック電極131と第2のオーミック電極132との間には、p型の第3の窒化物半導体層134を介在させてゲート電極133が形成されている。本実施形態においては、第1のオーミック電極131はソース電極であり、第2のオーミック電極132はドレイン電極である。図1においては、第1のオーミック電極131が2本、第2のオーミック電極132が3本の構成を示しているが、第1のオーミック電極131及び第2のオーミック電極132の数は何本であってもよい。

【0029】

第1のオーミック電極131及び第2のオーミック電極132は、チタン(Ti)とアルミニウム(Al)とからなり、チャネルとオーミック接触している。本実施形態においては、コンタクト抵抗を低減するために、第2の窒化物半導体層122と第1の窒化物半導体層121との界面よりも下側に達する凹部に形成されている。第1のオーミック電極131及び第2のオーミック電極132は、最も厚い部分における膜厚が250nm程度であり、幅は数μm程度である。幅を大きくするとオーミック電極の配線抵抗を低減できるが、チップ面積におけるチャネル領域の割合が減少するため、大きくとることは好ましくない。チャネル領域が大きいほどオン抵抗は小さくなり、大電流を流すことができるので、チャネル領域は大きい方が望ましい。第1のオーミック電極131及び第2のオーミック電極132はニッケル(Ni)、金(Au)又はバナジウム(V)等により形成してもよい。第1のオーミック電極131及び第2のオーミック電極132はリフトオフ法を用いれば容易に形成することができる。

【0030】

p型の第3の窒化物半導体層134は、膜厚が200nm程度のマグネシウム(Mg)がドープされたGaNからなる。ゲート電極133は、パラジウム(Pd)及びAuからなり、p型の第3の窒化物半導体層134とオーミック接触している。p型の第3の窒化物半導体層134と第2の窒化物半導体層122とによりPN接合が形成される。これにより、ゲート電極133に印加する電圧が0Vの場合においても、p型の第3の窒化物半導体層134から基板101側及び第2のオーミック電極132側に向かって、第2の窒化物半導体層122及び第1の窒化物半導体層121中に空乏層が広がる。従って、ゲート電極133に印加する電圧が0Vの場合においてもチャネルを流れる電流が遮断される、ノーマリオフ動作を行わせることが可能となる。本実施形態においては、閾値電圧を調整するために、p型の第3の窒化物半導体層134及びゲート電極133は、第2の窒化物半導体層122の膜厚が他の部分よりも薄いゲートリセス部(図示せず)に形成されている。ゲート電極133は、Ni、Ti、銀(Ag)又は白金(Pt)等により形成することも可能である。p型の第3の窒化物半導体層134を用いてノーマリオフ動作をするノーマリオフ型としたが、ゲートリセス構造等によりノーマリオフ型を実現してもよい。また、ノーマリオン型とすることも可能である。

【0031】

窒化物半導体層積層体102の上には、第1のオーミック電極131、第2のオーミック電極132及びゲート電極133を覆うように、膜厚が300nm程度のシリコン窒化膜(SiN膜)である第1の絶縁膜141が形成されている。第1の絶縁膜141は、窒化物半導体層積層体102の表面を安定化すると共に、後述する第2の絶縁膜142から窒化物半導体層積層体102への水分の侵入を低減する機能を有する。第1の絶縁膜141は、第1のオーミック電極131の上面を露出するストライプ状の第1の開口部及び第2のオーミック電極132の上面を露出するストライプ状の第2の開口部を有している。

【0032】

第1の絶縁膜141の上には、第1のオーミック電極配線151及び第2のオーミック電極配線152が形成されている。第1のオーミック電極配線151は、第1の開口部において第1のオーミック電極131と接続され、第2のオーミック電極配線152は第2の開口部において第2のオーミック電極132と接続されている。第1のオーミック電極配線151及び第2のオーミック電極配線152は、TiとAuとの積層膜となっており、Tiは第1のオーミック電極131及び第2のオーミック電極132との密着性を向上させる密着層である。第1のオーミック電極配線151及び第2のオーミック電極配線152の膜厚は5μm程度とすればよく、幅はそれぞれ第1のオーミック電極131及び第2のオーミック電極132の幅と同じ又はそれよりも広くすることが好ましい。

【0033】

第1のオーミック電極配線151及び第2のオーミック電極配線152を覆うように、第2の絶縁膜142が形成されている。本実施形態において第2の絶縁膜142は、膜厚が400nm程度のSiNからなる第1の膜142Aと、膜厚が10μm程度のポリベンズオキサゾール(PBO)からなる第2の膜142Bとの積層膜である。第1の膜142Aは、第2の膜142Bから窒化物半導体層積層体102への水分の侵入を低減する機能と、第2の膜142Bと下側の層との密着性を向上させる機能とを有する。

【0034】

第2の絶縁膜142の上には、電極パッドである第1の金属層161、第2の金属層162及び第3の金属層163が形成されている。本実施形態において第1の金属層161及び第2の金属層162は、活性領域102Aの上に形成されている。第1の金属層161と第2の金属層162とは、ゲート電極133が延びる方向(ゲート幅方向)と交差する辺同士が相対するように、互いに間隔をおいて配置されている。第2の絶縁膜142は、第1の金属層161の下側において第1のオーミック電極配線151の上面を露出する第3の開口部を有している。第3の開口部を埋めるように第1の金属層161と一体となった第1のビア165が形成されており、第1のビア165により第1の金属層161と第1のオーミック電極配線151とは接続されている。また、第2の金属層162の下側において第2のオーミック電極配線152の上面を露出する第2の開口部を有している。第2の開口部を埋めるように第2の金属層162と一体となった第2のビア166が形成されており、第2のビア166により第2の金属層162と第2のオーミック電極配線152とは接続されている。

【0035】

第1の金属層161、第2の金属層162及び第3の金属層163は、Ti、銅(Cu)及びNiの積層膜とすればよい。シート抵抗を低く抑えるためにCu膜の厚さは5μm程度とすることが好ましい。最上層にNi膜を設けることにより、Alワイヤ又はAlリボン等との密着性が向上し、信頼性が高い半導体装置を実現することができる。Ni膜の膜厚は1μm程度とすることが好ましい。Niに代えてAgを用いることも可能である。Au又はCu等からなるワイヤ、リボン又はクリップ等を用いる場合には最表面をAu層としてもよい。

【0036】

本実施形態において、第3の金属層163は活性領域102Aの上の第1の金属層161側の領域に形成されている。このような構成とすることにより、第3の金属層163と第2の金属層162との間の耐圧を確保しつつ、半導体装置のサイズを小さくすることができる。第3の金属層163は、素子分離領域102Bの上に形成されたゲート電極配線153と第3のビア167を介して接続されている。ゲート電極配線153は、活性領域102Aの外周を迂回して配置され、ゲート電極133と接続されている。本実施形態においては、第1のオーミック電極配線151及び第2のオーミック電極配線152を素子分離領域102Bに引き出して束ねていないため、ゲート電極配線153が第1のオーミック電極配線151及び第2のオーミック電極配線152を横切ることがない。活性領域が複数形成されている場合には、活性領域の間の素子分離領域において、複数のゲート電極を束ねるようにゲート電極配線を形成してもよい。

【0037】

第1の金属層161及び第2の金属層162を、活性領域102Aの上に形成する場合には、第1のオーミック電極131の一部は第2の金属層162の下側に位置し、第2のオーミック電極132の一部は第1の金属層161の下側に位置する。仮に、第1のオーミック電極配線151を形成せずに、第1の金属層161と第1のオーミック電極131とをビアにより直接接続する場合、ビアと接するのは第1のオーミック電極131の第1の金属層161の下側に形成された部分だけである。第1のオーミック電極131は、膜厚が薄く幅も狭いため、配線抵抗が大きい。このため、第1のオーミック電極131の第2の金属層162の下側に形成されている部分においては、第1の金属層161と第1のオーミック電極131との間の抵抗を無視できなくなる。第2の金属層162と第2のオーミック電極132との間にも同じ問題が生じる。第1のオーミック電極131及び第2のオーミック電極132は、一般にリフトオフ法により形成するため、膜厚を厚くして配線抵抗を低減することは困難である。また、第1のオーミック電極131及び第2のオーミック電極132の幅は、デバイスのサイズによって制限されるため、幅を広くすることにより配線抵抗を低減することも困難である。

【0038】

本実施形態の半導体装置は、第1のオーミック電極131の上を覆うように第1のオーミック電極配線151が形成され、第2のオーミック電極132の上を覆うように第2のオーミック電極配線152が形成されている。第1のオーミック電極配線151及び第2のオーミック電極配線152は、第1のオーミック電極131及び第2のオーミック電極132よりも膜厚を厚くすることができるので、配線抵抗を小さくすることが容易である。このため、第1のオーミック電極配線151の第1の金属層161の下側の部分のみにビアが接続されていたとしても、第1の金属層161と第1のオーミック電極131との間の抵抗を小さく抑えることができる。第2の金属層162と第2のオーミック電極132との間においても同様である。本実施形態の半導体装置は、第1の金属層及び第2の金属層を第1のオーミック電極配線及び第2のオーミック電極配線を介さずに、第1のオーミック電極及び第2のオーミック電極と直接接続した場合と比べて、配線抵抗を約半分に低減することができる。

【0039】

配線抵抗を効果的に抑えるためには、第1のオーミック電極配線151及び第2のオーミック電極配線152は、ゲート幅方向と交差する方向の断面積が第1のオーミック電極131及び第2のオーミック電極132よりも大きくなるようにすればよい。第1のオーミック電極配線151及び第2のオーミック電極配線152をめっき法により形成すれば、膜厚を厚くすることが容易にできる。また、第1のオーミック電極配線151及び第2のオーミック電極配線152は、できるだけ電気抵抗が小さい材料を用いることが好ましく、Au若しくはCu又はこれらの合金等とすればよい。Al、Ni若しくはTi又はこれらの合金等を用いることも可能である。また、第1のオーミック電極131及び第2のオーミック電極132との密着性を向上するため、積層膜としてもよい。この場合には、密着層である下層は、Ti若しくはTa又はこれらの窒化物等を用いればよい。

【0040】

図1は第1のオーミック電極配線151がゲート電極133の上を覆うように形成された例を示している。第1のオーミック電極配線151をゲート電極133よりも第2のオーミック電極132側に張り出した構造とすることにより、第1のオーミック電極配線151の断面積を大きくすることができるだけでなく、第1のオーミック電極配線151をフィールドプレートとして機能させることが可能となる。さらに、第1の金属層161及び第2の金属層162が活性領域102Aの上に形成されている。これにより、半導体装置がオフの状態において、ゲート電極133の端部及び第1のオーミック電極配線151からなるフィールドプレートの端部における電界集中を緩和することができる。従って、パッドオンエレメント構造ではない場合と比べて、電流コラプスを抑制することができる。

【0041】

本実施形態においては、第2の絶縁膜142をSiNからなる第1の膜142AとPBOからなる第2の膜142Bとの積層膜とした。PBO膜等の有機膜はスピン塗布により形成できるため、凹部への埋め込みが容易であり、第2の絶縁膜142の上面を容易に平坦化できる。第2の絶縁膜142の上面を平坦にすることにより、第2の絶縁膜142の上に形成する電極パッドである金属層を平坦にすることができる。電極パッドを平坦にすることにより電極パッド面とワイヤとの接触面積を大きくなるため、配線の抵抗を低減したり、ワイヤボンディングの歩留まりを向上させたりすることができる。

【0042】

PBOはAuとの密着性に劣る。このため、最上層がAuである第1のオーミック電極配線151及び第2のオーミック電極配線152と、第2の絶縁膜142との密着性を向上させるために、第2の膜142Bと第1のオーミック電極配線151及び第2のオーミック電極配線152との間に、SiNからなる第1の膜142Aを設けている。第1の膜142AはSiO2膜等とすることも可能であるが、SiN膜は耐水性が高いため、下層への水分の透過を抑える効果が得られる。第1の膜142Aは例えばプラズマ化学気相堆積層(CVD)法等により形成すればよい。

【0043】

第1の金属層161と第1のオーミック電極配線151とを接続するための第3の開口部及び第2の金属層162と第2のオーミック電極配線152とを接続するための第4の開口部は、第1の膜142Aの上端部における幅よりも、第2の膜142Bの下端部における幅が広い形状とすることが好ましい。これにより、第1のビア165及び第2のビア166は、第2の膜142Bの下端部における面積が第1の膜142Aの上端部における面積より大きくなる。このような構成とすれば、Auとの密着性が悪い第2の膜142Bが第1のオーミック電極配線151及び第2のオーミック電極配線152の上面と直接接することがなく、第2の絶縁膜142の剥がれ等を抑えることができる。第1の膜142Aに形成する開口部は、ドライエッチングにより形成すればよい。第2の膜142Bに形成する開口部は、第2の膜142Bを感光性樹脂とする場合にはフォトリソグラフィーにより形成すればよい。また、SiO2膜等をハードマスクとして用いたドライエッチングにより形成してもよい。

【0044】

第2の膜142Bは、PBOに代えて、ポリイミド、ベンゾシクロブテン(BCB)、エポキシ系の感光性樹脂(例えば、化薬マイクロケム社製SU−8)又はフッ素系の感光性樹脂(例えば、旭硝子社製AL−X2)等の有機膜としてもよい。但し、ポリイミド等の吸湿性を有する材料を用いる場合には、吸湿により第2の膜142Bが膨張し、第2の膜142Bに亀裂が発生したり、下層への水分の透過が生じたりするおそれがある。このため、第2の膜142Bの上にさらに耐水性の第3の膜を形成することが好ましい。

【0045】

Al−X2等のAuとの密着性に優れた材料を用いた場合には、第1の膜142Aを省略してもよい。また、第1のオーミック電極配線151及び第2のオーミック電極配線152の最上層をTi又はCu等の有機膜と比較的密着しやすい材料とした場合にも、第1の膜142Aを省略することが可能である。

【0046】

また、第2の膜142Bにガラス系材料を用いてもよい。この場合には、リンを含有することが望ましい。このようにすることにより、第2の絶縁膜142の膜応力を緩和し、膜剥がれの発生を抑えることができる。また、リンのゲッタリング効果により、活性領域102Aへのアルカリ性不純物の侵入を防ぐ効果も得られるため、半導体装置の信頼性を向上させることができる。

【0047】

本実施形態においては、第3の金属層163の面積を、第1の金属層161及び第2の金属層162よりも小さくしている。これは、ゲート電極には高い電圧を印加する必要がないため、第3の金属層163には細いワイヤを接続するためである。また、第3の金属層163を第1の金属層161よりに形成している。これは、ドレイン電極パッドである第2の金属層162には、より高い電圧を印加するためである。但し、必要な絶縁破壊耐圧を確保できれば、第3の金属層163の位置は特に限定されない。

【0048】

第1の金属層161と第2の金属層162及び第3の金属層163と第2の金属層162との最小の間隔をS1とし、半導体装置全体を封止する樹脂封止の絶縁破壊耐圧をA1とすると、S1とA1との積が必要とする絶縁耐圧よりも大きくなるようにすればよい。

【0049】

また、絶縁破壊耐圧を確保するためには、電極パッドである金属層同士の間隔だけでなく、第1のオーミック電極配線151と第2のオーミック電極配線152との間隔、第1のオーミック電極配線151と第2の金属層162との間隔、第2のオーミック電極配線152と第1の金属層161との間隔も重要である。これらの間隔のうちの最も狭いものをS2とし、第2の絶縁膜142の絶縁破壊電圧をA2とすると、S2とA2との積が必要とする絶縁破壊耐圧よりも大きくなるようにすればよい。例えば、PBOの絶縁破壊電圧は250V/μmである。このため、必要とする絶縁破壊耐圧が600Vの場合には、最小の間隔S1を2.4μm以上とし、1000Vの場合には4μm以上とすればよい。本実施形態においては、S1を5μmとなるように設計した。

【0050】

本実施形態の半導体装置は、基板101における窒化物半導体層積層体102と反対側の面(裏面)には、例えばAu、スズ(Sn)、クロム(Cr)若しくはNi又はこれらの合金等からなる裏面電極164を形成した例を示している。裏面電極164を形成することにより外部から基板101に電位を与えることが可能となる。また、裏面電極164と第1のオーミック電極131とを電気的に接続してもよい。この場合には、裏面電極164をソース電極パッドとすることも可能である。裏面電極164と第1のオーミック電極131との接続には貫通ビアを用いてもよい。裏面電極164は例えば、スパッタ法又は蒸着法等により形成すればよい。

【0051】

本実施形態の半導体装置は、第1の金属層161と第1のオーミック電極配線151とを接続する第1のビア165は、活性領域102Aの上に複数形成されている。第2の金属層162と第2のオーミック電極配線152とを接続する第2のビア166も同様である。このため、ワイヤボンディングの際の圧力から活性領域を保護する効果が得られる。しかし、第1の金属層161と第1のオーミック電極配線151とを接続する第1のビア165及び第2の金属層162と第2のオーミック電極配線152とを接続する第2のビア166は、素子分離領域102Bの上に形成してもよい。この場合には、図4に示すように、第1のオーミック電極配線151を互いに接続する配線155を素子分離領域102Bに形成し、配線155と第1の金属層161とを第1のビア165により接続すればよい。また、第2のオーミック電極配線152を互いに接続する配線156を活性領域102Aを挟んで配線155と反対側に形成し、配線156と第2の金属層162とを第2のビア166により接続すればよい。

【0052】

本実施形態において、シングルゲートの半導体装置について説明したが、インバータ又はマトリックスコンバータ等に用いることができるダブルゲートの半導体装置においても同様の構成としてかまわない。図5及び図6は、ダブルゲートの半導体装置の例であり、図5は平面構成を示し、図6は図5のVI−VI線における断面構成を示している。

【0053】

ダブルゲートの半導体装置は、第1のオーミック電極131と第2のオーミック電極132との間に、第1のゲート電極133Aと第2のゲート電極133Bとが、第1のオーミック電極131側から順に形成されている。図6は、ノーマリオフ型とするため第1のゲート電極133A及び第2のゲート電極133Bを、それぞれp型の第3の窒化物半導体層134の上に形成した例を示している。但し、ゲートリセス構造によりノーマリオフ型にしたり、ノーマリオン型にしたりすることも可能である。

【0054】

第1のゲート電極133A及び第2のゲート電極133Bに所定のバイアスを印加することにより、双方向スイッチとしても、ダイオードとしても動作させることができる。例えば、第1のゲート電極133Aと第2のゲート電極133Bとに、それぞれ、第1のオーミック電極131を基準として第1のゲート電極133Aの閾値電圧以上の電圧を印加し、第2のオーミック電極132を基準として第2のゲート電極133Bの閾値電圧以上の電圧を印加することにより、第1のオーミック電極131と第2のオーミック電極132との間に双方向に電流が流れる双方向通電動作をさせることができる。一方、第1のゲート電極133A及び第2のゲート電極133Bに印加するバイアス電圧をそれぞれ閾値電圧以下の電圧とすることにより第1のオーミック電極131と第2のオーミック電極132との間に双方向に電流が流れない双方向遮断動作をさせることができる。

【0055】

また、第1のゲート電極133Aに閾値電圧以上の電圧を印加し、第2のゲート電極133Bに閾値電圧以下の電圧を印加することにより、第1のオーミック電極131から第2のオーミック電極132へは電流が流れないが、第2のオーミック電極132から第1のオーミック電極131へは電流が流れるダイオード動作をさせることができる。第1のゲート電極133Aに閾値電圧以下の電圧を印加し、第2のゲート電極133Bに閾値電圧以上の電圧を印加することにより、第1のオーミック電極131から第2のオーミック電極132へは電流が流れるが、第2のオーミック電極132から第1のオーミック電極131へは電流が流れないダイオード動作をさせることができる。

【0056】

図5は、第1のオーミック電極配線151が第1のゲート電極133Aよりも第2のゲート電極133B側に広がり、第2のオーミック電極配線152が第2のゲート電極133Bよりも第1のゲート電極133A側に広がっている例を示している。このようにすれば、第1のオーミック電極配線151及び第2のオーミック電極配線152が、それぞれフィールドプレートとして機能する。また、第1のゲート電極133Aと第2のゲート電極133Bとの間に発生する電気力線の一部を、第1のオーミック電極配線151及び第2のオーミック電極配線152により切断することができる。これにより、第1のゲート電極133Aと第2のゲート電極133Bとの間の寄生抵抗Cggを低減することが可能となり、ゲートノイズを抑制することができる。

【0057】

図5に示すように、第1のゲート電極133A同士を接続する第1のゲート電極配線153Aと第2のゲート電極同士を接続する第2のゲート電極配線153Bとを、活性領域102Aを挟んで反対側に形成することにより、配線の形成が容易となる。第3の金属層163Aは、第1の金属層161側に形成し、第4の金属層163Bは、第2の金属層162側に形成することが好ましい。

【0058】

図7に示すように、ショットキーダイオードにおいても同様の構成とすることができる。この場合には、2DEGとオーミック接触したカソード電極である第1の電極231と、ショットキー接触したアノード電極である第2の電極232とを設ければよい。第1の電極231は、第1の電極配線251を介して第1の金属層261と接続し、第2の電極232は、第2の電極配線252を介して第2の金属層262と接続すればよい。

【0059】

図7では、第1の金属層261と第1の電極配線251とを接続する第1のビア265及び第2の金属層262と第2の電極配線252とを接続する第2のビア266を活性領域102Aの上に形成する例を示した。しかし、第1の電極配線251を互いに接続する配線及び第2の電極配線252を互いに接続する配線を素子分離領域102Bに形成し、電極パッドである金属層と配線とを接続するビアを素子分離領域102Bの上に形成してもよい。

【0060】

第1の電極231は、TiとNiとの積層体等とすればよく、第2の電極232はPd及びAuの合金等とすればよい。

【産業上の利用可能性】

【0061】

本発明に係る窒化物半導体装置は、活性層の上に電極パッドを形成する場合に生じる問題を解決し、オン抵抗の上昇を抑えることができ、電源回路用のパワーデバイス等を含む窒化物半導体装置として有用である。

【符号の説明】

【0062】

101 基板

102 窒化物半導体層積層体

102A 活性領域

102B 素子分離領域

120 バッファ層

121 第1の窒化物半導体層

122 第2の窒化物半導体層

131 第1のオーミック電極

132 第2のオーミック電極

133 ゲート電極

133A 第1のゲート電極

133B 第2のゲート電極

134 第3の窒化物半導体層

141 第1の絶縁膜

142 第2の絶縁膜

142A 第1の膜

142B 第2の膜

151 第1のオーミック電極配線

152 第2のオーミック電極配線

153 ゲート電極配線

153A 第1のゲート電極配線

153B 第2のゲート電極配線

155 配線

156 配線

161 第1の金属層

162 第2の金属層

163 第3の金属層

163A 第3の金属層

163B 第4の金属層

164 裏面電極

165 第1のビア

166 第2のビア

167 第3のビア

231 第1の電極

232 第2の電極

251 第1の電極配線

252 第2の電極配線

261 第1の金属層

262 第2の金属層

265 第1のビア

266 第2のビア

【特許請求の範囲】

【請求項1】

基板の上に形成され、素子分離領域に囲まれた活性領域を有する窒化物半導体層積層体と、

前記活性領域の上に互いに間隔をおいて形成されたフィンガー状の第1の電極及び第2の電極と、

前記第1の電極及び第2の電極を覆い、前記第1の電極の上面を露出する第1の開口部及び前記第2の電極の上面を露出する第2の開口部を有する第1の絶縁膜と、

前記第1の電極の上に形成され、前記第1の開口部において前記第1の電極と接する第1の電極配線と、

前記第2の電極の上に形成され、前記第2の開口部において前記第2の電極と接する第2の電極配線と、

前記第1の電極配線及び第2の電極配線を覆う第2の絶縁膜と、

前記第2の絶縁膜を介して前記活性領域の上に形成され、前記第1の電極配線と接続された第1の金属層とを備えていることを特徴とする窒化物半導体装置。

【請求項2】

前記第2の絶縁膜の上に前記第1の金属層と間隔をおいて形成された第2の金属層をさらに備え、

前記第2の金属層は、前記活性領域の上に形成され、前記第2の電極配線と接続されていることを特徴とする請求項1に記載の窒化物半導体装置。

【請求項3】

前記第1の金属層と前記第1の電極配線とを接続する第1のビアと、

前記第2の金属層と前記第2の電極配線とを接続する第2のビアとをさらに備え、

前記第1のビア及び第2のビアは前記活性領域の上に形成されていることを特徴とする請求項2に記載の窒化物半導体装置。

【請求項4】

前記第1の金属層と前記第1の電極配線とを接続する第1のビアと、

前記第2の金属層と前記第2の電極配線とを接続する第2のビアとをさらに備え、

前記第1のビア及び第2のビアは、前記素子分離領域の上に形成されていることを特徴とする請求項2に記載の窒化物半導体装置。

【請求項5】

前記第2の絶縁膜は、シリコン窒化膜又はシリコン酸化膜である第1の膜と、該第1の膜の上に形成された有機絶縁膜である第2の膜とを有し、

前記第1のビア及び第2のビアの開口部は、前記第2の膜の下端部における開口部の面積が、前記第1の膜の上端部における開口部の面積よりも大きいことを特徴とする請求項3又は4に記載の窒化物半導体装置。

【請求項6】

前記第1の電極配線と前記第2の電極配線との最短距離、前記第1の電極配線と前記第2の金属層との最短距離及び前記第2の電極配線と前記第1の金属層との最短距離のうちの最小の距離と、前記第2の絶縁膜の絶縁破壊電圧との積は、600V以上であることを特徴とする請求項2〜5のいずれか1項に記載の窒化物半導体装置。

【請求項7】

前記第1の電極は、カソード電極であり、

前記第2の電極は、アノード電極であることを特徴とする請求項1〜5のいずれか1項に記載の窒化物半導体装置。

【請求項8】

前記第1の電極と、前記第2の電極との間に形成されたフィンガー状の第1のゲート電極と、

前記第2の絶縁膜の上に、前記第1の金属層及び第2の金属層と間隔をおいて形成され且つ前記第1のゲート電極と接続された第3の金属層とをさらに備え、

前記第3の金属層と前記第2の金属層との間隔は、前記第3の金属層と前記第1の金属層との間隔以上であり、

前記第1の電極は、ソース電極であり、

前記第2の電極は、ドレイン電極であることを特徴とする請求項2〜5のいずれか1項に記載の窒化物半導体装置。

【請求項9】

前記基板に垂直で且つ前記第1の電極配線及び第2の電極配線を垂直に横切る断面において、

前記第1の電極配線の前記第2の電極側の端部は、前記第1のゲート電極よりも前記第2の電極側に位置していることを特徴とする請求項8に記載の窒化物半導体装置。

【請求項10】

前記第1のゲート電極と前記窒化物半導体層積層体との間に形成されたp型の窒化物半導体層をさらに備えていることを特徴とする請求項7又は8に記載の窒化物半導体装置。

【請求項11】

前記第1の電極と、前記第2の電極との間に、前記第1の電極側から順次形成されたフィンガー状の第1のゲート電極及び第2のゲート電極と、

前記第2の絶縁膜の上に、前記第1の金属層及び第2の金属層と間隔をおいて形成され且つ前記第1のゲート電極と接続された第3の金属層及び前記第2のゲート電極と接続された第4の金属層とをさらに備え、

前記第3の金属層と前記第2の金属層との間隔は、前記第3の金属層と前記第1の金属層との間隔以上であり、

前記第1の電極は、第1のオーミック電極であり、

前記第2の電極は、第2のオーミック電極であることを特徴とする請求項2〜5のいずれか1項に記載の窒化物半導体装置。

【請求項12】

前記基板に垂直で且つ前記第1の電極配線及び第2の電極配線を垂直に横切る断面において、

前記第1の電極配線の前記第2の電極側の端部は、前記第1のゲート電極よりも前記第2の電極側で且つ前記第2のゲート電極よりも前記第1のゲート電極側に位置し、

前記第2の電極配線の前記第1の電極側の端部は、前記第2のゲート電極よりも前記第1の電極側で且つ前記第1のゲート電極よりも前記第2のゲート電極側に位置していることを特徴とする請求項11に記載の窒化物半導体装置。

【請求項13】

前記第1のゲート電極及び第2のゲート電極と前記窒化物半導体層積層体との間にそれぞれ形成されたp型の窒化物半導体層をさらに備えていることを特徴とする請求項11又は12に記載の窒化物半導体装置。

【請求項1】

基板の上に形成され、素子分離領域に囲まれた活性領域を有する窒化物半導体層積層体と、

前記活性領域の上に互いに間隔をおいて形成されたフィンガー状の第1の電極及び第2の電極と、

前記第1の電極及び第2の電極を覆い、前記第1の電極の上面を露出する第1の開口部及び前記第2の電極の上面を露出する第2の開口部を有する第1の絶縁膜と、

前記第1の電極の上に形成され、前記第1の開口部において前記第1の電極と接する第1の電極配線と、

前記第2の電極の上に形成され、前記第2の開口部において前記第2の電極と接する第2の電極配線と、

前記第1の電極配線及び第2の電極配線を覆う第2の絶縁膜と、

前記第2の絶縁膜を介して前記活性領域の上に形成され、前記第1の電極配線と接続された第1の金属層とを備えていることを特徴とする窒化物半導体装置。

【請求項2】

前記第2の絶縁膜の上に前記第1の金属層と間隔をおいて形成された第2の金属層をさらに備え、

前記第2の金属層は、前記活性領域の上に形成され、前記第2の電極配線と接続されていることを特徴とする請求項1に記載の窒化物半導体装置。

【請求項3】

前記第1の金属層と前記第1の電極配線とを接続する第1のビアと、

前記第2の金属層と前記第2の電極配線とを接続する第2のビアとをさらに備え、

前記第1のビア及び第2のビアは前記活性領域の上に形成されていることを特徴とする請求項2に記載の窒化物半導体装置。

【請求項4】

前記第1の金属層と前記第1の電極配線とを接続する第1のビアと、

前記第2の金属層と前記第2の電極配線とを接続する第2のビアとをさらに備え、

前記第1のビア及び第2のビアは、前記素子分離領域の上に形成されていることを特徴とする請求項2に記載の窒化物半導体装置。

【請求項5】

前記第2の絶縁膜は、シリコン窒化膜又はシリコン酸化膜である第1の膜と、該第1の膜の上に形成された有機絶縁膜である第2の膜とを有し、

前記第1のビア及び第2のビアの開口部は、前記第2の膜の下端部における開口部の面積が、前記第1の膜の上端部における開口部の面積よりも大きいことを特徴とする請求項3又は4に記載の窒化物半導体装置。

【請求項6】

前記第1の電極配線と前記第2の電極配線との最短距離、前記第1の電極配線と前記第2の金属層との最短距離及び前記第2の電極配線と前記第1の金属層との最短距離のうちの最小の距離と、前記第2の絶縁膜の絶縁破壊電圧との積は、600V以上であることを特徴とする請求項2〜5のいずれか1項に記載の窒化物半導体装置。

【請求項7】

前記第1の電極は、カソード電極であり、

前記第2の電極は、アノード電極であることを特徴とする請求項1〜5のいずれか1項に記載の窒化物半導体装置。

【請求項8】

前記第1の電極と、前記第2の電極との間に形成されたフィンガー状の第1のゲート電極と、

前記第2の絶縁膜の上に、前記第1の金属層及び第2の金属層と間隔をおいて形成され且つ前記第1のゲート電極と接続された第3の金属層とをさらに備え、

前記第3の金属層と前記第2の金属層との間隔は、前記第3の金属層と前記第1の金属層との間隔以上であり、

前記第1の電極は、ソース電極であり、

前記第2の電極は、ドレイン電極であることを特徴とする請求項2〜5のいずれか1項に記載の窒化物半導体装置。

【請求項9】

前記基板に垂直で且つ前記第1の電極配線及び第2の電極配線を垂直に横切る断面において、

前記第1の電極配線の前記第2の電極側の端部は、前記第1のゲート電極よりも前記第2の電極側に位置していることを特徴とする請求項8に記載の窒化物半導体装置。

【請求項10】

前記第1のゲート電極と前記窒化物半導体層積層体との間に形成されたp型の窒化物半導体層をさらに備えていることを特徴とする請求項7又は8に記載の窒化物半導体装置。

【請求項11】

前記第1の電極と、前記第2の電極との間に、前記第1の電極側から順次形成されたフィンガー状の第1のゲート電極及び第2のゲート電極と、

前記第2の絶縁膜の上に、前記第1の金属層及び第2の金属層と間隔をおいて形成され且つ前記第1のゲート電極と接続された第3の金属層及び前記第2のゲート電極と接続された第4の金属層とをさらに備え、

前記第3の金属層と前記第2の金属層との間隔は、前記第3の金属層と前記第1の金属層との間隔以上であり、

前記第1の電極は、第1のオーミック電極であり、

前記第2の電極は、第2のオーミック電極であることを特徴とする請求項2〜5のいずれか1項に記載の窒化物半導体装置。

【請求項12】

前記基板に垂直で且つ前記第1の電極配線及び第2の電極配線を垂直に横切る断面において、

前記第1の電極配線の前記第2の電極側の端部は、前記第1のゲート電極よりも前記第2の電極側で且つ前記第2のゲート電極よりも前記第1のゲート電極側に位置し、

前記第2の電極配線の前記第1の電極側の端部は、前記第2のゲート電極よりも前記第1の電極側で且つ前記第1のゲート電極よりも前記第2のゲート電極側に位置していることを特徴とする請求項11に記載の窒化物半導体装置。

【請求項13】

前記第1のゲート電極及び第2のゲート電極と前記窒化物半導体層積層体との間にそれぞれ形成されたp型の窒化物半導体層をさらに備えていることを特徴とする請求項11又は12に記載の窒化物半導体装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【公開番号】特開2012−23074(P2012−23074A)

【公開日】平成24年2月2日(2012.2.2)

【国際特許分類】

【出願番号】特願2010−157574(P2010−157574)

【出願日】平成22年7月12日(2010.7.12)

【出願人】(000005821)パナソニック株式会社 (73,050)

【Fターム(参考)】

【公開日】平成24年2月2日(2012.2.2)

【国際特許分類】

【出願日】平成22年7月12日(2010.7.12)

【出願人】(000005821)パナソニック株式会社 (73,050)

【Fターム(参考)】

[ Back to top ]