窒化物系半導体装置

【課題】MOS型デバイスのゲート絶縁膜の破壊を防止すると共に、信頼性を向上させ、かつ、チップサイズの増加を抑制した、窒化物系半導体装置を提供することができる、窒化物系半導体装置を提供することを目的とする。

【解決手段】ショットキー電極30が、ソース電極24とドレイン電極26とが対向する領域の、ソース電極24とドレイン電極26とが対向する方向と略直交する方向にゲート電極28と並んで形成されている。ショットキー電極30は、AlGaN層20とショットキー接合されており、ソース電極24に電気的に接続されている。

【解決手段】ショットキー電極30が、ソース電極24とドレイン電極26とが対向する領域の、ソース電極24とドレイン電極26とが対向する方向と略直交する方向にゲート電極28と並んで形成されている。ショットキー電極30は、AlGaN層20とショットキー接合されており、ソース電極24に電気的に接続されている。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、MOS構造を有するノーマリオフの窒化物系の半導体装置に関するものである。

【背景技術】

【0002】

従来から高周波デバイス用半導体素子には、半導体材料として窒化ガリウム(GaN)系化合物半導体装置(以下、GaN系半導体素子という)が用いられている。GaN系半導体素子では、基板の表面に、例えば有機金属化学気相成長(MOCVD:Metal−Organic Chemical Vapor Deposition)法を用いて形成されたバッファ層や、不純物がドープされた電子走行層が設けられている。最近では、高周波用途に加え、電力用半導体素子(パワーデバイス)にも適用可能であるという認識から、高耐圧、大電流を扱うGaN系半導体素子の開発が行われている。

【0003】

特許文献1には、MOS構造を有する窒化ガリウム系半導体素子が記載されている。特許文献1に記載されたMOS構造を有する窒化ガリウム系半導体素子の概略構成図を図13に示す。図13に示すように、従来の窒化ガリウム系半導体素子100は、基板112上に、GaN結晶を積層するためのバッファ層114を介して電子走行層として機能するGaN層116及び電子供給層として機能するAlGaN層120が積層され、ヘテロ接合構造が形成されている。図13の窒化ガリウム系半導体素子100では、GaN層116とAlGaN層120との界面直下(GaN層116の表面)に形成された2次元電子ガス118(2DEG:Two Dimensional Electron Gas)がキャリアとして利用される。

【0004】

AlGaN層120の表面の一部にはリセス部121が形成される。当該リセス部121にゲート絶縁膜123を介して、ゲート電極128が配置されて、MOS(n型MOS)構造(MOSFET部)を構成する。また、AlGaN層120の表面には表面保護膜122が形成されている。

【0005】

ゲート電極128に正の電圧を印加すると、ゲート絶縁膜123と接したGaN層116の表面に電子が集まり、MOSチャネルを形成し(オン状態になり)、GaN層116とAlGaN層120との界面に形成された2DEG層118と電気的に接続されて、ソース電極124とドレイン電極126との間が電気的に導通された状態になる。

【0006】

また、MOSチャネルがオフ状態の場合には、ソース電極124とドレイン電極126との間に電圧が印加されるとゲート端部から2DEG層118が空乏化して高耐圧を維持することが可能となり、大電力かつ、高耐圧の半導体素子として機能する。そのため、近年、高周波で高効率の電力用半導体素子として窒化物系半導体素子の開発が進んでいる。従来、ゲート部がショットキー接合となっているいわゆるHEMT(High Electron Mobility Transistor)と呼ばれるデバイスが主に開発されてきた。このようなデバイスは、絶縁ゲートのほうが駆動回路が容易であること、及びMOSFET部に印加されるゲート電圧が0Vの場合(ゲート電圧を印加しない場合)に、電気的にオフ状態になる、いわゆるノーマリオフデバイスに用いることが容易であることから、注目されている。

【0007】

電力用半導体素子として使用するためには、高速で動作し、導通抵抗が低いということは大きな利点である。一方、2DEG層118を空乏化させようとすると、ゲート部のドレイン側端部129に大きな電界が集中し、ゲート絶縁膜123が破壊されてしまうという不具合が頻発する場合があることがわかった。この原因は、高電界で発生した正孔がゲート絶縁膜123及びゲート絶縁膜123に近いAlGaN層120/GaN層116近傍に集まって、ドレイン電極126に印加された電圧の殆どがゲート絶縁膜123に印加されてしまうことためであることがわかった。

【0008】

さらに、破壊されない場合であっても、長時間にわたってドレイン電極126に大きな電圧を印加し続けた場合、ゲート絶縁膜123に高電界が長時間印加されることになり、その特性が経時的に劣化してしまうという、信頼性上の問題が発生する場合がある。

【0009】

これを防止するためには、2DEGの電子濃度を2×1012cm−2程度以下の濃度にすることが考えられる。これにより2DEGが空乏化されやすくなり、耐圧が維持される効果が得られる。しかし、2DEGの濃度を下げてしまうと、2DEG層118部分の導通抵抗が大きくなってしまうため、素子全体としてのオン抵抗が上昇してしまい、本来の窒化物系半導体を用いた素子としての利点が失われてしまうという難点がある。

【0010】

また、その他の手段として、ゲート電極128のドレイン側端部に、ゲート電極128端部に集中する電解を緩和するためにフィールドプレートとよばれる、ゲート絶縁膜123よりも厚い表面保護膜122の上にゲート電極128を延長させて、薄いゲート絶縁膜123部分の電界を和らげる手段が挙げられる。しかしながら、当該手段においても、2DEGの電子濃度が3×1012cm−2以上の場合では、ゲート絶縁膜123を保護することが困難である。

【0011】

またさらに、別の手段として、GaN層116をp型とすることにより、ゲート絶縁膜123周辺に集まる正孔をp型領域へと排出し、2DEG層118を空乏化させやすくするという手段が挙げられる。当該手段は、例えば、非特許文献1に示されているように、そのアクセプタ濃度を制御することにより空乏層が拡がりやすくなり、高耐圧を達成できるという利点がある。しかしながら、一般に、窒化ガリウムのp型層を形成することは困難であり、さらに濃度制御を1×1017cm−3程度で行うことが非常に難しい。特に基板112がシリコンより成る場合には、p型層そのものを得ることが困難である。すなわち、非常に制限された濃度範囲、基板材料の選択が必要となる。

【0012】

また、図13の構造においては、ソース側とドレイン側がゲート電極128を挟んで基本的に対照的な構造を有しているため、いわゆるフリーホイリングダイオード(以下、FWDという)が無い。このため、例えば、インバータ等に使用する場合には、窒化物系半導体素子外部にFWDの機能をになうダイオードを並列に接続することが必要とされる。

【0013】

一方、特許文献2には、ノーマリオンデバイスである、いわゆる高耐圧JFET(Junction−Field−Effect−Transistor)と低耐圧MOSFETとを直列にカスケード接続した高耐圧パワーデバイスが記載されている。図14に、当該JFETとMOSFETとの接続状況を示す。これは、JFETのゲート端子を直列に接続されたMOSFETのソースと短絡し、外から見ると、あたかも絶縁ゲートデバイスのように動作させようとするものである。MOSFETは、低耐圧でオン抵抗の低いデバイスを使用することができるため、JFETはノーマリオンであるが、高耐圧で抵抗の低いSiC MOSFETは低耐圧シリコンのMOSFETを接続し、ノーマリオフでオン抵抗が低く高耐圧のデバイスを実現させている。

【0014】

一方、例えば、図15に示すような、特許文献3に示される窒化物系半導体素子が知られている。図15に示した半導体素子200は、背面電極235、基板212、バッファ層214、電子走行層216、2DEG層218、電子供給層220、絶縁膜233、ソース電極224、ドレイン電極226、ゲート電極28、及びショットキー電極231を備えて構成されている。半導体素子200では、電子供給層220上に直接、ソース電極224、ドレイン電極226、ゲート電極28、及びショットキー電極231が形成されており、ドレイン電極226とゲート電極28との間に設けられたショットキー電極231がソース電極224と短絡されていることにより、高速動作を実現させている。この窒化物系半導体素子は、ゲート電極28部分にリセスが形成されておらず、特許文献1のように、図13でのドレイン側端部129に大きな電界が集中し、ゲート絶縁膜123が破壊されてしまうという不具合は生じない。しかし、特許文献3に示される窒化物系半導体素子は、ノーマリオン型であるため、故障時の安全性を確保できない。

【先行技術文献】

【特許文献】

【0015】

【特許文献1】国際公開第2003/071607号パンフレット

【特許文献2】US−6900537号公報

【特許文献3】特開2007−273795号公報

【非特許文献】

【0016】

【非特許文献1】Proceedings of International Symposium on Power Semiconductor Device and IC's “Enhancement-mode GaN Hybrid MOS-HEMTs with Ron,sp of 20mΩ-cm2”(2008) pp.295-298

【発明の概要】

【発明が解決しようとする課題】

【0017】

本発明は、上記に鑑みてなされたものであって、MOS型デバイスのゲート絶縁膜の破壊を防止すると共に、信頼性を向上させ、かつ、チップサイズの増加を抑制した、窒化物系半導体装置を提供することを目的とする。

【課題を解決するための手段】

【0018】

請求項1に記載の窒化物系半導体装置は、基板と、前記基板上に形成されたバッファ層と、前記バッファ層上に形成された窒化物系化合物半導体より成る電子走行層と、前記電子走行層上に形成され、前記電子走行層とはバンドギャップエネルギーが異なる電子供給層と、前記電子供給層上に、対向して配置されたソース電極及びドレイン電極と、前記ソース電極と前記ドレイン電極との間でかつ、前記ソース電極と前記ドレイン電極とが対向する方向と直交する方向の一部の領域に、前記電子供給層の表面から少なくとも前記電子走行層の表面に到るまでの領域に形成されたリセス部と、前記ソース電極と前記ドレイン電極との間でかつ、前記ソース電極と前記ドレイン電極とが対向する方向と直交する方向の他の領域に形成された、前記ソース電極に接続されてキャリアを輸送するキャリア輸送用電極と、前記リセス部内部を覆うように形成されたゲート絶縁膜と、前記リセス部内の前記ゲート絶縁膜上に形成されたゲート電極と、を備える。

【0019】

請求項2に記載の窒化物系半導体装置は、請求項1に記載の窒化物系半導体装置において、前記電子走行層に発生する2次元電子ガスのシートキャリア濃度は2×1012cm−2以上である。

【0020】

請求項3に記載の窒化物系半導体装置は、請求項1または請求項2に記載の半導体装置において、前記キャリア輸送用電極と前記ドレイン電極との距離が、前記ゲート電極と前記ドレイン電極との距離よりも短い。

【0021】

請求項4に記載の窒化物系半導体装置は、請求項1から請求項3のいずれか1項に記載の窒化物系半導体装置において、前記キャリア輸送用電極が、前記電子供給層及び前記電子走行層の少なくとも一方とショットキー接合されている。

【0022】

請求項5に記載の窒化物系半導体装置は、請求項4に記載の窒化物系半導体装置において、前記電子供給層の表面から前記電子供給層内部または前記電子走行層内部に到る深さまでの領域に前記キャリア輸送用電極が形成されている。

【0023】

請求項6に記載の窒化物系半導体装置は、請求項1から請求項3のいずれか1項に記載の窒化物系半導体装置において、前記電子供給層上にp型半導体層を備え、前記p型半導体層上に前記キャリア輸送用電極がオーミック接合されている。

【0024】

請求項7に記載の窒化物系半導体装置は、請求項1から請求項6のいずれか1項に記載の窒化物系半導体装置において、前記ソース電極から前記リセス部の下部領域に到るまでの前記ゲート絶縁膜の下部領域に形成され、前記ソース電極に接続された第1のn+半導体層と、前記リセス部の下部領域から前記キャリア輸送用電極の手前に到るまでの前記ゲート絶縁膜の下部領域に形成され、前記キャリア輸送用電極に接続されていない第2のn+層のうち少なくともいずれかを備える。

【0025】

請求項8に記載の窒化物系半導体装置は、請求項1から請求項7のいずれか1項に記載の窒化物系半導体装置において、前記ドレイン電極の下部領域の電子供給層及び電子走行層にn+半導体層を備える。

【発明の効果】

【0026】

MOS型デバイスのゲート絶縁膜の破壊を防止すると共に、信頼性を向上させ、かつ、チップサイズの増加を抑制した、窒化物系半導体装置を提供することができる、という効果を奏する。

【図面の簡単な説明】

【0027】

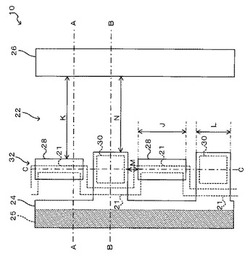

【図1】本発明の第1の実施の形態に係る窒化物系半導体素子の概略構成の一例を示す平面図である。

【図2】図1に示した窒化物系半導体素子のA−A断面の概略構成の一例を示す断面図である。

【図3】図1に示した窒化物系半導体素子のB−B断面の概略構成の一例を示す断面図である。

【図4】図1に示した窒化物系半導体素子のC−C断面の概略構成の一例を示す断面図である。

【図5】図1に示した窒化物系半導体素子の等価回路を示した回路図である。

【図6】図1に示した窒化物系半導体素子のその他の一例を示す平面図である。

【図7】図1に示した窒化物系半導体素子の製造方法の一例の一工程を説明するための説明図である。

【図8】図1に示した窒化物系半導体素子の製造方法の一例の一工程を説明するための説明図である。

【図9】本発明の第2の実施の形態に係る窒化物系半導体素子の概略構成の一例を示す断面図である。

【図10】本発明の第3の実施の形態に係る窒化物系半導体素子の概略構成の一例を示す断面図である。

【図11】本発明の第4の実施の形態に係る窒化物系半導体素子の概略構成の一例を示す断面図である。

【図12】本発明の第5の実施の形態に係る窒化物系半導体素子の概略構成の一例を示す断面図である。

【図13】従来の窒化物系半導体素子の概略構成の一例を示す断面図である。

【図14】従来の窒化物系半導体素子の等価回路を示した回路図である。

【図15】従来の窒化物系半導体素子の概略構成の一例を示す断面図である。

【発明を実施するための形態】

【0028】

[第1の実施の形態]

【0029】

以下、図面を参照して本実施の形態の窒化物系半導体装置について詳細に説明する。なお、本実施の形態は本発明の半導体装置の一例であり、本実施の形態により本発明が限定されるものではない。

【0030】

本実施の形態の窒化物系半導体装置である窒化物系半導体素子の概略構成の一例を示す平面図を図1に示す。また、図1に示した窒化物系半導体素子のA−A断面の概略構成の一例を図2に、B−B断面の概略構成の一例を図3に、C−C断面の概略構成の一例を図4にそれぞれ示す。

【0031】

本実施の形態の窒化物系半導体素子10は、基板12、バッファ層14、GaN層16、AlGaN層20、表面保護膜22、ゲート絶縁膜23、ソース電極24、ドレイン電極26、ゲート電極28、ショットキー電極30、及び層間絶縁膜38を備えて構成されている。また、本実施の形態の窒化物系半導体素子10は、等価回路としての見方をするとMOSFET部32とHEMT部34により構成されている。

【0032】

基板12の具体的一例としては、シリコン、サファイア、SiC、ZrB2、Si、GaN、MgO等、窒化物系化合物半導体を結晶成長させることが可能な材料からなる基板が挙げられる。バッファ層14は、GaN結晶を積層するための機能を有する層であり、GaN、AlN、AlGaN等を用いることができ、バッファ層14上に形成される電子走行層(本実施の形態ではGaN層16)を形成するGaN結晶と格子整合するように形成される。

【0033】

GaN層16は、電子走行層として機能するものであり、アンドープのGaN等からなる。また、GaN層16はN型でもP型でもよい。AlGaN層20は、電子供給層として機能するものであり、GaN層16とバンドギャップエネルギーが異なるAlGaN等からなる。また、AlGaN層20は、Al濃度の異なる複数の層構成を有していてもよい。GaN層16とAlGaN層20との界面にバンドオフセットが形成されると共に、AlGaN/GaN界面にAlGaN層20及びGaN層16の自発分極及びピエゾ分極によって、正の電荷が発生することにより、GaN層16の表面には、2DEGが生成される。本実施の形態では、2DEGが生成されたGaN層16の表面領域を2DEG層18という。このとき、正の電荷の量は、GaN層16及びAlGaN層20の膜厚とAl組成の調整によって、制御される。なお、本実施の形態では、GaN層16の厚さは2nm以上、500nm以下が好ましい。また、AlGaN層20の厚さは1nm以上、50nm以下であり、Al組成比が0.01以上、0.99以下であることが好ましい。

【0034】

電子走行層/電子供給層の組み合わせとしては、GaN/AlGaNの組み合わせに限定されず、電子供給層が電子走行層よりもバンドギャップエネルギーの大きい材料の組み合わせであればよく、例えばGaN/AlInGaN、InGaN/GaN、GaNAs/GaN、GaInNAsP/GaN、GaInNP/GaN、GaNP/GaN、GaN/AlGaInNAsP、または、AlInGaN/AlGaNの組み合わせであってもよい。これらの組み合わせの場合であっても、2DEGの濃度を最適範囲内とするため、電子供給層及び電子走行層の膜厚及び組成比を適宜調整すればよい。

【0035】

本実施の形態では、図1に示すようにソース電極24と平行する領域に、AlGaN層20を貫通してGaN層16に達する深さまでリセス部21が形成されており、図2のようにゲート絶縁膜23がリセス部21の内部を覆うように形成されていると共に、表面保護膜22がAlGaN層20の表面(ゲート電極28とソース電極24との間の表面、及びゲート電極28とドレイン電極26との間の表面)を覆うように形成されている。表面保護膜22及びゲート絶縁膜23は、SiO2やAl2O3、SiN、SiON、または、これらの複合膜を用いることができる。

【0036】

ソース電極24及びドレイン電極26は、オーミック電極(図1、ソース用オーミック電極部25等参照)であり、AlGaN層20上に直接形成されている。ゲート電極28は、リセス部21に形成されており、本実施の形態では、ゲート電極28の下部(MOFET部の下部)がGaN層16になっている。

【0037】

ショットキー電極30は、ソース電極24とドレイン電極26とが対向する領域に、ソース電極24とドレイン電極26とが対向する方向と略直交する方向(図1では、縦方向)にゲート電極28と並んで形成されている。また、AlGaN層20上の位置に、AlGaN層20とショットキー接合されて形成されており、ソース電極24に電気的に接続されている。

【0038】

図4のC−C断面図に示した層間絶縁膜38は、ゲート電極28の上面に形成されており、ゲート電極28と上面に形成された他の層(例えば、ソース電極24)とを絶縁する機能を有している。なお、層間絶縁膜38は、図面の簡略化のため、図2等のA−A断面図では、記載を省略している。

【0039】

なお、図1〜4に示した窒化物系半導体素子10の表面(ゲート電極28等の電極が形成されている側の面、図2〜4では上側にあたる面)には、外部からのごみや影響等を最低限に抑えるための表面保護膜22が設けられている。また、基板12の裏面には、裏面電極(図示省略)が形成されている。裏面電極は、通常はソース電極24と短絡する場合が多いが、ドレイン電極26と短絡したり、あるいはどちらとも接続しない(短絡しない)ようにしたり等、用途やパッケージ構造に合わせて接続を変更してもよい。

【0040】

図1〜4に示した窒化物系半導体素子10の等価回路図を図5に示す。ゲート電極28にオフ信号が入ると、本実施の形態の窒化物系半導体素子10はノーマリオフのデバイスであるため、MOSFET部32はオフ状態となる。MOSFET部32のドレイン側の電圧がドレイン電極26の電圧値と近くなることから、ドレイン電極26の電圧が上昇すると、ショットキー電極30の電圧値が、MOSFET部32のドレイン側の電圧値よりも低くなるため、ショットキー電極30によってMOSFET部32のドレイン側とドレイン電極26とが電気的に切断される。MOSFET部32のドレイン側にはショットキー電極30が2DEG層18をオフ状態にするための概略数V程度の電圧がかかるだけで、MOSFET部32がオフ状態でもゲート電極28の端部のゲート絶縁膜23には大きな電界が印加されず、一方、ショットキー電極30とドレインとの間には大きな電圧が印加される。

【0041】

一方、ゲート電極28にオン信号が入ると、MOSFET部32は導通状態となって、MOSFET部32のドレイン側の電圧値がソース電極24の電圧値と近くなり、ショットキー電極30がオフ状態からオン状態へと移行して、デバイス全体で導通状態となる。

【0042】

一般に、2DEGのシートキャリア濃度は、2×1012cm−2以上で用いられる。しかしながら図13に示したような従来の窒化物系半導体素子100では、2DEGのシートキャリア濃度を2×1012cm−2以上に大きくすると耐圧が極端に低下するが、本実施の形態の窒化物系半導体素子10は、上述した構造をとることにより、2DEGのシートキャリア濃度を、一般に好ましいとされている濃度である5×1012cm−2以上に大きくしても、耐圧を維持することができるようになった。すなわち、低いオン抵抗と高い耐圧とを同時に実現することが可能となった。

【0043】

さらに、オフ状態のときに、MOSFET部32のドレイン側に大きな電圧が印加されないため、ゲート絶縁膜23を保護することが可能となった。また、スイッチング動作時において、ドレイン電極26に電圧が印加されて電位の変動が生じるとき、MOSFET部32のドレイン側の電圧値の上昇が10V前後となり、従来のドレイン電極26に印加されていた電圧値と同等の電圧値(例えば300〜500V程度)が印加されていた状態に比べて、MOSFET部32のドレイン側の電圧値が小さくなったため、ゲート・ドレイン間容量に起因した帰還容量が著しく低減でき、より高速なスイッチング動作が可能となる副次的な効果が得られる。

【0044】

さらにまた、上述のように、図13に示したような従来の窒化物系半導体素子100では、内蔵ダイオード(FWD)が存在しないため、インバータ等に使用する場合では、外部にFWDを接続する必要がある場合があった。本実施の形態の窒化物系半導体素子10では、ショットキー電極30とMOSFET部32のドレイン側端部との間でショットキーダイオードを構成しているため、FWDを内蔵していることになり、新たに外部にFWを接続する必要がないため、全体の大きさを従来に比べて著しく縮小することが可能となった。

【0045】

なお、本実施の形態の窒化物系半導体素子10では、ゲート電極28と、ドレイン電極26と、の間の距離Kよりも、ショットキー電極30と、ドレイン電極26との間の距離Nの方が短いほうが、ショットキー電極30からドレイン電極26へ正孔を輸送(排出)する効率が上がるため、好ましい。一方、ショットキー電極30がドレイン電極26に近く、距離Nが短くなりすぎる場合、本発明のチップサイズの増加を抑制するという本発明の効果(詳細後述)が得られないため、距離Nは、正孔の輸送効率と、チップサイズの増加の抑制の観点から、窒化物系半導体素子10に所望の特性に応じて定められる。

【0046】

また、ショットキー電極30の領域の幅L(図1参照)は、当該幅Lに応じてMOSFET部32領域が少なくなるため、なるべく、短くすることが好ましい。具体的には、ショットキー電極30の厚さと同程度、より具体的には、3〜6μmが好ましい。

【0047】

また、MOSFET部32の領域の幅J(図1参照)は、長くなると、MOSFET部32の中央部(幅Jの中央部)における電位がドレイン電極30の電圧に近付くため正孔の輸送効率が低下するため好ましくない。ゲート絶縁膜23を保護するという目的のためには、幅J/2≦距離Kの範囲にすることが好ましい。

【0048】

またさらに、ショットキー電極30と、MOSFET部32との間(隙間)の距離Mは、長くなると、MOSFET部32のゲート電極28の端部に集まる正孔を排出することができなくなるため、あまり離れていないことが好ましく、具体的には、0から幅L程度の範囲内であることが好ましい。

【0049】

なお、ソース電極24が形成される領域は上述の形態(図1参照)に限らず、図6に示したように、ショットキー電極30の上部ならびに、MOSFET部32(ゲート電極28)の上部にわたって形成されていてもよい。

【0050】

なお、上述した本実施の形態の窒化物系半導体素子10は、例えば、以下のようにして製造することができる。なお、以下に示す製造方法は一例であり、これに限定されるものではない。

【0051】

MOCVD法や、分子線エピタキシャル成長(Molecular Beam Epitaxial、MBE)法等のエピタキシャル結晶成長法により、基板12上にバッファ層14及びGaN層16を順次積層させる。さらに、GaN層16の上にAlGaN層20を同様にエピタキシャル成長法により形成する(図7参照)。なお、2DEGのキャリア濃度を制御するため、AlGaN層20では、Alの組成や層厚が調整される。

【0052】

次に、AlGaN層20の表面にフォトレジストを塗布して、フォトリソグラフィ工程により、パターニングを行って予め定められたパターンを形成する。フォトレジストをマスクとして、リセス部21が形成される領域の、AlGaN層20及びGaN層16(一部)をエッチングにより除去する。さらに、化学気相成長(Chemical Vapor Deposirion、CVD)法等によりSiO2膜等のゲート絶縁膜23をリセス部21及び電極が形成される側の素子の表面に形成する。その後、フォトリソグラフィ工程を用いてパターニングを行い、ソース電極24、ドレイン電極26、及びショットキー電極30が形成される領域等のゲート絶縁膜23をエッチング除去する(図2、A−A断面図に対応する図8参照)。

【0053】

さらに、スパッタ法や真空蒸着法等によりドレイン電極26、及びゲート電極28を形成する。また、ショットキー電極30を形成する。さらに、ソース電極24とショットキー電極30とを電気的に接続するようにソース電極24を形成することにより、図1〜4に示した本実施の形態の窒化物系半導体素子10が製造される。

【0054】

以上説明したように、本発明者の多くの実験と破壊メカニズムの解析の結果得られた本実施の形態の窒化物系半導体素子10では、ドレイン電極26とゲート電極28との間に設けられたショットキー電極30がAlGaN層20とショットキー接合されている。また、ショットキー電極30とソース電極24とが接続されており、電気的に短絡している。これにより、ゲート電極28にオフ信号が入ると、MOSFET部32がオフ状態となり、MOSFET部32のドレイン側の電圧がドレイン電極26の電圧値と近くなる。ドレイン電極26の電圧が上昇すると、ショットキー電極30の電圧値が、MOSFET部32のドレイン側の電圧値よりも低くなるため、ショットキー電極30によってMOSFET部32のドレイン側とドレイン電極26とが電気的に切断される。

【0055】

このように本実施の形態では、ゲート電極28にオフ信号が入ると、ショットキー電極30によりMOSFET部32のドレイン側とドレイン電極26とが電気的に切断され、MOSFET部32のドレイン側端部に集まる正孔をソース電極24へ排出するため、ドレイン電極26に大きな電圧が印加された場合であっても、ゲート電極28の端部のゲート絶縁膜23には大きな電界が印加されない。

【0056】

また本実施の形態では、ショットキー電極30は、ソース電極24とドレイン電極26とが対向する領域に、ソース電極24とドレイン電極26とが対向する方向と略直交する方向(図1では、縦方向)にゲート電極28と並んだ領域に形成されている。

【0057】

このように本実施の形態では、ソース電極24とドレイン電極26とがゲート電極28を介さずに対向する領域にショットキー電極30が形成されているため、例えば、ゲート電極28とドレイン電極26との間の領域にショットキー電極30を設けた場合に比べ、ソース電極24とドレイン電極26とが対向する領域の面積を小さくすることができる。

【0058】

従って、ゲート絶縁膜23の破壊を防止すると共に、信頼性を向上させることができ、かつ、信頼性を向上させ、かつ、チップサイズの増加を抑制した、高耐圧、高速、低抵抗の窒化物系半導体素子10が得られる。

【0059】

なお、本実施の形態の窒化物系半導体素子10では、電子供給層としてAlGaN層20を用いているがこれに限らず、電子走行層となるGaN層16よりもバンドギャップエネルギーが大きい窒化物系化合物半導体であれば、他の組成であっても用いることができる。また、本実施の形態の窒化物系半導体素子10では、基板12上に1つの窒化物系半導体素子10が形成されている構成について説明したがこれに限らず、1つの基板12上に、お互いに電気的に絶縁された複数の窒化物系半導体素子10を配置して、お互いに配線することによってインバータ等を構成してもよい。

【0060】

[第2の実施の形態]

【0061】

第2の実施の形態の窒化物系半導体素子は、第1の実施の形態の窒化物系半導体素子10と略同様の構成及び動作であるため、同一部分には同一符号を付して詳細な説明を省略し、異なる部分のみ詳細に説明する。

【0062】

本実施の形態の窒化物系半導体装置である窒化物系半導体素子の概略構成の一例を示す断面図を図9(図2、A−A断面図に対応)に示す。本実施の形態の窒化物系半導体素子50では、リセス部51がGaN層16に達していない、すなわちMOSFET部32の下部がAlGaN層20であるように形成されている。MOSFET部32の閾値をある程度低くしても良い場合には、このように構成することが好ましい。なお、本実施の形態では、リセス部51が形成されているAlGaN層20が十分に薄いため、GaN層16の表面に生成された2DEGは濃度が十分に低く、ノーマリオフ型の窒化物系半導体装置として動作する。

【0063】

第1の実施の形態の窒化物系半導体素子10のようにGaN層16上にゲート絶縁膜53を形成する場合では、リセス部51を形成する際のエッチングプロセスによるダメージ等により、GaN層16表面に形成される電子の反転層の移動度が低下する。GaN層16とAlGaN層20との界面よりも上部にゲート絶縁膜53を形成することにより、移動度の低下を防止することができる。この場合には、MOSチャネルはGaN層16/AlGaN層20界面に形成されるため、MOSFET部32の抵抗の上昇が抑えられるという利点が生じる。

【0064】

このように本実施の形態の窒化物系半導体素子50では、リセス部51がAlGaN層20内に形成されているため、GaN層16表面に形成される電子の反転層の移動度の低下を防止すると共に、MOSFET部32の抵抗の上昇を抑えることができるという効果がさらに得られる。従って、安価で高性能なデバイスを提供することができる。

【0065】

[第3の実施の形態]

【0066】

第3の実施の形態の窒化物系半導体素子は、第1の実施の形態の窒化物系半導体素子10及び第2の実施の形態の窒化物系半導体素子50と略同様の構成及び動作であるため、同一部分には同一符号を付して詳細な説明を省略し、異なる部分のみ詳細に説明する。

【0067】

本実施の形態の窒化物系半導体装置である窒化物系半導体素子の概略構成の一例を示す断面図を図10(図3、B−B断面図に対応)に示す。本実施の形態の窒化物系半導体素子60では、第1の実施の形態の窒化物系半導体素子10では、AlGaN層20とショットキー接合された電極としてショットキー電極30が設けられているがこれにかわり、AlGaN層20とpn接合されたp−AlGaN層64(半導体層)と、p−AlGaN層64の上にオーミック接合されたオーミック電極62が設けられている。

【0068】

本実施の形態の窒化物系半導体素子60のp−AlGaN層64においても、第1の実施の形態の窒化物系半導体素子10のショットキー電極30と同様に、MOSFET部32のドレイン側端部に集まる正孔をソース電極24に排出する機能を有しているため、同様の効果が得られる。

【0069】

なお、第1の実施の形態に示したショットキー電極30と本実施の形態のp−AlGaN層64とを混載するように構成してもよい。

【0070】

[第4の実施の形態]

【0071】

第4の実施の形態の窒化物系半導体素子は、第1の実施の形態の窒化物系半導体素子10、第2の実施の形態の窒化物系半導体素子50、及び第3の実施の形態の窒化物系半導体素子60と略同様の構成及び動作であるため、同一部分には同一符号を付して詳細な説明を省略し、異なる部分のみ詳細に説明する。

【0072】

本実施の形態の窒化物系半導体装置である窒化物系半導体素子の概略構成の一例を示す断面図を図11(図3、B−B断面図に対応)に示す。本実施の形態の窒化物系半導体素子70では、第1の実施の形態の窒化物系半導体素子10ではAlGaN層20上に設けられていたショットキー電極30にかわり、AlGaN層20及びGaN層16に埋込まれたショットキー電極72が設けられている。

【0073】

本実施の形態では、AlGaN層20の表面から、AlGaN層20を貫通し、GaN層16に到るまでリセス部74が形成されており、当該リセス部74にショットキー電極72が設けられている。

【0074】

このようにリセス部74内にショットキー電極72が設けられていることにより、MOSFET部32界面に蓄積する正孔をより効率的にソース電極24に排出することができる。

【0075】

なお、リセス部74の深さは、少なくともAlGaN層20内部まででもよいが、好ましくは図11に示したようにGaN層16に到達している方がよく、特に2DEGの発生部分(2DEG層18)にショットキー電極72が接触していることが好ましい。

【0076】

[第5の実施の形態]

【0077】

第5の実施の形態の窒化物系半導体素子は、第1の実施の形態の窒化物系半導体素子10、第2の実施の形態の窒化物系半導体素子50、第3の実施の形態の窒化物系半導体素子60、及び第4の実施の形態の窒化物系半導体素子70と略同様の構成及び動作であるため、同一部分には同一符号を付して詳細な説明を省略し、異なる部分のみ詳細に説明する。

【0078】

本実施の形態の窒化物系半導体装置である窒化物系半導体素子の概略構成の一例を示す断面図を図12(図2、A−A断面図に対応)に示す。本実施の形態の窒化物系半導体素子80では、表面保護膜22及びゲート絶縁膜23の下部領域に第1のn+領域となるソース電極24側のn+AlGan層83−1及びn+GaN層82−1と、ドレイン電極26側のn+AlGaN層83−2及びn+GaN層82−2が設けられていると共に、ドレイン電極26の下部に第2のn+領域となるn+AlGaN層84及びn+GaN層86が設けられている。

【0079】

ソース電極24とゲート電極28との間の表面保護膜22及びゲート絶縁膜23の下部領域のn+領域であるn+AlGaN層83−1は、ソース電極24と接合されている。

【0080】

本実施の形態のn+領域(n+GaN層82−1、82−2及びn+AlGaN層83−1、83−2)は、AlGaN層20を形成後、該当個所にSiを1015cm−2程度でイオン注入し、その後1000℃前後で熱処理することにより、AlGaN層20がn+AlGaN層83−1、83−2に、GaN層16がn+GaN層82−1、82−2に変化することで形成される。

【0081】

このようにゲート絶縁膜23下部領域にn+領域が設けられていることにより、ゲート絶縁膜23の側壁部分(リセス部21の側壁部分)がチャネル領域となっているために、当該側壁部分を伝わって流れる抵抗成分を除去することができ、窒化物系半導体素子80全体の抵抗を小さくすることができる。

【0082】

また、本実施の形態の窒化物系半導体素子80では、ドレイン電極26の下部領域のAlGaN層20がn+AlGaN層84に、GaN層16がn+GaN層86に変化している。これにより、ドレイン電極26のオーミック抵抗を小さくすることができると共に、リーク電流を減少させることができる。

【符号の説明】

【0083】

10、50、60、70、80 窒化物系半導体素子

12 基板

14 バッファ層

16 GaN層

18 2DEG層

20 AlGaN層

21、51 リセス部

22、52 表面保護膜

23、53 ゲート絶縁膜

24 ソース電極

26 ドレイン電極

28 ゲート電極

30、72 ショットキー電極

32 MOSFET部

64 p−AlGaN層

【技術分野】

【0001】

本発明は、MOS構造を有するノーマリオフの窒化物系の半導体装置に関するものである。

【背景技術】

【0002】

従来から高周波デバイス用半導体素子には、半導体材料として窒化ガリウム(GaN)系化合物半導体装置(以下、GaN系半導体素子という)が用いられている。GaN系半導体素子では、基板の表面に、例えば有機金属化学気相成長(MOCVD:Metal−Organic Chemical Vapor Deposition)法を用いて形成されたバッファ層や、不純物がドープされた電子走行層が設けられている。最近では、高周波用途に加え、電力用半導体素子(パワーデバイス)にも適用可能であるという認識から、高耐圧、大電流を扱うGaN系半導体素子の開発が行われている。

【0003】

特許文献1には、MOS構造を有する窒化ガリウム系半導体素子が記載されている。特許文献1に記載されたMOS構造を有する窒化ガリウム系半導体素子の概略構成図を図13に示す。図13に示すように、従来の窒化ガリウム系半導体素子100は、基板112上に、GaN結晶を積層するためのバッファ層114を介して電子走行層として機能するGaN層116及び電子供給層として機能するAlGaN層120が積層され、ヘテロ接合構造が形成されている。図13の窒化ガリウム系半導体素子100では、GaN層116とAlGaN層120との界面直下(GaN層116の表面)に形成された2次元電子ガス118(2DEG:Two Dimensional Electron Gas)がキャリアとして利用される。

【0004】

AlGaN層120の表面の一部にはリセス部121が形成される。当該リセス部121にゲート絶縁膜123を介して、ゲート電極128が配置されて、MOS(n型MOS)構造(MOSFET部)を構成する。また、AlGaN層120の表面には表面保護膜122が形成されている。

【0005】

ゲート電極128に正の電圧を印加すると、ゲート絶縁膜123と接したGaN層116の表面に電子が集まり、MOSチャネルを形成し(オン状態になり)、GaN層116とAlGaN層120との界面に形成された2DEG層118と電気的に接続されて、ソース電極124とドレイン電極126との間が電気的に導通された状態になる。

【0006】

また、MOSチャネルがオフ状態の場合には、ソース電極124とドレイン電極126との間に電圧が印加されるとゲート端部から2DEG層118が空乏化して高耐圧を維持することが可能となり、大電力かつ、高耐圧の半導体素子として機能する。そのため、近年、高周波で高効率の電力用半導体素子として窒化物系半導体素子の開発が進んでいる。従来、ゲート部がショットキー接合となっているいわゆるHEMT(High Electron Mobility Transistor)と呼ばれるデバイスが主に開発されてきた。このようなデバイスは、絶縁ゲートのほうが駆動回路が容易であること、及びMOSFET部に印加されるゲート電圧が0Vの場合(ゲート電圧を印加しない場合)に、電気的にオフ状態になる、いわゆるノーマリオフデバイスに用いることが容易であることから、注目されている。

【0007】

電力用半導体素子として使用するためには、高速で動作し、導通抵抗が低いということは大きな利点である。一方、2DEG層118を空乏化させようとすると、ゲート部のドレイン側端部129に大きな電界が集中し、ゲート絶縁膜123が破壊されてしまうという不具合が頻発する場合があることがわかった。この原因は、高電界で発生した正孔がゲート絶縁膜123及びゲート絶縁膜123に近いAlGaN層120/GaN層116近傍に集まって、ドレイン電極126に印加された電圧の殆どがゲート絶縁膜123に印加されてしまうことためであることがわかった。

【0008】

さらに、破壊されない場合であっても、長時間にわたってドレイン電極126に大きな電圧を印加し続けた場合、ゲート絶縁膜123に高電界が長時間印加されることになり、その特性が経時的に劣化してしまうという、信頼性上の問題が発生する場合がある。

【0009】

これを防止するためには、2DEGの電子濃度を2×1012cm−2程度以下の濃度にすることが考えられる。これにより2DEGが空乏化されやすくなり、耐圧が維持される効果が得られる。しかし、2DEGの濃度を下げてしまうと、2DEG層118部分の導通抵抗が大きくなってしまうため、素子全体としてのオン抵抗が上昇してしまい、本来の窒化物系半導体を用いた素子としての利点が失われてしまうという難点がある。

【0010】

また、その他の手段として、ゲート電極128のドレイン側端部に、ゲート電極128端部に集中する電解を緩和するためにフィールドプレートとよばれる、ゲート絶縁膜123よりも厚い表面保護膜122の上にゲート電極128を延長させて、薄いゲート絶縁膜123部分の電界を和らげる手段が挙げられる。しかしながら、当該手段においても、2DEGの電子濃度が3×1012cm−2以上の場合では、ゲート絶縁膜123を保護することが困難である。

【0011】

またさらに、別の手段として、GaN層116をp型とすることにより、ゲート絶縁膜123周辺に集まる正孔をp型領域へと排出し、2DEG層118を空乏化させやすくするという手段が挙げられる。当該手段は、例えば、非特許文献1に示されているように、そのアクセプタ濃度を制御することにより空乏層が拡がりやすくなり、高耐圧を達成できるという利点がある。しかしながら、一般に、窒化ガリウムのp型層を形成することは困難であり、さらに濃度制御を1×1017cm−3程度で行うことが非常に難しい。特に基板112がシリコンより成る場合には、p型層そのものを得ることが困難である。すなわち、非常に制限された濃度範囲、基板材料の選択が必要となる。

【0012】

また、図13の構造においては、ソース側とドレイン側がゲート電極128を挟んで基本的に対照的な構造を有しているため、いわゆるフリーホイリングダイオード(以下、FWDという)が無い。このため、例えば、インバータ等に使用する場合には、窒化物系半導体素子外部にFWDの機能をになうダイオードを並列に接続することが必要とされる。

【0013】

一方、特許文献2には、ノーマリオンデバイスである、いわゆる高耐圧JFET(Junction−Field−Effect−Transistor)と低耐圧MOSFETとを直列にカスケード接続した高耐圧パワーデバイスが記載されている。図14に、当該JFETとMOSFETとの接続状況を示す。これは、JFETのゲート端子を直列に接続されたMOSFETのソースと短絡し、外から見ると、あたかも絶縁ゲートデバイスのように動作させようとするものである。MOSFETは、低耐圧でオン抵抗の低いデバイスを使用することができるため、JFETはノーマリオンであるが、高耐圧で抵抗の低いSiC MOSFETは低耐圧シリコンのMOSFETを接続し、ノーマリオフでオン抵抗が低く高耐圧のデバイスを実現させている。

【0014】

一方、例えば、図15に示すような、特許文献3に示される窒化物系半導体素子が知られている。図15に示した半導体素子200は、背面電極235、基板212、バッファ層214、電子走行層216、2DEG層218、電子供給層220、絶縁膜233、ソース電極224、ドレイン電極226、ゲート電極28、及びショットキー電極231を備えて構成されている。半導体素子200では、電子供給層220上に直接、ソース電極224、ドレイン電極226、ゲート電極28、及びショットキー電極231が形成されており、ドレイン電極226とゲート電極28との間に設けられたショットキー電極231がソース電極224と短絡されていることにより、高速動作を実現させている。この窒化物系半導体素子は、ゲート電極28部分にリセスが形成されておらず、特許文献1のように、図13でのドレイン側端部129に大きな電界が集中し、ゲート絶縁膜123が破壊されてしまうという不具合は生じない。しかし、特許文献3に示される窒化物系半導体素子は、ノーマリオン型であるため、故障時の安全性を確保できない。

【先行技術文献】

【特許文献】

【0015】

【特許文献1】国際公開第2003/071607号パンフレット

【特許文献2】US−6900537号公報

【特許文献3】特開2007−273795号公報

【非特許文献】

【0016】

【非特許文献1】Proceedings of International Symposium on Power Semiconductor Device and IC's “Enhancement-mode GaN Hybrid MOS-HEMTs with Ron,sp of 20mΩ-cm2”(2008) pp.295-298

【発明の概要】

【発明が解決しようとする課題】

【0017】

本発明は、上記に鑑みてなされたものであって、MOS型デバイスのゲート絶縁膜の破壊を防止すると共に、信頼性を向上させ、かつ、チップサイズの増加を抑制した、窒化物系半導体装置を提供することを目的とする。

【課題を解決するための手段】

【0018】

請求項1に記載の窒化物系半導体装置は、基板と、前記基板上に形成されたバッファ層と、前記バッファ層上に形成された窒化物系化合物半導体より成る電子走行層と、前記電子走行層上に形成され、前記電子走行層とはバンドギャップエネルギーが異なる電子供給層と、前記電子供給層上に、対向して配置されたソース電極及びドレイン電極と、前記ソース電極と前記ドレイン電極との間でかつ、前記ソース電極と前記ドレイン電極とが対向する方向と直交する方向の一部の領域に、前記電子供給層の表面から少なくとも前記電子走行層の表面に到るまでの領域に形成されたリセス部と、前記ソース電極と前記ドレイン電極との間でかつ、前記ソース電極と前記ドレイン電極とが対向する方向と直交する方向の他の領域に形成された、前記ソース電極に接続されてキャリアを輸送するキャリア輸送用電極と、前記リセス部内部を覆うように形成されたゲート絶縁膜と、前記リセス部内の前記ゲート絶縁膜上に形成されたゲート電極と、を備える。

【0019】

請求項2に記載の窒化物系半導体装置は、請求項1に記載の窒化物系半導体装置において、前記電子走行層に発生する2次元電子ガスのシートキャリア濃度は2×1012cm−2以上である。

【0020】

請求項3に記載の窒化物系半導体装置は、請求項1または請求項2に記載の半導体装置において、前記キャリア輸送用電極と前記ドレイン電極との距離が、前記ゲート電極と前記ドレイン電極との距離よりも短い。

【0021】

請求項4に記載の窒化物系半導体装置は、請求項1から請求項3のいずれか1項に記載の窒化物系半導体装置において、前記キャリア輸送用電極が、前記電子供給層及び前記電子走行層の少なくとも一方とショットキー接合されている。

【0022】

請求項5に記載の窒化物系半導体装置は、請求項4に記載の窒化物系半導体装置において、前記電子供給層の表面から前記電子供給層内部または前記電子走行層内部に到る深さまでの領域に前記キャリア輸送用電極が形成されている。

【0023】

請求項6に記載の窒化物系半導体装置は、請求項1から請求項3のいずれか1項に記載の窒化物系半導体装置において、前記電子供給層上にp型半導体層を備え、前記p型半導体層上に前記キャリア輸送用電極がオーミック接合されている。

【0024】

請求項7に記載の窒化物系半導体装置は、請求項1から請求項6のいずれか1項に記載の窒化物系半導体装置において、前記ソース電極から前記リセス部の下部領域に到るまでの前記ゲート絶縁膜の下部領域に形成され、前記ソース電極に接続された第1のn+半導体層と、前記リセス部の下部領域から前記キャリア輸送用電極の手前に到るまでの前記ゲート絶縁膜の下部領域に形成され、前記キャリア輸送用電極に接続されていない第2のn+層のうち少なくともいずれかを備える。

【0025】

請求項8に記載の窒化物系半導体装置は、請求項1から請求項7のいずれか1項に記載の窒化物系半導体装置において、前記ドレイン電極の下部領域の電子供給層及び電子走行層にn+半導体層を備える。

【発明の効果】

【0026】

MOS型デバイスのゲート絶縁膜の破壊を防止すると共に、信頼性を向上させ、かつ、チップサイズの増加を抑制した、窒化物系半導体装置を提供することができる、という効果を奏する。

【図面の簡単な説明】

【0027】

【図1】本発明の第1の実施の形態に係る窒化物系半導体素子の概略構成の一例を示す平面図である。

【図2】図1に示した窒化物系半導体素子のA−A断面の概略構成の一例を示す断面図である。

【図3】図1に示した窒化物系半導体素子のB−B断面の概略構成の一例を示す断面図である。

【図4】図1に示した窒化物系半導体素子のC−C断面の概略構成の一例を示す断面図である。

【図5】図1に示した窒化物系半導体素子の等価回路を示した回路図である。

【図6】図1に示した窒化物系半導体素子のその他の一例を示す平面図である。

【図7】図1に示した窒化物系半導体素子の製造方法の一例の一工程を説明するための説明図である。

【図8】図1に示した窒化物系半導体素子の製造方法の一例の一工程を説明するための説明図である。

【図9】本発明の第2の実施の形態に係る窒化物系半導体素子の概略構成の一例を示す断面図である。

【図10】本発明の第3の実施の形態に係る窒化物系半導体素子の概略構成の一例を示す断面図である。

【図11】本発明の第4の実施の形態に係る窒化物系半導体素子の概略構成の一例を示す断面図である。

【図12】本発明の第5の実施の形態に係る窒化物系半導体素子の概略構成の一例を示す断面図である。

【図13】従来の窒化物系半導体素子の概略構成の一例を示す断面図である。

【図14】従来の窒化物系半導体素子の等価回路を示した回路図である。

【図15】従来の窒化物系半導体素子の概略構成の一例を示す断面図である。

【発明を実施するための形態】

【0028】

[第1の実施の形態]

【0029】

以下、図面を参照して本実施の形態の窒化物系半導体装置について詳細に説明する。なお、本実施の形態は本発明の半導体装置の一例であり、本実施の形態により本発明が限定されるものではない。

【0030】

本実施の形態の窒化物系半導体装置である窒化物系半導体素子の概略構成の一例を示す平面図を図1に示す。また、図1に示した窒化物系半導体素子のA−A断面の概略構成の一例を図2に、B−B断面の概略構成の一例を図3に、C−C断面の概略構成の一例を図4にそれぞれ示す。

【0031】

本実施の形態の窒化物系半導体素子10は、基板12、バッファ層14、GaN層16、AlGaN層20、表面保護膜22、ゲート絶縁膜23、ソース電極24、ドレイン電極26、ゲート電極28、ショットキー電極30、及び層間絶縁膜38を備えて構成されている。また、本実施の形態の窒化物系半導体素子10は、等価回路としての見方をするとMOSFET部32とHEMT部34により構成されている。

【0032】

基板12の具体的一例としては、シリコン、サファイア、SiC、ZrB2、Si、GaN、MgO等、窒化物系化合物半導体を結晶成長させることが可能な材料からなる基板が挙げられる。バッファ層14は、GaN結晶を積層するための機能を有する層であり、GaN、AlN、AlGaN等を用いることができ、バッファ層14上に形成される電子走行層(本実施の形態ではGaN層16)を形成するGaN結晶と格子整合するように形成される。

【0033】

GaN層16は、電子走行層として機能するものであり、アンドープのGaN等からなる。また、GaN層16はN型でもP型でもよい。AlGaN層20は、電子供給層として機能するものであり、GaN層16とバンドギャップエネルギーが異なるAlGaN等からなる。また、AlGaN層20は、Al濃度の異なる複数の層構成を有していてもよい。GaN層16とAlGaN層20との界面にバンドオフセットが形成されると共に、AlGaN/GaN界面にAlGaN層20及びGaN層16の自発分極及びピエゾ分極によって、正の電荷が発生することにより、GaN層16の表面には、2DEGが生成される。本実施の形態では、2DEGが生成されたGaN層16の表面領域を2DEG層18という。このとき、正の電荷の量は、GaN層16及びAlGaN層20の膜厚とAl組成の調整によって、制御される。なお、本実施の形態では、GaN層16の厚さは2nm以上、500nm以下が好ましい。また、AlGaN層20の厚さは1nm以上、50nm以下であり、Al組成比が0.01以上、0.99以下であることが好ましい。

【0034】

電子走行層/電子供給層の組み合わせとしては、GaN/AlGaNの組み合わせに限定されず、電子供給層が電子走行層よりもバンドギャップエネルギーの大きい材料の組み合わせであればよく、例えばGaN/AlInGaN、InGaN/GaN、GaNAs/GaN、GaInNAsP/GaN、GaInNP/GaN、GaNP/GaN、GaN/AlGaInNAsP、または、AlInGaN/AlGaNの組み合わせであってもよい。これらの組み合わせの場合であっても、2DEGの濃度を最適範囲内とするため、電子供給層及び電子走行層の膜厚及び組成比を適宜調整すればよい。

【0035】

本実施の形態では、図1に示すようにソース電極24と平行する領域に、AlGaN層20を貫通してGaN層16に達する深さまでリセス部21が形成されており、図2のようにゲート絶縁膜23がリセス部21の内部を覆うように形成されていると共に、表面保護膜22がAlGaN層20の表面(ゲート電極28とソース電極24との間の表面、及びゲート電極28とドレイン電極26との間の表面)を覆うように形成されている。表面保護膜22及びゲート絶縁膜23は、SiO2やAl2O3、SiN、SiON、または、これらの複合膜を用いることができる。

【0036】

ソース電極24及びドレイン電極26は、オーミック電極(図1、ソース用オーミック電極部25等参照)であり、AlGaN層20上に直接形成されている。ゲート電極28は、リセス部21に形成されており、本実施の形態では、ゲート電極28の下部(MOFET部の下部)がGaN層16になっている。

【0037】

ショットキー電極30は、ソース電極24とドレイン電極26とが対向する領域に、ソース電極24とドレイン電極26とが対向する方向と略直交する方向(図1では、縦方向)にゲート電極28と並んで形成されている。また、AlGaN層20上の位置に、AlGaN層20とショットキー接合されて形成されており、ソース電極24に電気的に接続されている。

【0038】

図4のC−C断面図に示した層間絶縁膜38は、ゲート電極28の上面に形成されており、ゲート電極28と上面に形成された他の層(例えば、ソース電極24)とを絶縁する機能を有している。なお、層間絶縁膜38は、図面の簡略化のため、図2等のA−A断面図では、記載を省略している。

【0039】

なお、図1〜4に示した窒化物系半導体素子10の表面(ゲート電極28等の電極が形成されている側の面、図2〜4では上側にあたる面)には、外部からのごみや影響等を最低限に抑えるための表面保護膜22が設けられている。また、基板12の裏面には、裏面電極(図示省略)が形成されている。裏面電極は、通常はソース電極24と短絡する場合が多いが、ドレイン電極26と短絡したり、あるいはどちらとも接続しない(短絡しない)ようにしたり等、用途やパッケージ構造に合わせて接続を変更してもよい。

【0040】

図1〜4に示した窒化物系半導体素子10の等価回路図を図5に示す。ゲート電極28にオフ信号が入ると、本実施の形態の窒化物系半導体素子10はノーマリオフのデバイスであるため、MOSFET部32はオフ状態となる。MOSFET部32のドレイン側の電圧がドレイン電極26の電圧値と近くなることから、ドレイン電極26の電圧が上昇すると、ショットキー電極30の電圧値が、MOSFET部32のドレイン側の電圧値よりも低くなるため、ショットキー電極30によってMOSFET部32のドレイン側とドレイン電極26とが電気的に切断される。MOSFET部32のドレイン側にはショットキー電極30が2DEG層18をオフ状態にするための概略数V程度の電圧がかかるだけで、MOSFET部32がオフ状態でもゲート電極28の端部のゲート絶縁膜23には大きな電界が印加されず、一方、ショットキー電極30とドレインとの間には大きな電圧が印加される。

【0041】

一方、ゲート電極28にオン信号が入ると、MOSFET部32は導通状態となって、MOSFET部32のドレイン側の電圧値がソース電極24の電圧値と近くなり、ショットキー電極30がオフ状態からオン状態へと移行して、デバイス全体で導通状態となる。

【0042】

一般に、2DEGのシートキャリア濃度は、2×1012cm−2以上で用いられる。しかしながら図13に示したような従来の窒化物系半導体素子100では、2DEGのシートキャリア濃度を2×1012cm−2以上に大きくすると耐圧が極端に低下するが、本実施の形態の窒化物系半導体素子10は、上述した構造をとることにより、2DEGのシートキャリア濃度を、一般に好ましいとされている濃度である5×1012cm−2以上に大きくしても、耐圧を維持することができるようになった。すなわち、低いオン抵抗と高い耐圧とを同時に実現することが可能となった。

【0043】

さらに、オフ状態のときに、MOSFET部32のドレイン側に大きな電圧が印加されないため、ゲート絶縁膜23を保護することが可能となった。また、スイッチング動作時において、ドレイン電極26に電圧が印加されて電位の変動が生じるとき、MOSFET部32のドレイン側の電圧値の上昇が10V前後となり、従来のドレイン電極26に印加されていた電圧値と同等の電圧値(例えば300〜500V程度)が印加されていた状態に比べて、MOSFET部32のドレイン側の電圧値が小さくなったため、ゲート・ドレイン間容量に起因した帰還容量が著しく低減でき、より高速なスイッチング動作が可能となる副次的な効果が得られる。

【0044】

さらにまた、上述のように、図13に示したような従来の窒化物系半導体素子100では、内蔵ダイオード(FWD)が存在しないため、インバータ等に使用する場合では、外部にFWDを接続する必要がある場合があった。本実施の形態の窒化物系半導体素子10では、ショットキー電極30とMOSFET部32のドレイン側端部との間でショットキーダイオードを構成しているため、FWDを内蔵していることになり、新たに外部にFWを接続する必要がないため、全体の大きさを従来に比べて著しく縮小することが可能となった。

【0045】

なお、本実施の形態の窒化物系半導体素子10では、ゲート電極28と、ドレイン電極26と、の間の距離Kよりも、ショットキー電極30と、ドレイン電極26との間の距離Nの方が短いほうが、ショットキー電極30からドレイン電極26へ正孔を輸送(排出)する効率が上がるため、好ましい。一方、ショットキー電極30がドレイン電極26に近く、距離Nが短くなりすぎる場合、本発明のチップサイズの増加を抑制するという本発明の効果(詳細後述)が得られないため、距離Nは、正孔の輸送効率と、チップサイズの増加の抑制の観点から、窒化物系半導体素子10に所望の特性に応じて定められる。

【0046】

また、ショットキー電極30の領域の幅L(図1参照)は、当該幅Lに応じてMOSFET部32領域が少なくなるため、なるべく、短くすることが好ましい。具体的には、ショットキー電極30の厚さと同程度、より具体的には、3〜6μmが好ましい。

【0047】

また、MOSFET部32の領域の幅J(図1参照)は、長くなると、MOSFET部32の中央部(幅Jの中央部)における電位がドレイン電極30の電圧に近付くため正孔の輸送効率が低下するため好ましくない。ゲート絶縁膜23を保護するという目的のためには、幅J/2≦距離Kの範囲にすることが好ましい。

【0048】

またさらに、ショットキー電極30と、MOSFET部32との間(隙間)の距離Mは、長くなると、MOSFET部32のゲート電極28の端部に集まる正孔を排出することができなくなるため、あまり離れていないことが好ましく、具体的には、0から幅L程度の範囲内であることが好ましい。

【0049】

なお、ソース電極24が形成される領域は上述の形態(図1参照)に限らず、図6に示したように、ショットキー電極30の上部ならびに、MOSFET部32(ゲート電極28)の上部にわたって形成されていてもよい。

【0050】

なお、上述した本実施の形態の窒化物系半導体素子10は、例えば、以下のようにして製造することができる。なお、以下に示す製造方法は一例であり、これに限定されるものではない。

【0051】

MOCVD法や、分子線エピタキシャル成長(Molecular Beam Epitaxial、MBE)法等のエピタキシャル結晶成長法により、基板12上にバッファ層14及びGaN層16を順次積層させる。さらに、GaN層16の上にAlGaN層20を同様にエピタキシャル成長法により形成する(図7参照)。なお、2DEGのキャリア濃度を制御するため、AlGaN層20では、Alの組成や層厚が調整される。

【0052】

次に、AlGaN層20の表面にフォトレジストを塗布して、フォトリソグラフィ工程により、パターニングを行って予め定められたパターンを形成する。フォトレジストをマスクとして、リセス部21が形成される領域の、AlGaN層20及びGaN層16(一部)をエッチングにより除去する。さらに、化学気相成長(Chemical Vapor Deposirion、CVD)法等によりSiO2膜等のゲート絶縁膜23をリセス部21及び電極が形成される側の素子の表面に形成する。その後、フォトリソグラフィ工程を用いてパターニングを行い、ソース電極24、ドレイン電極26、及びショットキー電極30が形成される領域等のゲート絶縁膜23をエッチング除去する(図2、A−A断面図に対応する図8参照)。

【0053】

さらに、スパッタ法や真空蒸着法等によりドレイン電極26、及びゲート電極28を形成する。また、ショットキー電極30を形成する。さらに、ソース電極24とショットキー電極30とを電気的に接続するようにソース電極24を形成することにより、図1〜4に示した本実施の形態の窒化物系半導体素子10が製造される。

【0054】

以上説明したように、本発明者の多くの実験と破壊メカニズムの解析の結果得られた本実施の形態の窒化物系半導体素子10では、ドレイン電極26とゲート電極28との間に設けられたショットキー電極30がAlGaN層20とショットキー接合されている。また、ショットキー電極30とソース電極24とが接続されており、電気的に短絡している。これにより、ゲート電極28にオフ信号が入ると、MOSFET部32がオフ状態となり、MOSFET部32のドレイン側の電圧がドレイン電極26の電圧値と近くなる。ドレイン電極26の電圧が上昇すると、ショットキー電極30の電圧値が、MOSFET部32のドレイン側の電圧値よりも低くなるため、ショットキー電極30によってMOSFET部32のドレイン側とドレイン電極26とが電気的に切断される。

【0055】

このように本実施の形態では、ゲート電極28にオフ信号が入ると、ショットキー電極30によりMOSFET部32のドレイン側とドレイン電極26とが電気的に切断され、MOSFET部32のドレイン側端部に集まる正孔をソース電極24へ排出するため、ドレイン電極26に大きな電圧が印加された場合であっても、ゲート電極28の端部のゲート絶縁膜23には大きな電界が印加されない。

【0056】

また本実施の形態では、ショットキー電極30は、ソース電極24とドレイン電極26とが対向する領域に、ソース電極24とドレイン電極26とが対向する方向と略直交する方向(図1では、縦方向)にゲート電極28と並んだ領域に形成されている。

【0057】

このように本実施の形態では、ソース電極24とドレイン電極26とがゲート電極28を介さずに対向する領域にショットキー電極30が形成されているため、例えば、ゲート電極28とドレイン電極26との間の領域にショットキー電極30を設けた場合に比べ、ソース電極24とドレイン電極26とが対向する領域の面積を小さくすることができる。

【0058】

従って、ゲート絶縁膜23の破壊を防止すると共に、信頼性を向上させることができ、かつ、信頼性を向上させ、かつ、チップサイズの増加を抑制した、高耐圧、高速、低抵抗の窒化物系半導体素子10が得られる。

【0059】

なお、本実施の形態の窒化物系半導体素子10では、電子供給層としてAlGaN層20を用いているがこれに限らず、電子走行層となるGaN層16よりもバンドギャップエネルギーが大きい窒化物系化合物半導体であれば、他の組成であっても用いることができる。また、本実施の形態の窒化物系半導体素子10では、基板12上に1つの窒化物系半導体素子10が形成されている構成について説明したがこれに限らず、1つの基板12上に、お互いに電気的に絶縁された複数の窒化物系半導体素子10を配置して、お互いに配線することによってインバータ等を構成してもよい。

【0060】

[第2の実施の形態]

【0061】

第2の実施の形態の窒化物系半導体素子は、第1の実施の形態の窒化物系半導体素子10と略同様の構成及び動作であるため、同一部分には同一符号を付して詳細な説明を省略し、異なる部分のみ詳細に説明する。

【0062】

本実施の形態の窒化物系半導体装置である窒化物系半導体素子の概略構成の一例を示す断面図を図9(図2、A−A断面図に対応)に示す。本実施の形態の窒化物系半導体素子50では、リセス部51がGaN層16に達していない、すなわちMOSFET部32の下部がAlGaN層20であるように形成されている。MOSFET部32の閾値をある程度低くしても良い場合には、このように構成することが好ましい。なお、本実施の形態では、リセス部51が形成されているAlGaN層20が十分に薄いため、GaN層16の表面に生成された2DEGは濃度が十分に低く、ノーマリオフ型の窒化物系半導体装置として動作する。

【0063】

第1の実施の形態の窒化物系半導体素子10のようにGaN層16上にゲート絶縁膜53を形成する場合では、リセス部51を形成する際のエッチングプロセスによるダメージ等により、GaN層16表面に形成される電子の反転層の移動度が低下する。GaN層16とAlGaN層20との界面よりも上部にゲート絶縁膜53を形成することにより、移動度の低下を防止することができる。この場合には、MOSチャネルはGaN層16/AlGaN層20界面に形成されるため、MOSFET部32の抵抗の上昇が抑えられるという利点が生じる。

【0064】

このように本実施の形態の窒化物系半導体素子50では、リセス部51がAlGaN層20内に形成されているため、GaN層16表面に形成される電子の反転層の移動度の低下を防止すると共に、MOSFET部32の抵抗の上昇を抑えることができるという効果がさらに得られる。従って、安価で高性能なデバイスを提供することができる。

【0065】

[第3の実施の形態]

【0066】

第3の実施の形態の窒化物系半導体素子は、第1の実施の形態の窒化物系半導体素子10及び第2の実施の形態の窒化物系半導体素子50と略同様の構成及び動作であるため、同一部分には同一符号を付して詳細な説明を省略し、異なる部分のみ詳細に説明する。

【0067】

本実施の形態の窒化物系半導体装置である窒化物系半導体素子の概略構成の一例を示す断面図を図10(図3、B−B断面図に対応)に示す。本実施の形態の窒化物系半導体素子60では、第1の実施の形態の窒化物系半導体素子10では、AlGaN層20とショットキー接合された電極としてショットキー電極30が設けられているがこれにかわり、AlGaN層20とpn接合されたp−AlGaN層64(半導体層)と、p−AlGaN層64の上にオーミック接合されたオーミック電極62が設けられている。

【0068】

本実施の形態の窒化物系半導体素子60のp−AlGaN層64においても、第1の実施の形態の窒化物系半導体素子10のショットキー電極30と同様に、MOSFET部32のドレイン側端部に集まる正孔をソース電極24に排出する機能を有しているため、同様の効果が得られる。

【0069】

なお、第1の実施の形態に示したショットキー電極30と本実施の形態のp−AlGaN層64とを混載するように構成してもよい。

【0070】

[第4の実施の形態]

【0071】

第4の実施の形態の窒化物系半導体素子は、第1の実施の形態の窒化物系半導体素子10、第2の実施の形態の窒化物系半導体素子50、及び第3の実施の形態の窒化物系半導体素子60と略同様の構成及び動作であるため、同一部分には同一符号を付して詳細な説明を省略し、異なる部分のみ詳細に説明する。

【0072】

本実施の形態の窒化物系半導体装置である窒化物系半導体素子の概略構成の一例を示す断面図を図11(図3、B−B断面図に対応)に示す。本実施の形態の窒化物系半導体素子70では、第1の実施の形態の窒化物系半導体素子10ではAlGaN層20上に設けられていたショットキー電極30にかわり、AlGaN層20及びGaN層16に埋込まれたショットキー電極72が設けられている。

【0073】

本実施の形態では、AlGaN層20の表面から、AlGaN層20を貫通し、GaN層16に到るまでリセス部74が形成されており、当該リセス部74にショットキー電極72が設けられている。

【0074】

このようにリセス部74内にショットキー電極72が設けられていることにより、MOSFET部32界面に蓄積する正孔をより効率的にソース電極24に排出することができる。

【0075】

なお、リセス部74の深さは、少なくともAlGaN層20内部まででもよいが、好ましくは図11に示したようにGaN層16に到達している方がよく、特に2DEGの発生部分(2DEG層18)にショットキー電極72が接触していることが好ましい。

【0076】

[第5の実施の形態]

【0077】

第5の実施の形態の窒化物系半導体素子は、第1の実施の形態の窒化物系半導体素子10、第2の実施の形態の窒化物系半導体素子50、第3の実施の形態の窒化物系半導体素子60、及び第4の実施の形態の窒化物系半導体素子70と略同様の構成及び動作であるため、同一部分には同一符号を付して詳細な説明を省略し、異なる部分のみ詳細に説明する。

【0078】

本実施の形態の窒化物系半導体装置である窒化物系半導体素子の概略構成の一例を示す断面図を図12(図2、A−A断面図に対応)に示す。本実施の形態の窒化物系半導体素子80では、表面保護膜22及びゲート絶縁膜23の下部領域に第1のn+領域となるソース電極24側のn+AlGan層83−1及びn+GaN層82−1と、ドレイン電極26側のn+AlGaN層83−2及びn+GaN層82−2が設けられていると共に、ドレイン電極26の下部に第2のn+領域となるn+AlGaN層84及びn+GaN層86が設けられている。

【0079】

ソース電極24とゲート電極28との間の表面保護膜22及びゲート絶縁膜23の下部領域のn+領域であるn+AlGaN層83−1は、ソース電極24と接合されている。

【0080】

本実施の形態のn+領域(n+GaN層82−1、82−2及びn+AlGaN層83−1、83−2)は、AlGaN層20を形成後、該当個所にSiを1015cm−2程度でイオン注入し、その後1000℃前後で熱処理することにより、AlGaN層20がn+AlGaN層83−1、83−2に、GaN層16がn+GaN層82−1、82−2に変化することで形成される。

【0081】

このようにゲート絶縁膜23下部領域にn+領域が設けられていることにより、ゲート絶縁膜23の側壁部分(リセス部21の側壁部分)がチャネル領域となっているために、当該側壁部分を伝わって流れる抵抗成分を除去することができ、窒化物系半導体素子80全体の抵抗を小さくすることができる。

【0082】

また、本実施の形態の窒化物系半導体素子80では、ドレイン電極26の下部領域のAlGaN層20がn+AlGaN層84に、GaN層16がn+GaN層86に変化している。これにより、ドレイン電極26のオーミック抵抗を小さくすることができると共に、リーク電流を減少させることができる。

【符号の説明】

【0083】

10、50、60、70、80 窒化物系半導体素子

12 基板

14 バッファ層

16 GaN層

18 2DEG層

20 AlGaN層

21、51 リセス部

22、52 表面保護膜

23、53 ゲート絶縁膜

24 ソース電極

26 ドレイン電極

28 ゲート電極

30、72 ショットキー電極

32 MOSFET部

64 p−AlGaN層

【特許請求の範囲】

【請求項1】

基板と、

前記基板上に形成されたバッファ層と、

前記バッファ層上に形成された窒化物系化合物半導体より成る電子走行層と、

前記電子走行層上に形成され、前記電子走行層とはバンドギャップエネルギーが異なる電子供給層と、

前記電子供給層上に、対向して配置されたソース電極及びドレイン電極と、

前記ソース電極と前記ドレイン電極との間でかつ、前記ソース電極と前記ドレイン電極とが対向する方向と直交する方向の一部の領域に、前記電子供給層に形成されたリセス部と、

前記ソース電極と前記ドレイン電極との間でかつ、前記ソース電極と前記ドレイン電極とが対向する方向と直交する方向の他の領域に形成された、前記ソース電極に接続されてキャリアを輸送するキャリア輸送用電極と、

前記リセス部内部を覆うように形成されたゲート絶縁膜と、

前記リセス部内の前記ゲート絶縁膜上に形成されたゲート電極と、

を備えた窒化物系半導体装置。

【請求項2】

前記電子走行層に発生する2次元電子ガスのシートキャリア濃度は2×1012cm−2以上である、請求項1に記載の窒化物系半導体装置。

【請求項3】

前記キャリア輸送用電極と前記ドレイン電極との距離が、前記ゲート電極と前記ドレイン電極との距離よりも短い、請求項1または請求項2に記載の半導体装置。

【請求項4】

前記キャリア輸送用電極が、前記電子供給層及び前記電子走行層の少なくとも一方とショットキー接合されている、請求項1から請求項3のいずれか1項に記載の窒化物系半導体装置。

【請求項5】

前記電子供給層の表面から前記電子供給層内部または前記電子走行層内部に到る深さまでの領域に前記キャリア輸送用電極が形成されている請求項4に記載の窒化物系半導体装置。

【請求項6】

前記電子供給層上にp型半導体層を備え、前記p型半導体層上に前記キャリア輸送用電極がオーミック接合されている、請求項1から請求項3のいずれか1項に記載の窒化物系半導体装置。

【請求項7】

前記ソース電極から前記リセス部の下部領域に到るまでの前記ゲート絶縁膜の下部領域に形成された第1のn+半導体層と、

前記リセス部の下部領域から前記キャリア輸送用電極の手前に到るまでの前記ゲート絶縁膜の下部領域に形成され、前記キャリア輸送用電極に接続されていない第2のn+層のうち少なくともいずれか、

を備えた請求項1から請求項6のいずれか1項に記載の窒化物系半導体装置。

【請求項8】

前記ドレイン電極の下部領域の電子供給層及び電子走行層にn+半導体層を備える、請求項1から請求項7のいずれか1項に記載の窒化物系半導体装置。

【請求項1】

基板と、

前記基板上に形成されたバッファ層と、

前記バッファ層上に形成された窒化物系化合物半導体より成る電子走行層と、

前記電子走行層上に形成され、前記電子走行層とはバンドギャップエネルギーが異なる電子供給層と、

前記電子供給層上に、対向して配置されたソース電極及びドレイン電極と、

前記ソース電極と前記ドレイン電極との間でかつ、前記ソース電極と前記ドレイン電極とが対向する方向と直交する方向の一部の領域に、前記電子供給層に形成されたリセス部と、

前記ソース電極と前記ドレイン電極との間でかつ、前記ソース電極と前記ドレイン電極とが対向する方向と直交する方向の他の領域に形成された、前記ソース電極に接続されてキャリアを輸送するキャリア輸送用電極と、

前記リセス部内部を覆うように形成されたゲート絶縁膜と、

前記リセス部内の前記ゲート絶縁膜上に形成されたゲート電極と、

を備えた窒化物系半導体装置。

【請求項2】

前記電子走行層に発生する2次元電子ガスのシートキャリア濃度は2×1012cm−2以上である、請求項1に記載の窒化物系半導体装置。

【請求項3】

前記キャリア輸送用電極と前記ドレイン電極との距離が、前記ゲート電極と前記ドレイン電極との距離よりも短い、請求項1または請求項2に記載の半導体装置。

【請求項4】

前記キャリア輸送用電極が、前記電子供給層及び前記電子走行層の少なくとも一方とショットキー接合されている、請求項1から請求項3のいずれか1項に記載の窒化物系半導体装置。

【請求項5】

前記電子供給層の表面から前記電子供給層内部または前記電子走行層内部に到る深さまでの領域に前記キャリア輸送用電極が形成されている請求項4に記載の窒化物系半導体装置。

【請求項6】

前記電子供給層上にp型半導体層を備え、前記p型半導体層上に前記キャリア輸送用電極がオーミック接合されている、請求項1から請求項3のいずれか1項に記載の窒化物系半導体装置。

【請求項7】

前記ソース電極から前記リセス部の下部領域に到るまでの前記ゲート絶縁膜の下部領域に形成された第1のn+半導体層と、

前記リセス部の下部領域から前記キャリア輸送用電極の手前に到るまでの前記ゲート絶縁膜の下部領域に形成され、前記キャリア輸送用電極に接続されていない第2のn+層のうち少なくともいずれか、

を備えた請求項1から請求項6のいずれか1項に記載の窒化物系半導体装置。

【請求項8】

前記ドレイン電極の下部領域の電子供給層及び電子走行層にn+半導体層を備える、請求項1から請求項7のいずれか1項に記載の窒化物系半導体装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【公開番号】特開2012−64672(P2012−64672A)

【公開日】平成24年3月29日(2012.3.29)

【国際特許分類】

【出願番号】特願2010−206031(P2010−206031)

【出願日】平成22年9月14日(2010.9.14)

【出願人】(510035842)次世代パワーデバイス技術研究組合 (46)

【Fターム(参考)】

【公開日】平成24年3月29日(2012.3.29)

【国際特許分類】

【出願日】平成22年9月14日(2010.9.14)

【出願人】(510035842)次世代パワーデバイス技術研究組合 (46)

【Fターム(参考)】

[ Back to top ]