窒化物系III−V族化合物半導体装置の製造方法

【課題】バッファ層上の窒化物系III−V族化合物半導体の転位密度が小さくて優れた電気的特性を有する窒化物系III−V族化合物半導体装置の製造方法を提供する。

【解決手段】SiC基板71上にAlNのバッファ層72を形成した後、AlNのバッファ層72上にGaN層を成長させる。続いて、AlNのバッファ層72と上記GaN層の界面近傍に、Gaイオンを打ち込んで、AlNのバッファ層72と上記GaN層の界面付近にアモルファスの層74を形成する。その後、基板温度を800℃まで上げてアモルファスの層74の上の上記GaN層を再結晶化して、転位が少ないGaN層75層を形成する。

【解決手段】SiC基板71上にAlNのバッファ層72を形成した後、AlNのバッファ層72上にGaN層を成長させる。続いて、AlNのバッファ層72と上記GaN層の界面近傍に、Gaイオンを打ち込んで、AlNのバッファ層72と上記GaN層の界面付近にアモルファスの層74を形成する。その後、基板温度を800℃まで上げてアモルファスの層74の上の上記GaN層を再結晶化して、転位が少ないGaN層75層を形成する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、窒化物系III−V族化合物半導体装置の製造方法に関し、特に、窒化物系III−V族化合物半導体層を備えた半導体レーザ、発光ダイオードまたはHEMT(高電子移動度トランジスタ)等の窒化物系III−V族化合物半導体装置の製造方法に関する。

【背景技術】

【0002】

従来、窒化物系III−V族化合物半導体装置としては、基板材料としてサファイアを用いたもの(例えば、特許文献1参照)や、基板材料としてSiCを用いたもの(例えば、特許文献2参照)がある。これらの窒化物系III−V族化合物半導体装置は、夫々の基板の上方に、窒化物系III−V族化合物半導体を有するヘテロ構造を備えている。尚、サファイア基板上に窒化物系III−V族化合物半導体を成長させる場合、通常はC面が用いられるが、A面・R面・M面を用いた場合でも、その上の窒化物系III−V族化合物半導体はC面成長することが明らかとなっている。これは、窒化物系III−V族化合物半導体の結晶構造が六方晶系(ウルツ鉱構造)であることから、窒化物系III−V族化合物半導体がエネルギー的に安定なC軸配向(C面成長)する傾向が強いためである。

【0003】

また、他の窒化物系III−V族化合物半導体装置としては、基板材料としてSiを用いたものがあり、特に、Si基板と窒化物系III−V族化合物半導体の間にSiCを挿入する装置が一般的になっている(例えば、特許文献3参照)。また、基板材料としてSiを用いた別の装置としては、Si基板と窒化物系III−V族化合物半導体の間に多結晶のSiを挿入する装置もある(例えば、特許文献4参照)。

【0004】

窒化物系III−V族化合物半導体装置では、上記サファイア基板、SiC基板またはSi基板を用いた装置に限らず、どのような基板を用いた装置でも、基板と窒化物系III−V族化合物半導体の間の格子定数差、熱膨張係数差または結晶構造の違いを緩和するために、基板と窒化物系III−V族化合物半導体の間に、低温成長させたGaNやAlN(AlNの場合、高温成長も可能)等から成るバッファ層を形成している。

【0005】

また、更なる窒化物系III−V族化合物半導体装置としては、基板上に窒化物系III−V族化合物半導体を成長させた後、基板を除去して窒化物系III−V族化合物半導体を新たな基板材料にした装置がある(例えば、特許文献5参照)。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】米国特許5,296,395号明細書

【特許文献2】特開2001−177189号公報

【特許文献3】特開2001−17190号公報

【特許文献4】特開2001−7396号公報

【特許文献5】特開平10−70079号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

しかしながら、上記特許文献1〜4に示された窒化物系III−V族化合物半導体装置では、上記GaNやAlNから成るバッファ層に、一般的に転位が多数存在するため、この多数の転位が、バッファ層上の窒化物系III−V族化合物半導体の結晶構造に影響を及ぼして、窒化物系III−V族化合物半導体の結晶構造が悪くなり、窒化物系III−V族化合物半導体装置の移動度等の電気的特性が悪くなるという問題がある。

【0008】

例えば、MOCVD(有機金属気相成長法)またはGSMBE(ガスソース分子線エピタキシー法)を用いて、バッファ層の上に窒化物系III−V族化合物半導体を高温で成長させた場合、この窒化物系III−V族化合物半導体の成長モードが、グレイン成長モードになって、バッファ層の多数の転位の影響が、バッファ層上の窒化物系III−V族化合物半導体に及び易くなり、多数のグレインが、窒化物系III−V族化合物半導体に生じるという問題がある。そして、この多数のグレインの横方向の成長が進んで、異なるグレインの融合面がずれて、バッファ層上の窒化物系III−V族化合物半導体に多数の転位が生じ、窒化物系III−V族化合物半導体装置の移動度等の電気的特性がいっそう悪化するという問題がある。尚、詳細には、MOCVDを使用して、窒化物系III−V族化合物半導体を成長させると、この窒化物系III−V族化合物半導体の転位密度が、108cm-2から109cm-2程度の大きな値になることがわかっており、RF-MBE(高周波を用いる分子線エピタキシー法)またはECR-MBE(電子サイクロトロン共鳴を用いる分子線エピタキシー法)を使用して、窒化物系III−V族化合物半導体を成長させると、この窒化物系III−V族化合物半導体の転位密度が、109cm-2から1010cm-2程度の更に大きな値になることがわかっている。

【0009】

一方、特許文献5に示された装置の場合においても、除去される前の基板の性質および各層の成長方法で、窒化物系III−V族化合物半導体層の転位密度が決まっているために、バッファ層上の窒化物系III−V族化合物半導体の転位密度が、108cm-2から109cm-2程度になり、サファイア基板、SiC基板またはSi基板を用いた場合と同様に、窒化物系III−V族化合物半導体装置の移動度等の電気的特性が悪くなるという問題がある。

【0010】

そこで、本発明の目的は、バッファ層上の窒化物系III−V族化合物半導体の転位密度が小さくて優れた電気的特性を有する窒化物系III−V族化合物半導体装置の製造方法を提供することにある。

【課題を解決するための手段】

【0011】

上記目的を達成するため、本発明の窒化物系III−V族化合物半導体装置の製造方法は、

基板上に窒化物系III−V族化合物半導体からなるバッファ層を形成するバッファ層形成工程と、

上記バッファ層上に窒化物系III−V族化合物半導体層を成長させる化合物半導体成長工程と、

上記バッファ層と上記窒化物系III−V族化合物半導体層の界面近傍にイオンを打ち込んで、上記界面近傍をアモルファス化するイオン打ち込み工程と、

上記イオン打ち込み工程の後に熱処理を行う熱処理工程と

を有することを特徴としている。

【0012】

本発明によれば、上記バッファ層形成工程で、基板上に形成した窒化物系III−V族化合物半導体層からなるバッファ層と、上記化合物半導体成長工程でバッファ層上に成長させた窒化物系III−V族化合物半導体層との界面付近に、イオン打ち込み工程で、イオンを打ち込むので、このイオンの打ち込みによってバッファ層と窒化物系III−V族化合物半導体層の界面付近をアモルファス化することができて、バッファ層と窒化物系III−V族化合物半導体層を上記界面付近に存在するアモルファスの層によって切り離すことができる。また、次に行われる熱処理工程で、熱処理を行うことで、上記バッファ層と窒化物系III−V族化合物半導体層の界面付近に形成したアモルファスの層上の窒化物系III−V族化合物半導体層を再結晶化できて、この再結晶化を行った窒化物系III−V族化合物半導体層の部分の転位密度を、小さくすることができる。したがって、バッファ層よりも少ないものの多くの転位を内包しているバッファ層上の窒化物系III−V族化合物半導体層の転位を、効果的に消滅させることができて、窒化物系III−V族化合物半導体装置の電気的特性を優れたものにできる。

【0013】

また、一実施形態の窒化物系III−V族化合物半導体装置の製造方法は、上記打ち込まれるイオンが、C、N、Mg、Al、Zn、GaおよびInの内の少なくとも1つであることを特徴としている。

【0014】

上記実施形態によれば、打ち込むイオンを、窒化物系III−V族化合物半導体層を形成する元素であるAl,Ga,In,Nおよび窒化物系III−V族化合物半導体層に対してp型不純物となる元素であるC,Mg,Znの内の少なくとも1つに限定したので、例えば、窒化物系III−V族化合物半導体層に対してn型不純物となるSiイオンを注入したときのように、上記界面に高濃度のn型層ができることがない。このことから、例えば、上記実施形態の窒化物系III−V族化合物半導体装置の製造方法を用いて電界効果トランジスタを製造すれば、バッファ層と窒化物系III−V族化合物半導体層との界面に高濃度のn型層ができることがないので、n型層と電流が流れる通路であるチャネル層との間で生じるパラレル伝導がおこることがない。このことから、窒化物系III−V族化合物半導体装置の大電流化を実現できる。尚、上記パラレル伝導は、2次元電子ガスによるチャネル層およびバッファ層と窒化物系III−V族化合物半導体層との界面に存在する高濃度のn型層の2つの経路を電流が流れるという現象である。このパラレル伝導が発生すると、トランジスタのピンチオフが十分に起こらないという問題が発生する。

【0015】

また、一実施形態の窒化物系III−V族化合物半導体装置の製造方法は、上記熱処理工程の温度は、熱処理工程よりも前に形成された窒化物系III−V族化合物半導体層の成長温度よりも大きく、かつ、上記成長温度に200℃を加えた温度よりも小さいことを特徴としている。

【0016】

上記実施形態によれば、上記熱処理工程では、熱処理工程よりも前に形成された窒化物系III−V族化合物半導体層の成長温度よりも高く、かつ、熱処理工程よりも前の窒化物系III−V族化合物半導体層の成長温度に200℃を加えた温度よりも低い温度で、熱処理を行うので、窒化物系III−V族化合物半導体層の転位を減少させて転位密度を低減できる。

【0017】

本発明者は、熱処理工程の温度を成長温度と同じ、成長温度±100℃、±200℃、成長温度+250℃で行い、その転位密度と結晶性がどのように変化するかをTEMによって評価した。また、熱処理後の表面状態を走査型電子顕微鏡(SEM)により評価した。

【0018】

このとき、上記熱処理工程の熱処理温度が、熱処理工程よりも前に形成された窒化物系III−V族化合物半導体層の成長温度よりも低い温度になると、熱処理工程の前にGa層の堆積と窒化物系III−V族化合物半導体層の成長を行う場合には、この熱処理工程で、積層されたGa層のGaを窒化物系III−V族化合物半導体層に十分に拡散させて、窒化物系III−V族化合物半導体層の転位を消滅させることができず、また、熱処理工程の前にイオン打ち込み工程を行う場合には、イオンを打ち込むことによって、生成した上記アモルファス層上の窒化物系III−V族化合物半導体層の再結晶化を十分に行うことができず、この窒化物系III−V族化合物半導体層の転位を十分に減少させることができなかった。一方、熱処理工程の熱処理温度が、熱処理工程よりも前に形成された窒化物系III−V族化合物半導体層の成長温度に200℃を加えた温度よりも高い温度になると、窒化物系III−V族化合物半導体層の蒸発が発生した。

【発明の効果】

【0019】

本発明の窒化物系III−V族化合物半導体装置の製造方法によれば、窒化物系III−V族化合物半導体からなるバッファ層の上方の窒化物系III−V族化合物半導体層の転位を小さくできて、このバッファ層の上方の窒化物系III−V族化合物半導体層の移動度等の電気的特性を優れたものにすることができる。したがって、この転位が小さくて電気的特性に優れた窒化物系III−V族化合物半導体層を有するHFET等の窒化物系III−V族化合物半導体装置の移動度や高周波特性等の電気的特性を優れたものにすることができる。

【図面の簡単な説明】

【0020】

【図1】第1の参考例の窒化物系III−V族化合物半導体装置の製造方法の製造工程の原理を説明する模式図である。

【図2】第2の参考例の窒化物系III−V族化合物半導体装置の製造方法の製造工程の原理を説明する模式図である。

【図3】本発明の窒化物系III−V族化合物半導体装置の製造方法の製造工程の原理を説明する模式図である。

【図4】第1参考例の窒化物系III−V族化合物半導体装置の製造方法の製造工程を示す図である。

【図5】第2参考例の窒化物系III−V族化合物半導体装置の製造方法の製造工程の一部を示す図である。

【図6】図5に続く窒化物系III−V族化合物半導体装置の製造方法の製造工程の一部を示す図である。

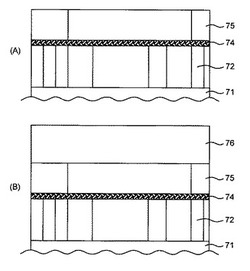

【図7】本発明の第1実施形態の窒化物系III−V族化合物半導体装置の製造方法の製造工程の一部を示す図である。

【図8】図7に続く窒化物系III−V族化合物半導体装置の製造方法の製造工程の一部を示す図である。

【図9】窒化物系III−V族化合物半導体装置のキャリア濃度と移動度との関係を示す図である。

【図10】窒化物系III−V族化合物半導体装置の一例としてのHEMT(高電子移動度トランジスタ)の構造を示す図である。

【発明を実施するための形態】

【0021】

以下、本発明を図示の実施の形態により詳細に説明する。

【0022】

先ず、図1〜図3を用いて3通りの窒化物系III−V族化合物半導体装置の製造方法の原理を簡単に説明する。

【0023】

図1は、第1の参考例の窒化物系III−V族化合物半導体装置の製造方法の原理を説明するための図であり、図2は、第2の参考例の窒化物系III−V族化合物半導体装置の製造方法の原理を説明するための図であり、図3は、本発明の窒化物系III−V族化合物半導体装置の製造方法の原理を説明するための図である。図1〜図3では、転位を模式的に縦線で表す。尚、図1〜図3では、バッファ層以下の層の図示を省略している。また、図1〜図3と、以下に示す図4〜図8および図10は模式図であり、図1〜図8および図10に示される各層の膜厚は、実際の装置における各層の膜厚と異なっている。

【0024】

第1の参考例の窒化物系III−V族化合物半導体装置の製造方法は、図1(A)に示すように、基板(図示せず)の上方に形成した転位のあるバッファ層1上にGa層2を堆積し、その後、Ga層2の上方から窒素源(以下、N源という)を照射する。このとき、上記N源の照射によって、上記Ga層2が再構築され、図1(B)に示すGaN層3として再結晶化する。このとき、上記GaN層3は、ランダムに結晶化するのではなく下地のバッファ層1の影響を受けて下地と同じ構造で再結晶化するが、GaN層の下層部4ではGa原子が転位を終焉させるため、バッファ層1の転位情報がGaN層の上層部5に伝えられることがない。このことから、GaN層の上層部5の上に成長させる窒化物系III−V族化合物半導体層の転位密度を減少させることができて、上記窒化物系III−V族化合物半導体層の結晶構造を、移動度等の電気的特性に優れた良好なものにすることができる。

【0025】

また、第2の参考例の窒化物系III−V族化合物半導体装置の製造方法は、図2(A)に示すように、基板(図示せず)の上方に形成した転位のあるバッファ層21上にGa層22を堆積し、さらに引き続いてGa層22上に、例えばGaN等の窒化物系III−V族化合物半導体層23を成長させる。次に、熱処理を行って、Ga層22の余分なGaが転位部分を通って表面から蒸発するまで、Ga層22中のGaを上方の窒化物III−V族化合物半導体層23の方に移動させて、Ga層22中の蒸発しなかったGaを、窒化物III−V族化合物半導体層23の転位付近に留まらせる。そして、上記窒化物III−V族化合物半導体層23の転位付近に留まらせたGaで、GaN等の窒化物III−V族化合物半導体層23の転位を消滅させて、図2(B)に示すように、Ga層22および窒化物III−V族化合物半導体層23を、転位が少なくて電気的特性に優れた良質な窒化物III−V族化合物半導体層25にする。

【0026】

また、本発明の窒化物系III−V族化合物半導体装置の製造方法は、図3(A)に示すように、基板(図示せず)の上方に形成した転位のあるバッファ層31上にバッファ層31よりも少ないものの多くの転位を内包しているGaN等の窒化物系III−V族化合物半導体層32を形成し、次に、上記バッファ層31と窒化物系III−V族化合物半導体層32との界面付近にイオンを注入して、図3(B)に示すように、上記界面付近にアモルファス層35を形成する。次に、熱処理を行って、アモルファス層35の一部およびアモルファス層35上の窒化物系III−V族化合物半導体層32とを再結晶化して、図3(C)に示すように、熱処理の後も残留しているアモルファス層35上の再結晶層37の転位を減少させて、この再結晶層37の結晶性を電気的特性に優れた良質なものにする。

【0027】

以下に、上記第1の参考例を、第1参考例で、上記第2の参考例を、第2参考例で、上記本発明を、第1実施形態で詳細に説明することにする。

【0028】

(第1参考例)

図4に、第1参考例の窒化物系III−V族化合物半導体装置の製造方法を示す。尚、図4においても図1〜図3と同様に、転位を縦線で模式的に示すものとする。

【0029】

先ず、基板酸化膜除去工程で、SiC基板41の基板温度を約1000℃まで上げて、SiC基板41の表面酸化膜を除去した後、バッファ層形成工程を行う。このバッファ層形成工程では、成長温度を800℃、Alビーム強度を2.0×10-7Torr、RF入力電力を200W、窒素流量を1.4sccmに夫々設定して、図4(A)に示すように、上記表面酸化膜が除去されたSiC基板41上に、膜厚が20nmのAlNのバッファ層42を形成する。

【0030】

次に、Ga堆積工程を行う。このGa堆積工程では、Gaビームの強度を6.0×10-7Torrに設定して、Gaビームを10秒間AlNのバッファ層42に照射することにより、図4(B)に示すように、AlNのバッファ層42上に膜厚が1nmのGa層43を形成する。尚、図4で、バッファ層42およびGa層43等に引かれた縦線は、バッファ層42およびGa層43等に存在する転位(ダングリングボンド(線欠陥))を模式的に表わしたものである。図4(B)において、Ga層43に引かれた縦線の数は、バッファ層42に引かれた縦線の数よりも少なくなっており、かつ、Ga層43に引かれた縦線は、バッファ層42に引かれた縦線につながっている。これは、Ga層43に生じる転位は、バッファ層42に生じる転位よりも少なく、かつ、バッファ層42の転位に引きずられて生成することを模式的に示すものである。

【0031】

引き続いて、RF入力電力を300W、窒素流量を2.0sccm、基板温度を略750℃に夫々設定して、結晶化工程を行う。この結晶化工程では、図4(B)に示すGa層43の上方から窒素をGa層43に照射してGa層43を結晶化する。

【0032】

このことにより、結晶化工程の前に、図4(B)で参照番号43で示されたGa層は、結晶化工程後に、図4(C)に示すように、GaN層の下層部44と、GaN層の上層部45に再構築される。結晶化工程でN源を照射して結晶化が行われたことにより、GaN層の下層部44の転位の数は、少なくなり(図4(B)でGa層43に4つ存在していた転位を、図4(C)に示すGaN層の下層部44では2つにし、このことを模式的に示している)、また、GaN層の上層部45は、転位の数がGaN層の下層部44の転位の数よりも更に少ない結晶構造が優れた層になる(図4(C)に示すGaN層の上層部45では、転位を0とし、このことを模式的に示している)。結晶化工程の後、GaN層の下層部44と、GaN層の上層部45のGa元素と窒素元素の化学量論比(Ga元素/窒素元素)は、1以上かつ1.5以下の値になっている。

【0033】

最後に、化合物半導体成長工程を行う。この化合物半導体成長工程では、基板温度を750℃、Gaビーム強度を6.0×10-7Torr、RF入力電力を450W、窒素流量を2.2sccmに夫々設定して、GaN層の上層部45に、Gaビームと窒素を照射して、図4(D)に示すように、GaN層の上層部45上に膜厚が2μmのGaN層46を形成して、第1参考例の窒化物系III−V族化合物半導体装置の要部の製造を完了する。

【0034】

上記第1参考例の窒化物系III−V族化合物半導体装置の製造方法を用いて、GaN層を備えた窒化物系III−V族化合物半導体装置を作製した場合と、通常のプラズマ励起窒素を用いた分子線エピタキシー法(RF-MBE法)を用いて、バッファ層上にGaN層を直接成長させた窒化物系III−V族化合物半導体装置を作成した場合の2通りについて、窒化物系III−V族化合物半導体装置のGaN層の電気的特性と転位密度を比較する実験を行った。

【0035】

その実験の結果、通常の方法でGaNを成長させた場合には、GaNの転位密度が2×1010cm-2前後の値になり、キャリア濃度が1×1019cm-3の場合に、移動度が98cm2/Vsの前後の値になった。また、キャリア濃度が1×1016cm-3の場合に、移動度が30cm2/Vsの前後の値になった。

【0036】

一方、上記第1参考例の方法でGaN層を成長させた場合には、GaN層の転位密度が、3×104cm-2前後の値になって、通常の方法でGaNを成長させた場合の2×1010cm-2前後の値よりも大幅に小さくなり、GaN層の結晶構造が結晶性に優れたものになった。また、上記第1参考例の方法でGaN層を成長させた場合には、キャリア濃度が1×1019cm-3の場合には、GaN層の移動度が100cm2/Vsになって、GaN層が通常の方法で形成されたGaN層の電気的特性と同等の電気的特性を示す一方、キャリア濃度が1×1016cm-3の場合には、移動度が1500cm2/Vsと非常に大きな値になって、上記第1参考例の方法で形成されたGaN層の電気特性が、通常の方法で形成されたGaN層と比べてはるかに優れたものになった。

【0037】

上記第1参考例の窒化物系III−V族化合物半導体装置の製造方法によれば、バッファ層形成工程でSiC基板41上に形成した転位のあるAlNのバッファ層42に、Ga堆積工程でGa層43を堆積して、更に、結晶化工程でGa層43の表面にN源を照射してGa層43の結晶化を行うので、N源の照射を行う結晶化工程の後、バッファ層42上に形成されるGaN層の下層部44の結晶構造が、転位(ダングリングボンド(線欠陥))が消滅した高品質な結晶構造になる。したがって、GaN層の下層部44のGaNの結晶構造が、ダングリングボンドが解消された高品質なものになるため、GaN層の上層部45まで、バッファ層42のダングリングボンドの情報が到達して転位情報が及ぶことを防止でき、GaN層の上層部45に、下地のバッファ層42の転位情報以外の情報のみを伝達することができる。つまり、GaN層の上層部45の結晶構造を転位がないバッファ層42の結晶構造と略同一な構造にすることができる。したがって、化合物半導体成長工程で、この転位が少ない良質のGaN層の上層部45の上に、転位密度が低いGaN層46を形成することができて、上記第1参考例の窒化物系III−V族化合物半導体装置の製造方法を用いて形成した窒化物系III−V族化合物半導体装置の移動度等の電気的特性を優れたものにすることができる。

【0038】

また、上記第1参考例の窒化物系III−V族化合物半導体装置の製造方法によれば、Ga堆積工程で堆積されるGa層43の厚さを、1nmにしたので、Ga層43上のGaN層46の転位を十分に消滅させることができると共に、Ga層43上のGaN層46の結晶性を良質なものにすることができる。

【0039】

尚、上記第1参考例では、SiC基板41を用いたが、SiC基板の代わりにサファイア基板やSi基板等のSiC基板以外の基板を用いても良い。

【0040】

また、上記第1参考例では、SiC基板41にAlNのバッファ層42を成長させたが、AlNのバッファ層に限らず、基板上にGaNのバッファ層やInNのバッファ層等の窒化物系III−V族化合物半導体のバッファ層を成長させても良い。

【0041】

また、上記第1参考例では、化合物半導体成長工程で、結晶化したGaN層の上層部45上にGaN層46を成長させたが、化合物半導体成長工程では、GaN層に限らず、結晶化したGaN層の上層部上にAlN層やInN層等の窒化物系III−V族化合物半導体層を成長させても良い。

【0042】

また、上記第1参考例では、Ga堆積工程で、AlNのバッファ層42上に膜厚が1nmのGa層43を形成したが、Ga堆積工程で、窒化物系III−V族化合物半導体のバッファ層上に、膜厚が0.1nm以上かつ10nm以下の厚さを有するGa層を形成しても良い。尚、窒化物系III−V族化合物半導体のバッファ層上に、膜厚が0.1nm以上かつ10nm以下の厚さを有するGa層を形成した場合においても、膜厚が1nmのGa層43を形成した場合と同様に、Ga層上の窒化物系III−V族化合物半導体の転位を十分に消滅させることができて、Ga層上の窒化物系III−V族化合物半導体の結晶性を良質なものにすることができる。

【0043】

(第2参考例)

図5および図6に、第2参考例の窒化物系III−V族化合物半導体装置の製造方法を示す。尚、図5および図6おいても図4と同様に、転位を縦線で模式的に示すものとする。

【0044】

先ず、基板酸化膜除去工程で、SiC基板51の基板温度を1000℃まで上げて、SiC基板51の表面酸化膜を除去した後、バッファ層形成工程を行う。このバッファ層形成工程では、成長温度を800℃、Alビーム強度を2.0×10-7Torr、RF入力電力を200W、窒素流量を1.4sccmに夫々設定して、図5(A)に示すように、上記表面酸化膜が除去されたSiC基板51上に、膜厚が20nmのAlNのバッファ層52を形成する。

【0045】

次に、Ga堆積工程を行う。このGa堆積工程では、Gaビームの強度を6.0×10-7Torrに設定して、このGaビームを10秒間AlNのバッファ層52に照射することにより、図5(B)に示すように、AlNのバッファ層52上に膜厚が1nmのGa層53を形成する。

【0046】

引き続いて、第1化合物半導体成長工程を行う。この第1化合物半導体成長工程では、基板温度を750℃、Gaビーム強度を6.0×10-7Torr、RF入力電力を450W、窒素流量を2.2sccmに夫々設定して、図5(C)に示すように、Ga層53上に厚さが20nmのGaN層54を形成する。

【0047】

次に、基板温度800℃まで上げて熱処理工程を行う。この熱処理工程では、Ga堆積工程で堆積させたGaを、図5(C)に示すGaN層54の転位を介してGaN層54の転位部分に移動させ、余分なGaをこの転位部分を通じてGaN層54の表面から蒸発させる。このとき、Ga堆積工程で堆積させたGaのうちで、表面から蒸発しなかったGaは、図5(C)に示すGaN層54の転位部分付近に留まる。そして、この図5(C)に示すGaN層54の転位部分付近に留まったGaは、図5(C)に示すGaN層54の転位を消滅させ、図5(C)に示すGaN層54を、図6(A)に示す転位が少ない良質なGaN層55にかえる。尚、上記熱処理工程では、Ga堆積工程で堆積させたGaを、GaN層54に移動させるので、熱処理工程の後、Ga層53は、消滅することになる。上記熱処理工程の後、上記転位が少なく良質なGaN層55のGa元素と窒素元素の化学量論比(Ga元素/窒素元素)は、1以上かつ1.5以下の値になっている。

【0048】

最後に、第2化合物半導体成長工程を行う。この第2化合物半導体成長工程では、基板温度を750℃、Gaビーム強度を6.0×10-7Torr、RF入力電力を450W、窒素流量を2.2sccmに夫々設定して、図6(B)に示すように、上記転位が少ない良質なGaN層55上に厚さが2μmのGaN層56を成長させて、第2参考例の窒化物系III−V族化合物半導体装置の要部の製造を終了する。

【0049】

上記第2参考例の窒化物系III−V族化合物半導体装置の製造方法を用いて作成した窒化物系III−V族化合物半導体装置の要部のGaN層56の電気的特性および転位密度と、通常のプラズマ励起窒素を用いた分子線エピタキシー法(RF-MBE法)を用いてバッファ層上に直接成長させたGaN層の電気的特性および転位密度とを比較する実験を行った。

【0050】

上記実験の結果、上記第2参考例の方法でGaN層56を成長させた場合には、GaN56の転位密度が、2×104cm-2前後の値になって、通常の方法でGaNを成長させた場合の転位密度の値である2×1010cm-2前後の値よりも大幅に小さくなった。

【0051】

また、上記第2参考例の方法でGaN層56を成長させた場合には、GaN層56のキャリア濃度が1×1019cm-3のときに、GaN層56の移動度が95cm2/Vsになって、GaN層56の電気的特性が通常の方法で形成されたGaN層の電気的特性と略同等の電気的特性を示す一方、GaN層56のキャリア濃度が1×1016cm-3のときに、GaN層56の移動度が1450cm2/Vsと非常に大きな値になって、GaN層56の電気的特性が、通常の方法で形成されたGaN層の電気的特性と比較してはるかに優れたものになった。

【0052】

上記第2参考例によれば、熱処理工程で熱処理を行うので、Ga堆積層のGaの一部を、図5(C)に示すGaN層54の転位部分を通って表面から蒸発させることができると共に、Ga層のGaの残りを、図5(C)に示すGaN層54の転位付近に移動させて、図5(C)に示すGaN層54の転位を消滅させることができる。すなわち、図5(C)に示す転位が多いGaN層54を、図6(A)に示す転位の少ない良質なGaN層55に再構築できるので、第2化合物半導体成長工程で、この転位の少ない良質なGaN層55上に形成するGaN層56の結晶性を、転位が少ない良質なものにできる。したがって、窒化物系III−V族化合物半導体装置の移動度等の電気的特性を優れたものにできる。

【0053】

また、上記第2参考例によれば、Ga堆積工程で堆積されるGa層53の厚さを1nmにしたので、Ga層53の上方のGaN層56の転位を十分に消滅させることができると共に、Ga層53の上方のGaN層56の結晶性を良質なものにすることができる。

【0054】

また、上記第2参考例によれば、熱処理工程では、第1化合物半導体成長工程の基板温度である750℃よりも高く、かつ、第1化合物半導体成長工程の基板温度である750℃に200℃を加えた温度である950℃よりも低い800℃で熱処理を行うので、GaN層54の蒸発が起きない状態で、Gaの拡散を十分に行うことができて、GaN層54の再結晶化を十分に行うことができる。したがって、熱処理を行ったGaN層54の転位を十分に減少させてGaN層54の転位密度を大幅に低減できる。

【0055】

尚、上記第2参考例では、SiC基板51を用いたが、SiC基板51の代わりにサファイア基板やSi基板等のSiC基板以外の基板を用いても良い。

【0056】

また、上記第2参考例では、SiC基板51上にAlNのバッファ層52を成長させたが、AlNのバッファ層に限らず、基板上にGaNのバッファ層やInNのバッファ層等の窒化物系III−V族化合物半導体のバッファ層を成長させても良い。

【0057】

また、上記第2参考例では、熱処理工程の後に、GaN層56を成長させたが、GaN層に限らず、熱処理工程の後に、AlN層やInN層等の窒化物系III−V族化合物半導体層を成長させても良い。

【0058】

また、上記第2参考例では、Ga堆積工程で、AlNのバッファ層52上に膜厚が1nmのGa層53を形成したが、Ga堆積工程で、窒化物系III−V族化合物半導体のバッファ層上に、膜厚が0.1nm以上かつ10nm以下の厚さを有するGa層を形成しても良い。そして、窒化物系III−V族化合物半導体のバッファ層上に、膜厚が0.1nm以上かつ10nm以下の厚さを有するGa層を形成した場合においても、膜厚が1nmのGa層53を形成した場合と同様に、Ga層上の窒化物系III−V族化合物半導体の転位を十分に消滅させることができると共に、Ga層上の窒化物系III−V族化合物半導体の結晶性を良質なものにすることができる。

【0059】

また、上記第2参考例では、基板温度を800℃まで上げて熱処理工程を行ったが、第1化合物半導体成長工程の基板温度である750℃よりも大きくて、かつ、第1化合物半導体成長工程の基板温度である750℃に200℃を加えた950℃よりも小さい温度に基板温度を設定して熱処理工程を行っても、基板温度を800℃まで上げて熱処理工程を行った場合と同様の作用効果を奏することが確認されている。尚、950℃以上の温度に基板温度を設定して熱処理工程を行うと、GaN層54の蒸発が起こって、窒化物系III−V族化合物半導体装置の品質が低下することになり、750℃以下の温度に基板温度を設定して熱処理工程を行うと、Gaの拡散を十分に行うことができなくなる。

【0060】

(第1実施形態)

図7および図8に、本発明の第1実施形態の窒化物系III−V族化合物半導体装置の製造方法を示す。尚、図7および図8においても図4、図5および図6と同様に、転位を縦線で模式的に示すものとする。

【0061】

先ず、基板酸化膜除去工程で、SiC基板71の基板温度を1000℃まで上げて、SiC基板71の表面酸化膜を除去した後、バッファ層形成工程を行う。このバッファ層形成工程では、成長温度を800℃、Alビーム強度を2.0×10-7Torr、RF入力電力を200W、窒素流量を1.4sccmに夫々設定して、図7(A)に示すように、SiC基板71上に、膜厚が20nmのAlNのバッファ層72を形成する。

【0062】

次に、化合物半導体成長工程を行う。この化合物半導体成長工程では、基板温度を750℃、Gaビーム強度を6.0×10-7Torr、RF入力電力を450W、窒素流量を2.2sccmに夫々設定して、図7(B)に示すようように、AlNのバッファ層72上に厚さが20nmのGaN層73を成長させる。

【0063】

引き続いて、イオン打ち込み工程を行う。このイオン打ち込み工程では、イオン注入原子としてGaを用い、このGaイオンの加速電圧20keV、このGaイオンの注入量を1×1018cm-3に設定して、AlNのバッファ層72とGaN層73の界面近傍に、Gaイオンを打ち込んで、図7(C)に示すように、AlNのバッファ層72とGaN層73の界面付近にアモルファスの層74を形成して、アモルファスの層74によりAlNのバッファ層72とGaN層73とを切り離す。

【0064】

次に、熱処理工程を行う。この熱処理工程では、基板温度を800℃まで上げて熱処理を行うことにより、図7(C)に示すアモルファスの層74の上のGaN層73を再結晶化して、図8(A)に示すように、転位が少ないGaN層75層を形成する。この熱処理工程を行った後、Gaイオンが打ち込まれて形成されたアモルファスの層74の膜厚は、図8(A)に示すように、小さくはなるが一部は残留する。図8(A)に示すこの残留したアモルファスの層74では、Ga元素と窒素の化学量論比(Ga元素/窒素)が1以上かつ1.5以下の値になっている。

【0065】

最後に、第2化合物成長工程を行う。この第2化合物成長工程では、基板温度を750℃、Gaビーム強度を6.0×10-7Torr、RF入力電力を450W、窒素流量を2.2sccmに夫々設定して、図8(B)に示すように、転位が少ないGaN層75層上に厚さが2μmのGaN層76を成長させる。このようにして、第1実施形態の窒化物系III−V族化合物半導体装置の要部の製造を終了する。

【0066】

上記第1実施形態の窒化物系III−V族化合物半導体装置の製造方法を用いて作成した窒化物系III−V族化合物半導体装置の要部のGaN層76の電気的特性および転位密度と、通常のプラズマ励起窒素を用いた分子線エピタキシー法(RF-MBE法)を用いてバッファ層上に直接成長させたGaN層の電気的特性および転位密度とを比較する実験を行った。

【0067】

上記実験の結果、上記第1実施形態の窒化物系III−V族化合物半導体装置の製造方法でGaNを成長させた場合には、GaNの転位密度が、4×104cm-2前後の値になって、通常の方法でGaNを成長させた場合の2×1010cm-2前後の値よりも大幅に小さくなった。

【0068】

また、上記第1実施形態の方法でGaN層76を成長させた場合には、GaN層76のキャリア濃度が1×1019cm-3のときに、GaN層76の移動度が103cm2/Vsになって、GaN層76の電気的特性が通常の方法で形成されたGaN層の電気的特性と略同等の電気的特性を示す一方、GaN層76のキャリア濃度が1×1016cm-3のときに、GaN層76の移動度が1480cm2/Vsと非常に大きな値になって、GaN層76の電気的特性が、通常の方法で形成されたGaN層の電気的特性と比べてはるかに優れたものになった。

【0069】

上記第1実施形態によれば、上記バッファ層形成工程で、SiC基板71上に形成したAlNからなるバッファ層72と、上記化合物半導体成長工程でAlNのバッファ層72上に成長させたGaN層73との界面付近に、イオン打ち込み工程で、Gaイオンを打ち込むので、AlNのバッファ層72とGaN層73の界面付近にアモルファスの層74を形成できて、AlNのバッファ層72とGaN層73とを切り離して、AlNのバッファ層72の転位情報が、GaN層73に伝わらないようにすることができる。また、次に行われる熱処理工程で、熱処理を行うことで、アモルファスの層74上のGaN層73を再結晶化して、図7(C)に示す転位が多いGaN層73を図8(A)に示す転位が少ないGaN層75に作りかえることができる。したがって、この転位が少ないGaN層75上に結晶性が良いGaN層76を形成できて、第1実施形態の窒化物系III−V族化合物半導体装置の要部を用いて作成された窒化物系III−V族化合物半導体装置の電気的特性を優れたものにできる。

【0070】

また、上記第1実施形態によれば、上記イオン打ち込み工程で、AlNのバッファ層72とGaN層73との界面付近にGaイオンを打ち込んだので、AlNのバッファ層とGaN層との界面付近にSiイオンを注入した場合のように、界面付近に高濃度のn型層ができることがない。したがって、例えば、上記第1実施形態の窒化物系III−V族化合物半導体装置の製造方法を用いて電界効果トランジスタを製造しても、AlNのバッファ層72とGaN層73との界面に高濃度のn型層ができることがなくて、このn型層が、電流が流れる通路であるチャネル層とパラレル伝導を引き起こすことがない。このことから、上記第1実施形態の窒化物系III−V族化合物半導体装置の製造方法を用いて製造された窒化物系III−V族化合物半導体装置の大電流化を実現できる。

【0071】

また、上記第1実施形態によれば、熱処理工程では、第1化合物半導体成長工程の基板温度である750℃より高く、かつ、第1化合物半導体成長工程の基板温度である750℃に200℃を加えた950℃よりも低い800℃で熱処理を行うので、GaN層73の再蒸発が起きない状態で、アモルファスの層74上のGaN層73の再結晶化を十分に行うことができて、再結晶化を行って形成したGaN層75の転位密度を低減できる。したがって、GaN層75上に形成したGaN層76の結晶性を更に優れたものにできる。

【0072】

尚、上記第1実施形態では、SiC基板71を用いたが、SiC基板71の代わりにサファイア基板やSi基板等のSiC基板以外の基板を用いても良い。

【0073】

また、上記第1実施形態では、SiC基板71上にAlNのバッファ層72を成長させたが、AlNのバッファ層に限らず、基板上にGaNのバッファ層やInNのバッファ層等の窒化物系III−V族化合物半導体のバッファ層を成長させても良い。

【0074】

また、上記第1実施形態では、化合物半導体成長工程で、AlNのバッファ層72上にGaN層73を成長させたが、GaN層に限らず、化合物半導体成長工程で、AlN等の窒化物系III−V族化合物半導のバッファ層上にAlN層やInN層等の窒化物系III−V族化合物半導体層を成長させても良い。

【0075】

また、上記第1実施形態では、イオン打ち込み工程で、AlNのバッファ層72とGaN層73の界面近傍に、Gaイオンを注入して、アモルファスの層74を形成したが、Gaイオンの代わりに、Cイオン、Nイオン、Mgイオン、Alイオン、ZnイオンおよびInイオンの内の1つを打ち込んでも、Gaイオンを打ち込んだときと同様の作用効果を奏する。また、Cイオン、Nイオン、Mgイオン、Alイオン、Znイオン、GaイオンおよびInイオンの内の任意の2つ以上のイオンを打ち込んでもGaイオンを打ち込んだときと同様の作用効果を奏する。

【0076】

また、上記第1実施形態では、基板温度を800℃まで上げて熱処理工程を行ったが、熱処理工程で使用される基板温度は、800℃に限定されるものではなくて、熱処理工程で使用される基板温度は、AlNの成長温度である750℃よりも高く、かつ、AlNの成長温度である750℃に200℃を加えた温度である950℃よりも低い温度であれば、どのような温度であっても良い。そして、この範囲の基板温度で、熱処理工程を行えば、基板温度を800℃まで上げて熱処理工程を行った場合と同様の作用効果を奏することが確認されている。尚、950℃以上の温度に基板温度を設定して熱処理工程を行うと、GaN層73の蒸発が起こって、窒化物系III−V族化合物半導体装置の品質が低下することになり、750℃以下の温度に基板温度を設定して熱処理工程を行うと、GaN層73の再結晶化を十分に行うことができなくなる。

【0077】

表1に、通常の窒化物系III−V族化合物半導体装置の製造方法と、第1参考例、第2参考例および第1実施形態の窒化物系III−V族化合物半導体装置の製造方法で作製された4通りの窒化物系III−V族化合物半導体装置の要部における最上層のGaN層の転位密度と、キャリア濃度が1×1019cm-3のときの上記GaN層の移動度と、キャリア濃度が1×1016cm-3のときの上記GaN層の移動度を示す。

【0078】

【表1】

【0079】

表1に示すように、1×1019cm-3の高キャリア濃度の場合、どの方法で窒化物系III−V族化合物半導体装置を形成しても、GaN層の移動度は、略100cm2/Vs前後の値になり、4つの方法でGaN層の電気的特性に違いが見られない。一方、1×1016cm-3の低キャリア濃度の場合、通常の方法で製作されたGaN層の移動度と、他の3つの方法(すなわち、第1参考例、第2参考例および第1実施形態の方法)で製作されたGaN層の移動度との間に、顕著な違いが見られる。

【0080】

図9に、通常の窒化物系III−V族化合物半導体装置の製造方法と、第1参考例、第2参考例および第1実施形態の窒化物系III−V族化合物半導体装置の製造方法で作製された4通りの窒化物系III−V族化合物半導体装置のGaN層のキャリア濃度と移動度との関係を示す。

【0081】

図9に示す丸印は、通常の窒化物系III−V族化合物半導体装置の製造方法を用いた場合の計測点であり、表1の結果をプロットしたものである。一方、図9に示す四角印は、第1参考例、第2参考例および第1実施形態の窒化物系III−V族化合物半導体装置の製造方法を用いた場合の計測点であり、表1の結果をプロットしたものである(図9の縮尺の尺度では、第1参考例、第2参考例および第1実施形態の違いを示せず、3つの発明は図上で同じ点をさす)。

【0082】

図9に示すように、キャリア濃度が1×1017.3cm-3以上の領域においては、同じキャリア濃度に対する移動度が、4つの方法で同等になっており、キャリア濃度が下がるにつれて、移動度が増加していることがわかる。

【0083】

一方、キャリア濃度が下がって1×1017.3cm-3に達すると、図9に示すように、通常の方法の移動度と、上記3つの方法(第1参考例、第2参考例、第1実施形態の方法)の移動度とが分岐することがわかる。詳細には、キャリア濃度が1×1015cm-3以上で1×1017.3cm-3未満の領域においては、通常の方法では、キャリア濃度が下がるにつれて、移動度も減少するのに対し、上記3つの方法では、キャリア濃度が下がるにつれて、移動度が増加していることがわかる。つまり、通常の方法と、上記3つの方法とで、移動度の振る舞いに大きな違いが生じていることがわかる。

【0084】

これは、GaN層の移動度μが、以下の式(1)に示すように、キャリア濃度nの1.5乗と転位密度Ndisl.により決定されるからである。

【0085】

【数1】

【0086】

詳細には、キャリア濃度が大きい場合には、キャリア濃度nの1.5乗の値が大きくなるので、GaNの移動度μは、上記式(1)により、主にキャリア濃度nの1.5乗の因子によって決定される。これは、キャリア濃度が大きくなるとキャリア同士の衝突が頻繁に起こって、キャリア‐キャリア散乱で移動度μが決定されることを意味している。つまり、キャリア濃度が1×1019cm-3等の大きな領域では、移動度μは、nの1.5乗の値だけで略決定され、転位密度Ndislの影響を受けにくくなる。これが、キャリア濃度が1×1019cm-3で、移動度μが、いずれの方法でも100cm2/Vs前後の値になることの理由である。

【0087】

一方、キャリア濃度が1×1016cm-3等の小さい領域では、式(1)の分子の値が小さくなり、移動度μは転位密度Ndislの影響を大きく受けることになる。これが、キャリア濃度が1×1016cm-3では、転位が多い通常の成長法では移動度が30cm2/Vs程度にしかならない一方、転位が少ない本発明の方法では移動度が1500cm2/Vs程度の大きな値になることの理由である。つまり、本発明の方法で作成したGaN層では、通常の成長法とは異なり、キャリア濃度が1012cm-3程度以下にならないと転位が支配的な領域には入らないのである。すなわち、本発明の方法を用いれば、転位が少ないGaN層を形成できるので、キャリア濃度が小さい領域においても、大きな移動度μを得ることができるのである。

【0088】

図10に、窒化物系III−V族化合物半導体装置の一例としてのHEMT(高電子移動度トランジスタ)の構造を示す。

【0089】

図10において、101はサファイア基板の(0001)面、102は低温成長させた膜厚20nmのGaNバッファ層、103はGaN層(バックグラウンドキャリア濃度1016cm-3以下、膜厚3μm)、104はAl0.25Ga0.75N層(膜厚30nm)、105はHf(ハフニウム)ソース/ドレイン電極、106はPd(パラジウム)ゲート電極である。

【0090】

次に、図10に示す層構造を有するHEMT(高電子移動度トランジスタ)を、MOCVD法を用いた通常の方法およびMOCVD法を用いた第1参考例、第2参考例および第1実施形態の方法で作成し、4つのHEMTのヘテロ構造特性およびHEMT特性を比較した。

【0091】

以下に、4つのHEMTの作製法について要点のみ簡単に述べる。

【0092】

初めに、通常の場合には、先ず、水素雰囲気中でサファイア基板の基板温度を1100℃にして、サファイア基板の酸化膜を除去するクリーニングを10分間行った後、サファイア基板の基板温度を500℃、Ga原料流量(トリメチルガリウムTMG)の流量を10sccm、HN3の流量を5slmに夫々設定してGaNバッファ層を成長させる。

【0093】

次に、基板温度を1000℃、Ga原料(トリメチルガリウムTMG)の流量を40sccmに設定して、GaN層を成長させた後、基板温度を1000℃、トリメチルアルミニウム(TMA)流量を5sccm、TMGの流量を25sccm、NH3の流量を6slmに夫々設定してAl0.25Ga0.75N層を成長させる。

【0094】

最後に、Al0.25Ga0.75N層にHf(ハフニウム)ソース/ドレイン電極、Pd(パラジウム)ゲート電極を形成してHEMTが作製される。

【0095】

次に、第1参考例の方法では、GaNバッファ層成長後にTMGのみを流してGaを堆積して温度を上げながら窒素源としてのNH3を流してGaを結晶化する。

【0096】

また、第2参考例の方法では、バッファ層成長後にTEGのみを流してGaを堆積した後、引き続いて成長温度を500℃にして20nm程度のGaN層を形成する。その後、基板温度を上げてGaNを成長させて、成長中断後に基板温度を1050℃に上げて1分間熱処理し、引き続いて1000℃でへテロ構造を成長させる。

【0097】

最後に、本発明の第1実施形態の方法では、低温バッファ層成長後にGaN層を成長させた後、イオン注入を行う。その後、1050℃で1分間の熱処理を行い、この熱処理に引き続いて1000℃でヘテロ構造を形成する。

【0098】

尚、上記4つの方法では、ゲート長Lgが0.1μm、ゲート幅Wgが200μmのHEMTを製造した。

【0099】

表2に、従来の方法と、第1参考例、第2参考例および第1実施形態の方法で製造した4つのHEMTの特性比較結果を示す。

【0100】

【表2】

【0101】

尚、表2において、DC/RF分散率は、直流印加時の特性と高周波印加時の特性の変化率であり、この値が小さいと、HEMT特性は、高周波応用に優れたものになる。

【0102】

表2に示すように、通常の方法と上記3つの方法(第1参考例,第2参考例および第1実施形態の方法)では、転位密度が2桁程度異なっているが、ヘテロ構造の電気的特性を示す移動度、HEMT特性である相互コンダクタンスgmおよび最大発信周波数fmaxに大きな違いは見られない。しかしながら、トラップとして働いていた転位密度が小さくなるため、上記3つの方法(第1参考例,第2参考例および第1実施形態の方法)では、通常の方法と比較して、DC/RF分散率が30%から10%以下に大きく減少し、HEMT特性が大きく改善されている。

【0103】

尚、上記HEMTを形成するにあたって、各層をMOCVD法を用いて成長させたが、RF-MBE法以外の分子線エキタピシー装置を用いた結晶成長法でもMOCVD法と同様の改善が見られることが確認されている(RF-MBE法を用いた成長方法では、転位が多いために移動度が極端に小さくて、十分なHEMT特性が出ないことが確認されている)。

【符号の説明】

【0104】

1,21,31 バッファ層

2,22,43,53 Ga層

3,46,54,55,56,73,75,76,103 GaN層

4,44 GaN層の下層部

5,55 GaN層の上層部

23,25,32 窒化物系III−V族化合物半導体層

35,74 アモルファスの層

41,51,71 SiC基板

42,52,72 AlNのバッファ層

101 サファイア基板

102 GaNバッファ層

104 AlGaN層

105 ソース/ドレイン電極

106 ゲート電極

【技術分野】

【0001】

本発明は、窒化物系III−V族化合物半導体装置の製造方法に関し、特に、窒化物系III−V族化合物半導体層を備えた半導体レーザ、発光ダイオードまたはHEMT(高電子移動度トランジスタ)等の窒化物系III−V族化合物半導体装置の製造方法に関する。

【背景技術】

【0002】

従来、窒化物系III−V族化合物半導体装置としては、基板材料としてサファイアを用いたもの(例えば、特許文献1参照)や、基板材料としてSiCを用いたもの(例えば、特許文献2参照)がある。これらの窒化物系III−V族化合物半導体装置は、夫々の基板の上方に、窒化物系III−V族化合物半導体を有するヘテロ構造を備えている。尚、サファイア基板上に窒化物系III−V族化合物半導体を成長させる場合、通常はC面が用いられるが、A面・R面・M面を用いた場合でも、その上の窒化物系III−V族化合物半導体はC面成長することが明らかとなっている。これは、窒化物系III−V族化合物半導体の結晶構造が六方晶系(ウルツ鉱構造)であることから、窒化物系III−V族化合物半導体がエネルギー的に安定なC軸配向(C面成長)する傾向が強いためである。

【0003】

また、他の窒化物系III−V族化合物半導体装置としては、基板材料としてSiを用いたものがあり、特に、Si基板と窒化物系III−V族化合物半導体の間にSiCを挿入する装置が一般的になっている(例えば、特許文献3参照)。また、基板材料としてSiを用いた別の装置としては、Si基板と窒化物系III−V族化合物半導体の間に多結晶のSiを挿入する装置もある(例えば、特許文献4参照)。

【0004】

窒化物系III−V族化合物半導体装置では、上記サファイア基板、SiC基板またはSi基板を用いた装置に限らず、どのような基板を用いた装置でも、基板と窒化物系III−V族化合物半導体の間の格子定数差、熱膨張係数差または結晶構造の違いを緩和するために、基板と窒化物系III−V族化合物半導体の間に、低温成長させたGaNやAlN(AlNの場合、高温成長も可能)等から成るバッファ層を形成している。

【0005】

また、更なる窒化物系III−V族化合物半導体装置としては、基板上に窒化物系III−V族化合物半導体を成長させた後、基板を除去して窒化物系III−V族化合物半導体を新たな基板材料にした装置がある(例えば、特許文献5参照)。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】米国特許5,296,395号明細書

【特許文献2】特開2001−177189号公報

【特許文献3】特開2001−17190号公報

【特許文献4】特開2001−7396号公報

【特許文献5】特開平10−70079号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

しかしながら、上記特許文献1〜4に示された窒化物系III−V族化合物半導体装置では、上記GaNやAlNから成るバッファ層に、一般的に転位が多数存在するため、この多数の転位が、バッファ層上の窒化物系III−V族化合物半導体の結晶構造に影響を及ぼして、窒化物系III−V族化合物半導体の結晶構造が悪くなり、窒化物系III−V族化合物半導体装置の移動度等の電気的特性が悪くなるという問題がある。

【0008】

例えば、MOCVD(有機金属気相成長法)またはGSMBE(ガスソース分子線エピタキシー法)を用いて、バッファ層の上に窒化物系III−V族化合物半導体を高温で成長させた場合、この窒化物系III−V族化合物半導体の成長モードが、グレイン成長モードになって、バッファ層の多数の転位の影響が、バッファ層上の窒化物系III−V族化合物半導体に及び易くなり、多数のグレインが、窒化物系III−V族化合物半導体に生じるという問題がある。そして、この多数のグレインの横方向の成長が進んで、異なるグレインの融合面がずれて、バッファ層上の窒化物系III−V族化合物半導体に多数の転位が生じ、窒化物系III−V族化合物半導体装置の移動度等の電気的特性がいっそう悪化するという問題がある。尚、詳細には、MOCVDを使用して、窒化物系III−V族化合物半導体を成長させると、この窒化物系III−V族化合物半導体の転位密度が、108cm-2から109cm-2程度の大きな値になることがわかっており、RF-MBE(高周波を用いる分子線エピタキシー法)またはECR-MBE(電子サイクロトロン共鳴を用いる分子線エピタキシー法)を使用して、窒化物系III−V族化合物半導体を成長させると、この窒化物系III−V族化合物半導体の転位密度が、109cm-2から1010cm-2程度の更に大きな値になることがわかっている。

【0009】

一方、特許文献5に示された装置の場合においても、除去される前の基板の性質および各層の成長方法で、窒化物系III−V族化合物半導体層の転位密度が決まっているために、バッファ層上の窒化物系III−V族化合物半導体の転位密度が、108cm-2から109cm-2程度になり、サファイア基板、SiC基板またはSi基板を用いた場合と同様に、窒化物系III−V族化合物半導体装置の移動度等の電気的特性が悪くなるという問題がある。

【0010】

そこで、本発明の目的は、バッファ層上の窒化物系III−V族化合物半導体の転位密度が小さくて優れた電気的特性を有する窒化物系III−V族化合物半導体装置の製造方法を提供することにある。

【課題を解決するための手段】

【0011】

上記目的を達成するため、本発明の窒化物系III−V族化合物半導体装置の製造方法は、

基板上に窒化物系III−V族化合物半導体からなるバッファ層を形成するバッファ層形成工程と、

上記バッファ層上に窒化物系III−V族化合物半導体層を成長させる化合物半導体成長工程と、

上記バッファ層と上記窒化物系III−V族化合物半導体層の界面近傍にイオンを打ち込んで、上記界面近傍をアモルファス化するイオン打ち込み工程と、

上記イオン打ち込み工程の後に熱処理を行う熱処理工程と

を有することを特徴としている。

【0012】

本発明によれば、上記バッファ層形成工程で、基板上に形成した窒化物系III−V族化合物半導体層からなるバッファ層と、上記化合物半導体成長工程でバッファ層上に成長させた窒化物系III−V族化合物半導体層との界面付近に、イオン打ち込み工程で、イオンを打ち込むので、このイオンの打ち込みによってバッファ層と窒化物系III−V族化合物半導体層の界面付近をアモルファス化することができて、バッファ層と窒化物系III−V族化合物半導体層を上記界面付近に存在するアモルファスの層によって切り離すことができる。また、次に行われる熱処理工程で、熱処理を行うことで、上記バッファ層と窒化物系III−V族化合物半導体層の界面付近に形成したアモルファスの層上の窒化物系III−V族化合物半導体層を再結晶化できて、この再結晶化を行った窒化物系III−V族化合物半導体層の部分の転位密度を、小さくすることができる。したがって、バッファ層よりも少ないものの多くの転位を内包しているバッファ層上の窒化物系III−V族化合物半導体層の転位を、効果的に消滅させることができて、窒化物系III−V族化合物半導体装置の電気的特性を優れたものにできる。

【0013】

また、一実施形態の窒化物系III−V族化合物半導体装置の製造方法は、上記打ち込まれるイオンが、C、N、Mg、Al、Zn、GaおよびInの内の少なくとも1つであることを特徴としている。

【0014】

上記実施形態によれば、打ち込むイオンを、窒化物系III−V族化合物半導体層を形成する元素であるAl,Ga,In,Nおよび窒化物系III−V族化合物半導体層に対してp型不純物となる元素であるC,Mg,Znの内の少なくとも1つに限定したので、例えば、窒化物系III−V族化合物半導体層に対してn型不純物となるSiイオンを注入したときのように、上記界面に高濃度のn型層ができることがない。このことから、例えば、上記実施形態の窒化物系III−V族化合物半導体装置の製造方法を用いて電界効果トランジスタを製造すれば、バッファ層と窒化物系III−V族化合物半導体層との界面に高濃度のn型層ができることがないので、n型層と電流が流れる通路であるチャネル層との間で生じるパラレル伝導がおこることがない。このことから、窒化物系III−V族化合物半導体装置の大電流化を実現できる。尚、上記パラレル伝導は、2次元電子ガスによるチャネル層およびバッファ層と窒化物系III−V族化合物半導体層との界面に存在する高濃度のn型層の2つの経路を電流が流れるという現象である。このパラレル伝導が発生すると、トランジスタのピンチオフが十分に起こらないという問題が発生する。

【0015】

また、一実施形態の窒化物系III−V族化合物半導体装置の製造方法は、上記熱処理工程の温度は、熱処理工程よりも前に形成された窒化物系III−V族化合物半導体層の成長温度よりも大きく、かつ、上記成長温度に200℃を加えた温度よりも小さいことを特徴としている。

【0016】

上記実施形態によれば、上記熱処理工程では、熱処理工程よりも前に形成された窒化物系III−V族化合物半導体層の成長温度よりも高く、かつ、熱処理工程よりも前の窒化物系III−V族化合物半導体層の成長温度に200℃を加えた温度よりも低い温度で、熱処理を行うので、窒化物系III−V族化合物半導体層の転位を減少させて転位密度を低減できる。

【0017】

本発明者は、熱処理工程の温度を成長温度と同じ、成長温度±100℃、±200℃、成長温度+250℃で行い、その転位密度と結晶性がどのように変化するかをTEMによって評価した。また、熱処理後の表面状態を走査型電子顕微鏡(SEM)により評価した。

【0018】

このとき、上記熱処理工程の熱処理温度が、熱処理工程よりも前に形成された窒化物系III−V族化合物半導体層の成長温度よりも低い温度になると、熱処理工程の前にGa層の堆積と窒化物系III−V族化合物半導体層の成長を行う場合には、この熱処理工程で、積層されたGa層のGaを窒化物系III−V族化合物半導体層に十分に拡散させて、窒化物系III−V族化合物半導体層の転位を消滅させることができず、また、熱処理工程の前にイオン打ち込み工程を行う場合には、イオンを打ち込むことによって、生成した上記アモルファス層上の窒化物系III−V族化合物半導体層の再結晶化を十分に行うことができず、この窒化物系III−V族化合物半導体層の転位を十分に減少させることができなかった。一方、熱処理工程の熱処理温度が、熱処理工程よりも前に形成された窒化物系III−V族化合物半導体層の成長温度に200℃を加えた温度よりも高い温度になると、窒化物系III−V族化合物半導体層の蒸発が発生した。

【発明の効果】

【0019】

本発明の窒化物系III−V族化合物半導体装置の製造方法によれば、窒化物系III−V族化合物半導体からなるバッファ層の上方の窒化物系III−V族化合物半導体層の転位を小さくできて、このバッファ層の上方の窒化物系III−V族化合物半導体層の移動度等の電気的特性を優れたものにすることができる。したがって、この転位が小さくて電気的特性に優れた窒化物系III−V族化合物半導体層を有するHFET等の窒化物系III−V族化合物半導体装置の移動度や高周波特性等の電気的特性を優れたものにすることができる。

【図面の簡単な説明】

【0020】

【図1】第1の参考例の窒化物系III−V族化合物半導体装置の製造方法の製造工程の原理を説明する模式図である。

【図2】第2の参考例の窒化物系III−V族化合物半導体装置の製造方法の製造工程の原理を説明する模式図である。

【図3】本発明の窒化物系III−V族化合物半導体装置の製造方法の製造工程の原理を説明する模式図である。

【図4】第1参考例の窒化物系III−V族化合物半導体装置の製造方法の製造工程を示す図である。

【図5】第2参考例の窒化物系III−V族化合物半導体装置の製造方法の製造工程の一部を示す図である。

【図6】図5に続く窒化物系III−V族化合物半導体装置の製造方法の製造工程の一部を示す図である。

【図7】本発明の第1実施形態の窒化物系III−V族化合物半導体装置の製造方法の製造工程の一部を示す図である。

【図8】図7に続く窒化物系III−V族化合物半導体装置の製造方法の製造工程の一部を示す図である。

【図9】窒化物系III−V族化合物半導体装置のキャリア濃度と移動度との関係を示す図である。

【図10】窒化物系III−V族化合物半導体装置の一例としてのHEMT(高電子移動度トランジスタ)の構造を示す図である。

【発明を実施するための形態】

【0021】

以下、本発明を図示の実施の形態により詳細に説明する。

【0022】

先ず、図1〜図3を用いて3通りの窒化物系III−V族化合物半導体装置の製造方法の原理を簡単に説明する。

【0023】

図1は、第1の参考例の窒化物系III−V族化合物半導体装置の製造方法の原理を説明するための図であり、図2は、第2の参考例の窒化物系III−V族化合物半導体装置の製造方法の原理を説明するための図であり、図3は、本発明の窒化物系III−V族化合物半導体装置の製造方法の原理を説明するための図である。図1〜図3では、転位を模式的に縦線で表す。尚、図1〜図3では、バッファ層以下の層の図示を省略している。また、図1〜図3と、以下に示す図4〜図8および図10は模式図であり、図1〜図8および図10に示される各層の膜厚は、実際の装置における各層の膜厚と異なっている。

【0024】

第1の参考例の窒化物系III−V族化合物半導体装置の製造方法は、図1(A)に示すように、基板(図示せず)の上方に形成した転位のあるバッファ層1上にGa層2を堆積し、その後、Ga層2の上方から窒素源(以下、N源という)を照射する。このとき、上記N源の照射によって、上記Ga層2が再構築され、図1(B)に示すGaN層3として再結晶化する。このとき、上記GaN層3は、ランダムに結晶化するのではなく下地のバッファ層1の影響を受けて下地と同じ構造で再結晶化するが、GaN層の下層部4ではGa原子が転位を終焉させるため、バッファ層1の転位情報がGaN層の上層部5に伝えられることがない。このことから、GaN層の上層部5の上に成長させる窒化物系III−V族化合物半導体層の転位密度を減少させることができて、上記窒化物系III−V族化合物半導体層の結晶構造を、移動度等の電気的特性に優れた良好なものにすることができる。

【0025】

また、第2の参考例の窒化物系III−V族化合物半導体装置の製造方法は、図2(A)に示すように、基板(図示せず)の上方に形成した転位のあるバッファ層21上にGa層22を堆積し、さらに引き続いてGa層22上に、例えばGaN等の窒化物系III−V族化合物半導体層23を成長させる。次に、熱処理を行って、Ga層22の余分なGaが転位部分を通って表面から蒸発するまで、Ga層22中のGaを上方の窒化物III−V族化合物半導体層23の方に移動させて、Ga層22中の蒸発しなかったGaを、窒化物III−V族化合物半導体層23の転位付近に留まらせる。そして、上記窒化物III−V族化合物半導体層23の転位付近に留まらせたGaで、GaN等の窒化物III−V族化合物半導体層23の転位を消滅させて、図2(B)に示すように、Ga層22および窒化物III−V族化合物半導体層23を、転位が少なくて電気的特性に優れた良質な窒化物III−V族化合物半導体層25にする。

【0026】

また、本発明の窒化物系III−V族化合物半導体装置の製造方法は、図3(A)に示すように、基板(図示せず)の上方に形成した転位のあるバッファ層31上にバッファ層31よりも少ないものの多くの転位を内包しているGaN等の窒化物系III−V族化合物半導体層32を形成し、次に、上記バッファ層31と窒化物系III−V族化合物半導体層32との界面付近にイオンを注入して、図3(B)に示すように、上記界面付近にアモルファス層35を形成する。次に、熱処理を行って、アモルファス層35の一部およびアモルファス層35上の窒化物系III−V族化合物半導体層32とを再結晶化して、図3(C)に示すように、熱処理の後も残留しているアモルファス層35上の再結晶層37の転位を減少させて、この再結晶層37の結晶性を電気的特性に優れた良質なものにする。

【0027】

以下に、上記第1の参考例を、第1参考例で、上記第2の参考例を、第2参考例で、上記本発明を、第1実施形態で詳細に説明することにする。

【0028】

(第1参考例)

図4に、第1参考例の窒化物系III−V族化合物半導体装置の製造方法を示す。尚、図4においても図1〜図3と同様に、転位を縦線で模式的に示すものとする。

【0029】

先ず、基板酸化膜除去工程で、SiC基板41の基板温度を約1000℃まで上げて、SiC基板41の表面酸化膜を除去した後、バッファ層形成工程を行う。このバッファ層形成工程では、成長温度を800℃、Alビーム強度を2.0×10-7Torr、RF入力電力を200W、窒素流量を1.4sccmに夫々設定して、図4(A)に示すように、上記表面酸化膜が除去されたSiC基板41上に、膜厚が20nmのAlNのバッファ層42を形成する。

【0030】

次に、Ga堆積工程を行う。このGa堆積工程では、Gaビームの強度を6.0×10-7Torrに設定して、Gaビームを10秒間AlNのバッファ層42に照射することにより、図4(B)に示すように、AlNのバッファ層42上に膜厚が1nmのGa層43を形成する。尚、図4で、バッファ層42およびGa層43等に引かれた縦線は、バッファ層42およびGa層43等に存在する転位(ダングリングボンド(線欠陥))を模式的に表わしたものである。図4(B)において、Ga層43に引かれた縦線の数は、バッファ層42に引かれた縦線の数よりも少なくなっており、かつ、Ga層43に引かれた縦線は、バッファ層42に引かれた縦線につながっている。これは、Ga層43に生じる転位は、バッファ層42に生じる転位よりも少なく、かつ、バッファ層42の転位に引きずられて生成することを模式的に示すものである。

【0031】

引き続いて、RF入力電力を300W、窒素流量を2.0sccm、基板温度を略750℃に夫々設定して、結晶化工程を行う。この結晶化工程では、図4(B)に示すGa層43の上方から窒素をGa層43に照射してGa層43を結晶化する。

【0032】

このことにより、結晶化工程の前に、図4(B)で参照番号43で示されたGa層は、結晶化工程後に、図4(C)に示すように、GaN層の下層部44と、GaN層の上層部45に再構築される。結晶化工程でN源を照射して結晶化が行われたことにより、GaN層の下層部44の転位の数は、少なくなり(図4(B)でGa層43に4つ存在していた転位を、図4(C)に示すGaN層の下層部44では2つにし、このことを模式的に示している)、また、GaN層の上層部45は、転位の数がGaN層の下層部44の転位の数よりも更に少ない結晶構造が優れた層になる(図4(C)に示すGaN層の上層部45では、転位を0とし、このことを模式的に示している)。結晶化工程の後、GaN層の下層部44と、GaN層の上層部45のGa元素と窒素元素の化学量論比(Ga元素/窒素元素)は、1以上かつ1.5以下の値になっている。

【0033】

最後に、化合物半導体成長工程を行う。この化合物半導体成長工程では、基板温度を750℃、Gaビーム強度を6.0×10-7Torr、RF入力電力を450W、窒素流量を2.2sccmに夫々設定して、GaN層の上層部45に、Gaビームと窒素を照射して、図4(D)に示すように、GaN層の上層部45上に膜厚が2μmのGaN層46を形成して、第1参考例の窒化物系III−V族化合物半導体装置の要部の製造を完了する。

【0034】

上記第1参考例の窒化物系III−V族化合物半導体装置の製造方法を用いて、GaN層を備えた窒化物系III−V族化合物半導体装置を作製した場合と、通常のプラズマ励起窒素を用いた分子線エピタキシー法(RF-MBE法)を用いて、バッファ層上にGaN層を直接成長させた窒化物系III−V族化合物半導体装置を作成した場合の2通りについて、窒化物系III−V族化合物半導体装置のGaN層の電気的特性と転位密度を比較する実験を行った。

【0035】

その実験の結果、通常の方法でGaNを成長させた場合には、GaNの転位密度が2×1010cm-2前後の値になり、キャリア濃度が1×1019cm-3の場合に、移動度が98cm2/Vsの前後の値になった。また、キャリア濃度が1×1016cm-3の場合に、移動度が30cm2/Vsの前後の値になった。

【0036】

一方、上記第1参考例の方法でGaN層を成長させた場合には、GaN層の転位密度が、3×104cm-2前後の値になって、通常の方法でGaNを成長させた場合の2×1010cm-2前後の値よりも大幅に小さくなり、GaN層の結晶構造が結晶性に優れたものになった。また、上記第1参考例の方法でGaN層を成長させた場合には、キャリア濃度が1×1019cm-3の場合には、GaN層の移動度が100cm2/Vsになって、GaN層が通常の方法で形成されたGaN層の電気的特性と同等の電気的特性を示す一方、キャリア濃度が1×1016cm-3の場合には、移動度が1500cm2/Vsと非常に大きな値になって、上記第1参考例の方法で形成されたGaN層の電気特性が、通常の方法で形成されたGaN層と比べてはるかに優れたものになった。

【0037】

上記第1参考例の窒化物系III−V族化合物半導体装置の製造方法によれば、バッファ層形成工程でSiC基板41上に形成した転位のあるAlNのバッファ層42に、Ga堆積工程でGa層43を堆積して、更に、結晶化工程でGa層43の表面にN源を照射してGa層43の結晶化を行うので、N源の照射を行う結晶化工程の後、バッファ層42上に形成されるGaN層の下層部44の結晶構造が、転位(ダングリングボンド(線欠陥))が消滅した高品質な結晶構造になる。したがって、GaN層の下層部44のGaNの結晶構造が、ダングリングボンドが解消された高品質なものになるため、GaN層の上層部45まで、バッファ層42のダングリングボンドの情報が到達して転位情報が及ぶことを防止でき、GaN層の上層部45に、下地のバッファ層42の転位情報以外の情報のみを伝達することができる。つまり、GaN層の上層部45の結晶構造を転位がないバッファ層42の結晶構造と略同一な構造にすることができる。したがって、化合物半導体成長工程で、この転位が少ない良質のGaN層の上層部45の上に、転位密度が低いGaN層46を形成することができて、上記第1参考例の窒化物系III−V族化合物半導体装置の製造方法を用いて形成した窒化物系III−V族化合物半導体装置の移動度等の電気的特性を優れたものにすることができる。

【0038】

また、上記第1参考例の窒化物系III−V族化合物半導体装置の製造方法によれば、Ga堆積工程で堆積されるGa層43の厚さを、1nmにしたので、Ga層43上のGaN層46の転位を十分に消滅させることができると共に、Ga層43上のGaN層46の結晶性を良質なものにすることができる。

【0039】

尚、上記第1参考例では、SiC基板41を用いたが、SiC基板の代わりにサファイア基板やSi基板等のSiC基板以外の基板を用いても良い。

【0040】

また、上記第1参考例では、SiC基板41にAlNのバッファ層42を成長させたが、AlNのバッファ層に限らず、基板上にGaNのバッファ層やInNのバッファ層等の窒化物系III−V族化合物半導体のバッファ層を成長させても良い。

【0041】

また、上記第1参考例では、化合物半導体成長工程で、結晶化したGaN層の上層部45上にGaN層46を成長させたが、化合物半導体成長工程では、GaN層に限らず、結晶化したGaN層の上層部上にAlN層やInN層等の窒化物系III−V族化合物半導体層を成長させても良い。

【0042】

また、上記第1参考例では、Ga堆積工程で、AlNのバッファ層42上に膜厚が1nmのGa層43を形成したが、Ga堆積工程で、窒化物系III−V族化合物半導体のバッファ層上に、膜厚が0.1nm以上かつ10nm以下の厚さを有するGa層を形成しても良い。尚、窒化物系III−V族化合物半導体のバッファ層上に、膜厚が0.1nm以上かつ10nm以下の厚さを有するGa層を形成した場合においても、膜厚が1nmのGa層43を形成した場合と同様に、Ga層上の窒化物系III−V族化合物半導体の転位を十分に消滅させることができて、Ga層上の窒化物系III−V族化合物半導体の結晶性を良質なものにすることができる。

【0043】

(第2参考例)

図5および図6に、第2参考例の窒化物系III−V族化合物半導体装置の製造方法を示す。尚、図5および図6おいても図4と同様に、転位を縦線で模式的に示すものとする。

【0044】

先ず、基板酸化膜除去工程で、SiC基板51の基板温度を1000℃まで上げて、SiC基板51の表面酸化膜を除去した後、バッファ層形成工程を行う。このバッファ層形成工程では、成長温度を800℃、Alビーム強度を2.0×10-7Torr、RF入力電力を200W、窒素流量を1.4sccmに夫々設定して、図5(A)に示すように、上記表面酸化膜が除去されたSiC基板51上に、膜厚が20nmのAlNのバッファ層52を形成する。

【0045】

次に、Ga堆積工程を行う。このGa堆積工程では、Gaビームの強度を6.0×10-7Torrに設定して、このGaビームを10秒間AlNのバッファ層52に照射することにより、図5(B)に示すように、AlNのバッファ層52上に膜厚が1nmのGa層53を形成する。

【0046】

引き続いて、第1化合物半導体成長工程を行う。この第1化合物半導体成長工程では、基板温度を750℃、Gaビーム強度を6.0×10-7Torr、RF入力電力を450W、窒素流量を2.2sccmに夫々設定して、図5(C)に示すように、Ga層53上に厚さが20nmのGaN層54を形成する。

【0047】

次に、基板温度800℃まで上げて熱処理工程を行う。この熱処理工程では、Ga堆積工程で堆積させたGaを、図5(C)に示すGaN層54の転位を介してGaN層54の転位部分に移動させ、余分なGaをこの転位部分を通じてGaN層54の表面から蒸発させる。このとき、Ga堆積工程で堆積させたGaのうちで、表面から蒸発しなかったGaは、図5(C)に示すGaN層54の転位部分付近に留まる。そして、この図5(C)に示すGaN層54の転位部分付近に留まったGaは、図5(C)に示すGaN層54の転位を消滅させ、図5(C)に示すGaN層54を、図6(A)に示す転位が少ない良質なGaN層55にかえる。尚、上記熱処理工程では、Ga堆積工程で堆積させたGaを、GaN層54に移動させるので、熱処理工程の後、Ga層53は、消滅することになる。上記熱処理工程の後、上記転位が少なく良質なGaN層55のGa元素と窒素元素の化学量論比(Ga元素/窒素元素)は、1以上かつ1.5以下の値になっている。

【0048】

最後に、第2化合物半導体成長工程を行う。この第2化合物半導体成長工程では、基板温度を750℃、Gaビーム強度を6.0×10-7Torr、RF入力電力を450W、窒素流量を2.2sccmに夫々設定して、図6(B)に示すように、上記転位が少ない良質なGaN層55上に厚さが2μmのGaN層56を成長させて、第2参考例の窒化物系III−V族化合物半導体装置の要部の製造を終了する。

【0049】

上記第2参考例の窒化物系III−V族化合物半導体装置の製造方法を用いて作成した窒化物系III−V族化合物半導体装置の要部のGaN層56の電気的特性および転位密度と、通常のプラズマ励起窒素を用いた分子線エピタキシー法(RF-MBE法)を用いてバッファ層上に直接成長させたGaN層の電気的特性および転位密度とを比較する実験を行った。

【0050】

上記実験の結果、上記第2参考例の方法でGaN層56を成長させた場合には、GaN56の転位密度が、2×104cm-2前後の値になって、通常の方法でGaNを成長させた場合の転位密度の値である2×1010cm-2前後の値よりも大幅に小さくなった。

【0051】

また、上記第2参考例の方法でGaN層56を成長させた場合には、GaN層56のキャリア濃度が1×1019cm-3のときに、GaN層56の移動度が95cm2/Vsになって、GaN層56の電気的特性が通常の方法で形成されたGaN層の電気的特性と略同等の電気的特性を示す一方、GaN層56のキャリア濃度が1×1016cm-3のときに、GaN層56の移動度が1450cm2/Vsと非常に大きな値になって、GaN層56の電気的特性が、通常の方法で形成されたGaN層の電気的特性と比較してはるかに優れたものになった。

【0052】

上記第2参考例によれば、熱処理工程で熱処理を行うので、Ga堆積層のGaの一部を、図5(C)に示すGaN層54の転位部分を通って表面から蒸発させることができると共に、Ga層のGaの残りを、図5(C)に示すGaN層54の転位付近に移動させて、図5(C)に示すGaN層54の転位を消滅させることができる。すなわち、図5(C)に示す転位が多いGaN層54を、図6(A)に示す転位の少ない良質なGaN層55に再構築できるので、第2化合物半導体成長工程で、この転位の少ない良質なGaN層55上に形成するGaN層56の結晶性を、転位が少ない良質なものにできる。したがって、窒化物系III−V族化合物半導体装置の移動度等の電気的特性を優れたものにできる。

【0053】

また、上記第2参考例によれば、Ga堆積工程で堆積されるGa層53の厚さを1nmにしたので、Ga層53の上方のGaN層56の転位を十分に消滅させることができると共に、Ga層53の上方のGaN層56の結晶性を良質なものにすることができる。

【0054】

また、上記第2参考例によれば、熱処理工程では、第1化合物半導体成長工程の基板温度である750℃よりも高く、かつ、第1化合物半導体成長工程の基板温度である750℃に200℃を加えた温度である950℃よりも低い800℃で熱処理を行うので、GaN層54の蒸発が起きない状態で、Gaの拡散を十分に行うことができて、GaN層54の再結晶化を十分に行うことができる。したがって、熱処理を行ったGaN層54の転位を十分に減少させてGaN層54の転位密度を大幅に低減できる。

【0055】

尚、上記第2参考例では、SiC基板51を用いたが、SiC基板51の代わりにサファイア基板やSi基板等のSiC基板以外の基板を用いても良い。

【0056】

また、上記第2参考例では、SiC基板51上にAlNのバッファ層52を成長させたが、AlNのバッファ層に限らず、基板上にGaNのバッファ層やInNのバッファ層等の窒化物系III−V族化合物半導体のバッファ層を成長させても良い。

【0057】

また、上記第2参考例では、熱処理工程の後に、GaN層56を成長させたが、GaN層に限らず、熱処理工程の後に、AlN層やInN層等の窒化物系III−V族化合物半導体層を成長させても良い。

【0058】

また、上記第2参考例では、Ga堆積工程で、AlNのバッファ層52上に膜厚が1nmのGa層53を形成したが、Ga堆積工程で、窒化物系III−V族化合物半導体のバッファ層上に、膜厚が0.1nm以上かつ10nm以下の厚さを有するGa層を形成しても良い。そして、窒化物系III−V族化合物半導体のバッファ層上に、膜厚が0.1nm以上かつ10nm以下の厚さを有するGa層を形成した場合においても、膜厚が1nmのGa層53を形成した場合と同様に、Ga層上の窒化物系III−V族化合物半導体の転位を十分に消滅させることができると共に、Ga層上の窒化物系III−V族化合物半導体の結晶性を良質なものにすることができる。

【0059】

また、上記第2参考例では、基板温度を800℃まで上げて熱処理工程を行ったが、第1化合物半導体成長工程の基板温度である750℃よりも大きくて、かつ、第1化合物半導体成長工程の基板温度である750℃に200℃を加えた950℃よりも小さい温度に基板温度を設定して熱処理工程を行っても、基板温度を800℃まで上げて熱処理工程を行った場合と同様の作用効果を奏することが確認されている。尚、950℃以上の温度に基板温度を設定して熱処理工程を行うと、GaN層54の蒸発が起こって、窒化物系III−V族化合物半導体装置の品質が低下することになり、750℃以下の温度に基板温度を設定して熱処理工程を行うと、Gaの拡散を十分に行うことができなくなる。

【0060】

(第1実施形態)

図7および図8に、本発明の第1実施形態の窒化物系III−V族化合物半導体装置の製造方法を示す。尚、図7および図8においても図4、図5および図6と同様に、転位を縦線で模式的に示すものとする。

【0061】

先ず、基板酸化膜除去工程で、SiC基板71の基板温度を1000℃まで上げて、SiC基板71の表面酸化膜を除去した後、バッファ層形成工程を行う。このバッファ層形成工程では、成長温度を800℃、Alビーム強度を2.0×10-7Torr、RF入力電力を200W、窒素流量を1.4sccmに夫々設定して、図7(A)に示すように、SiC基板71上に、膜厚が20nmのAlNのバッファ層72を形成する。

【0062】

次に、化合物半導体成長工程を行う。この化合物半導体成長工程では、基板温度を750℃、Gaビーム強度を6.0×10-7Torr、RF入力電力を450W、窒素流量を2.2sccmに夫々設定して、図7(B)に示すようように、AlNのバッファ層72上に厚さが20nmのGaN層73を成長させる。

【0063】

引き続いて、イオン打ち込み工程を行う。このイオン打ち込み工程では、イオン注入原子としてGaを用い、このGaイオンの加速電圧20keV、このGaイオンの注入量を1×1018cm-3に設定して、AlNのバッファ層72とGaN層73の界面近傍に、Gaイオンを打ち込んで、図7(C)に示すように、AlNのバッファ層72とGaN層73の界面付近にアモルファスの層74を形成して、アモルファスの層74によりAlNのバッファ層72とGaN層73とを切り離す。

【0064】

次に、熱処理工程を行う。この熱処理工程では、基板温度を800℃まで上げて熱処理を行うことにより、図7(C)に示すアモルファスの層74の上のGaN層73を再結晶化して、図8(A)に示すように、転位が少ないGaN層75層を形成する。この熱処理工程を行った後、Gaイオンが打ち込まれて形成されたアモルファスの層74の膜厚は、図8(A)に示すように、小さくはなるが一部は残留する。図8(A)に示すこの残留したアモルファスの層74では、Ga元素と窒素の化学量論比(Ga元素/窒素)が1以上かつ1.5以下の値になっている。

【0065】

最後に、第2化合物成長工程を行う。この第2化合物成長工程では、基板温度を750℃、Gaビーム強度を6.0×10-7Torr、RF入力電力を450W、窒素流量を2.2sccmに夫々設定して、図8(B)に示すように、転位が少ないGaN層75層上に厚さが2μmのGaN層76を成長させる。このようにして、第1実施形態の窒化物系III−V族化合物半導体装置の要部の製造を終了する。

【0066】

上記第1実施形態の窒化物系III−V族化合物半導体装置の製造方法を用いて作成した窒化物系III−V族化合物半導体装置の要部のGaN層76の電気的特性および転位密度と、通常のプラズマ励起窒素を用いた分子線エピタキシー法(RF-MBE法)を用いてバッファ層上に直接成長させたGaN層の電気的特性および転位密度とを比較する実験を行った。

【0067】

上記実験の結果、上記第1実施形態の窒化物系III−V族化合物半導体装置の製造方法でGaNを成長させた場合には、GaNの転位密度が、4×104cm-2前後の値になって、通常の方法でGaNを成長させた場合の2×1010cm-2前後の値よりも大幅に小さくなった。

【0068】

また、上記第1実施形態の方法でGaN層76を成長させた場合には、GaN層76のキャリア濃度が1×1019cm-3のときに、GaN層76の移動度が103cm2/Vsになって、GaN層76の電気的特性が通常の方法で形成されたGaN層の電気的特性と略同等の電気的特性を示す一方、GaN層76のキャリア濃度が1×1016cm-3のときに、GaN層76の移動度が1480cm2/Vsと非常に大きな値になって、GaN層76の電気的特性が、通常の方法で形成されたGaN層の電気的特性と比べてはるかに優れたものになった。

【0069】

上記第1実施形態によれば、上記バッファ層形成工程で、SiC基板71上に形成したAlNからなるバッファ層72と、上記化合物半導体成長工程でAlNのバッファ層72上に成長させたGaN層73との界面付近に、イオン打ち込み工程で、Gaイオンを打ち込むので、AlNのバッファ層72とGaN層73の界面付近にアモルファスの層74を形成できて、AlNのバッファ層72とGaN層73とを切り離して、AlNのバッファ層72の転位情報が、GaN層73に伝わらないようにすることができる。また、次に行われる熱処理工程で、熱処理を行うことで、アモルファスの層74上のGaN層73を再結晶化して、図7(C)に示す転位が多いGaN層73を図8(A)に示す転位が少ないGaN層75に作りかえることができる。したがって、この転位が少ないGaN層75上に結晶性が良いGaN層76を形成できて、第1実施形態の窒化物系III−V族化合物半導体装置の要部を用いて作成された窒化物系III−V族化合物半導体装置の電気的特性を優れたものにできる。

【0070】

また、上記第1実施形態によれば、上記イオン打ち込み工程で、AlNのバッファ層72とGaN層73との界面付近にGaイオンを打ち込んだので、AlNのバッファ層とGaN層との界面付近にSiイオンを注入した場合のように、界面付近に高濃度のn型層ができることがない。したがって、例えば、上記第1実施形態の窒化物系III−V族化合物半導体装置の製造方法を用いて電界効果トランジスタを製造しても、AlNのバッファ層72とGaN層73との界面に高濃度のn型層ができることがなくて、このn型層が、電流が流れる通路であるチャネル層とパラレル伝導を引き起こすことがない。このことから、上記第1実施形態の窒化物系III−V族化合物半導体装置の製造方法を用いて製造された窒化物系III−V族化合物半導体装置の大電流化を実現できる。

【0071】

また、上記第1実施形態によれば、熱処理工程では、第1化合物半導体成長工程の基板温度である750℃より高く、かつ、第1化合物半導体成長工程の基板温度である750℃に200℃を加えた950℃よりも低い800℃で熱処理を行うので、GaN層73の再蒸発が起きない状態で、アモルファスの層74上のGaN層73の再結晶化を十分に行うことができて、再結晶化を行って形成したGaN層75の転位密度を低減できる。したがって、GaN層75上に形成したGaN層76の結晶性を更に優れたものにできる。

【0072】

尚、上記第1実施形態では、SiC基板71を用いたが、SiC基板71の代わりにサファイア基板やSi基板等のSiC基板以外の基板を用いても良い。

【0073】

また、上記第1実施形態では、SiC基板71上にAlNのバッファ層72を成長させたが、AlNのバッファ層に限らず、基板上にGaNのバッファ層やInNのバッファ層等の窒化物系III−V族化合物半導体のバッファ層を成長させても良い。

【0074】

また、上記第1実施形態では、化合物半導体成長工程で、AlNのバッファ層72上にGaN層73を成長させたが、GaN層に限らず、化合物半導体成長工程で、AlN等の窒化物系III−V族化合物半導のバッファ層上にAlN層やInN層等の窒化物系III−V族化合物半導体層を成長させても良い。

【0075】

また、上記第1実施形態では、イオン打ち込み工程で、AlNのバッファ層72とGaN層73の界面近傍に、Gaイオンを注入して、アモルファスの層74を形成したが、Gaイオンの代わりに、Cイオン、Nイオン、Mgイオン、Alイオン、ZnイオンおよびInイオンの内の1つを打ち込んでも、Gaイオンを打ち込んだときと同様の作用効果を奏する。また、Cイオン、Nイオン、Mgイオン、Alイオン、Znイオン、GaイオンおよびInイオンの内の任意の2つ以上のイオンを打ち込んでもGaイオンを打ち込んだときと同様の作用効果を奏する。

【0076】

また、上記第1実施形態では、基板温度を800℃まで上げて熱処理工程を行ったが、熱処理工程で使用される基板温度は、800℃に限定されるものではなくて、熱処理工程で使用される基板温度は、AlNの成長温度である750℃よりも高く、かつ、AlNの成長温度である750℃に200℃を加えた温度である950℃よりも低い温度であれば、どのような温度であっても良い。そして、この範囲の基板温度で、熱処理工程を行えば、基板温度を800℃まで上げて熱処理工程を行った場合と同様の作用効果を奏することが確認されている。尚、950℃以上の温度に基板温度を設定して熱処理工程を行うと、GaN層73の蒸発が起こって、窒化物系III−V族化合物半導体装置の品質が低下することになり、750℃以下の温度に基板温度を設定して熱処理工程を行うと、GaN層73の再結晶化を十分に行うことができなくなる。

【0077】

表1に、通常の窒化物系III−V族化合物半導体装置の製造方法と、第1参考例、第2参考例および第1実施形態の窒化物系III−V族化合物半導体装置の製造方法で作製された4通りの窒化物系III−V族化合物半導体装置の要部における最上層のGaN層の転位密度と、キャリア濃度が1×1019cm-3のときの上記GaN層の移動度と、キャリア濃度が1×1016cm-3のときの上記GaN層の移動度を示す。

【0078】

【表1】

【0079】

表1に示すように、1×1019cm-3の高キャリア濃度の場合、どの方法で窒化物系III−V族化合物半導体装置を形成しても、GaN層の移動度は、略100cm2/Vs前後の値になり、4つの方法でGaN層の電気的特性に違いが見られない。一方、1×1016cm-3の低キャリア濃度の場合、通常の方法で製作されたGaN層の移動度と、他の3つの方法(すなわち、第1参考例、第2参考例および第1実施形態の方法)で製作されたGaN層の移動度との間に、顕著な違いが見られる。

【0080】

図9に、通常の窒化物系III−V族化合物半導体装置の製造方法と、第1参考例、第2参考例および第1実施形態の窒化物系III−V族化合物半導体装置の製造方法で作製された4通りの窒化物系III−V族化合物半導体装置のGaN層のキャリア濃度と移動度との関係を示す。

【0081】

図9に示す丸印は、通常の窒化物系III−V族化合物半導体装置の製造方法を用いた場合の計測点であり、表1の結果をプロットしたものである。一方、図9に示す四角印は、第1参考例、第2参考例および第1実施形態の窒化物系III−V族化合物半導体装置の製造方法を用いた場合の計測点であり、表1の結果をプロットしたものである(図9の縮尺の尺度では、第1参考例、第2参考例および第1実施形態の違いを示せず、3つの発明は図上で同じ点をさす)。

【0082】

図9に示すように、キャリア濃度が1×1017.3cm-3以上の領域においては、同じキャリア濃度に対する移動度が、4つの方法で同等になっており、キャリア濃度が下がるにつれて、移動度が増加していることがわかる。

【0083】

一方、キャリア濃度が下がって1×1017.3cm-3に達すると、図9に示すように、通常の方法の移動度と、上記3つの方法(第1参考例、第2参考例、第1実施形態の方法)の移動度とが分岐することがわかる。詳細には、キャリア濃度が1×1015cm-3以上で1×1017.3cm-3未満の領域においては、通常の方法では、キャリア濃度が下がるにつれて、移動度も減少するのに対し、上記3つの方法では、キャリア濃度が下がるにつれて、移動度が増加していることがわかる。つまり、通常の方法と、上記3つの方法とで、移動度の振る舞いに大きな違いが生じていることがわかる。

【0084】

これは、GaN層の移動度μが、以下の式(1)に示すように、キャリア濃度nの1.5乗と転位密度Ndisl.により決定されるからである。

【0085】

【数1】

【0086】

詳細には、キャリア濃度が大きい場合には、キャリア濃度nの1.5乗の値が大きくなるので、GaNの移動度μは、上記式(1)により、主にキャリア濃度nの1.5乗の因子によって決定される。これは、キャリア濃度が大きくなるとキャリア同士の衝突が頻繁に起こって、キャリア‐キャリア散乱で移動度μが決定されることを意味している。つまり、キャリア濃度が1×1019cm-3等の大きな領域では、移動度μは、nの1.5乗の値だけで略決定され、転位密度Ndislの影響を受けにくくなる。これが、キャリア濃度が1×1019cm-3で、移動度μが、いずれの方法でも100cm2/Vs前後の値になることの理由である。

【0087】

一方、キャリア濃度が1×1016cm-3等の小さい領域では、式(1)の分子の値が小さくなり、移動度μは転位密度Ndislの影響を大きく受けることになる。これが、キャリア濃度が1×1016cm-3では、転位が多い通常の成長法では移動度が30cm2/Vs程度にしかならない一方、転位が少ない本発明の方法では移動度が1500cm2/Vs程度の大きな値になることの理由である。つまり、本発明の方法で作成したGaN層では、通常の成長法とは異なり、キャリア濃度が1012cm-3程度以下にならないと転位が支配的な領域には入らないのである。すなわち、本発明の方法を用いれば、転位が少ないGaN層を形成できるので、キャリア濃度が小さい領域においても、大きな移動度μを得ることができるのである。

【0088】

図10に、窒化物系III−V族化合物半導体装置の一例としてのHEMT(高電子移動度トランジスタ)の構造を示す。

【0089】

図10において、101はサファイア基板の(0001)面、102は低温成長させた膜厚20nmのGaNバッファ層、103はGaN層(バックグラウンドキャリア濃度1016cm-3以下、膜厚3μm)、104はAl0.25Ga0.75N層(膜厚30nm)、105はHf(ハフニウム)ソース/ドレイン電極、106はPd(パラジウム)ゲート電極である。

【0090】

次に、図10に示す層構造を有するHEMT(高電子移動度トランジスタ)を、MOCVD法を用いた通常の方法およびMOCVD法を用いた第1参考例、第2参考例および第1実施形態の方法で作成し、4つのHEMTのヘテロ構造特性およびHEMT特性を比較した。

【0091】

以下に、4つのHEMTの作製法について要点のみ簡単に述べる。

【0092】

初めに、通常の場合には、先ず、水素雰囲気中でサファイア基板の基板温度を1100℃にして、サファイア基板の酸化膜を除去するクリーニングを10分間行った後、サファイア基板の基板温度を500℃、Ga原料流量(トリメチルガリウムTMG)の流量を10sccm、HN3の流量を5slmに夫々設定してGaNバッファ層を成長させる。

【0093】

次に、基板温度を1000℃、Ga原料(トリメチルガリウムTMG)の流量を40sccmに設定して、GaN層を成長させた後、基板温度を1000℃、トリメチルアルミニウム(TMA)流量を5sccm、TMGの流量を25sccm、NH3の流量を6slmに夫々設定してAl0.25Ga0.75N層を成長させる。

【0094】

最後に、Al0.25Ga0.75N層にHf(ハフニウム)ソース/ドレイン電極、Pd(パラジウム)ゲート電極を形成してHEMTが作製される。

【0095】

次に、第1参考例の方法では、GaNバッファ層成長後にTMGのみを流してGaを堆積して温度を上げながら窒素源としてのNH3を流してGaを結晶化する。

【0096】

また、第2参考例の方法では、バッファ層成長後にTEGのみを流してGaを堆積した後、引き続いて成長温度を500℃にして20nm程度のGaN層を形成する。その後、基板温度を上げてGaNを成長させて、成長中断後に基板温度を1050℃に上げて1分間熱処理し、引き続いて1000℃でへテロ構造を成長させる。

【0097】

最後に、本発明の第1実施形態の方法では、低温バッファ層成長後にGaN層を成長させた後、イオン注入を行う。その後、1050℃で1分間の熱処理を行い、この熱処理に引き続いて1000℃でヘテロ構造を形成する。

【0098】

尚、上記4つの方法では、ゲート長Lgが0.1μm、ゲート幅Wgが200μmのHEMTを製造した。

【0099】

表2に、従来の方法と、第1参考例、第2参考例および第1実施形態の方法で製造した4つのHEMTの特性比較結果を示す。

【0100】

【表2】

【0101】

尚、表2において、DC/RF分散率は、直流印加時の特性と高周波印加時の特性の変化率であり、この値が小さいと、HEMT特性は、高周波応用に優れたものになる。

【0102】

表2に示すように、通常の方法と上記3つの方法(第1参考例,第2参考例および第1実施形態の方法)では、転位密度が2桁程度異なっているが、ヘテロ構造の電気的特性を示す移動度、HEMT特性である相互コンダクタンスgmおよび最大発信周波数fmaxに大きな違いは見られない。しかしながら、トラップとして働いていた転位密度が小さくなるため、上記3つの方法(第1参考例,第2参考例および第1実施形態の方法)では、通常の方法と比較して、DC/RF分散率が30%から10%以下に大きく減少し、HEMT特性が大きく改善されている。

【0103】

尚、上記HEMTを形成するにあたって、各層をMOCVD法を用いて成長させたが、RF-MBE法以外の分子線エキタピシー装置を用いた結晶成長法でもMOCVD法と同様の改善が見られることが確認されている(RF-MBE法を用いた成長方法では、転位が多いために移動度が極端に小さくて、十分なHEMT特性が出ないことが確認されている)。

【符号の説明】

【0104】

1,21,31 バッファ層

2,22,43,53 Ga層

3,46,54,55,56,73,75,76,103 GaN層

4,44 GaN層の下層部

5,55 GaN層の上層部

23,25,32 窒化物系III−V族化合物半導体層

35,74 アモルファスの層

41,51,71 SiC基板

42,52,72 AlNのバッファ層

101 サファイア基板

102 GaNバッファ層

104 AlGaN層

105 ソース/ドレイン電極

106 ゲート電極

【特許請求の範囲】

【請求項1】

基板上に窒化物系III−V族化合物半導体からなるバッファ層を形成するバッファ層形成工程と、

上記バッファ層上に窒化物系III−V族化合物半導体層を成長させる化合物半導体成長工程と、

上記バッファ層と上記窒化物系族化合物半導体層との界面近傍にイオンを打ち込んで、上記界面近傍をアモルファス化するイオン打ち込み工程と、

上記イオン打ち込み工程の後に熱処理を行う熱処理工程と

を有することを特徴とする窒化物系III−V族化合物半導体装置の製造方法。

【請求項2】

請求項1に記載の窒化物系III−V族化合物半導体装置の製造方法において、

上記イオン打ち込み工程で打ち込まれるイオンは、C、N、Mg、Al、Zn、GaおよびInの内の少なくとも1つであることを特徴とする窒化物系III−V族化合物半導体装置の製造方法。

【請求項3】

請求項1に記載の窒化物系III−V族化合物半導体装置の製造方法において、

上記熱処理工程の温度は、熱処理工程よりも前に形成された窒化物系III−V族化合物半導体層の成長温度よりも大きく、かつ、上記成長温度に200℃を加えた温度よりも小さいことを特徴とする窒化物系III−V族化合物半導体装置の製造方法。

【請求項1】

基板上に窒化物系III−V族化合物半導体からなるバッファ層を形成するバッファ層形成工程と、

上記バッファ層上に窒化物系III−V族化合物半導体層を成長させる化合物半導体成長工程と、

上記バッファ層と上記窒化物系族化合物半導体層との界面近傍にイオンを打ち込んで、上記界面近傍をアモルファス化するイオン打ち込み工程と、

上記イオン打ち込み工程の後に熱処理を行う熱処理工程と

を有することを特徴とする窒化物系III−V族化合物半導体装置の製造方法。

【請求項2】

請求項1に記載の窒化物系III−V族化合物半導体装置の製造方法において、

上記イオン打ち込み工程で打ち込まれるイオンは、C、N、Mg、Al、Zn、GaおよびInの内の少なくとも1つであることを特徴とする窒化物系III−V族化合物半導体装置の製造方法。

【請求項3】

請求項1に記載の窒化物系III−V族化合物半導体装置の製造方法において、

上記熱処理工程の温度は、熱処理工程よりも前に形成された窒化物系III−V族化合物半導体層の成長温度よりも大きく、かつ、上記成長温度に200℃を加えた温度よりも小さいことを特徴とする窒化物系III−V族化合物半導体装置の製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【公開番号】特開2009−239315(P2009−239315A)

【公開日】平成21年10月15日(2009.10.15)

【国際特許分類】

【出願番号】特願2009−168930(P2009−168930)

【出願日】平成21年7月17日(2009.7.17)

【分割の表示】特願2003−85126(P2003−85126)の分割

【原出願日】平成15年3月26日(2003.3.26)

【出願人】(000005049)シャープ株式会社 (33,933)

【Fターム(参考)】

【公開日】平成21年10月15日(2009.10.15)

【国際特許分類】

【出願日】平成21年7月17日(2009.7.17)

【分割の表示】特願2003−85126(P2003−85126)の分割

【原出願日】平成15年3月26日(2003.3.26)

【出願人】(000005049)シャープ株式会社 (33,933)

【Fターム(参考)】

[ Back to top ]