窒化物電子デバイス、窒化物電子デバイスを作製する方法

【課題】リーク特性のばらつき幅を低減可能な、窒化物電子デバイスを作製する方法を提供する。

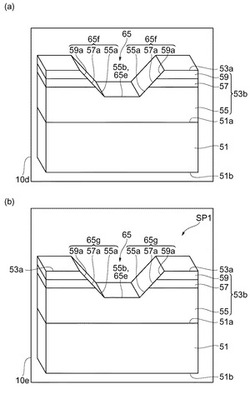

【解決手段】テトラメチルアンモニウムヒドロキシドを含む第1溶液を用いた処理を行って半導体積層53bに第1処理面65fを処理装置10dで形成する。第1溶液による処理温度は、摂氏50度以上摂氏100度以下である。第1溶液の濃度は5パーセント以上であり、50パーセント以下である。第1処理工程に引き続き第2処理工程を行う。第2処理工程では、テトラメチルアンモニウムヒドロキシド処理の後に、フッ化水素酸及び過酸化水素を含む第2溶液を用いた処理を半導体積層53bに行って半導体積層53bに第2処理面65gを処理装置10eで形成する。第2処理工程の後において、半導体積層53bの処理面65gのドナー性不純物の濃度は5×1017cm−3以下である。

【解決手段】テトラメチルアンモニウムヒドロキシドを含む第1溶液を用いた処理を行って半導体積層53bに第1処理面65fを処理装置10dで形成する。第1溶液による処理温度は、摂氏50度以上摂氏100度以下である。第1溶液の濃度は5パーセント以上であり、50パーセント以下である。第1処理工程に引き続き第2処理工程を行う。第2処理工程では、テトラメチルアンモニウムヒドロキシド処理の後に、フッ化水素酸及び過酸化水素を含む第2溶液を用いた処理を半導体積層53bに行って半導体積層53bに第2処理面65gを処理装置10eで形成する。第2処理工程の後において、半導体積層53bの処理面65gのドナー性不純物の濃度は5×1017cm−3以下である。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、窒化物電子デバイス、及び窒化物電子デバイスを作製する方法に関する。

【背景技術】

【0002】

特許文献1には、導電性基板上にヘテロ電界効果トランジスタを作製する方法が記載されている。特許文献2には、III 族窒化物半導体のウェットエッチング方法および半導体装置製造方法が記載されている。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開2006−286942号公報

【特許文献2】特開2008−10608号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

特許文献2では、n型GaN基板のR面表面上にSiO2からなる層間絶縁膜を形成する。次に、この層間絶縁膜をドライエッチングして、コンタクトホールを形成する。次に、摂氏90度の温度で、濃度25%のTMAH水溶液を用い、ウェットエッチングを行う。エッチングされた面の面方位はR面であるので、TMAH水溶液によるエッチングにより、エッチングのダメージ層が除去される。その後に、n型GaN基板のR面表面に金属膜を形成する。

【0005】

一方、発明者らの検討における半導体素子の作製では、n型III族窒化物半導体からなる自立基板の主面の上に、第1、第2及び第3のIII族窒化物半導体層を順に設けたエピタキシャル基板を形成した後に、第3のIII族窒化物半導体層から第2のIII族窒化物半導体層を介して第1のIII族窒化物半導体層に至る斜面を有する開口をエッチングによりエピタキシャル基板に形成して、ドリフト層、電流ブロック層及びコンタクト層並びに開口の斜面を含む半導体積層を形成する。この半導体積層の上に、III族窒化物からなるチャネル層及びIII族窒化物からなるキャリア供給層をエピタキシャル成長する。このように成長されたHEMTエピ構造を有する窒化物電子デバイスの作製では、低いリーク特性の窒化物電子デバイスがあれば、高いリーク特性ゆえにゲート電極からの電界に応じたスイッチ動作を示さない窒化物電子デバイスもある。つまり、窒化物電子デバイスにおけるチャネルリークにばらつきが大きい。窒化物電子デバイス間におけるリーク特性の広いばらつきに関する発明者らの検討から、大きなばらつきのリーク特性の原因を特定できた。また、この結果として、より優れたリーク特性を示す窒化物電子デバイスを得るに至った。

【0006】

本発明は、このような事情を鑑みて為されたものであり、リーク特性のばらつき幅を低減可能な、窒化物電子デバイスを作製する方法を提供することを目的とし、また、より優れたリーク特性を示す窒化物電子デバイスを提供することを目的とする。

【課題を解決するための手段】

【0007】

本発明に係る発明は、窒化物電子デバイスを作製する方法に係る。この方法は、(a)n型III族窒化物半導体からなる自立基板の主面の上に、ドリフト層、電流ブロック層及びコンタクト層のための第1、第2及び第3のIII族窒化物半導体層を順に設けたエピタキシャル基板を準備する工程と、(b)前記第3のIII族窒化物半導体層から前記第2のIII族窒化物半導体層を介して前記第1のIII族窒化物半導体層に至る斜面を有する開口をエッチングにより前記エピタキシャル基板に形成して、前記ドリフト層、前記電流ブロック層及び前記コンタクト層並びに前記開口の斜面を含む半導体積層を形成する工程と、(c)前記半導体積層を形成した後に、テトラメチルアンモニウムヒドロキシドを含む第1溶液を用いた第1処理を前記半導体積層に行うと共に、該第1処理の後に、フッ化水素酸及び過酸化水素を含む第2溶液を用いた第2処理を前記半導体積層に行って、前記第1処理及び前記第2処理による処理面を前記半導体積層に提供する工程と、(d)前記半導体積層の前記処理面の上に、III族窒化物からなるチャネル層及びIII族窒化物からなるキャリア供給層をエピタキシャル成長して、基板生産物を形成する工程とを備える。前記キャリア供給層の前記III族窒化物のバンドギャップは、前記チャネル層の前記窒化ガリウム系半導体のバンドギャップより大きく、前記第1及び第3のIII族窒化物半導体層はn型を有し、前記第2のIII族窒化物半導体層はp型を有する。

【0008】

この窒化物電子デバイスを作製する方法(以下「作製方法」として参照する)によれば、エピタキシャル基板に開口をエッチングにより形成するので、半導体積層は、エピタキシャル基板の表面に由来する主面と、エッチングにより形成される開口の斜面とを有する。半導体積層の開口がエッチングにより形成されるので、開口斜面にはエッチングによるドナー性欠陥が形成される。第1溶液を用いた処理は、半導体積層の主面及び斜面の両方に適用される。この処理に引き続き、第2溶液を用いた処理が半導体積層の表面に適用される。フッ化水素酸及び過酸化水素を含む第2溶液による処理は、第1溶液の処理により半導体積層からの反応生成物として生成された水酸化物の濃度を半導体積層の表面において低減するために有効である。第1溶液による処理及び第2溶液による処理の組み合わせ処理は、半導体積層表面上へ成長されるチャネル層及びキャリア供給層へのドナー性欠陥の影響を低減できる。この作製方法によれば、リーク電流及びそのばらつき幅を低減できる。

【0009】

また、第1溶液及び第2溶液を用いた処理により、製造工程におけるばらつきに影響が低減されて、また優れたサブスレッショルド特性を有する素子を作製できる。

【0010】

本発明に係る作製方法は、前記電流ブロック層に到達するコンタクトホールを前記半導体積層に形成する工程と、前記コンタクトホールを形成した後に、前記半導体積層の前記コンタクト層の上に電極を形成する工程とを備えることができる。

【0011】

この作製方法によれば、第2及び第3の窒化ガリウム系半導体層に対する電極を形成できる。

【0012】

本発明に係る作製方法では、前記第2溶液では、フッ化水素酸及び過酸化水素の容量比に関して、(フッ化水素酸)/(過酸化水素)≧5であることが好ましい。

【0013】

この作製方法によれば、テトラメチルアンモニウムヒドロキシドによる処理により水酸化物が形成される。第2溶液が上記の比率であるとき、水酸化物の除去に加えてドナー性欠陥の低減に有効である。

【0014】

本発明に係る作製方法では、前記自立基板の前記主面は、前記n型III族窒化物半導体のc面に対して−0.7度以上−0.1度以下又は+0.1度以上+0.7度以下の角度であることができる。この作製方法によれば、自立基板の主面が上記の角度範囲にあるとき、第1溶液による処理が開口側面に有効に働く。また、本発明に係る作製方法では、前記自立基板の前記主面は実質的にc面であることができる。

【0015】

本発明に係る作製方法では、前記第1処理において、前記第1溶液の温度は、摂氏50度以上であり、摂氏100度未満であることが好ましい。また、前記第1溶液は水溶液であることができる。

【0016】

この作製方法によれば、温度が摂氏50度以上であるとき、良好なエッチング速度が提供される。温度が摂氏100度以上では、溶液中に気泡が発生し、被処理の表面に付着する可能性がある。また、溶媒の蒸発により第1溶液の濃度が変化していく。第1溶液の溶媒に水を適用することができる。

【0017】

本発明に係る作製方法では、前記第1処理において、前記第1溶液の濃度は、5パーセント以上であり、50パーセント以下であることができる。この作製方法によれば、5パーセント以上の濃度では、良好なエッチング速度が提供される。50パーセント以下の濃度では、反応生成物が半導体積層表面の近傍で過飽和になる可能性があり、これ故に、処理時間が経過するにつれて沈殿物を生じる可能性がある。

【0018】

本発明に係る作製方法では、前記チャネル層及び前記キャリア供給層の材料の組み合わせは、前記チャネル層/前記キャリア供給層として記載したとき、InGaN/AlGaN、GaN/AlGaN及びAlGaN/AlNのいずれか一つであることができる。この作製方法によれば、良好な電流特性を提供できる好適なチャネル構造の組み合わせが提供される。

【0019】

本発明に係る作製方法では、前記第1〜第3のIII族窒化物半導体層の材料の組み合わせは、前記第3のIII族窒化物半導体層/前記第2のIII族窒化物半導体層/前記第1の窒化ガリウム系半導体層として記載したとき、n+型GaN/p型GaN/n型GaNまたはn+型GaN/p型AlGaN/n型GaNであることができる。この作製方法によれば、半導体積層を構成する好適な組み合わせが提供される。

【0020】

本発明に係る作製方法は、前記チャネル層及び前記キャリア供給層をエピタキシャル成長した後に、前記基板生産物の上に前記開口の前記斜面にゲート電極を形成する工程を備えることができる。

【0021】

この作製方法によれば、開口斜面にゲート電極が設けられるので、半導体積層の開口斜面のドナー性不純物が低減されるので、チャネルリーク電流が低減される。

【0022】

本発明に係る作製方法は、前記チャネル層及び前記キャリア供給層をエピタキシャル成長した後に、前記基板生産物の上に絶縁膜を形成する工程と、前記絶縁膜を成長した後に、前記基板生産物の上に前記開口の前記斜面にゲート電極を形成する工程とを備えることができる。

【0023】

この作製方法によれば、ドナー性不純物が低減された半導体積層斜面上のチャネル層に、開口斜面上の絶縁膜を介してゲート電極からの電界を印加できるので、チャネルリーク電流が低減される。

【0024】

本発明に係る作製方法では、前記半導体積層の前記処理面のドナー性不純物の濃度は5×1017cm−3以下であることができる。

【0025】

この作製方法によれば、第1及び第2溶液を用いた前処理により、再成長面のために下地が提供される。この下地の前処理面上にチャネル層及びキャリア供給層がエピタキシャル成長される。この成長により形成される界面のドナー性不純物濃度を低減できる。

【0026】

本発明に係る作製方法では、前記チャネル層はアンドープ窒化ガリウム系半導体層を含み、前記チャネル層の厚さは20nm以上であり、400nm以下であることができる。

【0027】

この作製方法によれば、チャネル層はアンドープ層であるので、ドナー性不純物に敏感である一方で、高いキャリア移動度を提供できる。

【0028】

本発明に係る作製方法では、前記電流ブロック層の第2のIII族窒化物半導体はp型GaNであり、前記電流ブロック層の膜厚は0.1μm以上〜2.0μm以下であり、前記電流ブロック層のp型GaNにはマグネシウム(Mg)が添加されており、前記電流ブロック層のMg濃度は、5×1016cm−3以上であり、5×1018cm−3以上であることができる。

【0029】

この作製方法によれば、電流ブロック層はチャネル層に対してバックゲートを提供すると共に、電流ブロック層の膜厚はチャネル長を規定する。ドナー性不純物の濃度は、電流ブロック層のp型ドーパント濃度に比べて低減されて、十分に小さくなる。

【0030】

本発明に係る作製方法は、前記自立基板の上にドレイン電極を形成する工程を備えることができる。この作製方法によれば、自立基板の主面は実質的にc面であるとき、開口の底部の面方位は実質的にc面である。第1溶液は、c面に対するドナー性欠陥の処理に比べて、電流ブロック層上の傾斜面上のドナー性欠陥の処理に優れる。開口の底部のドナー性欠陥は、n型層とn型層との界面に残留する。

【0031】

本発明に係る窒化物電子デバイスは、(a)支持基体の主面上に順に設けられたドリフト層、電流ブロック層及びコンタクト層を含むと共に、前記コンタクト層から前記電流ブロック層を介して前記ドリフト層に至る側面を有する半導体積層と、(b)前記側面に設けられ、窒化ガリウム系半導体からなるチャネル層と、(c)前記側面に設けられ、窒化ガリウム系半導体からなるキャリア供給層と、(d)前記側面に設けられたゲート電極と、(e)前記半導体積層の上に設けられたソース電極と、(f)前記半導体積層及び前記支持基体のいずれかに設けられたドレイン電極とを備える。前記半導体積層の前記側面と前記チャネル層との界面におけるドナー性欠陥の濃度は5×1017cm−3以下であり、前記ドリフト層は、第1の窒化ガリウム系半導体からなり、前記電流ブロック層は、第2の窒化ガリウム系半導体からなり、前記コンタクト層は、第3の窒化ガリウム系半導体からなり、前記チャネル層は前記キャリア供給層との前記側面との間に設けられ、前記キャリア供給層の前記III族窒化物のバンドギャップは、前記チャネル層の前記窒化ガリウム系半導体のバンドギャップより大きく、前記ドリフト層及び前記コンタクト層はn型を有し、前記電流ブロック層はp型を有する。

【0032】

この窒化物電子デバイスによれば、半導体積層の側面とチャネル層との界面におけるドナー性欠陥の濃度は5×1017cm−3以下であるので、ドナー性欠陥に起因するチャネルリークを低減できる。これ故に、これまでに比べても良好なドレインリーク特性を窒化物電子デバイスに提供できる。

【0033】

本発明に係る窒化物電子デバイスでは、前記ドリフト層の第1の窒化ガリウム系半導体はn型GaNであり、前記ドリフト層の膜厚は1μm以上であり、10μm以下であり、前記ドリフト層のn型GaNにはシリコン(Si)が添加されており、前記ドリフト層のSi濃度は、1×1015cm−3以上であり、3×1016cm−3以下であることができる。

【0034】

この窒化物電子デバイスによれば、上記のドリフト層を用いて、高耐圧に良い窒化物電子デバイスを提供できる。

【0035】

本発明に係る窒化物電子デバイスでは、前記電流ブロック層の第2の窒化ガリウム系半導体はp型GaNであり、前記電流ブロック層の膜厚は0.1μm以上であり、2.0μm以下であり、前記電流ブロック層のp型GaNにはマグネシウム(Mg)が添加されており、前記電流ブロック層のMg濃度は、5×1016cm−3以上であり、5×1018cm−3以下であることができる。

【0036】

この窒化物電子デバイスによれば、電流ブロック層はチャネル層に対してバックゲートを提供すると共に、電流ブロック層の膜厚はチャネル長を規定する。ドナー性不純物の濃度は、電流ブロック層のp型ドーパント濃度に比べて十分に小さく低減される。

【0037】

本発明に係る窒化物電子デバイスでは、前記コンタクト層の第3の窒化ガリウム系半導体はn型GaNであり、前記コンタクト層の膜厚は0.1μm以上であり、1.0μm以下であり、前記コンタクト層のn型GaNにはシリコン(Si)が添加されており、前記コンタクト層のSi濃度は、1×1016cm−3以上であることができる。この窒化物電子デバイスによれば、ソース抵抗を低くできる。

【0038】

本発明に係る窒化物電子デバイスでは、前記キャリア供給層はAlXGa1−XN(0<X<1)層を含み、前記キャリア供給層の厚さは5nm以上であり、40nm以下であり、前記チャネル層はアンドープGaN層を含み、前記チャネル層の厚さは20nm以上であり、400nm以下であり、前記キャリア供給層は前記チャネル層にヘテロ接合を成すことができる。

【0039】

この窒化物電子デバイスによれば、高い移動度で低いチャネルリークのヘテロ接合トランジスタを提供できる。

【発明の効果】

【0040】

以上説明したように、本発明によれば、リーク特性のばらつき幅を低減可能な、窒化物電子デバイスを作製する方法を提供でき、また、より優れたリーク特性を示す窒化物電子デバイスを提供できる。

【図面の簡単な説明】

【0041】

【図1】図1は、本実施の形態に係る窒化物電子デバイスを作製する方法における主要な工程を模式的に示す図面である。

【図2】図2は、本実施の形態に係る窒化物電子デバイスを作製する方法における主要な工程を模式的に示す図面である。

【図3】図3は、本実施の形態に係る窒化物電子デバイスを作製する方法における主要な工程を模式的に示す図面である。

【図4】図4は、本実施の形態に係る窒化物電子デバイスを作製する方法における主要な工程を模式的に示す図面である。

【図5】図5は、本実施の形態に係る窒化物電子デバイスを作製する方法における主要な工程を模式的に示す図面である。

【図6】図6は、本実施の形態に係る窒化物電子デバイスを作製する方法における主要な工程を模式的に示す図面である。

【図7】図7は、本実施の形態に係る窒化物電子デバイスを作製する方法における主要な工程を模式的に示す図面である。

【図8】図8は、チャネル層及びキャリア供給層を成長するための再成長温度シーケンスを示す図面である。

【図9】図9は、第1処理及び第2処理を行わずに作製されたトランジスタの測定結果のうち所望でない性能を示すトランジスタのId−Vd特性を示す図面である。

【図10】図10は、第1処理及び第2処理を行わずに形成された再成長界面にドナー性欠陥の濃度分布を示す図面である。

【図11】図11は、高い濃度のドナー性欠陥を含む再成長界面におけるバンド構造を示す図面である。

【図12】図12は、第1処理及び第2処理の後に形成された再成長界面にドナー性欠陥の濃度分布を示す図面である。

【図13】図13は、実施例におけるトランジスタのId−Vd特性を示す図面である。

【図14】図14は、本実施の形態に係る窒化物電子デバイスの構造を示す図面である。

【発明を実施するための形態】

【0042】

引き続いて、添付図面を参照しながら、窒化物電子デバイス、及び窒化物電子デバイスを作製する方法に係る実施の形態を説明する。可能な場合には、同一の部分には同一の符号を付する。

【0043】

図1〜図7は、本実施の形態に係る窒化物電子デバイス、エピタキシャル基板、及び基板生産物を作製する方法における主要な工程を模式的に示す図面である。

【0044】

図1の(a)部で示されるように、最初の工程では、窒化物電子デバイスのための自立基板を準備する。この基板は導電性を示し、例えば六方晶系のIII族窒化物からなることができる。自立のIII族窒化物半導体基板(以下、図1の(a)部で番号「51」で示される)は、例えばGaN、AlN等からなることができる。基板51は主面51a及び裏面51bを有する。

【0045】

図1の(a)部では、c軸方向を示すc軸ベクトルVCが示されている。好適な実施例では、このIII族窒化物半導体基板51(以下「基板51」として参照する)主面51aはc面からなることができるが、基板51のIII族窒化物のc軸に対して僅かなオフ、例えば−0.7度以上−0.1度以下又は+0.1度以上+0.7度以下の範囲のオフを有することができる。

【0046】

熱処理工程では、図1の(b)部に示されるように、III族窒化物半導体基板51を成長炉10aに配置した後に、III族窒化物半導体基板51の熱クリーニングを行う。熱クリーニングは、例えばアンモニア及び水素を含む雰囲気52においてIII族窒化物半導体基板51の熱処理によって行われる。熱処理は、例えば10分間程度である。また、熱処理温度は、例えば摂氏1030度程度である。炉内圧力は例えば100Torrである。

【0047】

第1成長工程では、図2の(a)部に示されるように、n型III族窒化物半導体からなる基板51の主面51aの上に、ドリフト層、電流ブロック層及びコンタクト層のための第1〜第3のIII族窒化物半導体層を順に設けたエピタキシャル基板Eを準備する。本実施例では、エピタキシャル基板Eは、基板51の主面51aに成長された半導体積層53を含む。半導体積層53の形成では、n−型窒化ガリウム系半導体からなる第1のIII族窒化物半導体層55、p型窒化ガリウム系半導体からなる第2のIII族窒化物半導体層57、及びn+型窒化ガリウム系半導体のための第3のIII族窒化物半導体層59を基板51の主面51a上に順に成長して、エピタキシャル基板Eを作製する。この成長は、例えば有機金属気相成長法で行われる。ドリフト層の第1のIII族窒化物半導体層55は、例えば厚さ5μmのアンドープGaNからなり、電流ブロック層の第2のIII族窒化物半導体層57は例えば厚さ0.5μmのMgドープp型GaNからなり、コンタクト層の第3のIII族窒化物半導体層59は例えば厚さ0.3μmのSiドープn+型GaNからなる。半導体積層53における接合61a、61bの各々も、基板51の主面51aの面方位と同じ面方位を示す。このとき、半導体積層53の厚さは5.8μmである。

【0048】

エピタキシャル基板Eを成長炉10aから取り出した後に、加工工程では、半導体積層53に開口を形成する。加工工程に先だって、マスク形成工程を行う。マスク形成のためにいくつかの工程が行われる。まず、図2の(b)部に示されるように、半導体積層53の開口を規定するためのマスクを形成するために、厚さTRのレジスト膜60を塗布する。次いで、露光及び現像工程では、図3の(a)部に示されるように、フォトリソグラフィ法を用いてレジスト膜60にパターン形成して、パターン形成されたレジスト層62を形成する。レジスト層62に形成されたパターンは、開口部の形状を規定する。レジスト層62は、露光及び現像により形成された側面62a及び上面62bを含む。露光及び現像工程の後に、ベーク工程を行う。ベーク工程では、図3の(b)部に示されるように、パターン形成されたレジスト層62をベーク装置10bでベークして、ベーク及びパターン形成されたレジスト膜、つまりマスク63を形成する。マスク63は、開口63aと、平坦な上面63b、上面63bに対して傾斜した側面63cを有する。ベーク条件は、レジスト膜厚に依存するが、例えば窒素雰囲気で、摂氏90度の熱処理温度、及び5分の熱処理時間である。マスク63の開口63aは、半導体積層53に形成される開口の形状及び位置を規定する。上記の実施例では、マスク63が、例えばレジスト膜から形成されたけれども、マスク63の形成に、シリコン酸化膜が用いられることができる。

【0049】

マスク63は、半導体積層53に形成される開口の形状及び位置を規定する開口63aを有する。上記のように、フォトリソグラフィで半導体積層53の表面53aにマスク63を形成した後に、図4の(a)部に示されるように、エピタキシャル基板Eの加工を行う。加工のために、エッチング装置10bにエピタキシャル基板Eを配置する。エッチング装置10c及びマスク63を用いて、半導体積層53のドライエッチングを行う。このドライエッチングは、例えば反応性イオンエッチング(RIE)であることができる。エッチャントとして、例えば塩素ガス、BCl3、CH4、アルゴン等を使用できる。マスク63を用いたエッチングにより、半導体積層53に開口65が形成される。開口形成の結果として、開口65を含む半導体積層53bが形成される。

【0050】

第3のIII族窒化物半導体層59から第2のIII族窒化物半導体層57を介して第1のIII族窒化物半導体層55に至る斜面を有する開口65をエッチングによりエピタキシャル基板Eに形成して、ドリフト層、電流ブロック層及びコンタクト層並びに開口65の斜面65dを含む半導体積層53bを形成する。開口65は、半導体積層53bの表面53aのコンタクト層の第3のIII族窒化物半導体層59からドリフト層の第1のIII族窒化物半導体層55に到達する。開口65は側面65d及び底面65eによって規定される。開口65の側面65dには、ドリフト層(以下、番号「55」して参照する)の側面55a及び底面55b、電流ブロック層(以下、番号「57」して参照する)の側面57a、及びコンタクト層(以下、番号「59」して参照する)の側面59aが現れている。開口65の底面65eには、ドリフト層の底面55bが現れている。好適な実施例では、基板51の主面51aは{0001}面からなるので、側面65dは{0001}面に対して傾斜している。

【0051】

加工工程の最後に、図4の(b)部に示されるように、マスク63が除去される。この結果、基板生産物SP1が形成される。基板生産物SP1では、開口65は、第1〜第3部分65a、65b、65cを有する。第1の部分65aでは、ドリフト層55の底面55b(底面65e)が露出している。第2の部分65b及び第3の部分65cでは、開口65の側面65dが、ドリフト層の第3のIII族窒化物半導体層55の底面55bから半導体積層53bの表面53aまで傾斜して延在する。

【0052】

図4の(b)部では、単一の開口65が描かれているけれども、基板51には多数の開口が配列されている。これ故に、半導体積層53bは、開口65の形状に応じて、メサ形状、或いは凹部(例えば溝)を含む形状を成す。側面65dは、基板51の主面51aに対して傾斜しており、また半導体積層53bの表面53aに対して傾斜している。側面65dの具体的な傾斜角は、エッチングにより制御されることができる。

【0053】

側面65dの一方は、全体としては、基準面R11に沿って延在しており、側面65dの他方は、全体としては、基準面R12に沿って延在している。これらの基準面R11、R12はIII族窒化物基板51のc軸の方向を示す基準軸Cx及び基板51の主面51aに対して傾斜している。基準面R11、R12の法線はc軸に対して傾斜しており、半導体積層53bの主面53aは基準面R13に沿って延在している。好適な実施例では、半導体積層53bの主面53aは基板51の主面51aと実質的に平行であることができる。基準面R11、R12(つまり、側面65d)と基準面R13(主面63a、51a)との成す角度は例えば5度〜40度の範囲にあることができる。

【0054】

開口65を形成した後に、半導体積層53bの表面53a及び側面65d上にHEMT構造の再成長を行う。発明者らの知見によれば、ドライエッチングにより形成した斜面には、ドナー性欠陥が残留している。この斜面への再成長界面がn型導電性を持ち、この界面特性がトランジスタ形成後のドレインリーク不良を引き起こす。

【0055】

この特性不良を避けるために、半導体積層53bを形成した後に、第1処理工程では、図5の(a)部に示されるように、テトラメチルアンモニウムヒドロキシドを含む第1溶液を用いた第1処理を処理装置10dで行って、半導体積層53bに第1処理面65fを形成する。

【0056】

好適な実施例では、この基板51の主面51aはc面からなることができるが、基板51のIII族窒化物のc軸に対して僅かなオフ、例えば−0.7度以上−0.1度以下又は+0.1度以上+0.7度以下の範囲のオフを有することができる。上記の角度範囲は、デバイスに有用であり、基板51の主面51aが上記の角度範囲にあるとき、第1溶液による処理が開口側面に有効に働く。

【0057】

また、第1溶液の温度は、摂氏50度以上であり、摂氏100度未満であることが好ましい。第1溶液による処理温度が摂氏50度以上であるとき、良好なエッチング速度が提供される。第1溶液による処理温度が摂氏100度以上では、溶液中に気泡が発生し、被処理の表面に付着する可能性がある。また、溶媒の蒸発により第1溶液の濃度が変化していく。第1溶液に水溶液を適用することができる。第1溶液の濃度(質量比)は5パーセント以上であり、50パーセント以下であることができる。この方法によれば、5パーセント以上の濃度では、良好なエッチング速度が提供される。50パーセント以下の濃度では、反応生成物が半導体積層表面の近傍で過飽和になる可能性があり、これ故に、処理時間が経過するにつれて沈殿物を生じる可能性がある。

【0058】

第1処理工程に引き続き第2処理工程を行う。第2処理工程では、テトラメチルアンモニウムヒドロキシド処理の後に、図5の(b)部に示されるように、フッ化水素酸及び過酸化水素を含む第2溶液を用いた第2処理を半導体積層53bに処理装置10eで行って、半導体積層53bに第2処理面65gを形成する。第2処理工程の後において、半導体積層53bの処理面65gのドナー性不純物の濃度は5×1017cm−3以下であることができる。第1及び第2溶液を用いた処理による前処理で再成長面が提供される。この再成長面にチャネル層及びキャリア供給層がエピタキシャル成長される。この再成長面のドナー性不純物の濃度が低減される。

【0059】

第2溶液では、フッ化水素酸及び過酸化水素の容量比に関して、(フッ化水素酸)/(過酸化水素)≧5であることが好ましい。テトラメチルアンモニウムヒドロキシドによる処理により半導体積層53bの第1処理面近傍には水酸化物が形成される。第2溶液が上記の比率であるとき、水酸化物の除去に加えてドナー性欠陥の低減に有効である。第2溶液の温度は、摂氏25度以上であり、摂氏50度以下であることが好ましい。第1溶液による処理温度が摂氏25度以上であるとき、水酸化物とドナー性欠陥を効率的に除去することができるからである。第1溶液による処理温度が摂氏50度以下では、フッ化水素の揮発を抑えて薬液の降下が持続される。

【0060】

必要な場合には、チャネル層及びキャリア供給層の成長に先立って基板生産物SP1の前処理(例えば、洗浄)を行った後に、次の工程において基板生産物SP1を成長炉10aに配置する。

【0061】

第1再成長工程では、アンモニア及びIII族元素原料を含む原料ガスG1を成長炉10aに供給して、図6の(a)部に示されるように、半導体積層53bの主面53a、開口65の第2処理面65g及び底面65e上に、チャネル層69を成長温度TG1で成長する。チャネル層69は窒化ガリウム系半導体からな、例えばアンドープ窒化ガリウム系半導体層からなることができる。チャネル層68は、第1の部分69a、第2の部分69b及び第3の部分69cを含む。第1の部分69aは、開口65の側面65d(つまり、処理面65g)上に成長され、基準面R21に沿って延在する。基準面R21は、チャネル層69の窒化ガリウム系半導体のc軸に直交する面及び基板51の主面51aに対して傾斜する。第2の部分69bは、半導体積層53bの主面53a上に成長され、c軸に直交する基準面R22に沿って延在する。第1の部分69aは、基準面R22に対して傾斜する。第3の部分69cは、開口65の底面65e上に成長され、基準面R23に沿って延在する。第1の部分69aは、基準面R23に対して傾斜する。好適な実施例では、基準面R23は基準面R22と実質的に平行であり、また基準面R23及び基準面R22は基板51の主面51aに平行である。

【0062】

第2再成長工程では、アンモニア及びIII族元素原料を含む原料ガスG2を成長炉10aに供給して、図6の(b)部に示されるように、チャネル層69の成長の後に、半導体積層53bの主面53a、開口65の側面65d及び底面65e上に、キャリア供給層71を成長温度TG2で成長する。キャリア供給層71はチャネル層69とヘテロ接合70を形成する。キャリア供給層71はIII族窒化物半導体からなる。キャリア供給層71は、第1の部分71a、第2の部分71b及び第3の部分71cを含む。第1の部分71aは、開口65の側面65d上に成長され、基準面R31に沿って延在する。基準面R31は、キャリア供給層71の窒化ガリウム系半導体のc軸(基板51のc軸と同じ方向を向く)に直交する面及び基板51の主面51aに対して傾斜する。第2の部分71bは、半導体積層53bの主面53a上に成長され、基準面R32に沿って延在する。第1の部分71aは、基準面R32に対して傾斜する。第3の部分71cは、開口65の底面65e上に成長され、基準面R33に沿って延在する。第1の部分71aは、基準面R33に対して傾斜する。本実施例では、基準面R33は基準面R32と実質的に平行であり、また基準面R33及び基準面R32は基板51の主面51aに平行である。キャリア供給層71のIII族窒化物半導体のバンドギャップは、チャネル層69の窒化ガリウム系半導体のバンドギャップより大きい。

【0063】

基準面R31に直交する第1の軸とキャリア供給層71の窒化ガリウム系半導体のc軸との成す第1の角度は、基準面R32に直交する第2の軸とキャリア供給層71の窒化ガリウム系半導体のc軸との成す第2の角度より大きい。基板51の主面51aがc面及びc面から僅かなオフ角を有するとき、第2の角度はゼロ及び微少な角度である。第1の角度は、開口65の側面65dの傾斜に対応しており、第2の角度より大きな角度であり、これ故に、第1の部分69a、71aの傾斜は大きい。

【0064】

上記の工程により基板生産物SP2が形成される。図7の(a)部に示されるように、基板生産物SP2を成長炉10aから取り出す。図7の(b)部に示されるように、電極形成工程では、キャリア供給層71上にゲート電極79を形成する。より具体的には、電極形成工程では、半導体積層53bの半導体層57、59に接触を成すソース電極73の形成、基板51の裏面51bに接触を成すドレイン電極75の形成、ゲート絶縁膜77の形成、及びゲート絶縁膜77に接触を成すゲート電極79の形成を行う。ゲート絶縁膜77は例えばAl2O3、SiN、SiO2、HfO2等からなることができる。

【0065】

例えば、ソース電極の形成に先だって、コンタクト工程では、コンタクト層59から電流ブロック層57に到達するコンタクトホールを半導体積層53bに形成する。コンタクトホールを形成した後に、ソース電極形成工程では、半導体積層53bのコンタクト層59の上にソース電極73を形成する。ソース電極73は、電流ブロック層57(第2の窒化ガリウム系半導体層)及びコンタクト層59(第3の窒化ガリウム系半導体層)に接触を成す。

【0066】

例えば、チャネル層69及びキャリア供給層71をエピタキシャル成長した後に、ゲート電極形成工程では、基板生産物SP2の上に開口斜面にショットキ接触を成すようにゲート電極79を形成する。この実施の形態によれば、開口斜面にゲート電極が設けられる半導体積層開口斜面のドナー性不純物が低減されるので、チャネルリーク電流が低減される。

【0067】

或いは、例えば、絶縁膜形成工程では、チャネル層69及びキャリア供給層71をエピタキシャル成長した後に、基板生産物SP2上に絶縁膜77を形成する。絶縁膜形成工程後のゲート電極形成工程では、基板生産物SP2上に開口斜面にゲート電極79を形成する。この作製方法によれば、絶縁膜77の形成の後に、開口斜面上にゲート電極79が設けられる。半導体積層53bの開口斜面のドナー性不純物が低減されるので、チャネルリーク電流が低減される。また絶縁膜77によりゲートリーク電流も低減される。

【0068】

例えば、ドレイン電極形成工程では、基板51上にドレイン電極75を形成する。基板51の主面51aは実質的にc面であるとき、開口の底部の面方位は実質的にc面である。第1溶液の処理は、c面に対するドナー性欠陥の除去能力に比べて、電流ブロック層57上の傾斜面上のドナー性欠陥の除去能力に優れる。開口の底部のドナー性欠陥は、n型層とn型層との界面にも残留する。

【0069】

図7の(b)部に示されるように、半導体積層53bの主面53a上にソース電極73を形成でき、このソース電極73は、電流ブロック層57及びコンタクト層59に電位を供給する。チャネル層69とキャリア供給層71とは接合70を成し、接合70には二次元キャリアガス層が形成される。ソース電極73は、チャネル層69を流れるキャリアを供給し、キャリアは二次元キャリアガス層を介してドリフト層55に流れる。この作製方法によれば、ソース電極73が電流ブロック層57及びコンタクト層59に電位を供給するので、電流ブロック層57がチャネル層69に対してバックゲートとして働く。

【0070】

この方法によれば、図6に示されるように、チャネル層69の第1の部分69aは、その窒化ガリウム系半導体のc軸に直交する面及び基板51の主面51aに対して傾斜した基準面R21に沿って延在する。これ故に、チャネル層69の第1及び第2の部分69a、69bは互いに異なる面方位を有する。キャリア供給層71の第1及び第2の部分71a、71bは、それぞれ、チャネル層69の第1及び第2の部分69a、69b上に成長される。

【0071】

本実施の形態では、キャリア供給層71の第1の部分71a上にゲート絶縁膜77を形成した後に、このゲート絶縁膜77上にゲート電極79を形成することができる。ゲート電極79はゲート絶縁膜77に接合を成す。この作製方法によれば、絶縁膜77を介してチャネルキャリアを制御するゲート電極79を有するトランジスタを提供できる。また、ゲートリークが低減される。

【0072】

或いは、ゲート絶縁膜77を形成することなく、キャリア供給層71の第1の部分71aに接合を成すゲート電極を形成することができる。この作製方法によれば、半導体にショットキ接合を成すゲート電極を用いてチャネルキャリアを制御するトランジスタを提供できる。

【0073】

チャネル層69及びキャリア供給層71の材料は、チャネル層/キャリア供給層として記載したとき、InGaN/AlGaN、GaN/AlGaN、及びAlGaN/AlNのいずれかであることができる。これらは、チャネル層69及びキャリア供給層71の好適な組み合わせを提供できる。

【0074】

コンタクト層(第3のIII族窒化物半導体層)59の窒化ガリウム系半導体、電流ブロック層(第2のIII族窒化物半導体層)57の窒化ガリウム系半導体、及びドリフト層(第1のIII族窒化物半導体層)55の窒化ガリウム系半導体は、第3のIII族窒化物半導体層/第2のIII族窒化物半導体層/第1のIII族窒化物半導体層として記載したとき、n+型GaN/p型GaN/n型GaN、及びn+型GaN/p型AlGaN/n型GaNのいずれかであることができる。これらは、ドリフト層55、電流ブロック層57及びコンタクト層59の好適な組み合わせを提供できる。

【0075】

(実験例1)

発明者らの実験において、導電性の基板を用いた縦型トランジスタ構造を形成している。この導電性基板上に、n−型GaNドリフト層、p型GaN電流ブロック層、n+型GaNコンタクト層のための3つのGaN膜を順に成長する。この後に、n+型GaN膜からn−型GaN膜に至る斜面を反応性イオンエッチング(RIE)により形成する。エッチングにより形成されたGaN傾斜面上に、成長炉でチャネル層及びバリア層を再成長する。チャネル層は、GaN傾斜面と再成長エピ界面を形成する。

【0076】

発明者らの観察及び検討によれば、上記のドライエッチングにおいては、エッチングにより形成された斜面に、ドナー性欠陥が導入されている。これ故に、再成長エピ界面はn型導電性を示す。このため、チャネル層には二次元電子ガスチャネルが形成される。しかしながら、再成長エピ界面のn型導電性のために、p型GaN電流ブロック層が有効に働かずに、二次元電子ガスチャネルが狭窄されない。したがって、Id−Vd特性においてドレインリーク不良が発生する。

【0077】

引き続き説明される実験例では、上記の斜面への再成長により形成される界面にドナー性欠陥が残留することに鑑み、その濃度を低減することによって、Id−Vd特性のばらつきによるドレインリーク不良の発生を抑制することを試みる。

【0078】

トランジスタの作製。

窒化ガリウム膜を有機金属気相成長(MOCVD)法により成膜する。ガリウム原料としてトリメチルガリウム(TMG)、アルミニウム原料としてトリメチルアルミニウム(TMA)を用いる。窒素原料としては、高純度アンモニアを用いる。キャリアガスとしては、純化した水素を用いる。高純度アンモニアの純度は、99.999%以上、純化水素の純度は99.999995%以上である。n型ドーパントとして水素ベースのシランを用い、p型ドーパントとしてビスシクロペンタジエニルマグネシウムを用いる。

【0079】

基板として、2インチサイズのn型c面窒化ガリウム基板を準備する。アンモニアと水素雰囲気中で、窒化ガリウム基板の主面にサーマルクリーニングを行う。この熱処理条件としては、例えば摂氏1030度の熱処理温度及び100Torrの成長炉内圧力を用いられる。この基板クリーニングの後に、摂氏1050度への昇温後に、複数の窒化ガリウム層を成膜する。この成膜において、炉内圧力は200Torrであり、原料ガスにおけるV/III比は1500である。

エピタキシャル基板の構造。

n型ドリフト層:厚さ5μm、キャリア濃度1×1016cm−3。

p型電流ブロック層:厚さ0.5μm、Mgドープ、Mg濃度1×1018cm−3。

n型キャップ層:厚さ0.2μm、Siドープ、キャリア濃度1×1018cm−3。

上記の成長により、エピタキシャル基板が作製され、このエピタキシャル基板は、上記のようなnpn構造を有する。npn構造には、開口のためのパターンを有するレジストマスクをフォトリソグラフィを用いてエピ表面に形成した後に、インダクティブ・カップリング・プラズマ−反応性イオンエッチング(ICP−RIE)によりnpn構造を加工して、斜面を有する基板生産物を形成する。レジストマスクを除去した後に基板洗浄を実施する。この後に、基板生産物を成長炉に配置して、チャネル層及びバリア層の再成長を行う。

【0080】

レジストマスクの除去と基板洗浄の後に、図8に示される再成長温度シーケンスに従ってチャネル層及びキャリア供給層を成長する。まず、時刻t0でMOCVD装置に基板生産物を導入して、時刻t1で摂氏400度に基板温度を上昇させる。さらに、アンモニア及び水素を含む雰囲気で摂氏950度まで温度を時刻t2で上昇しながら熱クリーニングを行う。次いで、引き続きアンモニア及び水素を成長炉に供給しながらIII族有機金属原料(TMG)を成長炉に供給して時刻t3に成長を開始し、厚さ150nmのi−GaNチャネル層を成長する。時刻t4でIII族有機金属原料の供給を停止してチャネル層の成長を終了する。この後に、アンモニア及び水素を含む雰囲気で基板温度を摂氏1080度まで時刻t4〜t5の期間で上昇しながら、時刻t6でIII族有機金属原料(TMG、TMA)を成長炉に供給して、Al組成0,25及び厚さ20nmのi−AlGaNキャリア供給層を成長する。時刻t7でIII族有機金属原料の供給を停止してキャリア供給層の成長を終了する。この後に、時刻t8から基板温度を降下する。時刻t9で、室温において基板生産物を成長炉から取り出す。

【0081】

その後に、基板生産物の全面に絶縁膜を成膜した後に、フォトリソグラフィとイオンビーム蒸着法を用いて、ソース、ドレイン電極をそれぞれエピタキシャル基板の表面と裏面に形成すると共に、ゲート電極を開口部側面に形成する。

【0082】

このように作製された多数のトランジスタのId−Vd特性を測定する。図9は、測定結果のうちの性能の一例を示すトランジスタのId−Vd特性を表す。この例のようなId−Vd特性では、ドレインリーク過多で電流ピンチオフが生じておらず、ゲートバイアス(Vg)によるドレイン電流(Id)の変調も観察されない。

【0083】

エッチングにより形成されるGaN面の品質を特定する。c面GaN基板上に、厚さ3μmのアンドープGaNバッファ層を成長して、エピタキシャル基板を作製する。ICP−RIE装置において、Ar/Cl2エッチャントを用いて、このエピタキシャル基板の全面をエッチングして、厚さ2μmのアンドープGaNバッファ層を形成する(つまり、1μm厚のエッチング)。次に、薬液処理(例えばSPM処置)をエッチング面に施した後に、再びMOCVD炉において、厚さ0.5μmのアンドープGaN層の成長を行う。この成長の後に、再成長のアンドープGaN層のエピ表面にショットキ電極を形成する。

【0084】

このショットキ電極を用いて、C−V測定により界面のキャリア濃度を測定する。図10は、再成長界面にドナー性欠陥の濃度分布を示す図面である。C−V測定で調べたエピ再成長界面のドナープロファイルによれば、1×1018cm−3程度の平均濃度、及び1×1018cm−3を越えるピーク濃度のドナー性欠陥が形成されている。ICP−RIE装置及びエッチング条件は実験例1と同様であり、この実験例によれば、エッチングにより形成されたGaN斜面上へのHEMT構造のエピタキシャル積層の再成長界面にも同程度のドナー性欠陥が観察されると考えられる。再成長界面に大きな濃度のドナー性欠陥が残留するとき、GaN斜面におけるバンド構造は予想と異なる形状を示すと考えられる。図11は、再成長界面におけるバンド構造を示す。図11の(a)部を参照すると、高い濃度のドナー性欠陥を含む再成長界面におけるバンド構造が示される。二次元電子ガスが、p型電流ブロック層界面のポテンシャルにより狭窄されず、この結果、ドレインリーク不良に至ると考えられる。

【0085】

(実験例2)

・トランジスタの作製。

実験例1と同様にエピタキシャル成長によりnpn構造を成長する。この後に、反応性イオンエッチング(RIE)により、斜面を有する開口を上記のnpn構造に形成する。エッチングにより形成された斜面におけるドナー性欠陥の濃度を低減するために、発明者らは検討を行っている。

【0086】

上記実験例と同様にエッチングした2枚のnpn構造基板に、上記のSPM洗浄に加えて以下の処理を行う。テトラメチルアンモニウムヒドロキシド水溶液(濃度24パーセント、質量比)による前処理を行うこと;テトラメチルアンモニウムヒドロキシド液(濃度24パーセント、質量比)による第1処理及びフッ化水素及び過酸化水素(HF(50%):H2O2=5:1)の混合液による第2処理を行うこと。これらの処理を施したnpn構造基板を再びMOCVD炉において、厚さ0.5μmのアンドープGaN層の成長を個々のnpn構造基板に行う。この成長の後に、再成長のアンドープGaN層のエピ表面にショットキ電極を形成する。このショットキ電極を用いて、C−V測定により界面のキャリア濃度を測定する。

【0087】

テトラメチルアンモニウムヒドロキシド液は、シリコン酸化物(例えばSiO2)に対して高い選択性を示し、テトラメチルアンモニウムヒドロキシドは金属元素を含まないので、プロセスの清浄性に優れている。また、GaNの異方性エッチングにも有効であるので、RIEより形成される斜面のダメージ層を除去するために有効であると考えられる。実際にアンドープGaN表面にテトラメチルアンモニウムヒドロキシド処理を施した表面にアンドープGaN層を再成長し更にショットキゲートを形成したnpn構造基板では、ショットキリークが多く、再成長界面のドナー濃度を測定できない。発明者らの実験によれば、再成長界面は、メタルコンタクトの形成に比べてウェットエッチングの残留物に敏感である。

【0088】

発明者らの検討によれば、テトラメチルアンモニウムヒドロキシドのエッチング機構では、GaN系半導体中のIII族元素が水酸化物を形成しつつエッチングが進行することので、エッチング固液界面付近には、テトラメチルアンモニウムヒドロキシド液中に溶け出した水酸化物が過飽和状態であり、GaN系半導体表面に水酸化物が沈殿している状況が考えられる。したがって、テトラメチルアンモニウムヒドロキシド処理したGaN系半導体表面にGaN系半導体を再成長するとき、再成長界面にIII族元素の水酸化物が残留することになる。これ故に、再成長エピ成長の半導体の品質が劣化している可能性がある。

【0089】

アンドープGaN表面にテトラメチルアンモニウムヒドロキシド処理を施した後に、npn構造基板にさらにフッ化水素及び過酸化水素(HF(50%):H2O2=5:1)の混合液による追加の処理を行う。追加処理のGaN系半導体表面上にアンドープGaN層を再成長し更にショットキゲートを形成する。このショットキ電極を用いたC−V測定により界面のキャリア濃度を測定する。図12は、再成長界面にドナー性欠陥の濃度分布を示す図面である。このとき、ドナー性欠陥の濃度が、従来に比べて小さく、5×1017cm−3程度まで低減され、好ましくは例えば4×1017cm−3以下低減され、更に好ましくは3×1017cm−3以下まで低減されている。この濃度は、テトラメチルアンモニウムヒドロキシド処理しないいくつかのGaN系半導体表面において測定された濃度の最小値に比べて小さい。

【0090】

(実験例3)

・トランジスタの作製。

実験例1と同様にnpn構造を成長した後に、RIEでnpn構造をエッチングして、npn構造に斜面を形成する。その後に、テトラメチルアンモニウムヒドロキシド水溶液(濃度24パーセント)による第1処理及びフッ化水素及び過酸化水素(HF(50%):H2O2=5:1)の混合液による第2処理を行う。これらの処理を施した後に、実験例1と同様にアンドープGaN層及びアンドープAlGaN層の再成長を行ってHEMTエピ構造を形成する。このHEMTエピ構造に、実験例1と同様に電極を形成して、トランジスタを形成する。図13は、このトランジスタのId−Vd特性を示す。図13を参照すると、ドレインリークが改善されており、ゲートバイアス(Vg)に対してドレイン電流(Id)が変調される。優れた特性でトランジスタが動作している。再成長界面におけるドナー性欠陥の濃度を低減することにより、ドレイン耐圧が改善される。図11の(b)部に示されるように、低い濃度のドナー性欠陥を含む再成長界面におけるバンド構造では、ゲート電極からの電界が、チャネル層とキャリア供給層とのヘテロ界面において二次元電子ガスの生成を制御できる。また、このトランジスタは、第1及び第2処理を適用せずに作成されたトランジスタに比べて優れたサブスレシュホルド特性を示す。さらに、上記の実験例ではGaN基板上に多数のトランジスタが作成され、これらのトランジスタのId−Vd特性のばらつきが縮小される。

【0091】

テトラメチルアンモニウムヒドロキシド水溶液(濃度24パーセント)による第1処理並びにフッ化水素及び過酸化水素(HF(50%):H2O2=5:2)の混合液による第3処理を行って、同様にトランジスタを作製する。このトランジスタでは、ショットキリークが増加し、逆にドレイン耐圧が劣化する結果が得られる。過酸化水素(H2O2)でフッ化水素酸(HF)が希釈されたことによって、逆に水酸化物の除去効率が低下している可能性がある。

【0092】

第2溶液では、フッ化水素酸及び過酸化水素の容量比に関して、(フッ化水素酸)/(過酸化水素)>5/2であることができ、さらに(フッ化水素酸)/(過酸化水素)≧5であることが好ましい。テトラメチルアンモニウムヒドロキシドによる処理により半導体積層の第1処理面近傍には水酸化物が形成される。第2溶液が上記の比率であるとき、水酸化物の除去に加えてドナー性欠陥の低減に有効である。また、(フッ化水素酸)/(過酸化水素)の比率の上限は20であることができ、過酸化水素の濃度が不十分でドナー性欠陥の除去効率が低下するためである。

【0093】

電子ブロック層(p型GaN層)のMg濃度は1×1017cm−3以下では残留ドナー性界面欠陥を補償しきれずに電流ピンチオフが実現されず、Mg濃度は1×1019cm−3以上ではHEMT構造エピ再成長時に2次元電子ガス界面にまでMgが拡散して、ドレイン電流に影響する。

【0094】

図14は、本実施の形態に係る窒化物電子デバイスの構造を示す図面である。窒化物電子デバイスの一例として、ヘテロ接合トランジスタ11を説明する。ヘテロ接合トランジスタ11は、導電性の支持基体13と、半導体積層15と、チャネル層19と、キャリア供給層21と、ゲート電極23とを備える。支持基体13は、III族窒化物の主面13aを有すると共に、III族窒化物の裏面13bを有する。III族窒化物主面13aは好ましくはc面であり、良好な結晶成長のために僅かなオフ角を有することができる。このオフ角の範囲は例えば−0.7度以上−0.1度以下又は+0.1度以上+0.7度以下であることができる。支持基体13は導電性の自立III族窒化物支持体であることができる。半導体積層15は支持基体13の主面13a上に搭載される。半導体積層15は、支持基体13の主面13aの方向に向けて窪む開口部16を有する。開口部16は、例えば半導体積層15に形成されたメサ、凹部又は溝により規定されることができる。チャネル層19は、窒化ガリウム系半導体からなり、また半導体積層15の開口部16内に設けられる。キャリア供給層21は、III族窒化物半導体からなり、また半導体積層15の開口部16内に設けられると共に開口部16内のチャネル層19上に延在する。ゲート電極23はキャリア供給層21上に設けられ、開口部16内においてキャリア供給層21はチャネル層19とゲート電極23との間に位置する。キャリア供給層21のIII族窒化物のバンドギャップは、チャネル層19の窒化ガリウム系半導体のバンドギャップより大きく、チャネル層19とキャリア供給層21とはヘテロ接合20を成す。ゲート電極23はヘテロ接合20に沿った二次元電子ガスの生成を制御する。

【0095】

半導体積層15は、ドリフト層25、電流ブロックト層27及びn型半導体層29を含む。ドリフト層25、電流ブロックト層27及びn型半導体層29は、支持基体13の主面13aの上に順に設けられる。ドリフト層25は、n導電性を示し、例えば第1窒化ガリウム系半導体からなる。電流ブロックト層27は、p導電性を示し、例えば第2窒化ガリウム系半導体からなる。また、ドリフト層25は、支持基体13の主面13aと電流ブロックト層27との間に設けられる。電流ブロックト層27の側面27aとゲート電極23との間には、キャリア供給層21及びチャネル層19が延在する。

【0096】

n型半導体層29は例えばn導電性を有し、また電流ブロック層27上に設けられる。n型半導体層29は第3窒化ガリウム系半導体からなり、例えばn+型GaNからなり、n型半導体層29の第3窒化ガリウム系半導体のn型ドーパント濃度は例えば1×1016cm−3以上であることができる。n型半導体層29の厚さは0.1μm以上であり、1μm以下である。n型半導体層29は、半導体積層15の開口部16の側面16aに位置する側面29aを更に含む。電流ブロックト層27がn型半導体層29と支持基体13の主面13aとの間に設けられ、n型半導体層29の導電型と異なるp導電性を有する。

【0097】

既に説明したように、開口部16はエッチングにより形成される。エッチングの後においては、開口斜面にドナー性欠陥が残留している。本実施形態で説明された処理の後において、半導体積層15の開口部16の斜面とチャネル層19との界面におけるドナー性欠陥の濃度は5×1017cm−3以下である。半導体積層15の側面16aからチャネル層19に至る半導体領域内には、図14に示されるように、濃度5×1017cm−3以下のドナー性欠陥を含む薄い半導体層17が設けられる。この半導体層17は電流ブロック層27とチャネル層19との間に設けられ、またドナー性欠陥や電流ブロック層27からのp型ドーパントを含む窒化ガリウム系半導体からなる。半導体層17は、主にエッチングに起因するドナー性欠陥を含み、その厚さは50nm〜200nmと見積もられる。

【0098】

このヘテロ接合トランジスタ11によれば、半導体積層斜面とチャネル層との界面におけるドナー性欠陥の濃度が5×1017cm−3以下であるので、ドナー性欠陥に起因するチャネルリークを低減できる。これ故に、これまでに比べても良好なサブスレッショルド特性を窒化物電子デバイスに提供できる。

【0099】

チャネル層19の厚さは5nm以上であることができ、またチャネル層19の厚さは40nm以下であることができる。キャリア供給層21の厚さは20nm以上であることができ、キャリア供給層21の厚さは400nm以下であることができる。半導体層17が5×1017cm−3以下のドナー性欠陥濃度を示すとき、p型半導体層27は良好なバックゲート層として働くと共に、キャリア供給層21とチャネル層19との界面には、ゲート電極23の電位により制御可能な二次元電子ガスが生成される。

【0100】

図14に示されるように、本実験例では開口部16の底面16b(底面25d)はほぼc面(c軸に直交する面)に沿って延在している。図14においては、結晶座標系CRが示され、基準軸Cxはc軸の方向を示している。m面は結晶座標系CRのm軸に直交する面であり、a面は結晶座標系CRのa軸に直交する面である。開口部16の側面16aは、III族窒化物半導体のa面に対して傾斜し、II族窒化物半導体のm面に対して傾斜すると共に前記III族窒化物半導体のc面に対して傾斜している。本実験例では、開口部16の側面16aは、m軸又はa軸の方向に延在する。

【0101】

ヘテロ接合トランジスタ11は、ソース電極31を更に備えることができる。ソース電極31がn型半導体層29に電位を供給する。また、ソース電極31はチャネル層19に接触を成して、チャネル層19にキャリアを供給できる。ソース電極31は電流ブロックト層27に接続されている。電流ブロックト層27が、ドナー性欠陥を含む半導体における補償に打ち勝ってチャネル層に接合を成すとき、電流ブロックト層27からのバイアスがチャネル層に作用する。電流ブロックト層27の電位はソース電極31から供給されて、これがバックバイアスとなる。このバックバイアスは、ヘテロ接合トランジスタ11のノーマリオフ動作に好適である。

【0102】

ヘテロ接合トランジスタ11では、支持基体13の裏面13bに設けられたドレイン電極33を更に備えることができる。ドレイン電極33が支持基体13の裏面13bに設けられるので、ドレイン電極33をゲート電極23及びソース電極31から隔てることができる。これ故に、高耐圧の実現に有効である。ドレイン電極33は例えばNi/Alからなることができ、ソース電極31は例えばTi/Alからなることができる。ゲート電極23は、例えばNi/Au、Pt/Au、Pd/Au、Mo/Au等からなることができる。

【0103】

ドリフト層25は、半導体積層15の開口部16の側面16aに位置する端面25aを有する。電流ブロックト層27は、半導体積層15の開口部16の側面16aに位置する側面27aを有する。チャネル層19は、n型半導体層29の側面29a、電流ブロックト層27の側面27a及びドリフト層25の側面25a及び上面25b上に設けられる。

【0104】

ドリフト層25の第1の面25bは、電流ブロックト層27の第2の面27cと接合を成す。ドリフト層25の第2の面25cは、支持基体13の主面13aと接合を成す。n型半導体層29の第1の面29bはチャネル層19と接合を成す。n型半導体層29の第2の面29cは、電流ブロックト層27の第1の面27bと接合を成す。

【0105】

開口部16の側面16aは、チャネル層19の裏面に接合を成し、チャネル層19の裏面は電流ブロックト層27の側面27aと接合を成すことができる。チャネル層19の裏面はn型半導体層29の側面29aと接合を成す。チャネル層19の裏面はドリフト層25の側面25aと接合を成す。キャリア供給層21の裏面は、チャネル層19の表面に接合を成す。ゲート電極18は、キャリア供給層21にショットキ接合を成すことができる。

【0106】

ドリフト層25の厚さは1μm以上であることができ、ドリフト層25の厚さは10μm以下であることができる。ドリフト層25の第1窒化ガリウム系半導体のn型ドーパント濃度は1×1015cm−3以上であることができ、第1窒化ガリウム系半導体のn型ドーパント濃度は3×1016cm−3以上であることができる。ドリフト層25は、オフ動作時のソース−ドレイン間における耐圧の向上と導通時のオン抵抗の低減とを両立を可能にする。高すぎるドナー濃度は、ソース−ドレイン間における耐圧を低下させる。低すぎるドナー濃度は、オン抵抗を増加させる。

【0107】

電流ブロック層27の厚さは0.1μm以上であることができ、ドレイン耐圧維持に有効だからである。電流ブロック層27の厚さは2μm以下であることができ、実効チャネル長を短くして低オン抵抗を実現できるからである。電流ブロック層27の第2窒化ガリウム系半導体のp型ドーパント濃度は5×1016cm−3以上であり、第2窒化ガリウム系半導体のp型ドーパント濃度は5×1018cm−3以下であることができる。ドリフト層17直上に設けられた電流ブロック層27において、上記の範囲におけるアクセプタ濃度は、窒化物電子デバイスにおける非導通の際のソース−ドレイン間の耐圧として所望の値を提供できる。

【0108】

ヘテロ接合トランジスタ11の一実施例を以下に示す。

支持基体13:n型GaN(キャリア濃度:1×1019cm−3)。

薄い半導体層17:ドナー性欠陥を含むGaN(ドナー性欠陥濃度:5×1017cm−3以下)。

チャネル層19:アンドープGaN(キャリア濃度:1×1015m−3、厚さ:30nm)。

キャリア供給層21:アンドープAlGaN(厚さ:30nm、Al組成比0.25)。

n型半導体層29:n型GaN(キャリア濃度:1×1018m−3、厚さ:0.3μm)。

電流ブロックト層27:p+型GaN(キャリア濃度:1×1018m−3、厚さ:0.5μm)。

ドリフト層25:アンドープGaN(キャリア濃度:1×1015m−3、厚さ:5μm)。

このヘテロ接合トランジスタによれば、実用的な構造の一例が提供される。この窒化物半導体電子デバイスによれば、ソース電極31からドリフト層25までの電流経路における抵抗増加を避けることができる。なお、ヘテロ接合トランジスタ11は、キャリア供給層21とゲート電極23との間に設けられた絶縁膜を更に備えてもよい。この絶縁膜を介してキャリア供給層21及びチャネル層19に電界が及ぶ。

【0109】

ヘテロ接合トランジスタ11の一実施例では、ドリフト層29の第1の窒化ガリウム系半導体はn型GaNであることができる。ドリフト層29の膜厚は1μm以上であり、10μm以下であることができる。ドリフト層のキャリア濃度は1×1015cm−3以上であり、3×1016cm−3以下であることができる。このヘテロ接合トランジスタ11では、上記のドリフト層29を用いて、高耐圧に良い窒化物電子デバイスを提供できる。ドリフト層29のn型GaNにはシリコン(Si)が添加されていてもよい。

【0110】

また、ヘテロ接合トランジスタ11の一実施例では、電流ブロック層27の第2の窒化ガリウム系半導体はp型GaNであることができる。電流ブロック層27の膜厚は0.1μm以上であり、2.0μm以下であることができる。電流ブロック層27のp型GaNにはマグネシウム(Mg)が添加されており、電流ブロック層27のMg濃度は5×1016cm−3以上であり、5×1018cm−3以上であることができる。このヘテロ接合トランジスタ11では、電流ブロック層27はチャネル層29に対してバックゲートを提供すると共に、電流ブロック層27の膜厚はチャネル長を規定する。ドナー性不純物の濃度は、電流ブロック層27のp型ドーパント濃度に比べて十分に小さく低減される。

【0111】

また、ヘテロ接合トランジスタ11の一実施例では、コンタクト25層の第3の窒化ガリウム系半導体はn型GaNであることができる。コンタクト層25の膜厚は0.1μm以上であり、1.0μm以下であることができる。コンタクト層25のn型GaNにはシリコン(Si)が添加されており、コンタクト層25のSi濃度は1×1016cm−3以上であることができる。ヘテロ接合トランジスタ11によれば、ソース抵抗を低くできる。

【0112】

また、ヘテロ接合トランジスタ11の一実施例では、キャリア供給層21はAlXGa1−XN(0<X<1)層を含むことができる。キャリア供給層21の厚さは5nm以上であり、40nm以下であることができる。チャネル層19はアンドープGaN層を含み、チャネル層19の厚さは20nm以上であり、400nm以下であることができる。キャリア供給層21はチャネル層19にヘテロ接合を成す。このヘテロ接合トランジスタ11では、高い移動度で低いチャネルリークのヘテロ接合トランジスタを提供できる。

【0113】

本発明は、本実施の形態に開示された特定の構成に限定されるものではない。

【産業上の利用可能性】

【0114】

本実施の形態によれば、リーク特性のばらつき幅を低減可能な、窒化物電子デバイスを作製する方法を提供でき、また、より優れたリーク特性を示す窒化物電子デバイスを提供できる。

【符号の説明】

【0115】

10a…成長炉、11…ヘテロ接合トランジスタ、13…導電性基板、15…半導体積層、16…開口、17…低ドナー性欠陥層、19…チャネル層、20…ヘテロ接合、21…バリア層、23…ゲート電極、25…ドリフト層、27…電流ブロック層、29…コンタクト層、31…ソース電極、33…ドレイン電極、CR…結晶座標系、51…基板、53、53b…半導体積層、55…第1のIII族窒化物半導体層、57…第2のIII族窒化物半導体層、59…第3のIII族窒化物半導体層、E…エピタキシャル基板、63…マスク、65…開口、65d…側面、65e…底面、R11、R12、R13、R31、R32、R33…基準面、69…チャネル層、71…キャリア供給層、73…ソース電極、77…ゲート絶縁膜、79…ゲート電極。

【技術分野】

【0001】

本発明は、窒化物電子デバイス、及び窒化物電子デバイスを作製する方法に関する。

【背景技術】

【0002】

特許文献1には、導電性基板上にヘテロ電界効果トランジスタを作製する方法が記載されている。特許文献2には、III 族窒化物半導体のウェットエッチング方法および半導体装置製造方法が記載されている。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開2006−286942号公報

【特許文献2】特開2008−10608号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

特許文献2では、n型GaN基板のR面表面上にSiO2からなる層間絶縁膜を形成する。次に、この層間絶縁膜をドライエッチングして、コンタクトホールを形成する。次に、摂氏90度の温度で、濃度25%のTMAH水溶液を用い、ウェットエッチングを行う。エッチングされた面の面方位はR面であるので、TMAH水溶液によるエッチングにより、エッチングのダメージ層が除去される。その後に、n型GaN基板のR面表面に金属膜を形成する。

【0005】

一方、発明者らの検討における半導体素子の作製では、n型III族窒化物半導体からなる自立基板の主面の上に、第1、第2及び第3のIII族窒化物半導体層を順に設けたエピタキシャル基板を形成した後に、第3のIII族窒化物半導体層から第2のIII族窒化物半導体層を介して第1のIII族窒化物半導体層に至る斜面を有する開口をエッチングによりエピタキシャル基板に形成して、ドリフト層、電流ブロック層及びコンタクト層並びに開口の斜面を含む半導体積層を形成する。この半導体積層の上に、III族窒化物からなるチャネル層及びIII族窒化物からなるキャリア供給層をエピタキシャル成長する。このように成長されたHEMTエピ構造を有する窒化物電子デバイスの作製では、低いリーク特性の窒化物電子デバイスがあれば、高いリーク特性ゆえにゲート電極からの電界に応じたスイッチ動作を示さない窒化物電子デバイスもある。つまり、窒化物電子デバイスにおけるチャネルリークにばらつきが大きい。窒化物電子デバイス間におけるリーク特性の広いばらつきに関する発明者らの検討から、大きなばらつきのリーク特性の原因を特定できた。また、この結果として、より優れたリーク特性を示す窒化物電子デバイスを得るに至った。

【0006】

本発明は、このような事情を鑑みて為されたものであり、リーク特性のばらつき幅を低減可能な、窒化物電子デバイスを作製する方法を提供することを目的とし、また、より優れたリーク特性を示す窒化物電子デバイスを提供することを目的とする。

【課題を解決するための手段】

【0007】

本発明に係る発明は、窒化物電子デバイスを作製する方法に係る。この方法は、(a)n型III族窒化物半導体からなる自立基板の主面の上に、ドリフト層、電流ブロック層及びコンタクト層のための第1、第2及び第3のIII族窒化物半導体層を順に設けたエピタキシャル基板を準備する工程と、(b)前記第3のIII族窒化物半導体層から前記第2のIII族窒化物半導体層を介して前記第1のIII族窒化物半導体層に至る斜面を有する開口をエッチングにより前記エピタキシャル基板に形成して、前記ドリフト層、前記電流ブロック層及び前記コンタクト層並びに前記開口の斜面を含む半導体積層を形成する工程と、(c)前記半導体積層を形成した後に、テトラメチルアンモニウムヒドロキシドを含む第1溶液を用いた第1処理を前記半導体積層に行うと共に、該第1処理の後に、フッ化水素酸及び過酸化水素を含む第2溶液を用いた第2処理を前記半導体積層に行って、前記第1処理及び前記第2処理による処理面を前記半導体積層に提供する工程と、(d)前記半導体積層の前記処理面の上に、III族窒化物からなるチャネル層及びIII族窒化物からなるキャリア供給層をエピタキシャル成長して、基板生産物を形成する工程とを備える。前記キャリア供給層の前記III族窒化物のバンドギャップは、前記チャネル層の前記窒化ガリウム系半導体のバンドギャップより大きく、前記第1及び第3のIII族窒化物半導体層はn型を有し、前記第2のIII族窒化物半導体層はp型を有する。

【0008】

この窒化物電子デバイスを作製する方法(以下「作製方法」として参照する)によれば、エピタキシャル基板に開口をエッチングにより形成するので、半導体積層は、エピタキシャル基板の表面に由来する主面と、エッチングにより形成される開口の斜面とを有する。半導体積層の開口がエッチングにより形成されるので、開口斜面にはエッチングによるドナー性欠陥が形成される。第1溶液を用いた処理は、半導体積層の主面及び斜面の両方に適用される。この処理に引き続き、第2溶液を用いた処理が半導体積層の表面に適用される。フッ化水素酸及び過酸化水素を含む第2溶液による処理は、第1溶液の処理により半導体積層からの反応生成物として生成された水酸化物の濃度を半導体積層の表面において低減するために有効である。第1溶液による処理及び第2溶液による処理の組み合わせ処理は、半導体積層表面上へ成長されるチャネル層及びキャリア供給層へのドナー性欠陥の影響を低減できる。この作製方法によれば、リーク電流及びそのばらつき幅を低減できる。

【0009】

また、第1溶液及び第2溶液を用いた処理により、製造工程におけるばらつきに影響が低減されて、また優れたサブスレッショルド特性を有する素子を作製できる。

【0010】

本発明に係る作製方法は、前記電流ブロック層に到達するコンタクトホールを前記半導体積層に形成する工程と、前記コンタクトホールを形成した後に、前記半導体積層の前記コンタクト層の上に電極を形成する工程とを備えることができる。

【0011】

この作製方法によれば、第2及び第3の窒化ガリウム系半導体層に対する電極を形成できる。

【0012】

本発明に係る作製方法では、前記第2溶液では、フッ化水素酸及び過酸化水素の容量比に関して、(フッ化水素酸)/(過酸化水素)≧5であることが好ましい。

【0013】

この作製方法によれば、テトラメチルアンモニウムヒドロキシドによる処理により水酸化物が形成される。第2溶液が上記の比率であるとき、水酸化物の除去に加えてドナー性欠陥の低減に有効である。

【0014】

本発明に係る作製方法では、前記自立基板の前記主面は、前記n型III族窒化物半導体のc面に対して−0.7度以上−0.1度以下又は+0.1度以上+0.7度以下の角度であることができる。この作製方法によれば、自立基板の主面が上記の角度範囲にあるとき、第1溶液による処理が開口側面に有効に働く。また、本発明に係る作製方法では、前記自立基板の前記主面は実質的にc面であることができる。

【0015】

本発明に係る作製方法では、前記第1処理において、前記第1溶液の温度は、摂氏50度以上であり、摂氏100度未満であることが好ましい。また、前記第1溶液は水溶液であることができる。

【0016】

この作製方法によれば、温度が摂氏50度以上であるとき、良好なエッチング速度が提供される。温度が摂氏100度以上では、溶液中に気泡が発生し、被処理の表面に付着する可能性がある。また、溶媒の蒸発により第1溶液の濃度が変化していく。第1溶液の溶媒に水を適用することができる。

【0017】

本発明に係る作製方法では、前記第1処理において、前記第1溶液の濃度は、5パーセント以上であり、50パーセント以下であることができる。この作製方法によれば、5パーセント以上の濃度では、良好なエッチング速度が提供される。50パーセント以下の濃度では、反応生成物が半導体積層表面の近傍で過飽和になる可能性があり、これ故に、処理時間が経過するにつれて沈殿物を生じる可能性がある。

【0018】

本発明に係る作製方法では、前記チャネル層及び前記キャリア供給層の材料の組み合わせは、前記チャネル層/前記キャリア供給層として記載したとき、InGaN/AlGaN、GaN/AlGaN及びAlGaN/AlNのいずれか一つであることができる。この作製方法によれば、良好な電流特性を提供できる好適なチャネル構造の組み合わせが提供される。

【0019】

本発明に係る作製方法では、前記第1〜第3のIII族窒化物半導体層の材料の組み合わせは、前記第3のIII族窒化物半導体層/前記第2のIII族窒化物半導体層/前記第1の窒化ガリウム系半導体層として記載したとき、n+型GaN/p型GaN/n型GaNまたはn+型GaN/p型AlGaN/n型GaNであることができる。この作製方法によれば、半導体積層を構成する好適な組み合わせが提供される。

【0020】

本発明に係る作製方法は、前記チャネル層及び前記キャリア供給層をエピタキシャル成長した後に、前記基板生産物の上に前記開口の前記斜面にゲート電極を形成する工程を備えることができる。

【0021】

この作製方法によれば、開口斜面にゲート電極が設けられるので、半導体積層の開口斜面のドナー性不純物が低減されるので、チャネルリーク電流が低減される。

【0022】

本発明に係る作製方法は、前記チャネル層及び前記キャリア供給層をエピタキシャル成長した後に、前記基板生産物の上に絶縁膜を形成する工程と、前記絶縁膜を成長した後に、前記基板生産物の上に前記開口の前記斜面にゲート電極を形成する工程とを備えることができる。

【0023】

この作製方法によれば、ドナー性不純物が低減された半導体積層斜面上のチャネル層に、開口斜面上の絶縁膜を介してゲート電極からの電界を印加できるので、チャネルリーク電流が低減される。

【0024】

本発明に係る作製方法では、前記半導体積層の前記処理面のドナー性不純物の濃度は5×1017cm−3以下であることができる。

【0025】

この作製方法によれば、第1及び第2溶液を用いた前処理により、再成長面のために下地が提供される。この下地の前処理面上にチャネル層及びキャリア供給層がエピタキシャル成長される。この成長により形成される界面のドナー性不純物濃度を低減できる。

【0026】

本発明に係る作製方法では、前記チャネル層はアンドープ窒化ガリウム系半導体層を含み、前記チャネル層の厚さは20nm以上であり、400nm以下であることができる。

【0027】

この作製方法によれば、チャネル層はアンドープ層であるので、ドナー性不純物に敏感である一方で、高いキャリア移動度を提供できる。

【0028】

本発明に係る作製方法では、前記電流ブロック層の第2のIII族窒化物半導体はp型GaNであり、前記電流ブロック層の膜厚は0.1μm以上〜2.0μm以下であり、前記電流ブロック層のp型GaNにはマグネシウム(Mg)が添加されており、前記電流ブロック層のMg濃度は、5×1016cm−3以上であり、5×1018cm−3以上であることができる。

【0029】

この作製方法によれば、電流ブロック層はチャネル層に対してバックゲートを提供すると共に、電流ブロック層の膜厚はチャネル長を規定する。ドナー性不純物の濃度は、電流ブロック層のp型ドーパント濃度に比べて低減されて、十分に小さくなる。

【0030】

本発明に係る作製方法は、前記自立基板の上にドレイン電極を形成する工程を備えることができる。この作製方法によれば、自立基板の主面は実質的にc面であるとき、開口の底部の面方位は実質的にc面である。第1溶液は、c面に対するドナー性欠陥の処理に比べて、電流ブロック層上の傾斜面上のドナー性欠陥の処理に優れる。開口の底部のドナー性欠陥は、n型層とn型層との界面に残留する。

【0031】

本発明に係る窒化物電子デバイスは、(a)支持基体の主面上に順に設けられたドリフト層、電流ブロック層及びコンタクト層を含むと共に、前記コンタクト層から前記電流ブロック層を介して前記ドリフト層に至る側面を有する半導体積層と、(b)前記側面に設けられ、窒化ガリウム系半導体からなるチャネル層と、(c)前記側面に設けられ、窒化ガリウム系半導体からなるキャリア供給層と、(d)前記側面に設けられたゲート電極と、(e)前記半導体積層の上に設けられたソース電極と、(f)前記半導体積層及び前記支持基体のいずれかに設けられたドレイン電極とを備える。前記半導体積層の前記側面と前記チャネル層との界面におけるドナー性欠陥の濃度は5×1017cm−3以下であり、前記ドリフト層は、第1の窒化ガリウム系半導体からなり、前記電流ブロック層は、第2の窒化ガリウム系半導体からなり、前記コンタクト層は、第3の窒化ガリウム系半導体からなり、前記チャネル層は前記キャリア供給層との前記側面との間に設けられ、前記キャリア供給層の前記III族窒化物のバンドギャップは、前記チャネル層の前記窒化ガリウム系半導体のバンドギャップより大きく、前記ドリフト層及び前記コンタクト層はn型を有し、前記電流ブロック層はp型を有する。

【0032】

この窒化物電子デバイスによれば、半導体積層の側面とチャネル層との界面におけるドナー性欠陥の濃度は5×1017cm−3以下であるので、ドナー性欠陥に起因するチャネルリークを低減できる。これ故に、これまでに比べても良好なドレインリーク特性を窒化物電子デバイスに提供できる。

【0033】

本発明に係る窒化物電子デバイスでは、前記ドリフト層の第1の窒化ガリウム系半導体はn型GaNであり、前記ドリフト層の膜厚は1μm以上であり、10μm以下であり、前記ドリフト層のn型GaNにはシリコン(Si)が添加されており、前記ドリフト層のSi濃度は、1×1015cm−3以上であり、3×1016cm−3以下であることができる。

【0034】

この窒化物電子デバイスによれば、上記のドリフト層を用いて、高耐圧に良い窒化物電子デバイスを提供できる。

【0035】

本発明に係る窒化物電子デバイスでは、前記電流ブロック層の第2の窒化ガリウム系半導体はp型GaNであり、前記電流ブロック層の膜厚は0.1μm以上であり、2.0μm以下であり、前記電流ブロック層のp型GaNにはマグネシウム(Mg)が添加されており、前記電流ブロック層のMg濃度は、5×1016cm−3以上であり、5×1018cm−3以下であることができる。

【0036】

この窒化物電子デバイスによれば、電流ブロック層はチャネル層に対してバックゲートを提供すると共に、電流ブロック層の膜厚はチャネル長を規定する。ドナー性不純物の濃度は、電流ブロック層のp型ドーパント濃度に比べて十分に小さく低減される。

【0037】

本発明に係る窒化物電子デバイスでは、前記コンタクト層の第3の窒化ガリウム系半導体はn型GaNであり、前記コンタクト層の膜厚は0.1μm以上であり、1.0μm以下であり、前記コンタクト層のn型GaNにはシリコン(Si)が添加されており、前記コンタクト層のSi濃度は、1×1016cm−3以上であることができる。この窒化物電子デバイスによれば、ソース抵抗を低くできる。

【0038】

本発明に係る窒化物電子デバイスでは、前記キャリア供給層はAlXGa1−XN(0<X<1)層を含み、前記キャリア供給層の厚さは5nm以上であり、40nm以下であり、前記チャネル層はアンドープGaN層を含み、前記チャネル層の厚さは20nm以上であり、400nm以下であり、前記キャリア供給層は前記チャネル層にヘテロ接合を成すことができる。

【0039】

この窒化物電子デバイスによれば、高い移動度で低いチャネルリークのヘテロ接合トランジスタを提供できる。

【発明の効果】

【0040】

以上説明したように、本発明によれば、リーク特性のばらつき幅を低減可能な、窒化物電子デバイスを作製する方法を提供でき、また、より優れたリーク特性を示す窒化物電子デバイスを提供できる。

【図面の簡単な説明】

【0041】

【図1】図1は、本実施の形態に係る窒化物電子デバイスを作製する方法における主要な工程を模式的に示す図面である。

【図2】図2は、本実施の形態に係る窒化物電子デバイスを作製する方法における主要な工程を模式的に示す図面である。

【図3】図3は、本実施の形態に係る窒化物電子デバイスを作製する方法における主要な工程を模式的に示す図面である。

【図4】図4は、本実施の形態に係る窒化物電子デバイスを作製する方法における主要な工程を模式的に示す図面である。

【図5】図5は、本実施の形態に係る窒化物電子デバイスを作製する方法における主要な工程を模式的に示す図面である。

【図6】図6は、本実施の形態に係る窒化物電子デバイスを作製する方法における主要な工程を模式的に示す図面である。

【図7】図7は、本実施の形態に係る窒化物電子デバイスを作製する方法における主要な工程を模式的に示す図面である。

【図8】図8は、チャネル層及びキャリア供給層を成長するための再成長温度シーケンスを示す図面である。

【図9】図9は、第1処理及び第2処理を行わずに作製されたトランジスタの測定結果のうち所望でない性能を示すトランジスタのId−Vd特性を示す図面である。

【図10】図10は、第1処理及び第2処理を行わずに形成された再成長界面にドナー性欠陥の濃度分布を示す図面である。

【図11】図11は、高い濃度のドナー性欠陥を含む再成長界面におけるバンド構造を示す図面である。

【図12】図12は、第1処理及び第2処理の後に形成された再成長界面にドナー性欠陥の濃度分布を示す図面である。

【図13】図13は、実施例におけるトランジスタのId−Vd特性を示す図面である。

【図14】図14は、本実施の形態に係る窒化物電子デバイスの構造を示す図面である。

【発明を実施するための形態】

【0042】

引き続いて、添付図面を参照しながら、窒化物電子デバイス、及び窒化物電子デバイスを作製する方法に係る実施の形態を説明する。可能な場合には、同一の部分には同一の符号を付する。

【0043】

図1〜図7は、本実施の形態に係る窒化物電子デバイス、エピタキシャル基板、及び基板生産物を作製する方法における主要な工程を模式的に示す図面である。

【0044】

図1の(a)部で示されるように、最初の工程では、窒化物電子デバイスのための自立基板を準備する。この基板は導電性を示し、例えば六方晶系のIII族窒化物からなることができる。自立のIII族窒化物半導体基板(以下、図1の(a)部で番号「51」で示される)は、例えばGaN、AlN等からなることができる。基板51は主面51a及び裏面51bを有する。

【0045】

図1の(a)部では、c軸方向を示すc軸ベクトルVCが示されている。好適な実施例では、このIII族窒化物半導体基板51(以下「基板51」として参照する)主面51aはc面からなることができるが、基板51のIII族窒化物のc軸に対して僅かなオフ、例えば−0.7度以上−0.1度以下又は+0.1度以上+0.7度以下の範囲のオフを有することができる。

【0046】

熱処理工程では、図1の(b)部に示されるように、III族窒化物半導体基板51を成長炉10aに配置した後に、III族窒化物半導体基板51の熱クリーニングを行う。熱クリーニングは、例えばアンモニア及び水素を含む雰囲気52においてIII族窒化物半導体基板51の熱処理によって行われる。熱処理は、例えば10分間程度である。また、熱処理温度は、例えば摂氏1030度程度である。炉内圧力は例えば100Torrである。

【0047】

第1成長工程では、図2の(a)部に示されるように、n型III族窒化物半導体からなる基板51の主面51aの上に、ドリフト層、電流ブロック層及びコンタクト層のための第1〜第3のIII族窒化物半導体層を順に設けたエピタキシャル基板Eを準備する。本実施例では、エピタキシャル基板Eは、基板51の主面51aに成長された半導体積層53を含む。半導体積層53の形成では、n−型窒化ガリウム系半導体からなる第1のIII族窒化物半導体層55、p型窒化ガリウム系半導体からなる第2のIII族窒化物半導体層57、及びn+型窒化ガリウム系半導体のための第3のIII族窒化物半導体層59を基板51の主面51a上に順に成長して、エピタキシャル基板Eを作製する。この成長は、例えば有機金属気相成長法で行われる。ドリフト層の第1のIII族窒化物半導体層55は、例えば厚さ5μmのアンドープGaNからなり、電流ブロック層の第2のIII族窒化物半導体層57は例えば厚さ0.5μmのMgドープp型GaNからなり、コンタクト層の第3のIII族窒化物半導体層59は例えば厚さ0.3μmのSiドープn+型GaNからなる。半導体積層53における接合61a、61bの各々も、基板51の主面51aの面方位と同じ面方位を示す。このとき、半導体積層53の厚さは5.8μmである。

【0048】

エピタキシャル基板Eを成長炉10aから取り出した後に、加工工程では、半導体積層53に開口を形成する。加工工程に先だって、マスク形成工程を行う。マスク形成のためにいくつかの工程が行われる。まず、図2の(b)部に示されるように、半導体積層53の開口を規定するためのマスクを形成するために、厚さTRのレジスト膜60を塗布する。次いで、露光及び現像工程では、図3の(a)部に示されるように、フォトリソグラフィ法を用いてレジスト膜60にパターン形成して、パターン形成されたレジスト層62を形成する。レジスト層62に形成されたパターンは、開口部の形状を規定する。レジスト層62は、露光及び現像により形成された側面62a及び上面62bを含む。露光及び現像工程の後に、ベーク工程を行う。ベーク工程では、図3の(b)部に示されるように、パターン形成されたレジスト層62をベーク装置10bでベークして、ベーク及びパターン形成されたレジスト膜、つまりマスク63を形成する。マスク63は、開口63aと、平坦な上面63b、上面63bに対して傾斜した側面63cを有する。ベーク条件は、レジスト膜厚に依存するが、例えば窒素雰囲気で、摂氏90度の熱処理温度、及び5分の熱処理時間である。マスク63の開口63aは、半導体積層53に形成される開口の形状及び位置を規定する。上記の実施例では、マスク63が、例えばレジスト膜から形成されたけれども、マスク63の形成に、シリコン酸化膜が用いられることができる。

【0049】

マスク63は、半導体積層53に形成される開口の形状及び位置を規定する開口63aを有する。上記のように、フォトリソグラフィで半導体積層53の表面53aにマスク63を形成した後に、図4の(a)部に示されるように、エピタキシャル基板Eの加工を行う。加工のために、エッチング装置10bにエピタキシャル基板Eを配置する。エッチング装置10c及びマスク63を用いて、半導体積層53のドライエッチングを行う。このドライエッチングは、例えば反応性イオンエッチング(RIE)であることができる。エッチャントとして、例えば塩素ガス、BCl3、CH4、アルゴン等を使用できる。マスク63を用いたエッチングにより、半導体積層53に開口65が形成される。開口形成の結果として、開口65を含む半導体積層53bが形成される。

【0050】

第3のIII族窒化物半導体層59から第2のIII族窒化物半導体層57を介して第1のIII族窒化物半導体層55に至る斜面を有する開口65をエッチングによりエピタキシャル基板Eに形成して、ドリフト層、電流ブロック層及びコンタクト層並びに開口65の斜面65dを含む半導体積層53bを形成する。開口65は、半導体積層53bの表面53aのコンタクト層の第3のIII族窒化物半導体層59からドリフト層の第1のIII族窒化物半導体層55に到達する。開口65は側面65d及び底面65eによって規定される。開口65の側面65dには、ドリフト層(以下、番号「55」して参照する)の側面55a及び底面55b、電流ブロック層(以下、番号「57」して参照する)の側面57a、及びコンタクト層(以下、番号「59」して参照する)の側面59aが現れている。開口65の底面65eには、ドリフト層の底面55bが現れている。好適な実施例では、基板51の主面51aは{0001}面からなるので、側面65dは{0001}面に対して傾斜している。

【0051】

加工工程の最後に、図4の(b)部に示されるように、マスク63が除去される。この結果、基板生産物SP1が形成される。基板生産物SP1では、開口65は、第1〜第3部分65a、65b、65cを有する。第1の部分65aでは、ドリフト層55の底面55b(底面65e)が露出している。第2の部分65b及び第3の部分65cでは、開口65の側面65dが、ドリフト層の第3のIII族窒化物半導体層55の底面55bから半導体積層53bの表面53aまで傾斜して延在する。

【0052】

図4の(b)部では、単一の開口65が描かれているけれども、基板51には多数の開口が配列されている。これ故に、半導体積層53bは、開口65の形状に応じて、メサ形状、或いは凹部(例えば溝)を含む形状を成す。側面65dは、基板51の主面51aに対して傾斜しており、また半導体積層53bの表面53aに対して傾斜している。側面65dの具体的な傾斜角は、エッチングにより制御されることができる。

【0053】

側面65dの一方は、全体としては、基準面R11に沿って延在しており、側面65dの他方は、全体としては、基準面R12に沿って延在している。これらの基準面R11、R12はIII族窒化物基板51のc軸の方向を示す基準軸Cx及び基板51の主面51aに対して傾斜している。基準面R11、R12の法線はc軸に対して傾斜しており、半導体積層53bの主面53aは基準面R13に沿って延在している。好適な実施例では、半導体積層53bの主面53aは基板51の主面51aと実質的に平行であることができる。基準面R11、R12(つまり、側面65d)と基準面R13(主面63a、51a)との成す角度は例えば5度〜40度の範囲にあることができる。

【0054】

開口65を形成した後に、半導体積層53bの表面53a及び側面65d上にHEMT構造の再成長を行う。発明者らの知見によれば、ドライエッチングにより形成した斜面には、ドナー性欠陥が残留している。この斜面への再成長界面がn型導電性を持ち、この界面特性がトランジスタ形成後のドレインリーク不良を引き起こす。

【0055】

この特性不良を避けるために、半導体積層53bを形成した後に、第1処理工程では、図5の(a)部に示されるように、テトラメチルアンモニウムヒドロキシドを含む第1溶液を用いた第1処理を処理装置10dで行って、半導体積層53bに第1処理面65fを形成する。

【0056】

好適な実施例では、この基板51の主面51aはc面からなることができるが、基板51のIII族窒化物のc軸に対して僅かなオフ、例えば−0.7度以上−0.1度以下又は+0.1度以上+0.7度以下の範囲のオフを有することができる。上記の角度範囲は、デバイスに有用であり、基板51の主面51aが上記の角度範囲にあるとき、第1溶液による処理が開口側面に有効に働く。

【0057】

また、第1溶液の温度は、摂氏50度以上であり、摂氏100度未満であることが好ましい。第1溶液による処理温度が摂氏50度以上であるとき、良好なエッチング速度が提供される。第1溶液による処理温度が摂氏100度以上では、溶液中に気泡が発生し、被処理の表面に付着する可能性がある。また、溶媒の蒸発により第1溶液の濃度が変化していく。第1溶液に水溶液を適用することができる。第1溶液の濃度(質量比)は5パーセント以上であり、50パーセント以下であることができる。この方法によれば、5パーセント以上の濃度では、良好なエッチング速度が提供される。50パーセント以下の濃度では、反応生成物が半導体積層表面の近傍で過飽和になる可能性があり、これ故に、処理時間が経過するにつれて沈殿物を生じる可能性がある。

【0058】

第1処理工程に引き続き第2処理工程を行う。第2処理工程では、テトラメチルアンモニウムヒドロキシド処理の後に、図5の(b)部に示されるように、フッ化水素酸及び過酸化水素を含む第2溶液を用いた第2処理を半導体積層53bに処理装置10eで行って、半導体積層53bに第2処理面65gを形成する。第2処理工程の後において、半導体積層53bの処理面65gのドナー性不純物の濃度は5×1017cm−3以下であることができる。第1及び第2溶液を用いた処理による前処理で再成長面が提供される。この再成長面にチャネル層及びキャリア供給層がエピタキシャル成長される。この再成長面のドナー性不純物の濃度が低減される。

【0059】

第2溶液では、フッ化水素酸及び過酸化水素の容量比に関して、(フッ化水素酸)/(過酸化水素)≧5であることが好ましい。テトラメチルアンモニウムヒドロキシドによる処理により半導体積層53bの第1処理面近傍には水酸化物が形成される。第2溶液が上記の比率であるとき、水酸化物の除去に加えてドナー性欠陥の低減に有効である。第2溶液の温度は、摂氏25度以上であり、摂氏50度以下であることが好ましい。第1溶液による処理温度が摂氏25度以上であるとき、水酸化物とドナー性欠陥を効率的に除去することができるからである。第1溶液による処理温度が摂氏50度以下では、フッ化水素の揮発を抑えて薬液の降下が持続される。

【0060】

必要な場合には、チャネル層及びキャリア供給層の成長に先立って基板生産物SP1の前処理(例えば、洗浄)を行った後に、次の工程において基板生産物SP1を成長炉10aに配置する。

【0061】

第1再成長工程では、アンモニア及びIII族元素原料を含む原料ガスG1を成長炉10aに供給して、図6の(a)部に示されるように、半導体積層53bの主面53a、開口65の第2処理面65g及び底面65e上に、チャネル層69を成長温度TG1で成長する。チャネル層69は窒化ガリウム系半導体からな、例えばアンドープ窒化ガリウム系半導体層からなることができる。チャネル層68は、第1の部分69a、第2の部分69b及び第3の部分69cを含む。第1の部分69aは、開口65の側面65d(つまり、処理面65g)上に成長され、基準面R21に沿って延在する。基準面R21は、チャネル層69の窒化ガリウム系半導体のc軸に直交する面及び基板51の主面51aに対して傾斜する。第2の部分69bは、半導体積層53bの主面53a上に成長され、c軸に直交する基準面R22に沿って延在する。第1の部分69aは、基準面R22に対して傾斜する。第3の部分69cは、開口65の底面65e上に成長され、基準面R23に沿って延在する。第1の部分69aは、基準面R23に対して傾斜する。好適な実施例では、基準面R23は基準面R22と実質的に平行であり、また基準面R23及び基準面R22は基板51の主面51aに平行である。

【0062】

第2再成長工程では、アンモニア及びIII族元素原料を含む原料ガスG2を成長炉10aに供給して、図6の(b)部に示されるように、チャネル層69の成長の後に、半導体積層53bの主面53a、開口65の側面65d及び底面65e上に、キャリア供給層71を成長温度TG2で成長する。キャリア供給層71はチャネル層69とヘテロ接合70を形成する。キャリア供給層71はIII族窒化物半導体からなる。キャリア供給層71は、第1の部分71a、第2の部分71b及び第3の部分71cを含む。第1の部分71aは、開口65の側面65d上に成長され、基準面R31に沿って延在する。基準面R31は、キャリア供給層71の窒化ガリウム系半導体のc軸(基板51のc軸と同じ方向を向く)に直交する面及び基板51の主面51aに対して傾斜する。第2の部分71bは、半導体積層53bの主面53a上に成長され、基準面R32に沿って延在する。第1の部分71aは、基準面R32に対して傾斜する。第3の部分71cは、開口65の底面65e上に成長され、基準面R33に沿って延在する。第1の部分71aは、基準面R33に対して傾斜する。本実施例では、基準面R33は基準面R32と実質的に平行であり、また基準面R33及び基準面R32は基板51の主面51aに平行である。キャリア供給層71のIII族窒化物半導体のバンドギャップは、チャネル層69の窒化ガリウム系半導体のバンドギャップより大きい。

【0063】

基準面R31に直交する第1の軸とキャリア供給層71の窒化ガリウム系半導体のc軸との成す第1の角度は、基準面R32に直交する第2の軸とキャリア供給層71の窒化ガリウム系半導体のc軸との成す第2の角度より大きい。基板51の主面51aがc面及びc面から僅かなオフ角を有するとき、第2の角度はゼロ及び微少な角度である。第1の角度は、開口65の側面65dの傾斜に対応しており、第2の角度より大きな角度であり、これ故に、第1の部分69a、71aの傾斜は大きい。

【0064】

上記の工程により基板生産物SP2が形成される。図7の(a)部に示されるように、基板生産物SP2を成長炉10aから取り出す。図7の(b)部に示されるように、電極形成工程では、キャリア供給層71上にゲート電極79を形成する。より具体的には、電極形成工程では、半導体積層53bの半導体層57、59に接触を成すソース電極73の形成、基板51の裏面51bに接触を成すドレイン電極75の形成、ゲート絶縁膜77の形成、及びゲート絶縁膜77に接触を成すゲート電極79の形成を行う。ゲート絶縁膜77は例えばAl2O3、SiN、SiO2、HfO2等からなることができる。

【0065】

例えば、ソース電極の形成に先だって、コンタクト工程では、コンタクト層59から電流ブロック層57に到達するコンタクトホールを半導体積層53bに形成する。コンタクトホールを形成した後に、ソース電極形成工程では、半導体積層53bのコンタクト層59の上にソース電極73を形成する。ソース電極73は、電流ブロック層57(第2の窒化ガリウム系半導体層)及びコンタクト層59(第3の窒化ガリウム系半導体層)に接触を成す。

【0066】

例えば、チャネル層69及びキャリア供給層71をエピタキシャル成長した後に、ゲート電極形成工程では、基板生産物SP2の上に開口斜面にショットキ接触を成すようにゲート電極79を形成する。この実施の形態によれば、開口斜面にゲート電極が設けられる半導体積層開口斜面のドナー性不純物が低減されるので、チャネルリーク電流が低減される。

【0067】

或いは、例えば、絶縁膜形成工程では、チャネル層69及びキャリア供給層71をエピタキシャル成長した後に、基板生産物SP2上に絶縁膜77を形成する。絶縁膜形成工程後のゲート電極形成工程では、基板生産物SP2上に開口斜面にゲート電極79を形成する。この作製方法によれば、絶縁膜77の形成の後に、開口斜面上にゲート電極79が設けられる。半導体積層53bの開口斜面のドナー性不純物が低減されるので、チャネルリーク電流が低減される。また絶縁膜77によりゲートリーク電流も低減される。

【0068】

例えば、ドレイン電極形成工程では、基板51上にドレイン電極75を形成する。基板51の主面51aは実質的にc面であるとき、開口の底部の面方位は実質的にc面である。第1溶液の処理は、c面に対するドナー性欠陥の除去能力に比べて、電流ブロック層57上の傾斜面上のドナー性欠陥の除去能力に優れる。開口の底部のドナー性欠陥は、n型層とn型層との界面にも残留する。

【0069】

図7の(b)部に示されるように、半導体積層53bの主面53a上にソース電極73を形成でき、このソース電極73は、電流ブロック層57及びコンタクト層59に電位を供給する。チャネル層69とキャリア供給層71とは接合70を成し、接合70には二次元キャリアガス層が形成される。ソース電極73は、チャネル層69を流れるキャリアを供給し、キャリアは二次元キャリアガス層を介してドリフト層55に流れる。この作製方法によれば、ソース電極73が電流ブロック層57及びコンタクト層59に電位を供給するので、電流ブロック層57がチャネル層69に対してバックゲートとして働く。

【0070】

この方法によれば、図6に示されるように、チャネル層69の第1の部分69aは、その窒化ガリウム系半導体のc軸に直交する面及び基板51の主面51aに対して傾斜した基準面R21に沿って延在する。これ故に、チャネル層69の第1及び第2の部分69a、69bは互いに異なる面方位を有する。キャリア供給層71の第1及び第2の部分71a、71bは、それぞれ、チャネル層69の第1及び第2の部分69a、69b上に成長される。

【0071】

本実施の形態では、キャリア供給層71の第1の部分71a上にゲート絶縁膜77を形成した後に、このゲート絶縁膜77上にゲート電極79を形成することができる。ゲート電極79はゲート絶縁膜77に接合を成す。この作製方法によれば、絶縁膜77を介してチャネルキャリアを制御するゲート電極79を有するトランジスタを提供できる。また、ゲートリークが低減される。

【0072】

或いは、ゲート絶縁膜77を形成することなく、キャリア供給層71の第1の部分71aに接合を成すゲート電極を形成することができる。この作製方法によれば、半導体にショットキ接合を成すゲート電極を用いてチャネルキャリアを制御するトランジスタを提供できる。

【0073】

チャネル層69及びキャリア供給層71の材料は、チャネル層/キャリア供給層として記載したとき、InGaN/AlGaN、GaN/AlGaN、及びAlGaN/AlNのいずれかであることができる。これらは、チャネル層69及びキャリア供給層71の好適な組み合わせを提供できる。

【0074】

コンタクト層(第3のIII族窒化物半導体層)59の窒化ガリウム系半導体、電流ブロック層(第2のIII族窒化物半導体層)57の窒化ガリウム系半導体、及びドリフト層(第1のIII族窒化物半導体層)55の窒化ガリウム系半導体は、第3のIII族窒化物半導体層/第2のIII族窒化物半導体層/第1のIII族窒化物半導体層として記載したとき、n+型GaN/p型GaN/n型GaN、及びn+型GaN/p型AlGaN/n型GaNのいずれかであることができる。これらは、ドリフト層55、電流ブロック層57及びコンタクト層59の好適な組み合わせを提供できる。

【0075】

(実験例1)

発明者らの実験において、導電性の基板を用いた縦型トランジスタ構造を形成している。この導電性基板上に、n−型GaNドリフト層、p型GaN電流ブロック層、n+型GaNコンタクト層のための3つのGaN膜を順に成長する。この後に、n+型GaN膜からn−型GaN膜に至る斜面を反応性イオンエッチング(RIE)により形成する。エッチングにより形成されたGaN傾斜面上に、成長炉でチャネル層及びバリア層を再成長する。チャネル層は、GaN傾斜面と再成長エピ界面を形成する。

【0076】

発明者らの観察及び検討によれば、上記のドライエッチングにおいては、エッチングにより形成された斜面に、ドナー性欠陥が導入されている。これ故に、再成長エピ界面はn型導電性を示す。このため、チャネル層には二次元電子ガスチャネルが形成される。しかしながら、再成長エピ界面のn型導電性のために、p型GaN電流ブロック層が有効に働かずに、二次元電子ガスチャネルが狭窄されない。したがって、Id−Vd特性においてドレインリーク不良が発生する。

【0077】

引き続き説明される実験例では、上記の斜面への再成長により形成される界面にドナー性欠陥が残留することに鑑み、その濃度を低減することによって、Id−Vd特性のばらつきによるドレインリーク不良の発生を抑制することを試みる。

【0078】

トランジスタの作製。

窒化ガリウム膜を有機金属気相成長(MOCVD)法により成膜する。ガリウム原料としてトリメチルガリウム(TMG)、アルミニウム原料としてトリメチルアルミニウム(TMA)を用いる。窒素原料としては、高純度アンモニアを用いる。キャリアガスとしては、純化した水素を用いる。高純度アンモニアの純度は、99.999%以上、純化水素の純度は99.999995%以上である。n型ドーパントとして水素ベースのシランを用い、p型ドーパントとしてビスシクロペンタジエニルマグネシウムを用いる。

【0079】

基板として、2インチサイズのn型c面窒化ガリウム基板を準備する。アンモニアと水素雰囲気中で、窒化ガリウム基板の主面にサーマルクリーニングを行う。この熱処理条件としては、例えば摂氏1030度の熱処理温度及び100Torrの成長炉内圧力を用いられる。この基板クリーニングの後に、摂氏1050度への昇温後に、複数の窒化ガリウム層を成膜する。この成膜において、炉内圧力は200Torrであり、原料ガスにおけるV/III比は1500である。

エピタキシャル基板の構造。

n型ドリフト層:厚さ5μm、キャリア濃度1×1016cm−3。

p型電流ブロック層:厚さ0.5μm、Mgドープ、Mg濃度1×1018cm−3。

n型キャップ層:厚さ0.2μm、Siドープ、キャリア濃度1×1018cm−3。

上記の成長により、エピタキシャル基板が作製され、このエピタキシャル基板は、上記のようなnpn構造を有する。npn構造には、開口のためのパターンを有するレジストマスクをフォトリソグラフィを用いてエピ表面に形成した後に、インダクティブ・カップリング・プラズマ−反応性イオンエッチング(ICP−RIE)によりnpn構造を加工して、斜面を有する基板生産物を形成する。レジストマスクを除去した後に基板洗浄を実施する。この後に、基板生産物を成長炉に配置して、チャネル層及びバリア層の再成長を行う。

【0080】

レジストマスクの除去と基板洗浄の後に、図8に示される再成長温度シーケンスに従ってチャネル層及びキャリア供給層を成長する。まず、時刻t0でMOCVD装置に基板生産物を導入して、時刻t1で摂氏400度に基板温度を上昇させる。さらに、アンモニア及び水素を含む雰囲気で摂氏950度まで温度を時刻t2で上昇しながら熱クリーニングを行う。次いで、引き続きアンモニア及び水素を成長炉に供給しながらIII族有機金属原料(TMG)を成長炉に供給して時刻t3に成長を開始し、厚さ150nmのi−GaNチャネル層を成長する。時刻t4でIII族有機金属原料の供給を停止してチャネル層の成長を終了する。この後に、アンモニア及び水素を含む雰囲気で基板温度を摂氏1080度まで時刻t4〜t5の期間で上昇しながら、時刻t6でIII族有機金属原料(TMG、TMA)を成長炉に供給して、Al組成0,25及び厚さ20nmのi−AlGaNキャリア供給層を成長する。時刻t7でIII族有機金属原料の供給を停止してキャリア供給層の成長を終了する。この後に、時刻t8から基板温度を降下する。時刻t9で、室温において基板生産物を成長炉から取り出す。

【0081】

その後に、基板生産物の全面に絶縁膜を成膜した後に、フォトリソグラフィとイオンビーム蒸着法を用いて、ソース、ドレイン電極をそれぞれエピタキシャル基板の表面と裏面に形成すると共に、ゲート電極を開口部側面に形成する。

【0082】

このように作製された多数のトランジスタのId−Vd特性を測定する。図9は、測定結果のうちの性能の一例を示すトランジスタのId−Vd特性を表す。この例のようなId−Vd特性では、ドレインリーク過多で電流ピンチオフが生じておらず、ゲートバイアス(Vg)によるドレイン電流(Id)の変調も観察されない。

【0083】

エッチングにより形成されるGaN面の品質を特定する。c面GaN基板上に、厚さ3μmのアンドープGaNバッファ層を成長して、エピタキシャル基板を作製する。ICP−RIE装置において、Ar/Cl2エッチャントを用いて、このエピタキシャル基板の全面をエッチングして、厚さ2μmのアンドープGaNバッファ層を形成する(つまり、1μm厚のエッチング)。次に、薬液処理(例えばSPM処置)をエッチング面に施した後に、再びMOCVD炉において、厚さ0.5μmのアンドープGaN層の成長を行う。この成長の後に、再成長のアンドープGaN層のエピ表面にショットキ電極を形成する。

【0084】

このショットキ電極を用いて、C−V測定により界面のキャリア濃度を測定する。図10は、再成長界面にドナー性欠陥の濃度分布を示す図面である。C−V測定で調べたエピ再成長界面のドナープロファイルによれば、1×1018cm−3程度の平均濃度、及び1×1018cm−3を越えるピーク濃度のドナー性欠陥が形成されている。ICP−RIE装置及びエッチング条件は実験例1と同様であり、この実験例によれば、エッチングにより形成されたGaN斜面上へのHEMT構造のエピタキシャル積層の再成長界面にも同程度のドナー性欠陥が観察されると考えられる。再成長界面に大きな濃度のドナー性欠陥が残留するとき、GaN斜面におけるバンド構造は予想と異なる形状を示すと考えられる。図11は、再成長界面におけるバンド構造を示す。図11の(a)部を参照すると、高い濃度のドナー性欠陥を含む再成長界面におけるバンド構造が示される。二次元電子ガスが、p型電流ブロック層界面のポテンシャルにより狭窄されず、この結果、ドレインリーク不良に至ると考えられる。

【0085】

(実験例2)

・トランジスタの作製。

実験例1と同様にエピタキシャル成長によりnpn構造を成長する。この後に、反応性イオンエッチング(RIE)により、斜面を有する開口を上記のnpn構造に形成する。エッチングにより形成された斜面におけるドナー性欠陥の濃度を低減するために、発明者らは検討を行っている。

【0086】

上記実験例と同様にエッチングした2枚のnpn構造基板に、上記のSPM洗浄に加えて以下の処理を行う。テトラメチルアンモニウムヒドロキシド水溶液(濃度24パーセント、質量比)による前処理を行うこと;テトラメチルアンモニウムヒドロキシド液(濃度24パーセント、質量比)による第1処理及びフッ化水素及び過酸化水素(HF(50%):H2O2=5:1)の混合液による第2処理を行うこと。これらの処理を施したnpn構造基板を再びMOCVD炉において、厚さ0.5μmのアンドープGaN層の成長を個々のnpn構造基板に行う。この成長の後に、再成長のアンドープGaN層のエピ表面にショットキ電極を形成する。このショットキ電極を用いて、C−V測定により界面のキャリア濃度を測定する。

【0087】

テトラメチルアンモニウムヒドロキシド液は、シリコン酸化物(例えばSiO2)に対して高い選択性を示し、テトラメチルアンモニウムヒドロキシドは金属元素を含まないので、プロセスの清浄性に優れている。また、GaNの異方性エッチングにも有効であるので、RIEより形成される斜面のダメージ層を除去するために有効であると考えられる。実際にアンドープGaN表面にテトラメチルアンモニウムヒドロキシド処理を施した表面にアンドープGaN層を再成長し更にショットキゲートを形成したnpn構造基板では、ショットキリークが多く、再成長界面のドナー濃度を測定できない。発明者らの実験によれば、再成長界面は、メタルコンタクトの形成に比べてウェットエッチングの残留物に敏感である。

【0088】

発明者らの検討によれば、テトラメチルアンモニウムヒドロキシドのエッチング機構では、GaN系半導体中のIII族元素が水酸化物を形成しつつエッチングが進行することので、エッチング固液界面付近には、テトラメチルアンモニウムヒドロキシド液中に溶け出した水酸化物が過飽和状態であり、GaN系半導体表面に水酸化物が沈殿している状況が考えられる。したがって、テトラメチルアンモニウムヒドロキシド処理したGaN系半導体表面にGaN系半導体を再成長するとき、再成長界面にIII族元素の水酸化物が残留することになる。これ故に、再成長エピ成長の半導体の品質が劣化している可能性がある。

【0089】

アンドープGaN表面にテトラメチルアンモニウムヒドロキシド処理を施した後に、npn構造基板にさらにフッ化水素及び過酸化水素(HF(50%):H2O2=5:1)の混合液による追加の処理を行う。追加処理のGaN系半導体表面上にアンドープGaN層を再成長し更にショットキゲートを形成する。このショットキ電極を用いたC−V測定により界面のキャリア濃度を測定する。図12は、再成長界面にドナー性欠陥の濃度分布を示す図面である。このとき、ドナー性欠陥の濃度が、従来に比べて小さく、5×1017cm−3程度まで低減され、好ましくは例えば4×1017cm−3以下低減され、更に好ましくは3×1017cm−3以下まで低減されている。この濃度は、テトラメチルアンモニウムヒドロキシド処理しないいくつかのGaN系半導体表面において測定された濃度の最小値に比べて小さい。

【0090】

(実験例3)

・トランジスタの作製。

実験例1と同様にnpn構造を成長した後に、RIEでnpn構造をエッチングして、npn構造に斜面を形成する。その後に、テトラメチルアンモニウムヒドロキシド水溶液(濃度24パーセント)による第1処理及びフッ化水素及び過酸化水素(HF(50%):H2O2=5:1)の混合液による第2処理を行う。これらの処理を施した後に、実験例1と同様にアンドープGaN層及びアンドープAlGaN層の再成長を行ってHEMTエピ構造を形成する。このHEMTエピ構造に、実験例1と同様に電極を形成して、トランジスタを形成する。図13は、このトランジスタのId−Vd特性を示す。図13を参照すると、ドレインリークが改善されており、ゲートバイアス(Vg)に対してドレイン電流(Id)が変調される。優れた特性でトランジスタが動作している。再成長界面におけるドナー性欠陥の濃度を低減することにより、ドレイン耐圧が改善される。図11の(b)部に示されるように、低い濃度のドナー性欠陥を含む再成長界面におけるバンド構造では、ゲート電極からの電界が、チャネル層とキャリア供給層とのヘテロ界面において二次元電子ガスの生成を制御できる。また、このトランジスタは、第1及び第2処理を適用せずに作成されたトランジスタに比べて優れたサブスレシュホルド特性を示す。さらに、上記の実験例ではGaN基板上に多数のトランジスタが作成され、これらのトランジスタのId−Vd特性のばらつきが縮小される。

【0091】

テトラメチルアンモニウムヒドロキシド水溶液(濃度24パーセント)による第1処理並びにフッ化水素及び過酸化水素(HF(50%):H2O2=5:2)の混合液による第3処理を行って、同様にトランジスタを作製する。このトランジスタでは、ショットキリークが増加し、逆にドレイン耐圧が劣化する結果が得られる。過酸化水素(H2O2)でフッ化水素酸(HF)が希釈されたことによって、逆に水酸化物の除去効率が低下している可能性がある。

【0092】

第2溶液では、フッ化水素酸及び過酸化水素の容量比に関して、(フッ化水素酸)/(過酸化水素)>5/2であることができ、さらに(フッ化水素酸)/(過酸化水素)≧5であることが好ましい。テトラメチルアンモニウムヒドロキシドによる処理により半導体積層の第1処理面近傍には水酸化物が形成される。第2溶液が上記の比率であるとき、水酸化物の除去に加えてドナー性欠陥の低減に有効である。また、(フッ化水素酸)/(過酸化水素)の比率の上限は20であることができ、過酸化水素の濃度が不十分でドナー性欠陥の除去効率が低下するためである。

【0093】

電子ブロック層(p型GaN層)のMg濃度は1×1017cm−3以下では残留ドナー性界面欠陥を補償しきれずに電流ピンチオフが実現されず、Mg濃度は1×1019cm−3以上ではHEMT構造エピ再成長時に2次元電子ガス界面にまでMgが拡散して、ドレイン電流に影響する。

【0094】

図14は、本実施の形態に係る窒化物電子デバイスの構造を示す図面である。窒化物電子デバイスの一例として、ヘテロ接合トランジスタ11を説明する。ヘテロ接合トランジスタ11は、導電性の支持基体13と、半導体積層15と、チャネル層19と、キャリア供給層21と、ゲート電極23とを備える。支持基体13は、III族窒化物の主面13aを有すると共に、III族窒化物の裏面13bを有する。III族窒化物主面13aは好ましくはc面であり、良好な結晶成長のために僅かなオフ角を有することができる。このオフ角の範囲は例えば−0.7度以上−0.1度以下又は+0.1度以上+0.7度以下であることができる。支持基体13は導電性の自立III族窒化物支持体であることができる。半導体積層15は支持基体13の主面13a上に搭載される。半導体積層15は、支持基体13の主面13aの方向に向けて窪む開口部16を有する。開口部16は、例えば半導体積層15に形成されたメサ、凹部又は溝により規定されることができる。チャネル層19は、窒化ガリウム系半導体からなり、また半導体積層15の開口部16内に設けられる。キャリア供給層21は、III族窒化物半導体からなり、また半導体積層15の開口部16内に設けられると共に開口部16内のチャネル層19上に延在する。ゲート電極23はキャリア供給層21上に設けられ、開口部16内においてキャリア供給層21はチャネル層19とゲート電極23との間に位置する。キャリア供給層21のIII族窒化物のバンドギャップは、チャネル層19の窒化ガリウム系半導体のバンドギャップより大きく、チャネル層19とキャリア供給層21とはヘテロ接合20を成す。ゲート電極23はヘテロ接合20に沿った二次元電子ガスの生成を制御する。

【0095】

半導体積層15は、ドリフト層25、電流ブロックト層27及びn型半導体層29を含む。ドリフト層25、電流ブロックト層27及びn型半導体層29は、支持基体13の主面13aの上に順に設けられる。ドリフト層25は、n導電性を示し、例えば第1窒化ガリウム系半導体からなる。電流ブロックト層27は、p導電性を示し、例えば第2窒化ガリウム系半導体からなる。また、ドリフト層25は、支持基体13の主面13aと電流ブロックト層27との間に設けられる。電流ブロックト層27の側面27aとゲート電極23との間には、キャリア供給層21及びチャネル層19が延在する。

【0096】

n型半導体層29は例えばn導電性を有し、また電流ブロック層27上に設けられる。n型半導体層29は第3窒化ガリウム系半導体からなり、例えばn+型GaNからなり、n型半導体層29の第3窒化ガリウム系半導体のn型ドーパント濃度は例えば1×1016cm−3以上であることができる。n型半導体層29の厚さは0.1μm以上であり、1μm以下である。n型半導体層29は、半導体積層15の開口部16の側面16aに位置する側面29aを更に含む。電流ブロックト層27がn型半導体層29と支持基体13の主面13aとの間に設けられ、n型半導体層29の導電型と異なるp導電性を有する。

【0097】

既に説明したように、開口部16はエッチングにより形成される。エッチングの後においては、開口斜面にドナー性欠陥が残留している。本実施形態で説明された処理の後において、半導体積層15の開口部16の斜面とチャネル層19との界面におけるドナー性欠陥の濃度は5×1017cm−3以下である。半導体積層15の側面16aからチャネル層19に至る半導体領域内には、図14に示されるように、濃度5×1017cm−3以下のドナー性欠陥を含む薄い半導体層17が設けられる。この半導体層17は電流ブロック層27とチャネル層19との間に設けられ、またドナー性欠陥や電流ブロック層27からのp型ドーパントを含む窒化ガリウム系半導体からなる。半導体層17は、主にエッチングに起因するドナー性欠陥を含み、その厚さは50nm〜200nmと見積もられる。

【0098】

このヘテロ接合トランジスタ11によれば、半導体積層斜面とチャネル層との界面におけるドナー性欠陥の濃度が5×1017cm−3以下であるので、ドナー性欠陥に起因するチャネルリークを低減できる。これ故に、これまでに比べても良好なサブスレッショルド特性を窒化物電子デバイスに提供できる。

【0099】

チャネル層19の厚さは5nm以上であることができ、またチャネル層19の厚さは40nm以下であることができる。キャリア供給層21の厚さは20nm以上であることができ、キャリア供給層21の厚さは400nm以下であることができる。半導体層17が5×1017cm−3以下のドナー性欠陥濃度を示すとき、p型半導体層27は良好なバックゲート層として働くと共に、キャリア供給層21とチャネル層19との界面には、ゲート電極23の電位により制御可能な二次元電子ガスが生成される。

【0100】

図14に示されるように、本実験例では開口部16の底面16b(底面25d)はほぼc面(c軸に直交する面)に沿って延在している。図14においては、結晶座標系CRが示され、基準軸Cxはc軸の方向を示している。m面は結晶座標系CRのm軸に直交する面であり、a面は結晶座標系CRのa軸に直交する面である。開口部16の側面16aは、III族窒化物半導体のa面に対して傾斜し、II族窒化物半導体のm面に対して傾斜すると共に前記III族窒化物半導体のc面に対して傾斜している。本実験例では、開口部16の側面16aは、m軸又はa軸の方向に延在する。

【0101】

ヘテロ接合トランジスタ11は、ソース電極31を更に備えることができる。ソース電極31がn型半導体層29に電位を供給する。また、ソース電極31はチャネル層19に接触を成して、チャネル層19にキャリアを供給できる。ソース電極31は電流ブロックト層27に接続されている。電流ブロックト層27が、ドナー性欠陥を含む半導体における補償に打ち勝ってチャネル層に接合を成すとき、電流ブロックト層27からのバイアスがチャネル層に作用する。電流ブロックト層27の電位はソース電極31から供給されて、これがバックバイアスとなる。このバックバイアスは、ヘテロ接合トランジスタ11のノーマリオフ動作に好適である。

【0102】

ヘテロ接合トランジスタ11では、支持基体13の裏面13bに設けられたドレイン電極33を更に備えることができる。ドレイン電極33が支持基体13の裏面13bに設けられるので、ドレイン電極33をゲート電極23及びソース電極31から隔てることができる。これ故に、高耐圧の実現に有効である。ドレイン電極33は例えばNi/Alからなることができ、ソース電極31は例えばTi/Alからなることができる。ゲート電極23は、例えばNi/Au、Pt/Au、Pd/Au、Mo/Au等からなることができる。

【0103】

ドリフト層25は、半導体積層15の開口部16の側面16aに位置する端面25aを有する。電流ブロックト層27は、半導体積層15の開口部16の側面16aに位置する側面27aを有する。チャネル層19は、n型半導体層29の側面29a、電流ブロックト層27の側面27a及びドリフト層25の側面25a及び上面25b上に設けられる。

【0104】

ドリフト層25の第1の面25bは、電流ブロックト層27の第2の面27cと接合を成す。ドリフト層25の第2の面25cは、支持基体13の主面13aと接合を成す。n型半導体層29の第1の面29bはチャネル層19と接合を成す。n型半導体層29の第2の面29cは、電流ブロックト層27の第1の面27bと接合を成す。

【0105】

開口部16の側面16aは、チャネル層19の裏面に接合を成し、チャネル層19の裏面は電流ブロックト層27の側面27aと接合を成すことができる。チャネル層19の裏面はn型半導体層29の側面29aと接合を成す。チャネル層19の裏面はドリフト層25の側面25aと接合を成す。キャリア供給層21の裏面は、チャネル層19の表面に接合を成す。ゲート電極18は、キャリア供給層21にショットキ接合を成すことができる。

【0106】

ドリフト層25の厚さは1μm以上であることができ、ドリフト層25の厚さは10μm以下であることができる。ドリフト層25の第1窒化ガリウム系半導体のn型ドーパント濃度は1×1015cm−3以上であることができ、第1窒化ガリウム系半導体のn型ドーパント濃度は3×1016cm−3以上であることができる。ドリフト層25は、オフ動作時のソース−ドレイン間における耐圧の向上と導通時のオン抵抗の低減とを両立を可能にする。高すぎるドナー濃度は、ソース−ドレイン間における耐圧を低下させる。低すぎるドナー濃度は、オン抵抗を増加させる。

【0107】

電流ブロック層27の厚さは0.1μm以上であることができ、ドレイン耐圧維持に有効だからである。電流ブロック層27の厚さは2μm以下であることができ、実効チャネル長を短くして低オン抵抗を実現できるからである。電流ブロック層27の第2窒化ガリウム系半導体のp型ドーパント濃度は5×1016cm−3以上であり、第2窒化ガリウム系半導体のp型ドーパント濃度は5×1018cm−3以下であることができる。ドリフト層17直上に設けられた電流ブロック層27において、上記の範囲におけるアクセプタ濃度は、窒化物電子デバイスにおける非導通の際のソース−ドレイン間の耐圧として所望の値を提供できる。

【0108】

ヘテロ接合トランジスタ11の一実施例を以下に示す。

支持基体13:n型GaN(キャリア濃度:1×1019cm−3)。

薄い半導体層17:ドナー性欠陥を含むGaN(ドナー性欠陥濃度:5×1017cm−3以下)。

チャネル層19:アンドープGaN(キャリア濃度:1×1015m−3、厚さ:30nm)。

キャリア供給層21:アンドープAlGaN(厚さ:30nm、Al組成比0.25)。

n型半導体層29:n型GaN(キャリア濃度:1×1018m−3、厚さ:0.3μm)。

電流ブロックト層27:p+型GaN(キャリア濃度:1×1018m−3、厚さ:0.5μm)。

ドリフト層25:アンドープGaN(キャリア濃度:1×1015m−3、厚さ:5μm)。

このヘテロ接合トランジスタによれば、実用的な構造の一例が提供される。この窒化物半導体電子デバイスによれば、ソース電極31からドリフト層25までの電流経路における抵抗増加を避けることができる。なお、ヘテロ接合トランジスタ11は、キャリア供給層21とゲート電極23との間に設けられた絶縁膜を更に備えてもよい。この絶縁膜を介してキャリア供給層21及びチャネル層19に電界が及ぶ。

【0109】

ヘテロ接合トランジスタ11の一実施例では、ドリフト層29の第1の窒化ガリウム系半導体はn型GaNであることができる。ドリフト層29の膜厚は1μm以上であり、10μm以下であることができる。ドリフト層のキャリア濃度は1×1015cm−3以上であり、3×1016cm−3以下であることができる。このヘテロ接合トランジスタ11では、上記のドリフト層29を用いて、高耐圧に良い窒化物電子デバイスを提供できる。ドリフト層29のn型GaNにはシリコン(Si)が添加されていてもよい。

【0110】

また、ヘテロ接合トランジスタ11の一実施例では、電流ブロック層27の第2の窒化ガリウム系半導体はp型GaNであることができる。電流ブロック層27の膜厚は0.1μm以上であり、2.0μm以下であることができる。電流ブロック層27のp型GaNにはマグネシウム(Mg)が添加されており、電流ブロック層27のMg濃度は5×1016cm−3以上であり、5×1018cm−3以上であることができる。このヘテロ接合トランジスタ11では、電流ブロック層27はチャネル層29に対してバックゲートを提供すると共に、電流ブロック層27の膜厚はチャネル長を規定する。ドナー性不純物の濃度は、電流ブロック層27のp型ドーパント濃度に比べて十分に小さく低減される。

【0111】

また、ヘテロ接合トランジスタ11の一実施例では、コンタクト25層の第3の窒化ガリウム系半導体はn型GaNであることができる。コンタクト層25の膜厚は0.1μm以上であり、1.0μm以下であることができる。コンタクト層25のn型GaNにはシリコン(Si)が添加されており、コンタクト層25のSi濃度は1×1016cm−3以上であることができる。ヘテロ接合トランジスタ11によれば、ソース抵抗を低くできる。

【0112】

また、ヘテロ接合トランジスタ11の一実施例では、キャリア供給層21はAlXGa1−XN(0<X<1)層を含むことができる。キャリア供給層21の厚さは5nm以上であり、40nm以下であることができる。チャネル層19はアンドープGaN層を含み、チャネル層19の厚さは20nm以上であり、400nm以下であることができる。キャリア供給層21はチャネル層19にヘテロ接合を成す。このヘテロ接合トランジスタ11では、高い移動度で低いチャネルリークのヘテロ接合トランジスタを提供できる。

【0113】

本発明は、本実施の形態に開示された特定の構成に限定されるものではない。

【産業上の利用可能性】

【0114】

本実施の形態によれば、リーク特性のばらつき幅を低減可能な、窒化物電子デバイスを作製する方法を提供でき、また、より優れたリーク特性を示す窒化物電子デバイスを提供できる。

【符号の説明】

【0115】

10a…成長炉、11…ヘテロ接合トランジスタ、13…導電性基板、15…半導体積層、16…開口、17…低ドナー性欠陥層、19…チャネル層、20…ヘテロ接合、21…バリア層、23…ゲート電極、25…ドリフト層、27…電流ブロック層、29…コンタクト層、31…ソース電極、33…ドレイン電極、CR…結晶座標系、51…基板、53、53b…半導体積層、55…第1のIII族窒化物半導体層、57…第2のIII族窒化物半導体層、59…第3のIII族窒化物半導体層、E…エピタキシャル基板、63…マスク、65…開口、65d…側面、65e…底面、R11、R12、R13、R31、R32、R33…基準面、69…チャネル層、71…キャリア供給層、73…ソース電極、77…ゲート絶縁膜、79…ゲート電極。

【特許請求の範囲】

【請求項1】

窒化物電子デバイスを作製する方法であって、

n型III族窒化物半導体からなる自立基板の主面の上に、ドリフト層、電流ブロック層及びコンタクト層のための第1、第2及び第3のIII族窒化物半導体層を順に設けたエピタキシャル基板を準備する工程と、

前記第3のIII族窒化物半導体層から前記第2のIII族窒化物半導体層を介して前記第1のIII族窒化物半導体層に至る斜面を有する開口をエッチングにより前記エピタキシャル基板に形成して、前記ドリフト層、前記電流ブロック層及び前記コンタクト層並びに前記開口の斜面を含む半導体積層を形成する工程と、

前記半導体積層を形成した後に、テトラメチルアンモニウムヒドロキシドを含む第1溶液を用いた第1処理を前記半導体積層に行うと共に、該第1処理の後に、フッ化水素酸及び過酸化水素を含む第2溶液を用いた第2処理を前記半導体積層に行って、前記第1処理及び前記第2処理による処理面を前記半導体積層に形成する工程と、

前記半導体積層の前記処理面の上に、窒化ガリウム系半導体からなるチャネル層及びIII族窒化物からなるキャリア供給層をエピタキシャル成長して、基板生産物を形成する工程と、

を備え、

前記キャリア供給層の前記III族窒化物のバンドギャップは、前記チャネル層の前記窒化ガリウム系半導体のバンドギャップより大きく、

前記第1及び第3のIII族窒化物半導体層はn導電性を有し、

前記第2のIII族窒化物半導体層はp導電性を有する、窒化物電子デバイスを作製する方法。

【請求項2】

前記電流ブロック層に到達するコンタクトホールを前記半導体積層に形成する工程と、

前記コンタクトホールを形成した後に、前記半導体積層の前記コンタクト層の上に電極を形成する工程と、

を備える、請求項1に記載された窒化物電子デバイスを作製する方法。

【請求項3】

前記第2溶液では、フッ化水素酸及び過酸化水素の容量比に関して、(フッ化水素酸)/(過酸化水素)≧5である、請求項1又は請求項2に記載された窒化物電子デバイスを作製する方法。

【請求項4】

前記自立基板の前記主面は、前記n型III族窒化物半導体のc面に対して−0.7度以上−0.1度以下又は+0.1度以上+0.7度以下の角度である、請求項1〜請求項3のいずれか一項に記載された窒化物電子デバイスを作製する方法。

【請求項5】

前記自立基板の前記主面は実質的にc面である、請求項1〜請求項4のいずれか一項に記載された窒化物電子デバイスを作製する方法。

【請求項6】

前記第1処理において、前記第1溶液の温度は、摂氏50度以上であり、摂氏100度未満である、請求項1〜請求項5のいずれか一項に記載された窒化物電子デバイスを作製する方法。

【請求項7】

前記第1処理において、前記第1溶液の濃度は、5パーセント以上であり、50パーセント以下である、請求項1〜請求項6のいずれか一項に記載された窒化物電子デバイスを作製する方法。

【請求項8】

前記チャネル層及び前記キャリア供給層の材料の組み合わせは、チャネル層/キャリア供給層として記載したとき、InGaN/AlGaN、GaN/AlGaN及びAlGaN/AlNのいずれかである、請求項1〜請求項7のいずれか一項に記載された窒化物電子デバイスを作製する方法。

【請求項9】

前記第1〜第3のIII族窒化物半導体層の材料の組み合わせは、第3のIII族窒化物半導体層/第2のIII族窒化物半導体層/第1のIII族窒化物半導体層として記載したとき、n+型GaN/p型GaN/n型GaNまたはn+型GaN/p型AlGaN/n型GaNである、請求項1〜請求項8のいずれか一項に記載された窒化物電子デバイスを作製する方法。

【請求項10】

前記チャネル層及び前記キャリア供給層をエピタキシャル成長した後に、前記基板生産物の上に前記開口の前記斜面にゲート電極を形成する工程を備える、請求項1〜請求項9のいずれか一項に記載された窒化物電子デバイスを作製する方法。

【請求項11】

前記チャネル層及び前記キャリア供給層をエピタキシャル成長した後に、前記基板生産物の上に絶縁膜を形成する工程と、

前記絶縁膜を形成した後に、前記開口の前記斜面にゲート電極を形成する工程と、

を備える、請求項1〜請求項10のいずれか一項に記載された窒化物電子デバイスを作製する方法。

【請求項12】

前記半導体積層の前記処理面のドナー性不純物の濃度は5×1017cm−3以下である、請求項1〜請求項11のいずれか一項に記載された窒化物電子デバイスを作製する方法。

【請求項13】

前記チャネル層はアンドープ窒化ガリウム系半導体層を含み、

前記チャネル層の厚さは20nm以上であり、400nm以下である、請求項1〜請求項12のいずれか一項に記載された窒化物電子デバイスを作製する方法。

【請求項14】

前記電流ブロック層の第2のIII族窒化物半導体はp型GaNであり、

前記電流ブロック層の膜厚は0.1μm以上であり、2.0μm以下であり、

前記電流ブロック層のp型GaNにはマグネシウム(Mg)が添加されており、

前記電流ブロック層のMg濃度は、5×1016cm−3以上であり、5×1018cm−3以上である、請求項1〜請求項13のいずれか一項に記載された窒化物電子デバイスを作製する方法。

【請求項15】

前記自立基板の上にドレイン電極を形成する工程を備える請求項1〜請求項14のいずれか一項に記載された窒化物電子デバイスを作製する方法。

【請求項16】

窒化物電子デバイスであって、

支持基体の主面上に順に設けられたドリフト層、電流ブロック層及びコンタクト層を含むと共に、前記コンタクト層から前記電流ブロック層を介して前記ドリフト層に至る側面を有する半導体積層と、

前記側面の上に設けられ、窒化ガリウム系半導体からなるチャネル層と、

前記側面の上に設けられ、III族窒化物からなるキャリア供給層と、

前記側面の上に設けられたゲート電極と、

前記半導体積層の上に設けられたソース電極と、

前記半導体積層及び前記支持基体のいずれかに設けられドレイン電極と、

を備え、

前記チャネル層は前記キャリア供給層との前記側面との間に設けられ、

前記半導体積層の前記側面と前記チャネル層との界面におけるドナー性欠陥の濃度は5×1017cm−3以下であり、

前記ドリフト層は、第1の窒化ガリウム系半導体からなり、

前記電流ブロック層は、第2の窒化ガリウム系半導体からなり、

前記コンタクト層は、第3の窒化ガリウム系半導体からなり、

前記キャリア供給層の前記III族窒化物のバンドギャップは、前記チャネル層の前記窒化ガリウム系半導体のバンドギャップより大きく、

前記ドリフト層及び前記コンタクト層はn型を有し、

前記電流ブロック層はp型を有する、窒化物電子デバイス。

【請求項17】

前記ドリフト層の前記第1の窒化ガリウム系半導体はn型GaNであり、

前記ドリフト層の膜厚は1μm以上であり、10μm以下であり、

前記ドリフト層のキャリア濃度は、1×1015cm−3以上であり、3×1016cm−3以上である、請求項16に記載された窒化物電子デバイス。

【請求項18】

前記電流ブロック層の前記第2の窒化ガリウム系半導体はp型GaNであり、

前記電流ブロック層の膜厚は0.1μm以上であり、2.0μm以下であり、

前記電流ブロック層のp型GaNにはマグネシウム(Mg)が添加されており、

前記電流ブロック層のMg濃度は、5×1016cm−3以上であり、5×1018cm−3以上である、請求項16又は請求項17に記載された窒化物電子デバイス。

【請求項19】

前記コンタクト層の前記第3の窒化ガリウム系半導体はn型GaNであり、

前記コンタクト層の膜厚は0.1μm以上であり、1.0μm以下であり、

前記コンタクト層のn型GaNにはシリコン(Si)が添加されており、

前記コンタクト層のキャリア濃度は、1×1016cm−3以上である、請求項16〜請求項18のいずれか一項に記載された窒化物電子デバイス。

【請求項20】

前記キャリア供給層はAlXGa1−XN(0<X<1)層を含み、

前記キャリア供給層の厚さは5nm以上であり、40nm以下であり、

前記チャネル層はアンドープGaN層を含み、

前記チャネル層の厚さは20nm以上であり、400nm以下であり、

前記キャリア供給層は前記チャネル層にヘテロ接合を成す、請求項16〜請求項19のいずれか一項に記載された窒化物電子デバイス。

【請求項1】

窒化物電子デバイスを作製する方法であって、

n型III族窒化物半導体からなる自立基板の主面の上に、ドリフト層、電流ブロック層及びコンタクト層のための第1、第2及び第3のIII族窒化物半導体層を順に設けたエピタキシャル基板を準備する工程と、

前記第3のIII族窒化物半導体層から前記第2のIII族窒化物半導体層を介して前記第1のIII族窒化物半導体層に至る斜面を有する開口をエッチングにより前記エピタキシャル基板に形成して、前記ドリフト層、前記電流ブロック層及び前記コンタクト層並びに前記開口の斜面を含む半導体積層を形成する工程と、

前記半導体積層を形成した後に、テトラメチルアンモニウムヒドロキシドを含む第1溶液を用いた第1処理を前記半導体積層に行うと共に、該第1処理の後に、フッ化水素酸及び過酸化水素を含む第2溶液を用いた第2処理を前記半導体積層に行って、前記第1処理及び前記第2処理による処理面を前記半導体積層に形成する工程と、

前記半導体積層の前記処理面の上に、窒化ガリウム系半導体からなるチャネル層及びIII族窒化物からなるキャリア供給層をエピタキシャル成長して、基板生産物を形成する工程と、

を備え、

前記キャリア供給層の前記III族窒化物のバンドギャップは、前記チャネル層の前記窒化ガリウム系半導体のバンドギャップより大きく、

前記第1及び第3のIII族窒化物半導体層はn導電性を有し、

前記第2のIII族窒化物半導体層はp導電性を有する、窒化物電子デバイスを作製する方法。

【請求項2】

前記電流ブロック層に到達するコンタクトホールを前記半導体積層に形成する工程と、

前記コンタクトホールを形成した後に、前記半導体積層の前記コンタクト層の上に電極を形成する工程と、

を備える、請求項1に記載された窒化物電子デバイスを作製する方法。

【請求項3】

前記第2溶液では、フッ化水素酸及び過酸化水素の容量比に関して、(フッ化水素酸)/(過酸化水素)≧5である、請求項1又は請求項2に記載された窒化物電子デバイスを作製する方法。

【請求項4】

前記自立基板の前記主面は、前記n型III族窒化物半導体のc面に対して−0.7度以上−0.1度以下又は+0.1度以上+0.7度以下の角度である、請求項1〜請求項3のいずれか一項に記載された窒化物電子デバイスを作製する方法。

【請求項5】

前記自立基板の前記主面は実質的にc面である、請求項1〜請求項4のいずれか一項に記載された窒化物電子デバイスを作製する方法。

【請求項6】

前記第1処理において、前記第1溶液の温度は、摂氏50度以上であり、摂氏100度未満である、請求項1〜請求項5のいずれか一項に記載された窒化物電子デバイスを作製する方法。

【請求項7】

前記第1処理において、前記第1溶液の濃度は、5パーセント以上であり、50パーセント以下である、請求項1〜請求項6のいずれか一項に記載された窒化物電子デバイスを作製する方法。

【請求項8】

前記チャネル層及び前記キャリア供給層の材料の組み合わせは、チャネル層/キャリア供給層として記載したとき、InGaN/AlGaN、GaN/AlGaN及びAlGaN/AlNのいずれかである、請求項1〜請求項7のいずれか一項に記載された窒化物電子デバイスを作製する方法。

【請求項9】

前記第1〜第3のIII族窒化物半導体層の材料の組み合わせは、第3のIII族窒化物半導体層/第2のIII族窒化物半導体層/第1のIII族窒化物半導体層として記載したとき、n+型GaN/p型GaN/n型GaNまたはn+型GaN/p型AlGaN/n型GaNである、請求項1〜請求項8のいずれか一項に記載された窒化物電子デバイスを作製する方法。

【請求項10】

前記チャネル層及び前記キャリア供給層をエピタキシャル成長した後に、前記基板生産物の上に前記開口の前記斜面にゲート電極を形成する工程を備える、請求項1〜請求項9のいずれか一項に記載された窒化物電子デバイスを作製する方法。

【請求項11】

前記チャネル層及び前記キャリア供給層をエピタキシャル成長した後に、前記基板生産物の上に絶縁膜を形成する工程と、

前記絶縁膜を形成した後に、前記開口の前記斜面にゲート電極を形成する工程と、

を備える、請求項1〜請求項10のいずれか一項に記載された窒化物電子デバイスを作製する方法。

【請求項12】

前記半導体積層の前記処理面のドナー性不純物の濃度は5×1017cm−3以下である、請求項1〜請求項11のいずれか一項に記載された窒化物電子デバイスを作製する方法。

【請求項13】

前記チャネル層はアンドープ窒化ガリウム系半導体層を含み、

前記チャネル層の厚さは20nm以上であり、400nm以下である、請求項1〜請求項12のいずれか一項に記載された窒化物電子デバイスを作製する方法。

【請求項14】

前記電流ブロック層の第2のIII族窒化物半導体はp型GaNであり、

前記電流ブロック層の膜厚は0.1μm以上であり、2.0μm以下であり、

前記電流ブロック層のp型GaNにはマグネシウム(Mg)が添加されており、

前記電流ブロック層のMg濃度は、5×1016cm−3以上であり、5×1018cm−3以上である、請求項1〜請求項13のいずれか一項に記載された窒化物電子デバイスを作製する方法。

【請求項15】

前記自立基板の上にドレイン電極を形成する工程を備える請求項1〜請求項14のいずれか一項に記載された窒化物電子デバイスを作製する方法。

【請求項16】

窒化物電子デバイスであって、

支持基体の主面上に順に設けられたドリフト層、電流ブロック層及びコンタクト層を含むと共に、前記コンタクト層から前記電流ブロック層を介して前記ドリフト層に至る側面を有する半導体積層と、

前記側面の上に設けられ、窒化ガリウム系半導体からなるチャネル層と、

前記側面の上に設けられ、III族窒化物からなるキャリア供給層と、

前記側面の上に設けられたゲート電極と、

前記半導体積層の上に設けられたソース電極と、

前記半導体積層及び前記支持基体のいずれかに設けられドレイン電極と、

を備え、

前記チャネル層は前記キャリア供給層との前記側面との間に設けられ、

前記半導体積層の前記側面と前記チャネル層との界面におけるドナー性欠陥の濃度は5×1017cm−3以下であり、

前記ドリフト層は、第1の窒化ガリウム系半導体からなり、

前記電流ブロック層は、第2の窒化ガリウム系半導体からなり、

前記コンタクト層は、第3の窒化ガリウム系半導体からなり、

前記キャリア供給層の前記III族窒化物のバンドギャップは、前記チャネル層の前記窒化ガリウム系半導体のバンドギャップより大きく、

前記ドリフト層及び前記コンタクト層はn型を有し、

前記電流ブロック層はp型を有する、窒化物電子デバイス。

【請求項17】

前記ドリフト層の前記第1の窒化ガリウム系半導体はn型GaNであり、

前記ドリフト層の膜厚は1μm以上であり、10μm以下であり、

前記ドリフト層のキャリア濃度は、1×1015cm−3以上であり、3×1016cm−3以上である、請求項16に記載された窒化物電子デバイス。

【請求項18】

前記電流ブロック層の前記第2の窒化ガリウム系半導体はp型GaNであり、

前記電流ブロック層の膜厚は0.1μm以上であり、2.0μm以下であり、

前記電流ブロック層のp型GaNにはマグネシウム(Mg)が添加されており、

前記電流ブロック層のMg濃度は、5×1016cm−3以上であり、5×1018cm−3以上である、請求項16又は請求項17に記載された窒化物電子デバイス。

【請求項19】

前記コンタクト層の前記第3の窒化ガリウム系半導体はn型GaNであり、

前記コンタクト層の膜厚は0.1μm以上であり、1.0μm以下であり、

前記コンタクト層のn型GaNにはシリコン(Si)が添加されており、

前記コンタクト層のキャリア濃度は、1×1016cm−3以上である、請求項16〜請求項18のいずれか一項に記載された窒化物電子デバイス。

【請求項20】

前記キャリア供給層はAlXGa1−XN(0<X<1)層を含み、

前記キャリア供給層の厚さは5nm以上であり、40nm以下であり、

前記チャネル層はアンドープGaN層を含み、

前記チャネル層の厚さは20nm以上であり、400nm以下であり、

前記キャリア供給層は前記チャネル層にヘテロ接合を成す、請求項16〜請求項19のいずれか一項に記載された窒化物電子デバイス。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【公開番号】特開2013−74061(P2013−74061A)

【公開日】平成25年4月22日(2013.4.22)

【国際特許分類】

【出願番号】特願2011−211456(P2011−211456)

【出願日】平成23年9月27日(2011.9.27)

【出願人】(000002130)住友電気工業株式会社 (12,747)

【Fターム(参考)】

【公開日】平成25年4月22日(2013.4.22)

【国際特許分類】

【出願日】平成23年9月27日(2011.9.27)

【出願人】(000002130)住友電気工業株式会社 (12,747)

【Fターム(参考)】

[ Back to top ]